#### Universite des Sciences et Technologies de Lille

#### ECOLE DOCTORALE SCIENCES POUR L'INGENIEUR

#### **THESE**

En vue de l'obtention du grade :

#### DOCTEUR DE L'UNIVERSITE

Spécialité : Microondes et Microtechnologies

Présentée et soutenue publiquement par

#### Jean GORISSE

Le 15 Novembre 2010

## Regulation of power amplifiers under VSWR conditions in CMOS 65nm for 60GHz WLAN applications

#### Composition du jury:

- Directeur : Andreas KAISER Professeur à l'ISEN-Lille

- Tuteur industriel : Andreia CATHELIN Ingénieur R&D STMicroelectronics

- Co-directeur : Eric KERHERVE Professeur à l'université de Bordeaux 1

- Président : Nathalie ROLLAND Professeur à l'université de Lille 1

- Rapporteurs : Bram NAUTA Professeur à l'université de Twente

Yann DEVAL Professeur à l'université de Bordeaux 1

- Invité : Philippe TORREGROSSA Ingénieur Agilent Technologies

#### Acknowledgements

Pursuing a PhD project is painful with hardships and frustrations. But it is also an enjoyable experience with encouragement, trust and help of so many people. And it is even truer when working with several laboratories and companies, as I did. I hence express in the following words my gratitude to all who have directly or indirectly contributed to this work.

First, I would like to express my deep and sincere gratitude to my supervisor, Professor Andreas Kaiser, IEMN-ISEN laboratory in Lille, who has directed this PhD. His wide knowledge has been of great value to me and we have had many fascinating discussions on a large variety of topics.

I am deeply grateful to my industrial supervisor, Andreia Cathelin, senior design expert in STMicroelectronics in Crolles. Her perpetual trust in my work was a major help to overcome my many doubts and wilting all along this PhD.

I wish to express my warm and sincere thanks to my supervisor, Professor Eric Kerhervé, IMS laboratory in Bordeaux. His perfect knowledge of the wave propagation mechanisms and his wide experience on RF Power Amplifiers were of prior importance for this work.

Then, I would like to acknowledge Professor Bram Nauta from the University of Twente and Professor Yann Deval from the University of Bordeaux for having accepted to report on this PhD thesis. I met both of them at ESSCIRC conference, Athens, in 2009; and I did not now at the time I was having a drink with my two PhD reviewers...

I am deeply grateful to Professor Nathalie Rolland, IEMN laboratory, who has accepted to chair my PhD defense. She also provided me access to the high-end measurement equipment available in her laboratory.

I wish to express my warm thanks to Philippe Torregrossa from Agilent Technologies. We have worked together on the system co-simulation aspects (detailed in the fifth chapter) where his perfect knowledge of the simulator engines and his efforts to understand my circuit designs have been of great value.

I also wish to kindly acknowledge Elisabeth Delos and Julien Fontaine from IEMN, Magali De Matos from IMS, and Christian Badard, Dimitri Goguet and Caroline Arnaud from STMicroelectronics for the helpful support and constructive advices on the circuit measurements.

I acknowledge Valérie Vandenhende from IEMN-ISEN and Pascale Maillet-Contoz for the administrative support.

I wish to express my warm and sincere thanks to Baudouin Martineau, Nicolas Seller, Olivier Richard, and Olivier Mazouffre for their technical support. I also wish to express my gratitude to all my colleagues from IEMN-ISEN, IMS and STMicroelectronics for the times we have spent together and the friendly discussions we have had.

I wish to kindly acknowledge my friends, my grand-parents, aunts and uncles, my cousins, the "Wednesday dinner club", the "pionniers" (explorers) from the scouting group of Le Mans. During those four years, we have spent many great moments of sharing and relaxation.

Finally I wish to acknowledge my family for the everyday help and its unconditional confidence. This work is dedicated to you, my parents, my brother Benoît and my sisters Marie, Thérèse and Elisabeth.

| Outline                                                                      |                                                                                                                                                       |                             |  |  |  |  |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|--|

| Acknowledgements Outline List of figures List of tables General introduction |                                                                                                                                                       |                             |  |  |  |  |

| СНАРТ                                                                        | ER I. CONTEXT OF THE STUDY                                                                                                                            | 15                          |  |  |  |  |

| -                                                                            | er introduction<br>er outline                                                                                                                         | 15<br>16                    |  |  |  |  |

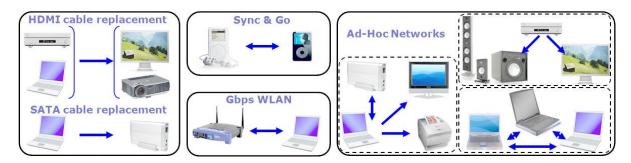

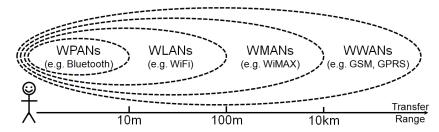

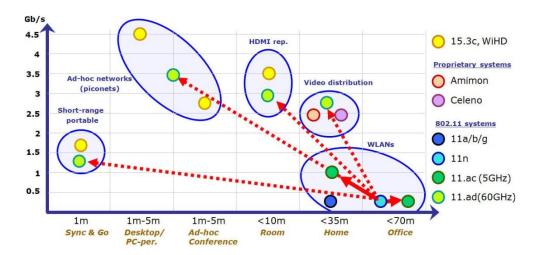

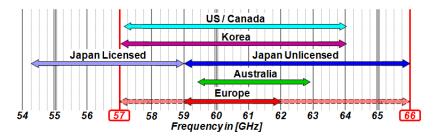

| I.1.<br>I.1.1.<br>I.1.2.<br>I.1.3.                                           | Building a WLAN-WPAN system at 60GHz Introduction and targeted applications Millimeter-Wave frequencies The IEEE 802.15.3c & WirelessHD standards     | 17<br>17<br>19<br>21        |  |  |  |  |

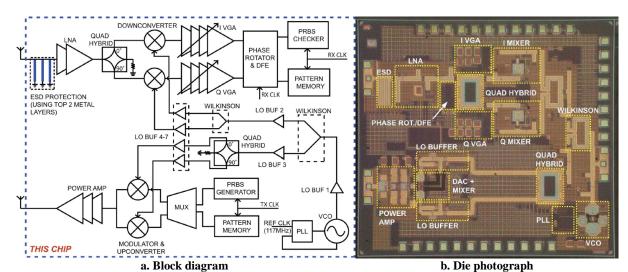

| I.2.<br>I.2.1.<br>I.2.2.                                                     | mmW transmitters in Silicon technology Transmitter architectures Power Amplifier                                                                      | <b>24</b><br>24<br>25       |  |  |  |  |

| I.3.<br>I.3.1.<br>I.3.2.<br>I.3.3.                                           | Antenna impedance variation with environmental conditions Introduction to standing wave formation 60GHz VSWR measurements Effects on Power Amplifiers | <b>29</b><br>29<br>32<br>36 |  |  |  |  |

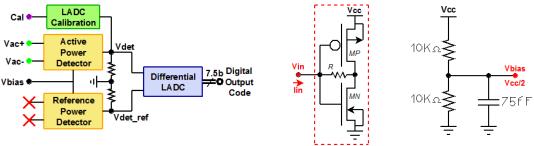

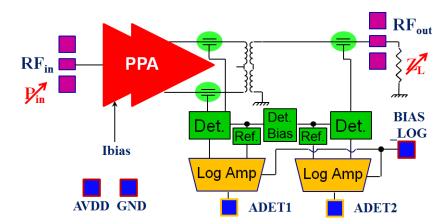

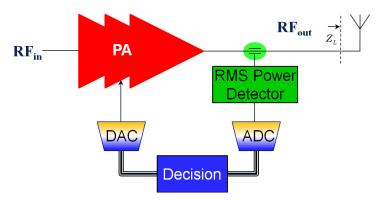

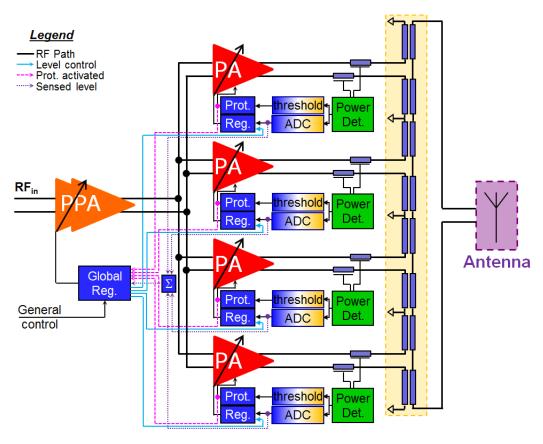

| 1.4.1.<br>1.4.2.<br>1.4.3.                                                   | Regulation of the antenna VSWR in a 60GHz power amplifier System architecture Integrated power detectors System requirements                          | <b>42</b><br>42<br>43<br>47 |  |  |  |  |

| -                                                                            | er conclusion<br>er references                                                                                                                        | 48<br>49                    |  |  |  |  |

| СНАРТ                                                                        | ER II. A 60GHZ 65NM CMOS POWER DETECTOR                                                                                                               | 53                          |  |  |  |  |

| •                                                                            | er introduction<br>er outline                                                                                                                         | 53<br>54                    |  |  |  |  |

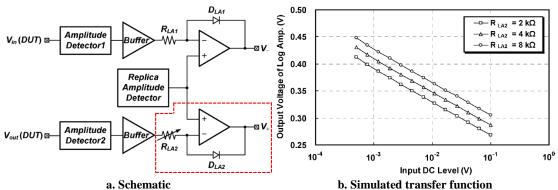

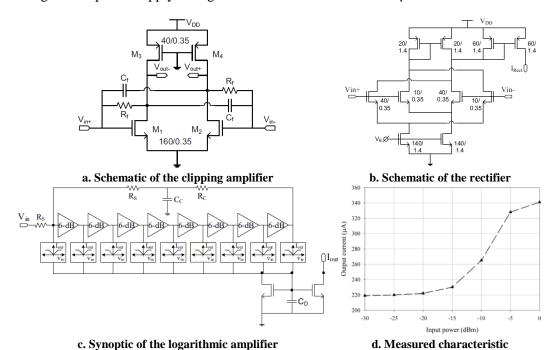

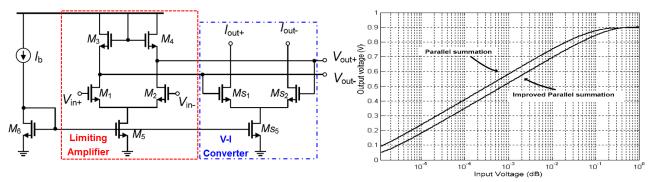

| II.1.<br>II.1.1.<br>II.1.2.                                                  | State of the art Power detector Power coupler                                                                                                         | <b>55</b><br>55<br>62       |  |  |  |  |

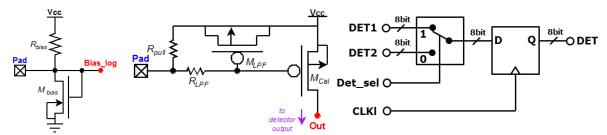

| II.2.<br>II.2.1.<br>II.2.2.                                                  | Chosen solution and Circuit Design Power detector Power coupler                                                                                       | <b>66</b><br>66<br>71       |  |  |  |  |

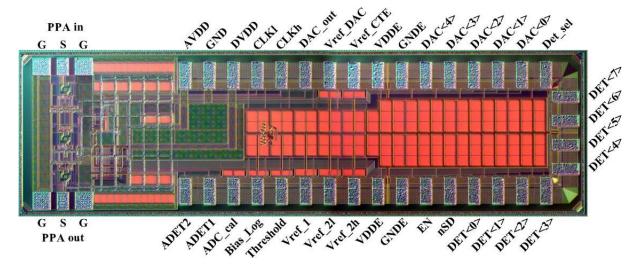

| II.3.1.<br>II.3.2.<br>II.3.3.                                                | Circuit physical implementation for testability Circuit synoptic Circuit implementation Full circuit physical implementation                          | <b>78</b><br>78<br>78<br>81 |  |  |  |  |

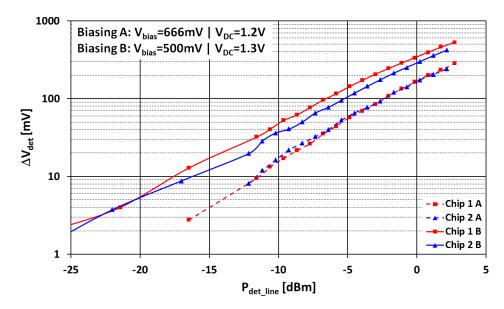

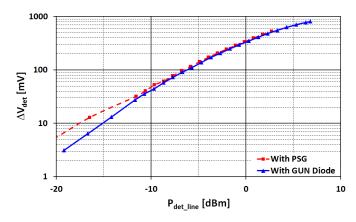

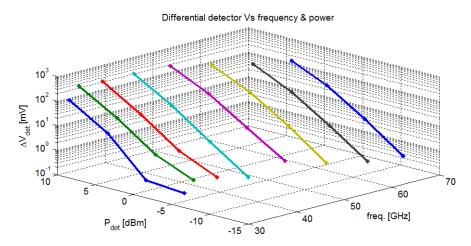

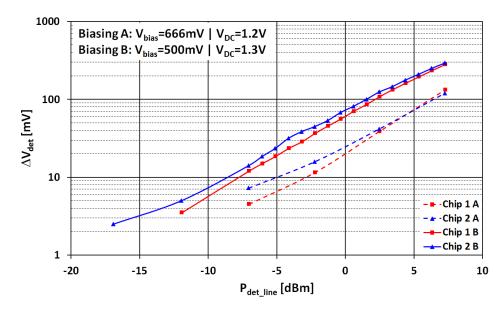

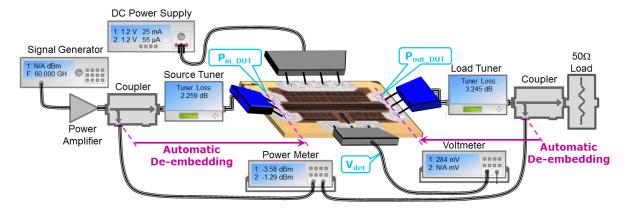

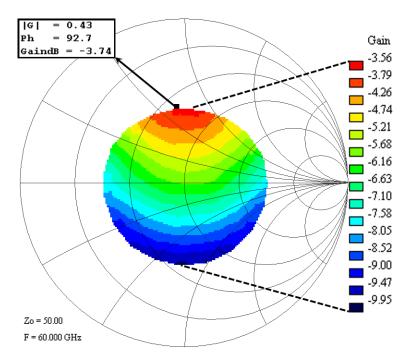

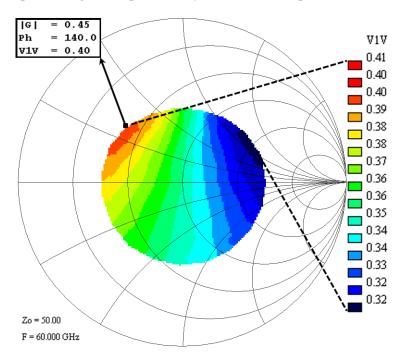

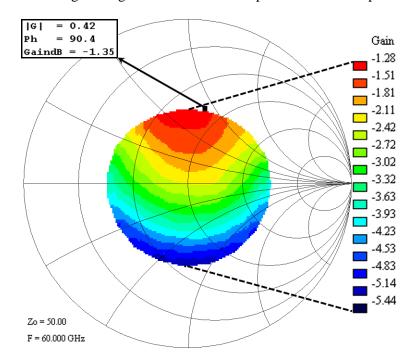

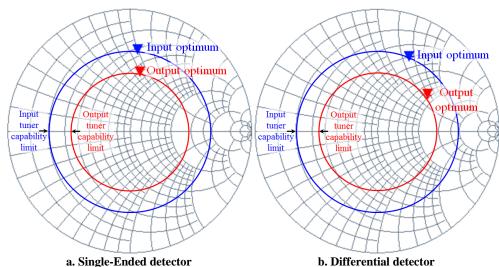

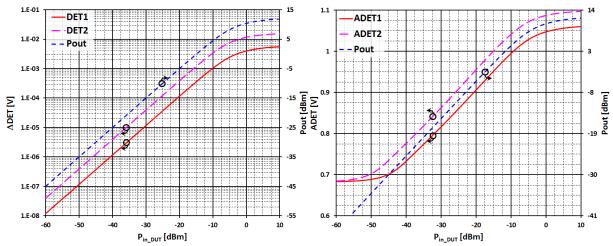

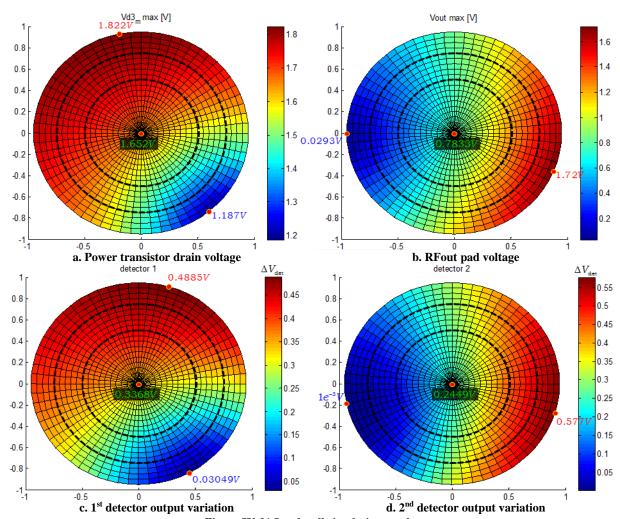

| II.4.1.<br>II.4.2.<br>II.4.3.                                                | Measurement results S-parameters Input power sweep Load-pull measurements                                                                             | <b>82</b><br>82<br>86<br>90 |  |  |  |  |

| -                                                                            | er conclusion<br>er references                                                                                                                        | 95<br>96                    |  |  |  |  |

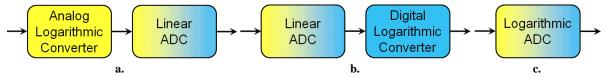

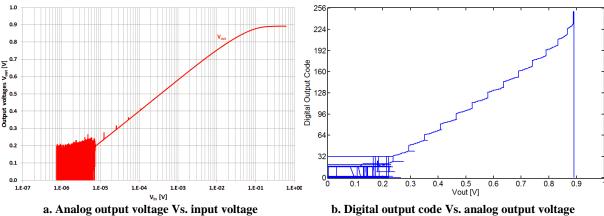

| CHAPTER III. LOGARITHMIC ANALOG-TO-DIGITAL CONVERTER                                                                                                                                                                           | 99                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Chapter introduction<br>Chapter outline                                                                                                                                                                                        | 99<br>100                              |

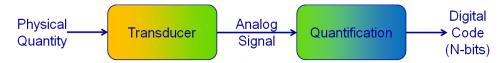

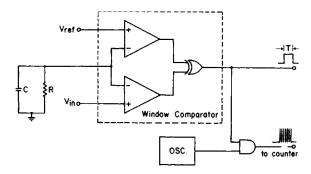

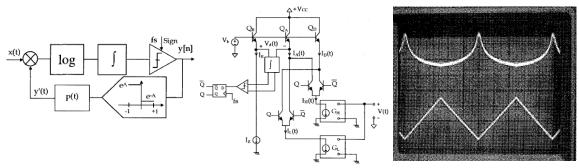

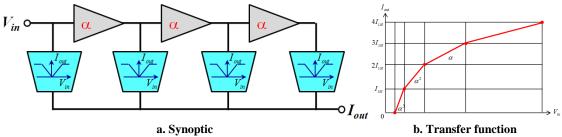

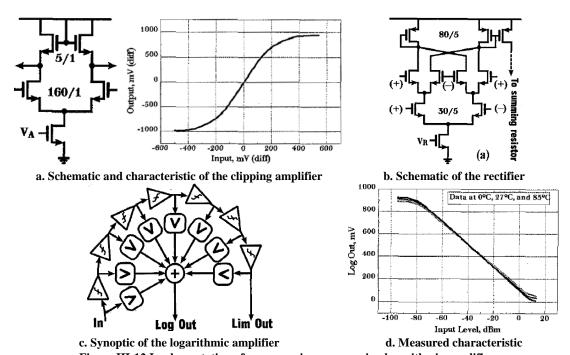

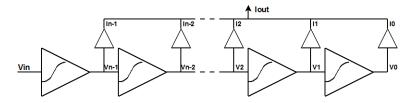

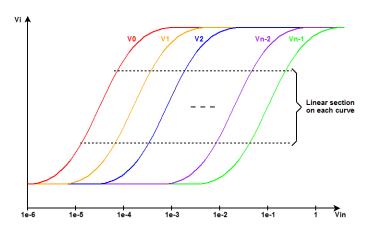

| III.1. Needs for logarithmic ADC & existing solutions III.1.1. Needs III.1.2. State-of-the-art                                                                                                                                 | <b>101</b><br>101<br>102               |

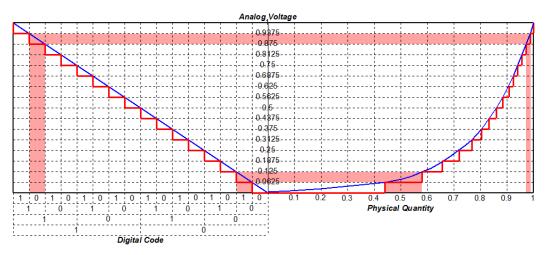

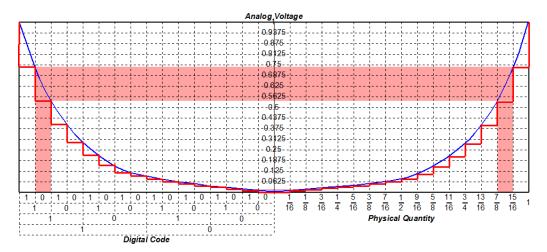

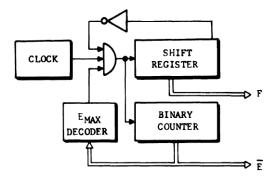

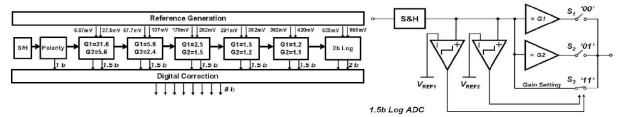

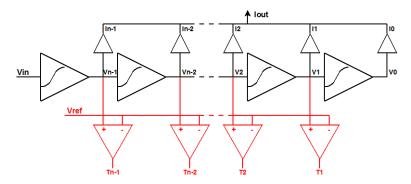

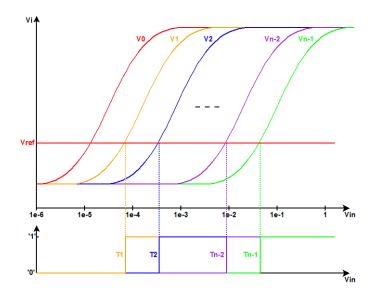

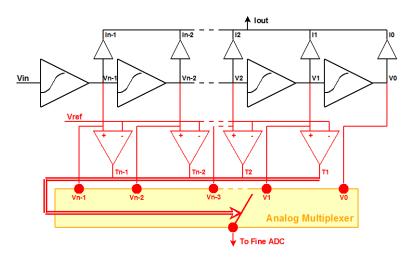

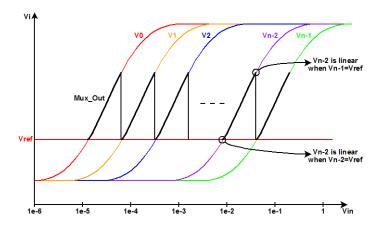

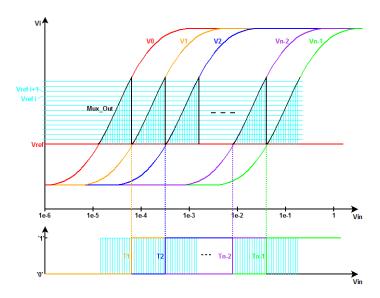

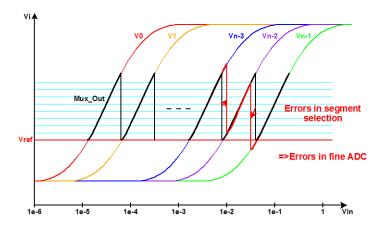

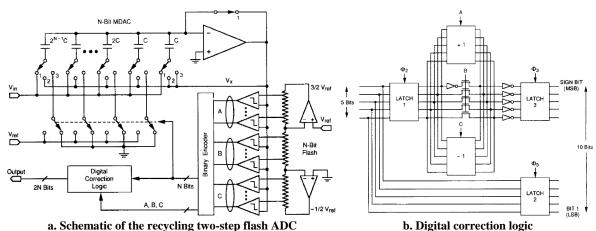

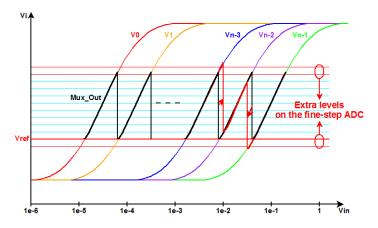

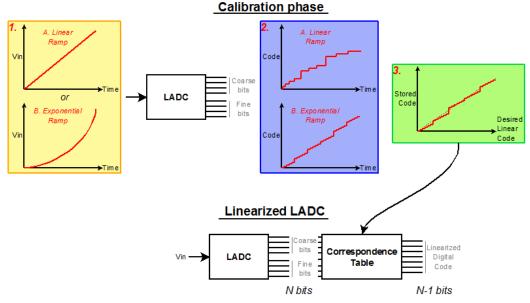

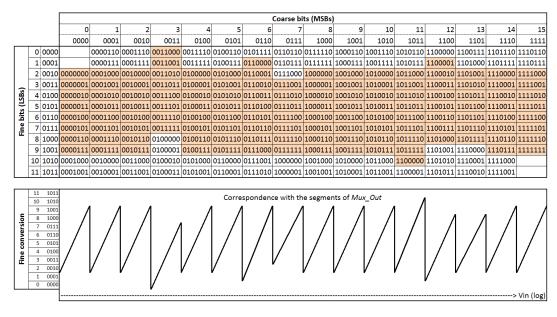

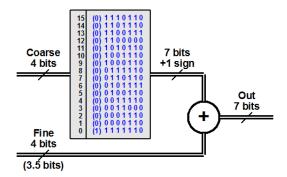

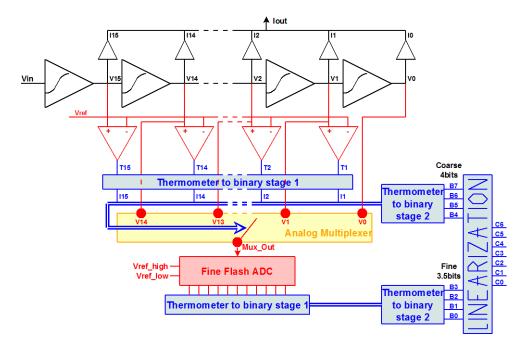

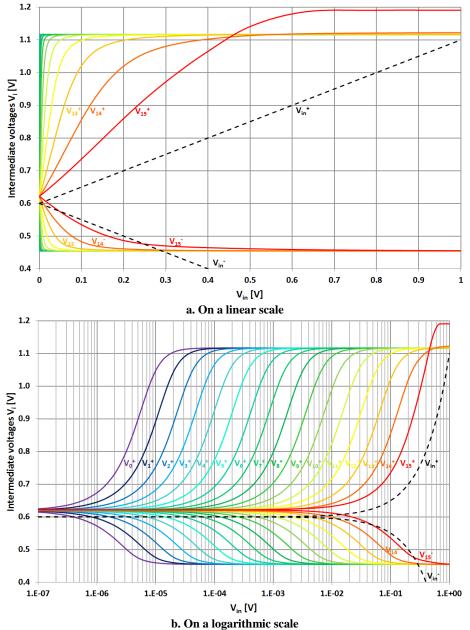

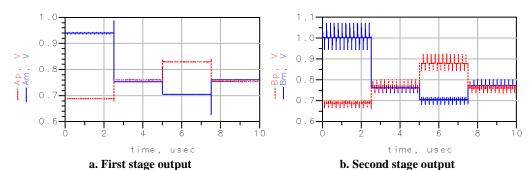

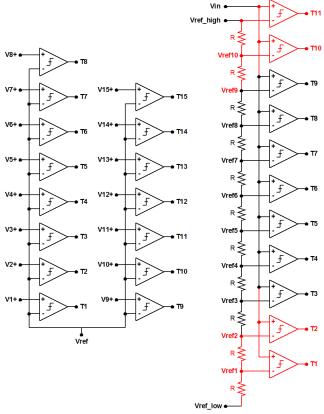

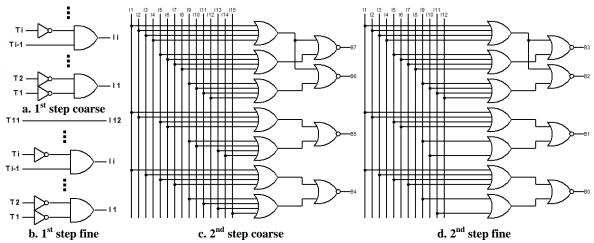

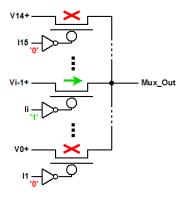

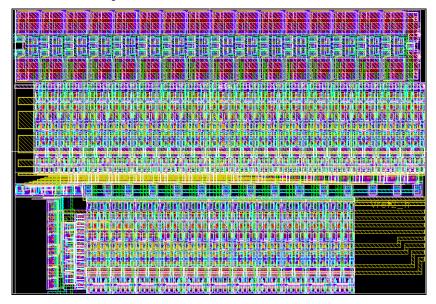

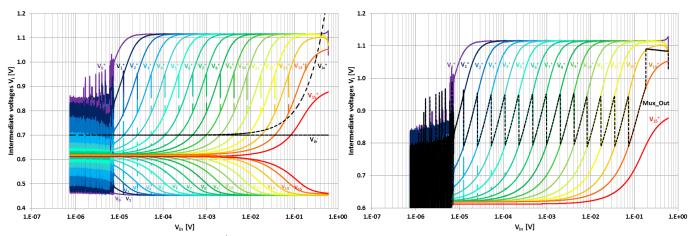

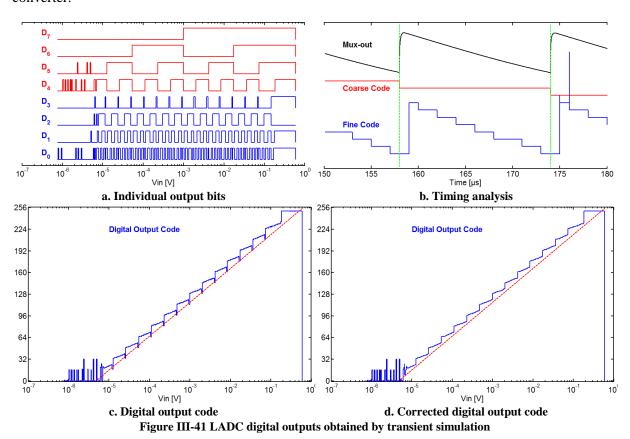

| III.2.1. Observations on a progressive compression logarithmic amplifier III.2.2. Coarse conversion III.2.3. Fine conversion III.2.4. Calibration considerations III.2.5. Advantages of this innovating solution               | 109<br>109<br>110<br>111<br>113<br>116 |

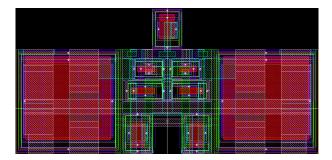

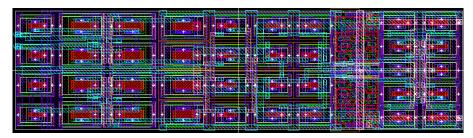

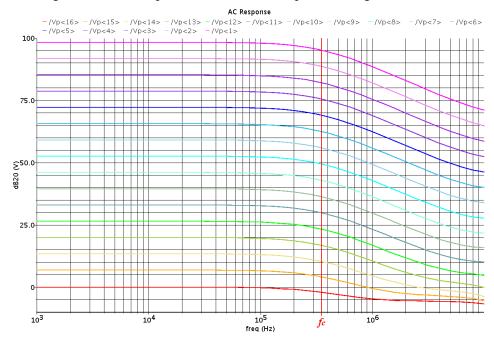

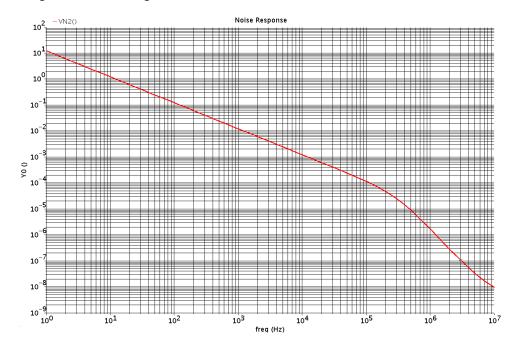

| III.3.1. Implementation III.3.2. Design considerations III.3.3. Transient simulations III.3.4. Frequency and noise limitations                                                                                                 | 117<br>117<br>118<br>126<br>129        |

| Chapter conclusion Chapter references                                                                                                                                                                                          | 131<br>132                             |

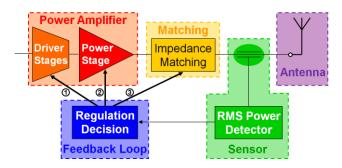

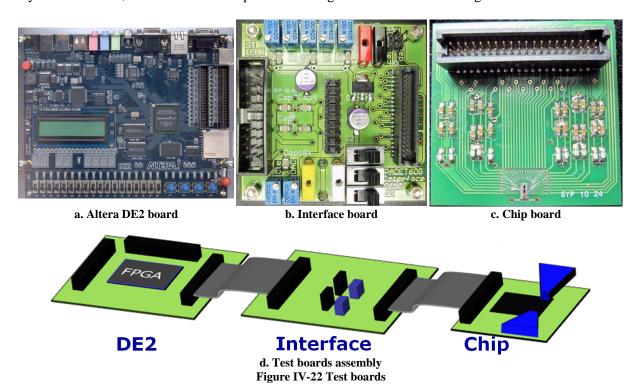

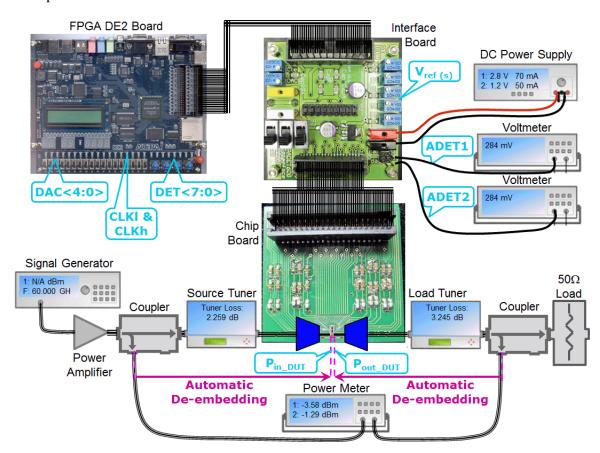

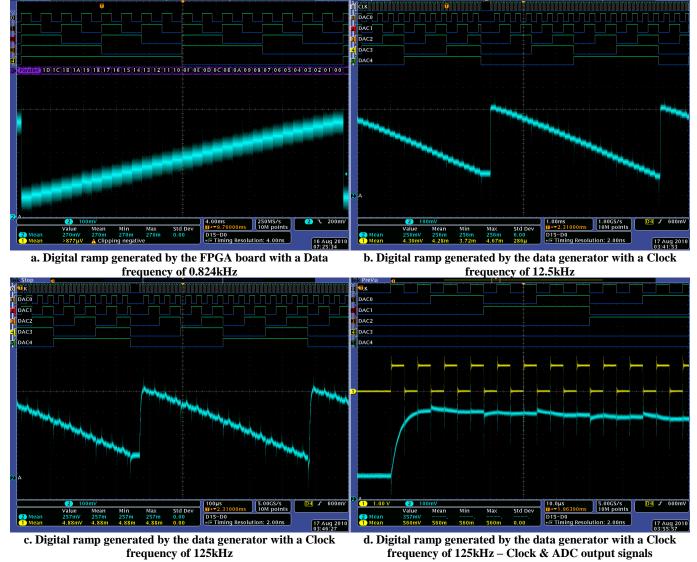

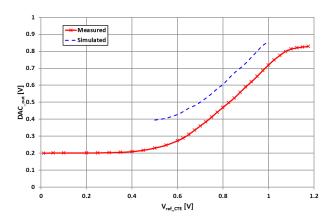

| CHAPTER IV. VSWR REGULATION                                                                                                                                                                                                    | 133                                    |

| Chapter introduction Chapter outline                                                                                                                                                                                           | 133<br>134                             |

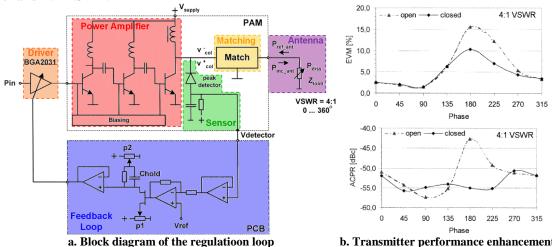

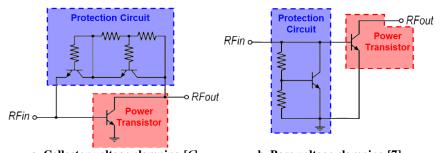

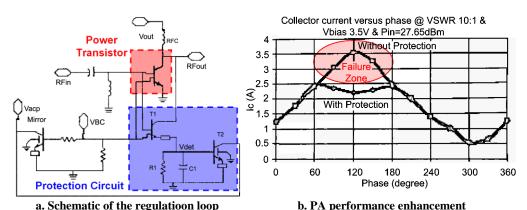

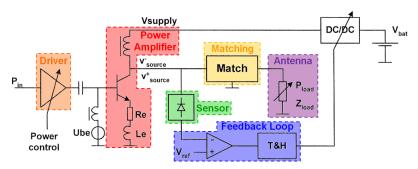

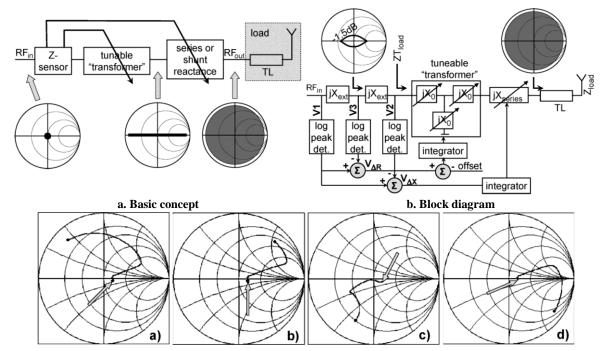

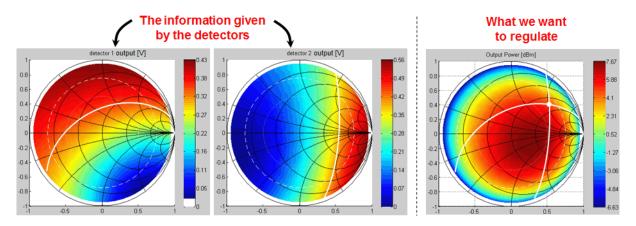

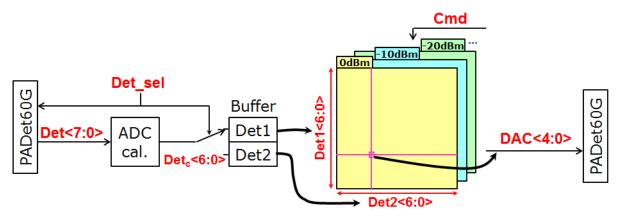

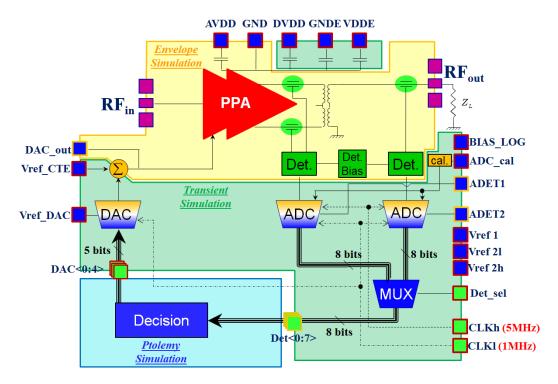

| IV.1. Regulation architecture IV.1.1. State of the art IV.1.2. Proposed solutions                                                                                                                                              | <b>135</b><br>135<br>139               |

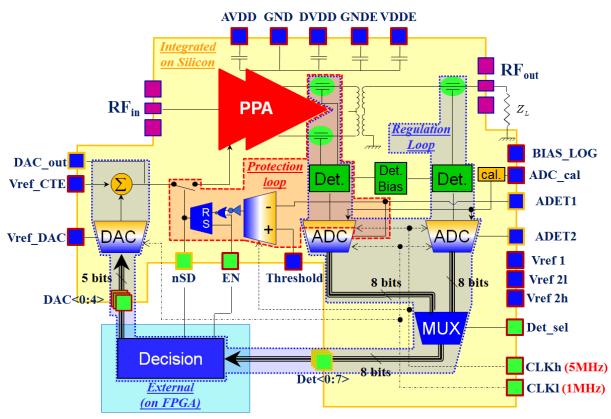

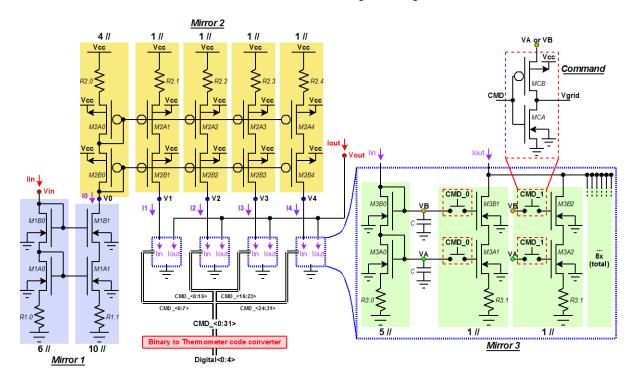

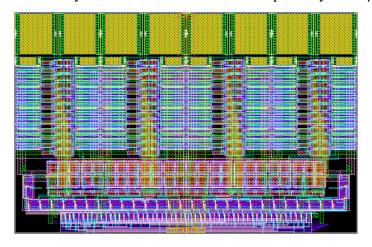

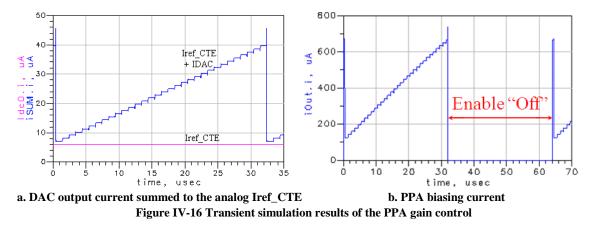

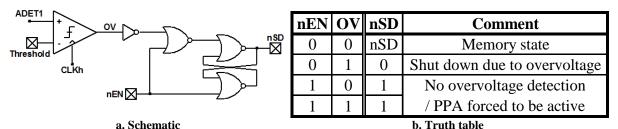

| <ul> <li>IV.2. Circuit design and implementation for testability</li> <li>IV.2.1. Add-ons on already presented blocks</li> <li>IV.2.2. Adjacent circuits</li> <li>IV.2.3. Full circuit physical implementation</li> </ul>      | 141<br>141<br>143<br>148               |

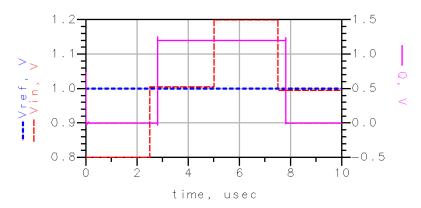

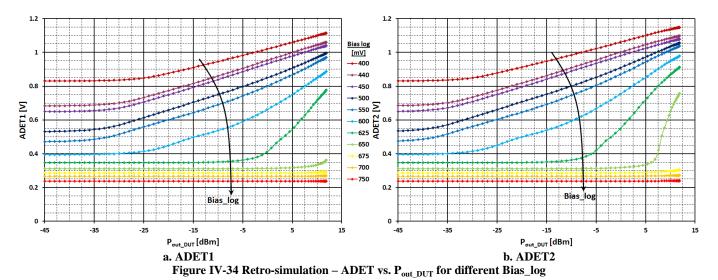

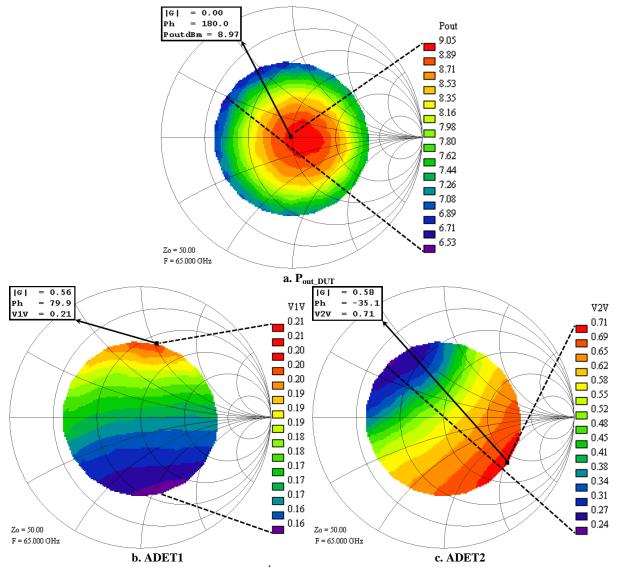

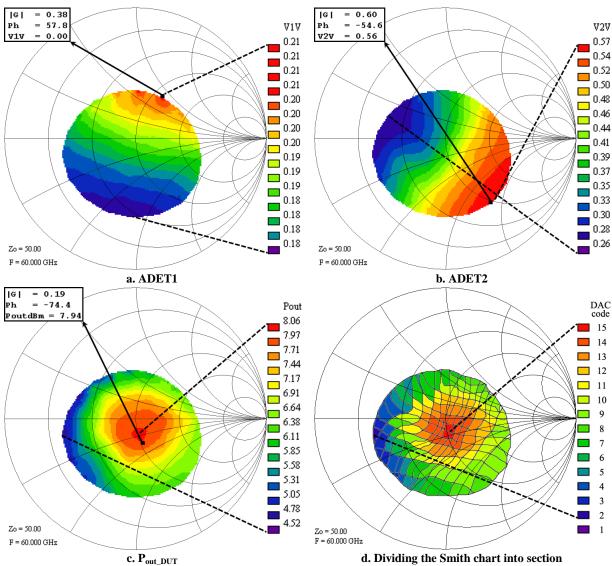

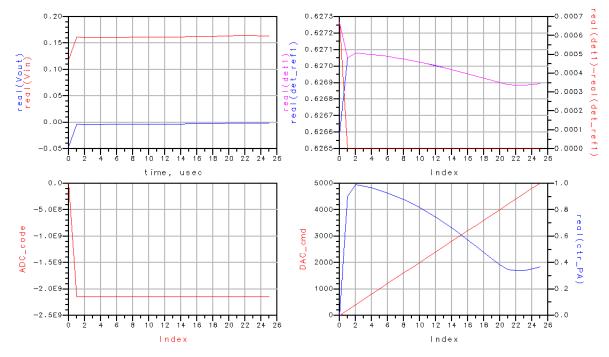

| <ul> <li>IV.3. Analog open-loop simulations</li> <li>IV.3.1. Simulation configuration</li> <li>IV.3.2. Power sweep simulations</li> <li>IV.3.3. Load-pull simulations</li> </ul>                                               | 149<br>149<br>149<br>150               |

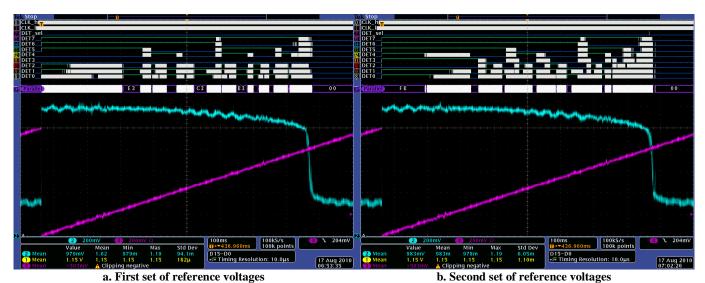

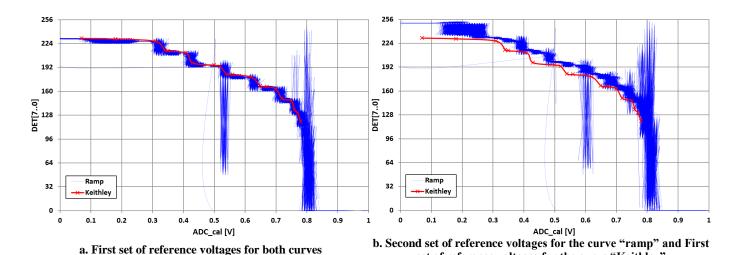

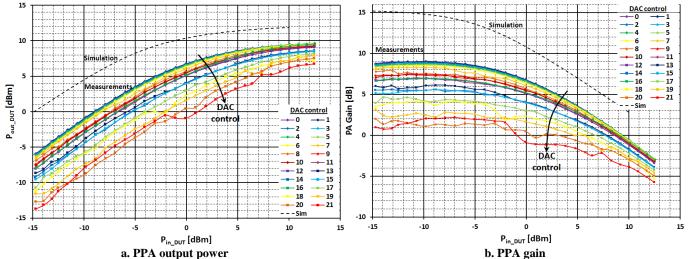

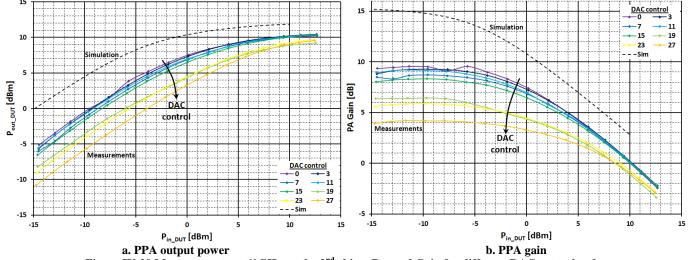

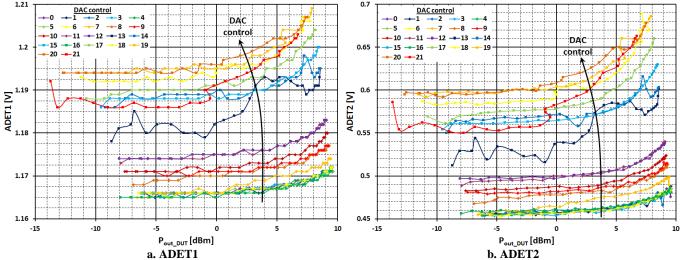

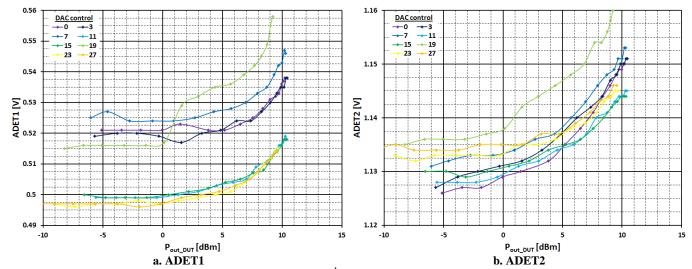

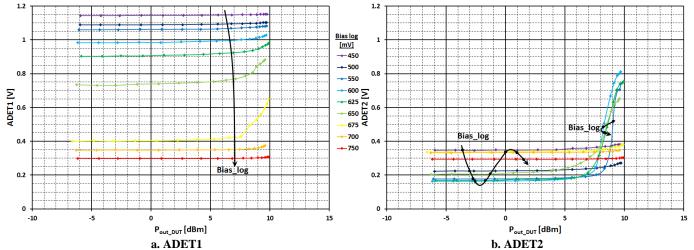

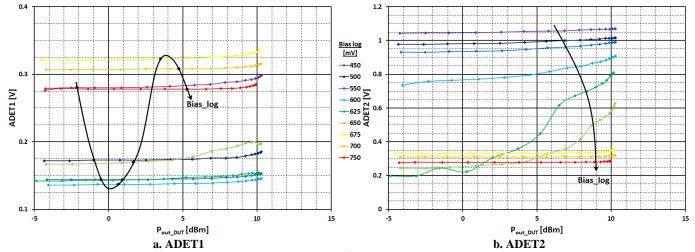

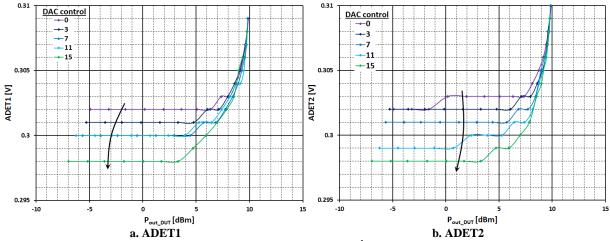

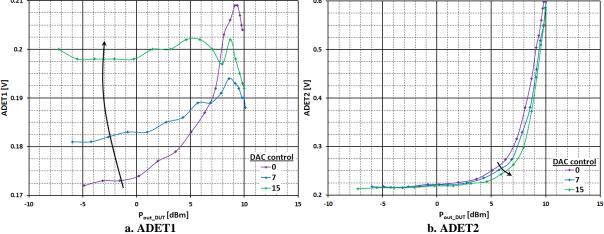

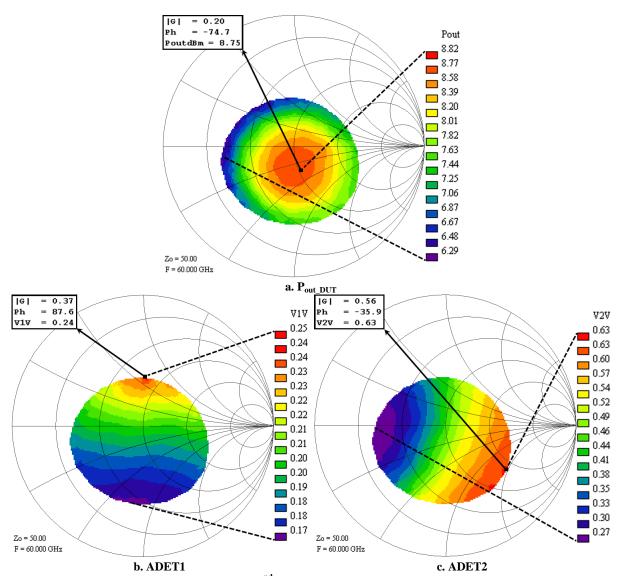

| IV.4. Measurement results  IV.4.1. Measurement configuration and procedure  IV.4.2. DAC measurements  IV.4.3. LADC measurements  IV.4.4. Power sweep measurements  IV.4.5. Load-pull measurements                              | 152<br>152<br>154<br>156<br>158<br>164 |

| <ul> <li>IV.5. VSWR-regulation concept</li> <li>IV.5.1. Concept overview</li> <li>IV.5.2. Algorithm to be implemented in the digital decision block</li> <li>IV.5.3. Table establishment in a simple practical case</li> </ul> | <b>166</b><br>166<br>166<br>167        |

| Chapter conclusion Chapter references                                                                                                                                                                                          | 169<br>170                             |

| CHAPTER V. SYSTEM SIMULATIONS                           | 171        |

|---------------------------------------------------------|------------|

| Chapter introduction Chapter outline                    | 171<br>172 |

| ·                                                       |            |

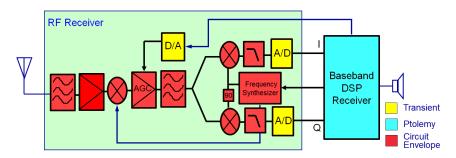

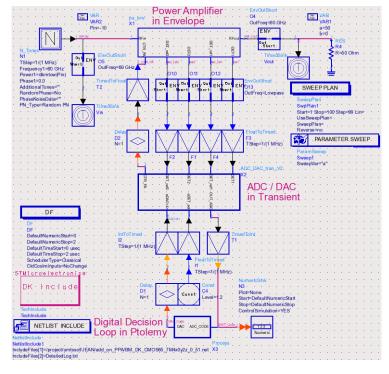

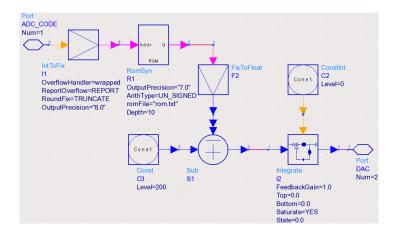

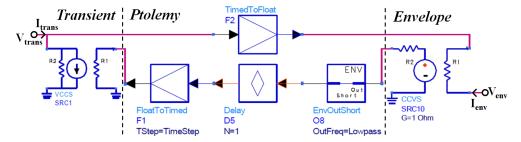

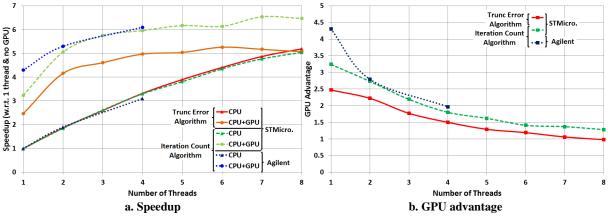

| V.1. System co-simulation                               | 173        |

| V.1.1. Introduction V.1.2. Co-simulation implementation | 173<br>174 |

| V.1.3. Difficulties and solutions                       | 178        |

| V.1.4. Simulation results                               | 180        |

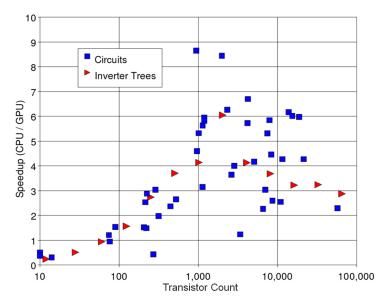

| V.2. Transient simulation speedup                       | 181        |

| V.2.1. Theoretical speedup                              | 181        |

| V.2.2. Practical speedup                                | 183        |

| Chapter conclusion Chapter references                   | 185<br>186 |

| * * *                                                   | 180        |

| ጥ ጥ ጥ                                                   |            |

| General conclusion                                      | 187        |

| Author's publications                                   | 190        |

| * * *                                                   |            |

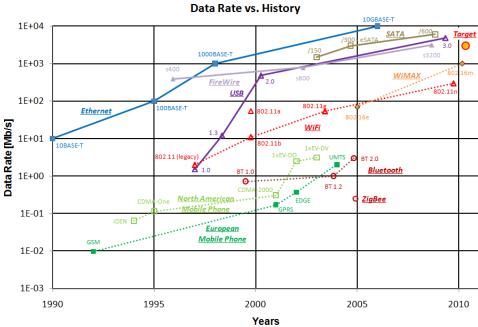

| ANNEX A. TRANSFERRING DATA, AUDIO AND VIDEO IN 2010     | 191        |

| Overview                                                | 191        |

| Outline                                                 | 191        |

| A.1. Wired connections                                  | 192        |

| A.2. Wireless connections                               | 193        |

| A.3. Discussion                                         | 197        |

| References                                              | 198        |

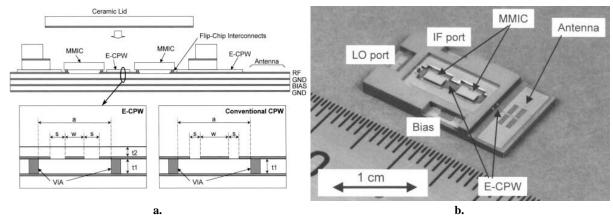

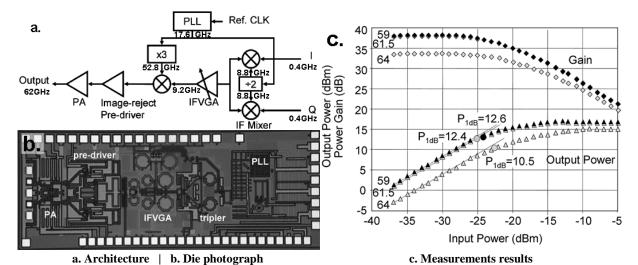

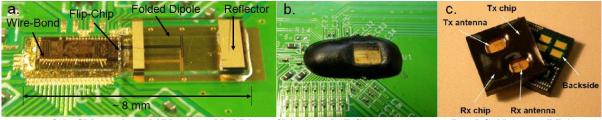

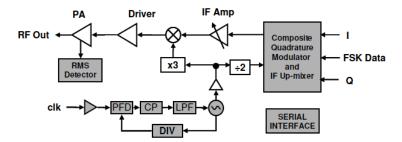

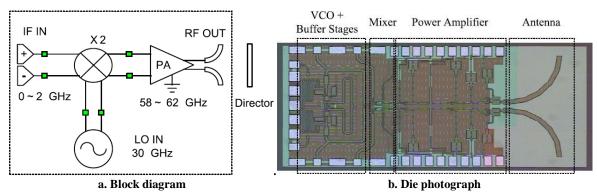

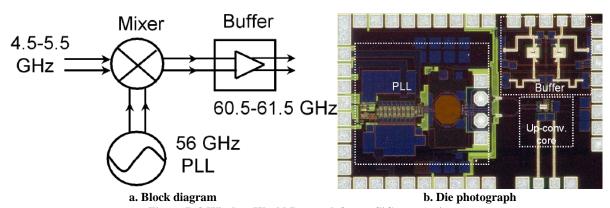

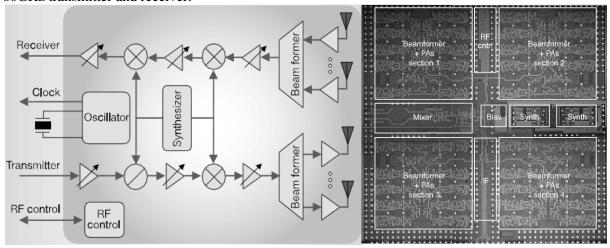

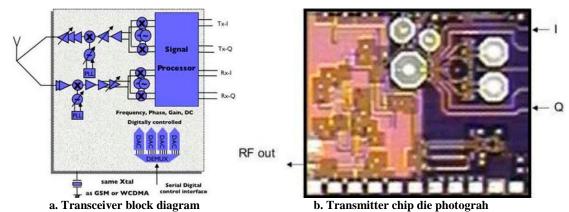

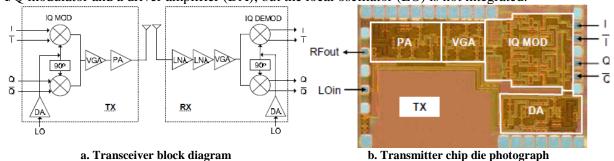

| ANNEX B. MMW TRANSMITTERS                               | 199        |

| Overview                                                | 199        |

| Outline                                                 | 199        |

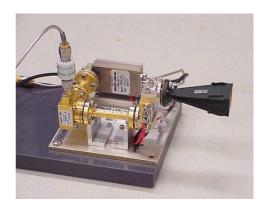

| B.1. From III-V technologies                            | 200        |

| B.2 to SiGe technologies                                | 201        |

| B.3 and CMOS technology                                 | 204        |

| References                                              | 206        |

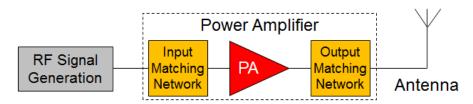

| ANNEX C. OVERVIEW ON POWER AMPLIFIER                    | 207        |

| Overview                                                | 207        |

| Outline                                                 | 207        |

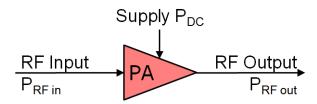

| C.1. Overview on PA characteristics                     | 208        |

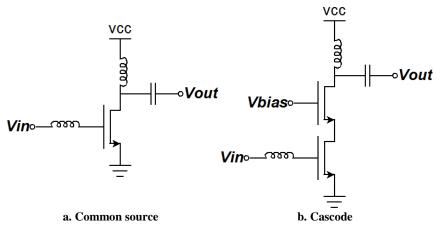

| C.2. Overview on PA topologies                          | 210        |

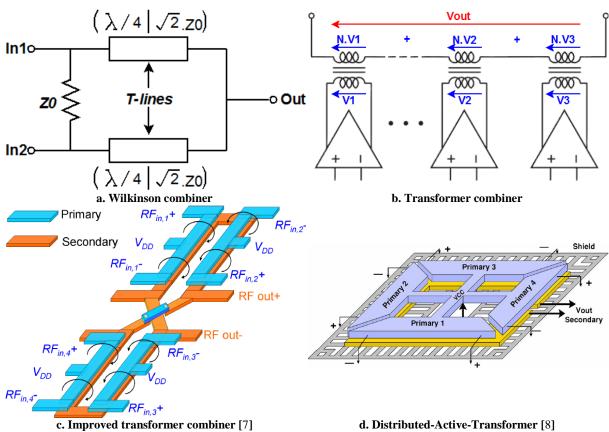

| C.3. Power combining techniques                         | 211        |

| References                                              | 212        |

|      | ANNEX                                                        | D. N-PORT NETWORKS                                                                                                                                                                                                              | 213                                                                |

|------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|      | Overvi<br>Outline                                            |                                                                                                                                                                                                                                 | 213<br>213                                                         |

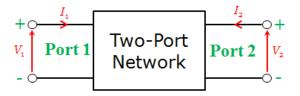

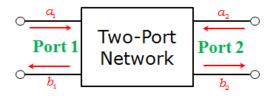

|      | D.1.                                                         | Definition of Z, Y, h, ABCD, S & T-parameters                                                                                                                                                                                   | 214                                                                |

|      | D.2.                                                         | Conversion between parameters                                                                                                                                                                                                   | 216                                                                |

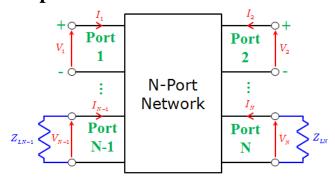

|      | D.3.                                                         | Conversion between parameters, generalization for N-port networks                                                                                                                                                               | 222                                                                |

|      | D.4.                                                         | N-port into M-port networks conversion                                                                                                                                                                                          | 223                                                                |

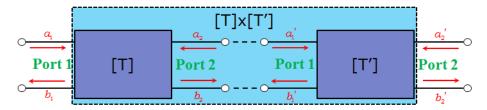

|      | D.5.                                                         | Cascading 2 two-port networks                                                                                                                                                                                                   | 224                                                                |

|      | D.6.                                                         | Cascading 2 three-port networks                                                                                                                                                                                                 | 225                                                                |

|      | D.7.                                                         | Cascading one three-port network and one two-port network                                                                                                                                                                       | 226                                                                |

|      | Refere                                                       | nces                                                                                                                                                                                                                            | 226                                                                |

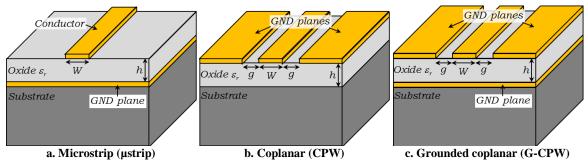

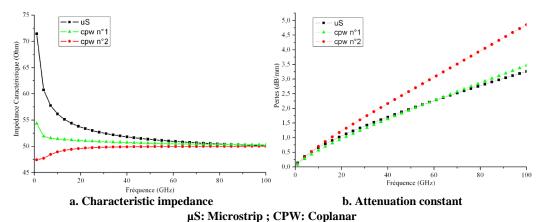

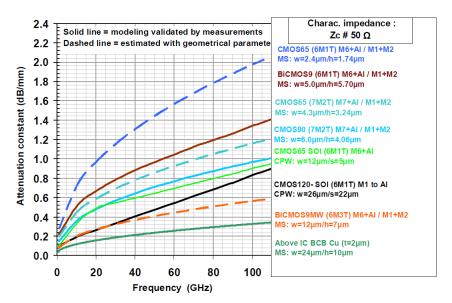

|      | ANNEX                                                        | E. T-LINES: THEORY AND MODELING                                                                                                                                                                                                 | 227                                                                |

|      | Overvi<br>Outline                                            |                                                                                                                                                                                                                                 | 227<br>227                                                         |

|      | E.1.                                                         | Theory on transmission lines                                                                                                                                                                                                    | 228                                                                |

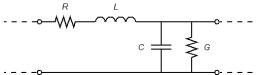

|      | E.2.                                                         | Modeling a T-line                                                                                                                                                                                                               | 230                                                                |

|      | Refere                                                       | nces                                                                                                                                                                                                                            | 232                                                                |

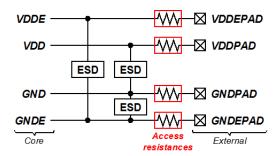

|      | ANNEX                                                        |                                                                                                                                                                                                                                 |                                                                    |

| TEST | ΓABILIT                                                      | Y                                                                                                                                                                                                                               | 233                                                                |

|      | Overvi                                                       |                                                                                                                                                                                                                                 | 233                                                                |

|      | Outline                                                      | •                                                                                                                                                                                                                               | 233                                                                |

|      | Outline <b>F.1.</b>                                          | Designed circuit for testability                                                                                                                                                                                                | 233<br><b>234</b>                                                  |

|      |                                                              |                                                                                                                                                                                                                                 |                                                                    |

|      | F.1.                                                         | Designed circuit for testability                                                                                                                                                                                                | 234                                                                |

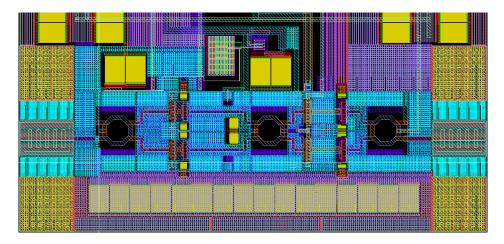

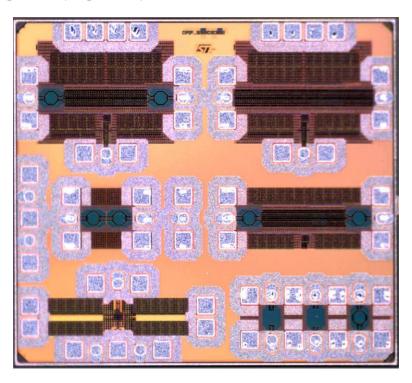

|      | F.1.<br>F.2.                                                 | Designed circuit for testability  Test structures  Die photograph                                                                                                                                                               | 234<br>238                                                         |

|      | F.1.<br>F.2.<br>F.3.                                         | Designed circuit for testability  Test structures  Die photograph  nces                                                                                                                                                         | 234<br>238<br>240                                                  |

|      | F.1.<br>F.2.<br>F.3.<br>Refere                               | Designed circuit for testability  Test structures  Die photograph  nces  G. DE-EMBEDDING TECHNIQUES                                                                                                                             | 234<br>238<br>240<br>240                                           |

|      | F.1. F.2. F.3. Refere                                        | Designed circuit for testability  Test structures  Die photograph  nces  G. DE-EMBEDDING TECHNIQUES                                                                                                                             | 234<br>238<br>240<br>240<br>241                                    |

|      | F.1. F.2. F.3. Refere  ANNEX Overvioon                       | Designed circuit for testability Test structures Die photograph nces  G. DE-EMBEDDING TECHNIQUES ew                                                                                                                             | 234<br>238<br>240<br>240<br>241<br>241<br>241                      |

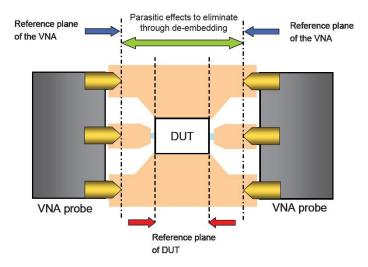

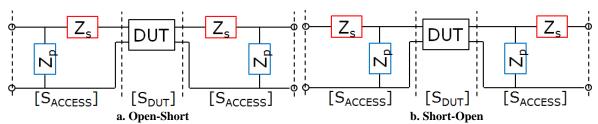

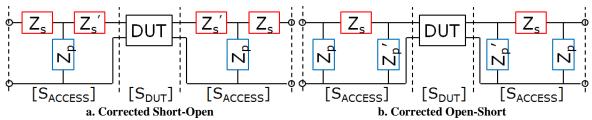

|      | F.1. F.2. F.3. Refere  ANNEX Overvice Outline G.1.           | Designed circuit for testability Test structures Die photograph nces  G. DE-EMBEDDING TECHNIQUES ew De-embedding theory                                                                                                         | 234<br>238<br>240<br>240<br>241<br>241<br>241<br>242               |

|      | F.1. F.2. F.3. Refere  ANNEX Overvior Outline G.1. G.2.      | Designed circuit for testability  Test structures  Die photograph  nces  G. DE-EMBEDDING TECHNIQUES  ew  De-embedding theory  Application to the balun circuits in PowDet60G  Power-sweep configuration de-embedding            | 234<br>238<br>240<br>240<br>241<br>241<br>241<br>242<br>245        |

|      | F.1. F.2. F.3. Refere  ANNEX Overvice Outline G.1. G.2. G.3. | Designed circuit for testability  Test structures  Die photograph  nces  G. DE-EMBEDDING TECHNIQUES  ew  De-embedding theory  Application to the balun circuits in PowDet60G  Power-sweep configuration de-embedding            | 234<br>238<br>240<br>240<br>241<br>241<br>241<br>242<br>245<br>246 |

|      | F.1. F.2. F.3. Refere  ANNEX Overvice Outline G.1. G.2. G.3. | Designed circuit for testability  Test structures  Die photograph  nces  G. DE-EMBEDDING TECHNIQUES  ew  De-embedding theory  Application to the balun circuits in PowDet60G  Power-sweep configuration de-embedding  nces  *** | 234<br>238<br>240<br>240<br>241<br>241<br>241<br>242<br>245<br>246 |

#### List of figures

| Figure I-1 Targeted applications of the new IEEE 802.15.3c standard                                                                   |     |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure I-2 WPAN, WLAN, WMAN, and WWAN definition with respect to the transfer range                                                   |     |

| Figure I-3 High Data Rate (HDR) standards with respect to the communication range and the data rate                                   |     |

| Figure I-4 Worldwide availability of a 60GHz frequency band                                                                           |     |

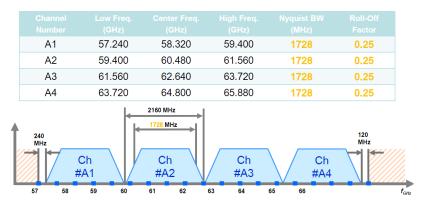

| Figure I-6 Channel organization of the 57-66GHz Band [18]                                                                             |     |

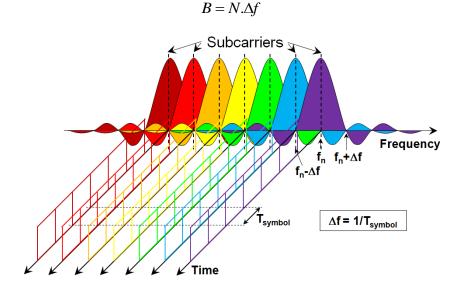

| Figure I-7 OFDM principle based on several orthogonal subcarriers                                                                     |     |

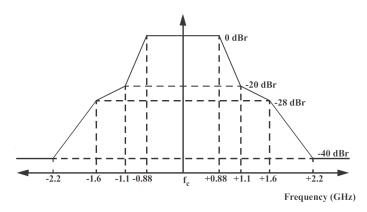

| Figure I-8 Transmitter spectral mask for one high rate channel                                                                        |     |

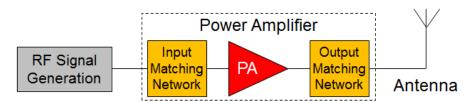

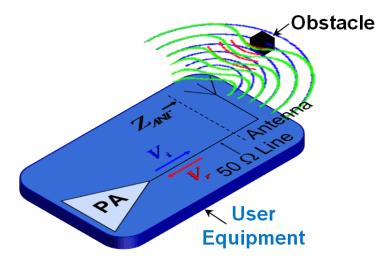

| Figure I-9 Power Amplifier and Antenna can be found in all RF transmitters                                                            |     |

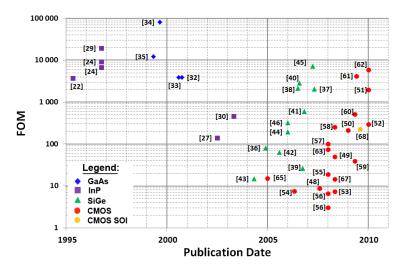

| Figure I-10 FOM of mmW PA with respect to the publication date                                                                        |     |

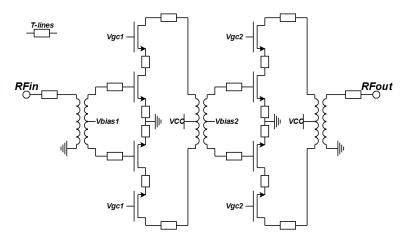

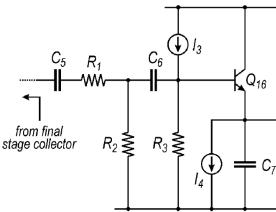

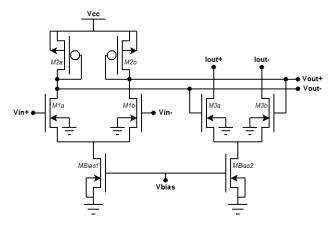

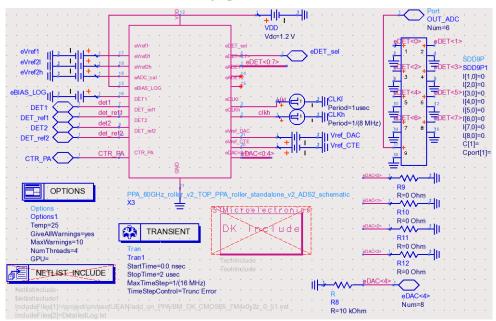

| Figure I-11 Schematic of the PPA used in this PhD work                                                                                | .27 |

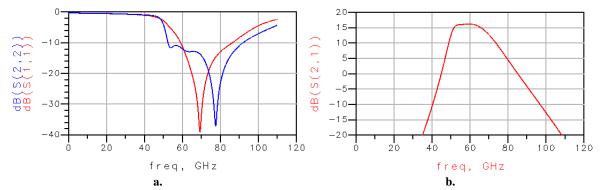

| Figure I-12 Simulated S <sub>11</sub> and S <sub>22</sub> matching (a.) and S <sub>21</sub> transmission (b.) S-parameters of the PPA |     |

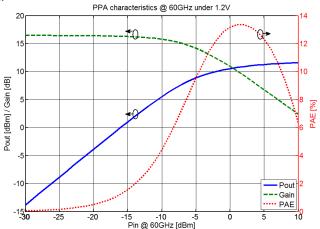

| Figure I-13 Output power, Gain and PAE characteristics of the 60GHz PPA with respect to the input power                               |     |

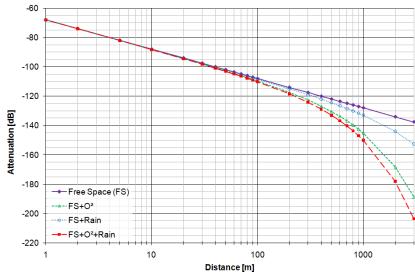

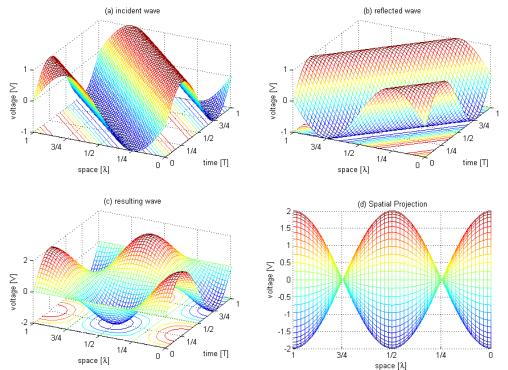

| Figure I-14 Creation of standing waves for a reflection coefficient of +1                                                             |     |

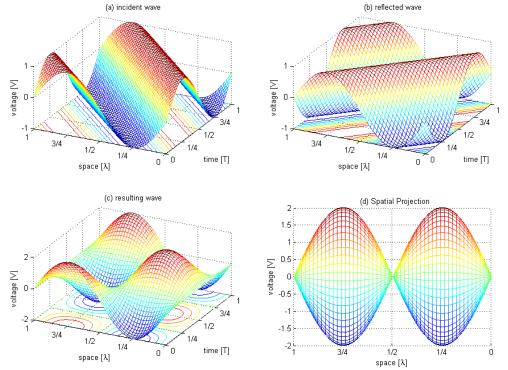

| Figure I-15 Creation of standing waves for a reflection coefficient of -1                                                             |     |

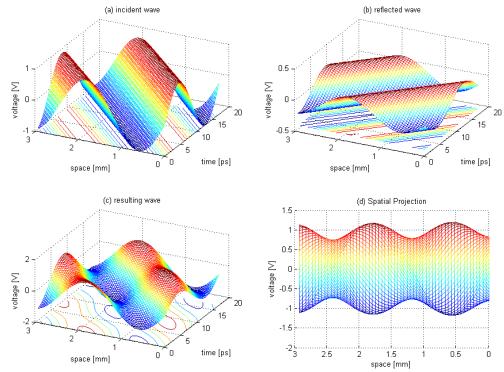

| Figure I-16 Creation of standing waves for Γ=0.2+j*0.1 and 1.2dB/mm attenuation coefficient on the T-line                             | .31 |

| Figure I-17 Link between electro-magnetic obstacles and antenna impedance variation                                                   |     |

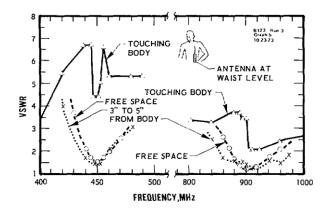

| Figure I-18 Link between electro-magnetic obstacles and antenna impedance variation [69]                                              |     |

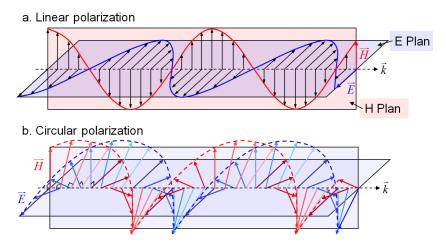

| Figure I-20 Linear (a.) and circular (b.) polarization of electromagnetic waves                                                       |     |

| Figure I-20 Efficac (a.) and Circum (b.) potatization of electroniagnetic waves.                                                      |     |

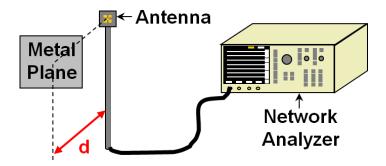

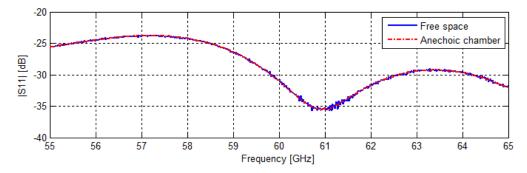

| Figure I-22 Free space vs. anechoic chamber reflection coefficient of the horn antenna                                                | .35 |

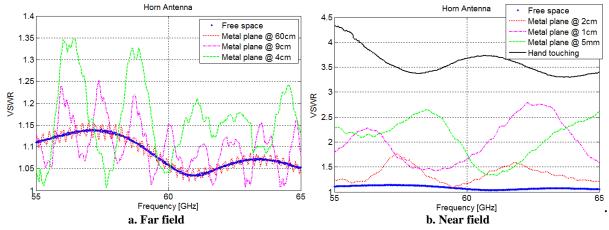

| Figure I-23 VSWR of the horn antenna with EM obstacle                                                                                 | .35 |

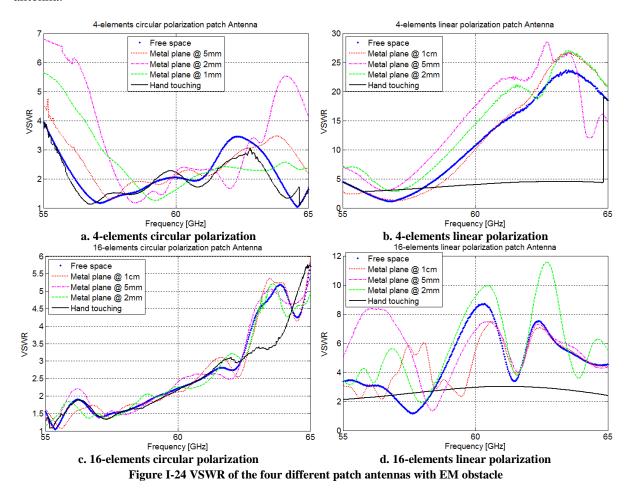

| Figure I-24 VSWR of the four different patch antennas with EM obstacle                                                                |     |

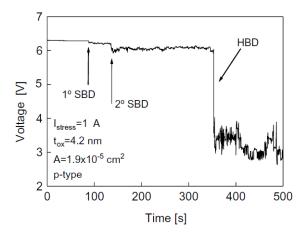

| Figure I-25 Evolution of the gate voltage during a constant current stress test during which several breakdown events                 |     |

| are detected as abrupt voltage drops                                                                                                  |     |

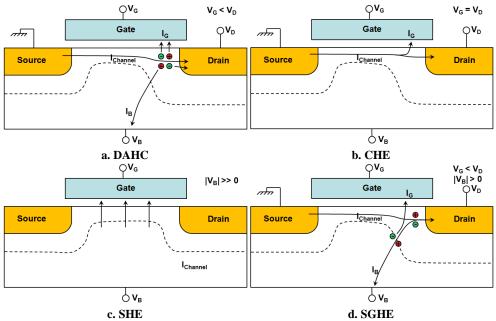

| Figure I-26 Hot-carrier injection mechanisms                                                                                          | .39 |

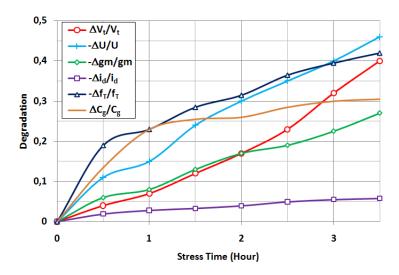

| Figure I-27 nMOSFET characteristics degradation under HCI stress                                                                      |     |

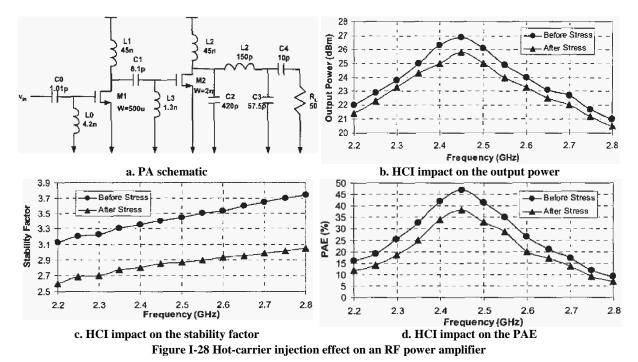

| Figure I-28 Hot-carrier injection effect on an RF power amplifier                                                                     |     |

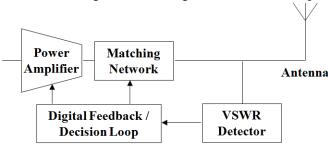

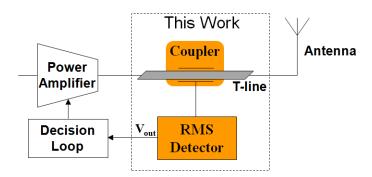

| Figure I-29 General architecture of the Antenna VSWR regulated Power Amplifier                                                        |     |

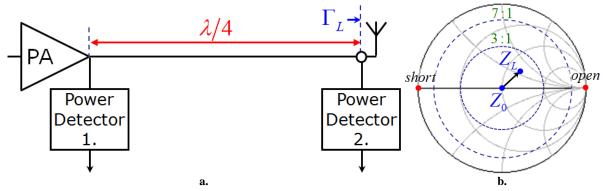

| Figure I-30 Location of the two power detectors (a.); Smith chart described by the antenna impedance (b.)                             |     |

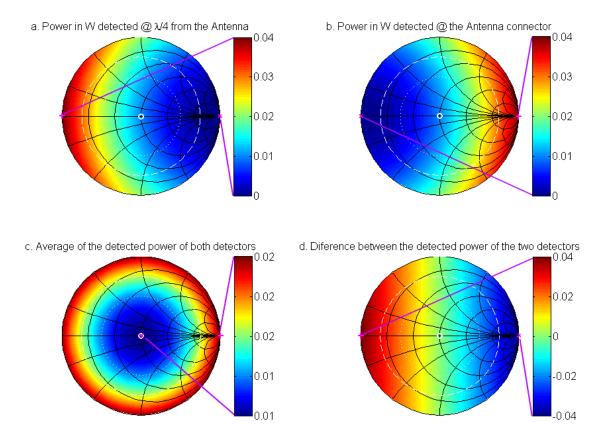

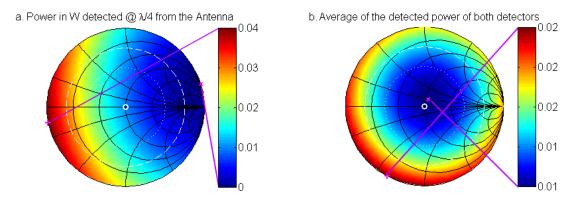

| Figure I-32 Power in the T-line for the first detector (a.) and average of both power (b.) considering a 55GHz signal                 |     |

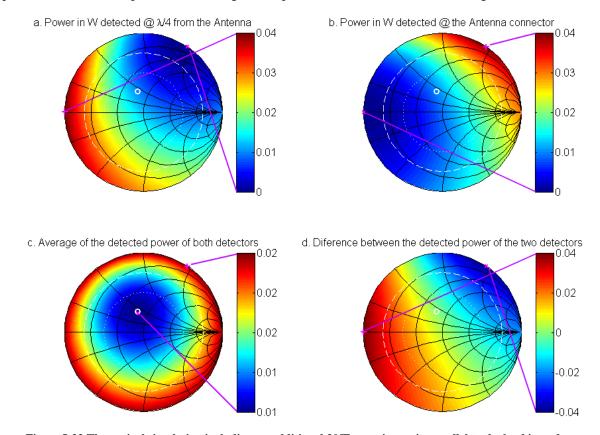

| Figure I-32 Theoretical simulation including an additional 30fF capacitance in parallel to the load impedance                         |     |

|                                                                                                                                       |     |

| Figure II-1 Integration of a coupler and a RMS detector                                                                               |     |

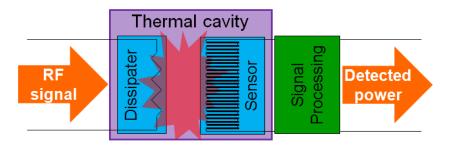

| Figure II-2 Principle of a thermal power detector                                                                                     |     |

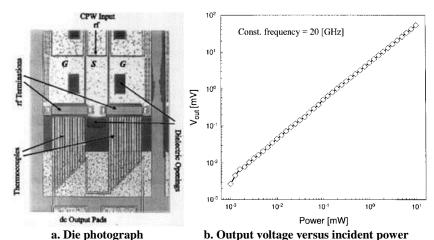

| Figure II-3 Thermal detector in commercial CMOS process using micromachining techniques                                               |     |

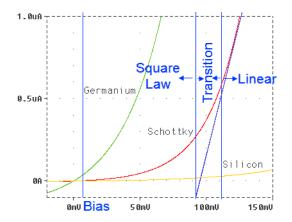

| Figure II-4 Silicon (yellow), Schottky (red) and Germanium (green) diodes characteristics                                             | .56 |

| Figure II-5 Diode detector Side implementation                                                                                        |     |

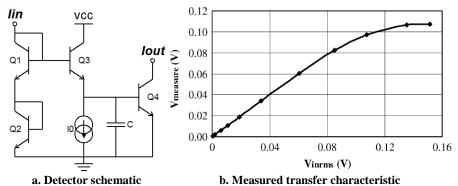

| Figure II-0 Meyer's detector.                                                                                                         |     |

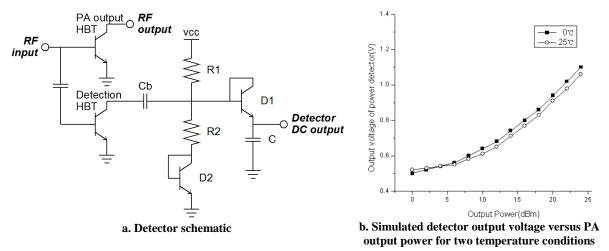

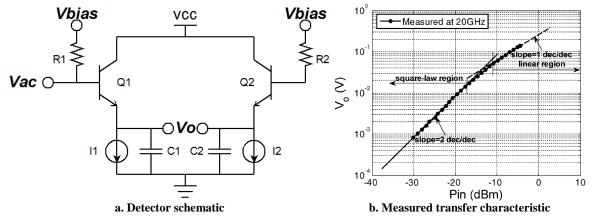

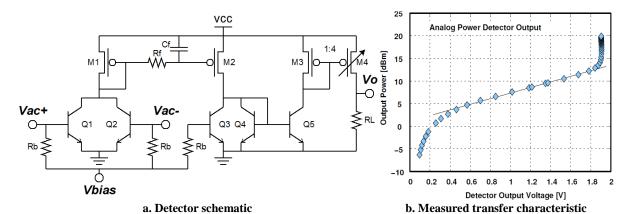

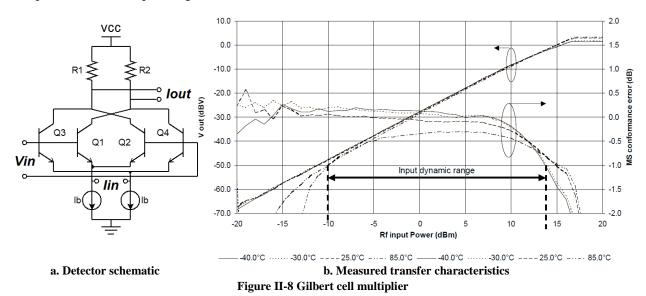

| Figure II-8 Gilbert cell multiplier                                                                                                   |     |

| Figure II-9 Translinear Detector                                                                                                      |     |

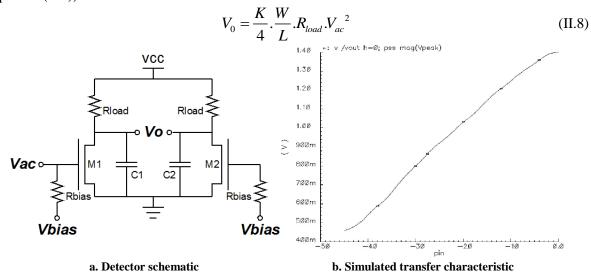

| Figure II-10 MOS Meyer detector                                                                                                       |     |

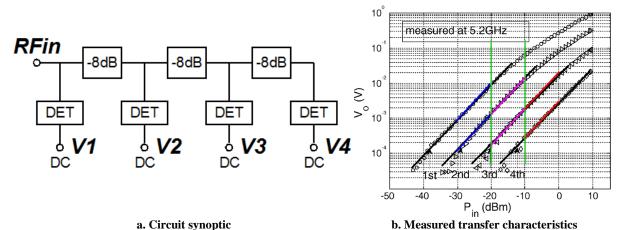

| Figure II-11 Dynamic range increasing technique                                                                                       |     |

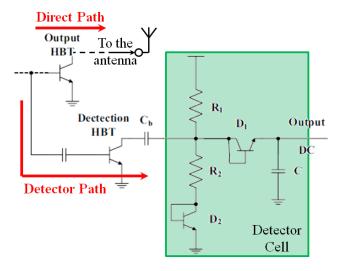

| Figure II-12 Direct connection of the power detector to the direct path                                                               | .62 |

| Figure II-13 R-C passive network connection between the envelope detector and the direct path                                         |     |

| Figure II-14 Parallelization of the power transistor                                                                                  |     |

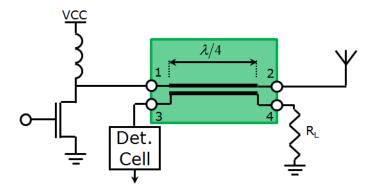

| Figure II-15 Directional coupler connection                                                                                           |     |

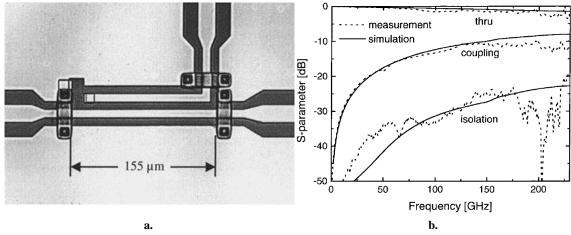

| Figure II-16 Integrated directional coupler on a GaAs substrate running at 180GHz                                                     |     |

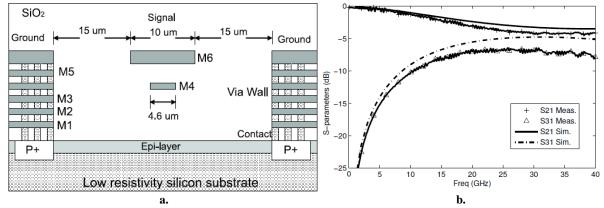

| Figure II-17 Integrated 10-40GHz directional coupler on a 0.18µm CMOS process                                                         |     |

| Figure II-18 Capacitive coupler using silicon backend process                                                                         |     |

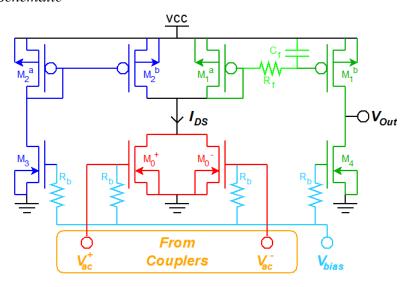

| Figure II-19 Designed detector schematic                                                                                              | .00 |

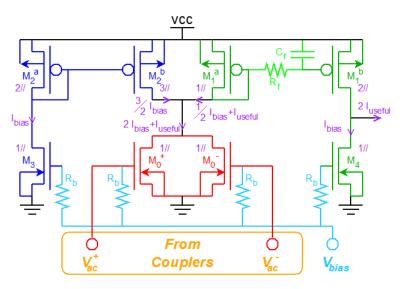

| Figure II-20 Designed detector schematic with current repartition $\frac{1}{2}$ For several biasing voltages $\frac{1}{2}$            |     |

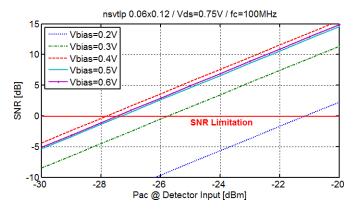

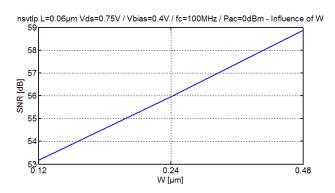

| Figure II-22 Noise simulation: SNR versus detection transistor width                                                                  | .69 |

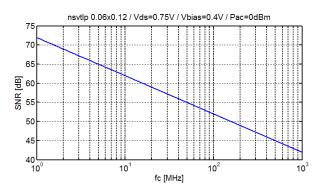

| Figure II-23 Noise simulation: SNR versus $1^{st}$ order low-pass filter cutoff frequency $f_c$                                       |     |

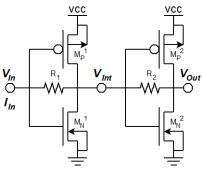

| Figure II-24 Current-to-Voltage Converter schematic                                                                                   | .70 |

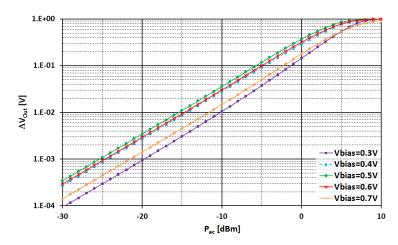

| Figure II-25 Detector and buffer characteristic for various biasing voltages with svtlp transistors (1st circuit)                     | .70 |

| Figure II-26 Detector and buffer characteristic for various biasing voltages with lvtlp transistors (2 <sup>nd</sup> circuit)         | .71 |

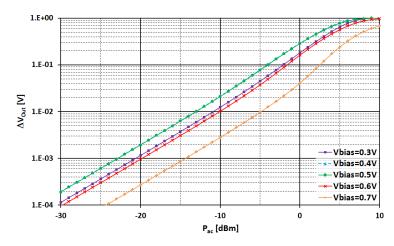

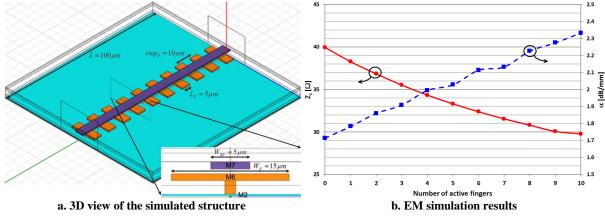

| Figure II-27 Simplification of the 65nm CMOS process from STMicroelectronics for EM simulation                                        |     |

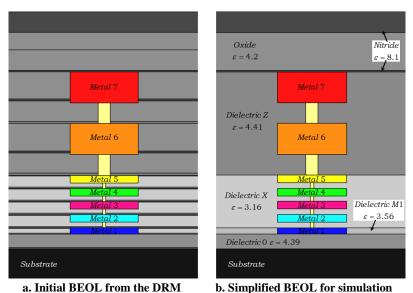

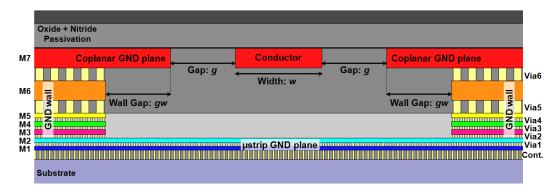

| Figure II-28 Cross section of the designed G-CPW                                                                                      | .72 |

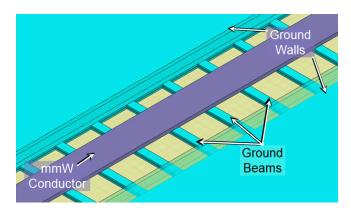

| Figure II-29 Designed G-CPW (3D view from Ansoft HFSS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

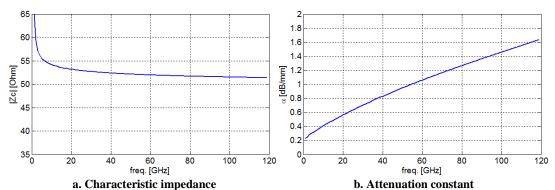

| Figure II-30 Main characteristics of the designed G-CPW (Ansoft HFSS simulation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73                                                              |

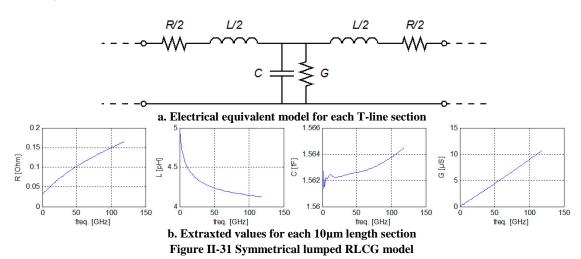

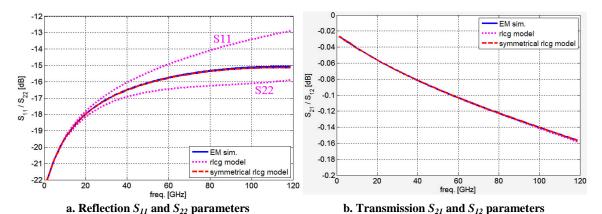

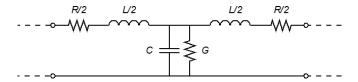

| Figure II-31 Symmetrical lumped RLCG model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74                                                              |

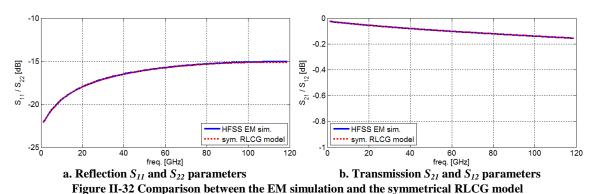

| Figure II-32 Comparison between the EM simulation and the symmetrical RLCG model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74                                                              |

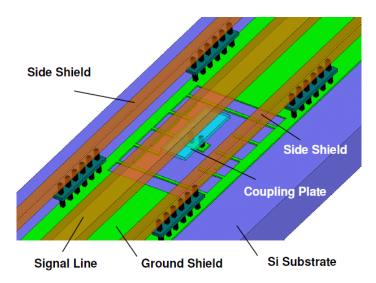

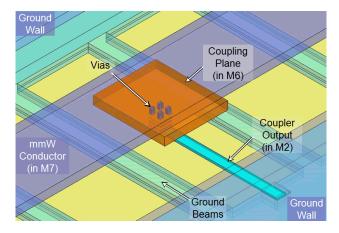

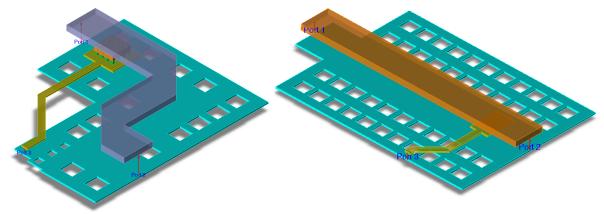

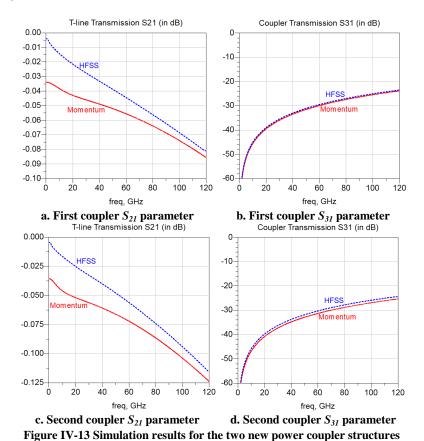

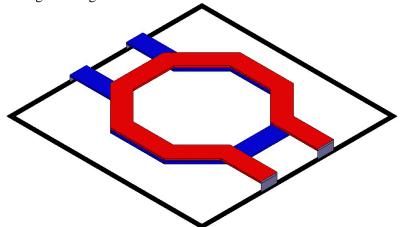

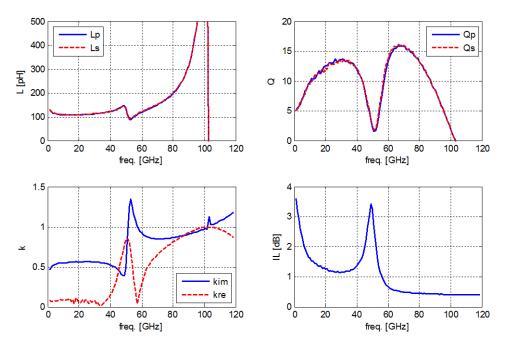

| Figure II-33 Designed capacitive coupler (3D view from Ansoft HFSS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75                                                              |

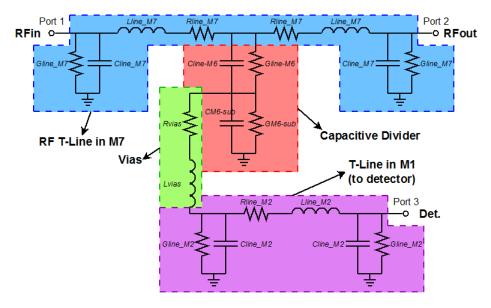

| Figure II-34 Equivalent circuit of the capacitive coupler region which was used in the time domain simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76                                                              |

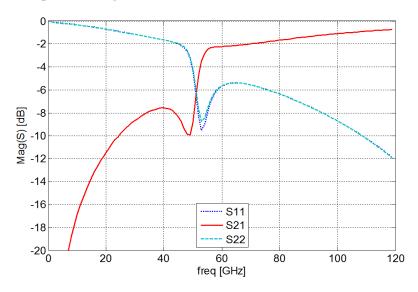

| Figure II-35 Comparison between the EM simulation (HFSS) and the RLCG model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                 |

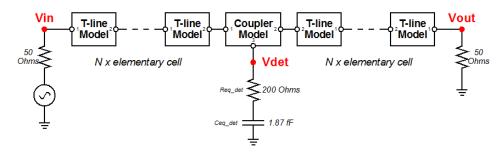

| Figure II-36 Schematic of the transient analysis of the coupler model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                 |

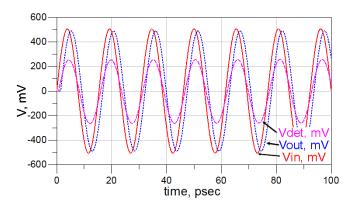

| Figure II-37 Input, output and detector voltages resulting from the transient analysis of the Figure II-36's schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 77                                                              |

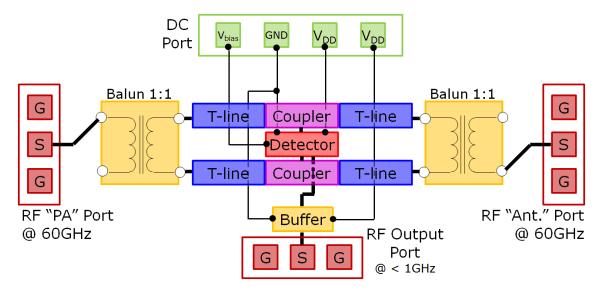

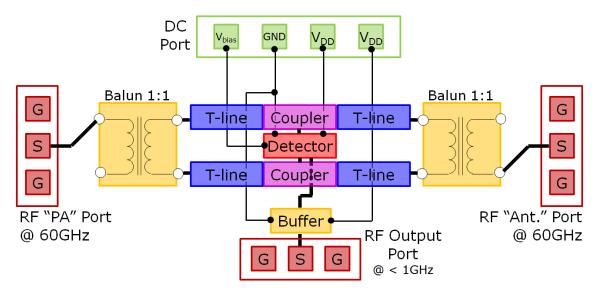

| Figure II-38 Power detection circuit synoptic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 78                                                              |

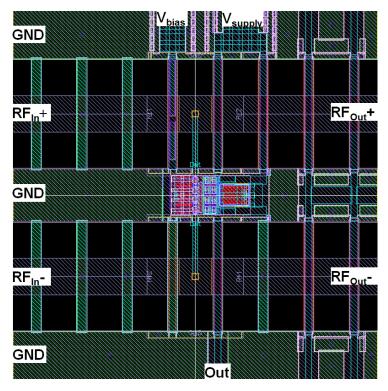

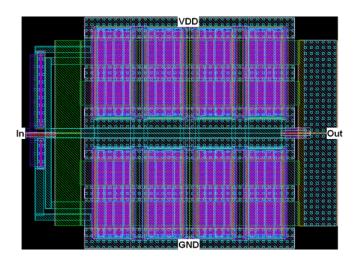

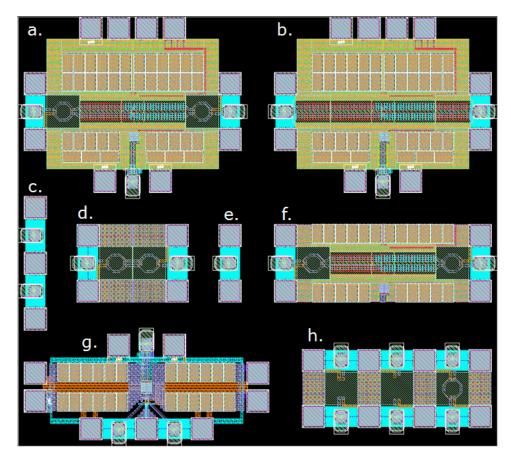

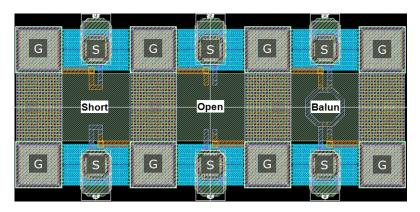

| Figure II-39 Power couplers and detector layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                 |

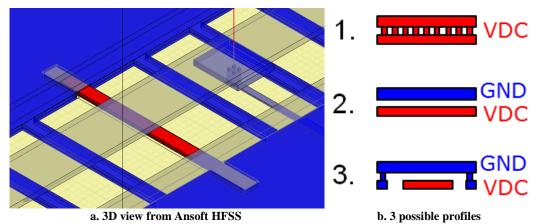

| Figure II-40 DC connection under the T-line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                 |

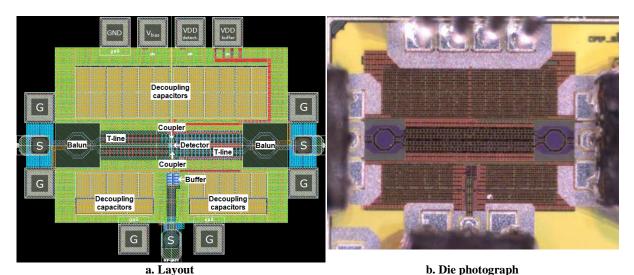

| Figure II-41 Implemented power detection circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |

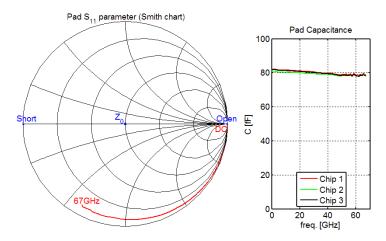

| Figure II-42 Pad capacitance effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                 |

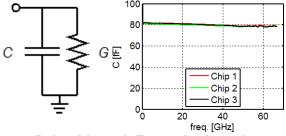

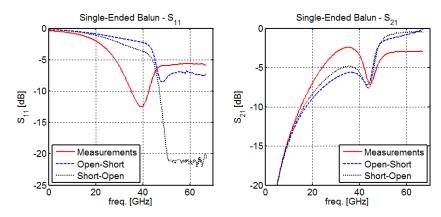

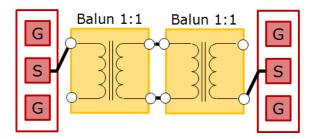

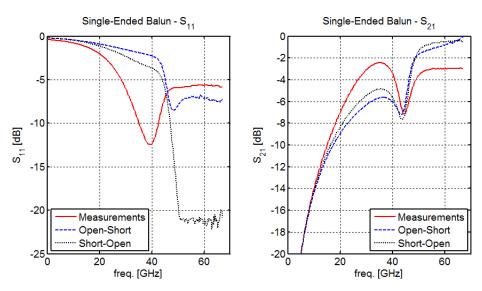

| Figure II-43 Single-Ended Balun $S_{II}$ and $S_{2I}$ parameters; measured and de-embedded results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 83                                                              |

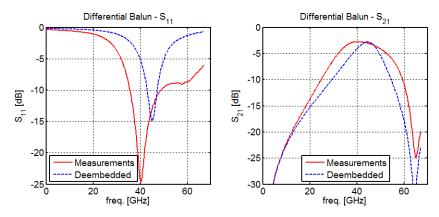

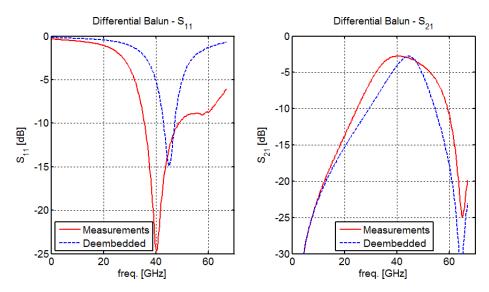

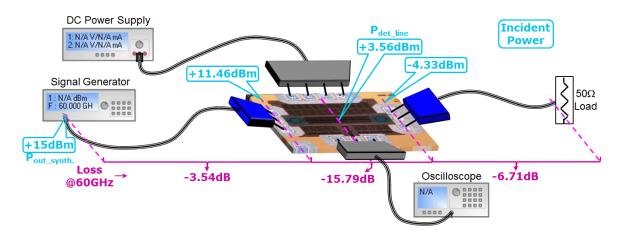

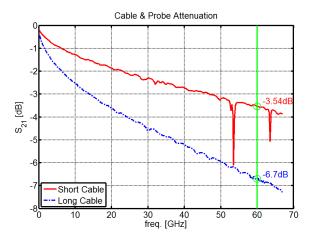

| Figure II-44 Differential Balun $S_{11}$ and $S_{21}$ parameters; measurements and open-short de-embedded results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                 |

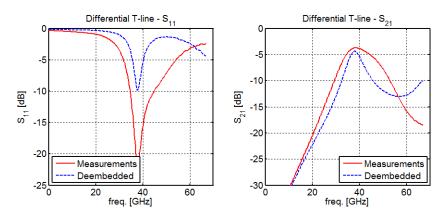

| Figure II-45 Differential T-line $S_{11}$ and $S_{21}$ parameters; measurements and open-short de-embedded results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                 |

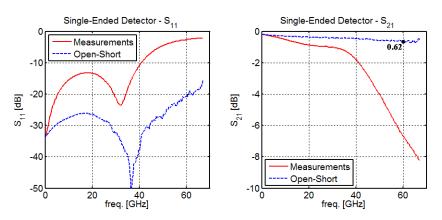

| Figure II-46 Single-ended Detector $S_{11}$ and $S_{21}$ parameters; measurements and open-short de-embedded results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                 |

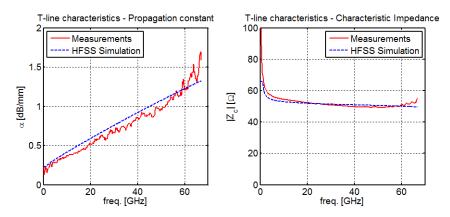

| Figure II-47 Single-ended T-line: extracted T-line characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                 |

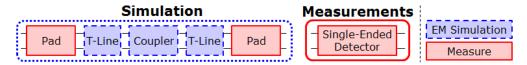

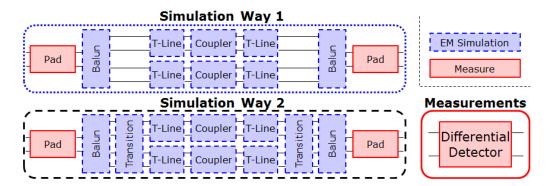

| Figure II-48 Retro-simulation configuration for the single-ended T-line circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 85                                                              |

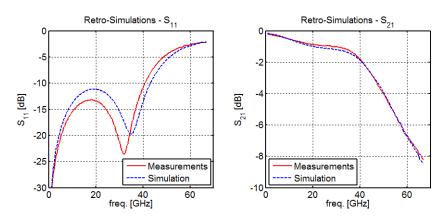

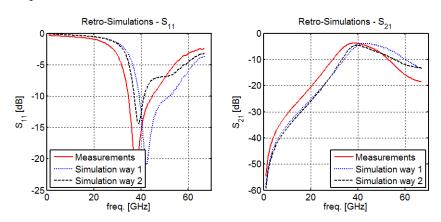

| Figure II-49 Comparison between the measurements and the retro-simulation for the single-ended T-line circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                 |