# THESE

Présentée à l'Université de Lille

Ecole Doctorale ENGSYS

Pour obtenir le grade de :

## DOCTEUR DE L'UNIVERSITE

Spécialité : Electronique, Microélectronique, Nanoélectronique

et Micro-Ondes

Par

## Kathia HARROUCHE

## Conception et réalisation de transistors de puissance à

## base du GaN jusqu'en bande W

## Design and fabrication of GaN-based field effect power

## transistors up to W-band

Soutenance le 16 décembre 2021 devant la Commission d'examen :

| Rapporteurs :        | Mme. Nathalie MALBERT | Professeur (IMS Bordeaux)        |

|----------------------|-----------------------|----------------------------------|

|                      | M. Olivier LATRY      | Professeur (GPM Rouen)           |

| Directeur de thèse : | M. Farid MEDJDOUB     | Chargé de recherche CNRS (IEMN)  |

| Examinateurs :       | Mme. Chloé BOUEXIERE  | Ingénieure (DGA)                 |

|                      | M. Didier FLORIOT     | Deputy CTO (UMS)                 |

|                      | M. Katir ZIOUCHE      | Professeur (Université de Lille) |

## Remerciements

Ce travail a été effectué au sein du groupe WIND à l'institut d'Electronique, Microélectronique et de Nanotechnologie de l'Université des Sciences et Technologies de Lille.

Je souhaite tout d'abord remercier et exprimer ma profonde reconnaissance à mon directeur de thèse **Dr. Farid MEDJDOUB**, chargé de recherche à l'IEMN pour m'avoir donné l'opportunité de réaliser cette thèse avec succès. Ces trois années de thèse effectuées sous sa direction sont marquées par une qualité d'encadrement exceptionnelle. Je le remercie profondément pour sa disponibilité sans limite, ses conseils avisés, son enthousiasme, ainsi que son expertise et sa passion communicative pour le GaN qui m'ont permis d'évoluer.

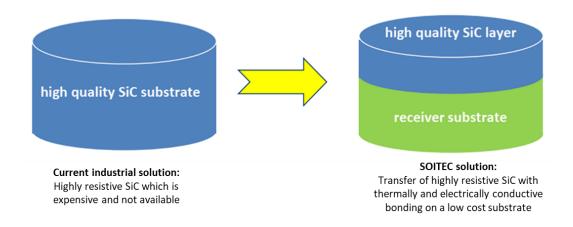

Je souhaite également remercier les membres du jury ayant apporté et examiné ces travaux de thèse. Merci au **Pr. Nathalie MALBERT**, professeure au laboratoire IMS, et au **Pr. Olivier LATRY**, professeur au laboratoire LAAS, qui m'ont fait l'honneur de rapporter ce travail. Je remercie également **Mme. Chloé BOUEXIERE**, ingénieure (DGA), **M. Didier FLORIOT**, deputy CTO (UMS) et **Pr. Katir ZIOUCHE**, professeur de l'université de Lille d'avoir examiné ce travail. Je souhaite également remercier l'ensemble des partenaire et financeurs, SOITEC, UMS, DGA, l'université de PADOVA, C2N et ILV avec qui j'ai eu l'honneur de travailler dans le cadre de plusieurs projets.

Je tiens à remercier tous le personnel de l'administration de l'IEMN notamment Nora, Andy et Laetitia pour leur efficacité. Le STAFF de la plateforme CMNF de l'IEMN, ou j'ai passé beaucoup de temps pour la fabrication des composants. Je remercie les responsables du pôle lithographie : **Christophe Boyaval** qui m'a aidé à prendre de belles photos sur le MEB. **Saliha Ouendi**, **François Vaurette**, **Pascal Tilmant** et **Yves Deblock** de m'avoir aidé à trouver des solutions quand le développement des résines se passe mal. Je remercie également les responsables du pôle gravure et implantation : **Timothey Bertrand** pour son intervention sur les bâtis RIE et ICP quand ils ne fonctionnent pas. **Dmitri Yarekha** pour ses conseils afin de pouvoir graver des grilles < 100 nm sur la CH1. **Laurent Fugere** pour tous les recuits et implants et sans oublier **David Troadec** pour les belles images FIB et les lames TEM. Je remercie aussi les responsables du pôle dépôt : **Isabelle Roche Jeune**, **Marc Dewitte** et **Annie Fattorini** pour leurs aides et conseils.

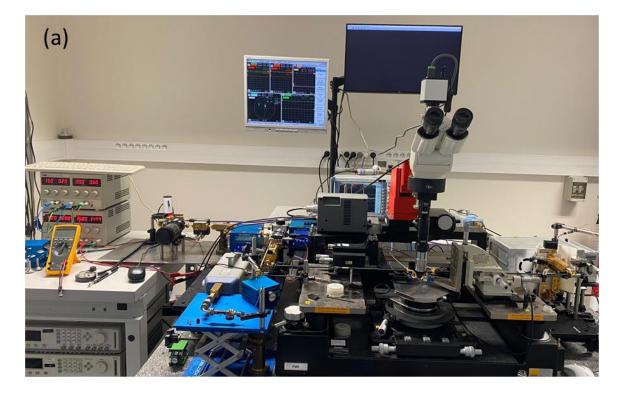

Je tiens à remercier le STAFF de la centrale de caractérisation avec qui j'ai eu le plaisir de travailler : **Sophie Barrois, Vanessa Avramovic, Sylvie Lepilliet** et surtout **Etienne Okada** pour sa patience et rigueur lors de son implication majeure à la caractérisation des composants et au développement du banc LP 94 GHz. Je souhaite remercier les membres de mon groupe WIND : **Idriss** (DUMMY) pour son aide et ses encouragements jusqu'au jour de ma soutenance, pour m'avoir accompagné en salle blanche et au bureau jusqu'à 22h30, et pour les tiroirs toujours remplis de sucre. **Tommy** et **Léna** pour leur sympathie et leur aide en salle blanche. Je souhaite aussi un bon courage et beaucoup de succès à l'ensemble des nouveaux arrivants dans le groupe WIND : la gentille **Elodie**, **Jash**, **Sri**, **François** AZIZ, et **Youcef**.

Une forte pensée pour **Riad** qui m'a beaucoup aidé et soutenu pendant les deux premières années de ma thèse, aujourd'hui il n'est plus parmi nous mais je pense toujours à lui et aux bons moments qu'on a partagés ensemble au labo.

Je remercie aussi l'ensemble de mes collègues et amis que j'ai eu la chance de côtoyer : mon tuteur de stage de master Jean-Marc qui m'a appris la structuration au laser femtoseconde. Cybelle ma confidente qui m'a soutenue dans les meilleurs et pires moments. Théo mon camarade de bureau des stagiaires qui m'a toujours impressionné avec ses expériences dangereuses. Mélanie qui m'a transmis sa passion pour l'escalade. Thierno qui me fait croire qu'il n'a pas froid tandis qu'il claque les dents discrètement. Fuanki et Kévin.R qui sont toujours à la hauteur des FDM.... Saliha pour les pauses café et les discussions interminables même pendant les écritures E-beam. Sylvie pour ses qualités humaines hors du commun et son support psychologique. Arthur, Joao, Simon, Vincent, Kévin. F, Arun, Vinnay, Pietr, Elias, Charbel, Hugo, Giuseppe, Ibrahim, Akkach (my freind). Tous les moments passés avec vous au labo ou à l'extérieur resteront gravés.

Je tiens à remercier ma cousine **Salma** pour m'avoir soutenue tout au long de ma thèse, je n'oublierai pas tous les moments passés avec elle : shopping à padouk, vacances à Majorque ou alors quand on a failli incendier sa maison avec une bougie ! Je remercie aussi mon cousin **Yazid** qui a su me remonter le moral même avec ses blagues pourries.... Mes copines de cœur **Nadjet** (Zine), **Massil** (mami) et **Dina** d'être présentes.

Je n'oublie pas ma famille qui m'a soutenu malgré la distance. Je tiens à témoigner toute ma reconnaissance à mes parents qui m'ont fait confiance et surtout cru en moi. Je remercie ma sœur **Lamia** et mon frère **Rachid** d'être toujours là pour moi. Toutes mes tantes et oncles mais surtout **Saliha** qui a été ma confidente et mon soutien émotionnel. Mon **grand-père** qui m'a toujours encouragé. Mes cousines et cousins : les adorales **Mélissa** (bilili) et **Miassa** (b..rou..rou), **Djamila**, **Nacira**, **Ania**, mon petit **Wassim**, **Kenzi**, **Mahdi**, **Amélia**, **walid**, **Ilyes**, **Sonia**.... Je n'oublie pas **Mohamed** pour son soutien de près.

## Abstract

In the last decades, remarkable progresses have been achieved with GaN high electron mobility transistors (HEMTs) for use in high-frequency power amplification and switching applications. Currently, the most matured GaN HEMTs are based on AlGaN/GaN heterostructures. More recently, Al-rich ultrathin sub-10 nm (In)(Ga)AIN/GaN heterostructures have also received much attention for millimeter-wave applications. This is because in contrast to AlGaN/GaN, they can provide more than two times higher 2 Dimensional-Electron-Gas (2DEG) sheet carrier density while offering a high aspect ratio (gate length / gate to channel distance) down to sub-100 nm gate lengths. As a result, Al-rich ultrathin barrier GaN HEMTs are able to operate at much higher speed without the use of gate recess, thus potentially enabling high device reliability. In this frame, a number of research groups have demonstrated a unique combination of higher power and wider bandwidth using advanced GaN transistors all the way to 100 GHz as compared to other technologies (GaAs or Silicon). However, most of the applications require very high efficiency power amplifiers with high linearity and proven reliability under harsh conditions. Current stateof-the-art GaN HEMTs are limited to about 50% power-added-efficiency (PAE) in the Ka band and much lower at higher frequency. Moreover, very few reports are available on the device reliability for sub-150 nm gate lengths. On the other hand, one of the major limitations of modern RF devices is the thermal dissipation. The dissipated power improves by 80% when the PAE increases from 50% to 80%.

The aim of this work is to provide leading edge technologies in this field through the development and the improvement of sub-150 nm GaN transistors for high frequency applications. In particular, we have performed an extensive buffer engineering while carefully optimizing an ultrathin sub-5nm AlN barrier layer in order to maximize the power gain, improve the electron confinement under high electric and simultaneously reduce the trapping effects. Furthermore, the development of a power bench at 94 GHz enabled the demonstration of a record W-band output power density with the fabricated devices. This is believed to constitute a decisive asset in securing high performances and reliable GaN devices for next-generation millimeter-wave amplifiers related to future 5G telecommunications, space or military applications.

**Key words**: GaN, Heterostructure, Ultra-thin barrier layers, HEMT, Q-band, W-band, Millimeter-wave, High frequency, Load-pull

## Résumé

Au cours des dernières décennies, des progrès remarquables ont été réalisés sur les transistors à haute mobilité électronique à base de GaN (HEMTs GaN) destinés aux applications d'amplification et de commutation de puissance à haute fréquence. Actuellement, les HEMTs GaN les plus matures sont basés sur des hétérostructures AlGaN/GaN. Plus récemment, les hétérostructures à barrières ultrafines (<10 nm) (In)(Ga)AIN/GaN riches en Al ont également présentées beaucoup d'intérêt pour les applications en gamme d'ondes millimétriques. En effet, contrairement aux structures AlGaN/GaN, les barrières ultrafines riches en Al peuvent fournir une densité d'électrons (2DEG) deux fois plus élevée tout en offrant un rapport d'aspect important (longueur de grille / distance grille-canal) y compris avec des grilles très courtes inferieures à 100 nm. Par conséquent, les HEMTs GaN à barrière ultrafine riche en Al permettent de fonctionner à une fréquence plus élevée de manière robuste. Dans ce contexte, plusieurs groupes de recherche ont démontré une combinaison unique de puissance plus élevée et une bande passante plus large jusqu'à 100 GHz par l'utilisation de transistors GaN par rapport aux autres technologies (GaAs ou silicium). Cependant, la plupart des applications nécessitent des amplificateurs de puissance à très haut rendement associé à une fiabilité éprouvée et une linéarité accrue. L'état de l'art des HEMTs GaN est limité aujourd'hui à environ 50% de rendement PAE (Power Added Efficiency) et peu de travaux reportés sur la fiabilité des composants GaN utilisant des grilles courtes inferieures à 150 nm. Néanmoins, l'une des limitations majeures des composants RF modernes est la dissipation thermique. En effet, la puissance dissipée s'améliore de 80% lorsque le rendement PAE passe de 50% à 80%.

L'objectif de ce travail est de fournir une technologie de pointe dans ce domaine avec le développement et l'optimisation de transistors GaN à grille sub-150 nm pour les applications en gamme d'ondes millimétriques. En particulier, nous avons effectué une optimisation des couches tampons (buffer) tout en optimisant une barrière AlN ultrafine inférieure à 5 nm afin d'augmenter le gain de puissance, d'améliorer le confinement des électrons sous fort champ électrique et de simultanément réduire les effets de pièges. De plus, le développement d'un banc de mesures de puissance à 94 GHz a permis de démontrer une densité de puissance à l'état de l'art en bande W avec les composants fabriqués. Ces travaux constituent une base de travail prometteuse pour garantir des performances élevées (notamment le rendement PAE) et fiables des HEMTs GaN pour l'amplification de puissance en gamme d'ondes millimétriques liée aux futures applications de télécommunication 5G, spatiales ou militaires. **Mots clé** : GaN, Hétérostructure, Barrières ultrafines, HEMT, bande Q, bande W, ondes millimétriques, Haute fréquence, Load-pull

# Summary

| Remer   | ciemer   | nts                                                               | 3  |

|---------|----------|-------------------------------------------------------------------|----|

| Introdu | uction . |                                                                   | 10 |

| 1)      | Conte    | xt of study                                                       | 10 |

| 2)      | Intere   | st of millimeter-wave band                                        | 11 |

| 3)      | Thesis   | organization                                                      | 13 |

| Chapte  | er 1: Ga | N HEMTs – Technology and Overview                                 | 16 |

| I. In   | troduc   | tion to GaN Technology                                            | 17 |

| I.1     | Tar      | geted applications for GaN millimeter-wave                        | 17 |

| I.1     | 1.1.     | High power amplification                                          | 18 |

| 1.1     | 1.2.     | Broadband amplifiers                                              | 20 |

| I.1     | 1.3.     | Fifth generation wireless communication                           | 22 |

| II. Ga  | aN mat   | erial system and properties                                       | 24 |

| II.1.   | Cry      | stal structure                                                    | 24 |

| II.2.   | Pola     | arization effect                                                  | 26 |

| II.3.   | Ma       | terial properties and comparison with other materials             |    |

| III.    | GaN-b    | ased device limitations                                           | 33 |

| IV.     | GaN h    | igh electron mobility transistors                                 |    |

| IV.1.   | . Hist   | orical development and incremental improvements                   |    |

| IV.2.   | . Figu   | re of merits of GaN-based HEMTs                                   | 37 |

| IV      | .2.1.    | High performances: PAE/output power density                       | 37 |

| IV      | .2.2.    | GaN HEMTs Reliability                                             |    |

| IV.3.   | Gal      | I HEMT epitaxial structures                                       | 41 |

| IV      | .3.1.    | Epitaxial structure and growth techniques                         | 41 |

| IV      | .3.2.    | Configuration and specific material systems of RF HEMT structures | 42 |

| V. Ga   | aN dev   | ice scaling technologies                                          | 52 |

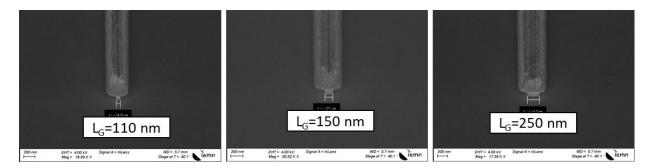

| V.1.    | T-sł     | naped gate and lateral scaling                                    | 54 |

| V.2.    | Adv      | anced ohmic contacts                                              | 55 |

| VI.     | GaN-F    | IEMTs: existing technologies in millimeter-wave range             | 56 |

| VI.1.   | Ga-      | polar technology                                                  | 57 |

| VI.2.   | . N-p    | olar technology                                                   | 59 |

| VII.  | Re      | view       | of state-of-the art GaN transistors                                                          | .61  |  |  |  |

|-------|---------|------------|----------------------------------------------------------------------------------------------|------|--|--|--|

| VIII. | Со      | Conclusion |                                                                                              |      |  |  |  |

| Chap  | ter 2   | : Dev      | vice fabrication and characterization methods for GaN HEMTs                                  | . 63 |  |  |  |

| I.    | Intro   | duct       | ion:                                                                                         | . 64 |  |  |  |

| II.   | Fabri   | catio      | on techniques                                                                                | . 65 |  |  |  |

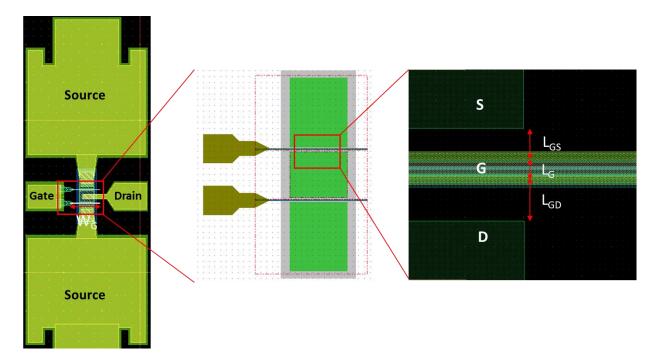

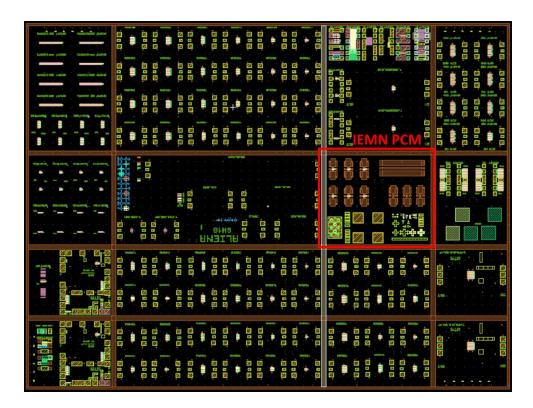

| 11.1  | 1.      | Desc       | ription of the mask layouts used                                                             | .67  |  |  |  |

| 11.2  | 2.      | Opti       | mization of device processing technology                                                     | .70  |  |  |  |

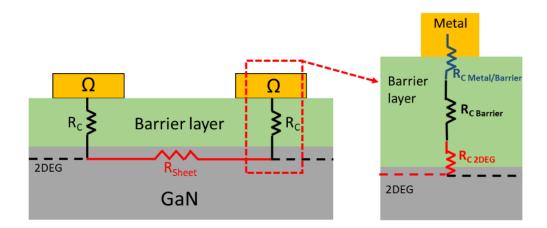

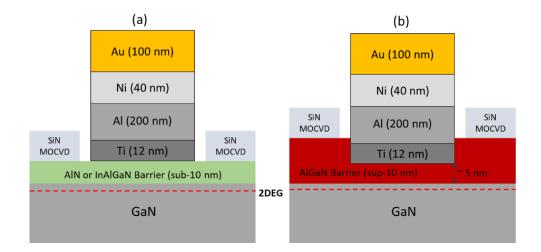

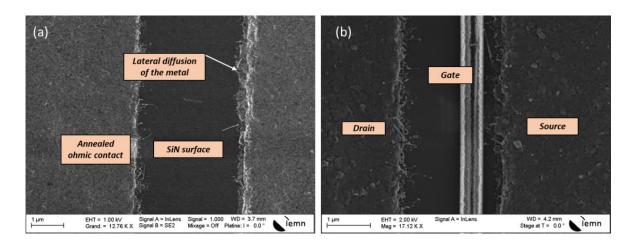

|       | II.2.1  | •          | Ohmic contacts realization                                                                   | .70  |  |  |  |

|       | 11.2.2  | •          | Gate Schottky optimization                                                                   | .76  |  |  |  |

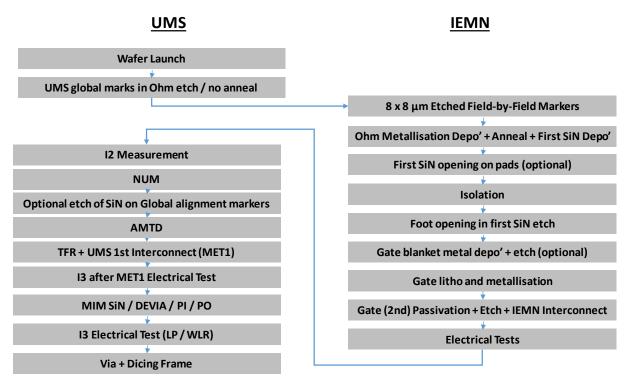

| 11.3  | 3.      | Preir      | ndustrial device fabrication with UMS foundry within the frame of a shared process           | . 80 |  |  |  |

| III.  | De      | vice       | characterization methods                                                                     | .82  |  |  |  |

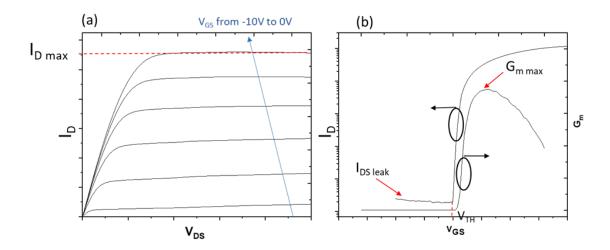

| 111.  | 1.      | DC c       | haracteristics                                                                               | . 82 |  |  |  |

|       | 111.1.1 | 1.         | Static I-V characteristics                                                                   | . 83 |  |  |  |

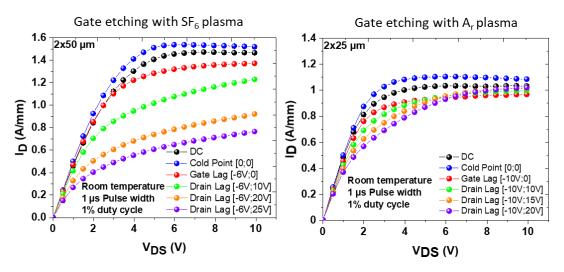

|       | 111.1.2 | 2.         | Pulsed I-V characteristics                                                                   | .85  |  |  |  |

| 111.  | 2.      | Smal       | II signal characteristics                                                                    | .86  |  |  |  |

| 111.  | 3.      | Large      | e signal characteristics                                                                     | . 88 |  |  |  |

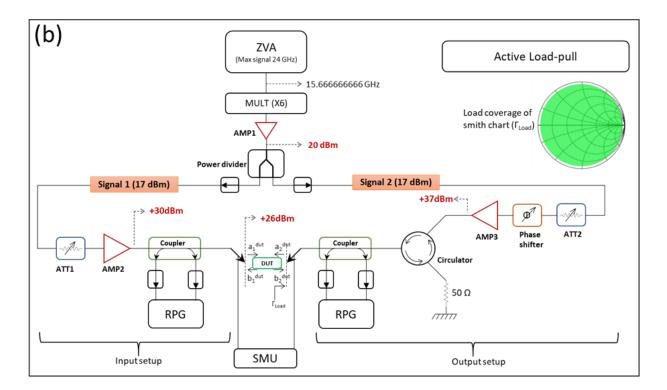

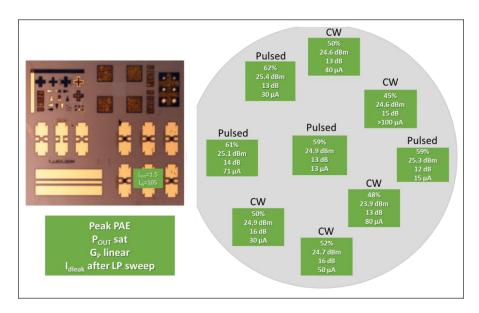

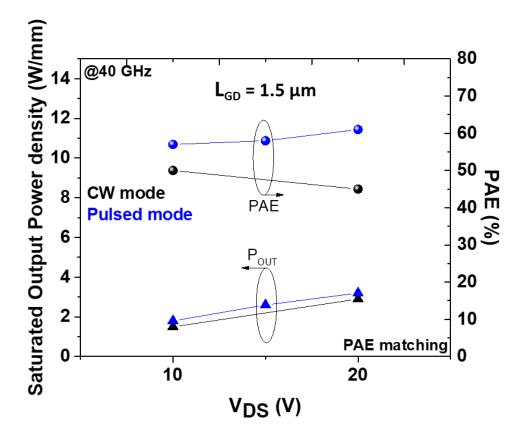

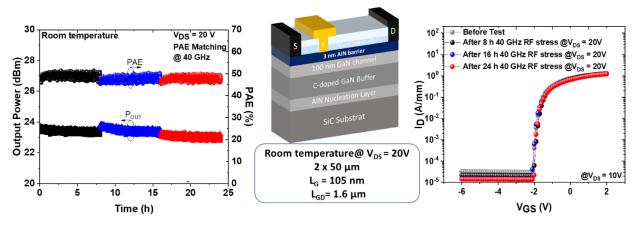

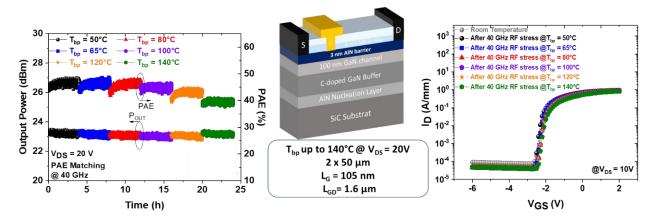

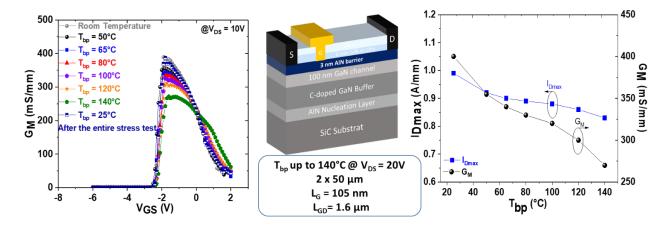

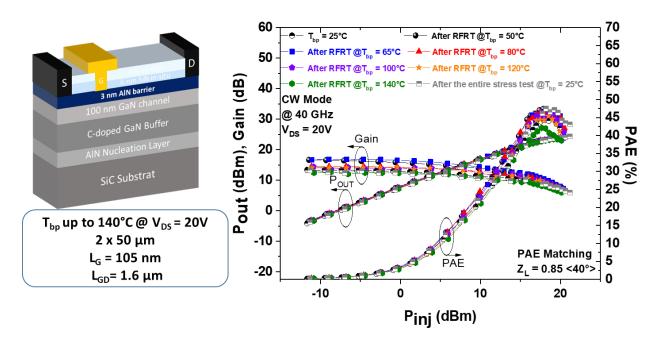

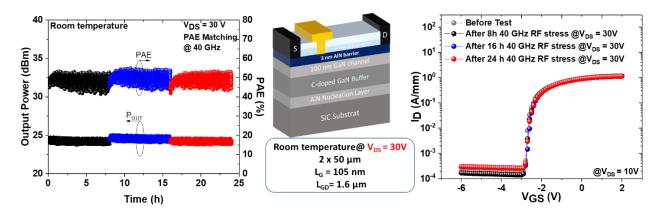

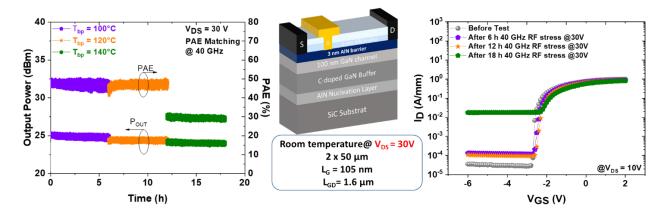

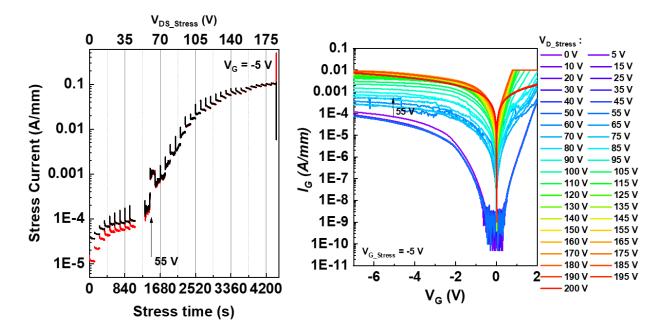

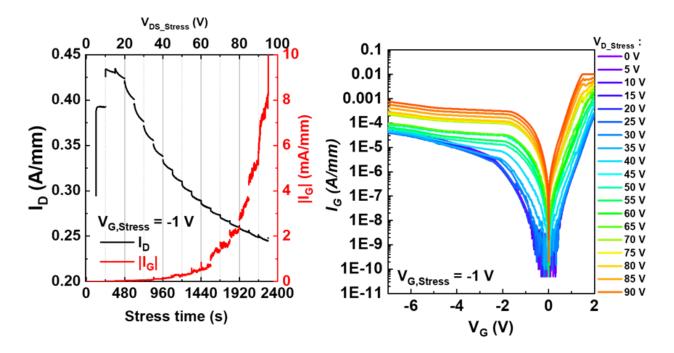

|       | III.3.1 | 1.         | Large signal characterization at 40 GHz                                                      | .90  |  |  |  |

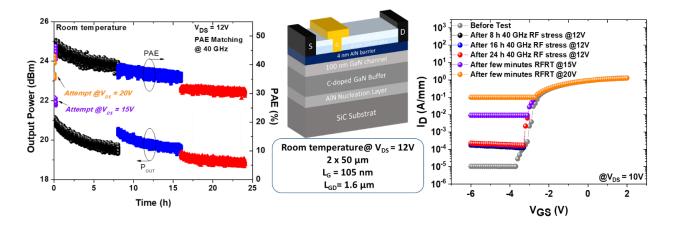

|       | 111.3.2 | 2.         | Short term reliability at 40 GHz                                                             | .92  |  |  |  |

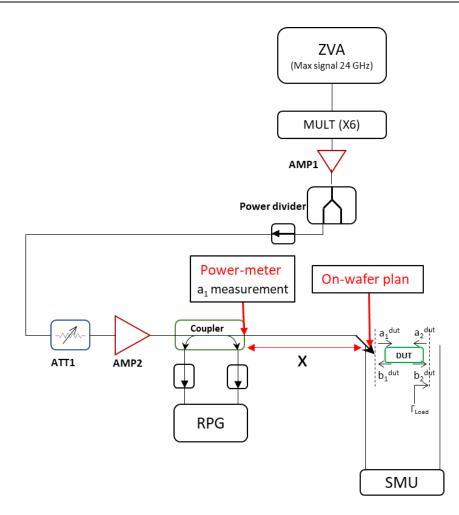

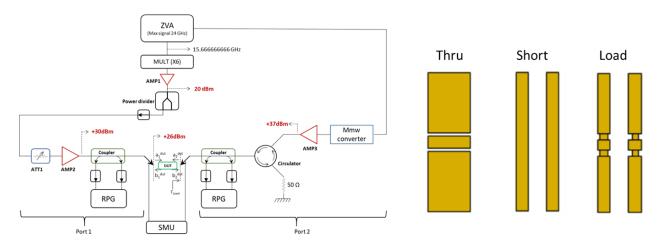

|       | 111.3.3 | 3          | Test bench development for large signal characterization at 94 GHz                           | .92  |  |  |  |

| IV.   | Со      | nclu       | sion                                                                                         | 100  |  |  |  |

|       |         |            | wards ultrathin Al-rich barrier layers for millimeter-wave devices: Electrical and structure |      |  |  |  |

|       |         |            | on of AIN/GaN HEMTs                                                                          |      |  |  |  |

|       |         |            | ion                                                                                          |      |  |  |  |

|       |         |            | aN HEMTs limits in the millimeter-wave range                                                 |      |  |  |  |

| 11.1  |         |            | ce fabrication                                                                               |      |  |  |  |

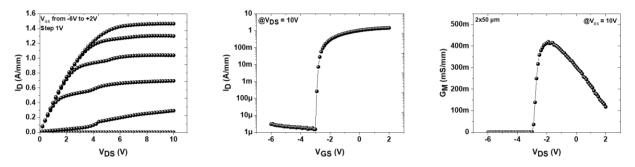

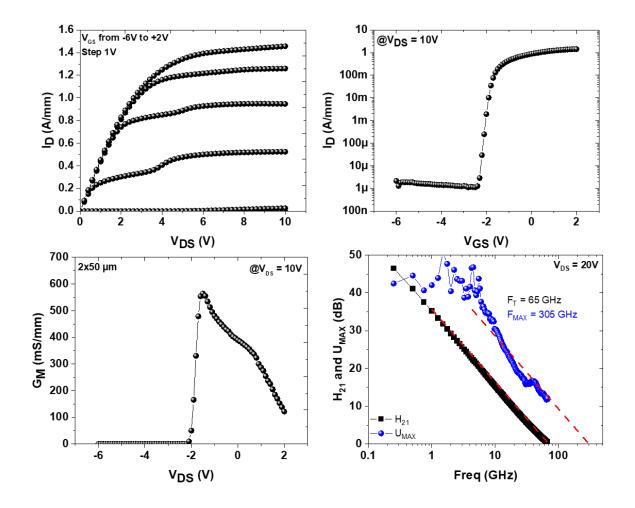

| 11.2  | 2.      | DC a       | nd small signal characterization                                                             | 104  |  |  |  |

| III.  | Ult     | trath      | in AIN/GaN technology                                                                        | 106  |  |  |  |

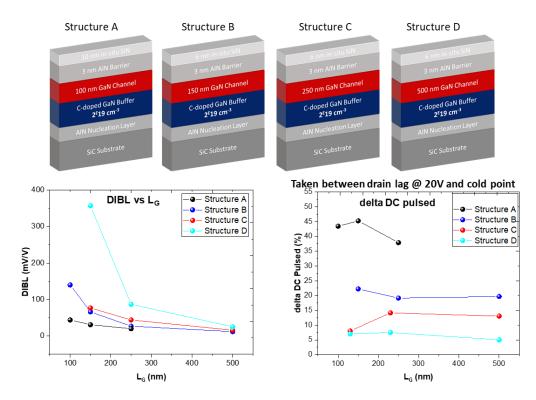

| 111.  | 1.      | Impa       | act of the channel thickness and C-doping concentration in the buffer                        | 106  |  |  |  |

|       | 111.1.1 | 1.         | Device fabrication                                                                           | 107  |  |  |  |

|       | 111.1.2 | 2.         | Impact of the undoped channel thickness variation                                            | 107  |  |  |  |

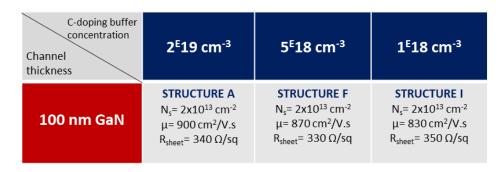

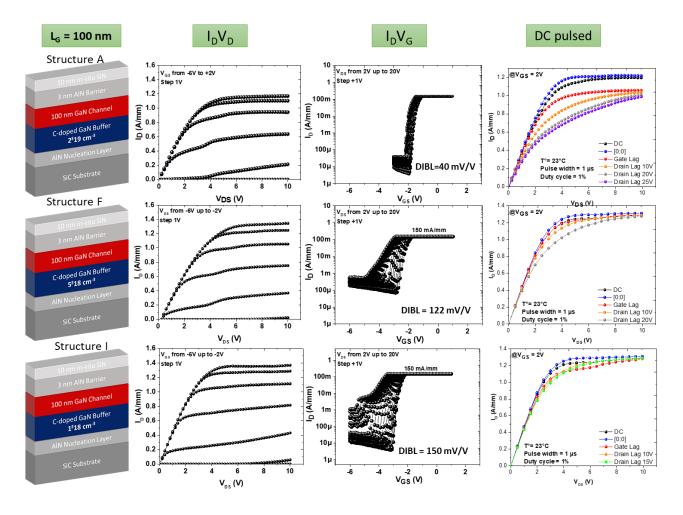

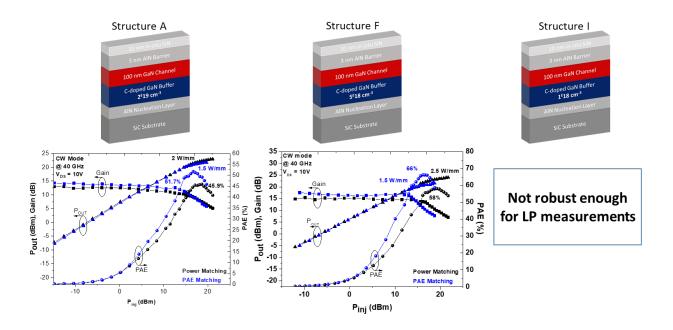

|       | 111.1.3 | 3.         | Impact of the Carbon-doped variation in the buffer                                           | 110  |  |  |  |

|       | 111.1.4 | 4. St      | tudy of structures with intermediate carbon doping and different channel thickness           | 113  |  |  |  |

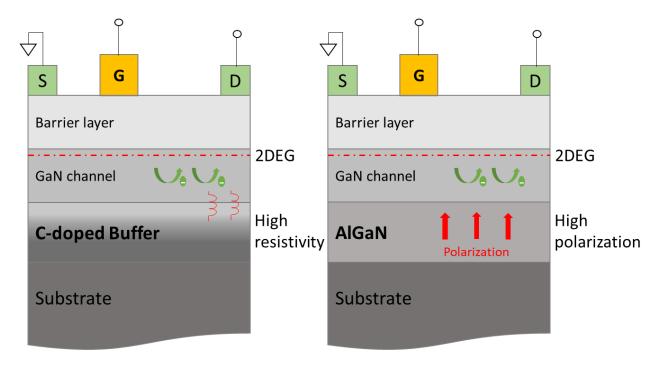

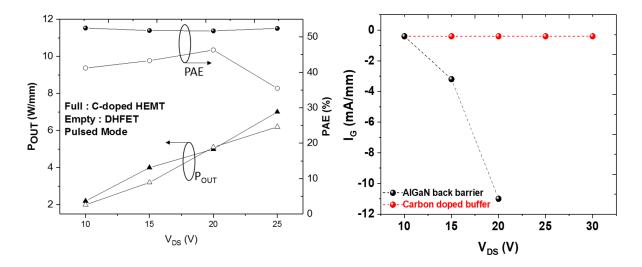

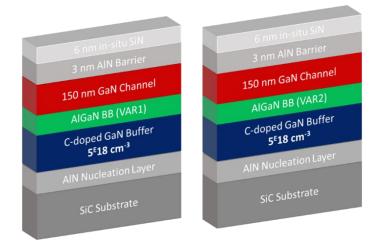

| II   | 1.2.                                       | Stud   | y of the AlGaN back barrier                                               | 115 |  |  |  |

|------|--------------------------------------------|--------|---------------------------------------------------------------------------|-----|--|--|--|

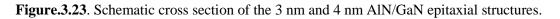

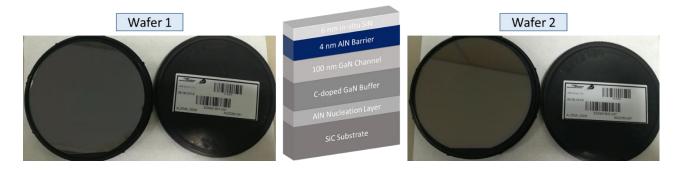

| II   | 1.3.                                       | Impa   | act of the barrier thickness 3 nm and 4 nm AIN/GaN                        | 118 |  |  |  |

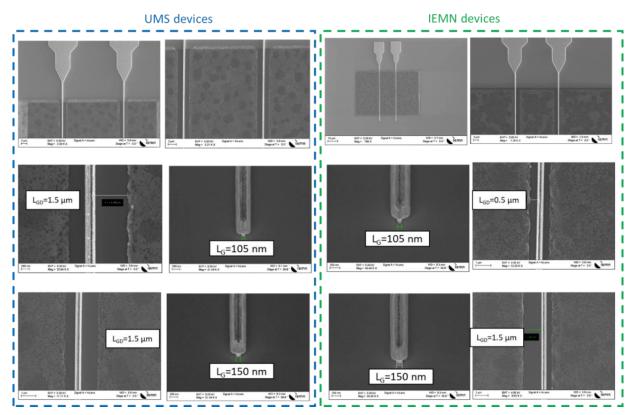

|      | III.3.                                     | 1.     | Shared process UMS-IEMN                                                   | 119 |  |  |  |

|      | III.3.                                     | 1.1.   | 4 nm AIN/GaN structures                                                   | 119 |  |  |  |

|      | III.3.                                     | 1.2.   | 3 nm AIN/GaN structures                                                   | 128 |  |  |  |

|      | III.3.                                     | 1.3.   | Comparison between 3 nm and 4 nm AIN/GaN structures                       | 140 |  |  |  |

|      | III.3.                                     | 1.4.   | Structural characterization of 3 nm and 4 nm AIN/GaN structures           | 142 |  |  |  |

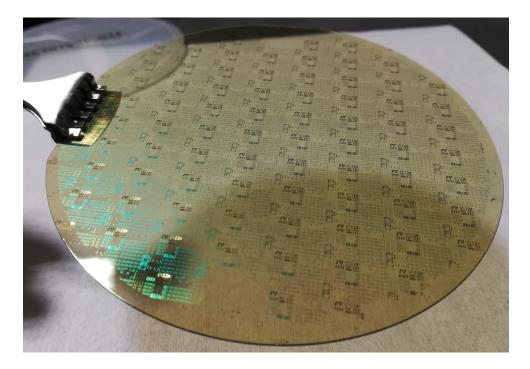

|      | III.3.                                     | 1.5.   | 3 nm AIN/GaN wafer characterization after UMS back-end processing         | 147 |  |  |  |

|      | III.3.                                     | 2.     | Large signal characterization @94 GHz for the 3 nm AIN/GaN structure      | 154 |  |  |  |

| IV.  | St                                         | ate-c  | of-the art AIN/GaN HEMT technology                                        | 155 |  |  |  |

| V.   | Con                                        | clusio | n                                                                         | 157 |  |  |  |

| Cha  | pter 4                                     | 4: Oth | ner technological approaches for high frequency millimeter-wave GaN HEMTs | 159 |  |  |  |

| ۱.   | Intro                                      | oduct  | ion                                                                       | 160 |  |  |  |

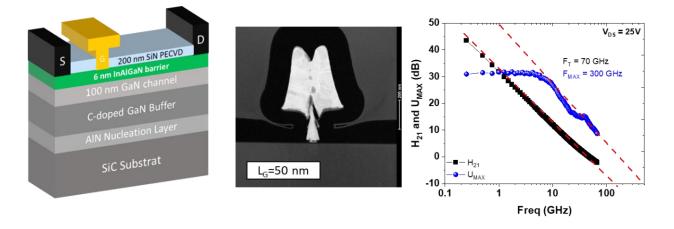

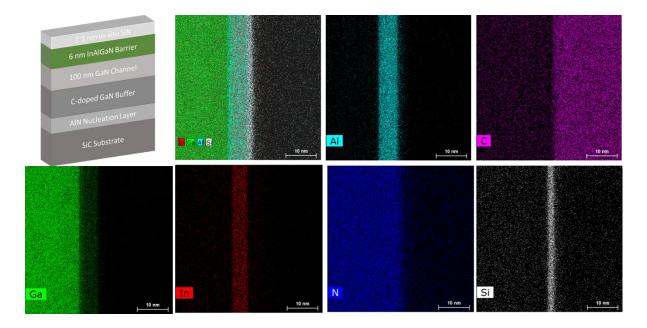

| II.  | InAl                                       | GaN b  | parrier layer                                                             | 160 |  |  |  |

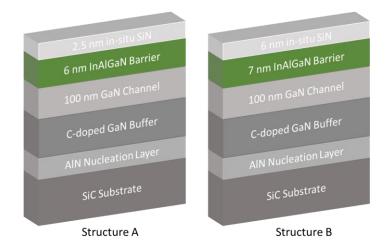

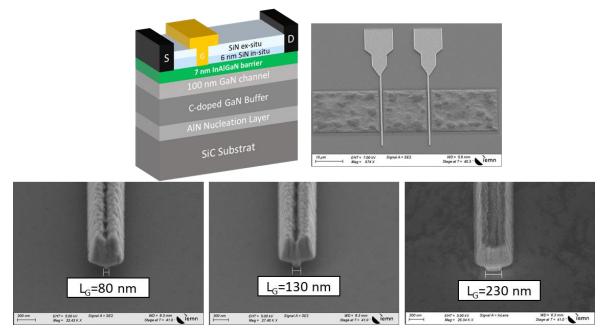

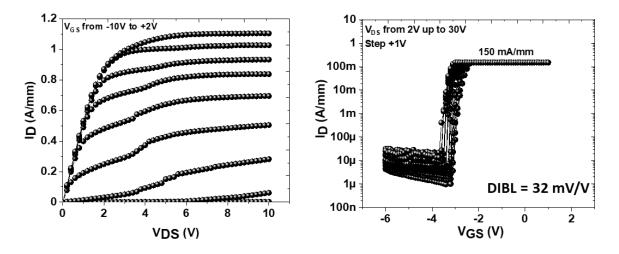

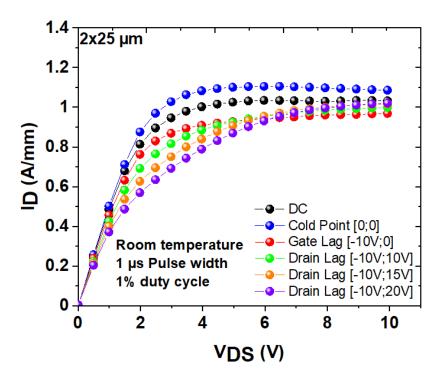

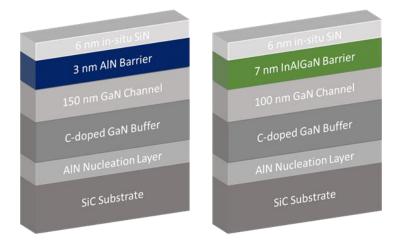

| II   | .1.                                        | 2.5 r  | nm SiN/6 nm InAlGaN/GaN (structure A)                                     | 161 |  |  |  |

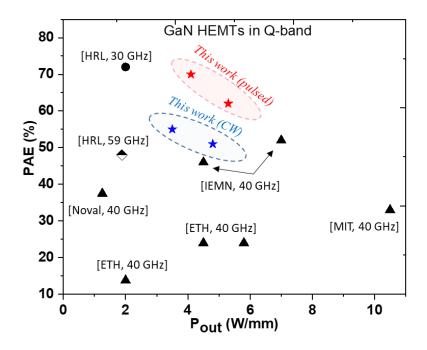

| II   | .2.                                        | 6 nm   | n SiN/7 nm InAlGaN/GaN (structure B)                                      | 170 |  |  |  |

| II   | .3.                                        | State  | e-of-the art InAlGaN/GaN HEMT technology                                  | 172 |  |  |  |

| III. | А                                          | lGaN/  | GaN buffer-free ultrathin HEMT technology                                 |     |  |  |  |

| IV.  | C                                          | onclu  | sion                                                                      | 175 |  |  |  |

| Con  | clusic                                     | on     |                                                                           | 177 |  |  |  |

| Out  | looks                                      | and    | future work                                                               | 179 |  |  |  |

| Ref  | References                                 |        |                                                                           |     |  |  |  |

| Pub  | Publications related to this PhD thesis197 |        |                                                                           |     |  |  |  |

| Ove  | rview                                      | of sa  | amples used in this work                                                  |     |  |  |  |

### Introduction

#### 1) Context of study

The last century has seen a remarkable evolution in the fields of science and technology related to many applications such as defense, military, space applications and wireless communications through the development and improvement of micro and nano-electronic devices. Most of the burden of microelectronics industry has been shouldered by the silicon (Si) material system. This is mainly due to the low cost and availability of Si worldwide. Nevertheless, progress in output power, gain and operating frequency are continually being achieved afterward.

Recent literature has demonstrated that Si-based devices, such as complementary metal oxide semiconductor (CMOS), Si-on-insulator (SOI) can achieve relatively high power at high frequencies. Consequently, they can be applied to high-power applications requiring a few watts below Ka-band. However, at higher frequencies, Si-based devices are limited to deliver the necessary output power due to the material constrains of Si. As a result, the industry has been looking for alternate materials in order to go beyond the limits of Si particularly III-V wide band-gap semiconductors such as Gallium Arsenide (GaAs) [1][2][3], Indium Phosphide (InP) [4][5][6] and Gallium Nitride (GaN) [7] which present a way forward towards achieving the desired performances. Indeed, the recent trend in RF and microwave applications is toward circuits that are reliable with low power consumption and low cost. Devices based on III-V materials like GaAs MESFETs, InP Heterojunction Bipolar Transistors (HBTs), GaAs High Electron Mobility Transistors (HEMTs) have been the preferred choice for Monolithic Microwave Integrated Circuits (MMICs).

Despite the excellent achievements, InP- and GaAs-based power amplifiers operating at higher frequency are also limited in saturated power levels because of the low breakdown voltage and related drain bias operation. Moreover, the increasing applications in RF domain required circuits that are highly miniaturized integrated delivering high power at high frequency range. GaN has emerged as strong and promising material to replace the existing technologies and to cater to the needs of these applications. The superior properties and mechanical robustness together with the capability to operate at high temperature as compared to Si, GaAs and InP materials are additional benefits of GaN. GaN MMICs revolutionize the field of millimeter-wave solid-state power amplifiers (SSPAs) and enable new applications that were previously not practical because of the limited output power of SSPAs and large size of traveling wave tube amplifiers (TWTAs). This strongly motivates operators and industries to turn their attention towards new frequency bands and especially millimeter-wave bands that cover frequency between 30 GHz and 300 GHz.

### 2) Interest of millimeter-wave band

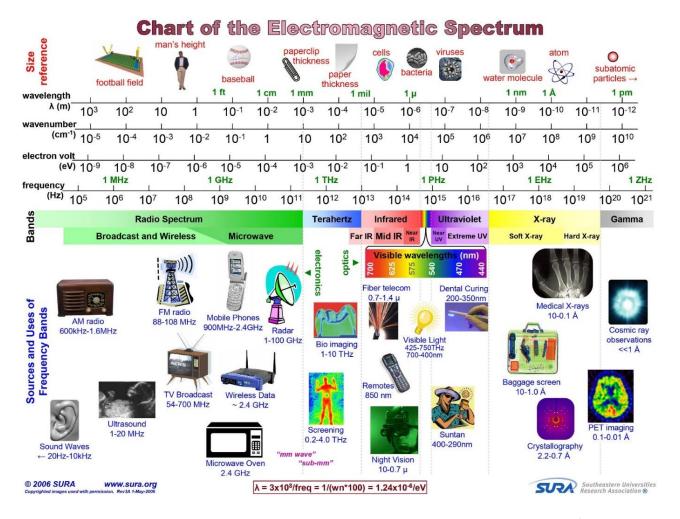

As device technology improves, emerging application systems are moving forward to higher frequencies. A diagram of the entire electromagnetic spectrum is shown in **Figure.1**. In the past decade, an impressive development has extended the capability of detection based on magnetic, acoustic, ultrasound, microwave, millimeter-wave, Terahertz, infrared and X-ray sensors.

Historically, the lowest frequency bands have been used by the early radio systems for simple voice communication with sufficient bandwidth. As technology enhanced and wireless communication increased in size as well as complexity, system designers require more bandwidth at higher frequencies. The first exploration of the microwave spectrum, however, was done in the development of radar for military applications, where higher frequency allows high antenna resolution.

As engineers pushed higher in frequency for RF applications, interest in millimeter-wave band increases. Millimeter-wave radiation occupies a region of the electromagnetic spectrum between microwaves and terahertz. Thanks to its reduced wavelength from 30 GHz (10 mm wavelength) to 300 GHz (1 mm wavelength), millimeter-wave radiation has better transmission properties through most dielectrics, good penetration ability and high resolution. It is able to pass through obscurants such as fog, cloud and smoke. In addition, mm-W radiation is non-ionizing.

Although THz provides high resolution, it does not allow a large scene illumination due to the high atmospheric absorption and its medium penetration. Infrared technique is not the appropriate alternative and does not meet the requirements because of its low penetration. On the other hand, X-ray imager limits the human body illumination due to its safety concerns (ionizing radiation) and low range of detection and imaging. Therefore, the choice of mm-wave system is the most suitable solution to meet the requirement thanks to its properties and wide available bandwidth which enable smaller components with improved performances.

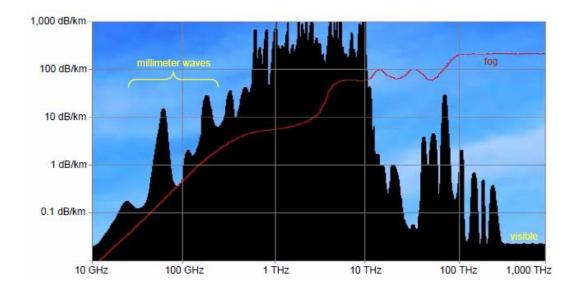

The transmission characteristics of millimeter-wave radiation are highly affected by the Earth's atmosphere. **Figure.1.2** shows the attenuation of electromagnetic radiation in the atmosphere as a function of frequency at a given temperature, pressure, and humidity. The attenuation in the atmosphere from millimeter-wave to THz region is marked by several resonant peaks of high attenuation and windows of lower attenuation between the peaks. These peaks render the atmosphere nearly opaque to most of the submm and far-infrared wavelengths. It can be noticed that wavelengths in the windows are the ones typically used for transmission in this region.

**Figure.1.1** The electromagnetic spectrum as measured in wavelength (m), wavenumber (cm<sup>-1</sup>), energy (eV), and frequency (Hz). <u>www.sura.org</u>

Continuing even higher in frequency, the absorption characteristics become dominated by molecular vibration and electron transition energy levels. Therefore, the attenuation increases with frequency starting in the microwave region until far-infrared region, then falls eventually through the infrared until reaching a minimum in the visible region. While the millimeter-wave region provides low attenuation and broad propagation windows the attenuation within the sub- millimeter-wave and THz regions rises to 100 dB/km and more. Millimeter-wave systems can be operated under humid, moistly, and rainy conditions. Also dust and fog can be propagated easily. It has the capability to operate during day and nighttime and under bad weather conditions. Moreover, it can "see through" some wall material such as drywall or dry plywood, but not through structural materials or metal sheets.

Figure.1.2. Absorption features in Earth's atmosphere

### 3) Thesis organization

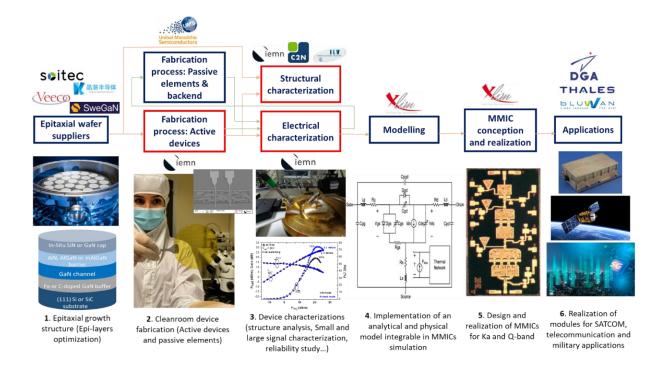

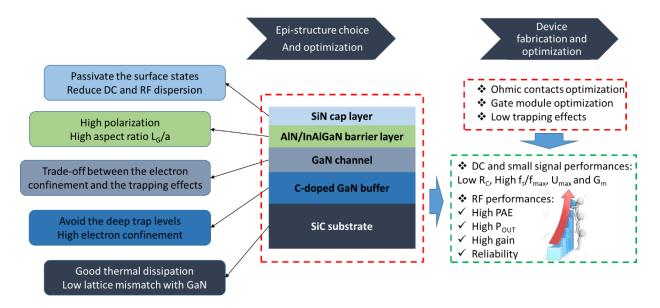

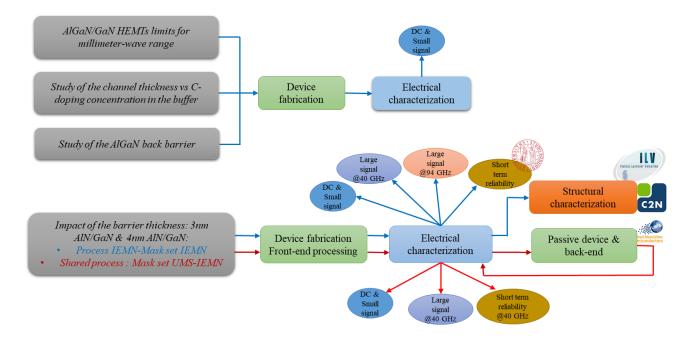

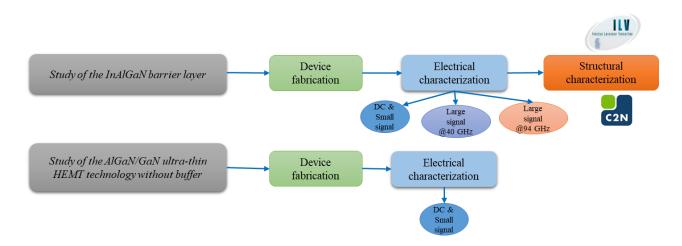

This thesis work is part of several projects (FUI VeGaN, ANR COMPACT, EU EDA EUGaNiC and DGA-CNRS GREAT) at IEMN with the aim of developing a new GaN technology on SiC substrates for Ka and W-band frequency. The process is described in **Figure.1.3**. Between the epitaxial structure growth and the targeted applications, there are several steps, which are part of this thesis work.

This approach begins with device fabrication at IEMN using various epitaxial structures grown by different suppliers (Soitec, Veeco, SweGaN). Investigated research in this work for GaN technology development has several objectives: first, the development of a robust technology with high millimeter-wave performances while maintaining high operating voltages ( $V_{DS} > 20V$ ). Second, a technology that will push the limits in terms of power density, current density and especially high power-added-efficiency. Third, a technology with a reduced impact of thermal and trapping effects.

Subsequently, in order to evaluate the heterostructure and the transistor performances, advanced characterizations are necessary. Several types of characterizations are carried out: static, small signal, pulsed and large signal at IEMN (details will be given in the next chapter) and structural characterizations.

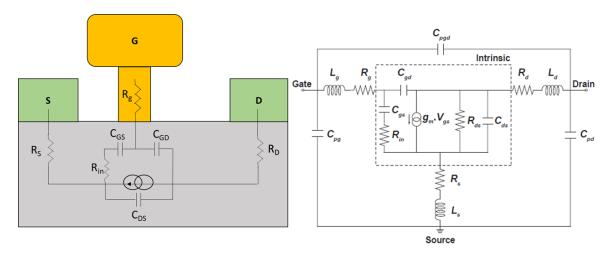

Electric characterization is followed by a modelling step with the aim of implementing physical phenomena within a component using electrical diagram based on transistors and elementary components (capacitance, inductance, resistance...).

Once the electrical model reproduces the component behavior, the next step is to design the circuits. These devices typically perform functions such as microwave mixing, power amplification, low-noise amplification, and high-frequency switching. As part of this research, the design focused on power amplifiers. Precise specifications have been set for the design of these amplifiers in order to ensure required needs of industrial for emerging applications (Thales, BluWan, etc).

This work covers the following steps: GaN-based active device fabrication and electrical / structural characterizations in millimeter-wave frequency (Figure 3 in red). The aim is to support the development of a complete European supply chain from III-V semiconductor material to a demonstrator. This is believed to constitute a decisive asset in securing a reliable European source of GaN for next-generation millimeter-wave amplifiers related to future 5G telecommunications, space or military applications.

The thesis begins with **chapter 1**, which introduces GaN technology and its role for millimeterwave applications and describes the main industrial and academic players. The overview includes GaN material properties, GaN-based heterostructures and intrinsic characteristics of III-nitrides semiconductors. Then, GaN HEMT structure and related technologies are described showing the advantages and limitations for high frequency applications. Finally, the device design, fabrication, and optimization of millimeterwave GaN-based HEMT as well as state-of-the art GaN devices are presented.

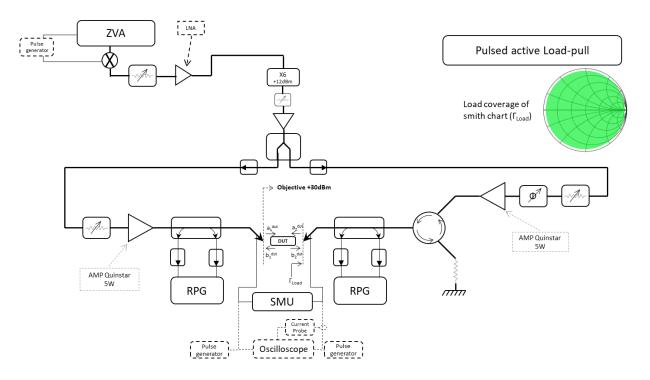

**Chapter 2** summarizes the device fabrication steps and optimizations of GaN-based HEMT technology for high frequency. An overview of the test benches used in the frame of this thesis are described (static, small signal and DC pulsed, large signal up to 40GHz). The development of a power measurement set-up for carrying-out active Load-pull measurements in continuous (CW) and pulsed mode up to 94GHz is reported.

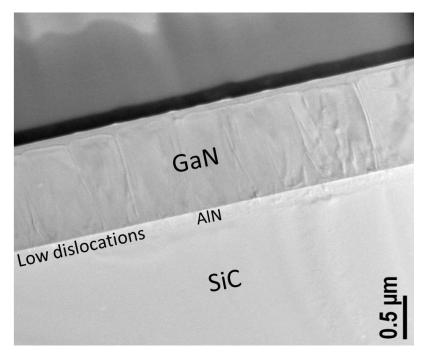

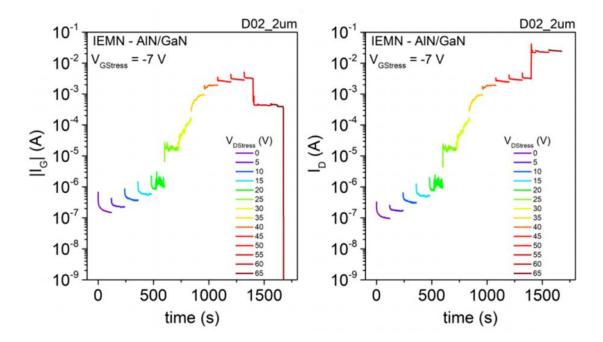

**Chapter 3** presents the structural and electrical characterization of GaN technology on silicon carbide substrates. In this chapter, several batches of HEMT structures are studied in order to analyze various parameters affecting the device performances and reliability. In particular, the impact of both the undoped GaN channel thickness, the carbon concentration within the buffer, and the AlN barrier thickness has been extensively studied by means of DC, pulsed, RF, power measurements up to 94 GHz, and structural analysis.

**Chapter 4** gives an overview of other approaches for high frequency GaN HEMTs based on InAlGaN/GaN and thin-HEMT AlGaN/GaN technology. Structural and preliminary electrical characterizations are realized on the InAlGaN/GaN structure.

Figure.1.3. Simplified process of the GaN technology system realization

# Chapter 1: GaN HEMTs – Technology and Overview

### I. Introduction to GaN Technology

### I.1 Targeted applications for GaN millimeter-wave

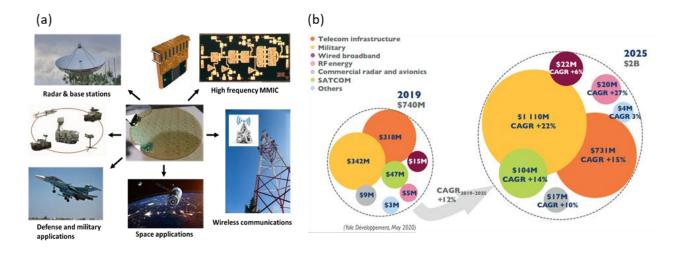

Recent improvement in GaN-based devices have allowed a demonstration of a variety of next generation millimeter-wave circuits. With its wide bandgap, high saturated electron velocity and higher breakdown voltage, GaN technology is a very promising candidate for realizing circuits with high power, high efficiency and wide operational bandwidth. GaN has also a high thermal conductivity, which combined with its wide bandgap makes them suitable for high temperature applications. These advantages are attractive for many applications such as defense and military, space applications and next-generation millimeter-wave amplifiers related to future 5G cellular telecommunications. Some of these applications are illustrated in **Figure.1.4.a**.

Figure.1.4. Illustration of some applications for GaN HEMTs (a), 2019-2025 packaged GaN RF device market forecast (b)

These applications have received a boost from the implementation of GaN technology in the past few years. The total GaN RF market will increases from \$740M to more than \$2B by 2025 in order to meet the needs of millimeter-wave spectrum (**Figure.1.4.b**) [8].

In telecom infrastructure, the wireless communication frontier is shifting from the current fourth generation (4G) to the forthcoming fifth generation (5G) while paving the way for millimeter-wave technology. GaN-based devices will overcome several challenges in order to meet ever-greater system level requirements especially in terms of efficiency, power levels and modulation bandwidth. The increase in bandwidth will favor increasing GaN deployment in the coming years.

For military applications, TWT-based systems have been replaced by GaN technology in order to improve the national security. While the demand is increasing for efficiency under harsh-conditions, GaN is a potential solution to satisfy the RF millimeter-wave transmitter/receiver module requirements for defense especially radar communication. The total GaN RF military market may surpass \$1.1B in 2025.

For aerospace applications, some of the requirements for a device in a spacecraft are small size, and high/low temperature operation. Moreover, GaN-based devices deliver lower losses and have the capability to operate at high temperature. In addition, GaN material are inherently radiation-hard, which means that such devices are less sensitive to the radiation damaging effects. It can be noticed that no major European RF GaN devices industrial player has revealed any roadmap for radiation hard devices in millimeter-wave range dedicated to space up to now. The total GaN space application market will increase to more than \$104M by 2025.

Such growth is explained by the fact that GaN will play a major role to satisfy such practical requirements of high-power amplification, broadband amplifiers and emerging 5G wireless communication network.

### I.1.1. High power amplification

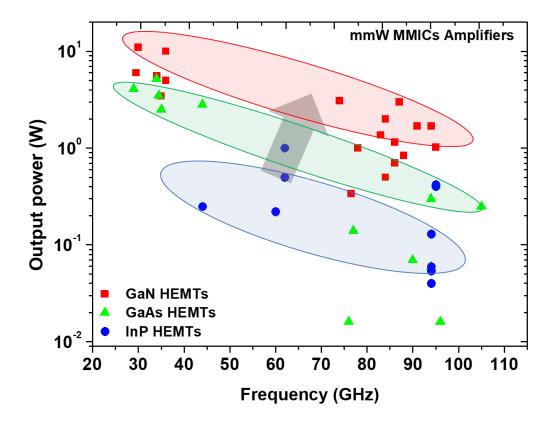

Recent and ongoing progress in semiconductor device fabrication and processing technology has pushed the limits of MMICs for millimeter-wave frequency. The first MMIC was reported in 1976 [9] and progress in output power, gain and operating frequency are continually being achieved afterwards. Indeed, MMIC components operating in millimeter-wave frequencies will be used to improve the sensitivity and performance of radiometers, receivers for communication systems and transceivers for radar instruments. Advanced GaN MMICs have demonstrated high power and recognized as a revolutionary technology, surpassing any other technologies such as GaAs and InP-based devices by a factor of 5 to 10 [7]. PAs-based on millimeter-wave GaN HEMT technology have been demonstrated up to W-band. Figure 1.5 shows the main semiconductor technologies and their limits in terms of output power and operating frequency. Stateof-the-art power level amplifiers have been reported with about 10 W and 3 W at Ka-band [10]-[12] and W-band [7][13]–[21] under continuous wave (CW) conditions, respectively. As expected, the output power decreases at higher frequencies due to the device scaling. Indeed, the gate length and the lateral device dimensions (gate-drain distance) are key parameters for high frequency operation. Furthermore, in order to reach high output power density, a high drain voltage is mandatory, which is typically inversely proportional to the device downscaling. On the other hand, spatial power combining enabled 5.2 W output power W-band GaN MMIC [22]. GaN is well known for its high output impedance and low output capacitance and high power MMIC performances.

**Figure.1.5**. Output power of MMIC amplifiers under CW operation based on various semiconductor transistor technologies [23].

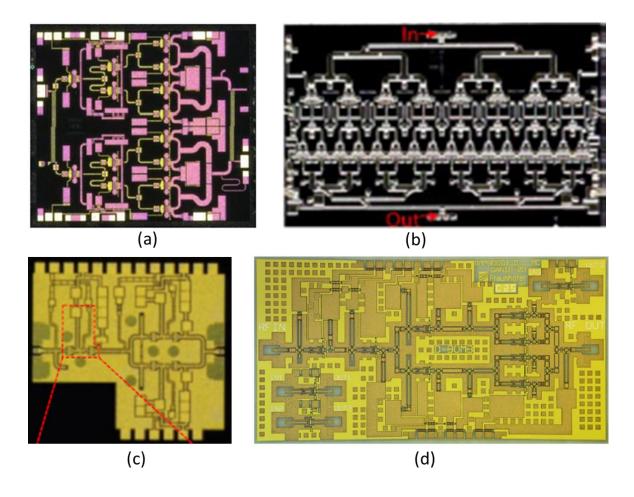

A summary of different MMICs designed in millimeter-wave frequency is shown in **Figure.1.6.** 3stages Ka-band MMIC design based on AlGaN/GaN HEMTs fabricated on SiC is shown in **Figure.1.6.a** [12]. The measured results under CW operation for the balanced 3-stages demonstrate 9.5-11 W output power and 26-30% associated Power Added Efficiency (PAE) between 28-31 GHz. **Figure.1.6.b** illustrates Ka-band AlGaN/GaN HEMTs MMIC amplifier [24]. The designed amplifier is two-stage single-ended amplifier. The achieved output power under CW operation is 20 W and the PAE is 19% at 26.5 GHz. In the frequency range of (26 - 28) GHz the output power is greater than 15 W with an associated PAE of 13%. **Figure.1.6.c** shows a fabricated W-band GaN PA MMICs, which consist of two-stage cascade units with two transistors each and identical gate lengths in order to provide high gain and low loss matching circuit [14]. At 86 GHz, the maximum output power density was 3.6 W/mm with a PAE of 12.3% at V<sub>DS</sub> = 20V under CW condition. **Figure.1.6.d** depicts a D-band PA MMICs using AlGaN/GaN HEMTs [25]. The MMIC consists of four actively matched cascode stages. Large signal measurements show a maximum output power density of 1.4 W/mm at 120 GHz at V<sub>DS</sub> = 15V with associated PAE of 11.5%.

Figure.1.6. Examples of millimeter-wave MMICs at different frequencies: Ka-band (a)(b), W-band (c) and D-band (d).

### I.1.2. Broadband amplifiers

Broadband power amplifiers have been considered as key components used in many applications such as instrumentation or communication systems that require the integration of several services with reduced number of components and size as well as operating in wide bandwidth. To date, systems covering a wide frequency range require multiple narrowband power amplifiers. Theses amplifiers are connected by means of switches or triplexers. In either case, the additional circuity causes losses and therefore such a system is not advantageous. A single broadband power amplifier covering multiple bands is necessary to replace multiple amplifiers in order to reduce costs and system complexity. Recently wideband power amplifier MMICs based on GaN have been largely used for high performance millimeter-wave components that are employed in emerged applications such as military and wireless communication. For 5G, GaN MMIC PAs are expected to be widely deployed in cellular base stations in order to reduce size and improve system integration. Therefore, it is essential for MMIC implementation to develop low-loss and compact

circuits in order to improve efficiency, output power, linearity, gain and bandwidth, which are key parameters to evaluate the power amplifiers performances.

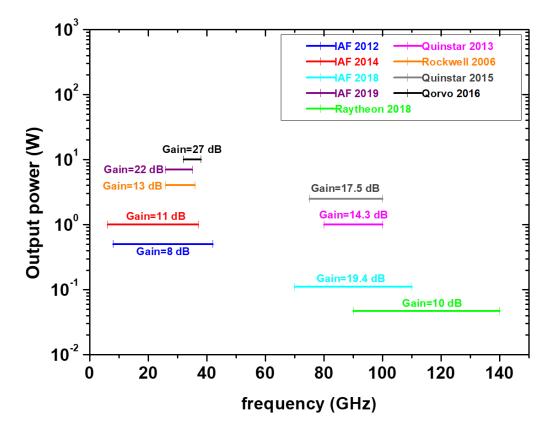

Figure.1.7. Output power of Broadband MMIC amplifiers [23].

The state-of-the-art broadband high-power millimeter-wave GaN MMIC is summarized in **Figure.1.7.** These results indicate the great potential of GaN-based PAs to increase solid-state power levels while maintaining wide bandwidth. Broadband GaN MMICs have been reported up to 140 GHz with output power ranging from 10 W over 32 - 38 GHz [11] to 47 mW over 90 - 140 GHz [26]. While these MMICs have produced attractive power levels, the highest output power is associated to a much narrower bandwidth as expected. However, by using on-chip traveling-wave power combiner circuit techniques, several watts output power using GaN MMICs have been reported by Quinstar with a bandwidth approaching the entire W-band [27]. Another reported technology enabling wide bandwidth amplifiers with high gain is the non-uniform distributed power amplifiers (NDPA). In this case, the amplifier uses dual-gate HEMTs in the driver stage of an NDPA, which boost the gain of the overall amplifier at wide bandwidth. IAF reported NDPA MMICs covering a frequency range from 6 - 37 GHz and from 8 - 42 GHz with an output power of 1 W and 500 mW with corresponding power gain above 11 dB and 8 dB, respectively [28][29].

### I.1.3. Fifth generation wireless communication

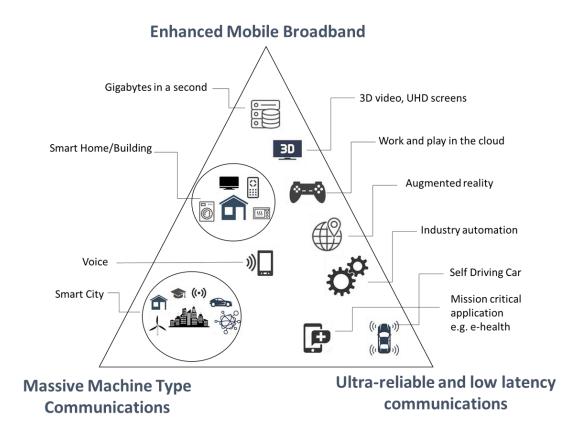

To date, the wireless network evolution was principally driven by a need for higher data rate and the increasing number of connections for mobile communication, which offer exciting user experience in our every-day lives. Currently, the wireless communication frontier is shifting from the current fourth generation (4G) to the forthcoming fifth generation (5G). Major international communication companies and manufacturers are all competing to demonstrate 5G capabilities and features, while simultaneously paving the way for millimeter-wave technology that makes 5G fundamentally different from previous generations of mobile telecommunications. The broadband radio access and wireless networks cover several aspects of 5G, not only for the telecommunication industry but also for a wide range of sectors, including robotics, automotive, factory automation, healthcare, and education. Although the expected features and use cases for 5G are extensive and diverse, the start of 5G deployment will likely address only a few of the highlighted use cases through three scenarios: ultra-reliable low latency communications (uRLLC), enhanced mobile broadband (eMBB) and massive machine type communications (mMTC) as illustrated in **Figure.1.8**. Under the 5G umbrella, these scenarios have quite different system-level performance requirements such as latency, mobility, number of users and data rate while targeting to surpass any performances of previous mobile telecommunication generation.

The future 5G network for eMBB targets 20 Gb/s peak data rate, which represents ten times improvement compared with 4G LTE network. New waveform, along with Massive Input Massive Output (MIMO), beamforming and millimeter-wave technologies are considered as key features for 5G in order to reach dramatic network performance in terms of high efficiency, and high-power PA performance over a large frequency range, leading to low-cost, large bandwidth, and small size base-station system [30]. GaN will surpass conventional semiconductor materials for 5G network applications, requiring higher frequencies, tight integration, and minimal implementation cost while operating under harsh environments. Moreover, the device technology selection as well as the circuit configuration are critical in order to meet the complex requirements of PAs for 5G applications. As the development of GaN technology increases, advanced PA architectures have evolved in order to meet ever-greater system level requirements especially in term of efficiency, power levels and modulation bandwidth. Furthermore, silicon still dominates the sub-6 GHz band, but at higher frequencies, GaN is highly attractive. On the other hand, the critical allocation of spectrum will dictate the design and implementation of transceiver hardware. Therefore, the choice of millimeter-wave frequencies is required in order to extend the current 4G frequency band and to push the available spectrum limits for high data rates in the microwave range.

**Figure.1.8.** Some usage scenarios proposed by International Mobile Telecommunications (IMT)-2020 [31].

Recently, various GaN PAs have been reported in this frame. In order to increase data rate while operating at higher frequencies, modulated signals with large bandwidth and a more complex scheme are used. Moreover, with the increasing needs of efficiency under multiband, multimode operation, several approaches such as Doherty amplifiers, Envelope tracking amplifiers and a digital transmitter based on GaN have been demonstrated [32]–[34]. While millimeter-wave 5G is being developed, it will be first implemented on sub-6 GHz 5G systems using the same MIMO beamforming techniques but at lower and more technologically accessible frequencies [35]. 5G communication network is designed not only for spectrum bands below 6 GHz but also for high bands above 24 GHz. A number of sub-6 GHz 5G MIMO systems have been demonstrated at 3.3, 4.2 and 2.14 GHz [35][36]. In the millimeter-wave, several GaN PAs have been proposed. **Table.1.1** summarizes some performance results of PAs at different frequencies especially in Ka-band for 5G applications. Despite the proposed approaches, there are a large room for improvement of PA performances in order to satisfy such practical requirements of 5G wireless communication network, such as millimeter-wave, high linearity, high output power, large bandwidth and

compact size. GaN-based devices are among the most suitable for power amplifiers and will certainly play a major role as broadband technology for 5G wireless communication.

| Reference | е Туре               | Size                                     | F (GHz)     | P <sub>out</sub> (dBm) | PAE (%)      | PAR (dBm) | Gain (dB)  |

|-----------|----------------------|------------------------------------------|-------------|------------------------|--------------|-----------|------------|

| [32]      | РА                   | $2.9 \text{ mm} \times 1.7 \text{ mm}^2$ | 26.5 – 29.5 | 36.9 to 38             | 17.9 to 23   | NA        | NA         |

| [35]      | Doherty PA           | 1.8 mm × 1.7 mm                          | 28          | 36                     | 51           | NA        | 30         |

| [37]      | Switching mode<br>PA | NA                                       | 28 – 39     | 24.3                   | 59           | NA        | 8.2        |

| [24]      | PA                   | $3.8 \text{ mm} \times 6.2 \text{ mm}^2$ | 26 – 28     | 43.3 to 41.6           | 19.8 to 13.2 | NA        | NA         |

| [38]      | НРА                  | 3.4 mm × 3.3 mm                          | 26.5 – 29   | 39                     | 25           | NA        | 21.1 to 24 |

| [39]      | Doherty              | $3.4 \text{ mm} \times 2 \text{ mm}^2$   | 23          | 36.9                   | 27           | 29.4      | 15.4       |

| [40]      | Doherty PA           | $2.7 \text{ mm} \times 1.6 \text{ mm}^2$ | 27.5 – 29.5 | 35.6                   | 25.5         | NA        | NA         |

Table.1.1. Performance comparison of different PAs for 5G applications [24], [32], [35], [37]–[40].

The 5G network system has been defined as the key for IoE application. Research efforts invested in millimeter-wave wireless communications and the success of 5G tests have enabled the commercialization and deployment of 5G wireless networks since 2020. The increasing number of new applications such as wireless backhaul, VR/AR and space travel makes it questionable whether they can satisfy emerging services and newer applications that have not been conceived yet. This creates a motivation towards sixth generation (6G) networks. Future 6G wireless communication will be implemented in 2030 [41] with devices operating up to the THz range. The key figure of merits for the evaluation of 6G wireless networks include a peak data rate of 1 Tb/s, which is 100 times that of 5G, a latency of  $10 - 100 \mu$ s, an energy efficiency of 10 - 100 times better than 5G. The level of 6G maturity reachable in ten years by sub-THz can make this technology a powerful enabler.

### II. GaN material system and properties

#### II.1. Crystal structure

The III-Nitride semiconductors group (AlN, GaN, and InN) can be found in three following common structures: rock-salt, wurtzite (hexagonal), and zinc-blend (cubic) crystal structures. The rock-salt structure is not relevant to electronic devices so far. The zinc-blend structure is the thermodynamically metastable polytype of GaN. It is used for device applications such as smaller bandgap and higher carrier

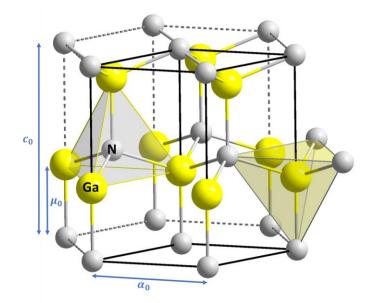

mobility due to the higher electron drift mobility and lower effective mass compared to wurtzite structure. At room temperature and atmospheric pressure, the wurtzite hexagonal structure is the thermodynamically stable crystal phase of nitride semiconductors. This structure is therefore the most commonly used for GaN-based HEMTs growth. The chemical bonds of III-nitride such as GaN are predominantly covalent, which means that each atom is tetrahedrally bonded to four atoms of the other type (see **Figure.1.9**). In addition, because of the large difference in electronegativity of Ga and N atoms, there is an ionic contribution of the bond which determines the stability of the structural phase. The GaN wurtzite structure has no inversion symmetry in the [0001] direction (c-axis). As a result, depending on whether the material is grown with Ga or N on top, it is possible to distinguish two different orientations of GaN crystals commonly known as Gaface and the N-face, which correspond to the [0001], and  $[000\overline{1}]$  crystalline faces as shown in **Figure.1.9**.

Figure.1.9. Hexagonal wurtzite crystal GaN

These two faces have different chemical properties: N-face crystal is chemically active which allows wet-chemical material etching. Therefore, they suffer from a rough surface morphology. Ga-face crystal is more chemically inert and presents much smoother surface morphology. In addition, Ga-face incorporates easier acceptors, while the N-face incorporates easier donors. Therefore, Ga-face is preferred for device operation thanks to its high electron transport properties.

The wurtzite crystal lattice parameters can be defined by the edge length of the basal hexagon  $a_0$  (3.189Å), the height of the hexagonal lattice cell  $c_0$  (5.185Å) and the internal parameter  $\mu_0$  defined as the length of the bond parallel to the c-axis, in units of  $c_0$  as shown in **Figure.1.9**. The Ga and N atoms are arranged in two interpenetrating hexagonal closey packed lattice with a shift of 3/8  $c_0$ . The subscript '0'

indicates that these values are those of the equilibrium lattice. **Table.1.2** shows an overview of these lattice parameters of wurtzite III-nitrides. Knowing that the ideal ratio lattice constant is  $c_0/a_0 = 1.633$ , GaN is the closest to the ideal wurtzite structure followed by InN and AlN. The increasing of the non-ideality crystal structure ( $\mu_0$  increases,  $c_0/a_0$  ratio decreases) allows an increase of the spontaneous polarization which will be discussed in the next section [42] [43].

| Parameters         | GaN                      | InN                      | AIN                      |

|--------------------|--------------------------|--------------------------|--------------------------|

| $lpha_0$ (Å)       | 3.189                    | 3.54                     | 3.112                    |

| c <sub>0</sub> (Å) | 5.185                    | 5.705                    | 4.982                    |

| $c_0/\alpha_0$     | 1.627 [42]<br>1.634 [43] | 1.612 [42]<br>1.627 [43] | 1.601 [42]<br>1.619 [43] |

| $\mu_0$            | 0.376 [43]               | 0.377 [43]               | 0.380 [43]               |

Table.1.2. Lattice constants of GaN, InN and AlN

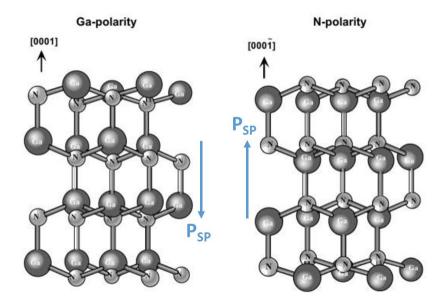

Figure.1.10. Hexagonal wurtzite crystal GaN: Ga-face polarity and N-face polarity

### **II.2.** Polarization effect

Polarization effect in III-nitrides is a crucial material property. The total polarization is the sum of spontaneous polarization  $P_{SP}$  and piezoelectric polarization  $P_{PE}$ . The spontaneous polarization is induced because of the polar nature of III-N bonds and the low inversion symmetry of the crystal, which is due to

the large difference in electronegativity of Ga and N atoms. Indeed, Ga and N atoms exhibits anionic and cationic characteristics, respectively, thus resulting in negative spontaneous polarization along c-axis given by  $P_{SP} = P_{SP}$ .  $\hat{z}$ . "Spontaneous" means that the polarization is present at thermodynamic equilibrium in the absence of constraints and "negative" because the vector  $P_{SP}$  is pointing opposite to the c-axis as illustrated in **Figure.1.10**. As a result,  $P_{SP}$  increases with decreasing the  $c_0/a_0$  ratio. For example, AlN crystal with a  $c_0/a_0$  of 1.619 presents a higher  $P_{SP}$  (-0.081 C/m<sup>2</sup>) with respect to a GaN crystal (-0.029 C/m<sup>2</sup>) which have a  $c_0/a_0$  ratio of 1.634 [43].

Moreover, an additional contribution to the polarization called piezoelectric  $P_{PE}$  is induced when external stress changes the ideality of the structure and the  $c_0/a_0$  ratio. The  $P_{PE}$  is due to the mechanical deformation and the condition for a structure to exhibit  $P_{PE}$  is to lack a center of symmetry. A standard AlGaN/GaN heterostructure is grown along the c-axis direction. Furthermore, due to the different energy gaps between AlGaN film and GaN, the band diagram shows an energy discontinuity. In addition, the constant of AlGaN has to match the lattice constant of GaN ( $a_0^{GaN} > a_0^{AlGaN}$ ), which induces a strong stress on the grown AlGaN layer. This stress causes strain in both basal plane and growth direction in order to compensate the in-plane lattice mismatch. Within the strained AlGaN/GaN heterostructure, the  $P_{PE}$  is induced along the c-axis (growth direction) or in the basal plane. The relevant relationship is [42]:

$$P_{PE} = e_{33} \epsilon_Z + e_{31} \left( \epsilon_x + \epsilon_y \right) \quad (1)$$

Where  $\epsilon_z = \frac{(c-c_0)}{c_0}$  is the strain along the c-axis,  $\epsilon_x = \epsilon_y = (a - a_0)/a_0$  are the in-plane strain assumed to be isotropic,  $e_{33}$ ,  $e_{31}$  are the piezoelectric coefficients, and *a* and *c* are the lattice constants of the strained layer. The relation between the lattice constants in the hexagonal structure is given by [42]:

$$\frac{c-c_0}{c_0} = -2 \frac{c_{13}}{c_{33}} \frac{a-a_0}{a_0} \qquad (2)$$

Where  $C_{13}$  and  $C_{33}$  are elastic constants. Combining the equations (1) and (2) the P<sub>PE</sub> along the c-axis can be also expected as [42]:

$$P_{PE} = 2 \frac{a - a_0}{a_0} \left( e_{31} - e_{33} \frac{c_{13}}{c_{33}} \right) \quad (3)$$

The piezoelectric polarization is negative for tensile strain and positive for compressive strain. Furthermore, the orientation of the piezoelectric and the spontaneous polarization is parallel in the case of tensile strain (AlGaN/GaN heterostructure), and antiparallel in the case of compressively strained AlGaN barrier (GaN/AlGaN heterostructure). For Ga-polar AlGaN/GaN heterostructure under tensile strain, the

piezoelectric and spontaneous polarization point in the same direction toward the GaN substrate as shown in **Figure.1.10**.

The polarization induced charge density in space is given by:

$$\sigma_p = -\nabla P \quad (4)$$

The polarization gradient at the interface of an AlGaN/GaN heterostructure determines a polarization induced charge density defined by:

$$|\sigma(x)| = |[P_{SP}(AlGaN) + P_{PE}(AlGaN) - P_{SP}(GaN)]|$$

(5)

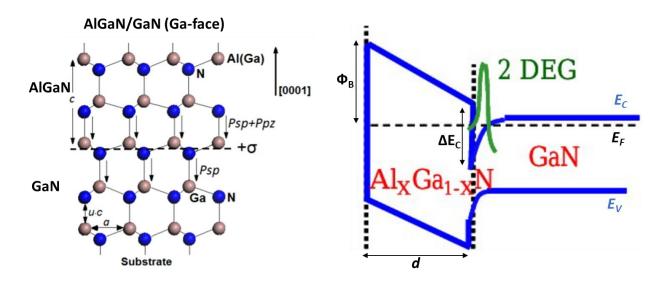

For Ga-face AlGaN/GaN structure, the polarization induced sheet charge is found to be positive  $(+\sigma)$ . Therefore, free electrons tend to compensate the charges induced by polarization generating "Two Dimensional Electron Gas" (2DEG). The 2DEG is accumulated in the triangular quantum well at the lower AlGaN/GaN interface below the fermi level E<sub>F</sub> as shown in **Figure.1.11**.

**Figure.1.11.** (a) Schematic of AlGaN/GaN heterostructure showing the spontaneous and piezoelectric polarization vector and (b) schematic band diagram of an AlGaN/GaN heterostructure [46].

In the case of N-face polarity, the spontaneous and piezoelectric polarizations have opposite directions to Ga-face polarity (point away from the substrate), which results in a negative polarization induced sheet charge density  $(-\sigma)$ . The negative sheet charge density causes an accumulation of holes at the interface, which assists to the formation of a "Two Dimensional Hole Gas" (2DEHG) upper GaN/AlGaN interface.

In a real AlGaN/GaN device, Schottky metal contact is formed by the gate electrode and the channel at the AlGaN interface. Therefore, the sheet carrier density of the 2DEG is modulated via external gate voltage bias. The maximum sheet electron concentration  $n_s(x)$  can be expected as [42]:

$$n_s(x) = \frac{\sigma(x)}{e} - \left(\frac{\epsilon_0 \epsilon(x)}{de^2}\right) \left[e \phi_b(x) + E_F(x) - \Delta E_C(x)\right] \quad (6)$$

Where, *d* is the thickness of the barrier layer,  $\epsilon(x)$  is the relative dielectric constant of AlGaN,  $e\phi_b(x)$  is the effective Schottky barrier of the gate contact,  $E_F(x)$  is the fermi level with respect to the GaN conduction-band-edge energy, and  $\Delta E_C(x)$  is the conduction band offset at the AlGaN/GaN interface.

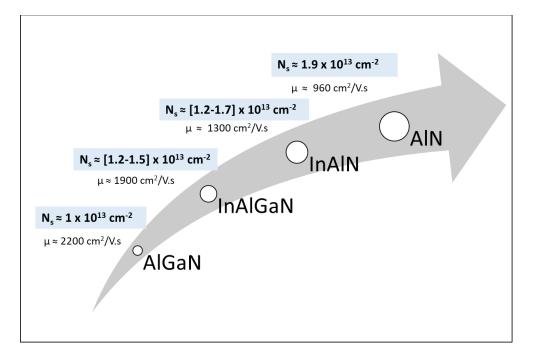

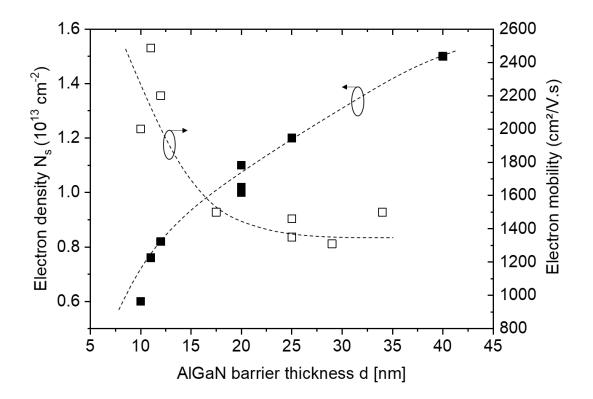

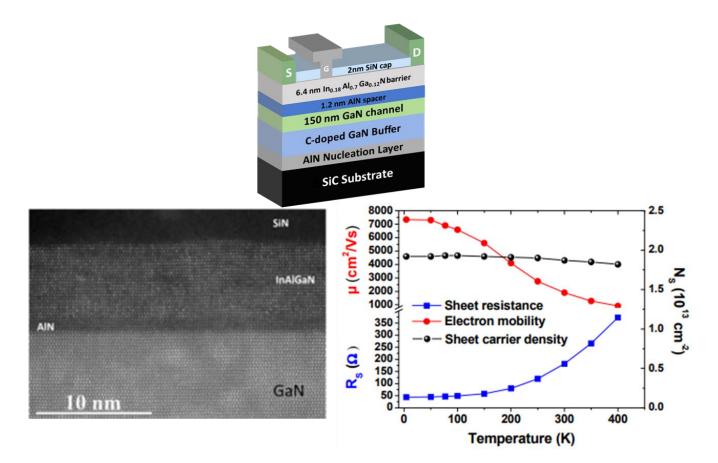

The sheet carrier density of the 2DEG for a conventional AlGaN/GaN heterostructure is usually around  $1 \times 10^{13}$  cm<sup>-2</sup> with an electron mobility around 2000 cm<sup>2</sup>/V.s [44][45]. It is found from Eq (6) that the sheet carrier concentration is dominated by the total polarization induced sheet charge, which can be controlled by the alloy composition and the thickness of the barrier layer. Several barrier layers especially ultrathin Al-rich material have been studied for millimeter-wave device applications. This part will be explained in more detail in the next sections.

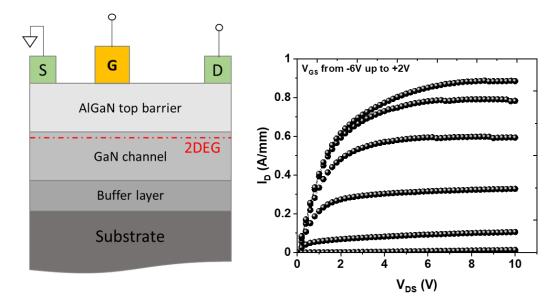

Figure.1.12. (a) Device schematic cross section of an AlGaN/GaN HEMT and (b)  $I_D(V_{DS})$  output characteristics of a HEMT

**Figure.1.12.a** shows a schematic cross section of the AlGaN/GaN HEMT including ohmic contacts (source and drain), and a Schottky contact (gate electrode). The 2DEG is naturally present at the AlGaN/GaN interface. Therefore, the current flowing in the 2DEG channel, between source and drain contacts, is modulated by the voltage applied at the gate. **Figure.1.12.b** illustrates an example of typical

output characteristics  $I_{DS}$  ( $V_{DS}$ ) showing the maximum output current, which is modulated by the bias applied to the gate. HEMT design technology and characteristics will be discussed widely in this work.

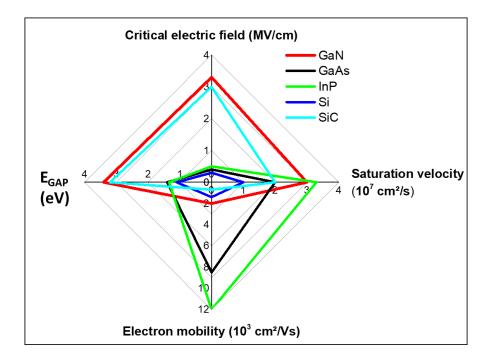

### II.3. Material properties and comparison with other materials

**Table.1.3** summarizes the material properties of widely used millimeter-wave semiconductors, demonstrating the benefit of GaN-based material system for high frequency and high-power applications. GaN technology is recognized as a key strategic enabling technology that has the potential to improve RF output power for millimeter-wave applications. Thanks to its excellent properties, a wider energy gap of 3.4 eV that exceed 3 times those of InP, GaAs and Si enables higher breakdown voltage and higher operating voltage. Another attractive characteristic of GaN is the high-saturated electronic velocity of  $2.5 \times 10^7$  cm/s. The electron velocity is related to the current density; that is why at high voltage, GaN is able to produce high current. Therefore, the wide energy gap and the high electron velocity enable for ideal power devices since power is a function of voltage and current. Moreover, GaN-based heterostructures deliver a high electron mobility of  $1-2 \times 10^3$  cm<sup>2</sup>/Vs, which allows low on-resistances. Therefore, at high frequencies, high PAE can be achieved. Also, GaN thermal conductivity (in the range of 1.3 - 2.1 W/cm.K) is much higher than GaAs and InP.

|                                                                | Si   | InP   | GaAs | SiC | GaN     | Diamond |

|----------------------------------------------------------------|------|-------|------|-----|---------|---------|

| E <sub>gap</sub> (eV)                                          | 1.1  | 1.34  | 1.43 | 3.3 | 3.4     | 5.5     |

| Electron<br>mobility<br>(cm²/V.s)                              | 1350 | 12000 | 8500 | 900 | 2000    | 1900    |

| Saturation<br>velocity<br>(10 <sup>7</sup> cm <sup>2</sup> /s) | 1    | 3.3   | 1    | 2   | 1.5-2.5 | 1.9     |

| Critical<br>electric<br>field<br>(MV/cm)                       | 0.3  | 0.5   | 0.4  | 3   | 3.3     | 10      |

| Thermal<br>conductivit<br>y (W/cm.K)                           | 1.3  | 0.7   | 0.5  | 4.9 | 2       | 6-20    |

Table.1.3. Material properties of commonly used semiconductors

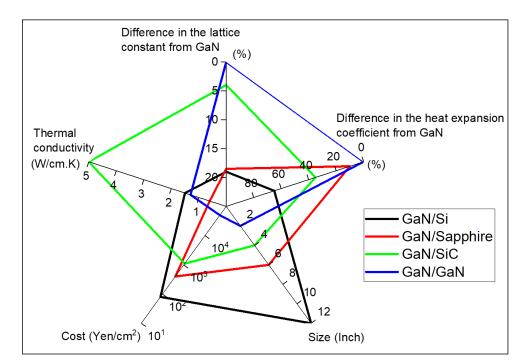

**Figure.1.13** shows a diagram comparison between material properties of semiconductors, which highlights the superiority of GaN over its counterparts. The thermal conductivity is a key factor directly related to the power dissipation from the device. For ultra-short components operating at millimeter-wave frequencies, GaN-based heterostructures on SiC substrate are preferred in order to benefit from both properties of GaN and thermal conductivity of SiC so that heat generated by self-heating can be properly spread, allowing devices to operate at high-power densities and high frequency. In addition, GaN-based material benefit from the advantage of high temperature operation and it is inherently radiation hard. They can be used in extreme conditions where Si-based devices cannot be used [47][48]. These characteristics are very promising for space applications such as telecommunications, earth observation and science missions. Nevertheless, it is necessary to validate the reliability of GaN-transistors by studying in-depth and performing robustness tests under space operational conditions [49]. More details on GaN HEMT device reliability and available products will be discussed in this manuscript.

Figure.1.13. Material properties comparison of semiconductors [23]

Different figures of merits are used in order to evaluate the device performances based on different materials. They are expressed as a function of the intrinsic characteristic of the material to be analyzed. Among the indicator factors provided in the literature, we can distinguish:

Johnson's figure of merit (JFoM), widely used for RF devices, indicates the ability of the semiconductor material to operate at both high frequency and high power:

$$JFoM = \frac{V_{sat}E_{C}}{2\pi} \qquad (7)$$

Where  $E_c$  is the critical electric field and  $V_{sat}$  is the electron saturation velocity.

It can be noticed that JFoM can be expressed as a function of the breakdown voltage ( $V_{BK}$ ) and cut-off frequency ( $F_T$ ) in order to evaluate the RF performances. It is given by [50][51]:

$$JFoM = V_{BK} \times F_T \qquad (8)$$

Baliga's figure of merit (BFoM) provides an assessment in terms of voltage withstand capability and the resistive losses of the device, considering that it is given as a function of the dielectric constant of the material, the carrier mobility and critical electric field of the semiconductor:

$$BFoM = \epsilon \mu E_C^3 \qquad (9)$$

**Table.1.4** summarizes the main figure of merits of different WBG semiconductors normalized with respect to Si. Diamond shows the best figure of merits with values exceeding every other semiconductor. However, in addition to the extreme high cost and small wafer size, the growth of GaN on diamond is still challenging due to the large lattice mismatch and thermal expansion mismatch [52][53].

GaN and SiC show similar figure of merits, which presents greater advantages over conventional semiconductors. Many of the present RF devices research are focused on GaN/SiC heterostructure and have already demonstrated superior performances compared to other technologies [54][55].

Table.1.4. Main figures of merits for WBG semiconductors compared with Si [56]

|      | Si | GaAs | 4H-SiC | GaN   | Diamond |

|------|----|------|--------|-------|---------|

| JFoM | 1  | 1.8  | 215.1  | 215.1 | 81000   |

| BFoM | 1  | 14.8 | 223.1  | 186.7 | 25106   |

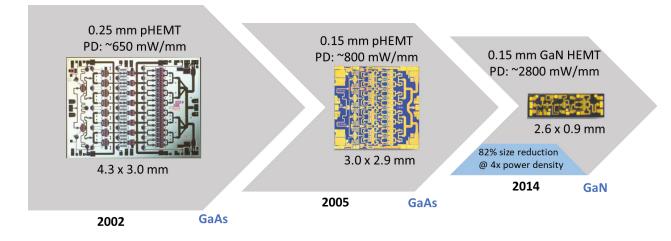

GaN is well suited not only for high RF performances, but also lead to smaller and cheaper chip size. The GaN MMICs reported so far have more than 5 times higher power density with smaller size than GaAs MMICs. As illustrated in **Figure.1.14**, GaN MMICs enables the reduction by 82% as compared to GaAs pHEMT MMICs while providing more than 4 times power density. As a result, GaN MMICs can deliver higher efficiency due to the reduced on-chip combining losses both at the MMIC and module levels.

That is why, GaN MMICs will revolutionize the field of mmW SSPAs and enable new applications, that were previously not practical due to limited power of SSPAs or large size and high cost of TWTAs.

Figure.1.14. MMICs comparison with different technologies [23]

### III. GaN-based device limitations

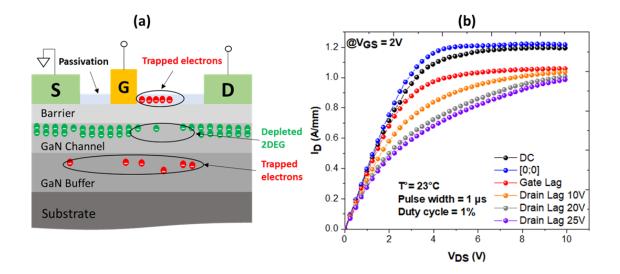

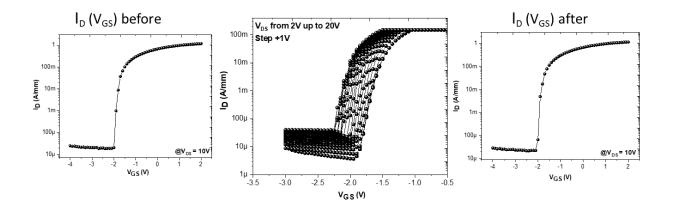

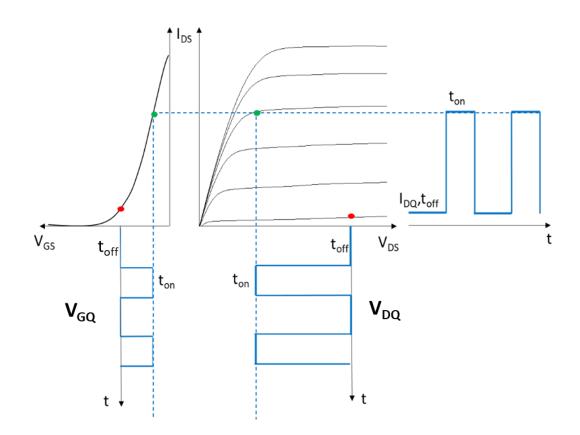

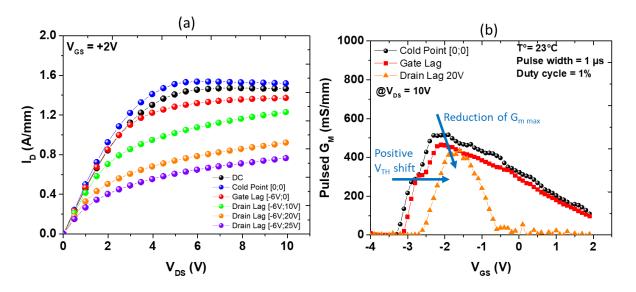

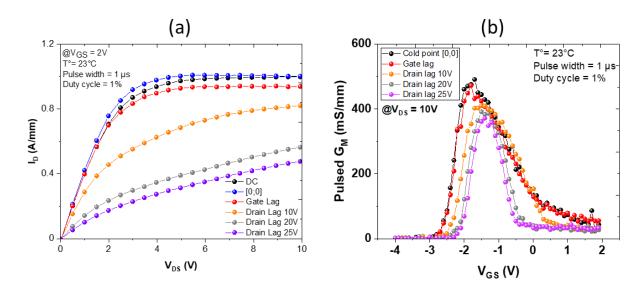

Despite the superior properties of GaN-based devices, they are still plagued by two important phenomena, especially when reducing the device dimensions: the trapping effects and the self-heating, which can directly cause current collapse and kink effect, thus reducing the device performances [57][58]. Trapping effects that occur at different location of the devices are mostly related to the crystalline imperfection induced during growth and defect-induced by device processing as shown in **Figure.1.15.a**. Surface [59][60] or buffer trapping [61] is generally electric field dependent. Several techniques are used to assess the trapping effects such as deep level transient spectroscopy measurements [62][63], temperature dependent threshold voltage analysis [64] or pulsed measurements [62][65]. As shown in **Figure.1.15.b**, pulsed I-V characteristics performed with quiescent drain voltages up to 25V at  $V_{GS} = +2V$  of AlN/GaN HEMT devices can show rather strong trapping effects as seen from the gate and drain lag due to the presence of surface and buffer traps.

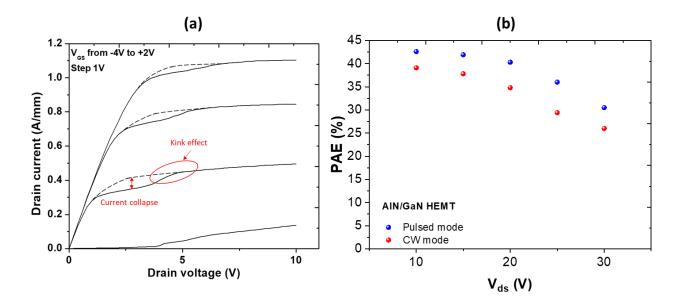

The trapping/de-trapping mechanisms induce electrical parasitic effects such as current collapse and kink effect are shown in **Figure.1.16.a**. Several investigations have demonstrated that current collapse effects are related to the presence of traps and hot electron injection into the buffer layer under high electric field [58]. It was also shown that the current collapse is attributed to trapping under the gate and in the gatedrain access region using photo-transient measurements [66]. Another electrical parasitic effect due to the trapping mechanism is the kink effect that increases the drain current, resulting in a shift of pinch-off voltage towards more negative voltages. Several explanations have been suggested [67]: the impact ionization and subsequent hole accumulation causing the change of surface or channel/substrate interface, field-dependent trapping/de-trapping in deep levels [68] and a combined effect of impact ionization and deep levels which induce a modification of surface states, buffer or channel/substrate interface deep levels by the generated holes [69]. Other studies have reported that kink effects in GaN HEMTs are related to both impact ionization coupled with the presence of slow traps in the epitaxial layers under the gate, possibly into the GaN buffer [70][71].

**Figure.1.15**. Schematic cross section of a GaN HEMT, indicating electron trapping location (a), Pulsed I-V characteristics with various quiescent bias points: Cold point:  $V_{DS} = 0V$ ,  $V_{GS} = 0V$ , gate lag:  $V_{DS} = 0V$ ,  $V_{GS} = -6V$ , and drain lag:  $V_{DS} = [10V-25V]$ ,  $V_{GS} = -6V$  (b) [23].

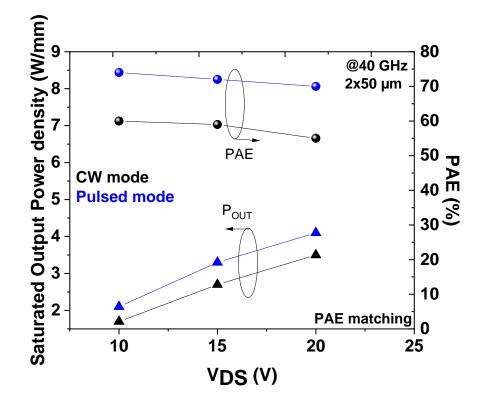

**Figure.1.16.b** [72] shows a comparison between large signal CW and pulsed mode at 40 GHz of the PAE as a function of  $V_{DS}$  of an AlN/GaN HEMT. The gap in terms of performances between CW and pulsed mode confirms the presence of traps within these devices. That is why, the optimization of material quality, and related process technology is necessary in order to minimize the trapping effect phenomena. Many efforts have been carried out to minimize the parasitic effects due to electron trapping such as:

- The use of silicon nitride passivation  $(Si_3N_4)$  to improve the gate lag [57][62][73],

- The optimization of epitaxial growth conditions in order to suppress deep level traps into the buffer layers [74],

- The use of gate field plates technology to spread the electric field in the vicinity of the gate [75] or the use of an in-situ SiN passivation reducing drastically the surface states are key parameters to improve RF performances.

**Figure.1.16**. I-V characteristics showing the current collapse and kink effects due to electron trapping (a) and CW/pulsed PAE as a function of  $V_{DS}$  at 40 GHz of AlN/GaN HEMT (b).

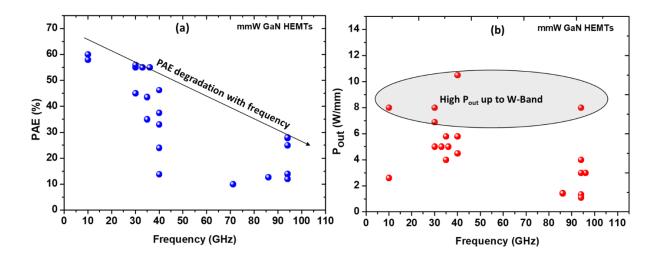

Figure.1.17. PAE (a) and associated P<sub>OUT</sub> (b) of GaN HEMTs as a function of the frequency operation [23].

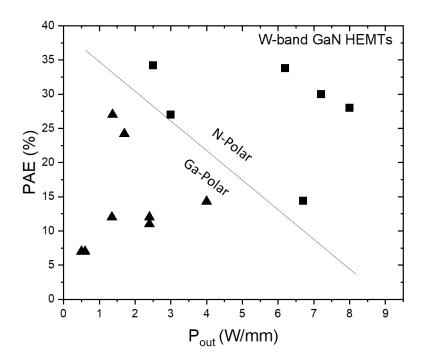

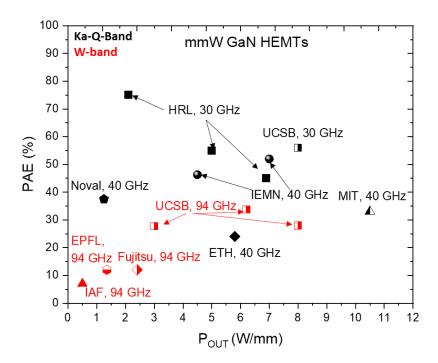

High frequency operation requires aggressive device scaling to increase the gain and the frequency performances of GaN HEMTs. **Figure.1.17** shows a benchmark of PAE and  $P_{OUT}$  of GaN HEMTs as a function of frequency. A remarkable PAE and  $P_{OUT}$  have been reported at Q-band. However, at higher frequency, the efficiency of GaN HEMTs is still limited mainly due to an insufficient gain. At W-band, the highest PAE reported to date is 33 % [76]. As shown in **Figure.1.17.a** the PAE decreases with frequency while  $P_{OUT}$  remains above 8 W/mm (**Figure.1.17.b**). The major current challenge for millimeter-wave GaN based devices is to maintain high PAE at high frequencies together with strong robustness. Thus, the

robustness and subsequent reliability remain under investigation as both scaled material and devices need to demonstrate high stability, reproducibility and uniformity.

### IV. GaN high electron mobility transistors

### **IV.1.** Historical development and incremental improvements

The history of solid-state electronic devices was marked by the introduction of the high electron mobility transistor (HEMT). The HEMT was first invented by Takashi Mimura at Fujitsu labs in 1980 using AlGaAs/GaAs device [77]. Moreover, a number of new structures HEMT-based on III-V material semiconductors have been developed by other researchers at Bell Labs in 1978 [78].

Later, GaN material demonstrated more advantages over other III-V semiconductors. The first demonstration of a 2DEG in AlGaN/GaN HEMT dates back to 1992 by Kahn [79]. This was followed by the first DC and RF measurements of an AlGaN/GaN HEMT by the same group in 1993 and 1994 [80][81]. In 1996 the first large signal RF power data at 2 GHz of an AlGaN/GaN HEMT reported an output power density of 1.1 W/mm by Wu et al [82]. The output power density increased over years up to 40 W/mm at 8 GHz [83] due to improved epitaxial growth and more advanced processing techniques.

However, the increasing demand for high frequency applications requires the development of new structures design in order to enhance the efficiency and the reliability. As discussed earlier, several research has demonstrated outstanding GaN HEMT performances in the millimeter-wave range [84][76][55][85]. Currently, reaching high PAE at high frequency of operation is the main challenge and not demonstrated so far due to the lack of power gain, enhanced trapping effects and reduced electron confinement when downscaling the device size or the self-heating.

Based on WBG material, GaN HEMTs are getting a significant focus of research activities in the recent years and are one of the most promising devices for high frequency applications. One of the approaches is the use of an ultrathin Al-rich barrier layer based heterostructure, which is promising for millimeter-wave range, because of the possibility to highly scale the epitaxial structure, while still benefiting from high polarization. Several investigations have been demonstrated that a thin InAlN and AlN barrier layers are very attractive for high frequency millimeter-wave devices. In 2006, Medjdoub *et al* at IEMN were first to demonstrate the capability of an InAlN/GaN heterostructure to deliver higher power density at high frequency and to be more stable than AlGaN/GaN structure [86][87]. Some years later, the same group has reported the high potential of the ultrathin AlN/GaN structure for high power millimeter-wave applications [88][89][90].

### **IV.2.** Figure of merits of GaN-based HEMTs

In this thesis, the main focus of the research is to develop a high performances GaN HEMT device for future high frequency power applications. In order to better understand the purpose of this thesis, it is useful to review the most important aspects of GaN HEMTs operating in the millimeter-wave range. The targeted performances required for high frequency devices include the combination of high power/high efficiency and device reliability.

#### IV.2.1. High performances: PAE/output power density

In this frame, GaN HEMT devices should be capable of delivering high large signal gain, high efficiencies and high output power density at the targeted frequency range. Equations for assessing the RF device performances at a particular frequency are given by:

$$PAE = \frac{P_{RFOUT} - P_{RFIN}}{P_{DC}} = \frac{P_{RFOUT}}{P_{DC}} \times \left(1 - \frac{1}{G_p}\right)$$

(10)

$$\eta = \frac{P_{RFOUT}}{P_{DC}}$$

(11)

$$P_{OUT} = \frac{\left(V_{DSQ} - V_{knee}\right) \times I_{DSS}}{4}$$

(12)

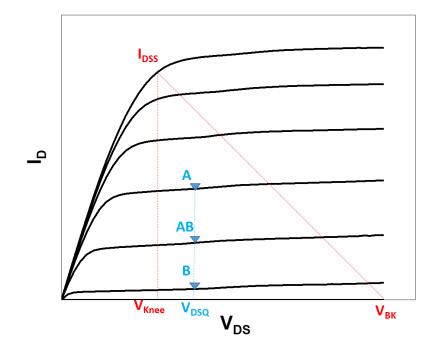

In equation (10), PAE is the power added efficiency,  $P_{RFOUT}$  is the output power density,  $P_{DC}$  is the dissipated DC power density and  $G_p$  the power gain at the frequency of interest. The PAE is the best factor in order to access the device heat management. The way in which a transistor is operated determines the polarization class. As shown in **Figure.1.18**, there are many different types of polarization class (A, AB, B...) but the main one used in this work is deep class AB. In class AB, the quiescent drain current is set to the optimum value corresponding to a trade-off between the linearity and efficiency. Furthermore, in order to achieve the highest possible PAE, a high-power gain and high drain efficiency are necessary.

$\eta$  is the drain efficiency in equation (11) which is used when the power gain G<sub>p</sub> is high enough to neglect the input power compared to the output power. To achieve the highest drain efficiency, the ratio between breakdown voltage and knee voltage should be high.

In equation (12),  $V_{DSQ}$  is quiescent drain-source voltage bias,  $V_{knee}$  is knee voltage of the transistor's I-V curve, and  $I_{DSS}$  is the saturated current density. High breakdown voltage allows high quiescent drain-source voltage operation and thus increasing the output power density.

Figure.1.18. I-V curve of GaN HEMT showing three different polarization types

The main limiting factor of the PAE and the output power density is the combination of the DC to RF dispersion and the thermal effects. The dispersion (so-called current collapse) is due to the traps and leads to a drop of  $P_{OUT}$ , the PAE as well as the drain efficiency. Moreover, self-heating within the HEMT appears at high drain voltage and have a significant impact on the PAE mainly by reducing the electron mobility.

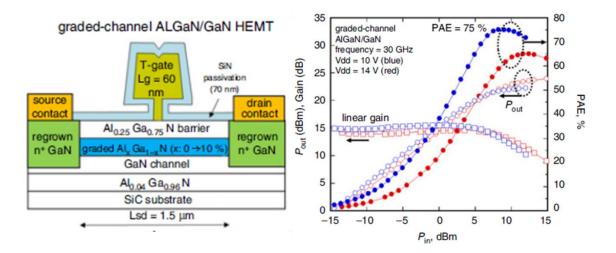

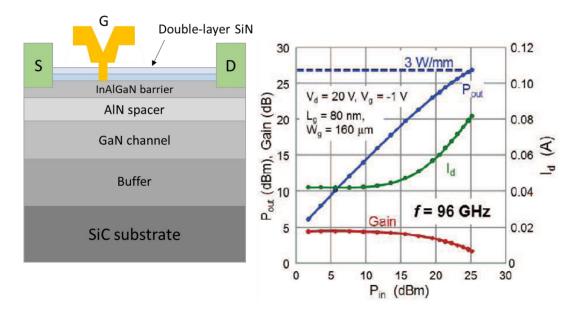

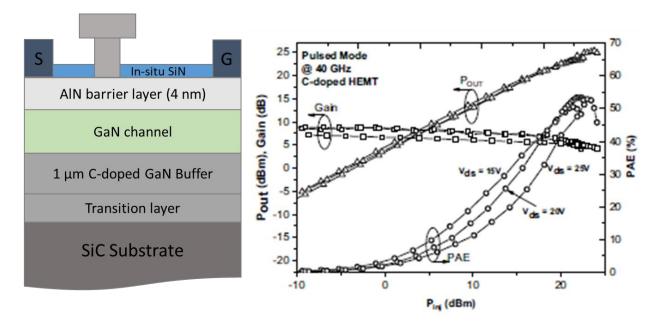

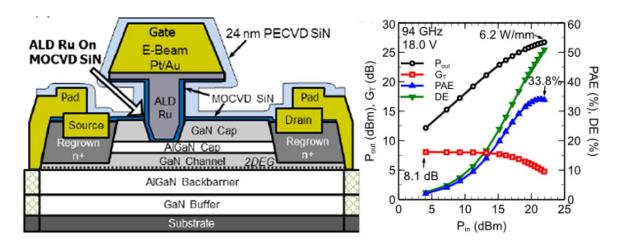

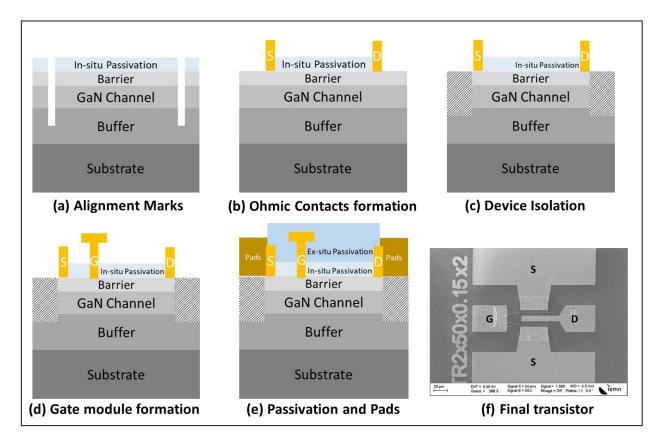

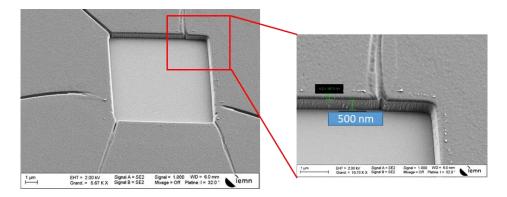

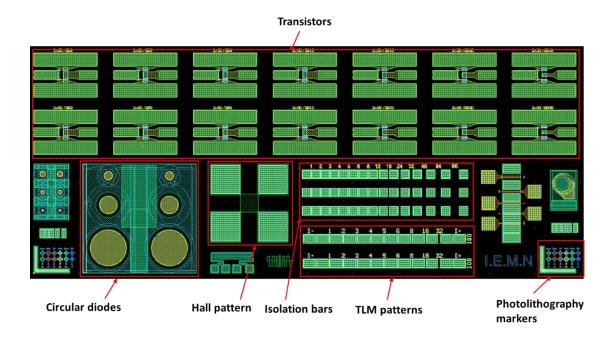

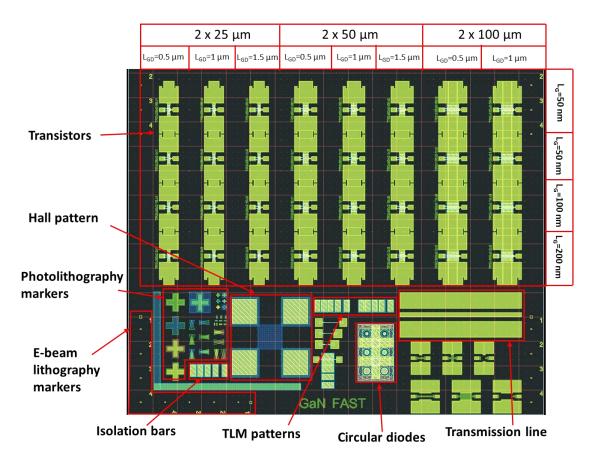

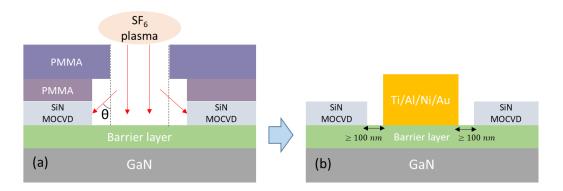

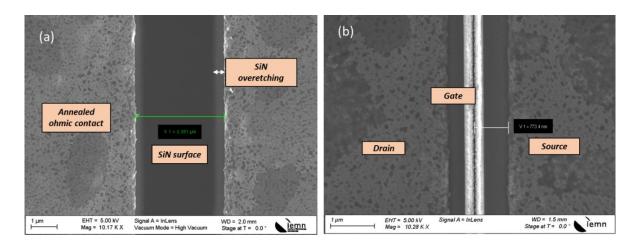

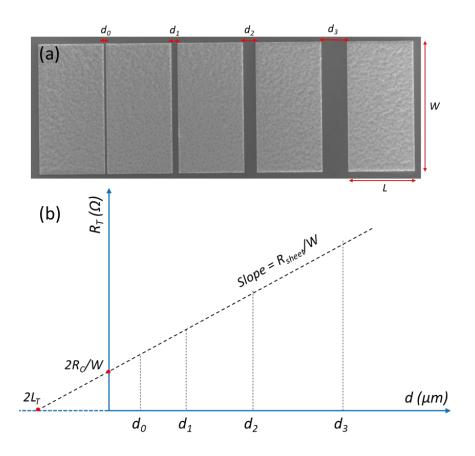

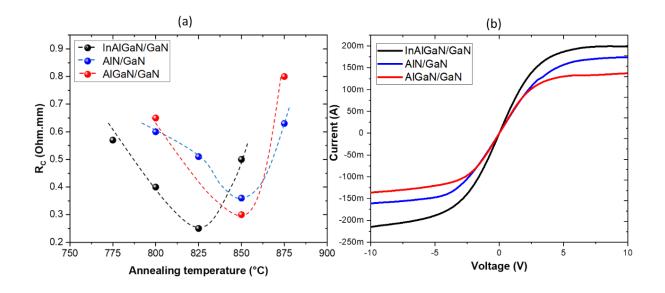

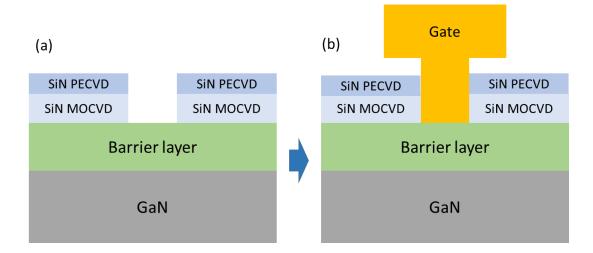

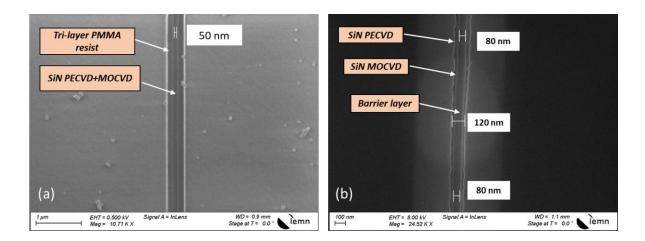

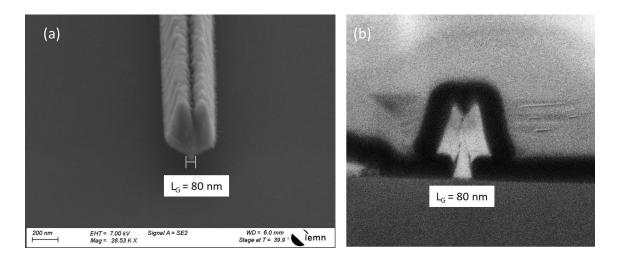

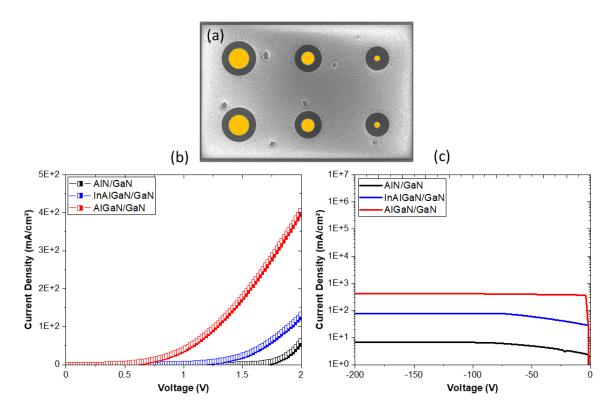

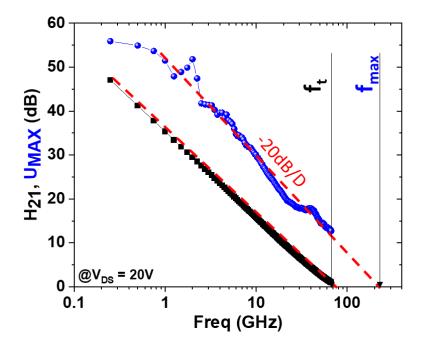

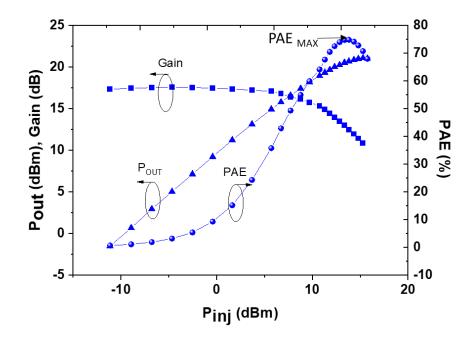

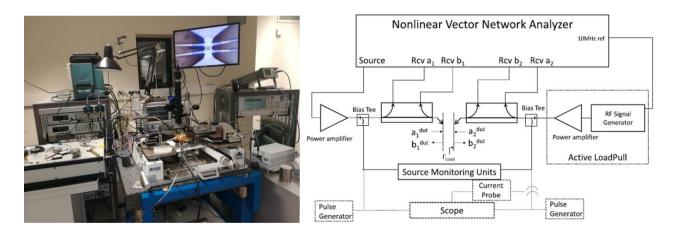

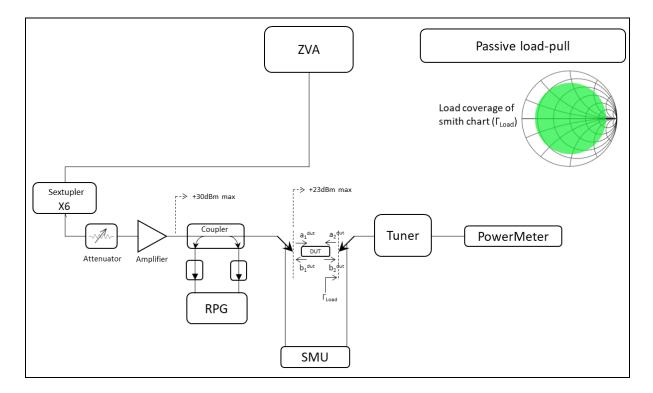

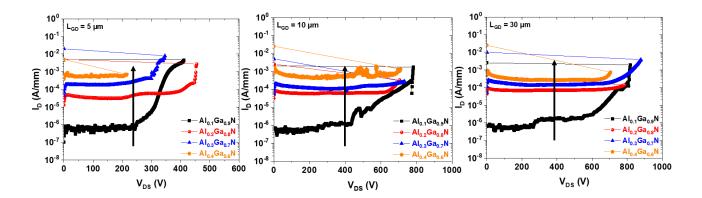

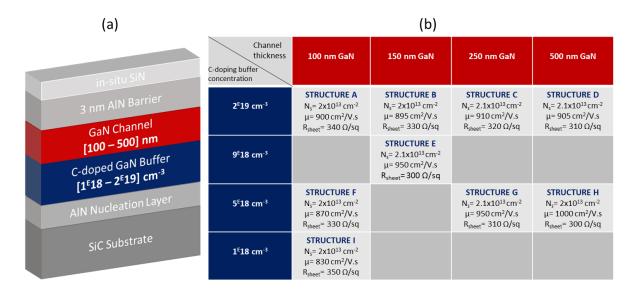

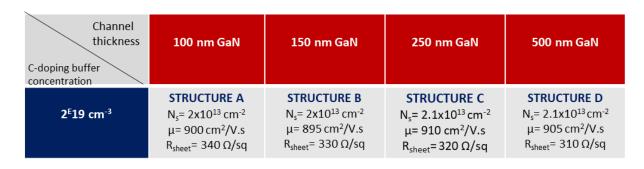

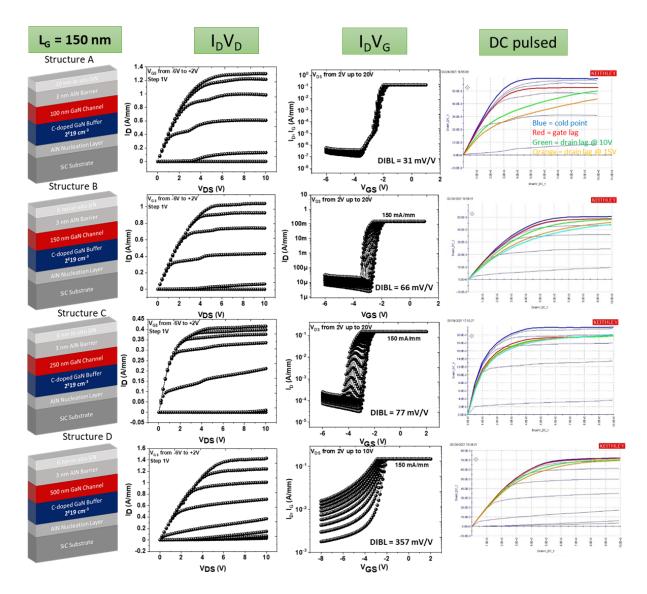

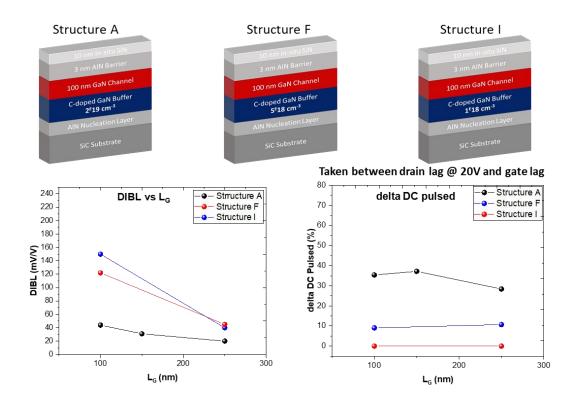

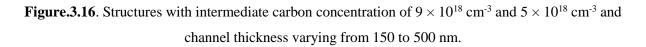

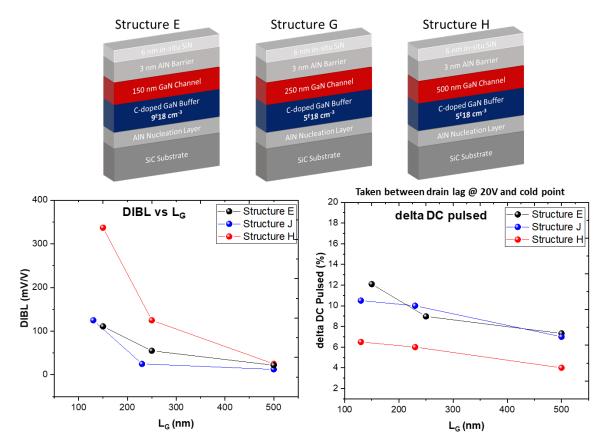

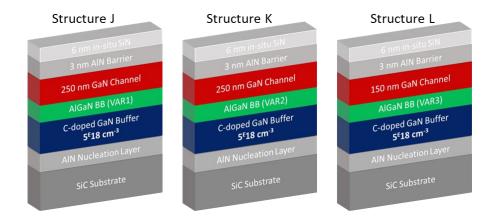

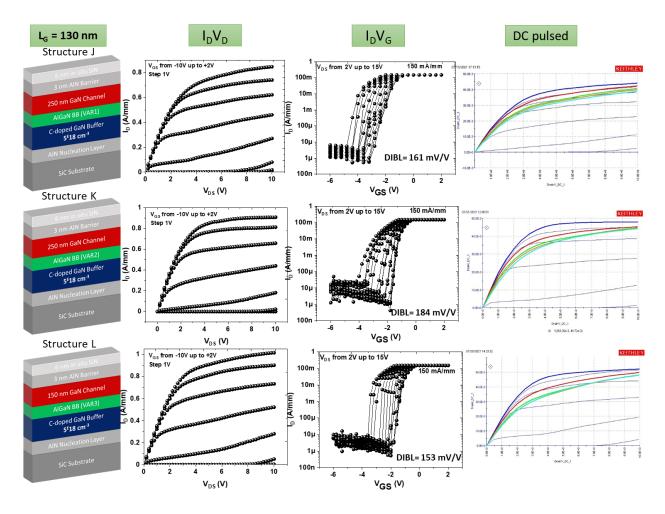

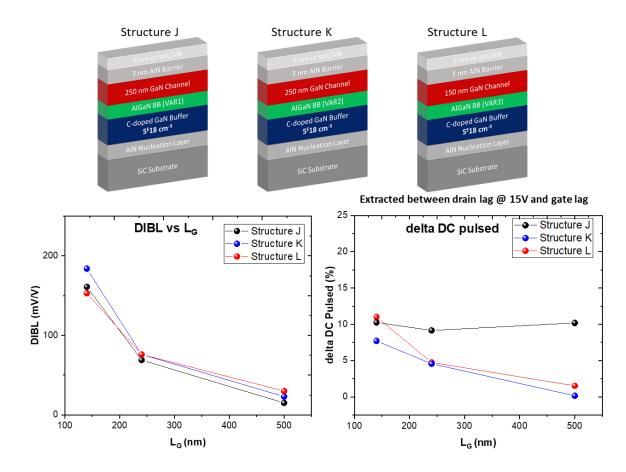

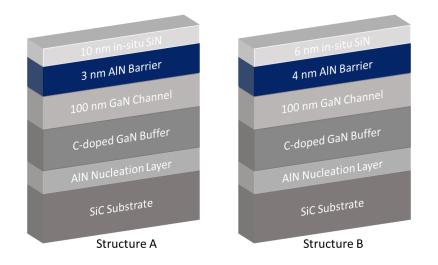

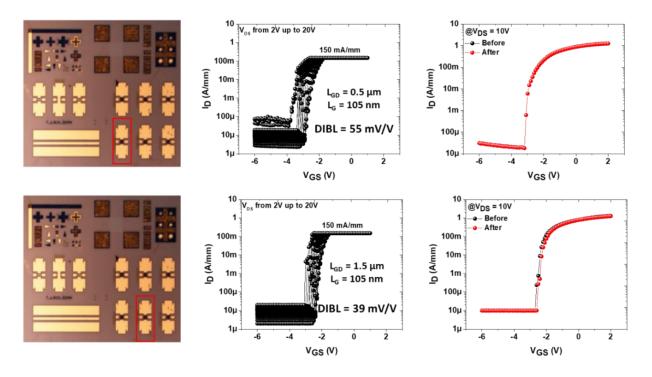

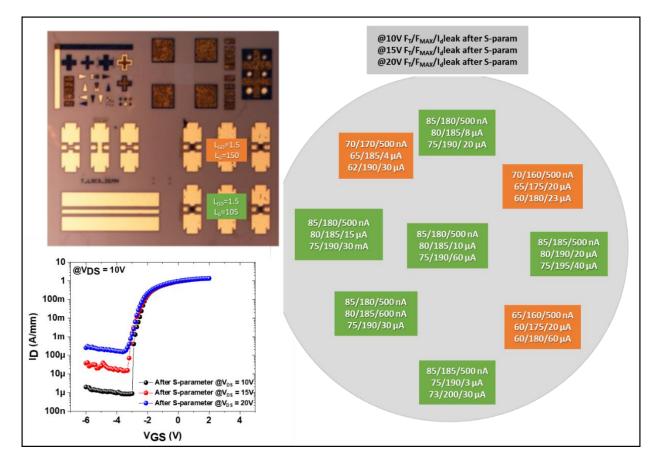

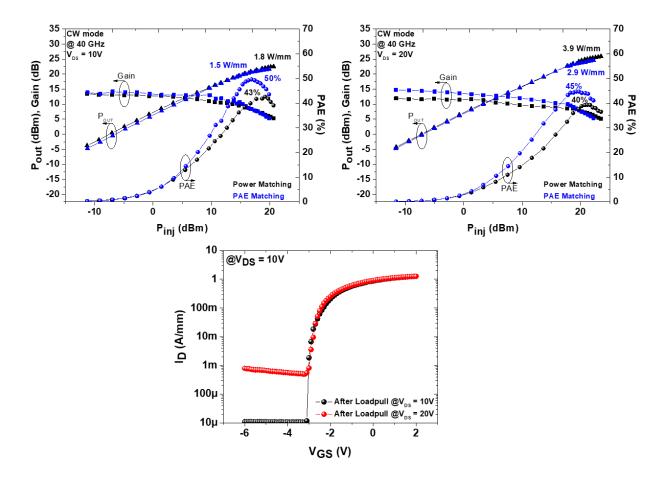

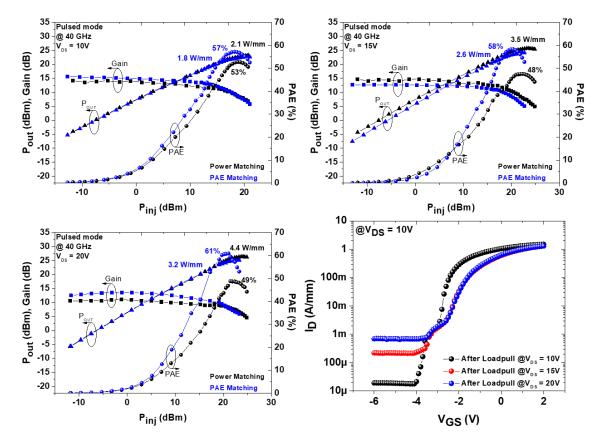

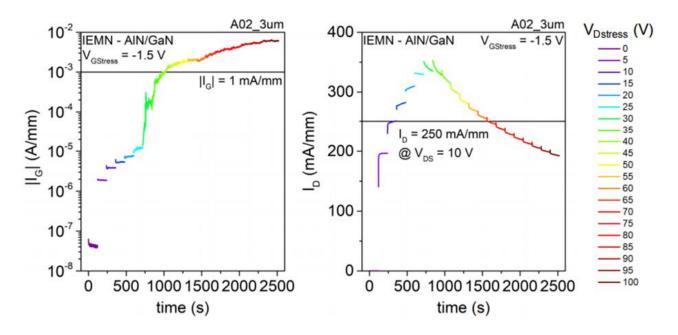

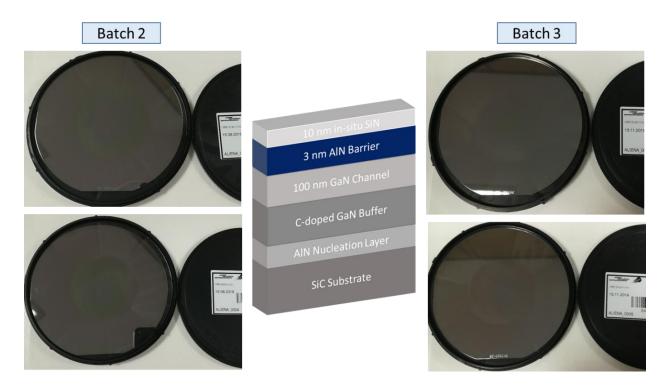

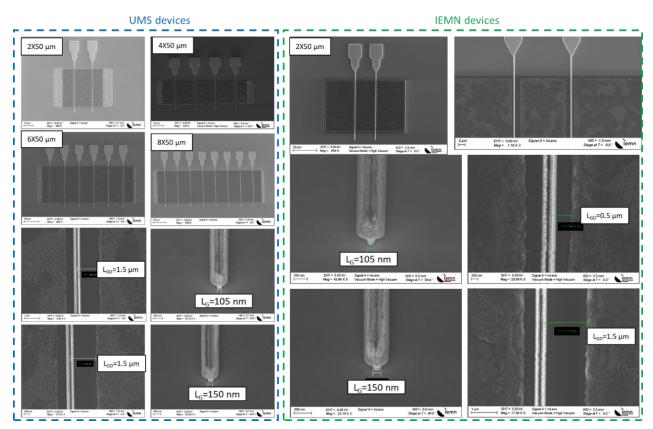

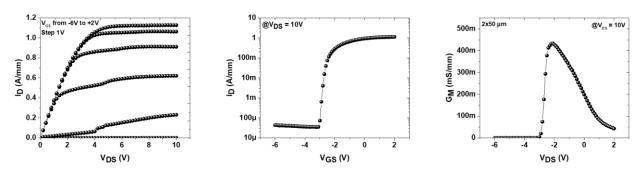

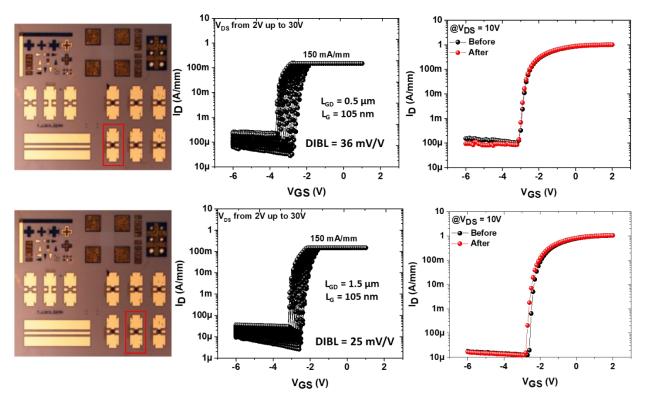

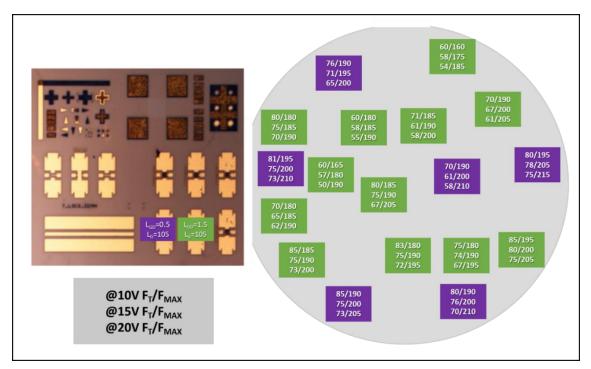

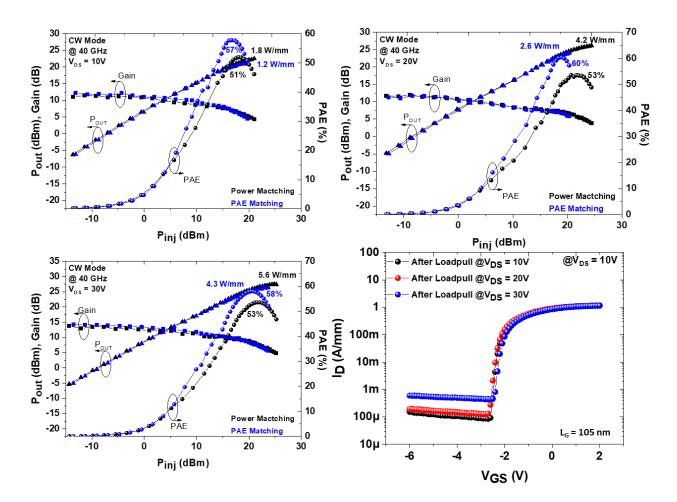

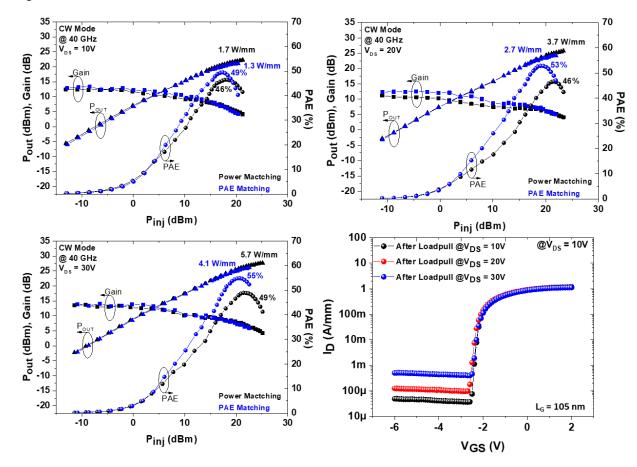

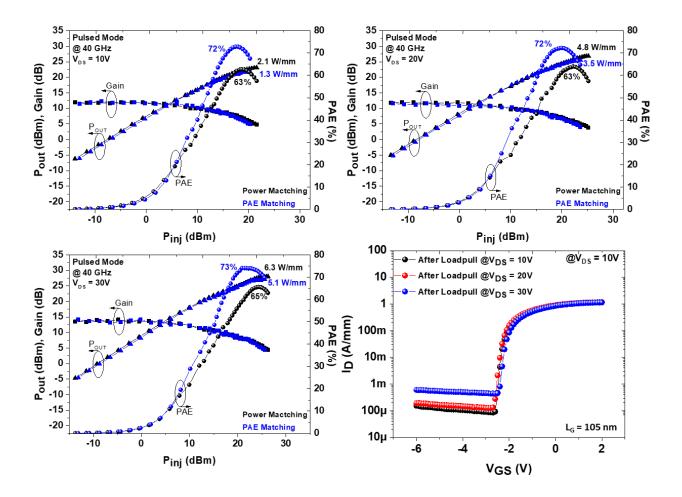

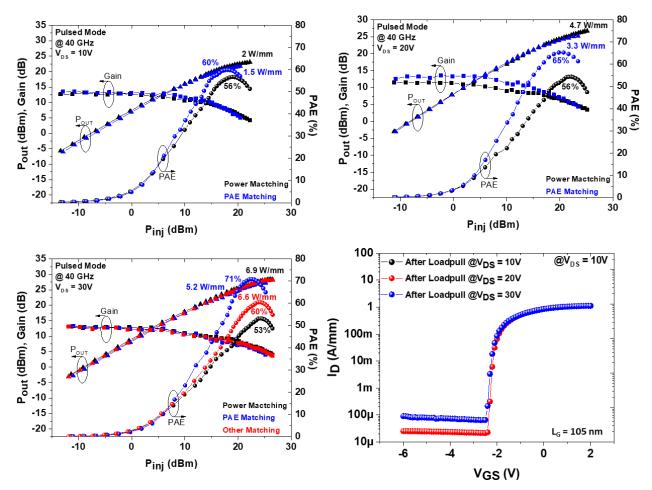

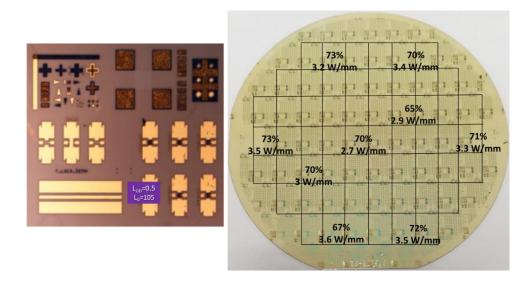

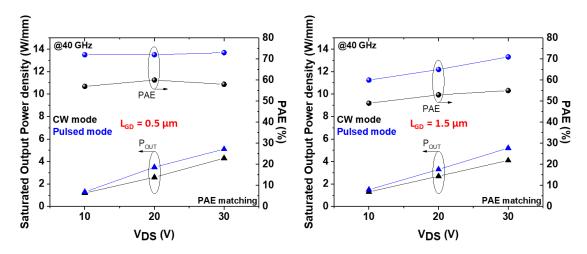

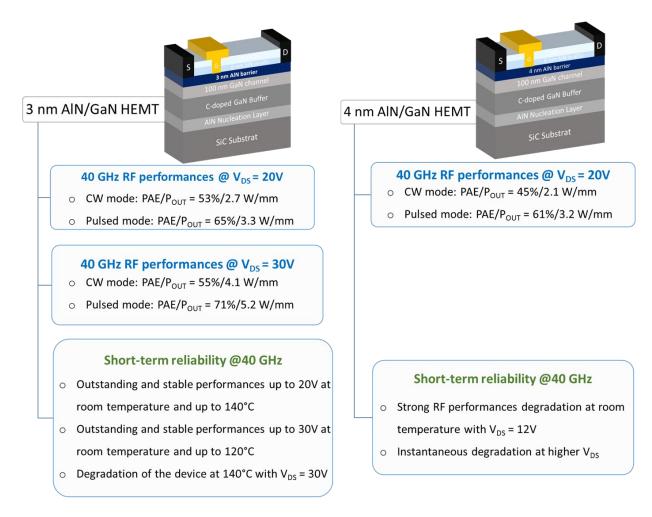

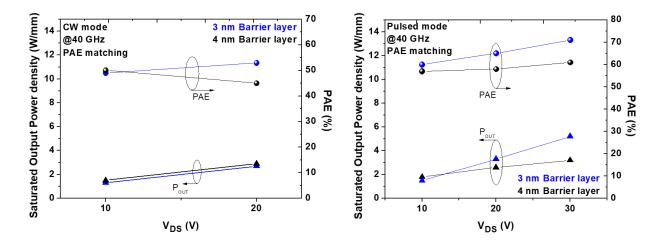

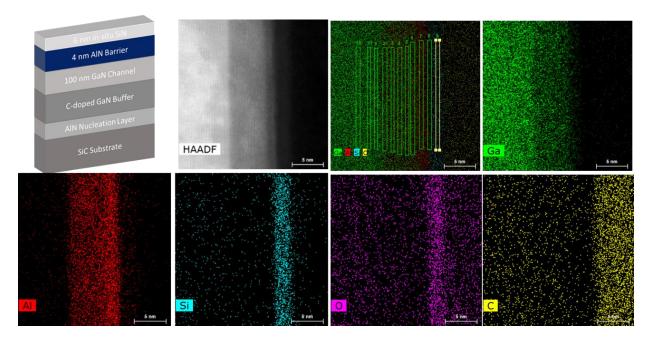

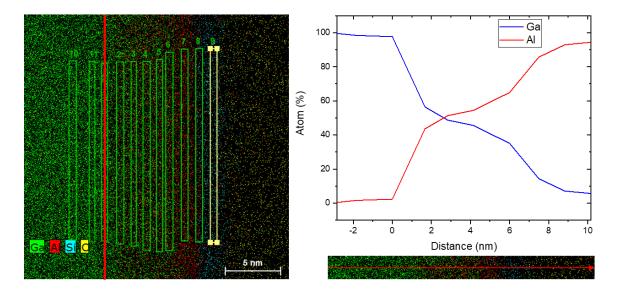

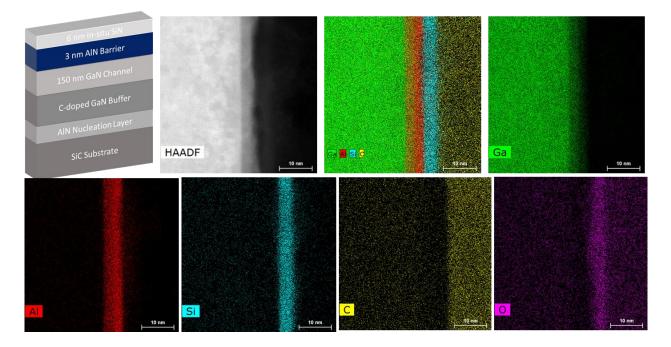

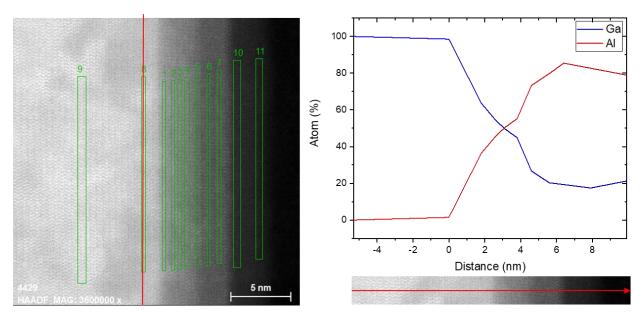

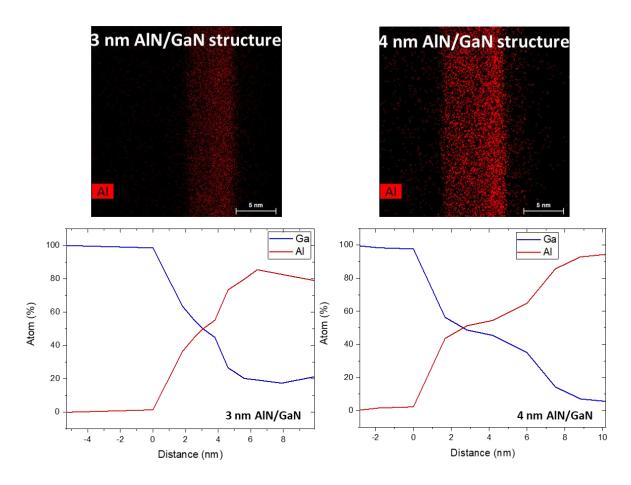

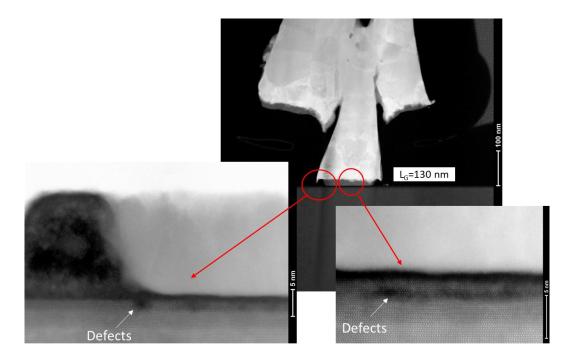

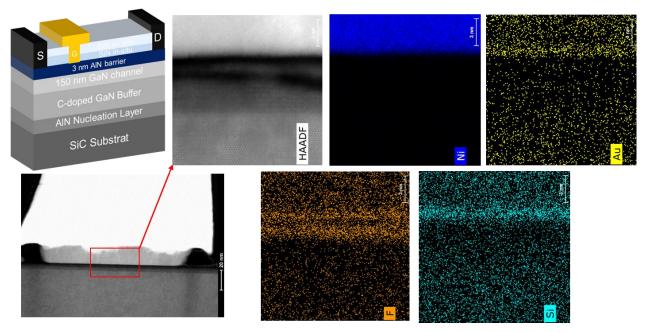

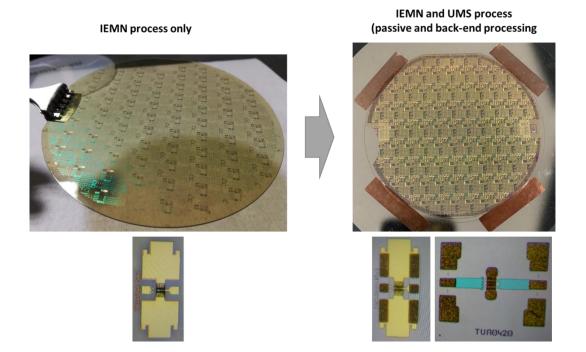

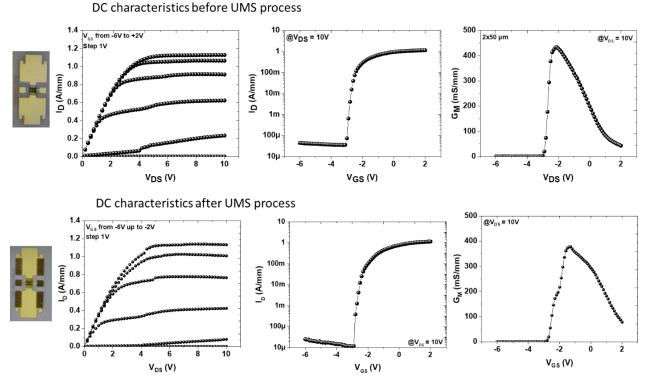

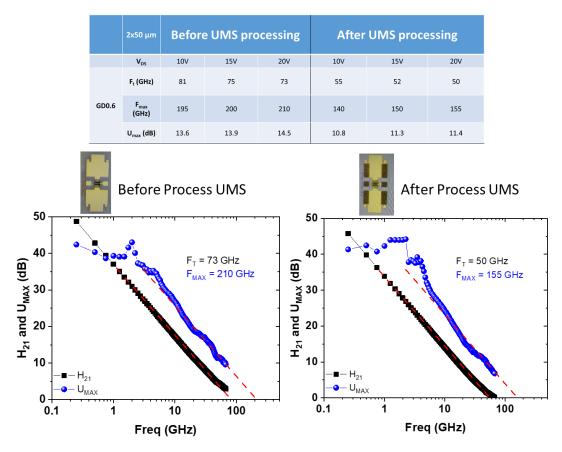

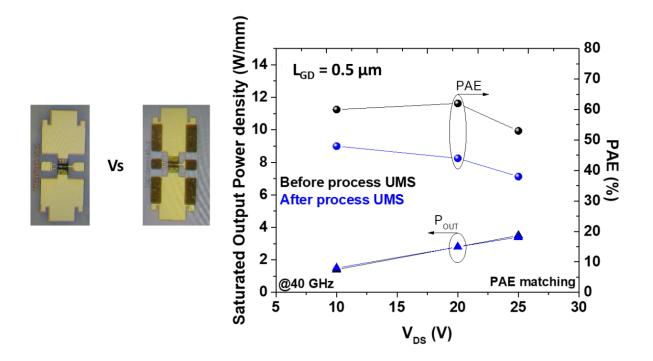

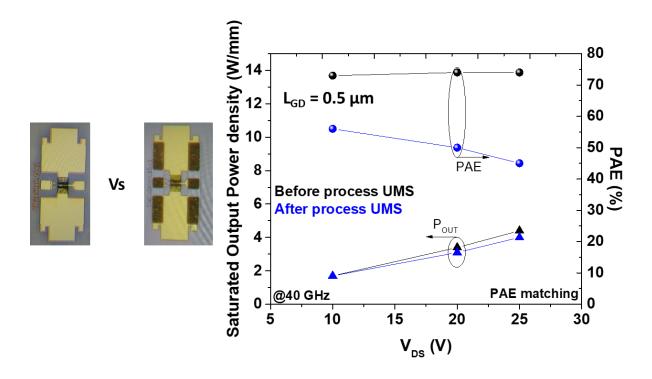

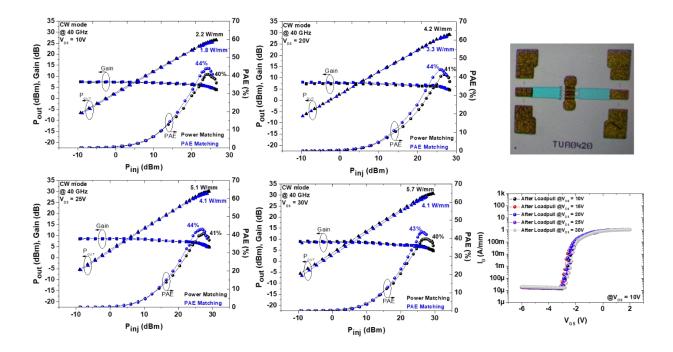

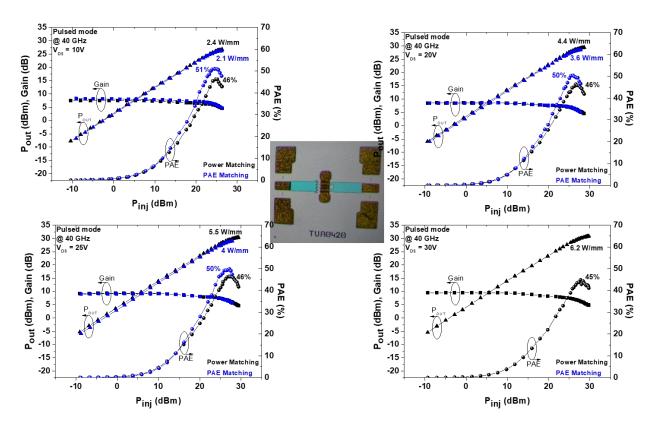

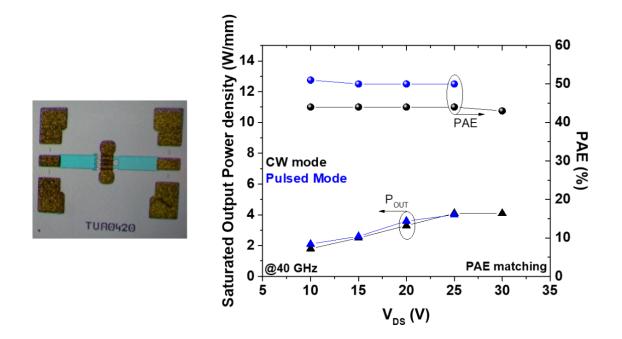

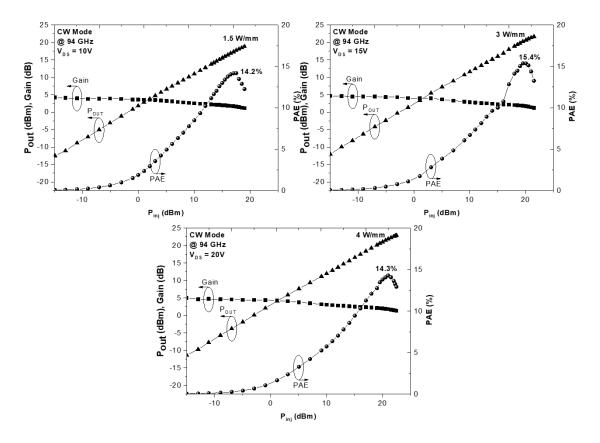

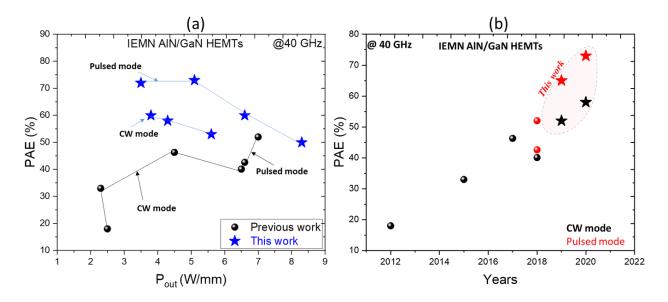

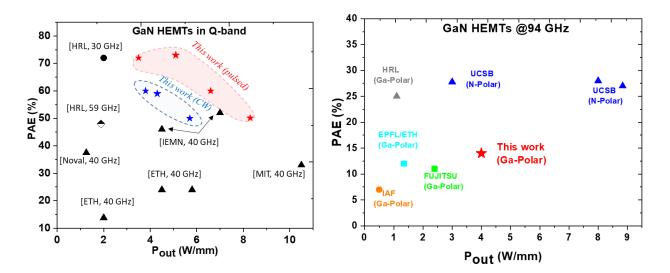

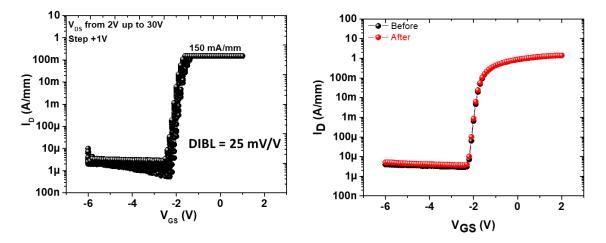

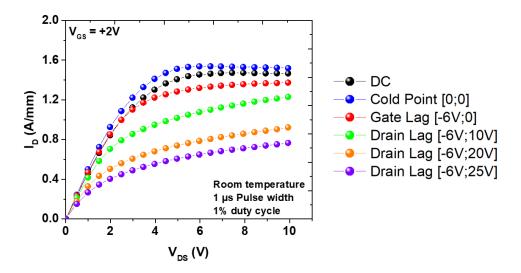

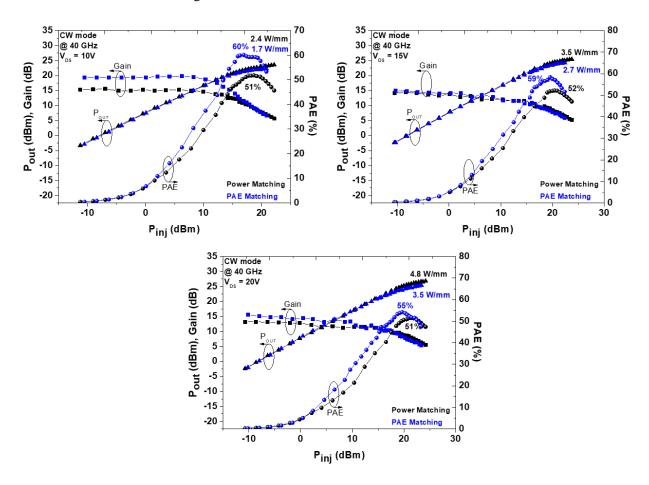

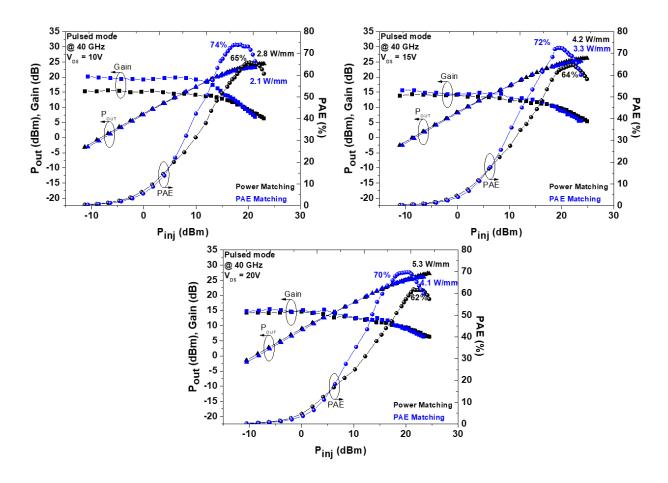

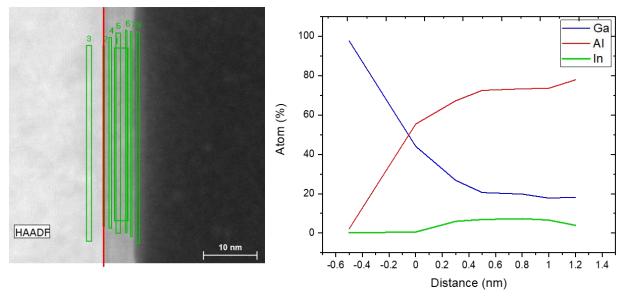

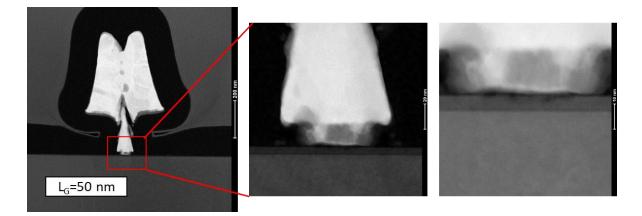

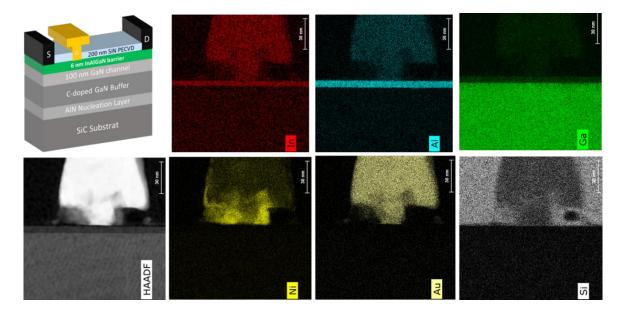

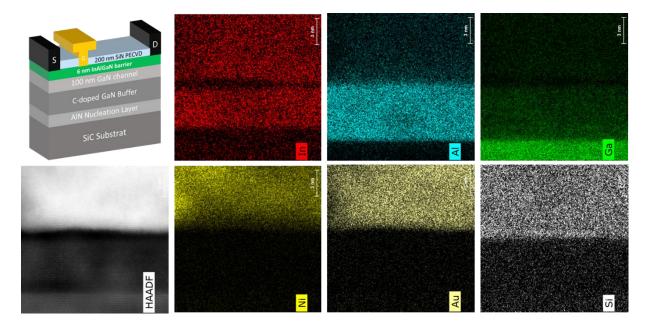

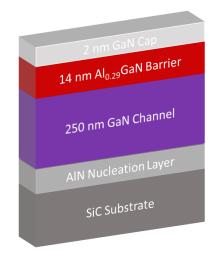

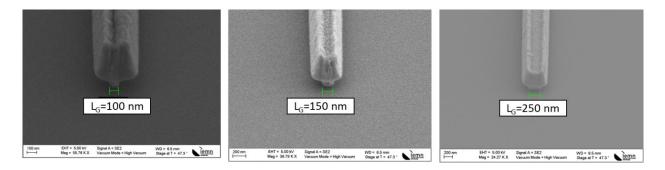

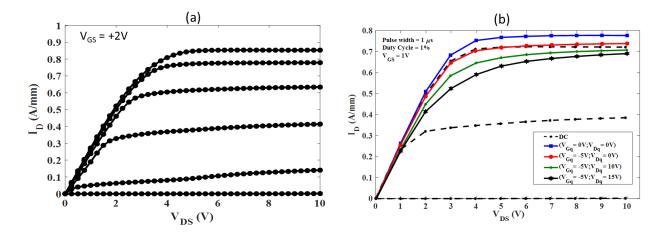

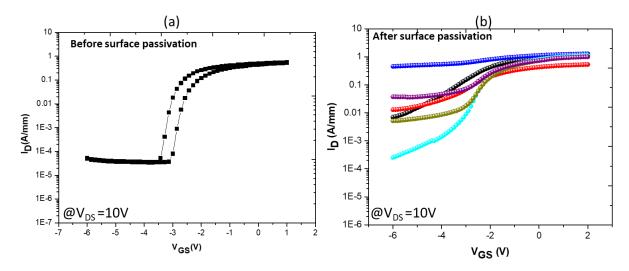

A successful control of the dispersion while simultaneously achieving reasonable large signal gain at high frequency is an important accomplishment of this work.