#### **THESE**

Présentée à l'Université de Lille Ecole Doctorale Sciences de l'ingénierie et des systèmes.

Institut d'Electronique, de Microélectronique et de nanotechnologies de Lille

Pour obtenir le grade de :

DOCTEUR DE L'UNIVERSITE

**Spécialité**: Electronique, Photonique

Par

#### HAFSA IKZIBANE

### Integrated Metrology Devices for The Study of Transport Properties in Silicon Nanostructures

Towards a direct zT metrology based on the transient Harman technique

### Dispositifs de Métrologie Intégrée pour l'Etude des Propriétés de Transport dans les Nanostructures en Silicium

#### Vers une métrologie directe de zT basée sur la technique transitoire de Harman

Soutenue le 29 novembre devant le jury composé de :

| Katir ZIOUCHE, <i>Professeur</i> , IUT Université de Lille, Lille       | Président du jury :<br>Examinateur |

|-------------------------------------------------------------------------|------------------------------------|

| Olivier BOURGEOIS, Directeur de Recherche CNRS, Institut Néel, Grenoble | Examinateur                        |

| Sylvie HEBERT, Directrice de Recherche CNRS, CRISMAT, Caen              | Examinatrice                       |

| Masahiro NOMURA, Professeur, Tokyo-University, Japan                    | Rapporteur                         |

| Nicolas STEIN, Maître de conférences, Institut Jean Lamour, Nancy       | Rapporteur                         |

| Nolwenn FLEURENCE, Ingénieur R&D, LNE, Trappes                          | Invitée                            |

| Jean-François ROBILLARD, Enseignant-Chercheur, Junia, Lille             | Directeur de thèse                 |

| Emmanuel DUBOIS, Directeur de recherche CNRS, Lille                     | Directeur de thèse                 |

#### **Mille Mercis**

This thesis was conducted at the *Institut d'Electronique*, *de Microélectronique et de Nanotechnologies* (*IEMN*) in Lille, and it was financially supported through a doctoral contract with the *Faculty of Science and Technology (FST)* at the University of Lille. I extend my heartfelt gratitude to numerous individuals who made significant contributions to this research.

I wish to express my deep appreciation to my thesis directors, **Jean-François ROBILLARD** and **Emmanuel DUBOIS**, for their invaluable support and mentorship. **Jean-François ROBILLARD** provided profound knowledge, priceless advice, and extensive experience, guiding this thesis through its challenges and elevating its quality. **Emmanuel DUBOIS** was consistently accessible, generously sharing expertise and knowledge to help us navigate and surmount obstacles. Their combined contributions have been indispensable to the successful completion of this research.

This thesis also received substantial support from **Jean-Michel DROULEZ**, who provided me with all the essential computer tools necessary for the completion of my work. Additionally, I extend my gratitude to **Florence ALBERTI** for greatly facilitating various travels during this thesis.

I express my gratitude to **Masahiro NOMURA** and **Nicolas STEIN** for agreeing to review this manuscript. I appreciate their dedication in setting aside time from their busy schedules to read and assess this dissertation. Additionally, I extend my thanks to the members of the PhD committee: **Olivier BOURGEOIS**, **Sylvie HEBERT**, **Katir ZIOUCHE**, and **Nolwenn FLEURENCE**, for their willingness to be part of this defense and for dedicating their time to review this research work.

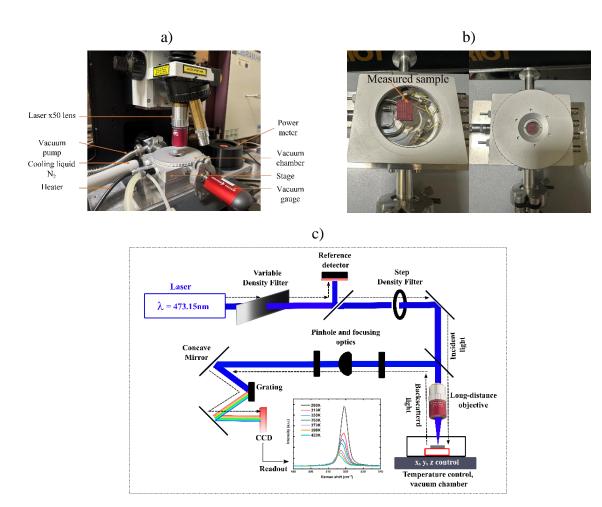

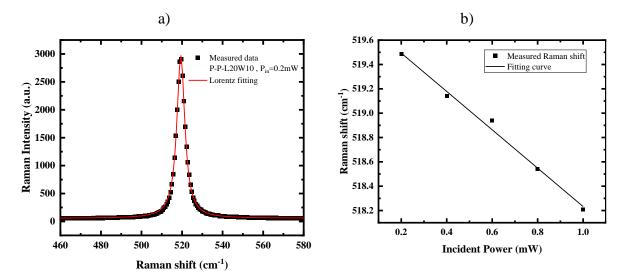

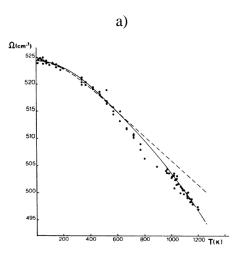

Working within the *Silicon Microelectronic Group* has been both an honor and a source of immense pleasure. I am truly fortunate to have had the opportunity to collaborate with such outstanding colleagues. I extend my special thanks to group members **Mélanie BROUILLARD**, **Jon CANOSA DIAZ**, **Daniel GHEYSENS**, and **Corentin MERCIER** for their invaluable contributions as colleagues. I am especially grateful to my colleague **Akash PATIL** for generously conducting Raman measurements on my sample, even while juggling the demands of his own Ph.D. pursuits. This act of support was truly appreciated. I would like to express my gratitude to **Etienne BLANDRE** for his assistance in calculating the absorption of Si using RCWA. His expertise was helpful in this aspect of the research.

A heartfelt and substantial thanks goes to my colleague and best friend, **Maya ALAWAR**. Being in a foreign country, **Maya ALAWAR** has been like a family member, standing by my side through both good and challenging times. Her support has been instrumental in helping me cope with the pain of missing my family and the challenges of being in a foreign country. I would also like to thank her for the wonderful moments we have shared and her solid companionship.

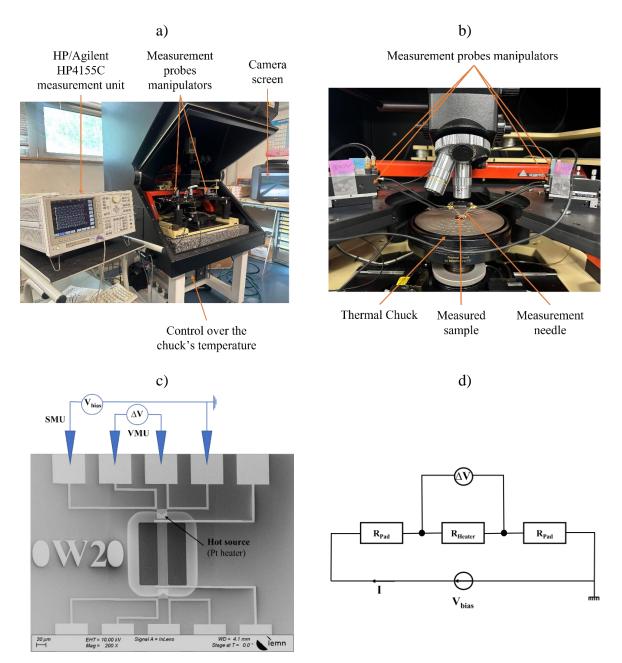

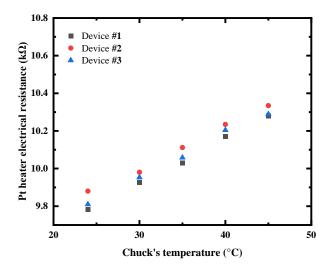

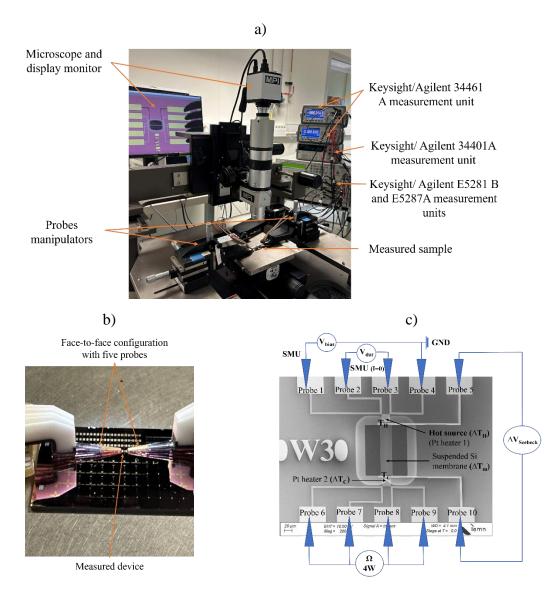

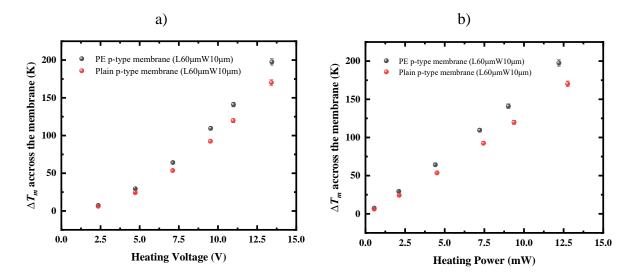

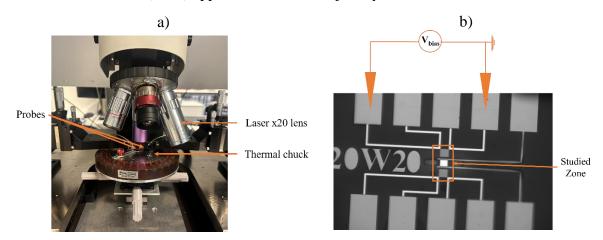

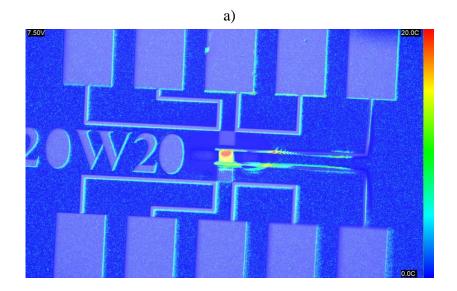

The research undertaken in this thesis, which is presented in the ensuing chapters, was primarily conducted at the micro and nano fabrication center within *IEMN*. I wish to convey my deep appreciation to the entire team at the center, which includes François VAURETTE, Pascal TILMANT, Saliha OUENDI, Dmitri YAREKHA, Laurent FUGÈRE, Marc DEWITTE, Christophe BOYAVAL, Jean-Marcel HOUPIN, Carlos MONCASI LUQUE, Timothey BERTRAND, Yves DEBLOCK, Christophe COINON, and Guillaume COCHEZ, etc. Their training in the use of various equipment proved to be essential in carrying out my research. Their support was invaluable, especially when I encountered challenges due to my lack of expertise or when access to specific equipment was limited. After the fabrication of the components, the diverse stages of component characterization were conducted within the characterization facility at *IEMN*. I extend my gratitude to **Etienne OKADA** for his guidance during the thermoelectric component characterization and his assistance in Louvain for TTR measurements. On this note, I would like to express my sincere thanks to **Alex PIP** for conducting these measurements and hosting us in Louvain. I also appreciate Sylvie LEPILLIET for her assistance during periods when Etienne was unavailable. I extend my thanks to Nora BENBHALLOULI and Andy LEDENT from the Human Resources team for their outstanding support during my time here. Their assistance has greatly contributed to a positive work environment.

I want to extend my gratitude to my siblings; **Hajar**, **Aida** and **Sami** for their belief in my abilities and unwavering support. Their confidence in me has been a constant source of motivation. To my **in-laws**, I am truly thankful for their encouragement. I would like to express my heartfelt gratitude to **Martha** and **Patrick PEYRE** for their constant kindness, encouragement, and assistance from the very first day I arrived in France. I want to express my deepest gratitude to my husband, **Lutfullah**. There are truly no words that can fully convey the depth of my appreciation. Thanks to your support and dedication, this academic journey became not just mine, but ours. Throughout this journey, you have been my constant source of encouragement, lifting my spirits and providing boundless comfort during both the high points and the challenging times. While I could enumerate countless reasons for my gratitude, no words can truly capture the magnitude of the goodness and support you have showered upon me. I address my special acknowledgments to my parents in my mother tongue:

أود أن أعبر عن امتناني العميق لوالديّ، الأب الحبيب الحسين الذي عمل بجد من أجلنا وساهم ماليًا في إكمال در استي ،ولوالدتي، الأم الحنونة فاضمة، التي قدمت تضحيات كبيرة في حياتها لنحقق أعلى المراكز والإنجاز ات .هذا الإنجاز ليس فقط إنجازي بل إنجاز هما أيضًا

إلى أمي، فاضمة، أريد أن أقول شكرًا لك على كونك أمًا، شقيقة، وصديقة لي لقد كنتِ أكثر من مجرد دعم قوي، بل كنتِ شريكة في هذا العمل بكل المعاني

| GENERAL IN | ITRODUCTION                                                                | 11 |

|------------|----------------------------------------------------------------------------|----|

| CHAPTER 1  | THERMOELECTRIC PROPERTIES OF SILICON: GENERALITIES AND STATE OF THE ART    | 14 |

| ABSTRACT   |                                                                            | 14 |

| 1.1 THE    | RMOELECTRIC ENERGY HARVESTING FOR SUSTAINABLE WIRELESS SENSOR NETWORKS     | 14 |

| 1.2 THE    | RMOELECTRIC EFFECT                                                         | 15 |

| 1.2.1      | Seebeck effect                                                             | 16 |

| 1.2.2      | Peltier effect                                                             | 16 |

| 1.2.3      | Thomson effect                                                             | 16 |

| 1.3 THE    | ORY OF THERMOELECTRIC POWER GENERATING DEVICES                             | 17 |

| 1.4 THE    | RMOELECTRIC TRANSPORT PROPERTIES                                           | 18 |

| 1.4.1      | Thermal conductivity                                                       |    |

| 1.4.2      | Electrical conductivity                                                    |    |

| 1.4.3      | Seebeck coefficient                                                        |    |

|            | RMOELECTRICITY-MATERIAL CHOICE                                             |    |

| 1.6 Op     | FIMIZATION METHODS OF ZT FIGURE OF MERIT OF SILICON                        |    |

| 1.6.1      | Nano-structuration                                                         |    |

| 1.6.2      | Oxidization and roughness                                                  |    |

| 1.6.3      | Phonon engineering                                                         |    |

|            | EGRATION OF SI FOR THERMOELECTRIC APPLICATIONS                             |    |

| Conclusion | DN                                                                         | 33 |

|            | THEORETICAL STUDIES AND MODELING OF ZT FIGURE OF MERIT DIRECT MEASUREMENTS |    |

| ABSTRACT   |                                                                            | 35 |

|            | DIRECT MEASUREMENT                                                         |    |

|            | SIGN OF DIRECT ZT MEASUREMENT DEVICE                                       |    |

| 2.2.1      | Direct zT measurement device for Bulk materials                            |    |

| 2.2.2      | Direct zT measurement device for nanostructured materials                  |    |

| 2.3 THE    | ORETICAL STUDY OF ZT DIRECT MEASUREMENT ADAPTED TO MEMBRANES               |    |

| 2.3.1      | zT using Harman technique                                                  |    |

| 2.3.2      | zT considering Joule effect as heat source                                 |    |

| 2.3.3      | zT considering all losses terms                                            |    |

| 2.4 Mc     | DELING STUDY OF ZT DIRECT MEASUREMENT ADAPTED TO MEMBRANES                 |    |

| 2.4.1      | Finite Element Method definition                                           | 53 |

| 2.4.2      | Heat transport equations definition                                        |    |

| 2.4.3      | Physical modeling of zT direct measurement on a thin film                  |    |

| Conclusion | N                                                                          | 63 |

|            | FABRICATION OF THE INTEGRATED METROLOGY DEVICE DEDICATED TO TRANSIENT HA   |    |

| ABSTRACT   |                                                                            | 65 |

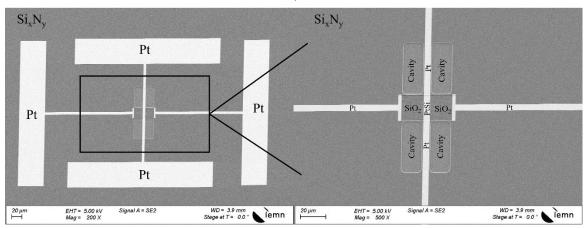

|            | SIGN                                                                       |    |

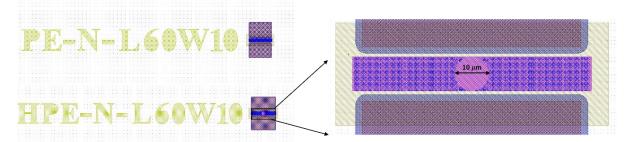

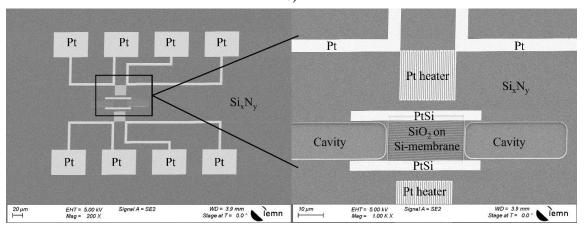

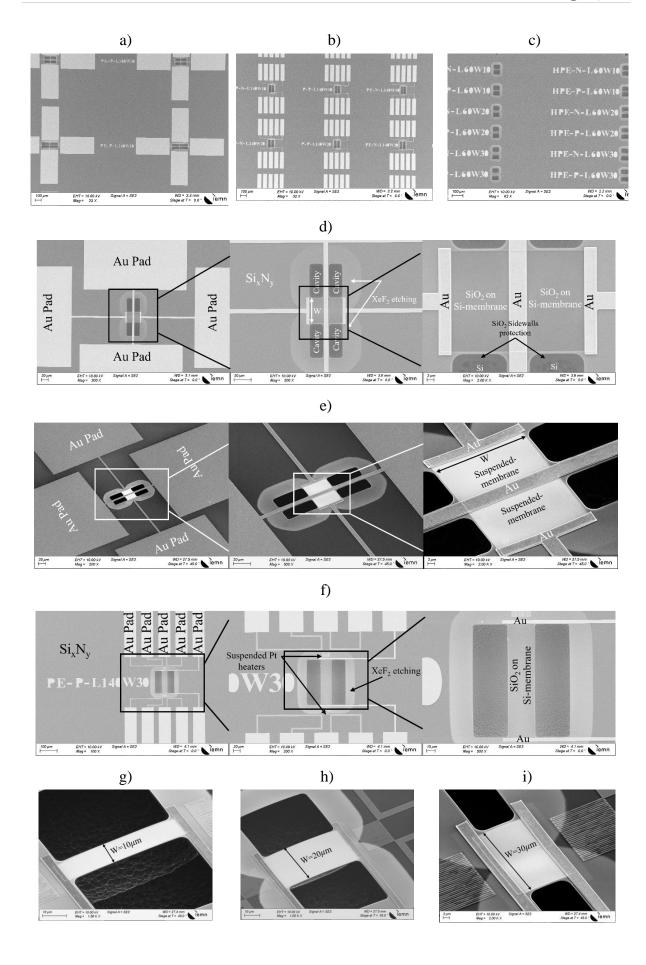

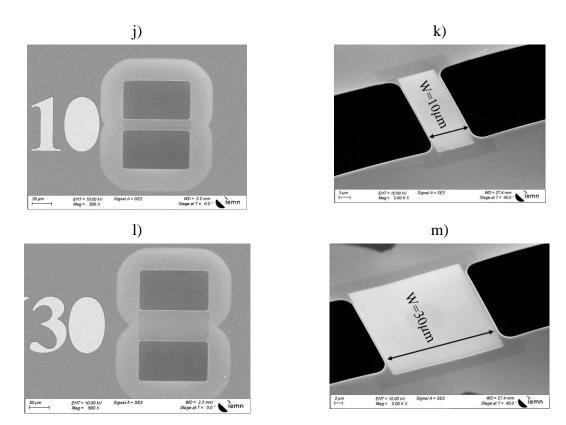

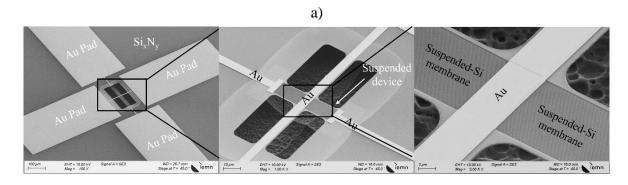

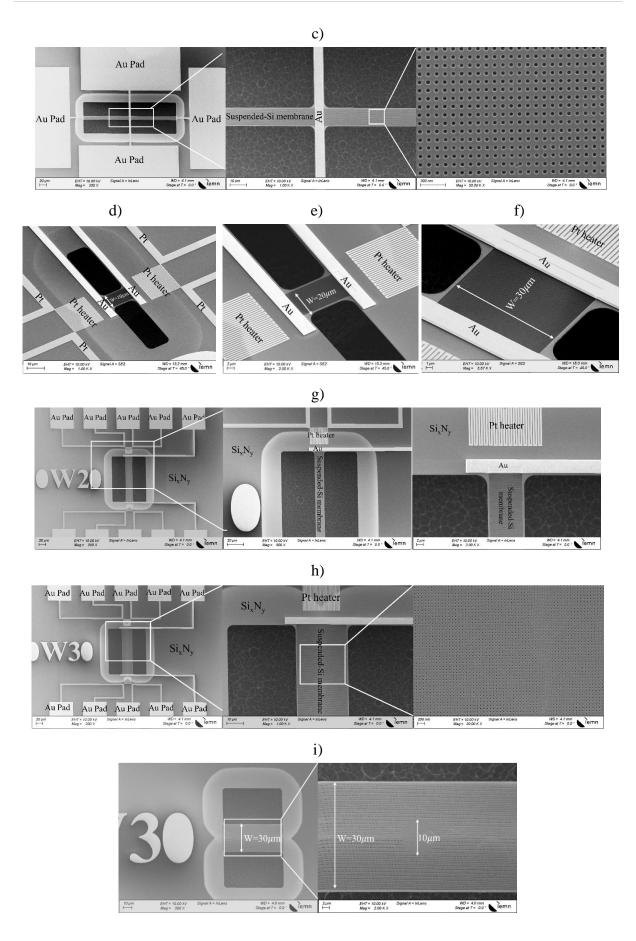

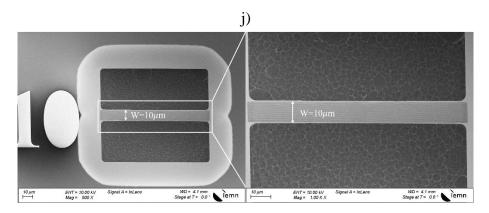

| 3.1.1      | Transient Harman demonstrators                                             |    |

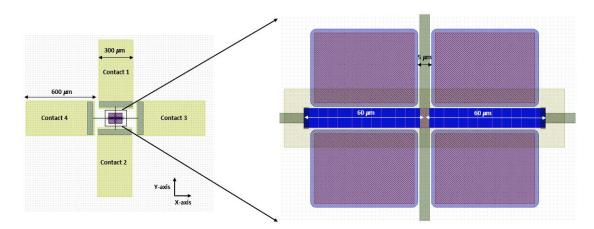

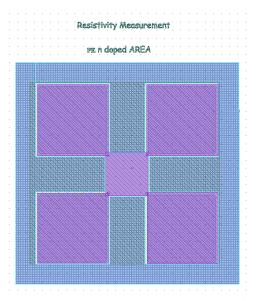

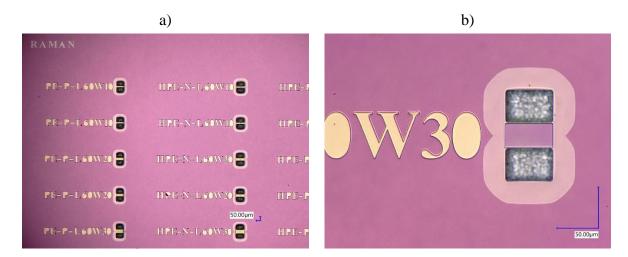

| 3.1.2      | Doping level measurement platforms                                         |    |

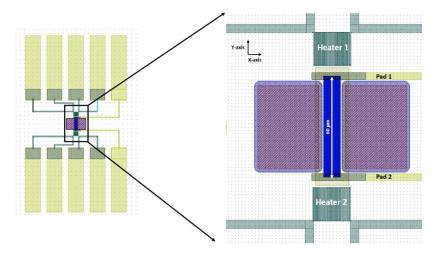

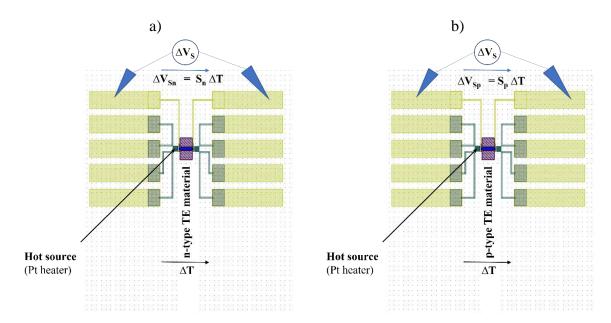

| 3.1.3      | Seebeck coefficient measurement devices                                    |    |

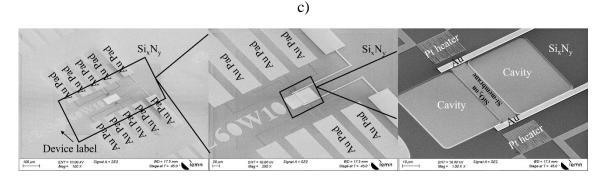

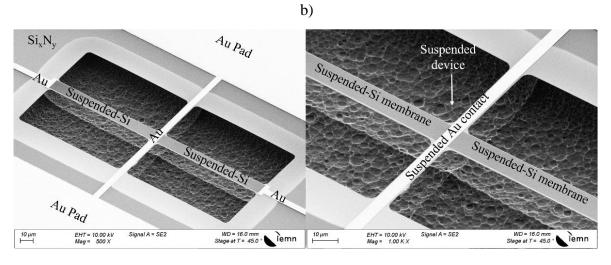

| 3.1.4      | Thermal conductivity measurement devices                                   |    |

| _          | RICATION                                                                   |    |

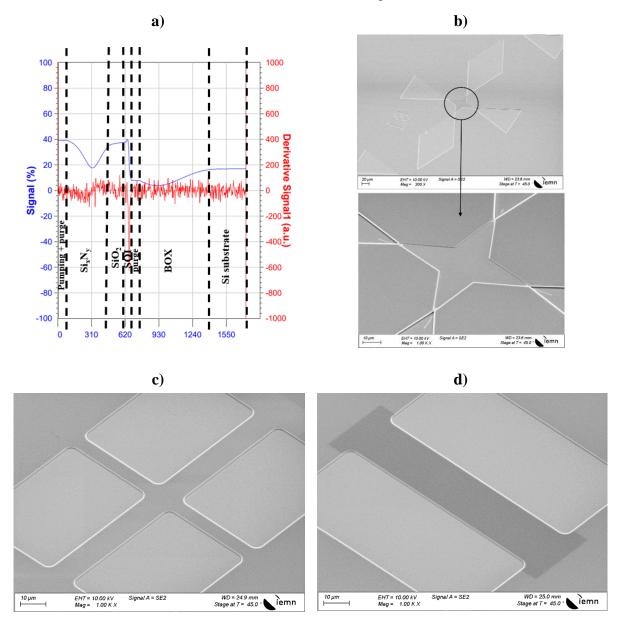

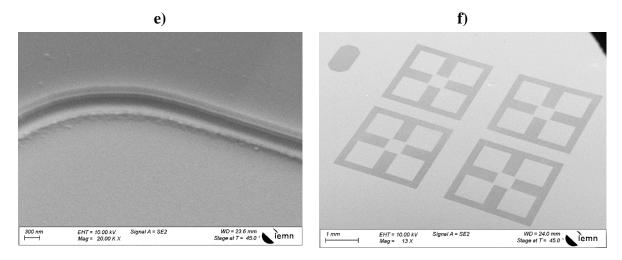

| 3.2.1      | Preliminary step: wafer cleaning and etching of alignment markers          |    |

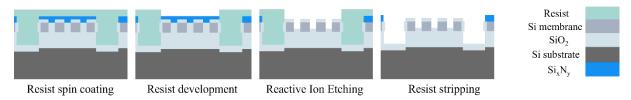

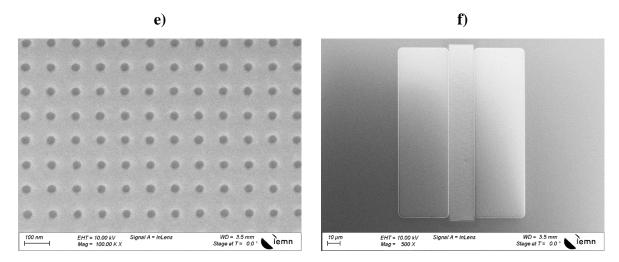

| 3.2.2      | Step 1: Phononic engineering patterning                                    |    |

| 3.2.3      | Step 2: SOI oxidation & Ion implantation                                   |    |

| 3.2.4      | Step 3: SixNy deposition                                                   |    |

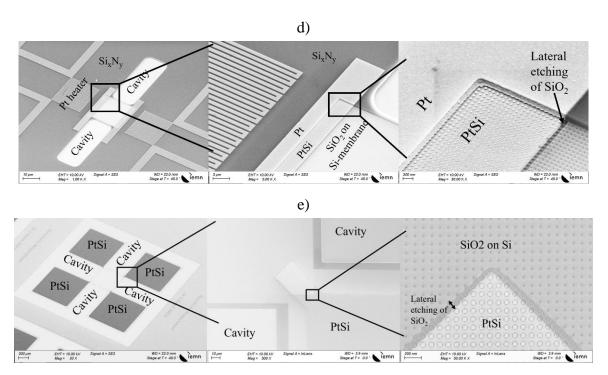

| 3.2.5      | Step 4: Cavities Opening                                                   |    |

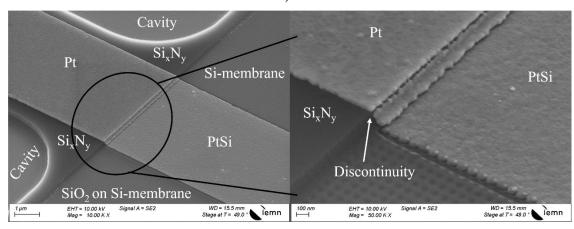

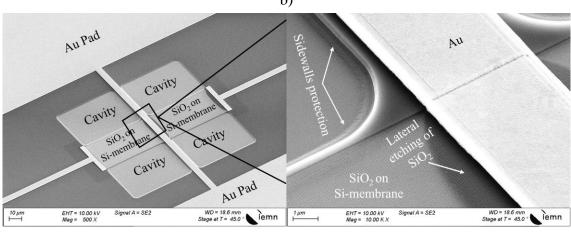

| 3.2.6      | Step 5: Sidewalls protection                                               |    |

| 3.2.0      | Step 6: SixNu removal                                                      | 9/ |

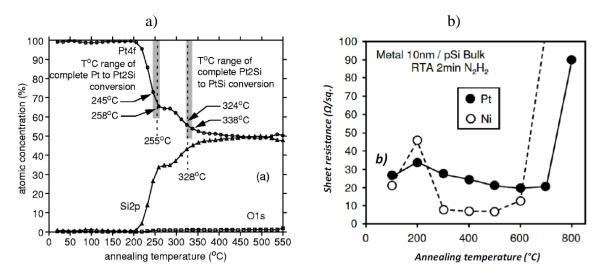

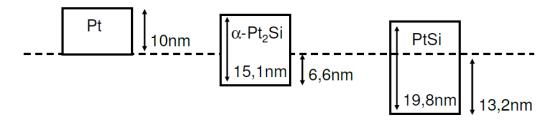

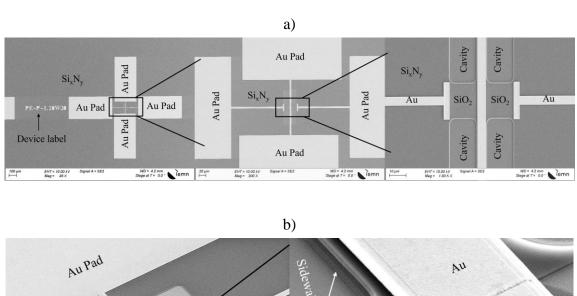

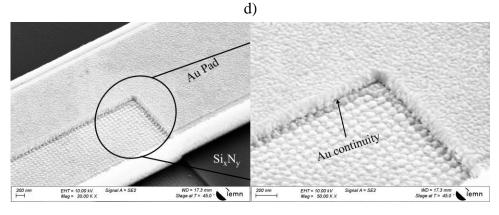

| 3.2.8        | Step 7: Metallization                                       | 96  |

|--------------|-------------------------------------------------------------|-----|

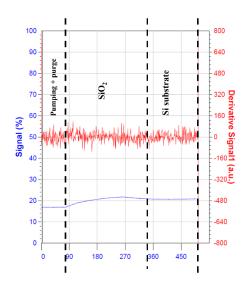

| 3.2.9        | Step8: XeF2 & Vapor HF etching                              | 104 |

| Conclusio    | N                                                           | 111 |

| CHAPTER 4 C  | HARACTERIZATION OF THE FABRICATED DEVICES AND RESULTS       | 112 |

| ABSTRACT     |                                                             | 112 |

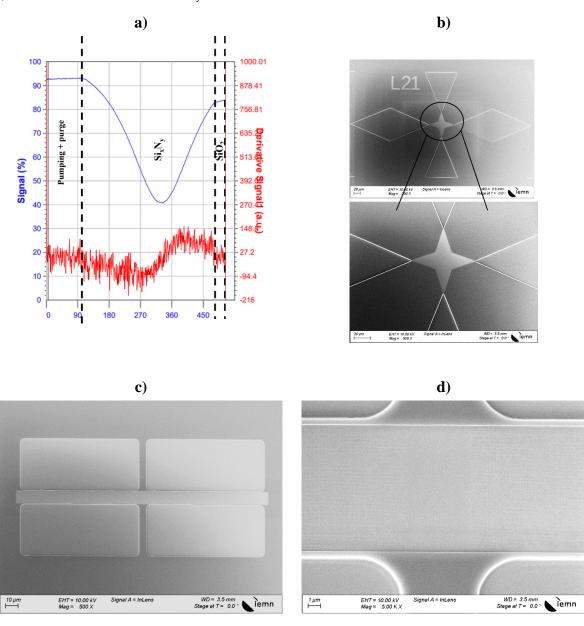

| 4.1 SEEB     | ECK COEFFICIENT MEASUREMENTS                                | 112 |

| 4.1.1        | Measurement protocol                                        | 112 |

| 4.1.2        | Seebeck coefficient measurements results                    | 120 |

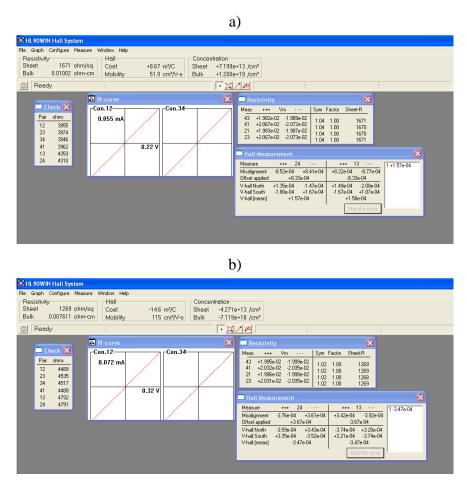

| 4.2 DOP      | NG LEVEL / ELECTRICAL CONDUCTIVITY MEASUREMENTS             | 133 |

| 4.2.1        | Measurement protocol                                        | 133 |

| 4.2.2        | Doping level / Electrical conductivity measurements results | 136 |

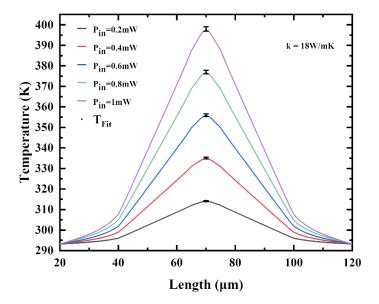

| 4.3 THER     | MAL CONDUCTIVITY MEASUREMENTS                               | 138 |

| 4.3.1        | Measurement protocol                                        | 138 |

| 4.3.2        | Thermal conductivity measurements results                   | 148 |

| 4.4 Figu     | re of merit (zT) determination                              | 152 |

| 4.4.1        | Analytical figure of merit (zT)                             | 152 |

| 4.4.2        | Direct measured figure of merit (zT)                        | 155 |

| Conclusion   | N                                                           | 157 |

| GENERAL CO   | NCLUSION                                                    | 158 |

| PERSPECTIVE  | S                                                           | 161 |

| APPENDIX 1   |                                                             | 163 |

| APPENDIX 2   |                                                             | 167 |

| SCIENTIFIC P | RODUCTION                                                   | 168 |

| REFERENCES   |                                                             | 169 |

### Integrated Metrology Devices for The Study of Transport Properties in Silicon Nanostructures. Towards a direct *zT* metrology based on the transient Harman technique.

In thermoelectricity, silicon nanostructures represent an interesting alternative to conventional thermoelectric materials due to Si abundance, non-toxic nature, and its compatibility with CMOS technology. Researchers have investigated methods to enhance the silicon figure of merit zT by increasing the  $\sigma/\kappa$  ratio; decreasing the thermal conductivity  $\kappa$  by (i) using nanometric structure such as thin membranes or nanowires, (ii) roughening, (iii) oxidization of the surface achieved relatively low value of  $\kappa$ . Yet, few experimental measurements of zT in crystalline silicon nano-objects were presented with important data dispersion. Usually, the thermoelectric figure of merit is obtained through independent measurement of materials transport properties ( $\kappa$ ,  $\sigma$  and S). The uncertainty of zT can easily reach 50% considering that each parameter has an uncertainty of 5% to 20%. Harman's technique is a simple and rapid method to measure zT directly in bulk materials. This thesis proposes an adaptation of the transient Harman technique for suspended crystalline nano-membranes. A correction factor is introduced to account for radiation, contact resistances, and Joule heating effects. Furthermore, a device implementation is presented, enabling direct access to zT through purely electrical measurements, eliminating the need for separate measurements of transport parameters. Additionally, elementary devices are examined to determine the transport properties of silicon, including thermal conductivity, Seebeck coefficient, and electrical conductivity. The measured Seebeck coefficient, showing similarity to Bulk Si near room temperature, raises a fundamental question concerning the relative contributions of electron diffusion and phonon transport.

# Dispositifs de Métrologie Intégrée pour l'Etude des Propriétés de Transport dans les Nanostructures en Silicium. Vers une métrologie directe du *zT* basée sur la technique transitoire de Harman.

En thermoélectricité, les nanostructures de silicium représentent une alternative intéressante aux matériaux thermoélectriques conventionnels en raison de leur abondance, de leur caractère non toxique et de leur compatibilité avec la technologie CMOS. Les chercheurs ont étudié différentes méthodes visant à améliorer le facteur de mérite zT du silicium en augmentant le rapport  $\sigma/\kappa$ ; en diminuant la conductivité thermique  $\kappa$  en utilisant (i) des structures nanométriques telles que des membranes minces ou des nano-fils, (ii) en utilisant la rugosité de surface, (iii) en procédant à une oxydation de la surface, ce qui permet d'obtenir une faible valeur de κ. Cependant, peu de mesures expérimentales de zT sur des nano-objets en silicium cristallin ont été présentées, et ces données présentent une dispersion importante. Habituellement, le facteur de mérite est obtenu par une mesure indépendante des propriétés de transport des matériaux ( $\kappa$ ,  $\sigma$  et S). L'incertitude de zT peut facilement atteindre 50 %, étant donné que chaque paramètre présente une incertitude de 5 % à 20 %. La technique de Harman est une méthode simple et rapide pour mesurer directement zT dans les matériaux bulk. Cette thèse propose une adaptation de la technique de Harman transitoire pour les nano-membranes cristallines suspendues. Un facteur de correction est introduit pour prendre en compte les effets du rayonnement, des résistances de contact et du chauffage par effet Joule. De plus, une mise en œuvre du dispositif est présentée, permettant d'accéder directement à zT par des mesures purement électriques, éliminant ainsi le besoin de mesures séparées des paramètres de transport. De plus, des dispositifs élémentaires sont examinés pour déterminer les propriétés thermiques du silicium, notamment la conductivité thermique, le coefficient de Seebeck et la conductivité électrique. Le coefficient Seebeck mesuré, montrant une similitude avec le Si bulk près de la température ambiante, soulève une question fondamentale concernant les contributions relatives de la diffusion des électrons et du transport des phonons.

#### **General Introduction**

Thermoelectricity, the conversion of heat fluxes into electrical energy, holds immense potential for sustainable energy harvesting and waste heat recovery. In this context, silicon nanostructures emerge as a captivating avenue due to their abundant availability, non-toxic nature, and compatibility with CMOS technology. Unlike conventional thermoelectric materials, silicon offers unique advantages. This thesis investigates the utilization of silicon nanostructures in thermoelectric applications, with a focus on enhancing silicon's thermoelectric characteristics and developing a precise efficiency measurement technique.

In the field of thermoelectricity, silicon nanostructures are being explored as a promising alternative to traditional thermoelectric materials. Silicon possesses a relatively high Seebeck coefficient (S), around  $400\mu\text{V/K}$ , but its thermal conductivity ( $\kappa$ ) is relatively high, approximately 149W/mK near room temperature, which results in a low figure of merit (zT). Efforts have been made to enhance silicon's figure of merit by improving the ratio of electrical conductivity ( $\sigma$ ) to thermal conductivity ( $\kappa$ ). This has involved investigating techniques such as using thin membranes or nanowires, controlled oxidation processes, and surface roughening to reduce  $\kappa$  while maximizing  $\sigma$ . The introduction of nanostructures into silicon has generated interest and research in this area. Researchers have developed Si-based micro thermoelectric generators ( $\mu$ TEGs) that have shown promise. For instance, Thierno-Bah *et al.*[1] achieved significant improvements by reducing the thickness of single-crystalline silicon to 70 nanometers and patterning the membrane with a network of "pores" approximately 40 nanometers in diameter and spaced at intervals of 100 nanometers ("pitch"). Under a temperature difference of 5.5 Kelvin, they achieved a notable power output of  $4.5\mu\text{W/cm}^2$ . These findings highlight the potential of silicon nanostructures to enhance thermoelectric technology.

Despite these promising developments, challenges persist. One challenge is the variability in experimental zT measurements for crystalline silicon nano-objects. Calculating zT involves measuring  $\kappa$ ,  $\sigma$ , and the Seebeck coefficient (S) independently, each with its uncertainties ranging from 5% to 20%. Thus, the resulting zT uncertainty can exceed 50%. Addressing this issue, the Harman technique offers a direct means to measure zT in bulk materials. This thesis introduces an adapted version of this technique for suspended crystalline nano-membranes, considering radiative effects, contact resistances, and Joule heating. Additionally, a device integration approach is presented, allowing direct zT determination through electrical measurements, simplifying the process. Complementary to these advancements, the study investigates fundamental devices that facilitate a comprehensive understanding of silicon's properties, this entails measuring and analyzing thermal conductivity, Seebeck coefficient, and electrical conductivity. The thesis is organized into four chapters:

#### Chapter1: Thermoelectric Properties of Silicon: Generalities and State of the Art.

In this first chapter, we explore the fundamentals of thermoelectricity and the relevance of silicon as a thermoelectric material. We report essential thermoelectric properties, including the Seebeck effect, Peltier effect, and Thomson effect, which are fundamental to the operation of thermoelectric devices. We also delve into the theory behind thermoelectric power-generating devices and discuss key transport properties such as thermal conductivity, electrical conductivity, and the Seebeck coefficient, all of which significantly impact the efficiency of thermoelectric materials. Furthermore, we examine the importance of material selection in thermoelectric applications, with a particular focus on silicon. Additionally, we explore various methods used to optimize silicon's thermoelectric performance, including nano-structuration, oxidization, surface roughness, and phonon engineering. Finally, we discuss the practical integration of silicon into thermoelectric

applications, particularly in micro thermoelectric generators configured for applications around room temperature.

### Chapter 2: Theoretical Studies and Modeling of zT Figure of Merit Direct Measurement Adapted to Membranes.

Expanding upon the foundational insights presented in the previous chapter, the second chapter focuses on the challenges surrounding the determination of zT due to the data dispersion observed in experimental measurements of crystalline silicon nano-objects. This dispersion can be attributed to the uncertainty inherent in the separate measurement of zT's components. To address this challenge, we introduce a novel methodology inspired by the transient Harman method for directly measuring zT in nanostructured planar membranes. We begin by explaining the conventional "Harman technique"[2] and then present our adapted method designed for membrane-based measurements. This chapter also provides a comprehensive overview of the design of the measurement device specifically adapted for implementing the transient Harman technique on membranes. Furthermore, we derive a formula to calculate the intrinsic figure of merit ( $zT_i$ ) of planar suspended membranes. This formula establishes a relationship between the zT value acquired using the conventional technique ( $zT_H$ ), the membrane's geometric characteristics, and the correction terms applied to account for measurement losses.

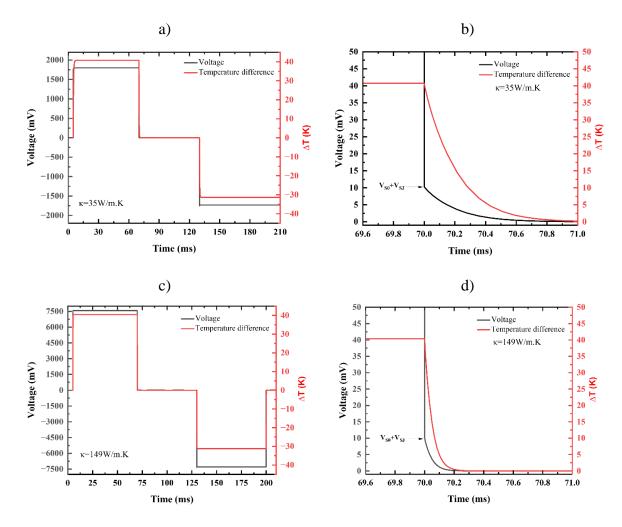

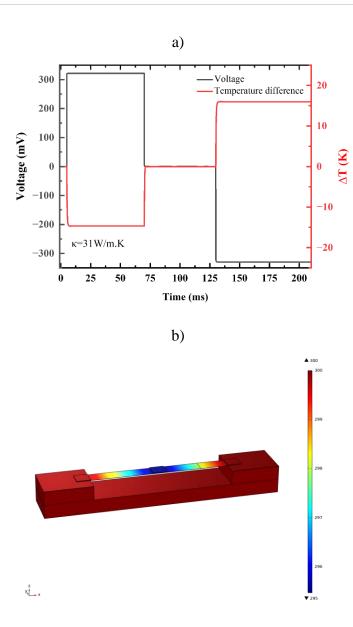

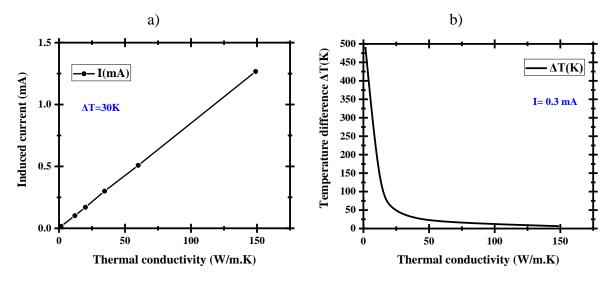

In addition, computational modeling is conducted using the Finite Element Method (FEM) to evaluate our proposed technique across various scenarios of silicon thermal conductivity, encompassing bulk thermal conductivity and reduced thermal conductivity. These simulations facilitated a comparative analysis between zT values determined using the classical Harman method and our adapted membrane-based technique, validating the efficacy of our proposed approach.

### Chapter 3: Fabrication of the Integrated Metrology Device Dedicated to Transient Harman Measurement of Silicon Nano-meshes.

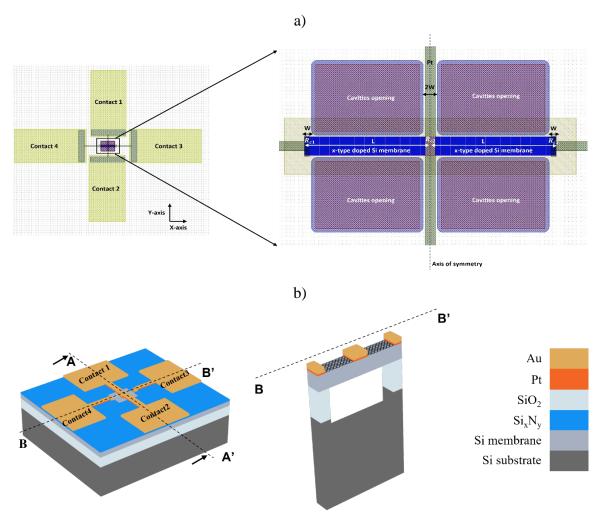

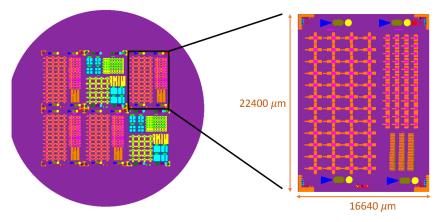

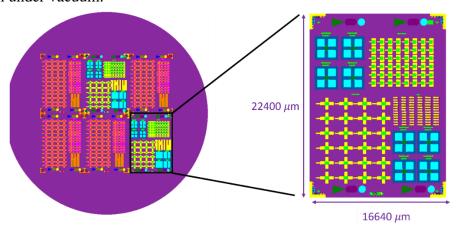

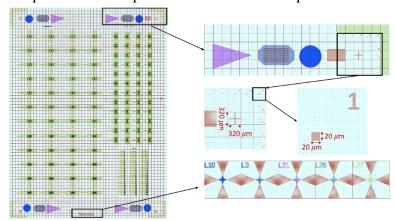

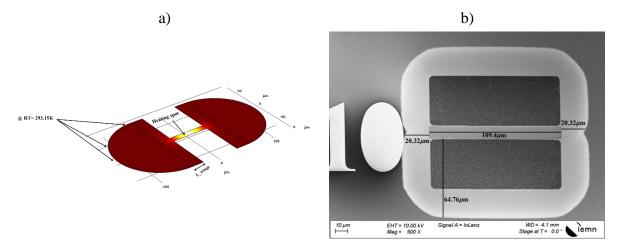

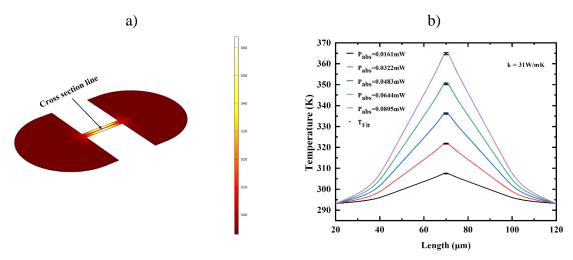

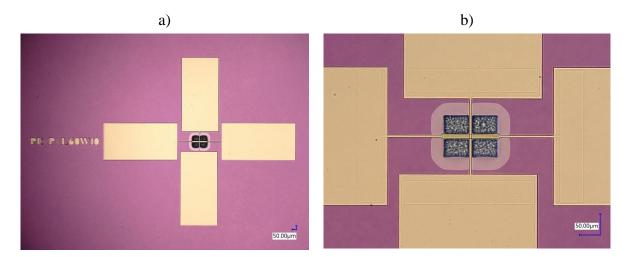

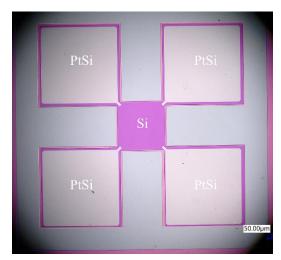

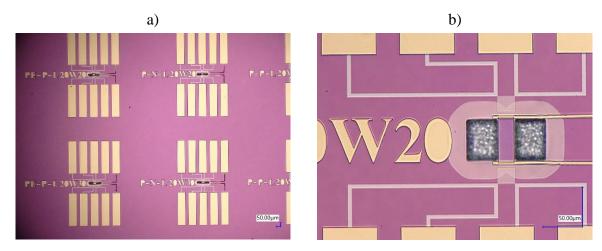

The third chapter takes a turn toward practical implementation, focusing on the fabrication process of an integrated metrology device dedicated to transient Harman measurements of silicon nano-meshes. The primary objective is to fabricate this measurement device, accompanied by elementary devices instrumental in determining transport properties such as thermal conductivity, Seebeck coefficient, and electrical conductivity. These measurements encompass various membrane geometries and types, including both plain and patterned membranes. The chapter meticulously outlines the design phase, which encompasses the development of transient Harman demonstrators, doping level measurement platforms, Seebeck coefficient measurement devices, and thermal conductivity measurement devices.

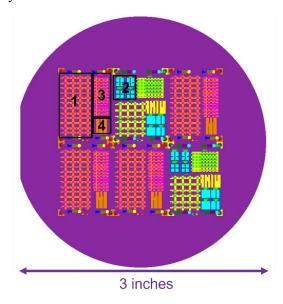

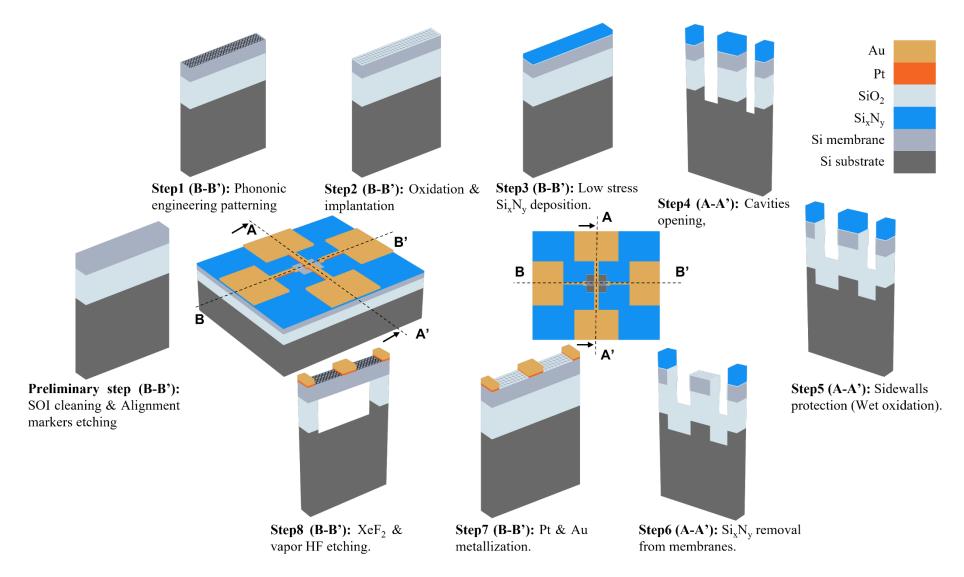

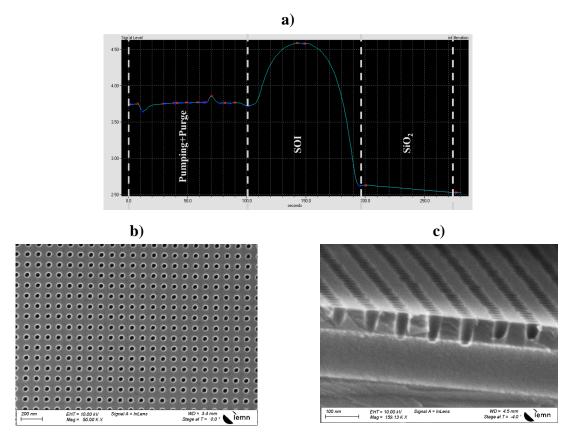

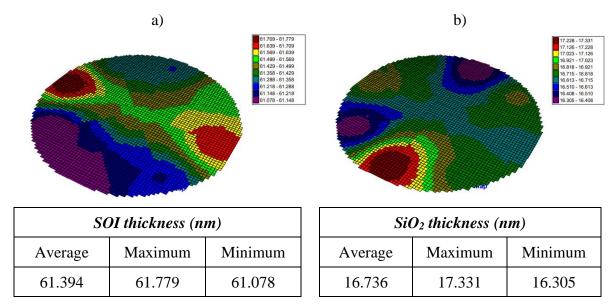

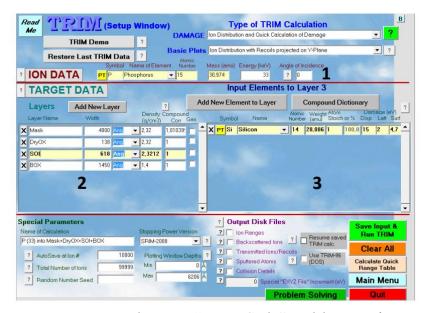

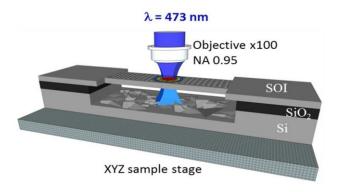

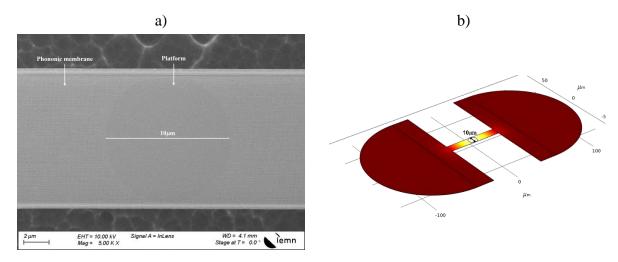

The fabrication process, and realization of these devices, emphasizing their integration onto a Silicon On Insulator (SOI) wafer is detailed in a step-by-step manner, commencing with preliminary procedures such as wafer cleaning and alignment marker etching. Subsequently, we proceed to more intricate stages, including phononic engineering patterning,  $Si_xN_y$  deposition, cavities opening, sidewalls protection, metallization and the suspension of membranes using  $XeF_2$  & Vapor HF etching. Furthermore, we address the challenges encountered during the realization process and provide practical solutions to overcome them. This chapter plays a vital role within the thesis, serving as the foundational infrastructure required to conduct experiments and extract results in the following chapter. It is noteworthy that this fabrication process aligns with the standard complementary metal–oxide–semiconductor (CMOS) fabrication process, ensuring compatibility with industrial silicon CMOS process lines.

Chapter 4: Characterization of the Fabricated Devices and Results.

In the fourth chapter, the spotlight shifts to the characterization of the devices developed throughout the thesis and the ensuing discussions of the achieved outcomes. The chapter is segmented into four sections, each dedicated to distinct measurement protocols and the impact of phonon engineering on specific properties. Starting with the measurement of the Seebeck coefficient, the chapter outlines conditions, procedures, and the influence of phonon engineering on this parameter in both p and n-type Si membranes. Following this, the subsequent sections cover electrical measurements using the conventional "Van Der Pauw" method, thermal conductivity measurements, and zT figure of merit measurements. Each section sheds light on the protocols, conditions, and the effects of phonon engineering. We thoroughly analyze and discuss the results and make comparisons with relevant literature to provide a comprehensive understanding.

## Chapter 1 Thermoelectric properties of silicon: generalities and state of the art

#### Abstract

The first chapter explores thermal energy harvesting, with a specific focus on thermoelectric power generation. The study investigates the thermoelectric effect, transport properties, and optimization techniques, particularly for monocrystalline silicon. This chapter focuses mainly on improving the thermoelectric properties of monocrystalline silicon and its integration into micro thermoelectric harvesters in a planar configuration for near-temperature applications.

| ABSTRACT. |                                                                        | 14 |

|-----------|------------------------------------------------------------------------|----|

| 1.1 THE   | RMOELECTRIC ENERGY HARVESTING FOR SUSTAINABLE WIRELESS SENSOR NETWORKS | 14 |

| 1.2 THE   | RMOELECTRIC EFFECT                                                     | 15 |

| 1.2.1     | Seebeck effect                                                         | 16 |

| 1.2.2     | Peltier effect                                                         | 16 |

| 1.2.3     | Thomson effect                                                         | 16 |

|           | ORY OF THERMOELECTRIC POWER GENERATING DEVICES                         |    |

| 1.4 THE   | RMOELECTRIC TRANSPORT PROPERTIES                                       |    |

| 1.4.1     | Thermal conductivity                                                   | 18 |

| 1.4.2     | Electrical conductivity                                                | 19 |

| 1.4.3     | Seebeck coefficient                                                    | 20 |

|           | RMOELECTRICITY-MATERIAL CHOICE                                         |    |

| 1.6 OPT   | IMIZATION METHODS OF ZT FIGURE OF MERIT OF SILICON                     |    |

| 1.6.1     | Nano-structuration                                                     | 23 |

| 1.6.2     | Oxidization and roughness                                              | 26 |

| 1.6.3     | Phonon engineering                                                     | 27 |

| 1.7 INTE  | EGRATION OF SI FOR THERMOELECTRIC APPLICATIONS                         | 30 |

| Conclusio | )N                                                                     | 33 |

### 1.1 Thermoelectric Energy Harvesting for Sustainable Wireless Sensor Networks

The application of Wireless Sensory Networks (WSN) is fast growing within many sectors (including, but not restricted to security, industry, and aviation), playing the pivotal role of gathering and storing information. In fact, with significant advancement and investment in the technology, wireless sensors network market is forecasted to grow at a compound annual growth rate (CAGR) of 17.64% and be valued at approximately \$123.93B USD by 2026 [3]. The vast majority of WSN currently rely on batteries to store and supply the energy required for their operation. However, the batteries are also considered a major limiting factor in the growth of WSN due to the significant costs and logistical challenges associated with individually replacing sensors with depleted batteries. Additionally, batteries also have the major drawback associated with their relatively large size and weight in microscopic applications.

Regarding the problem of battery lifetime, several solutions have previously been considered. They include "energy-aware Medium Access Control (MAC) protocols (SMAC [4], BMAC [5], XMAC [6]), power aware storage, routing and data dissemination protocols [7][8][9], duty-cycling strategies [10][11], adaptive sensing rate [12] and tiered system

architectures [13]. Though these solutions assist in marginally increasing battery life, they nevertheless only manage to 'kick the can down the road' as the batteries will continue being depleted and will ultimately need to be replaced. Furthermore, increased battery life can create other challenges like larger size and heavier weight, in addition to increased production costs.

The miniaturization of the wireless sensor nodes limits the use of batteries as a power source due to their large size. In microscopic scale the integration of batteries is very complex and difficult. Energy converters are sufficient to supply microscopic sensors with low energy requirements. Furthermore, they open the possibility to integrate the sensor, the energy supply and the communication circuit within one small smart system.

To address the challenge of size and bypass the issue of battery life, energy harvesting is often seen as a potential solution. Energy harvesting refers to scavenging energy or converting energy from one form to the other. The principle of energy harvesting is to extract small amounts of energy from various ambient sources of the environment. The available energy for harvesting is mainly provided by ambient sources such as: 1- light (artificial and natural lighting), 2- thermal sources, 3- mechanical vibration sources and also 4- ambient radio frequency. The abundance of heat, and wasted heat specifically, makes thermoelectric harvesting a particularly advantageous enterprise. Wasted heat is defined as the unused thermal energy given to the surrounding environment in the process of converting primary energy carriers to final use. It is estimated that 72% of global primary energy consumption is wasted, with wasted heat being dispersed into the environment at every step of the energy conversion process [14]. Looking at the electrical energy consumption in residential premises, close to twothirds of the energy is wasted as heat in the extraction process at the power plants and approximately a further one-tenth of the energy is lost as heat in the transportation process. Around 60% of the energy extracted from power plants is lost as waste heat during its generation [15], and between 8% and 15% is lost as heat in the electrical lines for its transport and transformation [16]. Energy harvesting can increase efficiency, minimize cost and reduce maintenance requirements in WSNs. Moreover, large scale heat loss and the ability to redirect this wastage as a source of energy in the energy harvesting process, makes thermal energy harvesting a key consideration in moving forward with the ubiquitous growth of the WSNs.

#### 1.2 Thermoelectric effect

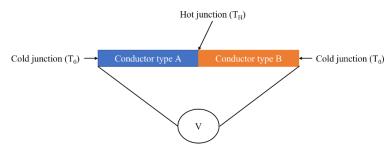

Thermoelectric effects, initially examined during the first half of nineteenth century by T.J. Seebeck and J. Peltier, refers to the conversion of temperature differences into voltage and *vice versa* at the contact point of two distinct electrical conductors, known as the thermocouple (Figure 1-1). Thermoelectric devices, such as the Seebeck generator, employ thermoelectric effects in practical operations to control and measure temperature or generate voltage. The three thermoelectric effects are known as the Seebeck Effect, Peltier Effect and Thomson Effect.

Figure 1-1: Principle of a thermocouple, illustrating the thermoelectric effect. The voltage (V) generated is proportional to the temperature difference  $(T_H - T_0)$  between the hot junction  $(T_H)$  and the cold junction  $(T_0)$ .

#### 1.2.1 Seebeck effect

Of the three individually discovered thermoelectric effects, Seebeck effect was the first, discovered by Thomas Seebeck in 1821. Seebeck demonstrated that an electromotive force could be created at the connection point of two different metals with a temperature difference. Observations made by Seebeck included the deflection of a needle when a bismuth-copper (Bi-Cu), forming a closed loop, was heated. Thus, the misleading term of thermomagnetic was coined. It was later understood that the deflection of the needle was the result of electrical potential thermally built in the thermocouple. The generated electric field (E) is given by the following equation:

$$E = -S. \nabla T$$

Equation 1-1

Where S [V.K<sup>-1</sup>] is the Seebeck coefficient (also known as thermopower), an intrinsic property of the material, and  $\nabla T$  [K.m<sup>-1</sup>] is the temperature gradient.

#### 1.2.2 Peltier effect

The second thermoelectric effect was discovered shortly after, by Jean Peltier and is thus referred to as the Peltier effect. Inverse to the Seebeck effect, the Peltier Effect is the cooling or heating effect when an electric current is passed through a thermocouple. Although there are similarities between the Peltier effect and Joule's heat effect, which also converts electric current into heat, there are crucial differences between these two phenomena. Unlike the Joule heating effect, which is a completely irreversible effect that depends only on the square of the current density (the Joule effect always occurs regardless of the direction of current flow in the element), the Peltier effect is directional (its magnitude depends linearly on the current flow), the amount of heat pumped/released is directly proportional to the current, and is observed only at the junction of the thermocouple (not throughout the entire conductor, as in the Joule heating effect). The Peltier effect is represented as follows:

$$q = \pi$$

. j

Equation 1-2

Where q [W] is absorbed/generated heat, j [A] is the electrical current and  $\pi$  [V] is the Peltier coefficient. The interrelation between the Seebeck and Peltier effects is represented by the following link between their coefficients:  $\pi$  = TS.

#### 1.2.3 Thomson effect

Physicist William Thomson (Lord Kelvin) recognized the internal relation between the Seebeck Effect and Peltier Effect in 1855. The Thomson effect, as opposed to considering a thermocouple like the Seebeck and Peltier effects, describes the thermoelectric effect within a single homogenous conducting material in the presence of a large thermal gradient  $\nabla T$  and electrical current j. Thomson Effect is described using the following equation:

$$q = \beta$$

. j.  $\Delta T$

Equation 1-3

Where  $\beta$  [V.K<sup>-1</sup>] is the Thomson coefficient and  $\Delta T$  is the temperature difference between the two ends of the TE material. The Thomson coefficient is linked to the Seebeck coefficient through:

$$\beta = T \frac{dS}{dT}$$

Equation 1-4

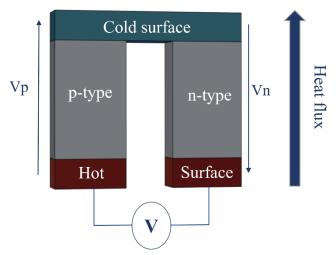

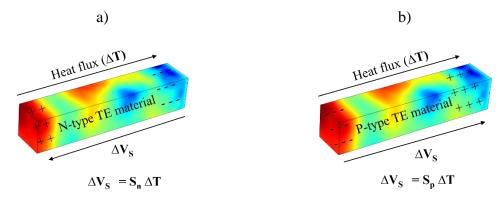

#### 1.3 Theory of thermoelectric power generating devices

The principles of thermoelectric devices will be introduced here, with a discussion on thermoelectric material choice in subsequent pages (p.21). In principle, a power generating thermocouple device comprises two electrically different materials; namely, the n-type and p-type semiconducting materials. In an n-type material, the majority carriers being electrons, a gradient of heat will lead to a drift of electrons along the heat flux. Oppositely, in the p-type material, holes drift is involved. These semiconductors are connected in an electrically series and thermally parallel arrangement (as depicted in Figure 1-2) and are bridged at each end *via* a superior electrical and thermal conducting material. At the hot end, T<sub>H</sub>, extraneously supplied heat ensures a higher temperature is maintained relative to the cold end, T<sub>C</sub>, which is kept at a constant but lower temperature. The temperature difference created between the hot and cold junctions results in an electric current flowing through the load resistor (attached to the cold ends of the system) that closes the electric loop.

Figure 1-2: Thermoelectric power generating device principle.

Thermoelectric generators are evaluated by their efficiency that is given as a function of the Carnot efficiency  $\eta_{carnot}$  and the thermopiles' figure of merit ZT. With  $T_C$ ,  $T_H$ ,  $S_x$ ,  $\rho_x$ ,  $\kappa_x$ , being respectively the temperature of cold and hot sources, Seebeck coefficient, electrical resistivity, and thermal conductivity of x-doped material (x = n, p).

$$\begin{split} \eta &= \frac{Power\ supplied\ to\ load}{Heat\ absorbed\ at\ hot\ junction} \\ \eta &= \eta_{carnot} \times \frac{\sqrt{(1+ZT)}-1}{\sqrt{1-ZT+\frac{T_C}{T_H}}} \\ \eta_{carnot} &= 1-\frac{T_C}{T_H} \end{split}$$

$$ZT = \frac{\left(S_p - S_n\right)^2}{\left(\sqrt{\rho_n \kappa_n} + \sqrt{\rho_p \kappa_p}\right)^2} \times \overline{T}$$

$$\overline{T} = \frac{T_C + T_H}{2}$$

Equation 1-6

Maximizing the thermoelectric efficiency is achieved by increasing the figure of merit that is dependent on the thermoelectric material's transport properties. Good thermoelectric material must combine three main parameters: high electrical conductivity, high Seebeck coefficient and low thermal conductivity.

#### 1.4 Thermoelectric transport properties

#### 1.4.1 Thermal conductivity

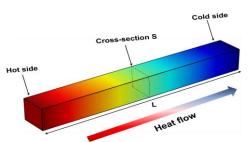

Heat is transferred between objects via several mechanisms: conduction (between objects via direct physical contact), convection (though fluids and gas) and radiation (through electromagnetic radiation). In thermoelectric harvesting, composed of n-type and p-type semi-conductors discussed in p.17, heat is transferred through materials via conduction. Thermal conductivity is a material specific property and is defined as the material's ability to carry thermal energy in the presence of a thermal gradient. The equation for thermal conductivity is given by Fourier's law:

$$\vec{q} = -\kappa . \vec{\nabla} T$$

Equation 1-7

Where  $\kappa$  [W/m.K] is the material's thermal conductivity, q is the local heat flux density [W/m<sup>2</sup>] and  $\nabla T$  is the temperature gradient [K/m].

The two major mechanisms for conduction are the collective excitation of the lattice structure, termed phonons, and the transfer of energy by free charge carriers through the structure. In metal samples with high purity, the electronic contribution to conduction dominates that of phonons; this is a result of the high concentration of the delocalized electrons. The electron thermal conductivity of a material is related to its electrical conductivity by the Wiedemann-Franz law – good electrical conductors are also good thermal conductors – and the specific contribution of the electrons in conducting heat is given by Lorentz' number, L (L=1.6- $2.5 \times 10^{-8}$ V<sup>2</sup>.K<sup>-2</sup>):

$$\kappa_{\rho} = \sigma \cdot L \cdot T$$

Equation 1-8

In insulators, on the contrary, it is the phonons that dominate the propagation of heat due to the relatively lower concentration of free electrons within the material's structure.

$$\kappa_{ph} = \frac{C_v \cdot L_{ph} \cdot v}{3}$$

Equation 1-9

Where  $\kappa_{ph}$  is the lattice thermal conductivity related to the heat propagation through the lattice vibrations (phonons) depending on mean free path  $L_{ph}[m]$ , sound velocity  $v[m.s^{-1}]$  and heat capacity per unit volume  $C_v[J.K^{-1}.m^{-3}]$ .

In semiconductors, even though phonons are responsible for a major part of conduction, there can be instances when phonons and electrons can both play a significant role in thermal conductivity. Thus, the thermal conductivity of a semiconductor is given as a sum of both components: the phonon and electronic contributions.

$$\kappa = \kappa_e + \kappa_{ph}$$

Equation 1-10

In an undoped semiconductor, the free charge density is equal to the intrinsic charge density ( $n_i$ ). In a doped semiconductor (n or p), the charge density is equal to the sum of the intrinsic charge density of the material ( $n_i$ ) and the density of free electrons (donor atoms,  $N_D$ ) or free holes (acceptors,  $N_A$ ). Semiconductors are generally classified in one of two states: extrinsic and intrinsic. At low temperatures (the thermal energy in a material is relatively low), the donor impurity atoms donate an electron, and the acceptor atoms accept an electron (donate a hole). The assumption of complete ionization is often used. Thus, for significant dopant concentration, the density of the majority carriers (the electrons for an n-doped material or the holes for a p-doped material) is almost equal to the density of the impurity atoms n= $n_i$ + $N_D \approx N_D$ . This case corresponds to the extrinsic regime. When the temperature rises and reaches a sufficient level, electron-hole pairs are generated directly under the effect of thermal motion and the concentrations  $n_i$  ( $p_i$ ) of the corresponding charge carriers then rapidly predominate over those of the impurity atoms. The doped material is then in the intrinsic regime.

#### 1.4.2 <u>Electrical conductivity</u>

Electrical conductivity is defined as the ability to carry electric charge and, like thermal conductivity, is material specific. Metallic bonds, where there are positive ions and large seas of delocalized electrons, are most favorable to electrical conductivity. The mobility and 'free' nature of these outer electrons allow them to move along the metallic lattice and thus carry electric charge. From the perspective of the energy band theory, there are sufficiently large number of electrons near the Fermi level leading to large electrical conductivity. The Fermi level of semiconductors is in the band gap, somewhere between the valence and conduction bands. The band gap, also known as the forbidden energy band, is an energy range without electronic states. As discussed earlier (p.18), semiconductors are classified as being in either intrinsic or extrinsic regimes; and the capacity of the semiconductor to conduct electricity is largely dependent on which of these two states it is in. At room temperature in the intrinsic scenario, the valence band is predominantly occupied, leading to a shortage of available holes for charge transport. Similarly, the conduction band is mostly unoccupied, resulting in a scarcity of electrons for charge transport. When in the extrinsic state, by either receiving dopant atoms or employing supplied energy to transfer electrons to the conduction band, resistance is reduced, and the semiconductor can behave as a metal (an electrical conductor). When a sufficiently high temperature is reached, the conduction resistance is reduced exponentially; the relationship can be presented as in the following equations:

$$\sigma(T) \approx \sigma_0 \cdot \exp\left[-\frac{E_G(T)}{k_B \cdot T}\right]$$

$$\sigma(T) = \sigma_p(T) + \sigma_n(T)$$

Equation 1-12

$$\sigma_n(T) = \mu_n(T) \cdot n(T) \cdot |q|$$

Equation 1-13

$$\sigma_p(T) = \mu_p(T) \cdot p(T) \cdot |q|$$

Equation 1-14

Where n and p are the holes and electrons concentrations,  $\mu$  is their mobility [m²/V/s], q is the electronic charge (1.6.10<sup>-19</sup>Coulombs), E<sub>G</sub> is the band gap energy [eV] and k<sub>B</sub> is Boltzmann constant (1.38.10<sup>-23</sup> J/K).

#### 1.4.3 Seebeck coefficient

With the Seebeck effect being the conversion of temperature difference into electromotive force, the Seebeck coefficient is a measure representing the material's ability to do such. The formal mathematical definition of Seebeck coefficient is represented as follows:

$$S = \frac{\Delta V}{\Delta T} \bigg| \Delta T \to 0$$

Equation 1-15

Linking the Seebeck Coefficient to electrical conductivity, Cutler *et al.* [17] redefined a more general formula called the Mott formula as a function of the electrical conductivity expressed as a function of energy E:

$$S = \frac{\pi^2 \cdot k_B^2}{3q} \cdot T \cdot \frac{d(\ln[\sigma(E)])}{dE} \bigg|_{E=E_F}$$

Equation 1-16

Looking at semiconductors more closely, Fritzsche [18] expressed the Seebeck Coefficient as:

$$S_n = \frac{k_B}{q} \cdot \left(\frac{E_c - E_F}{k_B T} + A_n\right)$$

Equation 1-17

$$S_p = \frac{k_B}{q} \cdot \left(\frac{E_v - E_F}{k_B T} + A_p\right)$$

Equation 1-18

With  $E_c$ ,  $E_v$  and  $E_F$  being the conduction band energy, the valence band energy and the Fermi level;  $A_p$  and  $A_n$  are material specific constants.

Having the effective densities of states in valence and conduction bands, the equation above can be further simplified to:

$$S_n = \frac{k_B}{q} \cdot \left( \ln \left( \frac{N_C}{n} \right) + A_n \right)$$

Equation 1-19

$$S_p = -\frac{k_B}{q} \cdot \left( \ln \left( \frac{N_v}{p} \right) + A_p \right)$$

Equation 1-20

With N<sub>c</sub> and N<sub>v</sub> denoting the effective density of states in valence and conduction bands.

#### 1.5 Thermoelectricity-Material choice

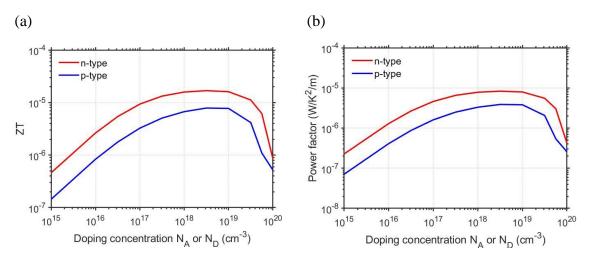

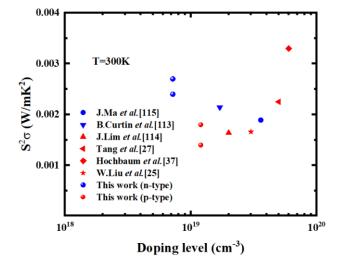

An efficient thermoelectric material should achieve the so-called "phonon-glass/electron-crystal" limit[19]. Semi-conductors offer optimal compromise between S,  $\sigma$  and  $\kappa$ , resulting in the highest zT value. The optimal doping level that refers to the highest zT and power factor (PF) values of Si material at room temperature (T=300K) is  $10^{19}$  cm<sup>-3</sup>.

To distinguish between the figure of merit of a thermoelectric device and that of the thermoelectric material, we assign ZT for the device and zT for the material[20].

Figure 1-3: (a) Si zT as a function of doping concentration, (b) Si power factor as a function of doping level; blue line refers to p-type Si and red line to n-type Si<sup>1</sup>.

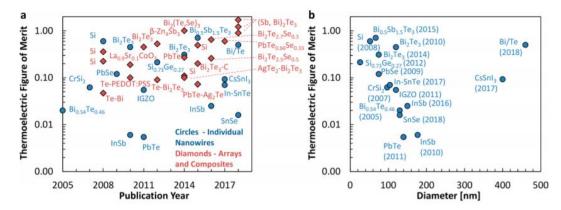

The more commonly investigated thermoelectric materials are based on BiTe, Sb and Pb alloys. Especially the Bi<sub>2</sub>Te<sub>3</sub> class is the reference material due to its high zT value (1.1 state-of-the-art, 0.7 industrial state-of-the -art). However, they remain expensive, harmful and feature low compatibility with low-cost and established CMOS processes. Cheap, ecofriendly and CMOS compatible materials based on silicon and germanium exhibit zT<<1 at room temperature. However, research has demonstrated different methods to enhance the thermoelectric efficiency of Si-based materials near room temperature (Figure 1-4). These methods rely on nanoscale effects, among which thermal conductivity reduction, to reach in some cases a figure of merit close to 1. Therefore, we will opt to use silicon as thermoelectric material in our device. Research has demonstrated the different methods to enhance the thermoelectric efficiency of Si material – this will be discussed in section 1.6.

<sup>&</sup>lt;sup>1</sup> This plot has been obtained by M. Haras and modified by me based on bulk Si parameters. (unpublished)

Figure 1-4: Reported thermoelectric figures of merit (zT) of representative nanowires at room temperature, (a) in chronological order and (b) as a function of wire diameter [21]

#### 1.6 Optimization methods of zT figure of merit of silicon

In section 1.3 we gave the ZT figure of merit of a TE device and in this section, we will present the zT figure of merit of a TE material. The efficiency of a thermoelectric material is evaluated by its thermoelectric figure of merit (zT).

$$zT = \frac{S^2 \sigma}{\kappa} T$$

#### Equation 1-21

Where T is the temperature, S is the Seebeck coefficient,  $\sigma$  is the electrical conductivity and  $\kappa$  is the thermal conductivity.

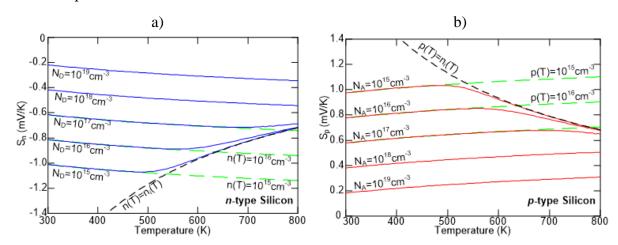

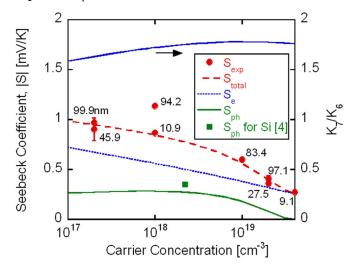

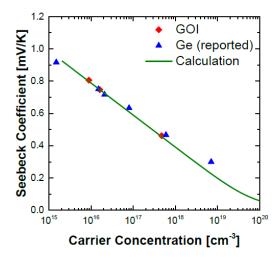

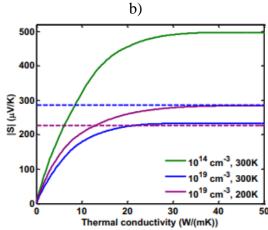

Thermal conductivity is a sum of two contributions dominating lattice  $\kappa_e$  and  $\kappa_{ph}$  (Equation 1- 10). Therefore, to enhance zT, S and the  $(\sigma/\kappa)$  ratio must be increased. Seebeck coefficient is proportional to the logarithm of the carriers' concentration (the Seebeck coefficient decreases with the carriers' concentration). Figure 1-5 shows the variation of Seebeck coefficient as a function of Si level doping and the temperature. Metals have small S due to their high density of free carriers. In contrast, insulators exhibit high S due to low carrier density that facilitates thermally induced movement of carriers from hot region to cold one. Besides,  $\sigma$  for insulators is very low. The figure of merit zT is expressed as  $zT = S^2\sigma T/(k_e + k_{ph})$ . In the metallic limit,  $k_e$  becomes dominant and equals  $L\sigma T$  (Equation 1- 8). Consequently, zT can be simplified to  $zT = S^2/L$  in the case of a metallic scenario.

Figure 1-5: Silicon Seebeck coefficient versus temperature for different doping concentrations. Blue continuous line for n-type doping. Red continuous line for p-type doping. Green dashed line assuming carrier and doping concentrations equality and temperature independence. Black dashed line Seebeck coefficient in intrinsic semiconductor <sup>2</sup>.

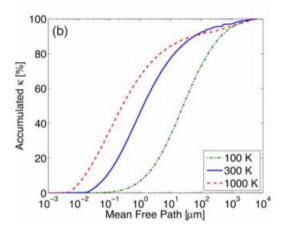

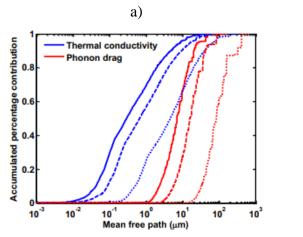

Research investigated to increase the  $(\sigma/\kappa)$  ratio by decreasing the thermal conductivity without affecting the electrical one through the partial suppression of lattice thermal transport. The phonons mean free path  $L_{ph}$  and the electrons mean free path  $L_e$  for Si bulk at room temperature differ by two orders of magnitude ( $L_{ph}\sim300$ nm,  $L_e\sim1.2$ nm) [22]. Moreover, at room temperature more than 85% of the  $\kappa$  value is contributed by the phonons which MFP is between 100 nm and 10  $\mu$ m[23] (Figure 1-6).

Figure 1-6: Accumulated silicon κ over wide range of phonon's free path for different temperatures[23].

Research developed various kind of studies on thermal transport allowing the thermal conductivity reduction such as:

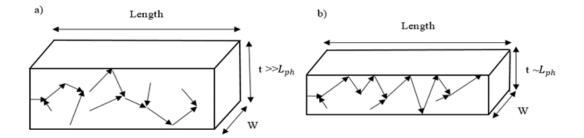

#### 1.6.1 Nano-structuration

Nano-structuration permits the reduction of thermal conductivity by the reduction of the heat flow carried by phonons. The interest in low-dimensional materials approach is to increase the internal interfaces (boundary scattering), the length scale being comparable to the phonon mean free path. Recent progress in nanotechnology enables the fabrication of materials with lower dimensions than  $L_{ph}$ . Hence,  $L_{ph}$  is shortened due to collision with the sample boundaries. Consequently, the thermal conductivity is reduced. Figure 1-7 illustrates the phonon propagation in bulk material and nanostructured material.

<sup>&</sup>lt;sup>2</sup> This plot has been obtained by M. Haras and modified by me based on bulk Si parameters. (unpublished)

Figure 1-7: Phonon propagation in the material, a) in bulk material, b) in nanostructured material.

Improvement of the figure of merit zT has been established using different nanostructured systems 0D (quantum dots), 1D (Nanowires), and 2D (thin films). Therefore, the structure miniaturization represents a key to improve the thermoelectric properties of non-conventional materials such as Silicon and Germanium.

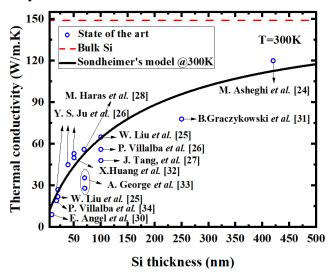

#### 1.6.1.1 2D-silicon membranes and meshes

Thinning effect (2D effect) was experimentally confirmed for several Si thickness[24][25][26][27][28][29][30][31][32][33][34]. The observed reduction in thermal conductivity within thin films is a result of an interplay of intrinsic factors arising from their confined dimensions. These factors encompass interfaces, grain boundaries, and surfaces, introducing additional scattering sites for phonons. Consequently, boundary scattering is intensified, perturbing the smooth propagation of heat. In parallel, the restricted dimensions impose constraints on the mean free paths of phonons, limiting their ability to traverse longer distances before encountering scattering events. As a cumulative effect, this leads to an overall attenuation of heat conduction within thin films. Figure 1-8 graphically presents the relationship between Thermal conductivity and thickness for 2D silicon membranes and meshes (2D).

Figure 1-8: Thermal conductivity as a function of thickness for 2D silicon membranes and meshes (2D).

The silicon thinning allows a significant reduction of the thermal conductivity down to  $9W.m^{-1}.K^1$  for 9 nm thick silicon membrane [30], this incredible reduction opens the way for commercialized silicon thin films based thermoelectric energy harvesters compatible with CMOS technology.

#### 1.6.1.2 1D-silicon nanowires

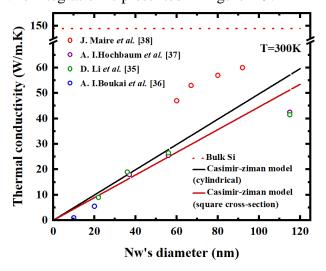

Silicon narrowing effect (1D effect) has been investigated by researchers [35][36] [37][38] for its potential in thermoelectric applications. The principle is the same as the thinning effect by developing silicon nanowires with the smallest possible diameter, owing to the reduction of the thermal conductivity by increasing the borders scattering and the quantum confinement phenomenon. Experimental confirmation of the reduction in silicon's thermal conductivity through nanowire integration is presented in Figure 1-9.

Figure 1-9: Thermal conductivity as a function of Si nanowire's diameter (1D).

#### 1.6.1.3 0D-silicon quantum dots

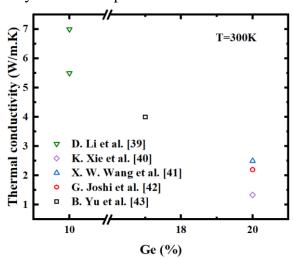

Silicon germanium (SiGe) with an intrinsic lower thermal conductivity than silicon has attracted significant attention as a good thermoelectric material. Numerous scholars[39][40][41][42][43] have observed an additional reduction of the thermal conductivity to the thinning or narrowing effect. This additional reduction is caused by the augmented phonon scattering off the increased density of nano-grain boundaries. D. Li *et al.*[39] have noticed that alloy scattering of phonons in the SiGe segments is the dominant scattering mechanism in the superlattice nanowires in additional to the boundaries scattering. Figure 1-10 reviews the thermal conductivity at room temperature as a function of the Ge percentage.

Figure 1-10: Thermal conductivity as a function of Ge percentage in Si (0D).

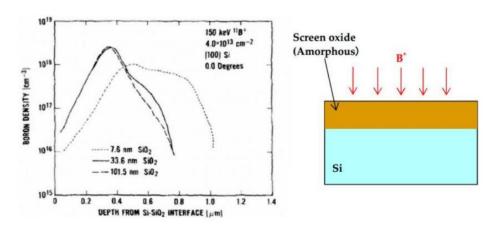

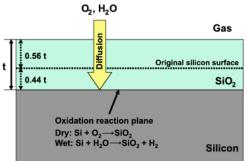

#### 1.6.2 Oxidization and roughness

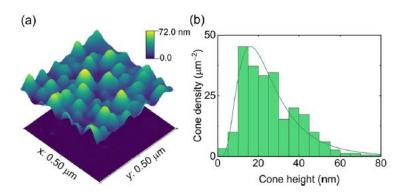

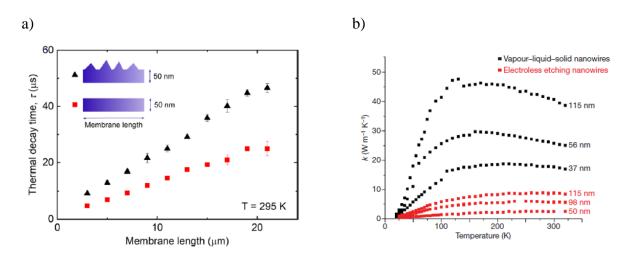

The thermal conductivity of nanostructured systems can be further decreased by roughening[32] [44] or oxidization [45] [46] of the surface. George *et al.*[45] studied the influence of an ultrathin Al film on 70 nm-thick Si membranes using three types of samples: Si membrane without aluminum, with aluminum of 0.5 nm set thickness and with aluminum of 1 nm set thickness. The thermal conductivity was independent of the thickness of deposited aluminum and it decreased from 35 to 23 W.m<sup>-1</sup>·K<sup>-1</sup> and from 28 to 20 W.m<sup>-1</sup>·K<sup>-1</sup> at room temperature for n-type and p-type samples, respectively. Moreover, the electrical conductivity was not affected by the aluminum film which leaded to an increase of the figure of merit *zT*. The results are given in Figure 1-11. Furthermore, a reduction of the thermal conductivity of more than 40% was experimentally demonstrated by Huang *et al.* [32] by roughening the Si surface with arrays of nano-cones (Figure 1-12). Figure 1-13 (a) shows experimentally measured thermal decay times of both samples with and without nano-cones, a long decay time indicates lower heat conductance for constant heat capacity. In addition, 100-fold reduction in thermal conductivity of rough Si nanowire with diameter of about 50 nm synthesized by electrochemical route was reported by Hochbaum *et al.* [44] Figure 1-13 (b).

Figure 1-11: Measured (a) thermal conductivity, (b) electrical conductivity, and (c) figure of merit (zT) of Si membrane as a function of aluminum set thickness[45].

Figure 1-12: (a) AFM images of membranes with (upper) and without (lower) nanocones.(b) Histogram of nanocone height distribution [32].

Figure 1-13:(a) Thermal decay time as a function of length of 50 nm-thick silicon membranes with and without nano-cones at 295K[32], (b) Thermal conductivity of rough Si nanowire (black lines) with different diameters and smooth one (red lines) as a function of temperature[44].

#### 1.6.3 Phonon engineering

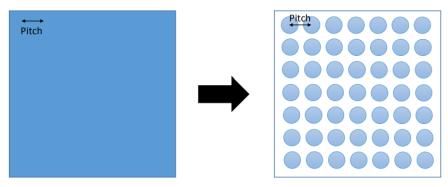

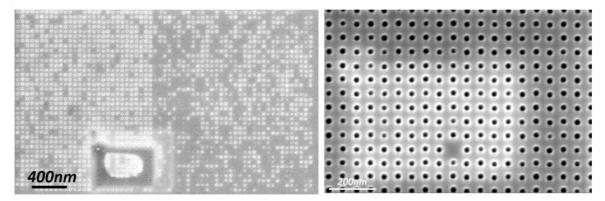

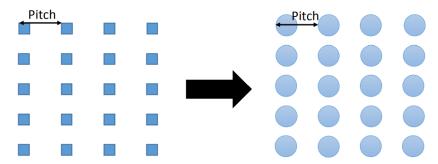

The Si thinning, narrowing, oxidization or roughness improves the  $(\sigma/\kappa)$  ratio. On the other hand, zT increases. However, it remains insignificant, due to the change being less than 1 (zT <1) at room temperature. The key to more develop the  $(\sigma/\kappa)$  ratio is to couple the thinning, narrowing, oxidization and roughness with a phononic engineering solution. Phonon engineering (PnCs) represents the nano-patterning of thin films [47] [31] [48] or nanowires [49] [46] [50] with two-dimensional (2D) arrays of holes. These arrays of holes serve as barriers (or additional scattering sites) to phonons during propagation. Thus, the thermal conductivity reduction. This reduction depends on the placement of holes [50] [51], their diameter [52] [49] [53], periodicity [49] [46], the pitch (the distance between the pores' centers) and the neck (the distance between the edges of two neighboring pores).

Phononic engineering has been studied by both theoretical and experimental means. Tang *et al.* investigated the thermoelectric properties of 100 nm thin silicon membranes patterned with several phononic engineering patterns as given in Figure 1-14. Results show that the pitch and neck size between holes are the key parameters to further reduce thermal conductivity.

Moreover, the doping increases the probability of phonon scattering through the addition of impurities into material and thus the reduction of thermal conductivity.

Figure 1-14: Holey silicon geometry and the measured thermal conductivity at 300K, \*denotes doped samples (Boron  $(5.10^{19} \text{ cm}^{-3})[52]$ .

Yanagisawa *et al.* combined narrowing, surface roughness and phonon engineering to increase the surface scattering rate. Hence, reduce thermal conductivity. Figure 1-15 describes the impact of the holes' diameter, the limiting dimensions, and the pitch size on  $\kappa$  of 1D Si rough and smooth PnCs at 295K and 4K. The neck and pitch size between holes play the most important roles in thermal conductivity reduction. Moreover, the thermal conductivity depends less on the period than on the surface roughness.

Figure 1-15:Measured thermal conductivity of 1D PnCs and nanowires (NWs) as a functions of the hole diameter and the limiting dimension (neck size) at (a) T=295K and (b) T=4K for pitch a=300 nm (black circles) and a=600 nm (red circles)[49].

In the same context, further research studied the impact of the placement of pores in the thermal conductivity. Wagner *et al.* [54] showed that the coherent acoustic phonon modes are suppressed with the introduction of disorder in pore alignment. Nakagawa *et al.* [51] found that the placement of pores has a strong influence on κ when the period is within the range of the thermal phonon mean free path. Maire *et al.* [55] demonstrated that Incoherent boundary scattering depends only on the shape, size, and separation of the holes, although coherent boundary scattering additionally depends on pores' disorder at low temperature (Figure 1-16)

60 0.016 50 к (Wm<sup>-1</sup>K<sup>-1</sup> 40 30 RT 3.7 K 20 0.010 0 15 5 10 15 Disorder (%) 10 20 Disorder (%)

Figure 1-16: Thermal conductivity of the thermos-crystals with hole diameters d=135 nm (red dots) and d=170 nm (blue dots) at room temperature and at 3.7 K.

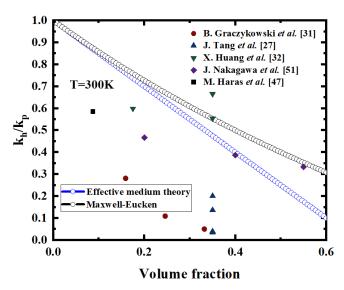

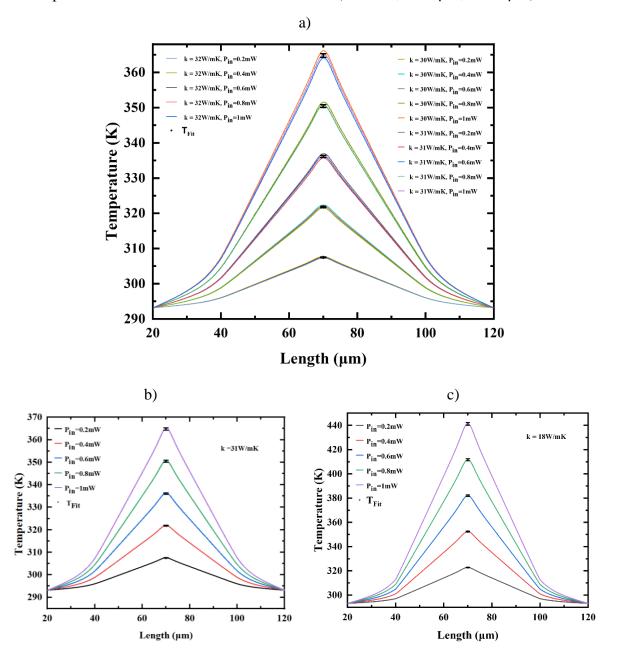

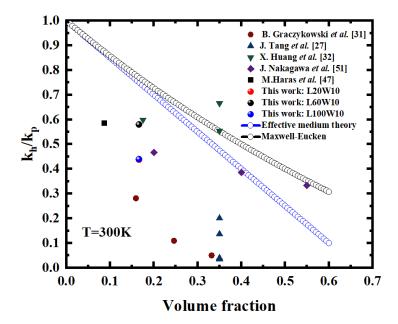

Figure 1-17 gives the measured thermal conductivity of silicon phononic crystals ( $\kappa_h$ ) / the thermal conductivity of plain silicon ( $\kappa_p$ ) ratio at room temperature according to the volume fraction. Thermal conductivity close to amorphous Si limit was obtained by both Tang *et al.*[52] et Graczykowski *et al.* [31]. As can be seen in Figure 1-17, none of the analytical models - the effective medium theory or Mawxell-Eucklen - can describe the thermal conductivity result caused by the formation of phononic crystals in the Si membrane, since the thermal conductivity depends not only on the percentage of porosity (volume fraction), but also on the neck and pitch between the holes.

Figure 1-17: The thermal conductivity of silicon phononic crystals  $(\kappa_h)$  /the thermal conductivity of plain silicon  $(\kappa_p)$  ratio at 300K as a function of volume fraction, including the effective medium theory (blue circles) and Maxwell-Eucken (black circles) fitting.

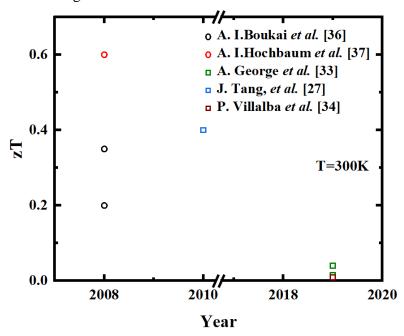

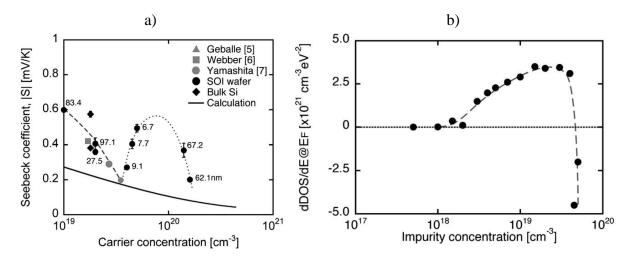

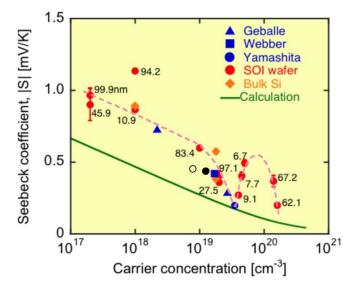

Despite the relatively low value of  $\kappa$  achieved using nanometric structure, few experimental measurements of zT in crystalline silicon nano-objects are presented with significant data dispersion (Figure 1-18). Few measurements were made because each thermoelectric parameter had to be measured separately. Hence the fabrication of different devices. Direct measurement of zT with one device would be a good solution to study the efficiency of the thermoelectric material produced. In chapter 2, all methods for direct determination of zT are investigated.

Figure 1-18: Reported values of zT for crystalline silicon planar configurations.

#### 1.7 Integration of Si for thermoelectric applications

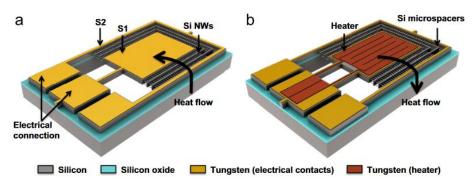

The improvement of the material's figure of merit due to the introduction of nanostructures has encouraged research in this area. Various Si-based micro thermoelectric generators (µTEGs) have been developed. Different designs and configurations were elaborated based on the heat flow direction / device leg growth: (i) Type lateral / lateral (in-plane configuration), (ii) Type vertical / lateral (cross-plane configuration and (iii) Type vertical / vertical (cross-plane configuration). In this thesis we focus on the in-plane configuration (Type lateral / lateral). In in-plane devices, heat flows along the surface, through the TE material which allows a better thermal gradient management. Consequently, it enhances the output voltage and output power. Exploiting the simple planar geometry and the compatibility with Si technology, one-dimensional (1D) nanowire structures grown by the CVD-VLS mechanism have been employed by Devila *et al.* [56]. The fabricated device is based on an architecture consisting of a thermocouple with a uni-leg (p-type) Si arrays. Figure 1-19 schematically illustrates the design of the proposed thermoelectric micro-generator (µTEG).

Figure 1-19: Sketch showing the design of the basic structure. (a) A thermally isolated suspended silicon mass (S1) is connected to the surrounding silicon bulk (S2) through silicon nanowires (Si NWs) allowing a planar temperature difference to be achieved, conforming in this way a thermos-element in which the Si NWs act as a nanostructured thermoelectric material; (b) sketch of a similar device showing an integrated heater employed both as heat source and sensor to control and characterize the temperature gradients attainable in the structure. Heat flow is reversed in this configuration [56].

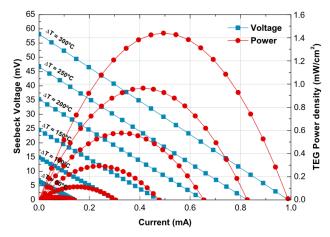

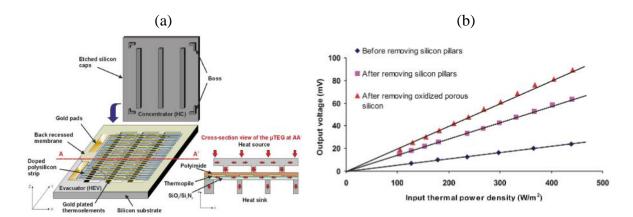

The fabricated  $\mu$ TEG have shown Seebeck voltages up to 60 mV, 4.4 mV and generated power densities up to 1.44 mW/cm², 9  $\mu$ W/cm² respectively, for  $\Delta$ T=300 °C and  $\Delta$ T=27 °C (across the nanowires), working as energy harvesters (Figure 1-20). Other monolithic planar  $\mu$ TEGs (p-type Si) with double thermal deflection was presented by Ziouche *et al.* [57]. In order to improve the heat flow path, a zig-zag thermopiles are embedded between a dielectric film and a layer of polyimide/BCB that electrically isolate it from two periodically etched Silicon wafers which serve as heat concentrator (HC) and heat evacuator (HEV). The  $\mu$ TEG topology proposed is depicted in Figure 1-21 (a). The  $\mu$ TEG was characterized at 3 different steps of the process: (i) before removing the Si  $\mu$ columns, (ii) after removing the Si  $\mu$ columns and (iii) after removing the oxidized porous Si. The results obtained are shown in Figure 1-21 (b). The maximum output power for a five-membranes-based  $\mu$ TEG is 12.3 $\mu$ W/cm² for an input power of 2 W/cm². Due to its high thermal resistance (44.3 K/W) [58], this  $\mu$ TEG allows a heat adaptation to any environment with a high thermal resistance.

Figure 1-20: I–V and power density measurements at high temperature differences. I–V and power curves measured as a function of the temperature difference attained in a structure containing 9 Si NW arrays consecutively bridged. The power generated by the thermo-element (TEG Power) was obtained by measuring the generated voltages as a function of current for diverse temperature differences (DT), which were achieved by applying a DC current to the heater integrated in the structures [56].

Figure 1-21: (a) 3D "exploded" structure and cross-section view of a 3-membranes planar  $\mu$ TEG. The red arrows symbolize heat paths; (b) Output voltage of the 5-membranes  $\mu$ TEG as a function of the input power density[57].

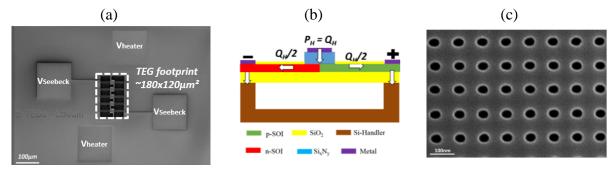

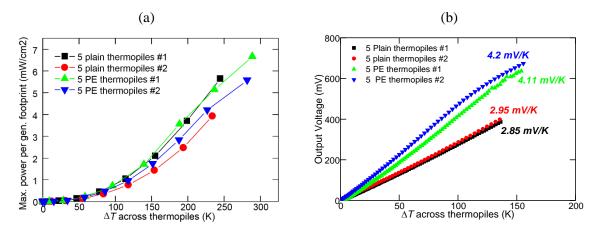

Two dimensions (2D) planar Si-based  $\mu$ TEGs containing ultra-thin single-crystalline Si membranes, 100nm in thickness, as the active TE material were developed by Perez-Marin *et al.*[59]. A power output of  $4.5\mu$ W/cm² was achieved under a temperature difference of 5.5 K. Substantial improvements were achieved by Thierno-Bah *et al.*[1] by reducing the single-crystalline Si thickness to 70 nm and patterning the membrane with an opening of a network of "pores" of ~ 40 nm in diameter and spaced 100nm ("pitch") Figure 1-22. A  $\mu$ TEG with 5 suspended patterned thermopiles (PE) connected thermally in parallel and electrically in series generated a power density about  $6.1 \mu$ W/cm² under a temperature difference of 5.5 K, that could reach few mW/cm² under a temperature difference higher than 100 K. In addition, Seebeck coefficient increases with PE. Hence, patterned thermopiles generate more tension.

Figure 1-22: (a)  $\mu$ TEG made of 5 suspended thermopiles; (b) Cross section of the  $\mu$ TEG giving the heat flow direction; (c) Opening of a network of "pores" of ~ 40nm in diameter and spaced 100nm ("pitch")[1]

Figure 1-23: (a) Electric power generation per generator footprint of 2 samples of patterned thermopiles (PE) and 2 samples of plain membranes(plain) as a function of the temperature difference across the thermopiles; (b) The output voltage and the Seebeck coefficient of 2 samples of patterned thermopiles (PE) and 2 samples of plain membranes(plain) as a function of the temperature difference across the thermopiles[1].

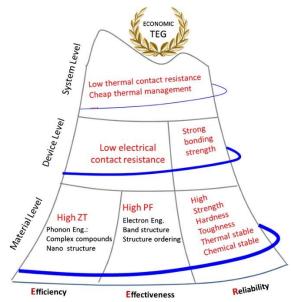

These significant studies open up the opportunity to use silicon-based  $\mu$ TEGs for autonomous sensor nodes' power supplying. However, only few  $\mu$ TEGs were realized. [W. Liu et al.] [60] has shown that high ZT is not the only concern for a reliable, efficient and stable  $\mu$ TEG. Figure 1-24 summarizes the requirements to be taken into account for  $\mu$ TEG fabrication in 3 levels: material level, device level and system level.

Figure 1-24: Hierarchical requirements for  $\mu$ TEG: the efficiency–effectiveness–reliability mountain[60].

#### **Conclusion**

This chapter presented an introduction to the main aspects of thermoelectric materials efficiency and characterization, with a brief introduction to the key theories needed in the discussion of subsequent chapters. In this chapter we discussed the selection choice made on silicon as thermoelectric material of our device. Furthermore, we presented all methods

investigated leading to improve the zT figure of merit of monocrystalline silicon material near room temperature. Examples of integration of silicon and sector of application were also presented in both planar and lateral configuration. Chapter 2 will review all different techniques used to measure the zT figure of merit directly on bulk thermoelectric material or millimetric material where the suspension of the TE material was achieved using wires. Furthermore, it will present a theoretical study and modeling of zT figure of merit direct measurement adapted to membranes.

# Chapter 2 Theoretical studies and modeling of zT figure of merit direct measurement adapted to membranes.

#### Abstract

In the previous chapter, we highlighted the state-of-the-art on improving silicon thermoelectric properties in a planar configuration, by reducing the thermal conductivity component related to phonons. We saw that a relatively low value of thermal conductivity is achieved either by using nano-structuration, narrowing or oxidation. A few experimental measurements of zT figure of merit in crystalline silicon nano-objects were presented with significant data dispersion, as shown in Figure 1-18 chapter 1. This dispersion could be attributed to the determination of zT, which involves measuring the individual components of the thermoelectric figure of merit separately. It is important to acknowledge that significant uncertainty can be associated with each of these parameters. In fact, the uncertainty in zT can readily exceed 50%, considering that each material property may possess an uncertainty range between 5% and 20%. To address this limitation, in this chapter, we present a suitable methodology for direct zT measurement of nanostructured membranes in a planar geometry. This methodology is an adaptation of the transient Harman method. To understand this adapted approach, it's essential to first comprehend the conventional "Harman technique." Therefore, the initial section of this chapter provides an explanation of the conventional methodology.

In this chapter, we demonstrate our methodology using both theoretical (analytical formula) and computational (Finite element modeling) means. The theoretical aspects of the study aim at:

- Determining zT as a function of Joule heating for nanostructured planar configuration.

- Determining zT figure of merit as a function of correction terms.

And the physical aspects of the modeling study via FEM (Finite Element Modeling) intend to:

- Confirm the adapted methodology for direct zT measurement.

- Determining *zT* figure of merit of fabricated membranes using the adapted methodology for nanostructured thermoelectric materials.

| 2.1 zT DIREC | CT MEASUREMENT                                                   | 36   |

|--------------|------------------------------------------------------------------|------|

| 2.2 DESIGN   | OF DIRECT ZT MEASUREMENT DEVICE                                  | 38   |

| 2.2.1 L      | Direct zT measurement device for Bulk materials                  | . 38 |

| 2.2.2 L      | Direct zT measurement device for nanostructured materials        | . 39 |

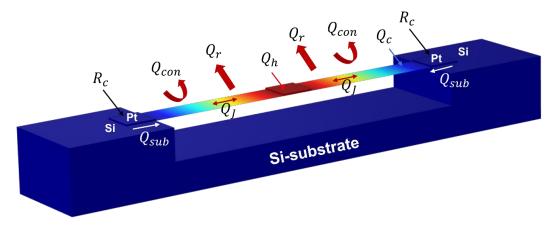

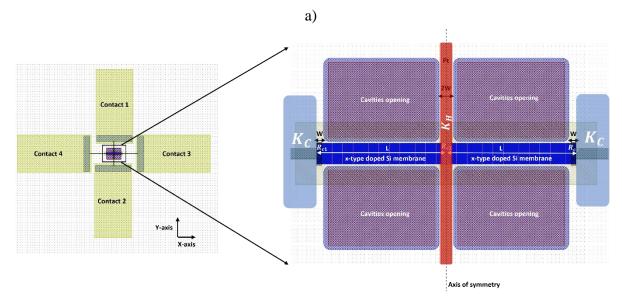

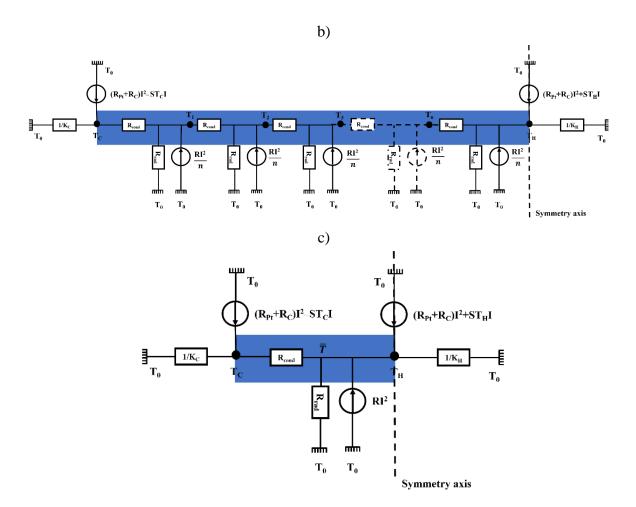

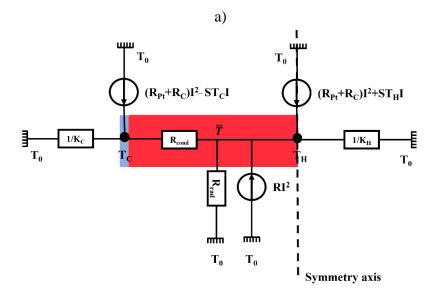

| 2.2.2.1      | Heat transfer mechanisms                                         | 41   |

|              | TICAL STUDY OF ZT DIRECT MEASUREMENT ADAPTED TO MEMBRANES        |      |

| 2.3.1 z      | rT using Harman technique                                        | . 43 |

| 2.3.2 z      | rT considering Joule effect as heat source                       | . 45 |

| 2.3.3 z      | rT considering all losses terms                                  | . 48 |

| 2.4 Model    | ING STUDY OF ZT DIRECT MEASUREMENT ADAPTED TO MEMBRANES          | 53   |

| 2.4.1 F      | Finite Element Method definition                                 | . 53 |

| 2.4.2 H      | Heat transport equations definition                              | . 54 |

| 2.4.3 F      | Physical modeling of zT direct measurement on a thin film        |      |

| 2.4.3.1      | zT direct measurement using Harman technique                     | 56   |

| 2.4.3.2      | zT direct measurement considering Joule heating source           |      |

| 2.4.3.3      | Direct zT with Nanostructured Membranes: Experimental Parameters |      |

| CONCLUSION   |                                                                  | . 63 |

#### 2.1 zT direct measurement

The efficiency of thermoelectric materials is characterized by their figure of merit zT. Various research investigated on enhancing the conversion efficiency by increasing the zT figure of merit with improving the thermoelectric materials performance, rapid, simple and consistent technique to determine its performance is one of the important factors. There are several methods to determine zT, either using analytical or experimental approach where zT measured by experimentation can be obtained directly or indirectly. Generally, the thermoelectric figure of merit components is measured independently employing the individual measurements of the contributing material properties ( $\kappa$ ,  $\rho$  and S). The uncertainty of zT could easily reach 50% considering that each parameter has an uncertainty of 5% to 20% [61].

$$\frac{\Delta z}{z} = 2\frac{\Delta S}{S} + \frac{\Delta \sigma}{\sigma} + \frac{\Delta D}{D}$$

#### Equation 2-1

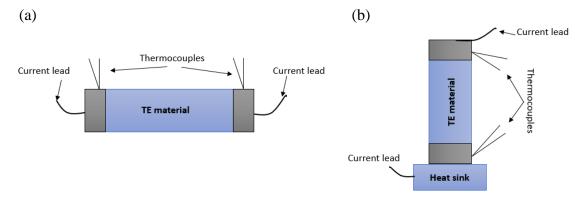

Harman's technique (1958)[2] is an easy and quick method to measure zT directly. The principle of this method is depicted in Figure 2-1(a). The TE material is suspended using two wires that will serve also for current injection in order to minimize the heat losses, 2 thermocouples are used for voltage measurement. For enabling equilibrium at different temperatures to be established rapidly, a heat sink is added as illustrates the Figure 2-1(b).

Figure 2-1: Harman's method principle (a) without heat sink; (b) with heat sink.

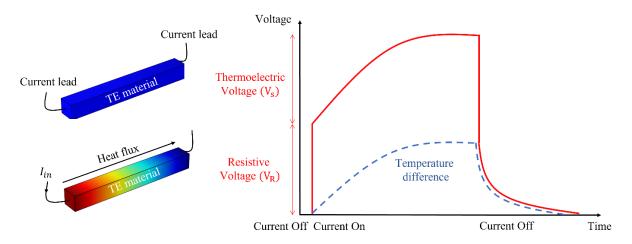

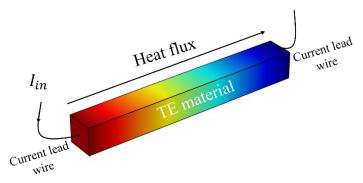

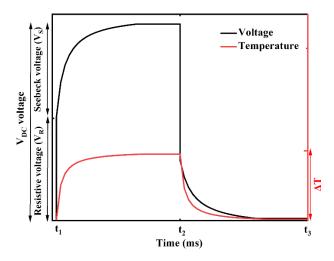

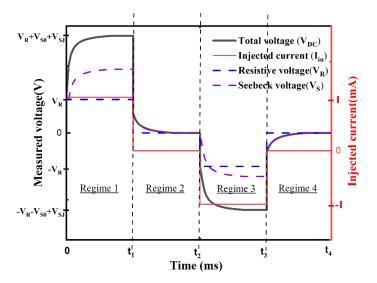

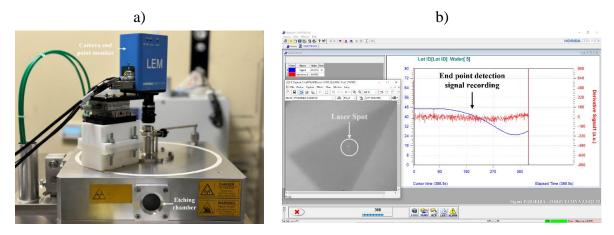

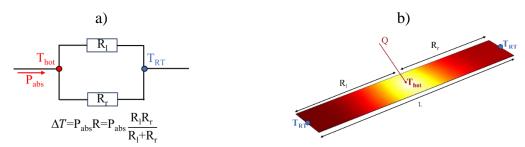

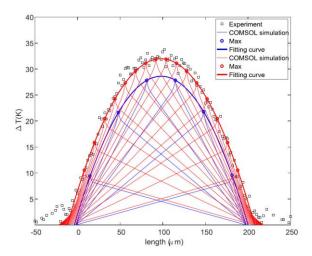

In Harman's technique the Joule heating and the heat losses occurring from within the sample being neglected. Figure 2-2 shows a schematic of Harman measurement method. Under Vacuum and adiabatic condition, a DC current  $I_{in}$  passes through the sample and a voltmeter measures electrical potential drop across the TE element. At the moment the current is injected, while temperature difference across the membrane is equal to 0, the measured voltage  $(V_R)$  corresponds to the multiplication of the current  $I_{in}$ , and electrical resistance (R). In the steady state, the heat flow through the sample due to the temperature difference will be equal to heat generated at the junction when an electrical current  $I_{in}$  flows through the sample due to the Peltier effect ( $SI_{in}T=K\Delta T$ ). Therefore, the Seebeck equation can also be written in relation to the thermal conductance (K), Seebeck coefficient (S) and voltage drop in the electrode as:

$$V_S = S\Delta T = \frac{S^2 T I_{in}}{K}$$

#### Equation 2- 2

DC potential drop across the sample  $V_{dc}$  becomes  $V_{dc} = IR + S\Delta T = V_R + V_S$ .

The Harman zT is given as follows[2]:

$$zT = \frac{S^2T}{RK} = \frac{V_S}{V_R} = \frac{V_{dc}}{V_R} - 1$$

Equation 2-3

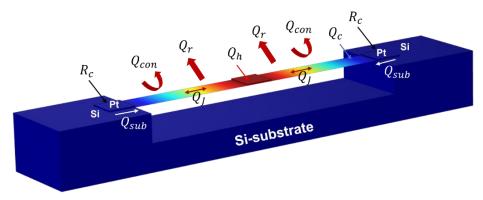

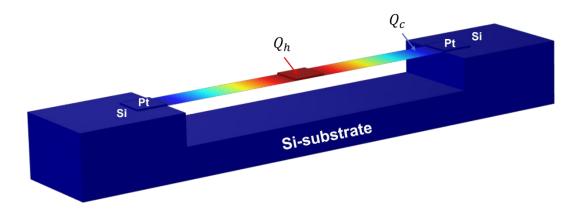

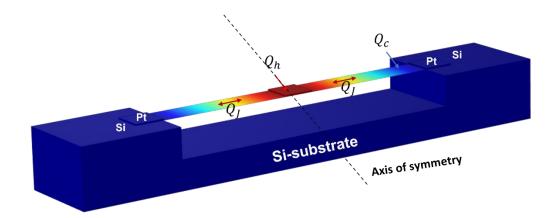

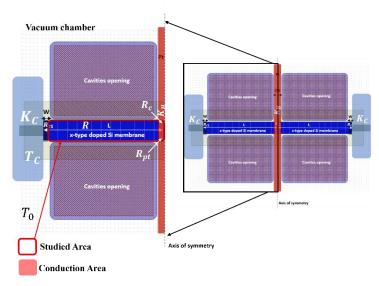

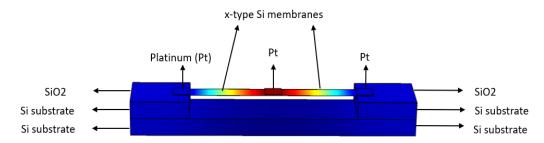

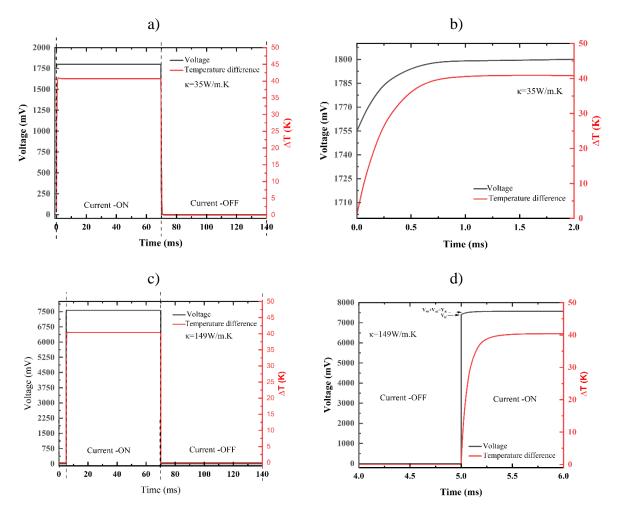

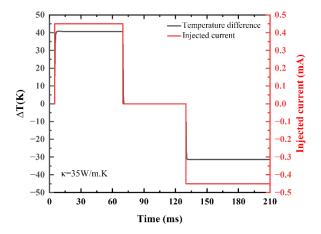

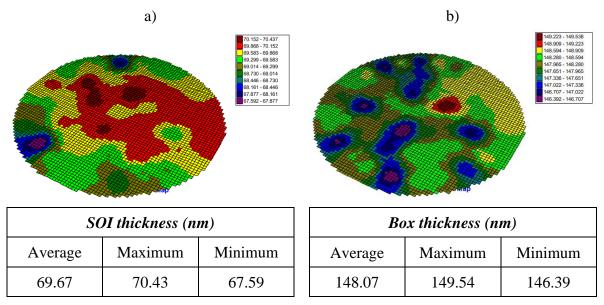

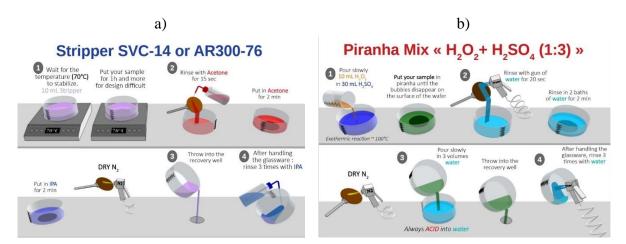

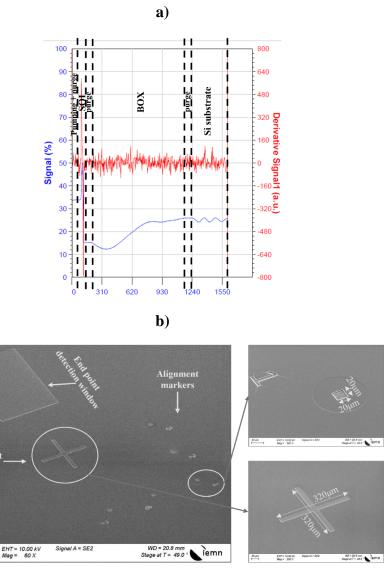

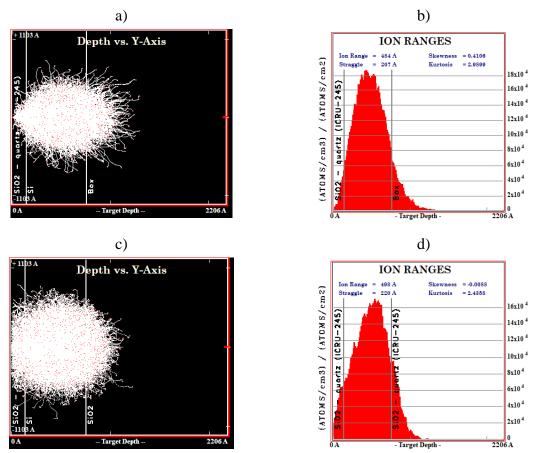

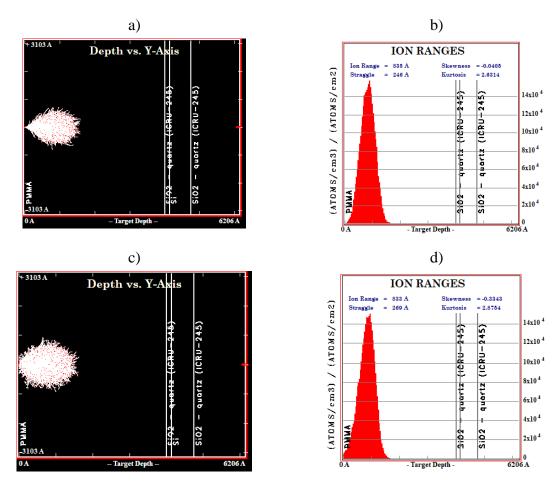

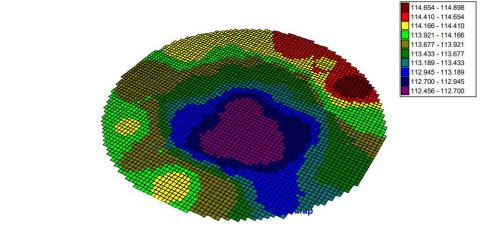

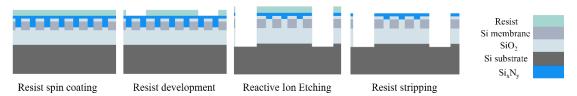

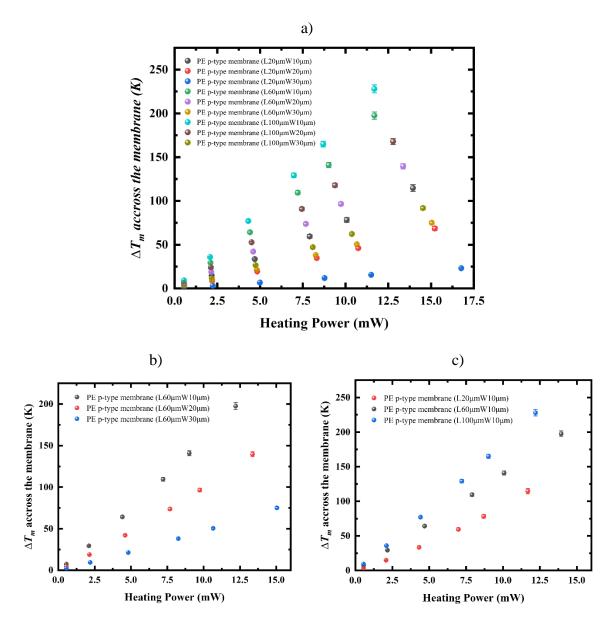

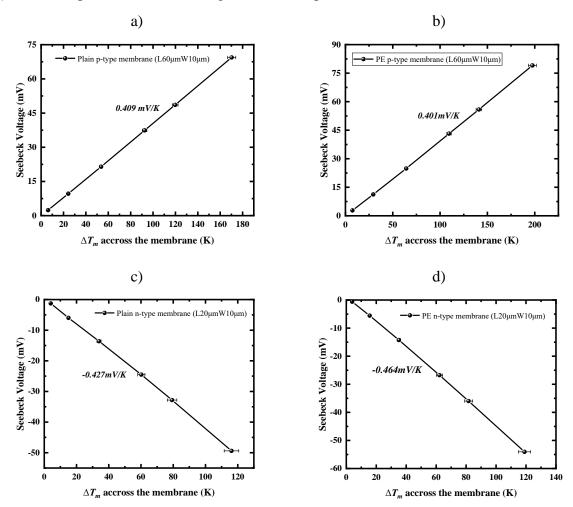

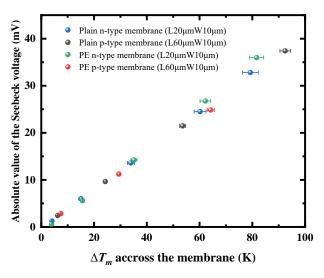

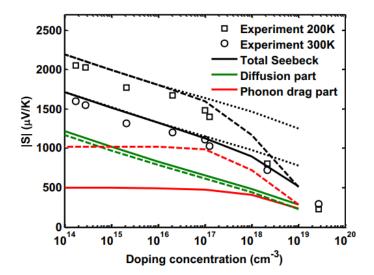

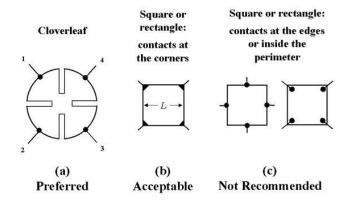

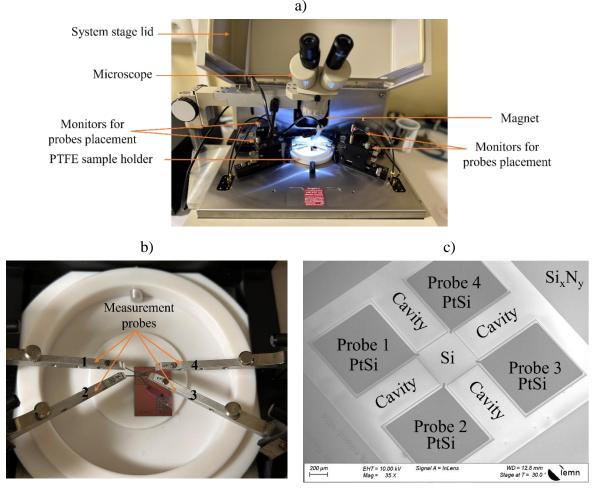

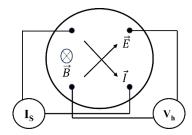

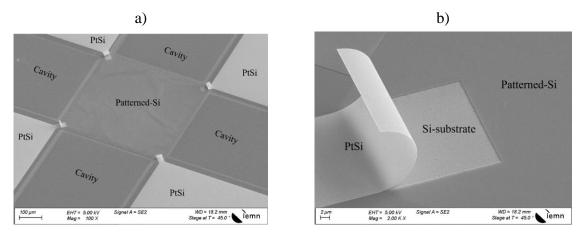

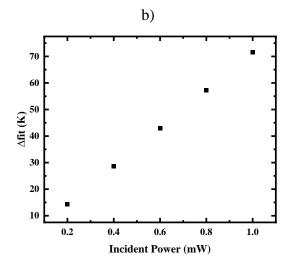

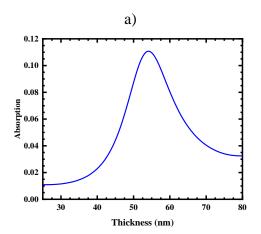

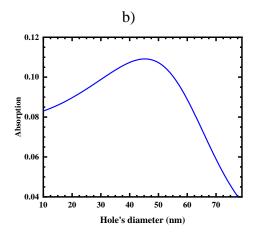

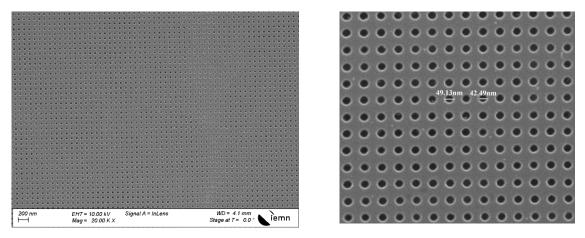

Figure 2-2: Schematic of Harman measurement method depicting i) the suspended thermoelectric element before and after injection of a DC current  $I_{in}$  ii) the measured voltage accross the sample versus time.