# **THÈSE**

Présentée à l'Université de Lille École doctorale 632 : Science de l'ingénierie et des systèmes

En vue d'obtenir le grade de

### **DOCTEUR**

en

"Électronique, Microélectronique, nanoélectronique et Micro-ondes"

Novel Hybrid Approach to 2 step SAR Assisted ADC with Bidirectional Digital Slope for Low Power Applications

Nouvelle approche du SAR hybride à 2 étages, assisté d'une pente digitale bidirectionnelle pour des applications à faible consommation d'énergie.

Préparée en collaboration avec:

STMicroelectronics, Grenoble, France Le laboratoire IEMN, Lille, France

Présentée le 8 Décembre 2023 par :

### Jean-Baptiste CASANOVA

### Jury

| M. Haralampos Stratigopoulos            | DR, HDR - LIP6 – Sorbonne Université | Président du Jury  |  |

|-----------------------------------------|--------------------------------------|--------------------|--|

| M. Dominique Dallet                     | PR, HDR - IMS Bordeaux               | Rapporteur         |  |

| M. Daniel Dzahini                       | IGR, HDR -TIMA-Grenoble INP          | Rapporteur         |  |

| <b>Mme Caroline Lelandais- Perrault</b> | MCF, Ph.D - GEEPS - Centrale-Supelec | Examinatrice       |  |

| M. Chadi Jabbour                        | MCF, HDR - Télécom Paris             | Examinateur        |  |

| <b>Mme Sandrine Nicolas</b>             | Ing - STMicroelectronics             | Encadrante         |  |

| Mme Danika Perrin                       | Ing -STMicroelectronics              | Encadrante         |  |

| M. Andreas Kaiser                       | DR, HDR - Junia, Université de Lille | Directeur de Thèse |  |

À mon grand-père

#### Résumé

Dans un contexte d'objets toujours plus connectés, la réalisation de chaînes de réception radio faible consommation devient un défi. Dans le cadre d'un financement Cifre ST-IEMN, cette thèse aborde l'enjeu des performances de l'ADC afin d'alléger les contraintes de la chaîne radio analogique. Un ADC présentant 68dB de SNDR à une cadence de 64MS/s avec une consommation inférieur à 300µW est ciblé pour ces travaux.

Après une analyse de l'état de l'art cette thèse propose une innovation de l'approche des convertisseurs SAR hybrides assistés de convertisseur à rampes. Une approche pseudo différentielle permet de diviser par deux la consommation et le temps de conversion de l'étage rampe. Une modélisation complète du système en VerilogA a permis de démontrer la fonctionnalité de la nouvelle architecture ainsi que l'implémentation d'algorithme de calibration. A partir de mesures publiées sur des réalisations similaires, les performances en termes de consommation de l'ADC sont extrapolées. En gardant une marge d'erreur de 30% l'ADC présente une consommation inférieure à 250μW, un SNDR de 67.1 dB pour un échantillonnage de 64MS/s. Ces résultats permettent d'estimer une figure de mérite de Schreier au-delà de 178dB. Une étude des effets non linéaires dues à la bande passante limité du comparateur temps continu de l'étage rampe est également proposée. Leur impact sur la conversion est exprimé en fonction d'un unique paramètre et une correction à partir de ce paramètre est proposé. Cette méthode est comparé à l'état de l'art et montre un gain significatif en performance pour l'application visée.

### **Abstract**

In a context of increasingly connected objects, the creation of low-power radio reception chains is becoming a challenge. As an industrial partnership Ph.D between STMicroelectronics and IEMN lab, this thesis studies the ADC performance challenge in order to alleviate the constraints of the analogue chain. An ADC with 68dB SNDR at 64MS/s and a power consumption of less than  $300\mu W$  is targeted for this work.

Following an analysis of the state of the art, this thesis proposes an innovative approach to hybrid SAR ADCs assisted by ramp converters. A pseudo-differential approach is used to halve the power consumption and conversion time of the ramp stage. Full modelling of the system in VerilogA was used to demonstrate the functionality of the new architecture and the implementation of a calibration algorithm. ADC power consumption was extrapolated from published measurements of similar systems. With a margin of error of 30%, the ADC has a power consumption of less than 250µW and an SNDR of 67.1dB at a sampling rate of 64MS/s. These results allow an estimate of a Schreier figure of merit above 178dB. A study of the non-linear effects due to the bandwidth limitation of the ramp stage's continuous time comparator is also proposed. Their impact on conversion result is expressed in terms of a single parameter and a correction as a function of this parameter is proposed. This method is compared with the state of the art and shows a significant gain in performance for the targeted application.

# **Table of Content**

| SCIENTI           | IFIC PRODUCTION                                 | 13 |

|-------------------|-------------------------------------------------|----|

| GENERA            | AL INTRODUCTION                                 | 14 |

| INTROD            | DUCTION GENERALE (FRANÇAIS)                     | 17 |

| <u>Chap</u>       | oter 1                                          |    |

| 1.1               | RF-RX CHALLENGES                                | 21 |

| 1.1.1             | CHALLENGES IN RX FRONT-END DEVELOPMENT          | 21 |

| 1.2               | ADC IN RF RECEIVER CHAIN                        | 23 |

| 1.2.1             | ADC KEY PARAMETERS                              | 23 |

| 1.2.2             | 2 Interaction between ADC and RX front end      | 25 |

| 1.2.3             | ADC Specifications                              | 27 |

| 1.3               | SURVEY OF ADC STATE OF THE ART                  | 29 |

| 131               | L METRICS AND TOOLS TO COMPARE.                 | 70 |

| 1.3.2             |                                                 |    |

| <b>Chap</b> 2.1.1 | MAIN ADCS ARCHITECTURES                         | 34 |

| 2.1.1             | FLASH, OVERSAMPLED, AND PIPELINED ARCHITECTURES | 34 |

| 2.2               | 1.1.1 Flash Topology                            | 35 |

| 2.2               | 1.1.2 $\Sigma\Delta$ topology                   | 36 |

| 2.2               | 1.1.3 Pipelined topology                        | 38 |

| 2.1.2             | 2 Successive Approximation Register (SAR)       | 40 |

| 2.2               | QUANTITATIVE ANALYSIS OF THE ADC SURVEY         | 45 |

|                   | OVERALL SURVEY, SILICON MEASUREMENTS FROM [11]  |    |

| 2.2.2             | 2 OVERALL SURVEY, FILTERED SILICON REALIZATIONS | 46 |

| 2.3               | HYBRID SAR ARCHITECTURES                        |    |

| 2.3.1             | Hybrid SAR Pipeline                             | 48 |

| 2.3               | 3.1.1 Amplify and quantize the residue          | 48 |

| 2.3               | 3.1.2 State of the art performance              | 49 |

| 2.3.2             |                                                 |    |

|                   | 3.2.1 Noise Shaping SAR (NS-SAR) Overview       |    |

|                   | 3.2.2 State of the art performance              |    |

| 2.3.3             |                                                 |    |

| 221               | I Hyppin SAR TDC [60]                           | 5/ |

| 2.3         | 3.4.1 Overall architecture                                          | 54  |

|-------------|---------------------------------------------------------------------|-----|

| 2.3         | 3.4.2 Performances and drawbacks                                    | 55  |

| 2.3         | 3.4.3 Calibration and repeatability                                 | 56  |

| 2.3.5       | HYBRID SAR DS [3]                                                   | 57  |

| 2.3         | 3.5.1 Overall architecture                                          | 57  |

| 2.3         | 3.5.2 Advantages and drawbacks                                      | 59  |

| 2.4         | CONCLUSION                                                          | 60  |

| <u>Chap</u> | <u>ter 3</u>                                                        |     |

| 3.1         | PROPOSED ARCHITECTURE                                               | 63  |

| 3.1.1       | CONCEPTS AND CHALLENGES OF THE ARCHITECTURE                         | 63  |

| 3.1         | 1.1.1 Use of the SAR LSB as information                             | 65  |

| 3.1.2       | ERROR SOURCES AND CORRECTION                                        | 70  |

| 3.1         | 1.2.1 Comparator offset and noise in the SAR                        | 70  |

| 3.1         | 1.2.2 Inter stage redundancy                                        | 73  |

| 3.1         | 1.2.3 SAR redundancy                                                | 74  |

| 3.1         | 1.2.4 Offset calibration                                            | 76  |

| 3.1         | 1.2.5 CT-CMP Latency                                                | 77  |

| 3.1         | 1.2.6 Latency correction                                            | 79  |

| 3.1         | 1.2.7 DAC non idealities                                            | 81  |

| 3.1         | 1.2.8 Noise balance                                                 | 82  |

| 3.1         | 1.2.9 Extra capacitance impact on dynamic                           | 84  |

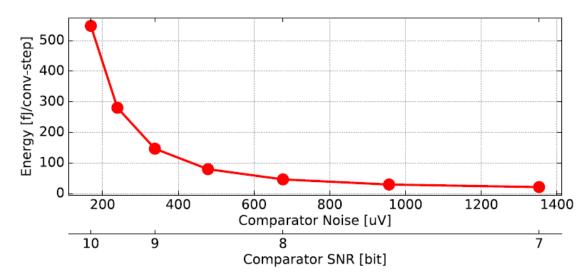

| 3.2 SIZIN   | NG OF THE PROPOSED ARCHITECTURE                                     | 85  |

| 3.2.1       | BIT REPARTITION BETWEEN STAGES                                      | 85  |

| 3.2.2       | NOISE BALANCE IN THE PROPOSED ARCHITECTURE                          | 87  |

| 3.2.3       | DETAILS OF PROPOSED ARCHITECTURE                                    | 89  |

| 3.2.5       | 2 <sup>ND</sup> STAGE DIGITAL SLOPE DESCRIPTION                     | 91  |

| 3.3         | VERILOGA MODEL                                                      | 95  |

| 3.3.1       | DESCRIPTION OF THE VERILOGA MODEL                                   |     |

| 3.3.2       | TESTBENCH AND SIMULATION RESULTS                                    |     |

| 3.3.3       | POWER CONSUMPTION ESTIMATION                                        | _   |

| 3.3.4       | COMPARISON WITH STATE OF THE ART                                    |     |

|             |                                                                     |     |

| 3.4         | CONCLUSION                                                          | 104 |

| <b>~</b>    |                                                                     |     |

| <u>Chap</u> | ter 4                                                               |     |

| 4.1         | 2 <sup>ND</sup> STAGE CT-CMP DESIGN                                 | 107 |

| 4.1.1       | STATE OF THE ART OF CONTINUOUS TIME COMPARATOR                      |     |

| 4.1.2       | DESIGN SPECIFICATION OF THE CT-CMP IN BIDIRECTIONAL DS ARCHITECTURE | 109 |

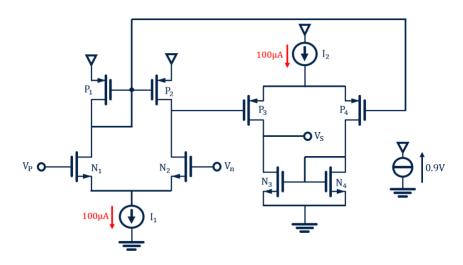

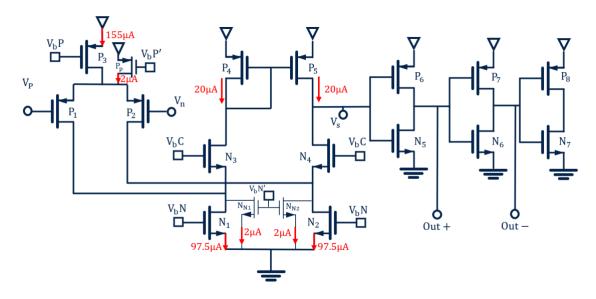

| 4.1.3       | CT-CMP, 2 STAGE AMPLIFIERS DESIGN IN 18NM TECHNOLOGY                | 110 |

| 4.2         | NON LINEARITY BEHAVIOR DUE TO BANDWIDTH RESTRICTION                 | 113 |

| 4.3        | FOLDED CASCODE CT-CMP                                                  | 115 |

|------------|------------------------------------------------------------------------|-----|

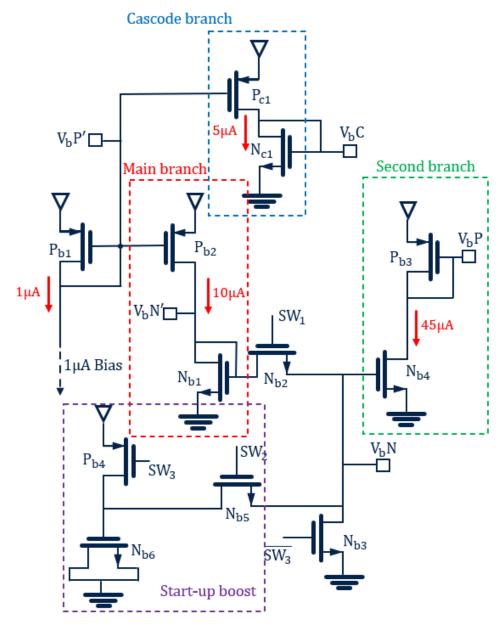

| 4.4        | BIAS AND START-UP STAGE                                                | 117 |

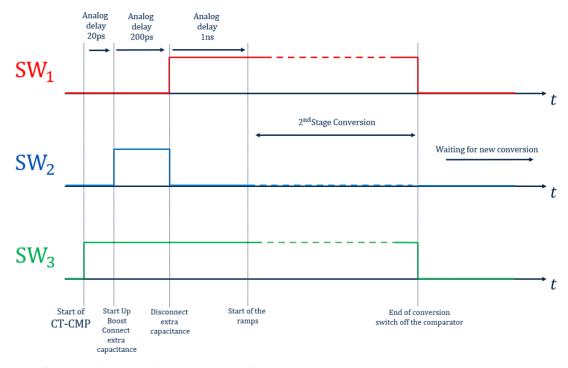

| 4.5        | LAYOUT AND PLS RESULTS                                                 | 121 |

| 4.6        | CONCLUSION                                                             | 125 |

| <u>Cha</u> | <u>pter 5</u>                                                          |     |

| 5.1        | NON-LINEARITY IN CT-CMP                                                | 128 |

| 5.2        | NON-LINEARITY COMPENSATION                                             | 130 |

| 5.2.       | .1 COMPENSATION OF THE NON-CONSTANT DELAY AT THE BEGINNING OF THE RAMP | 131 |

| 5.2.       | .2 COMPENSATION OF THE NON-CONSTANT DELAY AT THE END OF THE RAMP       | 133 |

| 5.2.       | .3 VALIDATION OF THE LINEARIZATION WITH POST-LAYOUT SIMULATIONS        | 134 |

| 5.3        | DIGITAL POST-CORRECTION                                                | 137 |

|            |                                                                        | 138 |

| 5.3.       | .1 DELAY MODEL                                                         | 138 |

| 5.3.       | .2 MODEL BASED OUTPUT ERROR CORRECTION                                 | 139 |

| 5.3.       | .4 VALIDATION OF OUTPUT ERROR CORRECTION WITH SIMULATED DATA           | 141 |

| 5.3.       | .4 PRACTICAL IMPLEMENTATION OF DIGITAL POST CORRECTION                 | 141 |

| 5.5        | CONCLUSION                                                             | 143 |

| <b>~</b> 1 |                                                                        |     |

| <u>Cha</u> | <u>pter 6</u>                                                          |     |

| 6.1        | CONCLUSION                                                             | 145 |

| 6.2        | FUTURE WORK                                                            | 147 |

# List of Figures

| Figure 1 - a) Block diagram of mixed analog-digital super-heterodyne receiver b) Spectrum               |       |

|---------------------------------------------------------------------------------------------------------|-------|

| representation of signal before and after down conversion                                               | 21    |

| Figure 2 - Representation of frequency sampling and mirror frequency on first and second Nyquist        | 22    |

| Figure 3 - Bock diagram of a superheterodyne receiver frontend                                          | 23    |

| Figure 4 - Inspired from [9] Receiver signal, noise flow diagram and ADC parameter                      | 25    |

| Figure 5 - Example of tradeoff between RF front end and ADC (a) ADC relaxed (b) Front-end relaxed       |       |

| Figure 6 - Dimensioning of the minimum SNR compared to the I/C standard requirement                     | 28    |

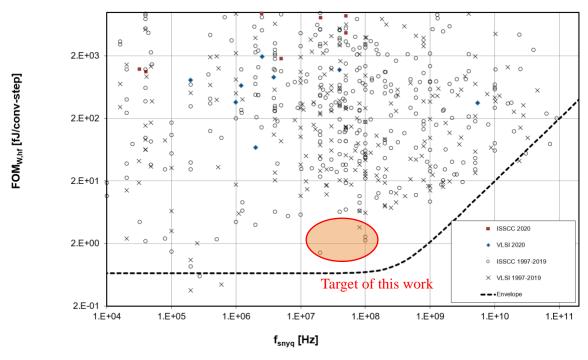

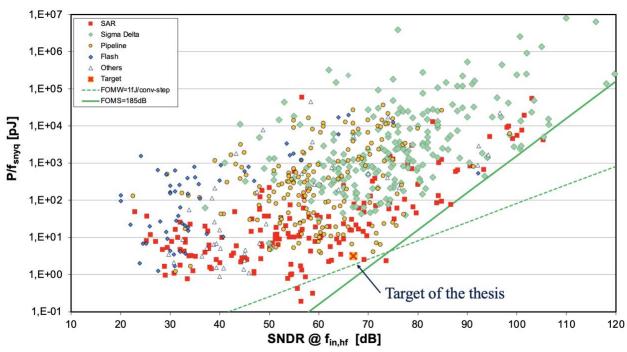

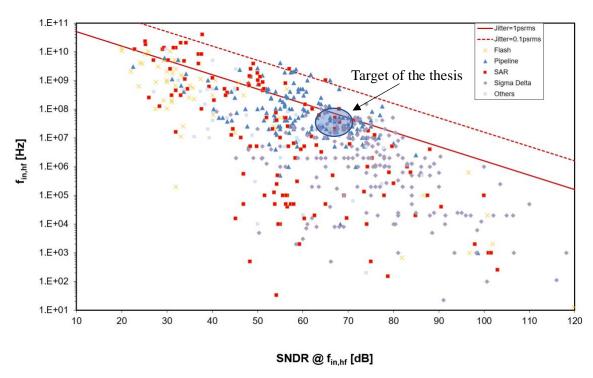

| Figure 7 - Walden FOM plot compared to sampling frequency (1997-2020) from [11]                         | 31    |

| Figure 8 - Schreier FOM plot compared to sampling frequency (1997-2020) from [11]                       | 31    |

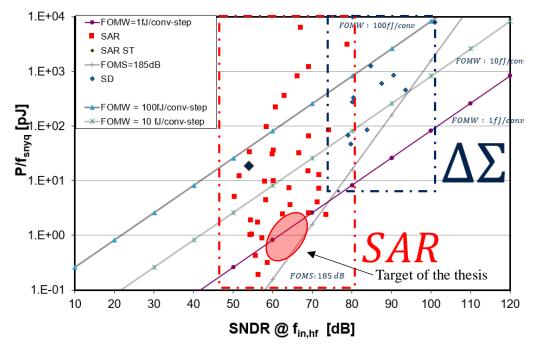

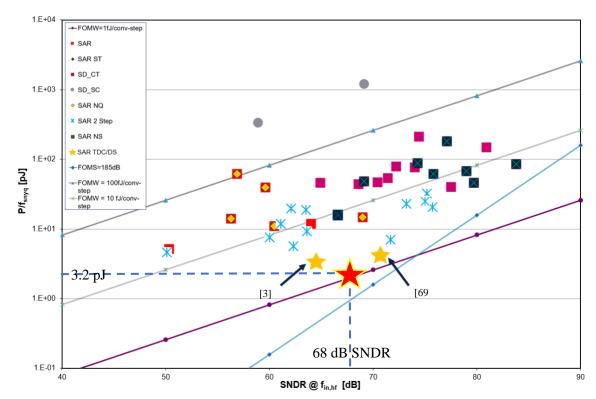

| Figure 9 - Main performance trends of ADC topologies, inspired by [31], with data of [12]. The star     |       |

| symbol identifies the target specifications for this work as defined in chapter 1                       | 34    |

| Figure 10 - Concept representation of flash ADC                                                         |       |

| Figure 11 - Simplified block representation of a ΣΔ ADC                                                 |       |

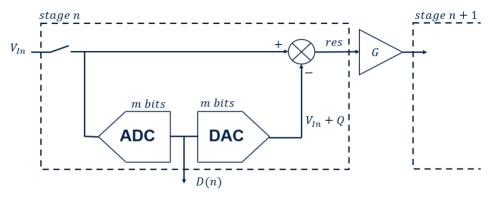

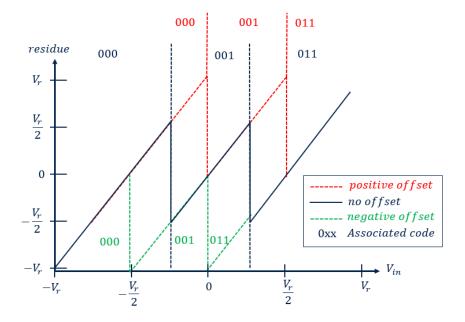

| Figure 12 - Block diagram of a m bits unit stage in a pipelined ADC                                     |       |

| Figure 13 -Example of transfer function of a 1.5-bit pipeline stage introducing a redundancy of 0.5 bit |       |

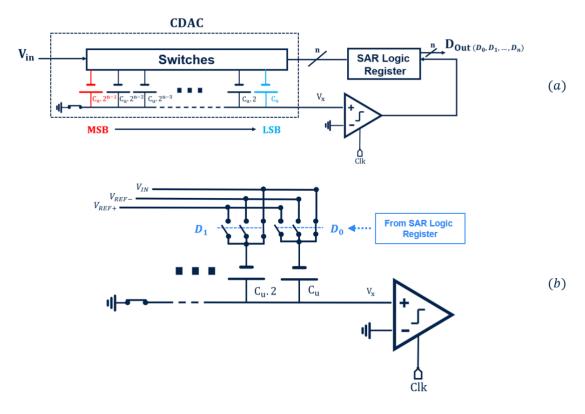

| Figure 14 - Block diagram of a charge redistribution SAR ADC (a) zoom on switches (b)                   |       |

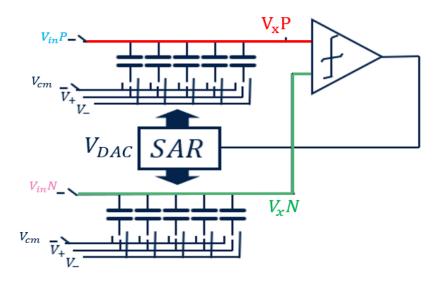

| Figure 15 - Block diagram of a differential top plate sampling SAR ADC architecture                     |       |

| Figure 16 - Example of 3 bit differential SAR operation                                                 |       |

| Figure 17 - Quotient of power over the frequency compared to SNDR on the whole B. Murmann Sur           |       |

| Figure 18 - Nyquist frequency compared to SNDR on the whole B. Murmann Survey                           |       |

| Figure 19 - Plot of filtered ADC - Power/Frequency in function of the SNDR                              | 47    |

| Figure 20 - Plot of filtered ADC - F_in high frequency equivalent to the bandwidth of Nyquist ADC       |       |

| compared to SNDR                                                                                        | 47    |

| Figure 21 - Block representation of a pipelined SAR architecture                                        | 48    |

| Figure 22 - From [11] energy efficiency depending on resolution for realizations close to the target    | 49    |

| Figure 23 - Generic block diagram of an NS-SAR ADC                                                      | 50    |

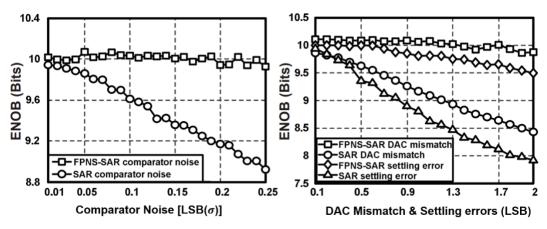

| Figure 24 - From [65] comparison of simulated comparator noise effect and DAC mismatch and settl        | ling  |

| error effect on SAR architecture with and without fully passive noise shaping (FPNS)                    | 51    |

| Figure 25 - From [11] energy efficiency depending on resolution for realizations close to the target    |       |

| including with focus on NS-SAR architectures                                                            | 52    |

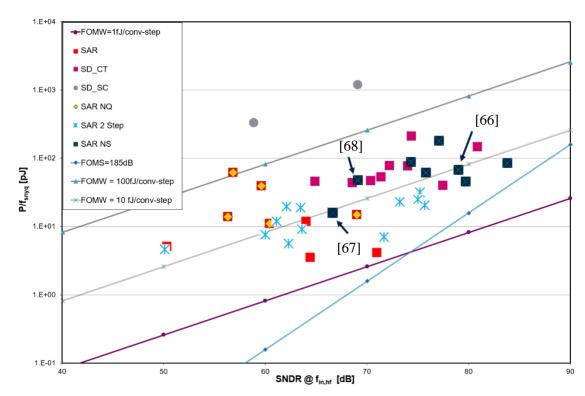

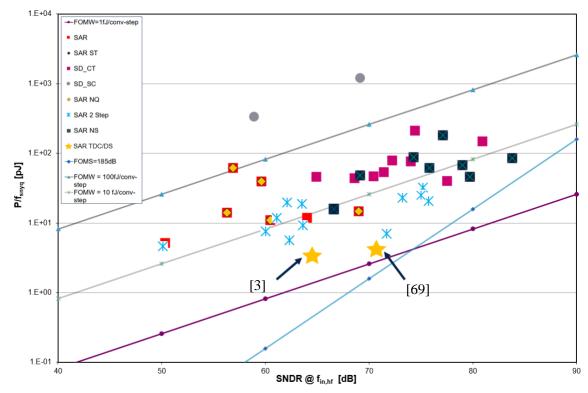

| Figure 26 - From [11] energy efficiency depending on resolution for realizations close to the target    | 53    |

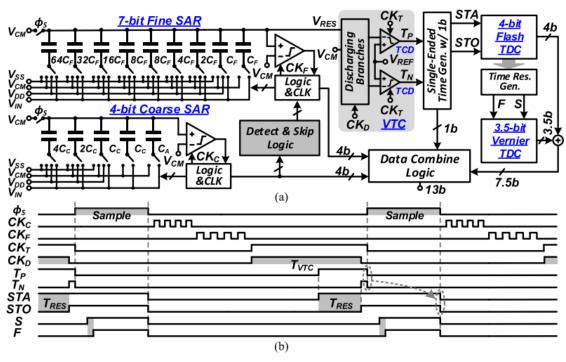

| Figure 27 - From [69], block (a) and timing diagram (b) of the proposed architecture (single-ended S    | SAR   |

| ADC for simplicity)                                                                                     | 54    |

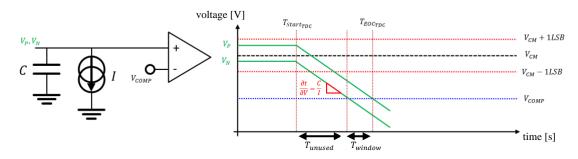

| Figure 28 - Temporal representation of the differential VTC presented in [69]                           | 55    |

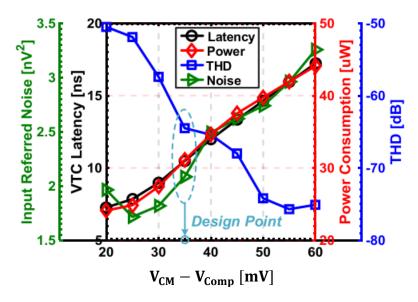

| Figure 29 - From [69], Simulated tradeoff between the VTC latency, power consumption, THD, and          | input |

| referred noise.                                                                                         |       |

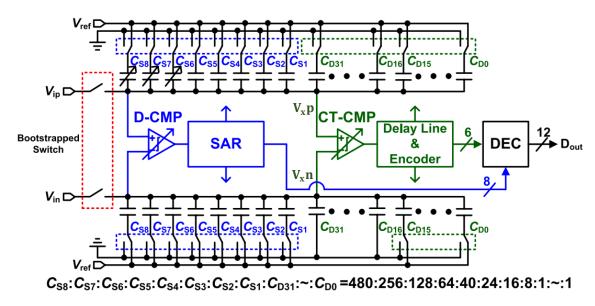

| Figure 30 - From [3], block diagram of the SAR assisted DS ADC                                          |       |

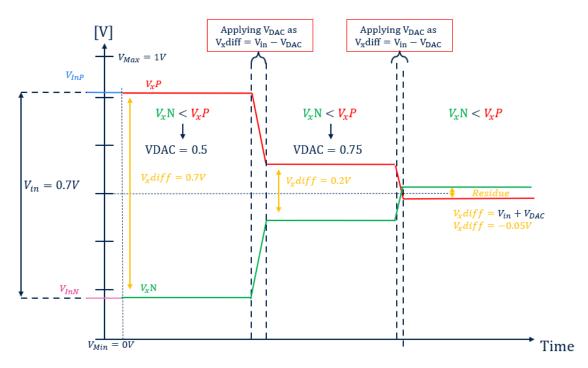

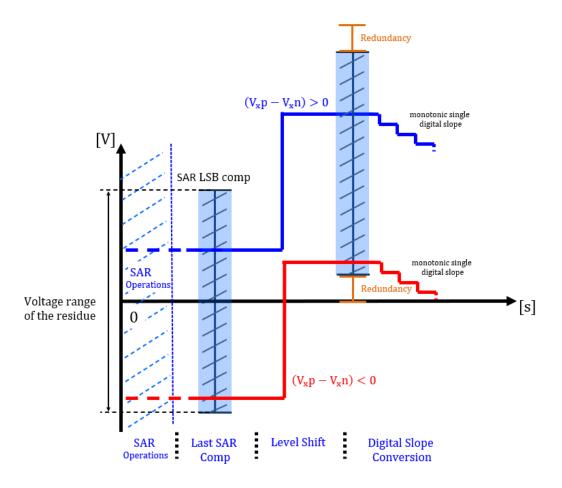

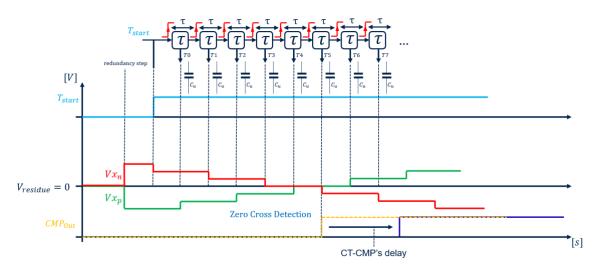

| Figure 31 - Example of second stage [3] digital slope time operation for positive and negative residue  | e58   |

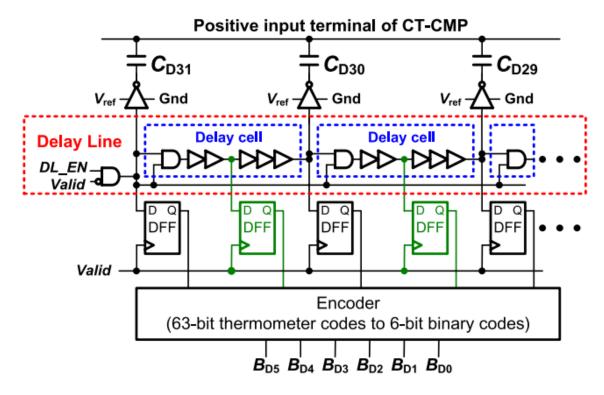

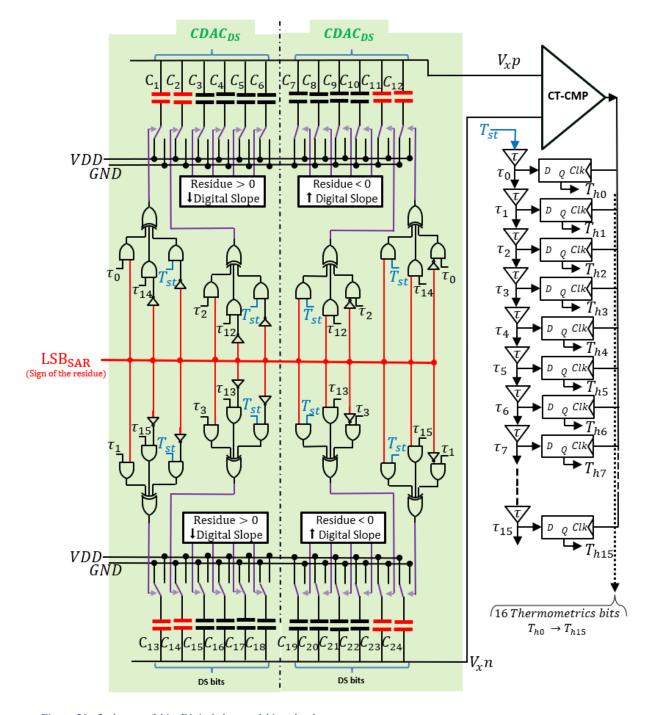

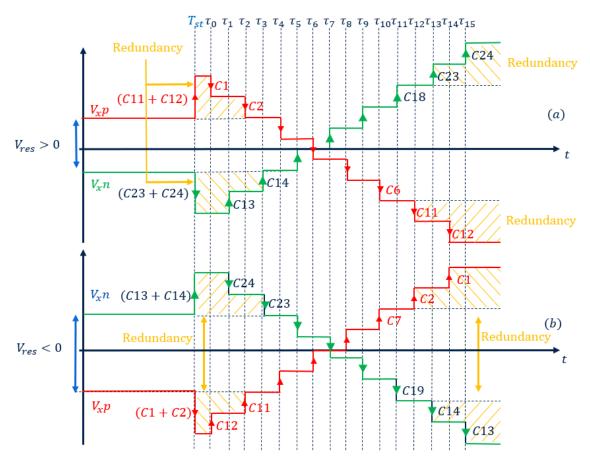

| Figure 32 - From [3], implementation of the 6-bit digital slope fine ADC                                |       |

| Figure 33 - General concept of the bi-directional digital slope SAR assisted ADC - 12 bit example       | 63    |

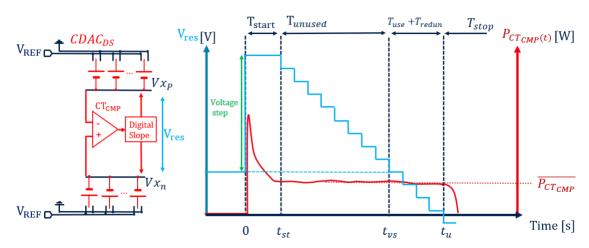

| Figure 34 - Representation of the comparator consumption for the second stage                           | 64    |

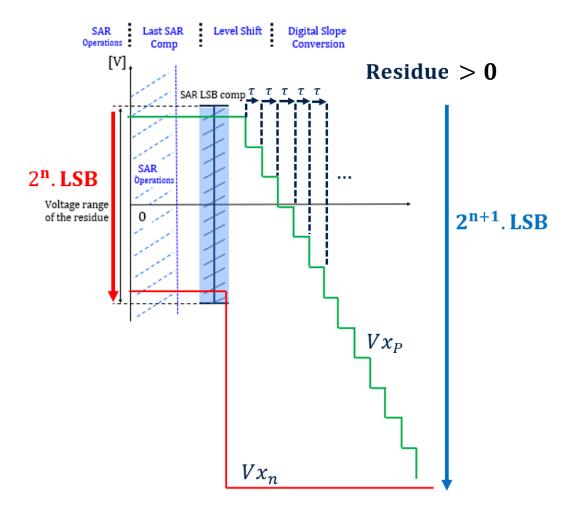

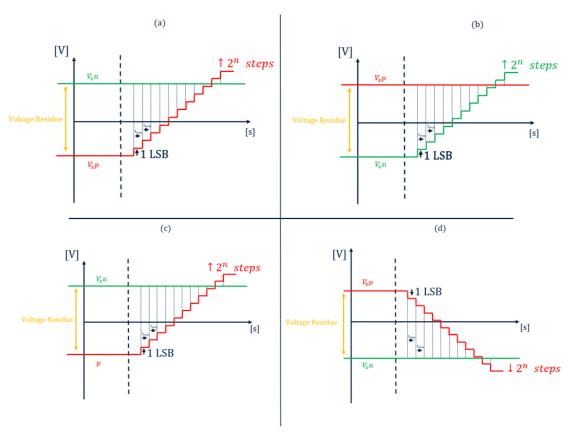

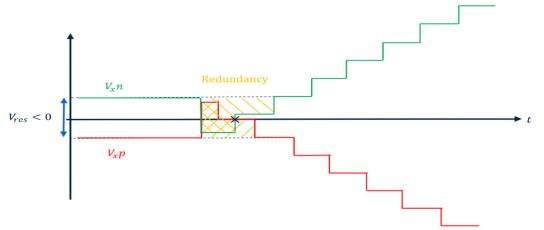

| Figure 35 - Illustration of 2 <sup>nd</sup> stage monotonic digital slope behavior for a residue > 065        |

|---------------------------------------------------------------------------------------------------------------|

| Figure 36 - different approaches of digital slope based on residue sign: double monotonic digital slope for   |

| a negative residue (a) and a positive residue (b) - single bidirectional digital slope for a negative residue |

| (c) and a positive residue (d)66                                                                              |

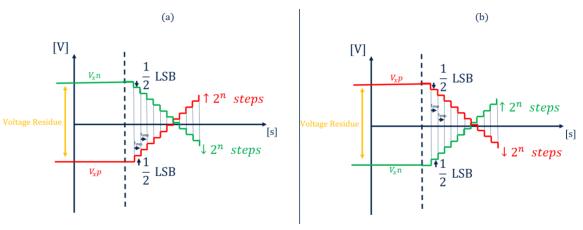

| Figure 37 - Time voltage diagram of a fully differential bidirectional digital slope for a negative residue   |

| (a) and a positive residue (b)                                                                                |

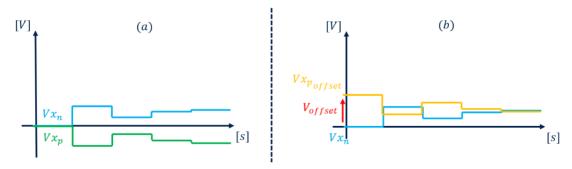

| Figure 38 - temporal voltage representation of proposed pseudo differential bidirectional digital slope for   |

| negative residue (a) and positive residue (b)                                                                 |

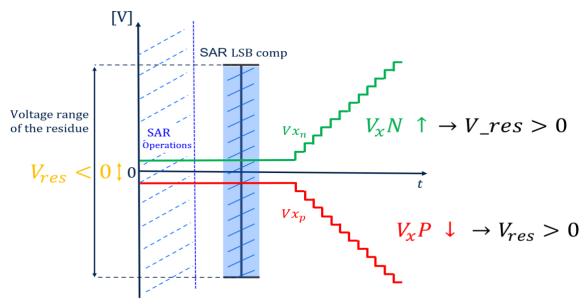

| Figure 39 - Temporal voltage representation of SAR sign error causing bidirectional digital slope             |

| divergence. (Negative voltage residue and positive sign behavior)69                                           |

| Figure 40 - Temporal voltage representation of SAR sign error corrected by 4 step redundancy. (Negative       |

| voltage residue and positive sign behavior)69                                                                 |

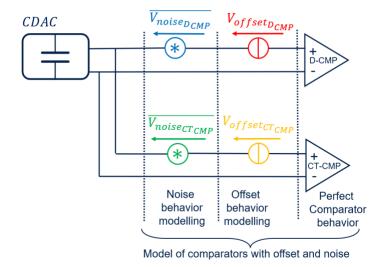

| Figure 41 - Systemic non idealities representation of the comparators in the proposed architecture70          |

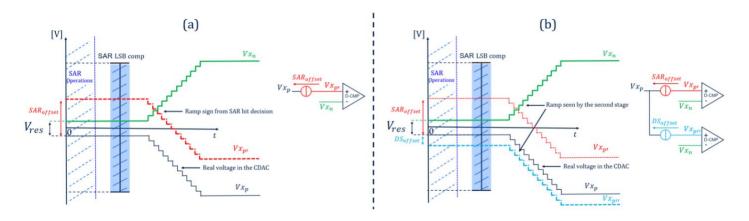

| Figure 42 - Temporal voltage representation of sign error due to offset. Wrong sign decision taken by the     |

| SAR (a) and ramps presented at the second stage comparator (b) compared to the voltage present in the         |

| CDAC (Vxp)71                                                                                                  |

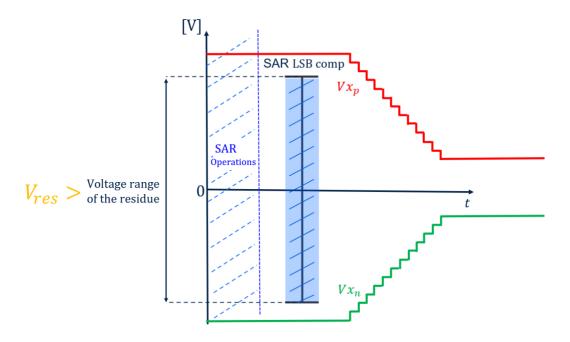

| Figure 43 - Bidirectional ramps through time for a voltage residue greater than the 2nd stage dynamic72       |

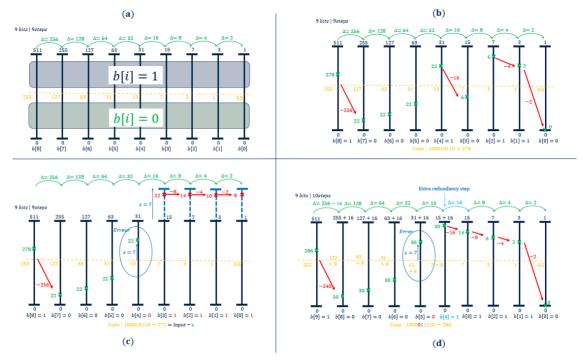

| Figure 44 - Representation of the voltage residue equivalent code through 9 bit SAR example process           |

| with, bit decision area (a), example of non-error conversion without redundancy (b), example of               |

| conversion with error without redundancy (c), and example of conversion with error and extra step             |

| redundancy on 6 <sup>th</sup> comparison to correct the code (d)                                              |

| Figure 45 - Proposed architecture with offset calibration dedicated CDAC- concept diagram block76             |

| Figure 46 - Representation of the voltage evolution in the proposed foreground calibration on the top plate   |

| of the CDAC (a) and seen by the comparator presenting offset (b)77                                            |

| Figure 47 - Representation of the second stage comparator latency compared to ideal output with               |

| bidirectional slope                                                                                           |

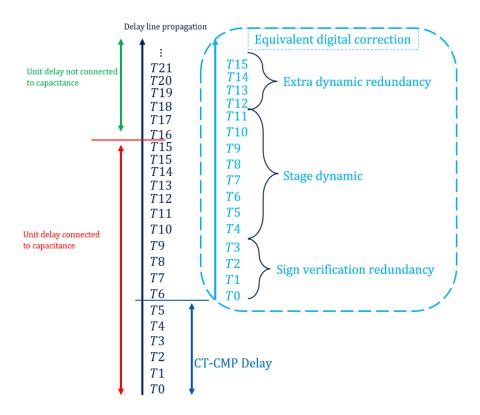

| Figure 48 - Timing diagram of the proposed delay measurement of the comparator using redundancy as            |

| expected result79                                                                                             |

| Figure 49 - 3 bit + 1 bit redundancy delay line equivalent thermometric code with proposed digital            |

| correction for 6T CT-CMP delay80                                                                              |

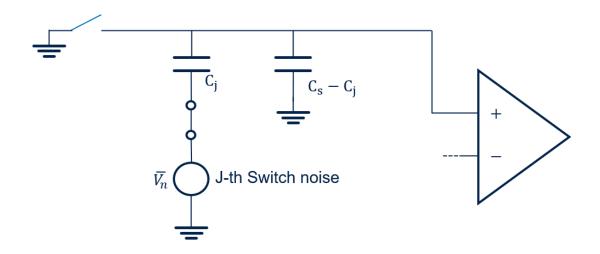

| Figure 50 - Noise model in CDAC based ADC in the evaluation phase with Cj capacitance switched                |

| amongst Cs capacitance used in the sampling phase82                                                           |

| Figure 51- From [87], energy consumption by conversion step of a strong-arm comparator as a function          |

| of its input referred noise. Simulated 5fF capacitive load in 65nm86                                          |

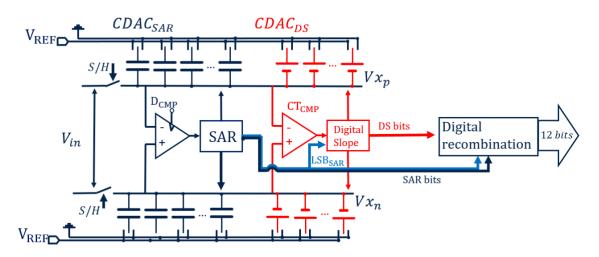

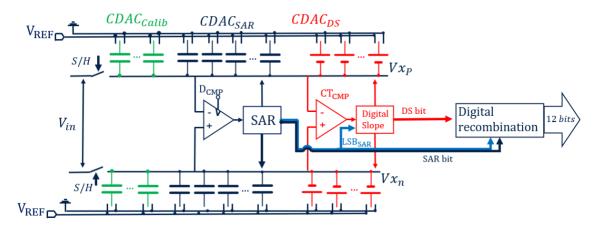

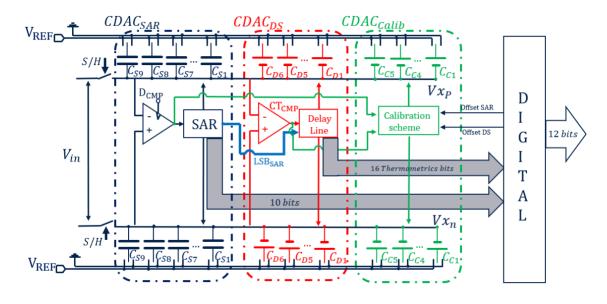

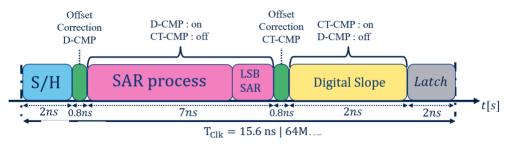

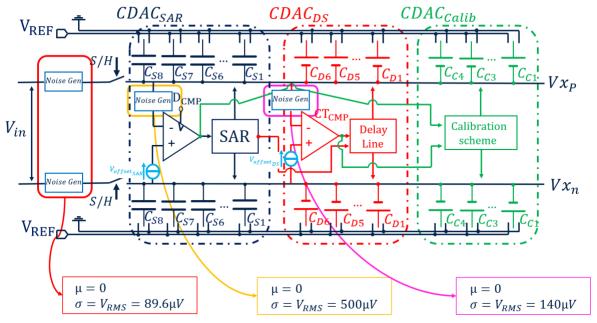

| Figure 52 - SAR-Assisted Two stages differential DS block schematic                                           |

| Figure 53 - Proposed ADC time sequence for 64MS/s90                                                           |

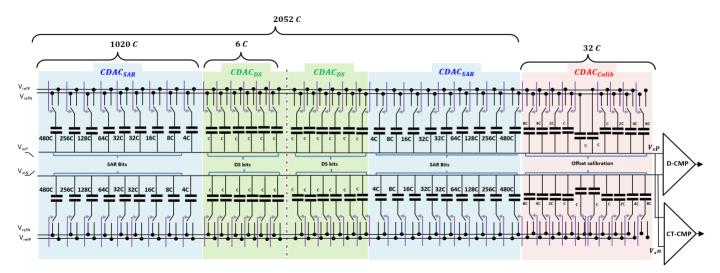

| Figure 54 - Bloc-level representation of the differential CDAC used in the ADC for SAR, TDC and               |

| calibration purpose. [VrefP = VDD; VrefN = GND]90                                                             |

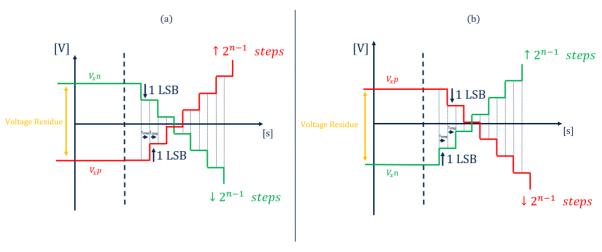

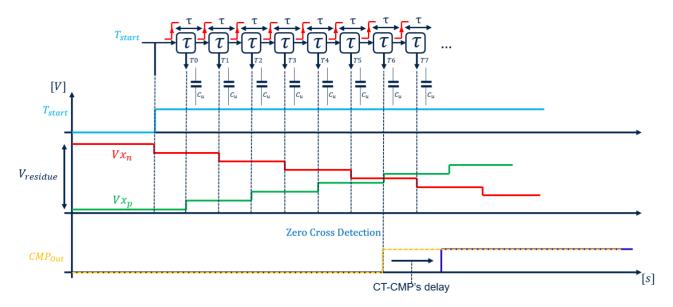

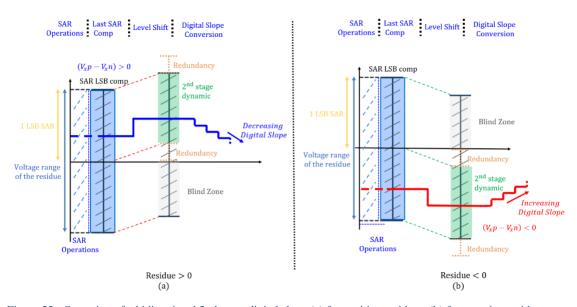

| Figure 55 - Operation of a bidirectional 2nd stage digital slope (a) for positive residue - (b) for negative  |

| residue92                                                                                                     |

| Figure 56 - 2nd stage: 3 bits Digital slope + 1 bit redundancy                                                |

| Figure 57 - 3 bit pseudo differential Digital Slope with redundancy (a) for positive residue (b) for          |

| negative residue94                                                                                            |

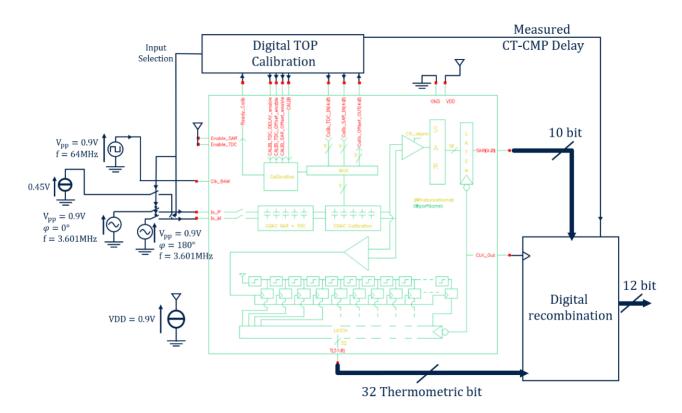

| Figure 58 - Representation of VerilogA model of the SAR-Assisted Two stages differential DS block             |

| schematic including noise, offset and calibration96                                                           |

| Figure 59 - Cadence VerilogA model cellview with block representation of the test bench simulated in          |

| Spectre 97                                                                                                    |

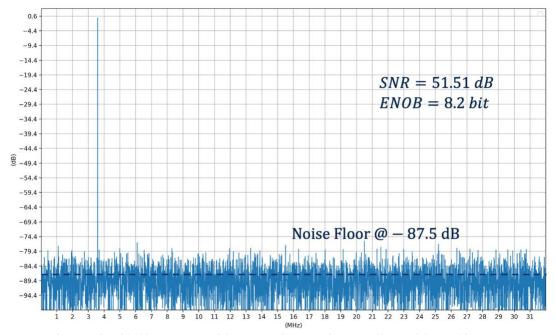

| Figure 60 - Simulated 8192 points FFT of the proposed ADC with noise, offset models - Calibratio                       | n OFF. |

|------------------------------------------------------------------------------------------------------------------------|--------|

|                                                                                                                        |        |

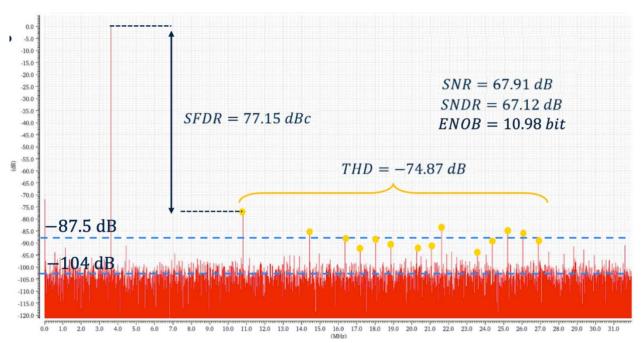

| Figure 61 - Simulated 8192 points FFT of the proposed ADC with noise, offset models and mismated draw) Calibration ON. |        |

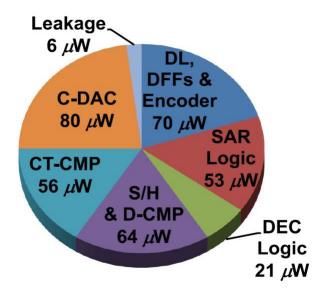

| Figure 62 - Power consumption breakdown measurements from [3]                                                          |        |

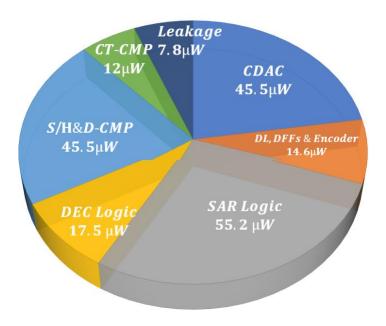

| Figure 63 - Extrapolated power consumption breakdown for SAR assisted bidirectional ADC from                           |        |

| measurements.                                                                                                          |        |

| Figure 64 - From figure 2.17 - From B.Murmann survey, energy efficiency depending on resolution                        |        |

| realizations close to the target including proposed work placed with extrapolated power consumption                    |        |

| performances                                                                                                           |        |

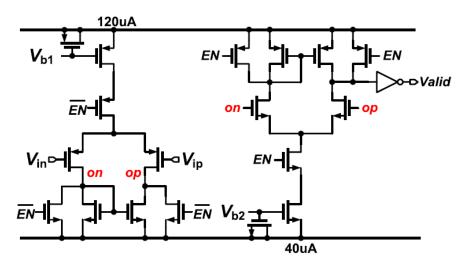

| Figure 65 - From [3], schematic of low noise low power CT-CMP                                                          |        |

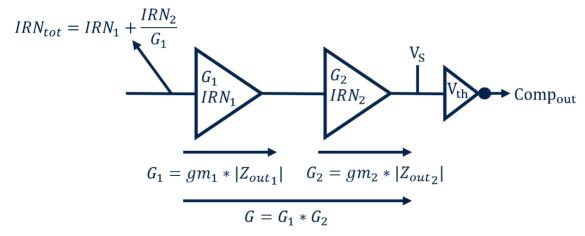

| Figure 66 - Block representation of two stages amplifier followed by an inverter cell                                  |        |

| Figure 67 - Design of 2 stages amplifier CT-CMP based on [3] and [73]                                                  |        |

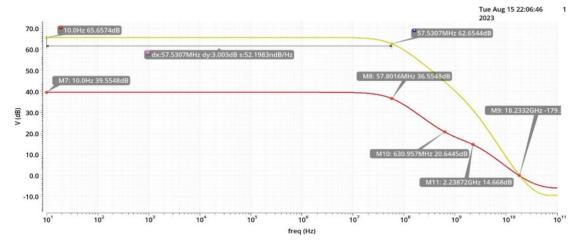

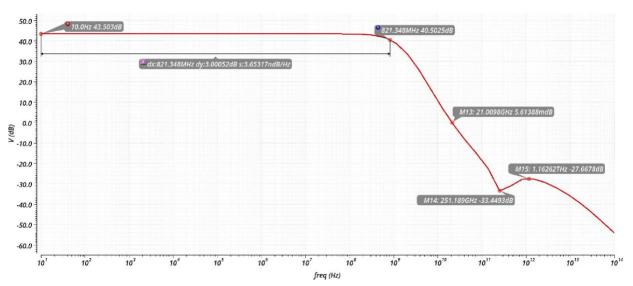

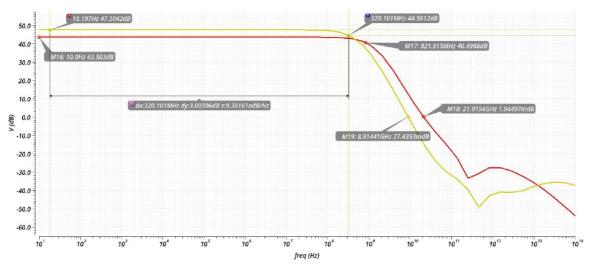

| Figure 68 - Transfer function of the 2-stage amplifier CT-CMP schematic (first stage transfer function)                |        |

| red / second stage transfer function - yellow) - no offset correction                                                  |        |

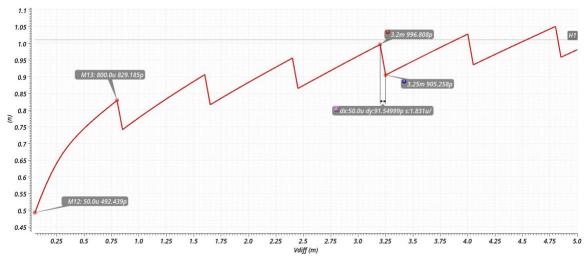

| Figure 69 - Simulated delay on the output caused by the CT-CMP (time compared between input cr                         |        |

| and output rising edge)                                                                                                |        |

| Figure 70 - (a) First order model of the CT-CMP - (b) Time domain response of the comparator for                       |        |

| input voltage ramp                                                                                                     |        |

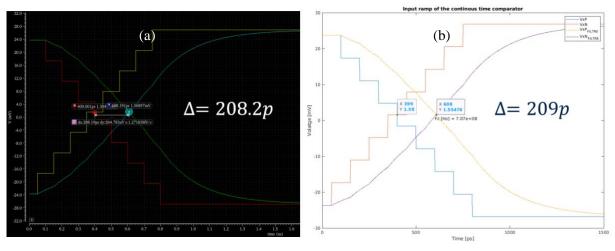

| Figure 71 - Cadence (a) and Matlab (b) simulation of first order model CT-CMP                                          |        |

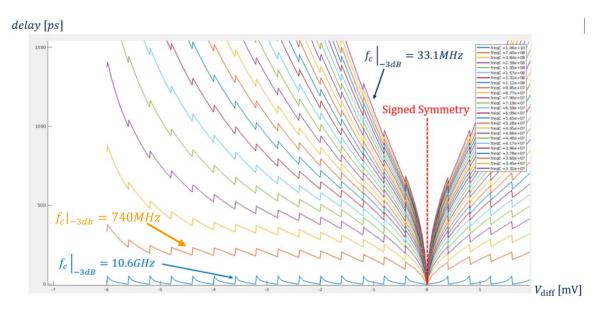

| Figure 72 - Delay simulated depending of the input for several bandwidth                                               |        |

| Figure 73 - Schematic of the proposed folded cascode CT-CMP to increase bandwidth                                      |        |

| Figure 74 - Transfer function of the proposed folded cascode CT-CMP - no offset correction                             | 117    |

| Figure 75 - Schematic of the proposed bias stage used to start-up the comparator                                       | 118    |

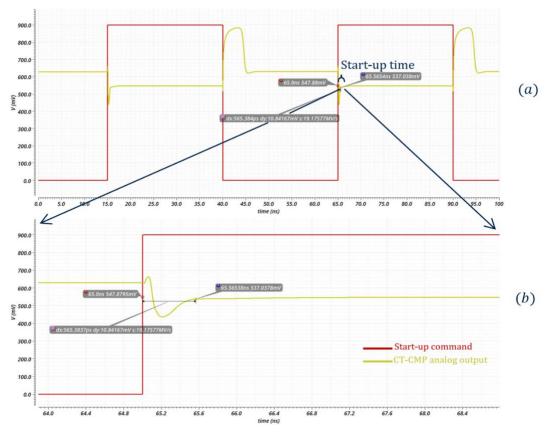

| Figure 76 - Timing diagram of the start-up command                                                                     | 119    |

| Figure 77 - (a) Sequence of start & stop to measure comparator timing - (b) Zoom on start-up                           |        |

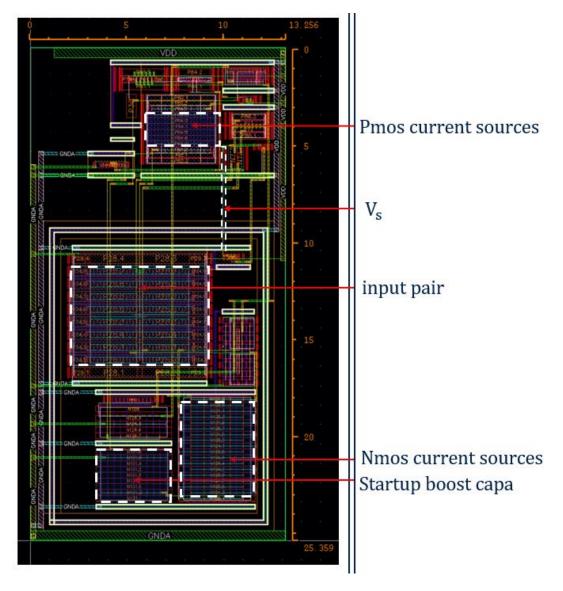

| Figure 78 - Layout of the folded cascode CT-CMP                                                                        | 122    |

| Figure 79 - Transfer function of the proposed folded cascode CT-CMP with schematic and RCc view                        | w - no |

| offset correction                                                                                                      |        |

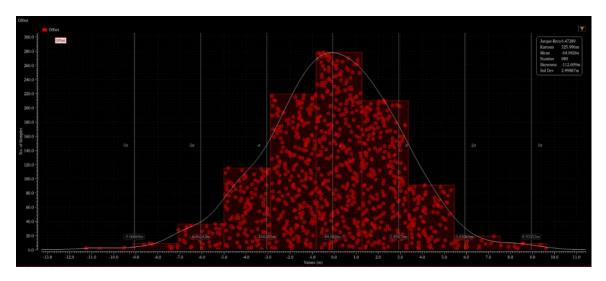

| Figure 80 - Offset Monte Carlo histogram simulation for RCc view - systematic offset corrected                         |        |

| Figure 81 - Temporal model representation of the input and output linearized of the CT-CMP for a g                     | given  |

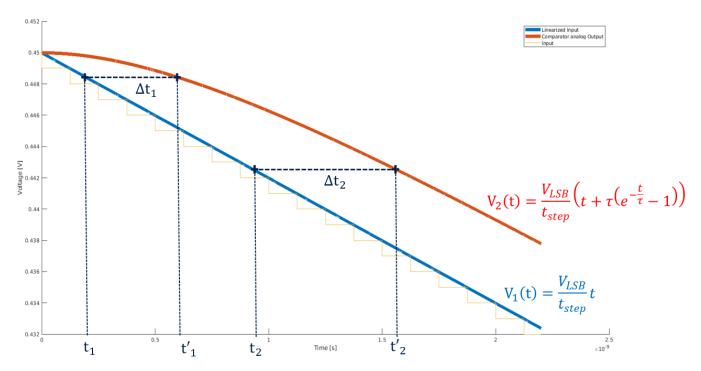

| bandwidth                                                                                                              |        |

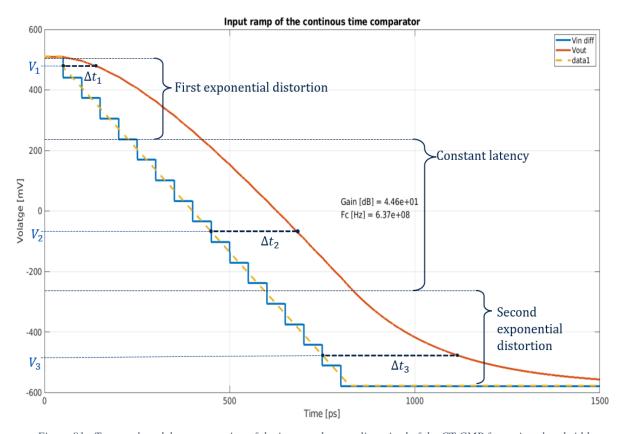

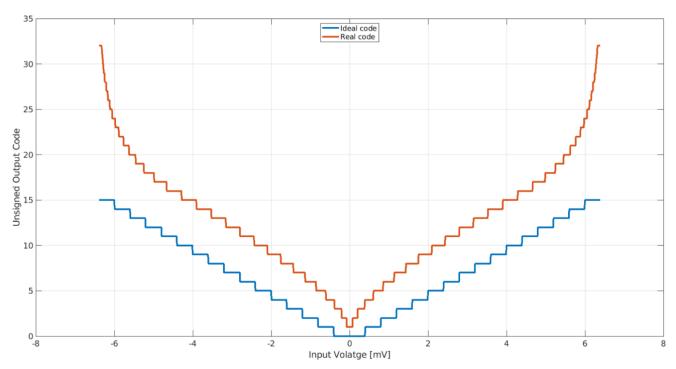

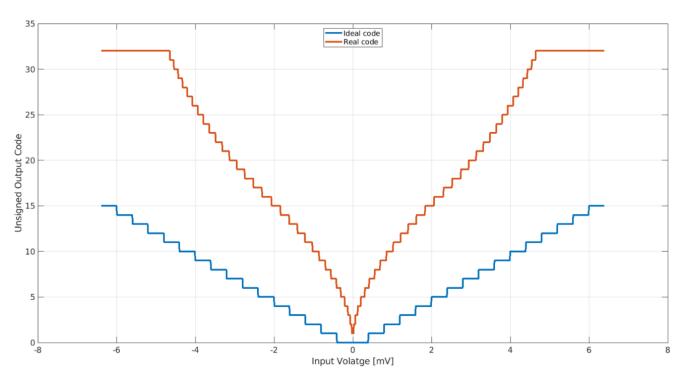

| Figure 82 - Simulated unsigned output code vs. ideal unsigned output code over the $\pm 4$ bit input ra                | _      |

| $(LSB = 400\mu V, BW = 637MHz, Timestep 50ps, 16 steps)$                                                               |        |

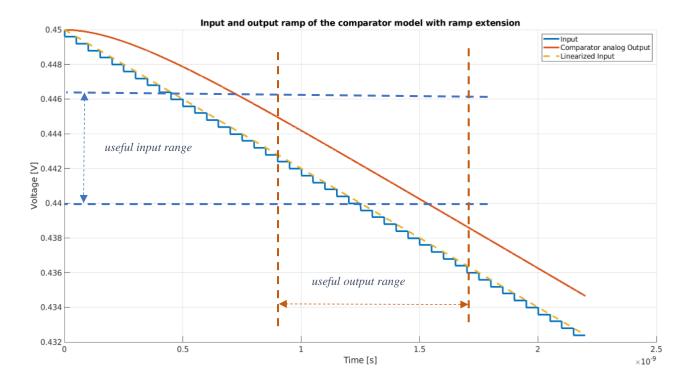

| Figure 83 - Temporal model representation of the input and output linearized of the CT-CMP for a g                     |        |

| bandwidth with ramp extension                                                                                          |        |

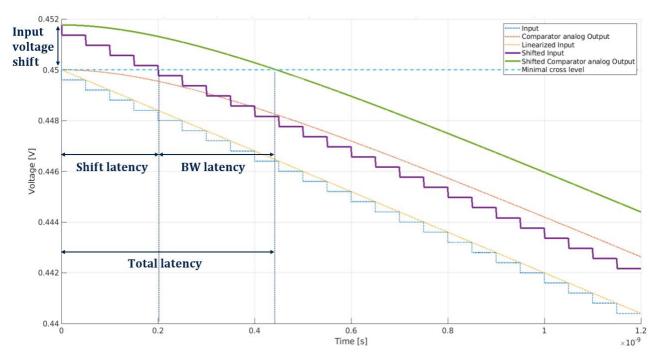

| Figure 84 - Temporal model representation of the input and output of the CT-CMP for a given band                       |        |

| with ramp extension and shifted input to compensate first distortion.                                                  |        |

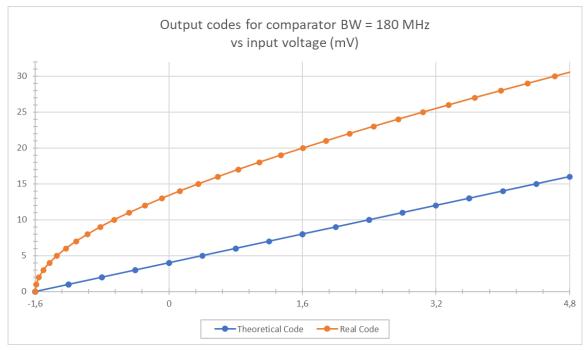

| Figure 85 - Simulated unsigned output code vs. ideal unsigned output code over the $\pm 4$ bit input ra                |        |

| (LSB = $400\mu$ V, BW = $180$ MHz, Timestep 50ps, 16 steps)                                                            |        |

| (LSB = $400\mu$ V, BW = $180$ MHz, Timestep 50ps, 32 ramp steps in total)                                              | •      |

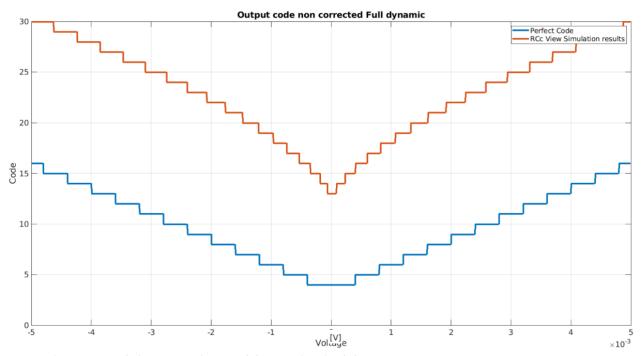

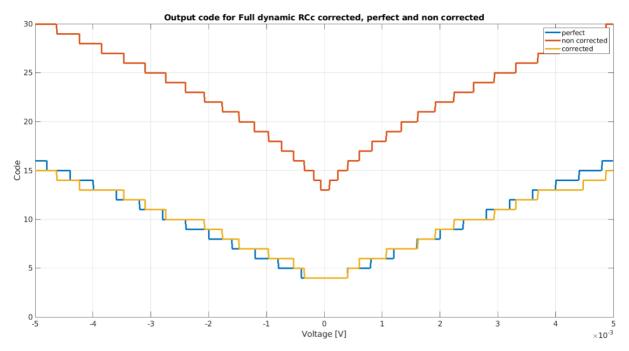

| Figure 87 - Output code for RCc simulation and theoretical perfect behavior                                            |        |

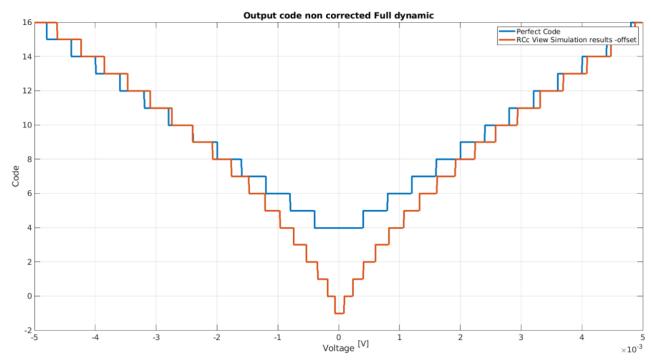

| Figure 88 - Output code for RCc simulation and theoretical perfect behavior                                            |        |

| behaviorbehavior                                                                                                       | •      |

|                                                                                                                        |        |

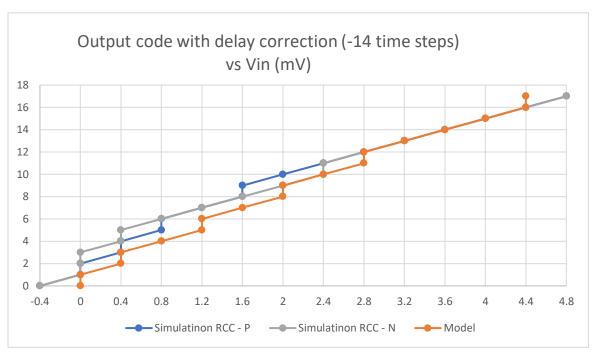

| Figure 89 - Output code for RCc simulation (corrected by a 14 step constant offset) and output code     |      |

|---------------------------------------------------------------------------------------------------------|------|

| predicted by mathematical model                                                                         | .138 |

| Figure 90 - Linearized model transient simulation                                                       | .139 |

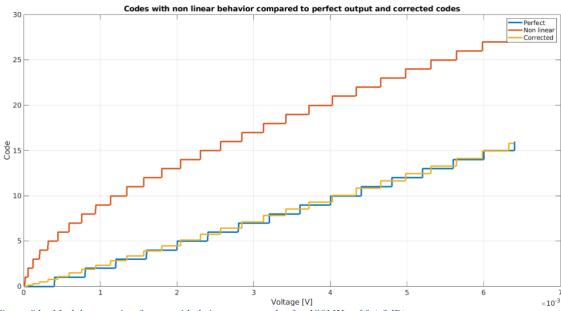

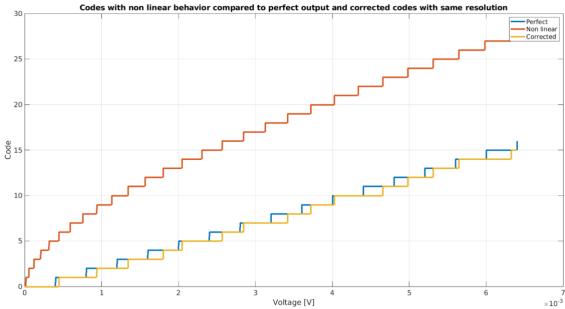

| Figure 91 - Model correction for one sided sign output codes for 180MHz of f_(-3dB)                     | .140 |

| Figure 92 - Model correction for one sided sign output codes for 180MHz of f_(-3dB) [quantized          |      |

| correction]                                                                                             |      |

| Figure 93 - Simulated results of RCc view with ramp extension and post digital correction compared to   |      |

| ideal output.                                                                                           | .141 |

|                                                                                                         |      |

| List of Tables                                                                                          |      |

|                                                                                                         |      |

| Table 1- Specifications of the aimed ADC for this work                                                  | 29   |

| Table 2 - Flash ADCs in the literature                                                                  |      |

| Table 3 - $\Sigma \Delta$ ADCs in the literature                                                        |      |

| Table 4 - Pipeline ADCs in the literature                                                               |      |

| Table 5 - Remarkable SAR ADCs in the literature                                                         |      |

| Table 6 - Detailed performances of highlighted pipelined SAR ADC realizations in Figure 22              |      |

| Table 7 - Detailed performances of highlighted NS SAR ADC realizations in Figure 25                     |      |

| Table 8 - Detailed performances of highlighted hybrid SAR-Time domain ADC realizations presented        |      |

| Figure 26                                                                                               |      |

| Table 9 - Summarize of simulated model performance compared to state of the art                         | .103 |

| Table 10 - Performances specification of the proposed CT-CMP                                            | .109 |

| Table 11 - Transistors sizing of CT-CMP 2 stage amplifier                                               | .111 |

| Table 12 - Transistor sizing of CT-CMP folded cascode architecture                                      | .116 |

| Table 13 - Transistors sizing of CT-CMP cascode bias/start stage                                        | .120 |

| Table 14 - Resume of comparators performances (2stage, folded with schematic and extracted views)       | - no |

| offset correction                                                                                       | .123 |

| Table 15 - Resume of comparators performances with offset correction (2stage, folded with schematic     |      |

| extracted views)                                                                                        |      |

| Table 16: Maximum value of measurable $\tau$ /t_step for ramps lengths of 16, 32 and 64 steps. From (5) | -    |

|                                                                                                         |      |

| Table 17 - Summarize of simulated model performance compared to updated state of the art                | .146 |

## **Scientific Production**

## **Related to the Thesis:**

### International Conference:

- J.-B. Casanova, D. Perrin, S. Nicolas and A. Kaiser, "A Very Low Power 12 bit 64-MS/s 2 step SAR Assisted Bidirectional Digital Slope ADC," 2023 IEEE International Symposium on Circuits and Systems (ISCAS), Monterey, CA, USA, 2023, pp. 1-5, doi: 10.1109/ISCAS46773.2023.10181656.

#### Patent:

- J.-B. Casanova, S. Nicolas, D. Perrin, "CAPACITANCE SWITCHING SCHEME FOR DIGITAL SLOPE ADC", Patent ID 83130816, Ref N° 22-GR2-0455FR01,2022.

## Non related to the Thesis:

### **International Conference:**

Nicolas Goux, Jean-Baptiste Casanova, Gaël Pillonnet, and Franck Badets. 2020. A 640pW 32kHz switched-capacitor ILO analog-to-time converter for wake-up sensor applications, ISLPED '20: Proceedings of the ACM/IEEE International Symposium on Low Power Electronics and Design. Association for Computing Machinery, New York, NY, USA, 43–48. https://doi.org/10.1145/3370748.3406582

### Journal:

- N. Goux, J.-B. Casanova, G. Pillonnet and F. Badets, "A 6-nW 0.0013-mm<sup>2</sup> ILO Bandpass Filter for Time-Based Feature Extraction," in *IEEE Solid-State Circuits Letters*, vol. 3, pp. 306-309, 2020, doi: 10.1109/LSSC.2020.3016716.

#### Patent:

- Franck Badets, **Jean-Baptiste Casanova**, "SUMMING CIRCUIT WITH MULTI INJECTION PHASE", Patent, EP21209011.2, US20220164632A1, 2021.

## **General Introduction**

Wireless devices have known a significant grown though past decades, specifically in terms of short-range communications. The exponential growth of devices aimed to communicate each other imposed new way to consider emission and reception of data. The authorized frequency being clearly delimited in each continent put every communicating device in a narrow crowdy spectral area. The design and the legislation around the communicating system became more and more aggressive through years, specifically to transfer more data, faster while consuming less energy. The minimal power of signal to detect has also been set lower through years as the maximum signal emitted became stronger. This in a context with several devices communicating together makes severe constraints on receiver circuits.

In the context of wireless communication, the receiver is a system composed of several subsystems. The antenna, the analog front-end, the analog to digital conversion and the digital signal processing functions are all at least required to receive and process wireless data. All these functions interact with each other and are considered to reach targeted performances. In the context of SoC (System on Chip) receiver the considerations can be different. In ST Microelectronics, wireless telecommunicating devices are developed on SoC with both receiver and transceiver functions. The complexity and interactions of each function is thus increased as for the power management or the clock generation. The power consumption also become a challenge to present a competitive industrial product.

This manuscript is the result of a CIFRE PhD program from a collaboration between STMicroelectronics, Grenoble, France and the IEMN Laboratory at the University of Lille, France. This thesis aims to address industrial challenges in analog to digital converter design, notably the continuous demand on reduction of the power consumption. The context of the work is the future industrial development of advanced radio frequency devices similar to those in the Spirit [1] or BlueNRG [2] product portfolios for sub-gigahertz and Bluetooth short range radios from STMicroelectronics.

The analog to digital conversion functions represents a key parameter for the performance of the global receiver functions. Indeed, the analog front-end parameters such as gain, or noise can be alleviated by the ADC (Analog to digital converter) performances. The targeted performances for this work have been identified in a 12 bit 64MS/s ADC presenting a power consumption below 300µW. The possibility to present two modes of functioning is also required. A high precision mode presenting the discussed performances and a lower power mode presenting at least 9 bit for the same sampling frequency.

This manuscript presents an enhanced ADC topology targeted to fulfill these industrial requirements while presenting sufficient performances to relax future generations of front ends in SoC receivers. The objectives of this work can be summarized as:

- Find an architecture able to fulfill the targeted ADC requirements.

- Develop a resilient architecture sized for industrial requirements.

- Propose an architecture with modularity by having two modes of functioning.

- Reduce power consumption.

- Reduce the required area.

The study starts with an analysis of the ADC impact on the receiver analog front-end. The targeted specifications are then detailed before a state-of-the-art survey. The state-of-the-art analysis starts with the most widely used architectures compared to the targeted specifications. Hybrid topologies are also discussed, and the analysis converges to a SAR Digital Slope hybrid ADC. This architecture looks the most promising and after an analysis of the strength and the weakness of the hybrid topology, an improvement is proposed.

The proposed ADC presents a new way to execute the second stage processing with a pseudo differential approach. The bidirectional ramps proposed in this work enable the second stage to convert its input in a time twice shorter compared to the existing method. Because the consumption of this stage is linear with its time on converting, the proposed architecture divides power consumption of the second stage by two. The proposed architecture is conceptually detailed with offset and latency calibration as with built-in redundancy to correct internal errors. The VerilogA model used to implement the ADC is then discussed before presenting the result simulated confirming the theoretical sizing of the ADC. The power consumption extrapolated from [3] with an arbitrary 30% of margin allows to compare the proposed ADC favorably with state of the art.

The present manuscript is organized in 5 chapters as:

- Chapter 1: This first chapter presents the discussion between analog front end performances and ADC performances. It allows to underline the importance of sampling frequency and resolution in the global receiver design.

- Chapter 2: This chapter presents a survey of the state of the art in ADC realizations.

Main topologies as SAR, pipeline or oversampled structures are discussed. The classical

structures being too far of the target of this work, hybrid architectures are discussed, mainly with SAR topology. The most interesting realizations are discussed in detail and converge to SAR assisted topology with Digital Slope second stage.

- Chapter 3: The third chapter presents the proposed ADC topology. A structural presentation is first given with theoretical considerations and interactions. Then the sizing of the proposed ADC is detailed before the model implementation. The VerilogA model is presented as the simulation results obtained with it. An extrapolation of the power consumption from [3] is detailed.

- Chapter 4: This chapter provides information on the designed CT-CMP used in the

proposed second stage. This design has been done in a 18nm node to validate second

stage implementation. Schematic and post-layout results are presented, then the impact of

parasitic degrading the bandwidth of the comparator is discussed as its impact on the

system.

- Chapter 5: The last chapter presents methods to overcome the low bandwidth impact.

Methods from state of the art are presented as their weakness about low power design. A

new post digital correction is detailed theoretically then applied to previous post layout

results to show digital improvements without extra consumption.

# Introduction générale (Français)

Les dispositifs sans fil ont connu une croissance significative au cours des dernières décennies, notamment en termes d'objets communicants à courte portée. La croissance exponentielle des dispositifs destinés à communiquer entre eux a imposé une nouvelle manière de considérer l'émission et la réception de données. La fréquence autorisée étant clairement délimitée sur chaque continent, chaque dispositif communicant se retrouve dans un espace fréquentiel étroit et encombré. La conception et la réglementation autour du système de communication sont devenues de plus en plus agressives au fil des ans, notamment pour transférer plus de données, plus rapidement, tout en consommant moins d'énergie. La puissance minimale du signal à détecter a également été réduite au fil des ans, tandis que le signal maximal émis est devenu plus fort. Dans un contexte où plusieurs dispositifs communiquent ensemble, cela impose des contraintes sévères sur les circuits récepteurs.

Dans ce contexte des communications sans fil, le récepteur est un système composé de plusieurs soussystèmes. L'antenne, le front-end analogique, la conversion analogique-numérique et les fonctions de traitement numérique du signal sont tous au moins nécessaires pour recevoir et traiter les données sans fil. Toutes ces fonctions interagissent les unes avec les autres et sont dimensionnées pour atteindre les performances ciblées. Dans le contexte d'un récepteur SoC (System on Chip), les considérations peuvent être différentes. Chez ST Microelectronics, les dispositifs de télécommunication sans fil sont développés sur SoC avec à la fois des fonctions de réception et de transmission. La complexité et les interactions de chaque fonction sont ainsi augmentées, tout comme la gestion de l'alimentation ou la génération de l'horloge. La consommation d'énergie devient un défi pour présenter un produit industriel compétitif.

Ce manuscrit est le résultat d'un programme de doctorat CIFRE issu d'une collaboration entre STMicroelectronics, Grenoble, France et le Laboratoire IEMN de l'Université de Lille, France. Cette thèse vise à relever les défis industriels liés à la conception de convertisseurs analogique-numérique, notamment dans ce contexte de demande continue de réduction de la consommation d'énergie. La projection de ce travail est le développement industriel futur de dispositifs radiofréquences avancés similaires à ceux des portefeuilles de produits Spirit ou BlueNRG pour les radios sub-gigahertz et Bluetooth à courte portée de STMicroelectronics.

La fonction de conversion analogique-numérique représente un paramètre clé pour les performances des fonctions globales du récepteur. En effet, les paramètres du front-end analogique tels que le gain ou le bruit peuvent être atténués par les performances de l'ADC (convertisseur analogique-numérique). Les performances ciblées pour ce travail ont été identifiées dans un ADC de 12 bits à 64 MS/s présentant une consommation électrique inférieure à 300  $\mu$ W. La possibilité de présenter deux modes de fonctionnement est également requise. Un mode haute précision présentant les performances discutées et un mode basse consommation présentant au moins 9 bits pour la même fréquence d'échantillonnage.

Ce manuscrit présente une topologie d'ADC améliorée visant à répondre à ces exigences industrielles tout en présentant des performances suffisantes pour simplifier les futures générations de front-ends dans les récepteurs SoC. Les objectifs de ce travail peuvent être résumés comme suit :

- Trouver une architecture capable de répondre aux exigences ciblées de l'ADC.

- Développer une architecture résiliente adaptée aux exigences industrielles.

- Proposer une architecture avec une modularité en ayant deux modes de fonctionnement.

- Réduire la consommation d'énergie.

- Réduire la surface requise.

L'étude commence par une analyse de l'impact de l'ADC sur le front-end analogique du récepteur. Les spécifications ciblées sont ensuite détaillées avant une étude de l'état de l'art. L'analyse de l'état de l'art commence par les architectures les plus largement utilisées comparées aux spécifications ciblées. Les topologies hybrides sont également discutées, et l'analyse converge vers un ADC hybride SAR Digital Slope (pente numérique). Cette architecture semble la plus prometteuse et après une analyse des forces et des faiblesses de la topologie hybride, une amélioration est proposée.

L'ADC proposé présente une nouvelle façon d'exécuter le traitement du deuxième étage à pente numérique avec une approche pseudo différentielle. Les rampes bidirectionnelles proposées dans ce travail permettent au deuxième étage de convertir son entrée en un temps deux fois plus court par rapport à la méthode existante. Comme la consommation de cet étage est linéaire avec son temps de conversion, l'architecture proposée divise la consommation électrique du deuxième étage par deux. L'architecture proposée est détaillée conceptuellement avec une calibration des décalages et des latences ainsi qu'une redondance intégrée pour corriger les erreurs internes. Le modèle VerilogA utilisé pour implémenter l'ADC est ensuite discuté avant de présenter les résultats simulés confirmant le dimensionnement théorique de l'ADC. La consommation électrique extrapolée à partir de [3] avec une marge arbitraire de 30 % permet de comparer favorablement l'ADC proposé avec l'état de l'art.

Le présent manuscrit est organisé en 5 chapitres :

- Chapitre 1 : Ce premier chapitre présente la discussion entre les performances du front-end analogique et les performances de l'ADC. Il permet de souligner l'importance de la fréquence d'échantillonnage et de la résolution dans la conception globale du récepteur.

- Chapitre 2 : Ce chapitre présente une étude sur l'état de l'art des réalisations d'ADC. Les principales topologies telles que SAR, pipeline ou les structures suréchantillonnées sont discutées. Les structures classiques étant trop éloignées de la cible de ce travail, les architectures hybrides sont étudiées, principalement avec la topologie SAR. Les réalisations les plus intéressantes sont présentées en détail et convergent vers la topologie assistée SAR avec deuxième étage à pente numérique.

- Chapitre 3 : Le troisième chapitre présente la topologie de l'ADC proposée. Une présentation structurelle est d'abord donnée avec des considérations théoriques et le détail de ses interactions. Ensuite, le dimensionnement de l'ADC proposé est présenté avant l'implémentation du modèle. Le modèle VerilogA est détaillé ainsi que les résultats de simulation obtenus avec lui. Une extrapolation de la consommation électrique à partir de [3] est explicitée.

- Chapitre 4 : Ce chapitre fournit des informations sur le comparateur temps continu (CT-CMP) conçu et utilisé dans le deuxième étage proposé. Cette conception a été réalisée avec une technologie 18nm SOI pour valider l'implémentation du deuxième étage. Les résultats schématiques et post-extracts sont présentés, puis l'impact des parasites dégradant la bande passante du comparateur est discuté ainsi que son impact sur le système.

- Chapitre 5 : Le dernier chapitre développe des méthodes pour surmonter l'impact de la faible bande passante. Les méthodes de l'état de l'art sont présentées ainsi que leurs faiblesses en matière de conception à faible consommation d'énergie. Une nouvelle correction post-digitale est détaillée théoriquement puis appliquée aux résultats précédents en post-traitement pour montrer des améliorations numériques sans consommation supplémentaire.

# Chapter 1

# **RX chain & ADC**

| 1.1 R   | F-RX CHALLENGES                          | 21 |

|---------|------------------------------------------|----|

|         | CHALLENGES IN RX FRONT-END DEVELOPMENT   |    |

| 1.2 A   | DC IN RF RECEIVER CHAIN                  | 23 |

| 1.2.1   | ADC KEY PARAMETERS                       | 23 |

| 1.2.2   | INTERACTION BETWEEN ADC AND RX FRONT END | 25 |

| 1.2.3   | ADC Specifications                       | 27 |

| 1.3 SI  | URVEY OF ADC STATE OF THE ART            | 29 |

| 1.3.1 N | METRICS AND TOOLS TO COMPARE             | 29 |

| 1.3.2   | GRAPHS AND ARCHITECTURES                 | 30 |

## 1.1 RF-RX Challenges

### 1.1.1 Challenges in RX front-end development

Over the past years the number of connected devices has grown exponentially through massive use in domestic, industrial, and urban networks. This forces receiver circuits to handle a crowdy spectral environment and coexistence of multiple systems and networks has become a major concern. Receiver circuits are mainly composed of a mostly analog RF front-end and a digital core for baseband processing. Naturally, the interface between these two functions, the analog-to-digital converter is of key importance for the receiver performances. A RF front end is usually composed of analog blocks dedicated to a particular application or protocol. The data converter must also be sized coherently to optimize the global power efficiently. If the performances are not matched, the overdesigned sections will consume unnecessary energy. The context of this work are applications such as Sub-Ghz and Bluetooth short range radio communications for IoT requiring high performance and low power. The specifications of the different blocks are thus determined by these applications [4]. The converter is a key parameter to reach global performance and system optimization [5]. This global streamlining is possible thanks to the dedicated application unlike approaches such as software defined radio for example. A receiver addressing a wide range of protocols cannot be sized in an optimal way for a specific application and requires extremely high ADC performance [6].

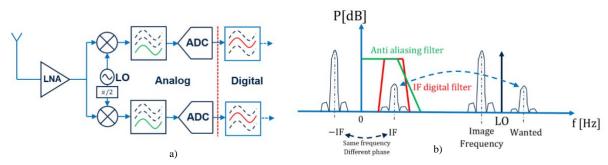

Figure 1-a) Block diagram of mixed analog-digital super-heterodyne receiver b) Spectrum representation of signal before and after down conversion

For every wireless system like mobile phone, broadcasting, radioastronomy, etc. a strictly defined frequency band is given. From a transmitter perspective this means to not emit outside this band, and from a receiver perspective, this means that signals received outside the limits should not be processed. To achieve such selective reception, a well-known architecture is the super-heterodyne receiver. The wanted signal is amplified then split in two orthogonal branches downconverted from the RF carrier frequency to an intermediate frequency (IF) [7]. It is a choice to have an IF different of 0 (Zero

IF structure), this alleviates the requirements and the processing of offset along the reception chain. The purpose of downconverting the signal is to avoid the system working at high frequency. The system presents then a baseband analog section consuming less energy and with relaxed constraints. However, down conversion performs by construction a spectrum folding (Figure 1), i.e. two frequency bands are translated to the same IF frequency band. Signals in the unwanted frequency band would be superimposed to the wanted signal and treated by the rest of the circuit. The two branches representing imaginary and real part of the signal (called respectively I & Q) allow the digital part of the system to suppress the image frequency folded on the wanted signal thanks to phase difference. Nevertheless, the ADC presents also down-conversion behavior around its sampling frequency (Shannon theorem) thus an antialiasing filter is then required before the analog to digital conversion. This increases area and power consumption.

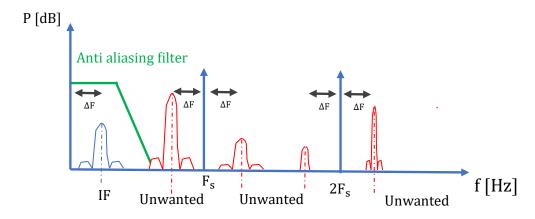

As mentioned above, the sampling process of the ADC input signal also down-converts signals in the bands around the multiples of the sampling frequency to the baseband. Unwanted signals can thus be super-imposed to the wanted signal through the conversion. An anti-aliasing filter is thus required to suppress high frequency signals before the sampling as represented in Figure 2. In the targeted systems, the sampling frequency is higher than the IF and the signal bandwidth. The antialiasing filter allows thus to reduce unwanted signal in band and to avoid frequency folding on the wanted signal. There is a trade-off between the IF and the sampling frequency, as shown in Figure 2 representing the first and second Nyquist respect to a multiple of the sampling frequency will be down converted to IF frequency. The first unwanted signal that could be down converted on the band of interest is therefore located at Fs-IF. That means that the closer the IF is to half the sampling frequency, the more the antialiasing filter needs to be be selective [8]. The sampling frequency is a key parameter to reduce antialiasing filter constraints.

Figure 2 - Representation of frequency sampling and mirror frequency on first and second Nyquist

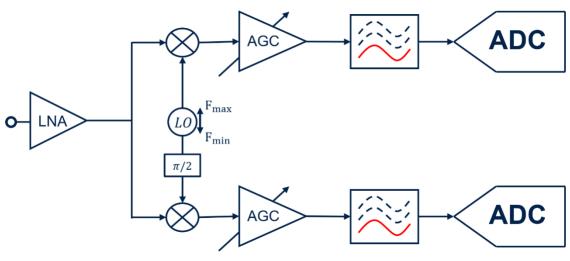

Furthermore, the RF receiver chain is a system with high level of interdependencies between the different blocks. Key parameters are gain, noise, non-linearity and power-consumption. The receiver frontend is shown on Figure 3. This work addresses the tradeoff between front-end constraints and ADC performance by proposing a new low power ADC sized for RX chain requirement. Obviously, solutions must be reliable, reproducible and resilient with small area.

Figure 3 – Bock diagram of a superheterodyne receiver frontend

# 1.2 ADC in RF receiver chain

### 1.2.1 ADC key parameters

In a simplified approach, an analog to digital converter (ADC) is a linear transformer from analog signals such as voltage or current to the digital domain. The conversion is as foretold cadenced by a sampling frequency  $F_s$  with a given resolution defined by the minimal fraction of analog signal that can be discriminated called the quanta q. Consequently, a signal  $S_n + \varepsilon$  should be converted at  $S_n$  as long as the relation  $-\frac{q}{2} \le \varepsilon \le \frac{q}{2}$  is verified. If the quantization error  $\varepsilon$  can be seen as uniformly distributed across the quantization interval, the mean-squared value of  $\varepsilon$  will then be:

$$E(\varepsilon^2) = \frac{1}{q} \int_{-\frac{q}{2}}^{\frac{q}{2}} \varepsilon^2 d\varepsilon \tag{1.1}$$

From equation (1.1), it is commonly admitted to define the rms quantization error voltage as  $e_{qns}^2 = E(\varepsilon^2)$ . By solving the integral, we can define:

$$e_{qns}^2 = \frac{1}{12}q^2 \tag{1.2}$$

Because an ADC is an amplitude quantized system using n binary weighted bits quantization levels, in the case of a large pure sine signal, its maximum peak-to-peak amplitude can be defined as:

$$A_{pp_{max}} = 2^n q \tag{1.3}$$

With equation (1.2) and (1.3) the maximum signal to quantization noise ratio can be expressed in linear domain and in decibels as:

$$SNR_{RMS} = 2^n \sqrt{1.5} \rightarrow SNR = (n * 6.02 + 1.76) dB$$

(1.4)

Other noise sources in the conversion process contribute degrade the SNR from its theoretical value. From a general point of view, the SNR is described as:

$$SNR = 20.\log\left(\frac{S}{N}\right)dB\tag{1.5}$$

With S being the RMS value of the maximum signal and N representing the total RMS noise power including the quantization noise. Furthermore, the converter also presents non-linearities impacting the signal integrity. Non-linearity create spurious signals in the converted spectrum. It is commonly admitted that the total harmonic distortion (THD) allows to appreciate the non-linearity of a converter. This parameter is obtained by a FFT spectrum analysis of the converter output for a pure sine input. With a pure sine input, only the fundamental tone of the sine must be visible, but the non-linearity induced by the ADC create harmonics of the input. The definition of the THD is then:

$$THD = 10 \log \left( \frac{A_F^2}{A_{H2}^2 + A_{H3}^2 + A_{H4}^2 + \cdots} \right) dB$$

(1.6)

With  $A_F^2$  representing the power of the fundamental tone and  $A_{Hx}^2$  representing the power of the  $x^{th}$  harmonics. Combining SNR and THD allows to define a global performance parameter called the signal to noise and distortion ratio (SNDR) as:

$$SNDR = -10\log\left(10^{-\frac{SNR}{10}} + 10^{-\frac{THD}{10}}\right)dB \tag{1.7}$$

The SNDR measures the ratio of the power of wanted signal and the power of all unwanted signals. This parameter gives a good indication of the overall performance of an ADC. The value of the SNDR can be expressed as an equivalent number of bits:

$$ENOB = \frac{SNDR - 1.76}{6.02} \tag{1.8}$$

The ENOB allows to express the performance of an ADC by expressing the SNDR in the same domain as the main specification of an ADC, i.ex. the theoretical resolution expressed as the number of bits.

### 1.2.2 Interaction between ADC and RX front end

From the discussion above it has been discussed qualitatively the implications between sampling frequency and filtering, the correlation between gain and SNR, this section goes more deeply into dimensioning the RX front-end taking account the ADC parameters.

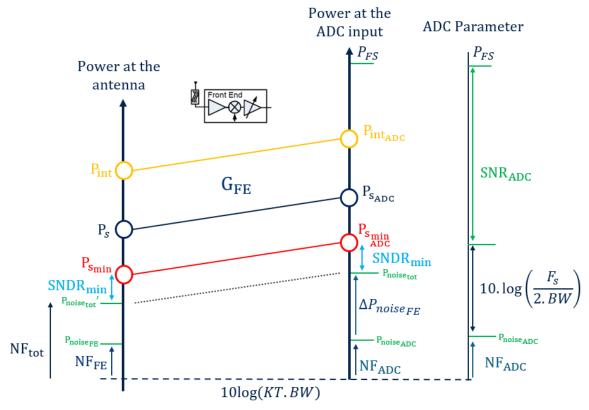

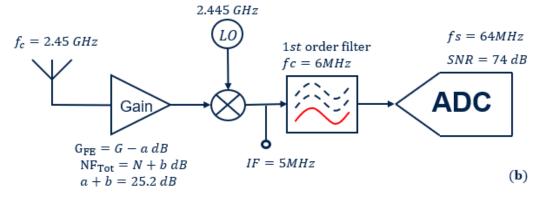

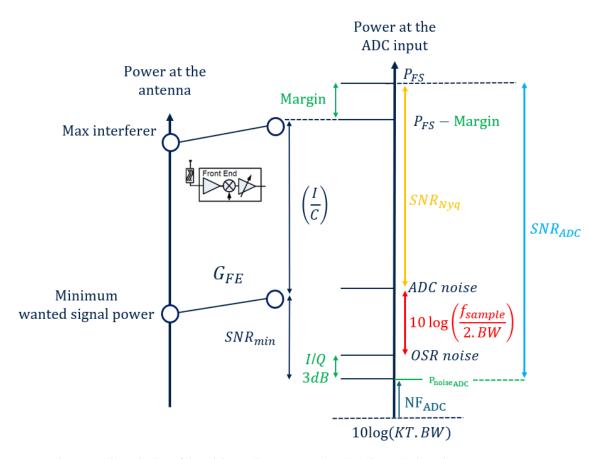

Figure 4 – Inspired from [9] Receiver signal, noise flow diagram and ADC parameter

Figure 4 shows the transcription of parameters as SNDR from the ADC to the receiver chain [9]. On the left of the figure is drawn the power presented at the antenna with different notable values. The example of the Figure 4 presents a interferer power, the wanted signal power and the minimum power accepted by the system  $(P_{Int}, P_s, P_{s,min})$ . The NF of the front-end is brought back to the antenna and

scaled with the thermal noise of the antenna, which allows to represent the power of noise induced by the analog front end  $(NF_{FE}, P_{noise_{FE}})$ . After gain consideration  $(G_{FE})$ , the power of different input components are represented at the input of the ADC. The noise added by the ADC  $(NF_{ADC})$  is represented from the thermal noise and added to the noise brought by the front end to obtain total noise  $(P_{noise_{tot}})$ . A minimal SNDR is given by the digital section of the system regarding the protocol and BER targeted  $(SNDR_{min})$ .

This kind of translation admits that noises are uncorrelated, but it allows to dimension the chain in term of noise figure (NF), and gain. By construction ADC are highly linear blocks, the challenges for the chain regarding the IP3 and linearity consideration for example are for block above ADC. But to dimension the gain of the chain for a given minimal power at the antenna, the SNR of the ADC is key parameter as translated to the  $NF_{ADC}$ . Increasing the SNR of the ADC can allow to relax the NF or to reduce the gain of the front-end chain or a mix of both. Careful system level design and optimization of the system is required to minimize the power consumption of the RX front end.

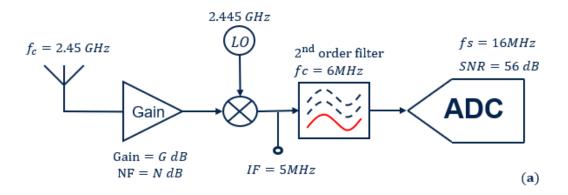

Figure 5 - Example of tradeoff between RF front end and ADC

- (a) ADC relaxed

- (b) Front-end relaxed

On Figure 4, these system elements are aligned with key parameters of the converter in regards of RX chain interaction. As represented on the right of Figure 4, the noise of the ADC depends on its resolution (SNR), its oversampling ratio by the term  $10 \log \left( \frac{f_{sample}}{2.BW} \right)$  and the noise floor as  $NF_{adc} = P_{FS} - SNR_{adc} - 10 \log \left( \frac{f_{sample}}{2.BW} \right)$ . From those elements with given specifications for the RX chain it's possible to draw tradeoff between RF front end and ADC.

In Figure 5 are drawn two simplified RX chains with the same specification, carrier frequency at 2.45 GHz, IF at 5MHz, BW = 1MHz and  $P_{FS,adc} = 8dBm$ . Let's assume that the SNDR<sub>min</sub> is the same for both structures. As seen on Figure 4, SNDR<sub>min</sub> could be written as SNDR<sub>min</sub> =  $P_{FS,adc} - SNR_{adc} - 10 \log \left(\frac{f_{sample}}{2.BW}\right) - NF_{tot} - G_{FE}$ . To relax the constraints on gain and noise, the Figure 5 (b) proposes an ADC with 18 dB more on its SNR than Figure 5 (a) and a sampling frequency 5.3 times greater which make a gain of 7.2 dB SNR through OSR. For the same SNDR<sub>min</sub>, and for the same performances as a system, 25.2 dB can be divided between front end elements allowing more noise in the front end or gain reduction. In terms of filtering, the second order filter required in Figure 5 (a) can be replaced by a first order filter with same cut frequency. Attenuation is then increased by ~9 dB as for the second order filter at 16MS/s:  $att_{mirror,16M} = -40 \log(16M - 5M) + 40 \log(6M) - 3 \approx -13 dB$  and for the first order filter at 64MS/s:  $att_{mirror,64M} = -20 \log(64M - 5M) + 20 \log(6M) - 3 \approx -22 dB$

To resume this example, by adding 3 bits and multiplying the sampling frequency by 4, the front end can reduce its gain and increase its NF in a range of more than 25 dB. The antialiasing filter could go through a second order to a first order for the same cutoff frequency and attenuation is still greater. This shows the impact of the ADC performances on the chain sizing.

The aspect of ADC's distortion hasn't been discussed here because the main concerns are about really small signals.. In the context of this work and as represented on Figure 3, an automatic gain control is present before the converter and assure that no strong signal is presented at the input to avoid saturation of the converter.

### 1.2.3 ADC Specifications

As said in introduction, nowadays receivers are drowned in a crowded spectral environment. Different protocols coexist at the same time and share bandwidth with adjacent channels. This is really challenging for the receiver chain because those adjacent signals are close to the bandwidth of interest, so hard to filter, and could be more powerful than the wanted signal. The receiver chain must be resilient to this kind of situation, and the standards give the requirements in terms of perturbation by a in band

interferer [1]. With the requirements of the standard it's possible to give a minimum SNR for the converter. On Figure 6 is represented how to translate this to the ADC parameters [9]. The SNR is shown as:

$$SNR_{ADC} = P_{FS} - Margin - \left(\frac{I}{C}\right) - SNR_{Min}$$

(1.9)

where I/C is Interfere to Carrier power ratio and SNR<sub>MIN</sub> is minimum SNR required for signal decoding. A Margin is added to account for channel variations and allows some headroom for the automatic gain control.

Figure 6 - Dimensioning of the minimum SNR compared to the I/C standard requirement.

Because of confidentiality on the STMicroelectronics products development, no details can be given for the different values for the reference case. With the given values in the worst case of interferences the calculation shows that the SNR at Nyquist frequency of the ADC must be at least 67 dB. This result comes from the analysis described in Figure 6 and is computed with a sampling frequency of 64MS/s for a signal bandwidth of 100KHz.

With front-end and system on chip (SOC) tradeoff considerations the objective has been fixed on a 12 bits ADC with a sampling frequency of 64MS/s. From the previous generation of ADCs this will bring resilience to interference by increasing the sampling frequency. Also relax the design of the front-end and bring more flexibility in digital signal processing (DSP) by increasing the resolution. The power consumption is targeted to  $300\mu W$ . The target specifications are summarized in Table 1.

ADC number of bits

Sampling Frequency

SNR

67 dB

SNDR

65 - 67 dB

Power consumption

<a href="mailto:20px blue="mailto:20px blue="mail

Table 1- Specifications of the aimed ADC for this work

# 1.3 Survey of ADC state of the art

### 1.3.1 Metrics and tools to compare.

A large variety of ADC architectures exists addressing different types of specifications. To guide the architecture choice for this work, a first comparison of these architecture with relevant metrics is useful as good metrics to compare them. Commonly used metrics are the figure of merit (FOM) of Schreier and the figure of merit of Walden. Both metrics are attempts to allow performance comparison between very different implementations independently of the specific resolution or sampling frequency of a particular implementation.

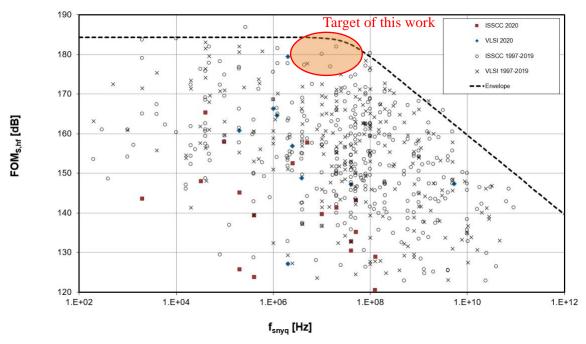

The first FOM proposed by Schreier [10] quantifies performance by associating effective conversion range and ratio of bandwidth and power consumption. The ratio is described in a log function to express the value in dB. A higher value of the FOM indicates better performance. This FOM underlines the capacity of a converter to reach high effective resolution and while consuming low energy for a conversion while regarding the sampling frequency used. It is usually described as:

$$FOM_{Schreier}[dB] = SNDR[dB] + 10 \log \left( \frac{f_{sample}[Hz]}{2.P[W]} \right)$$

(1.10)

Where P represents the power consumed in watt, this figure of merit allows to underline the tradeoff between SNDR and consumption. At the beginning of this work the envelope (best performance presented in state of the art) of this figure of merit was 185 dB.

The second, FOM Walden quantifies the energy consumed by the converter and compare it with its effective resolution (ENOB). The energy is calculated with the ratio of the power consumption and the sampling frequency, representing the energy consumed for one conversion divided by the effective number of codes ( $2^{ENOB}$ ) of the ADC. A lower FOM expresses higher performance in terms of the energy efficiency of a design with respect to its effective resolution. This FOM is defined as:

$$FOM_{Walden} \left[ \frac{fJ}{conv} \right] = \frac{P[fW]}{2^{\frac{SNDR [dB] - 1.76}{6.02}} f_{sample}[Hz]}$$

(1.11)

In the Walden's FOM, the energy per conversion is expressed in fJ which close to the order of magnitude of the best ADCs at this time. This FOM<sub>Walden</sub> is mostly used to compare high data rate converters. The envelop (best performance presented in state of the art) from the beginning of this work was  $1 \frac{fJ}{conv}$ .

The specifications presented in Table 1 considered with 300 $\mu$ W of power consumption presents a FOM<sub>Schreier</sub> = 177.3 dB and  $FOM_{Walden} = 2.3 \frac{fJ}{conv}$ .

### 1.3.2 Graphs and architectures

To compare the described specification with state of the art realizations, the Boris Murmann survey on the ADC is used. This is a useful tool to compare existing ADC realized on silicon, the survey references only ISSCC and VLSI production on converter. In its 2020 version [9], this survey gives a picture of the state of the at the beginning of this work.

The described FOMs of the survey data can be plotted as a function of the sampling frequency as shown in Figure 8 and Figure 7. These figures of allow to place the proposed specification on the graph. The orange circle shows with some margin the target performance compared to other realizations.

Figure~8 - Schreier~FOM~plot~compared~to~sampling~frequency~(1997-2020)~from~[11]

Figure 7 - Walden FOM plot compared to sampling frequency (1997-2020) from [11]

The target specification challenges the state of the art as shown on Figure 8 and Figure 7.

The next chapter will go deeper into the study of ADC architectures and 2020 state of the art to underline the direction taken to address the given specifications.

# Chapter 2

# State of the Art

| 2.1.1 MAIN ADCS ARCHITECT          | TURES3                     | 34             |

|------------------------------------|----------------------------|----------------|

| 2.1.1 FLASH, OVERSAMPLED, AN       | ND PIPELINED ARCHITECTURES | 34             |

|                                    | 3                          |                |

| 2.1.1.2 $\Sigma\Delta$ topology    | 3                          | 36             |

| 2.1.1.3 Pipelined topology.        | 3                          | 38             |

| 2.1.2 Successive Approximation     | Register (SAR)             | 10             |

| 2.2 QUANTITATIVE ANALYSIS          | OF THE ADC SURVEY4         | 15             |

| 2.2.1 OVERALL SURVEY, SILICON ME   | ASUREMENTS FROM [11]4      | <b>1</b> 5     |

| 2.2.2 OVERALL SURVEY, FILTERED SIL | ICON REALIZATIONS          | <del>1</del> 6 |

| 2.3 HYBRID SAR ARCHITECTU          | JRES4                      | 18             |

|                                    | 4                          |                |

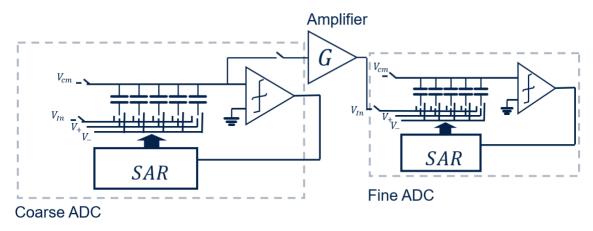

| 2.3.1.1 Amplify and quant          | ize the residue4           | 18             |

| 2.3.1.2 State of the art per       | formance4                  | 19             |

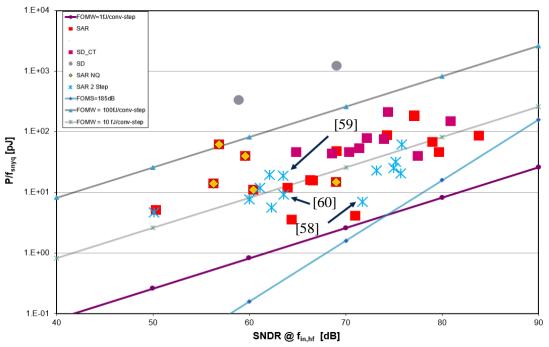

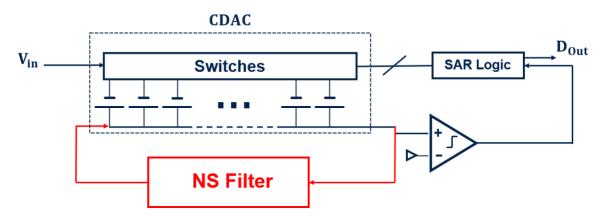

| 2.3.2 HYBRID SAR NOISE SHAP        | PING 5                     | 50             |

| 2.3.2.1 Noise Shaping SAR          | (NS-SAR) Overview5         | 50             |

| 2.3.2.2 State of the art per       | formance 5                 | 51             |

| 2.3.3 TIME-BASED APPROACHES        | S TO HYBRID SAR ADCs5      | 53             |

| 2.3.4 Hybrid SAR TDC [69]          | 5                          | 54             |

| 2.3.4.1 Overall architecture       | e5                         | 54             |

| 2.3.4.2 Performances and           | drawbacks5                 | 55             |

|                                    | peatability5               |                |

|                                    | 5                          |                |

| • •                                | e5                         |                |

|                                    | -<br>rawbacks5             |                |

|                                    | 6                          |                |

## 2.1.1 Main ADCs Architectures

### 2.1.1 Flash, oversampled, and pipelined architectures

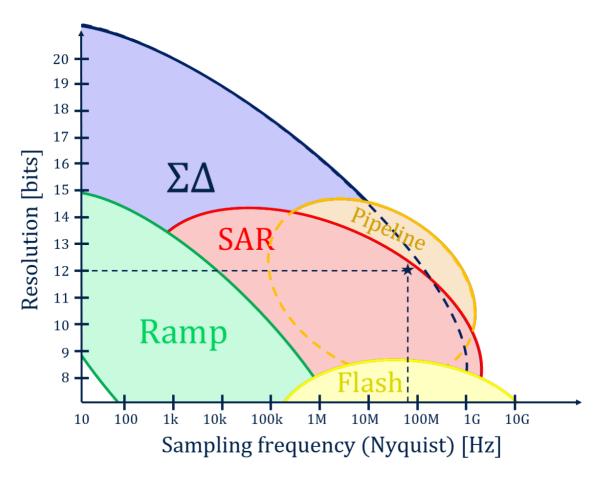

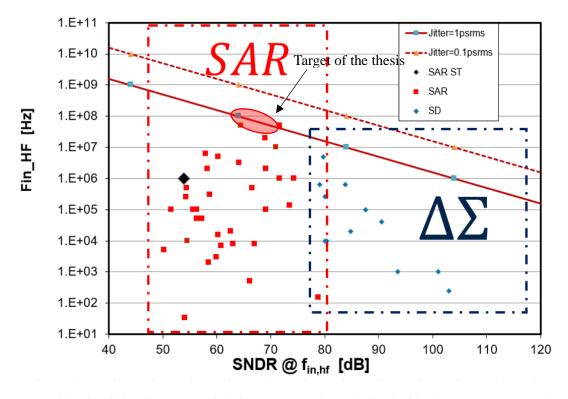

Figure 9 - Main performance trends of ADC topologies, inspired by [31], with data of [12]. The star symbol identifies the target specifications for this work as defined in chapter 1.

It is well known that in analog to digital conversion, some concepts have been so widely used that they are today classified in different topologies called main architectures. A survey of different ADC realizations published in ISSC and VLSI held by Boris Murmann [11] has been used at the beginning of this work in 2020, the version updated in 2023 is referenced as [12]., This chapter shows the challenges with respect to the state of the art in terms of architecture to meet the target specifications set for the this work. The main questions of this chapter are: What is the best topology to resolve the specification given in chapter 1? Can it be designed to meet industrial constraints? What improvements can be applied to the most relevant architectures to make them more effective in regard of the target?

Figure 9 shows the main architecture suitable for the target specifications in terms of resolution and bandwidth. Power consumption, area, linearity etc. are not considered at this stage. With 12 bit and

64MS/s as target, the SAR, the Pipeline, and the sigma-delta ( $\Sigma\Delta$ ) topologies seem to able to reach this area in terms of speed and precision. Because Figure 9 is an approximative representation of what is possible, the following sections will outline the challenges of each architecture, and how to find the good structure, if there is one.

### 2.1.1.1 Flash Topology

The essence of a flash architecture is to instantly compare the input signal to every discrete level possible in the ADC resolution. This means  $2^n$  different voltage level for a n bit converter. Generating those voltages and comparing the signal with precision consumes energy proportional to the number of levels. So, the power consumption grows exponentially with the resolution [13].

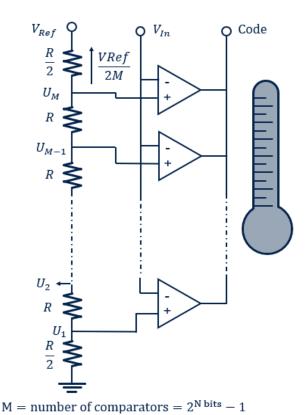

Figure 10 - Concept representation of flash ADC

On Figure 10 is represented a simple flash as described previously. The input is compared with every voltage equivalent to a code. This is described as thermometric code because similarly to a thermometer, the number of outputs with code 1 grows proportionally to the input voltage. Every code below the input equivalent code would be set as a "1", and every greater code would be set as a "0".

Some technics as folding or interpolating presented in [14] brought higher resolutions without exponential growth of the circuit complexity. In the context of this work, silicon realizations aimed for wireless

communication present good performances [15] but still a consumption of several hundreds of milliwatts which is not the target of this work. This type of structure is fast by construction, as shown in [16] reaching 2GS/s without interleaving, but consuming ~20mW for 6.5 bits ENOB. This is beyond the total energy budget of a complete receiver chain.

| Table 2 - | Flash ADCs | in the | literature |

|-----------|------------|--------|------------|

|           |            |        |            |

| Ref. | Architecture              | Techno | $F_{snyq}$ | Res. | SNDR | Supply | Power | FOMs  |

|------|---------------------------|--------|------------|------|------|--------|-------|-------|

|      |                           | [nm]   | [Hz]       |      | [dB] | [V]    | [W]   | [dB]  |

| [14] | Folding and interpolation | 1000   | 50M        | 12   | 63.6 | 5      | 300m  | 142.8 |

| [15] | Folding and interpolation | 600    | 50M        | 12   | 64   | 3.3    | 850m  | 138.6 |

| [16] | Flash                     | 65     | 2G         | 8    | 40.7 | 1.3    | 21m   | 171.8 |

Table 2 draws performances of previously cited realizations, showing a non-exhaustive picture of the possibility in state of the art for flash ADC.

From this analysis, it can be concluded that this architecture is not suitable by itself for the application of this work.

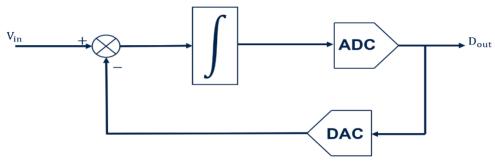

### $2.1.1.2 \Sigma \Delta$ topology

The concept of Oversampling (OS) can be used most of the classical topologies. One of the main advantages of having a sampling frequency greater than the target bandwidth is to reduce the power spectral density of the noise in the band after filtering [13]. This method increases the ENOB by  $\sim$ X bits where X  $\approx \frac{OSR}{4}$  and OSR defines the oversampling ratio as OSR =  $\frac{fs}{2*BW}$ , where fs is the sampling frequency and BW is the bandwidth of the signal to convert. From this point reaching high resolution with oversampling looks easy but to get for example 16 more bits the OSR must be  $\sim$ 4<sup>15</sup> so an order of magnitude of 10<sup>9</sup> which doesn't look a so good trade-off after all. From this observation, different

Figure 11 - Simplified block representation of a  $\Sigma\Delta$  ADC