Neuromorphic in-memory learning with analog integrated circuits and nanoscale memristive devices

Apprentissage neuromorphique en mémoire avec des circuits intégrés analogiques et des dispositifs mémoristifs à l'échelle nanométrique

Thèse de doctorat de l'Université de Lille préparée à UMR CNRS 8520 Institut d'Electronique, de Microélectronique et de Nanotechnologie – IEMN

École doctorale n°632 Sciences de l'Ingénierie et des Systèmes (ENGSYS) Spécialité de doctorat: Electronique, microélectronique, nanoélectronique et micro-ondes

> Thèse de doctorat de l'Université de Sherbrooke préparée à Laboratoire Nanotechnologies et Nanosystèmes – LN2 Spécialité de doctorat: Génie Electrique

> > Thèse présentée et soutenue le 5 December 2024, par

#### NIKHIL GARG

#### Composition du Jury:

Jean-Michel PORTAL

Professeur, Université Aix-Marseille Président

Sylvian SAIGHI

Professeur, Université de Bordeaux Rapporteur

Elisa VIANELLO

Senior Scientist, CEA-Leti Rapporteur

Sean WOOD

Assistant Professor, Université de Sherbrooke Rapporteur

Laura BEGON-LOURS

Assistant Professor, ETH Zurich Examinateur

Fabien ALIBART

Chargé de recherche, CNRS Directeur de thèse

Dominique DROUIN

Professeur, Université de Sherbrooke Directeur de thèse

Damien QUERLIOZ

Directeur de recherche, Université Paris-Saclay Invité

Yann BEILLIARD

Professeur Associé, Université de Sherbrooke Invité

## RÉSUMÉ

L'intégration de l'intelligence artificielle (IA) dans l'informatique en périphérie (EC) et les dispositifs portables présente des défis importants en raison des contraintes strictes en matière de puissance de calcul et de consommation d'énergie. L'informatique neuromorphique, inspirée par la conception économe en énergie du cerveau et ses capacités d'apprentissage continu, offre une solution prometteuse pour ces applications. Cette thèse propose un cadre flexible de co-conception algorithme-circuit qui aborde à la fois le développement des algorithmes et la conception matérielle, facilitant ainsi le déploiement efficace de l'IA sur du matériel spécialisé à ultra-basse consommation d'énergie.

La première partie se concentre sur le développement d'algorithmes et introduit la plasticité synaptique dépendante de la tension (VDSP), une règle d'apprentissage non supervisée inspirée du cerveau. Le VDSP vise à mettre en œuvre en ligne le mécanisme de plasticité de Hebb en utilisant des synapses memristives à l'échelle nanométrique. Ces dispositifs imitent les synapses biologiques en ajustant leur résistance en fonction de l'activité électrique passée, permettant ainsi un apprentissage en ligne efficace. Le VDSP met à jour la conductance synaptique en fonction du potentiel de membrane du neurone, éliminant ainsi le besoin de mémoire supplémentaire pour stocker les timings des pics d'activité. Cette approche permet un apprentissage en ligne sans les circuits de formage d'impulsions complexes habituellement requis pour la plasticité dépendante du timing des pics (STDP) avec des memristors. Nous montrons comment le VDSP peut être avantageusement adapté à trois types de dispositifs memristifs (synapses à filament d'oxyde métallique et jonctions tunnel ferroélectriques) avec des caractéristiques de commutation analogiques distinctives. Les simulations au niveau du système de réseaux neuronaux à impulsions utilisant ces dispositifs ont validé leurs performances sur des tâches de reconnaissance de motifs sur MNIST, atteignant jusqu'à 90 % de précision avec une meilleure adaptabilité et une réduction du réglage des hyperparamètres par rapport au STDP. De plus, nous avons évalué la variabilité des dispositifs et proposé des stratégies d'atténuation pour améliorer la robustesse.

Dans la deuxième partie, nous implémentons un neurone analogique de type LIF, accompagné d'un régulateur de tension et d'un atténuateur de courant, afin d'interfacer sans heurts les neurones CMOS avec des synapses memristives. La conception du neurone inclut une fuite double, facilitant l'apprentissage local via le VDSP. Nous proposons également un mécanisme d'adaptation configurable qui permet de reconfigurer les neurones LIF adaptatifs en temps réel. Ces circuits polyvalents peuvent s'interfacer avec une gamme de dispositifs synaptiques, permettant ainsi le traitement de signaux avec une variété de dynamiques temporelles. En intégrant ces neurones dans un réseau, nous présentons un bloc de construction neuronal auto-apprenant CMOS-memristor (NBB), composé de circuits analogiques pour la lecture en croix et de neurones LIF, ainsi que de circuits numériques pour basculer entre les modes d'inférence et d'apprentissage. Des réseaux neuronaux compacts, capables de s'adapter eux-mêmes, d'apprendre en temps réel et de traiter des données environnementales, lorsqu'ils sont réalisés sur du matériel à ultra-basse consommation

d'énergie, ouvrent de nouvelles perspectives pour l'IA dans l'informatique en périphérie. Les avancées à la fois en matériel (circuits) et en algorithmes (apprentissage en ligne) accéléreront considérablement le déploiement des applications d'IA en exploitant l'informatique analogique et les technologies de mémoire à l'échelle nanométrique.

Mots-clés: Neuromorphic engineering, Synaptic learning, In-memory computing, Memristors, On-chip learning, Spiking neural networks

### **ABSTRACT**

"Somewhere, Something Incredible Is Waiting To Be Known" - Carl Sagan

Integrating artificial intelligence (AI) into edge computing (EC) and portable devices presents significant challenges due to stringent constraints on computational power and energy consumption. Neuromorphic computing, inspired by the brain's energy-efficient design and continuous learning capabilities, offers a promising solution for these applications. This thesis proposes a flexible algorithm-circuit co-design framework that addresses both unsupervised online learning algorithm development and hardware design, facilitating the efficient deployment of AI on specialized, ultra-low-power high-density hardware.

The first part focuses on algorithm development and introduces voltage-dependent synaptic plasticity (VDSP), a brain-inspired unsupervised learning rule. VDSP is aimed at the online implementation of Hebb's plasticity mechanism using nanoscale memristive synapses. These devices mimic biological synapses by adjusting their resistance based on past electrical activity, enabling efficient online learning. VDSP updates synaptic conductance based on the membrane potential of the neuron, eliminating the need for additional memory to store spike timings. This approach allows for online learning without the complex pulse-shaping circuits typically required for spike-timing-dependent plasticity (STDP) with memristors. We show how VDSP can be advantageously adapted to three types of memristive devices (metal-oxide filamentary synapses, and ferroelectric tunnel junctions) with distinctive analog switching characteristics. System-level simulations of spiking neural networks using these devices validated their performance on MNIST pattern recognition tasks, achieving up to 90% accuracy with improved adaptability and reduced hyperparameter tuning compared to STDP. Additionally, we evaluated device variability and proposed mitigation strategies to enhance robustness.

In the second part, we implement an analog leaky integrate-and-fire (LIF) neuron, accompanied by a voltage regulator and current attenuator, to seamlessly interface CMOS neurons with memristive synapses. The neuron design features dual leakage, facilitating local learning through VDSP. We also propose a configurable adaptation mechanism that allows adaptive LIF neurons to be reconfigured in run-time. These versatile circuits can interface with a range of synaptic devices, allowing the processing of signals with a variety of temporal dynamics. Integrating these neurons into a network, we present a CMOS-memristor self-learning neural building block (NBB), consisting of analog circuits for crossbar reading and LIF neurons, along with digital circuits for switching between inference and learning modes. Compact neural networks that can self-adapt, learn in real time, and process environmental data, when realized on ultra-low-power hardware, open new possibilities for AI in edge computing. Advances in both hardware (circuits) and algorithms (online learning) will greatly accelerate the deployment of AI applications by leveraging analog computing and nanoscale memory technologies.

**Keywords:** Neuromorphic engineering, Synaptic learning, In-memory computing, Memristors, On-chip learning, Spiking neural networks

Dedicated to my parents whom I am indebted to for giving me their love of learning and life

Dédié à mes parents, à qui je suis redevable de m'avoir transmis leur amour de l'apprentissage et de la vie.

## **ACKNOWLEDGEMENTS**

The publication of this thesis marks the culmination of years of dedicated work, and its completion would not have been possible without the support of many individuals who played pivotal roles along the way. For this, I am profoundly grateful. I am especially indebted to my advisor, Prof. Fabien Alibart, who introduced me to this fascinating field and generously shared his time, expertise, and unwavering support at every stage of this journey. I extend my deepest appreciation to him for his guidance and encouragement.

This journey began in 2021 when I embarked on my thesis work in Lille. During my time at IEMN Lille, I had the privilege of working alongside an exceptional group of mentors, colleagues, and friends who supported me in countless ways, from administrative assistance to navigating the complexities of research. I am particularly grateful to Dr. Ankush Kumar for helping me settle in Lille and, along with Dr. Kamila Janzakova, for guiding me through cleanroom experiments at IEMN. The unforgettable experience of working with dendrites will always remain with me. My heartfelt thanks go to Nora and Andy from the administration, who were lifesavers in keeping my paperwork in order and frequently rescuing me with new access cards whenever I misplaced them. Emmanuelle, thank you for managing the reimbursements from my many missions. I am also grateful to Dr. Yannick Coffinier, Dr. Sébastien Pecqueur, Ravi, and Ravinder for their contributions in making my time at IEMN so memorable. Special thanks to Hammouda and Philippe for their warm welcome during my first month in France.

This work would not have been possible without Prof. Damien Querlioz, who graciously hosted me at the C2N lab in Paris. I am also thankful to the C2N team for their camaraderie during our lunches and daily walks to the university restaurant with exciting discussions. Additionally, I extend my sincere thanks to Dr. Laura Begon-Lours for welcoming me to IBM Zurich, introducing me to the neuromorphic device team, and teaching me cleanroom fabrication processes during my two weeks there. I am deeply appreciative of Prof. Jean-Michel Portal for his guidance and hospitality during the UNICO tapeout process in Marseille, where he patiently taught me the fundamentals of IC implementation. I fondly remember our late-night sessions finalizing the design. My gratitude extends to Dr. Eloi Muhr for helping me find housing in Marseille and in the layout of the chip, and to Dr. Mathieu C-Faye, who patiently taught me analog IC design and uplifted my spirits during tough times. A special thank-you to Jean-Pierre for managing the PDK, tools, and libraries, and to Prof. Marc Bocquet for providing critical equipment and training for characterization at the IO lab. Lastly, I must mention Bastien, whose meticulous work in managing delicate chip-to-instrument connections and volunteering to land the probes daily for two weeks was indispensable. I am also grateful to Nicole, Fadi, and Bastien for making my time at IM2NP unforgettable.

The second half of my thesis work took place in Canada at the University of Sherbrooke's 3IT institute. This phase would not have been possible without the mentorship of Prof. Dominique Drouin, who introduced me to imaging and fabrication techniques and gra-

ciously hosted a Christmas party at his home. I am profoundly grateful to my co-director, Prof. Yann Beilliard, who closely mentored me for over four years, integrating me deeply into the UNICO project. Collaborating with Ismael, who taught me about SNN simulation in Python and became both a great friend and colleague, was a highlight of this journey. My heartfelt thanks go to the NECOTIS team, including Ahmad, Ilham, Arnaud, Prof. Jean Rouat, and Prof. Sean Wood, for their invaluable collaboration and support. I am equally grateful to my colleagues at 3IT, especially Joao for being a wonderful friend and collaborator, as well as Raphael, Mathieu, Gaspard, Pierre, Dorian, Victor, Patrick, Davide, Tadeas, Javier, and Prof. Serge Ecoffey. I also want to acknowledge the Platforms team, particularly Johnathan, who spent countless hours helping me set up chip probing at LCSM, as well as Joel, Gabriel, and Charles for their technical assistance. My gratitude extends to my friends, housemates and colleagues, including Chander, Adi, Shrivani, and Swayam.

Lastly, I want to thank the reviewers of my thesis and all the jury members for their valuable time and insightful feedback. I am also deeply appreciative of my former teachers and mentors, including Prof. Veeky Baths, Prof. Amalin Prince, and Prof. Abhijit Pethe.

I would be remiss if I did not acknowledge my family and closest friends for their sacrifices and unwavering support. This work would not have been possible without them.

# TABLE OF CONTENTS

| 1.1 Context 1.2 Challenges 1.3 Research question and objectives 1.3.1 On device learning 1.3.2 Circuits 1.4 Organization of thesis 1.4.1 Background 1.4.2 Voltage dependent synaptic plasticity 1.4.3 Learning with memristive synapses 1.4.4 CMOS neuron for memristor integrated neuromorphic circuits 1.4.5 Neural building block for 3D integrated CMOS-RRAM SNNs 1.4.6 Conclusion and Perspective  2 Background 2.1 Outline 2.2 History 2.3 Neuromorphic computing principles 2.3.1 Time-domain computing 2.3.2 Memory 2.4 Learning and adaptation 2.4.1 Online 2.4.2 Unsupervised 2.4.3 Local | . 2  |                                         |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------|---|

| 1.3 Research question and objectives 1.3.1 On device learning 1.3.2 Circuits  1.4 Organization of thesis 1.4.1 Background 1.4.2 Voltage dependent synaptic plasticity 1.4.3 Learning with memristive synapses 1.4.4 CMOS neuron for memristor integrated neuromorphic circuits 1.4.5 Neural building block for 3D integrated CMOS-RRAM SNNs 1.4.6 Conclusion and Perspective  2 Background 2.1 Outline 2.2 History 2.3 Neuromorphic computing principles 2.3.1 Time-domain computing 2.3.2 Memory 2.4 Learning and adaptation 2.4.1 Online 2.4.2 Unsupervised                                       |      | Context                                 |   |

| 1.3.1 On device learning 1.3.2 Circuits  1.4 Organization of thesis 1.4.1 Background 1.4.2 Voltage dependent synaptic plasticity 1.4.3 Learning with memristive synapses 1.4.4 CMOS neuron for memristor integrated neuromorphic circuits 1.4.5 Neural building block for 3D integrated CMOS-RRAM SNNs 1.4.6 Conclusion and Perspective  2 Background 2.1 Outline 2.2 History 2.3 Neuromorphic computing principles 2.3.1 Time-domain computing 2.3.2 Memory 2.4 Learning and adaptation 2.4.1 Online 2.4.2 Unsupervised                                                                            | . 4  | Challenges                              |   |

| 1.3.2 Circuits  1.4 Organization of thesis  1.4.1 Background  1.4.2 Voltage dependent synaptic plasticity  1.4.3 Learning with memristive synapses  1.4.4 CMOS neuron for memristor integrated neuromorphic circuits  1.4.5 Neural building block for 3D integrated CMOS-RRAM SNNs  1.4.6 Conclusion and Perspective  2 Background  2.1 Outline  2.2 History  2.3 Neuromorphic computing principles  2.3.1 Time-domain computing  2.3.2 Memory  2.4 Learning and adaptation  2.4.1 Online  2.4.2 Unsupervised                                                                                       | . 6  | Research question and objectives        |   |

| 1.4 Organization of thesis  1.4.1 Background  1.4.2 Voltage dependent synaptic plasticity  1.4.3 Learning with memristive synapses  1.4.4 CMOS neuron for memristor integrated neuromorphic circuits  1.4.5 Neural building block for 3D integrated CMOS-RRAM SNNs  1.4.6 Conclusion and Perspective  2 Background  2.1 Outline  2.2 History  2.3 Neuromorphic computing principles  2.3.1 Time-domain computing  2.3.2 Memory  2.4 Learning and adaptation  2.4.1 Online  2.4.2 Unsupervised                                                                                                       | . 7  | 1.3.1 On device learning                |   |

| 1.4 Organization of thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 7  | 1.3.2 Circuits                          |   |

| 1.4.1 Background 1.4.2 Voltage dependent synaptic plasticity 1.4.3 Learning with memristive synapses 1.4.4 CMOS neuron for memristor integrated neuromorphic circuits 1.4.5 Neural building block for 3D integrated CMOS-RRAM SNNs 1.4.6 Conclusion and Perspective  2 Background 2.1 Outline 2.2 History 2.3 Neuromorphic computing principles 2.3.1 Time-domain computing 2.3.2 Memory 2.4 Learning and adaptation 2.4.1 Online 2.4.2 Unsupervised                                                                                                                                                |      |                                         |   |

| 1.4.2 Voltage dependent synaptic plasticity 1.4.3 Learning with memristive synapses 1.4.4 CMOS neuron for memristor integrated neuromorphic circuits 1.4.5 Neural building block for 3D integrated CMOS-RRAM SNNs 1.4.6 Conclusion and Perspective  2 Background 2.1 Outline 2.2 History 2.3 Neuromorphic computing principles 2.3.1 Time-domain computing 2.3.2 Memory 2.4 Learning and adaptation 2.4.1 Online 2.4.2 Unsupervised                                                                                                                                                                 |      | · ·                                     |   |

| 1.4.3 Learning with memristive synapses 1.4.4 CMOS neuron for memristor integrated neuromorphic circuits 1.4.5 Neural building block for 3D integrated CMOS-RRAM SNNs 1.4.6 Conclusion and Perspective  2 Background 2.1 Outline 2.2 History 2.3 Neuromorphic computing principles 2.3.1 Time-domain computing 2.3.2 Memory  2.4 Learning and adaptation 2.4.1 Online 2.4.2 Unsupervised                                                                                                                                                                                                            |      |                                         |   |

| 1.4.4 CMOS neuron for memristor integrated neuromorphic circuits 1.4.5 Neural building block for 3D integrated CMOS-RRAM SNNs 1.4.6 Conclusion and Perspective  2 Background 2.1 Outline 2.2 History 2.3 Neuromorphic computing principles 2.3.1 Time-domain computing 2.3.2 Memory 2.4 Learning and adaptation 2.4.1 Online 2.4.2 Unsupervised                                                                                                                                                                                                                                                     |      | ~ - · · · · · · · · · · · · · · · · · · |   |

| 1.4.5 Neural building block for 3D integrated CMOS-RRAM SNNs 1.4.6 Conclusion and Perspective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                                         |   |

| 1.4.6 Conclusion and Perspective  2 Background 2.1 Outline 2.2 History 2.3 Neuromorphic computing principles 2.3.1 Time-domain computing 2.3.2 Memory 2.4 Learning and adaptation 2.4.1 Online 2.4.2 Unsupervised                                                                                                                                                                                                                                                                                                                                                                                   |      |                                         |   |

| 2.1 Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | ŭ .                                     |   |

| 2.1 Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13   | dromound                                | 2 |

| 2.2 History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | •                                       | 4 |

| 2.3 Neuromorphic computing principles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |                                         |   |

| 2.3.1 Time-domain computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | v                                       |   |

| 2.3.2 Memory          2.4 Learning and adaptation          2.4.1 Online          2.4.2 Unsupervised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |                                         |   |

| 2.4 Learning and adaptation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                                         |   |

| 2.4.1 Online                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | v                                       |   |

| 2.4.2 Unsupervised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      | ÿ .                                     |   |

| r and r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                                         |   |

| 2.4.3 Local                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                                         |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                                         |   |

| 2.4.4 Circuits for learning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                                         |   |

| 2.5 Neuromorphic hardware systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | ·                                       |   |

| 2.5.1 Analog domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |                                         |   |

| 2.5.2 Memory centered architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | 2.5.2 Memory centered architectures     |   |

| 2.5.3 Emerging devices for the post-Moore era                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                                         |   |

| 2.5.4 Demonstrations with Crossbar Arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                         |   |

| 2.6 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 37 | Conclusion                              |   |

| 3 VDSP: Plasticity rule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41   | SP: Plasticity rule                     | 3 |

| 3.1 Preface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 42 | Preface                                 |   |

| 3.2 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 44 | Introduction                            |   |

| 3.3 Materials and methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                         |   |

| 3.3.1 Neuron modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |                                         |   |

| 3.3.2 Relation between spike time and membrane potential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | $\sim$                                  |   |

| 3.3.3 Proposed plasticity algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | -                                       |   |

| 3.3.4 MNIST classification network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                                         |   |

| 3.4 Results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                                         |   |

|   |     | 3.4.1 Presynaptic firing frequency dependence of VDSP | 54 |

|---|-----|-------------------------------------------------------|----|

|   |     |                                                       | 56 |

|   |     | 3.4.3 VDSP parameters optimization                    | 57 |

|   |     | •                                                     | 59 |

|   | 3.5 | Conclusion and future scope                           | 60 |

|   | 3.6 | •                                                     | 62 |

| 4 | Lea | rning with memristive synapses                        | 67 |

|   | 4.1 | Preface                                               | 68 |

|   | 4.2 | Introduction                                          | 70 |

|   | 4.3 | Results                                               | 74 |

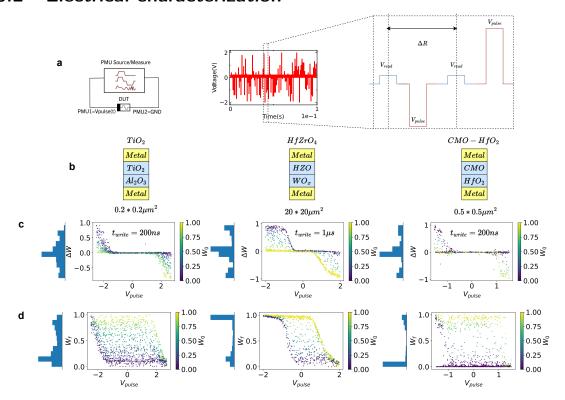

|   |     | 4.3.1 Voltage-dependent switching of memristors       | 74 |

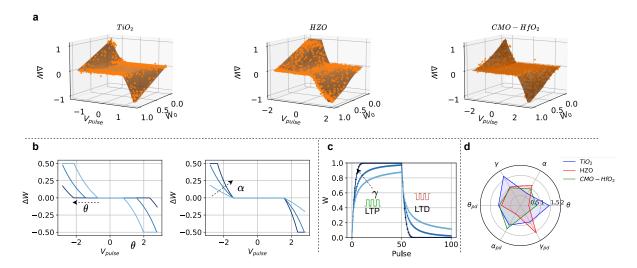

|   |     |                                                       | 77 |

|   |     |                                                       | 79 |

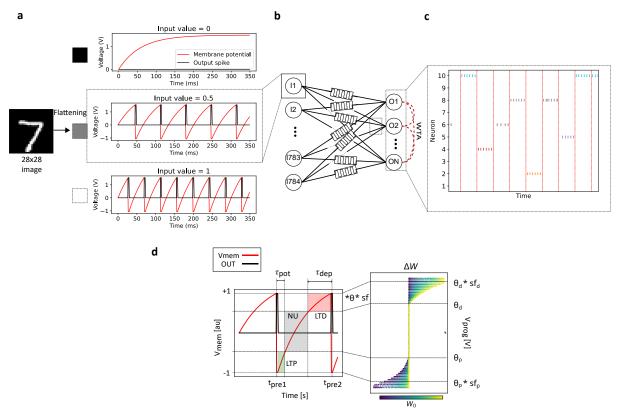

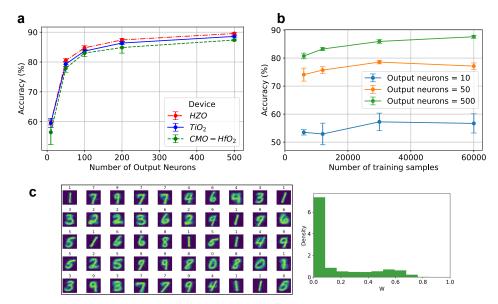

|   |     | 4.3.4 SNN benchmark                                   | 82 |

|   |     |                                                       | 86 |

|   | 4.4 |                                                       | 89 |

|   |     |                                                       | 89 |

|   |     |                                                       | 90 |

|   |     |                                                       | 91 |

|   | 4.5 |                                                       | 92 |

|   | 1.0 |                                                       | 92 |

|   |     |                                                       | 92 |

|   |     | 1                                                     | 93 |

|   |     | O .                                                   | 93 |

|   | 4.6 |                                                       | 95 |

| 5 | Ver | satile CMOS Analog LIF Neuron                         | 99 |

|   | 5.1 |                                                       | 00 |

|   | 5.2 | Introduction                                          | 02 |

|   | 5.3 | Materials and Methods                                 | 04 |

|   |     | 5.3.1 Implemented Design                              | 04 |

|   |     | 5.3.2 Circuits                                        | 05 |

|   | 5.4 | Results and Discussion                                | 07 |

|   |     |                                                       | 07 |

|   |     | v · ·                                                 | 08 |

|   |     |                                                       | 09 |

|   |     | 1 0                                                   | 12 |

|   |     |                                                       | 13 |

|   | 5.5 |                                                       | 14 |

| 6 | Neu | ıral building block 1                                 | 17 |

|   | 6.1 |                                                       | 18 |

|   | 6.2 |                                                       | 18 |

|   | 6.3 | Introduction                                          | 18 |

|   |     |                                                       |    |

| TABLE | OF | CON | TEN | TS |

|-------|----|-----|-----|----|

|       |    |     |     |    |

|               | 6.4           | Materials and Methods                                      | 121 |

|---------------|---------------|------------------------------------------------------------|-----|

|               |               | 6.4.1 Data path                                            |     |

|               |               | 6.4.2 Crossbar block                                       |     |

|               |               | 6.4.3 Input block                                          |     |

|               |               | 6.4.4 Top Architecture                                     |     |

|               | 6.5           | Results                                                    |     |

|               |               | 6.5.1 Configuring the chip                                 |     |

|               |               | 6.5.2 Neuron bank characterization                         |     |

|               |               | 6.5.3 VDSP based learning                                  |     |

|               | 6.6           | Discussion                                                 |     |

|               |               | 6.6.1 Back end of the line (BEOL) Integration              |     |

|               |               | 6.6.2 Demonstration of learning                            |     |

|               |               | 6.6.3 Conclusion                                           |     |

|               |               |                                                            |     |

| 7             | Con           | clusion                                                    | 153 |

|               | 7.1           | Local learning algorithm                                   | 154 |

|               | 7.2           | Learning with memristive synapses                          | 155 |

|               | 7.3           | Analog circuits for computing with memristor               | 156 |

|               | 7.4           | Mixed-signal in-memory computing and learning architecture | 157 |

|               | 7.5           | Summary                                                    | 158 |

|               | 7.6           | Publications                                               | 159 |

|               |               | 7.6.1 Primary contributions                                | 159 |

|               |               | 7.6.2 Related Collaborative Works                          |     |

|               | 7.7           | Future works                                               | 160 |

|               |               | 7.7.1 Multi-core architecture                              | 160 |

|               |               | 7.7.2 Neuron circuit                                       | 161 |

|               |               | 7.7.3 Device engineering and learning models               |     |

|               |               | 7.7.4 Interfacing with biology                             |     |

|               |               | 7.7.5 Summary                                              |     |

|               | 7.8           | Perspective                                                |     |

|               |               | 1                                                          |     |

| 8             | Con           | iclusion en français                                       | 169 |

|               | 8.1           | Travaux futurs                                             | 170 |

| Α             | UN            | ICO ASIC                                                   | 173 |

|               |               |                                                            |     |

| $\mathbf{LI}$ | $\mathbf{ST}$ | OF REFERENCES                                              | 177 |

# LIST OF FIGURES

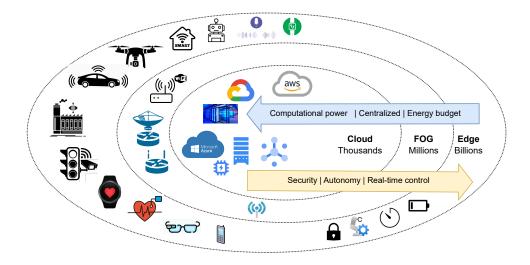

| 1.1<br>1.2                      | Edge AI: Applications and constraints                                                                                                                                                                                                                                          | 2                    |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1.3                             | cal learning with memristive synapses                                                                                                                                                                                                                                          | 8<br>10              |

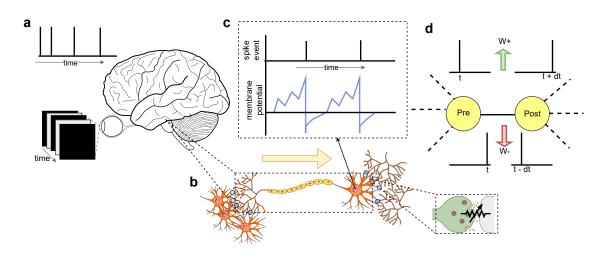

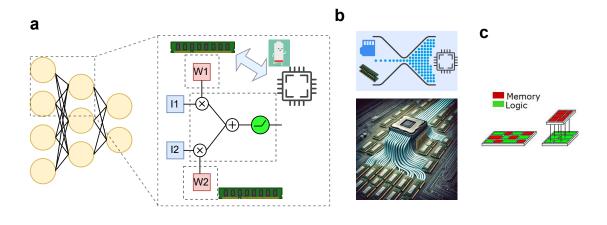

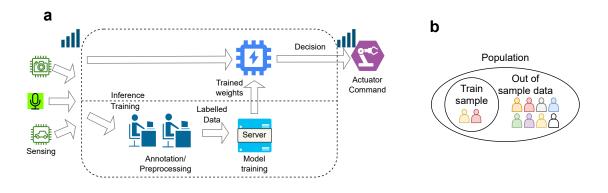

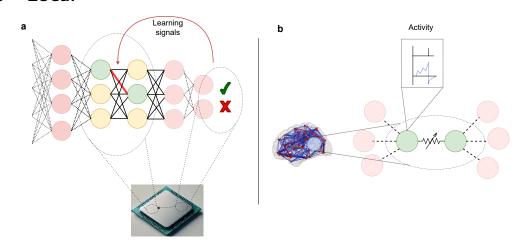

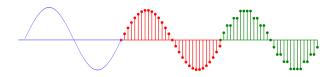

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Neuromorphic computing: The salient features of the human-brain worth taking inspiration for intelligent machines a Event-based sensing. b co-location of computation and memory. c evolving temporal dynamics. d synaptic plasticity based on local variables                 | 15<br>17<br>19<br>21 |

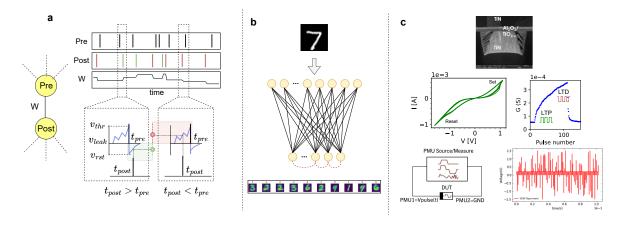

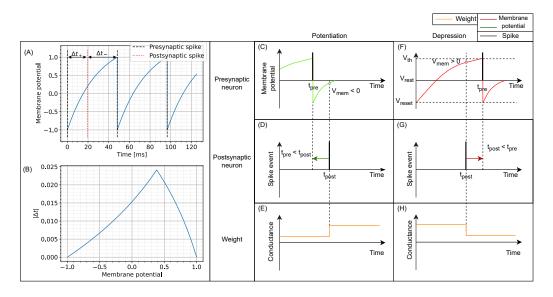

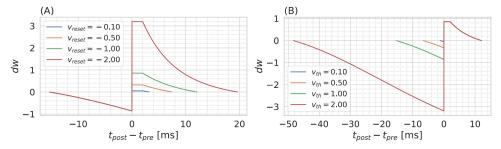

| 3.1                             | Schematic showing the VDSP learning rule between spiking neurons, illus-                                                                                                                                                                                                       |                      |

|                                 | trating membrane potential evolution, spike timing differences, and corresponding synaptic weight updates for potentiation and depression                                                                                                                                      | 50                   |

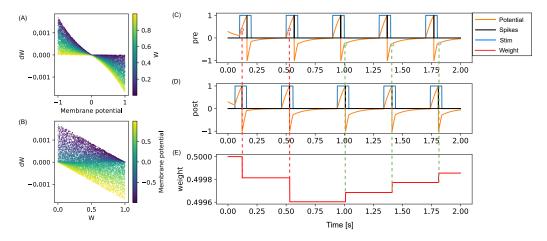

| 3.2                             | Illustration of weight update as a function of presynaptic neuron membrane potential, with linear dependence on weight for potentiation and depression. Synaptic weight evolution is shown, with updates occurring at postsynaptic                                             |                      |

| 3.3                             | spikes based on presynaptic voltage                                                                                                                                                                                                                                            | 52                   |

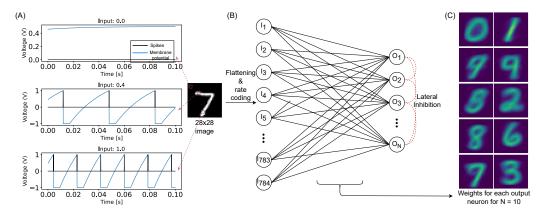

|                                 | the VDSP learning rule with the MNIST classification task                                                                                                                                                                                                                      | 53                   |

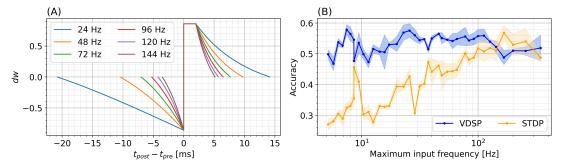

| 3.4<br>3.5                      | Presynaptic firing frequency dependence of VDSP and STDP A spiking neural network with 784 input neurons and varying output neurons (10 to 500) was trained on MNIST for 1 to 5 epochs, with mean accuracy and standard deviation error bars plotted for five trials on 10,000 | 55                   |

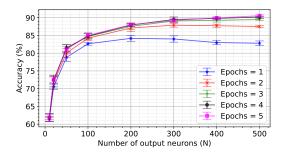

| 0.0                             | test images.                                                                                                                                                                                                                                                                   | 56                   |

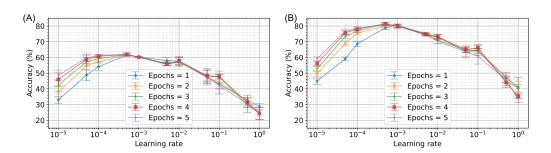

| 3.6                             | Dependence of the performance on learning rate and number of epochs for different network sizes                                                                                                                                                                                | 58                   |

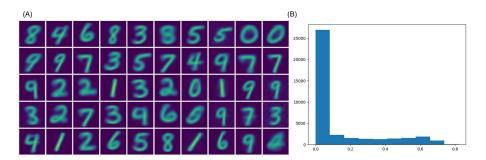

| 3.1                             | A network of 784 input and 50 output neurons was trained on 60,000 MNIST images over three epochs, resulting in weight maps for each output neuron                                                                                                                             | 00                   |

| 2.0                             | and a bimodal distribution of synaptic weights                                                                                                                                                                                                                                 | 62                   |

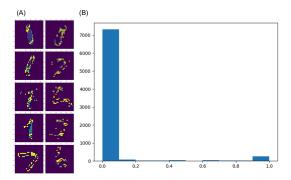

| 3.2                             | Additive VDSP weight plots show dW is independent of current weight, with output neuron weights set to either zero or one after training                                                                                                                                       | 62                   |

| 3.3                             | When the input neuron bias is set to zero, inactive input neurons are not depotentiated, and neurons that fire first for one image are more likely to                                                                                                                          | 02                   |

|                                 | fire for other digits due to pixel overlap.                                                                                                                                                                                                                                    | 63                   |

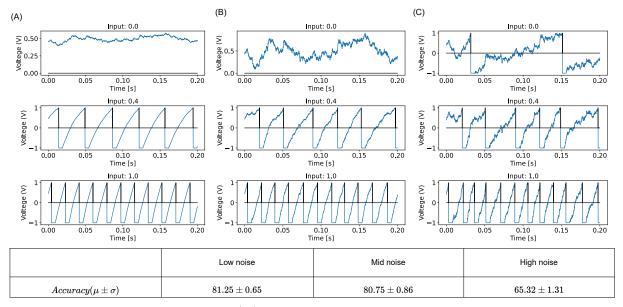

| 3.4<br>3.5   | Impact of the presynaptic LIF neuron's parameters on the shape of VDSP. 6 The neuron is excited with varying constant input magnitudes (0, 0.4, and 1) and Gaussian noise of different intensities for a network with 50 output |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.6          | neurons                                                                                                                                                                                                                         |

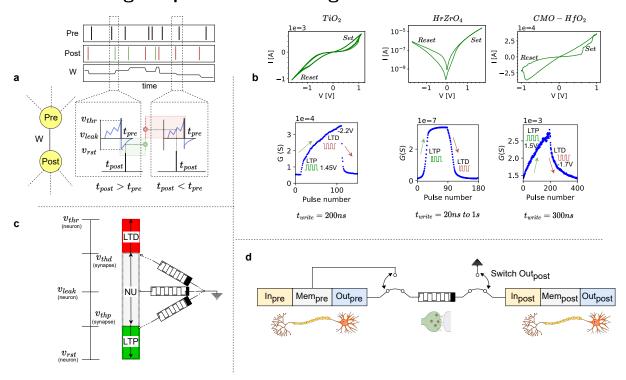

| 4.1          | Schematic representation of the VDSP learning rule implemented in a mem-                                                                                                                                                        |

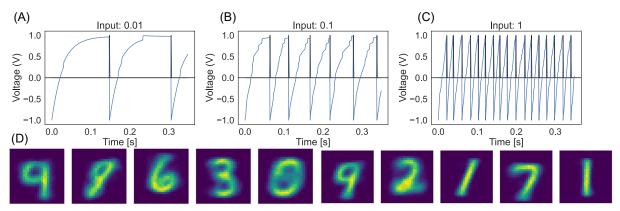

| 4.2          | ristive synapse between a pre- and postsynaptic spiking neuron                                                                                                                                                                  |

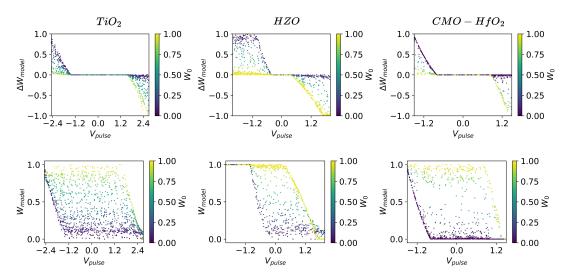

| 4.2          | Memristor model fitting and model parameter analysis                                                                                                                                                                            |

| 4.4          | MNIST benchmark and simulation-device mapping in SNN                                                                                                                                                                            |

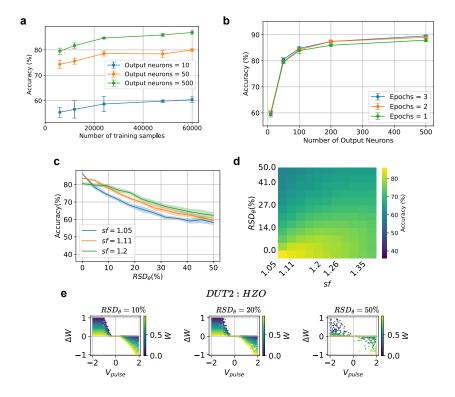

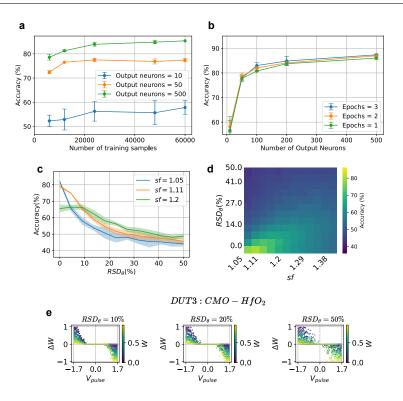

| 4.5          | MNIST benchmark results for different network sizes and number of samples. 8                                                                                                                                                    |

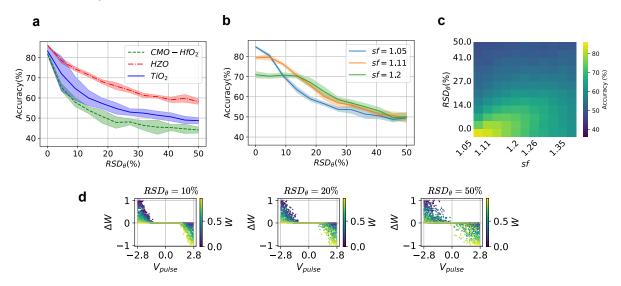

| 4.6          | Impact of device-to-device variability in switching threshold 8                                                                                                                                                                 |

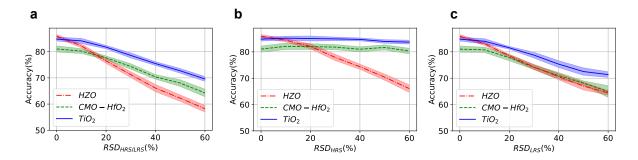

| 4.7          | Impact of device-to-device variability in HRS and LRS levels                                                                                                                                                                    |

| 4.1          | The fitted model's prediction on characterization data points 9                                                                                                                                                                 |

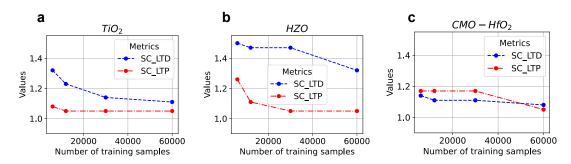

| 4.2          | Scaling factor based on the number of training samples                                                                                                                                                                          |

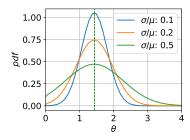

| 4.3          | Probability distribution function of $\theta$ for $TiO_2$ , showing variability in the                                                                                                                                          |

| 4.4          | form of relative standard dispersion $\left(\frac{\sigma}{\mu}\right)$                                                                                                                                                          |

| 4.5          | MNIST benchmark results for CMO-HfO <sub>2</sub> device                                                                                                                                                                         |

|              |                                                                                                                                                                                                                                 |

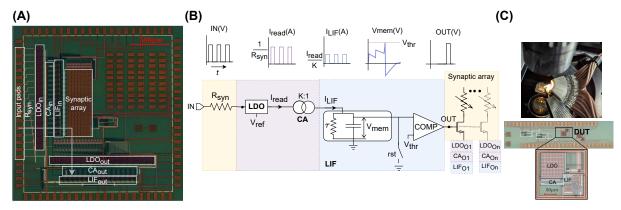

| 5.1          | Proposed architectures and approach: "UNICO" ASIC signal chain con-                                                                                                                                                             |

| 5.2          | nects input to output neurons via synaptic arrays                                                                                                                                                                               |

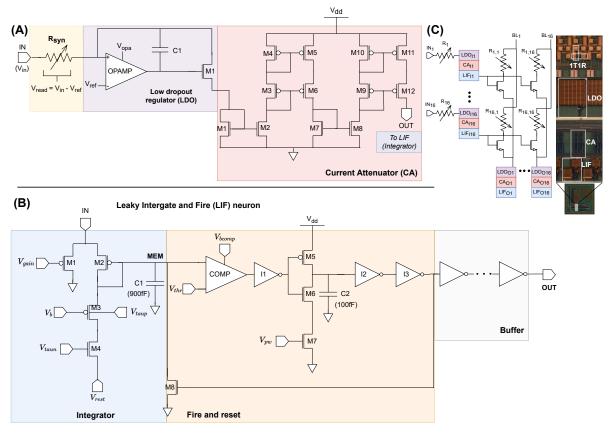

| 0.2          | uator (CA), and Leaky Integrate and Fire (LIF) neuron                                                                                                                                                                           |

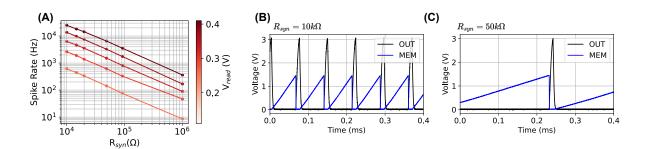

| 5.3          | Characterization of neuron's sensitivity to synaptic resistance                                                                                                                                                                 |

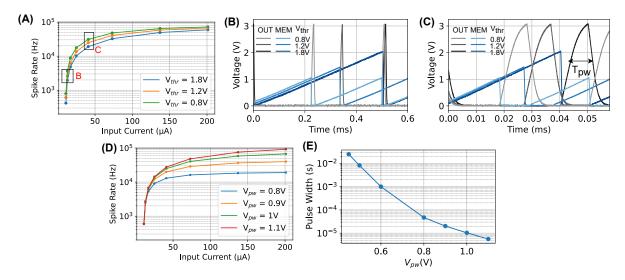

| 5.4          | Characterization of neuron's transfer function with DC excitation 10                                                                                                                                                            |

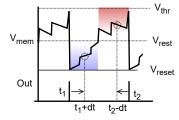

| 5.5          | Illustrative plot to show the behavior of a neuron with bi-directional leakage.10                                                                                                                                               |

| 5.6          | Characterization of temporal dynamics and modulation of leak rate through                                                                                                                                                       |

|              | bias voltages                                                                                                                                                                                                                   |

| 5.7          | Connection scheme to realize an adaptive LIF neuron with a pair of LIF neurons                                                                                                                                                  |

|              | neurons                                                                                                                                                                                                                         |

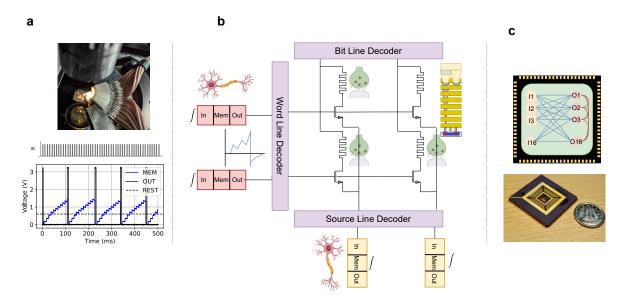

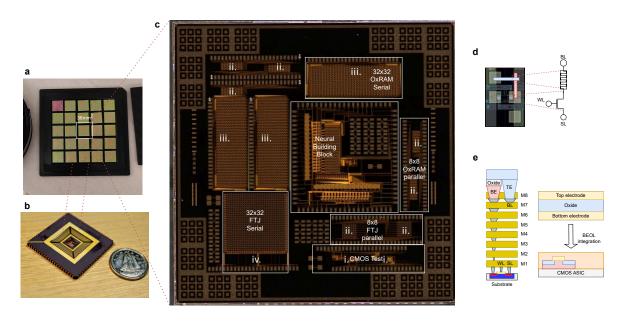

| 6.1          | Overview of Neural Building Block (NBB): micrograph and packaged die 11                                                                                                                                                         |

| 6.2          | Data path of NBB and modes of operation                                                                                                                                                                                         |

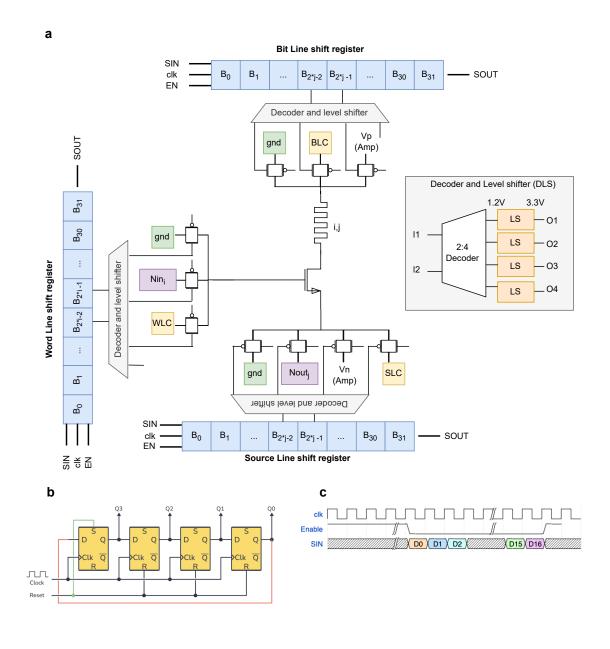

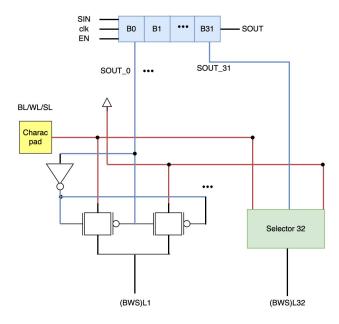

| 6.3          | Crossbar addressing circuits and logic                                                                                                                                                                                          |

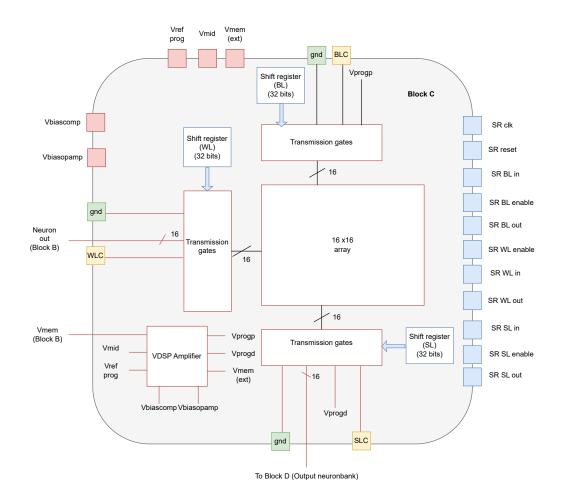

| 6.4          | Top Schematic Diagram of Block C (Crossbar Block). Around the 16x16 1T1R array, banks of transmission gates are serially configured by shift                                                                                    |

| 65           | registers                                                                                                                                                                                                                       |

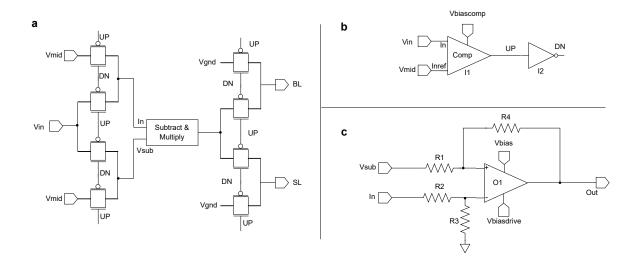

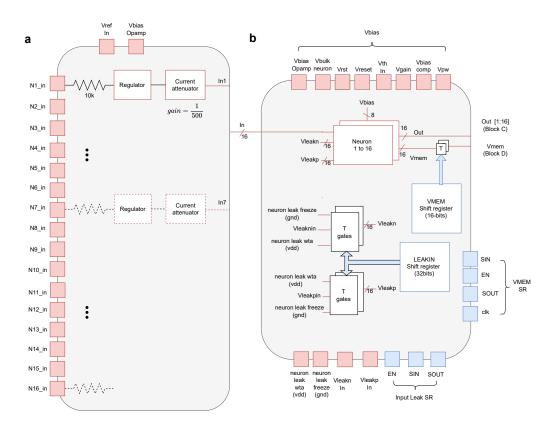

| $6.5 \\ 6.6$ | Schematic block diagram of input neuron bank: Block (A-B)                                                                                                                                                                       |

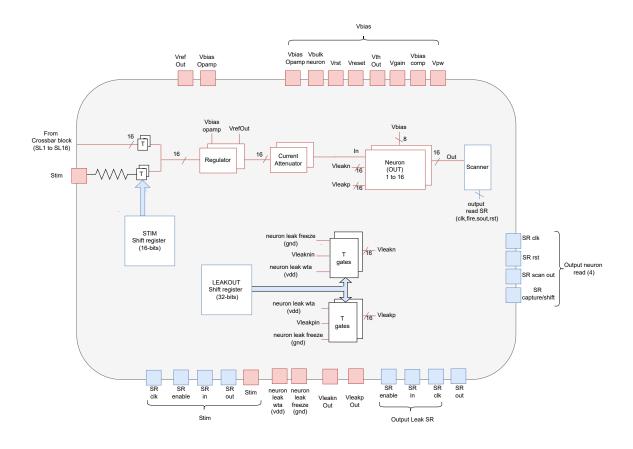

| 6.7          | Schematic diagram of Block D: Output neuron bank                                                                                                                                                                                |

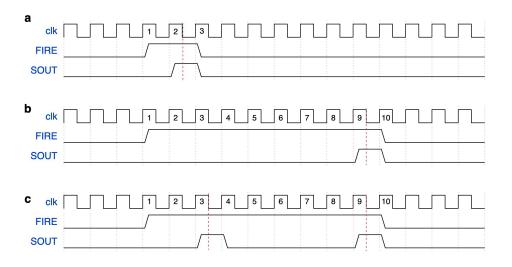

| 6.8          | Output block timing diagram illustrating the scanning logic for clk, FIRE,                                                                                                                                                      |

|              | and SOUT signals                                                                                                                                                                                                                |

LIST OF FIGURES xvii

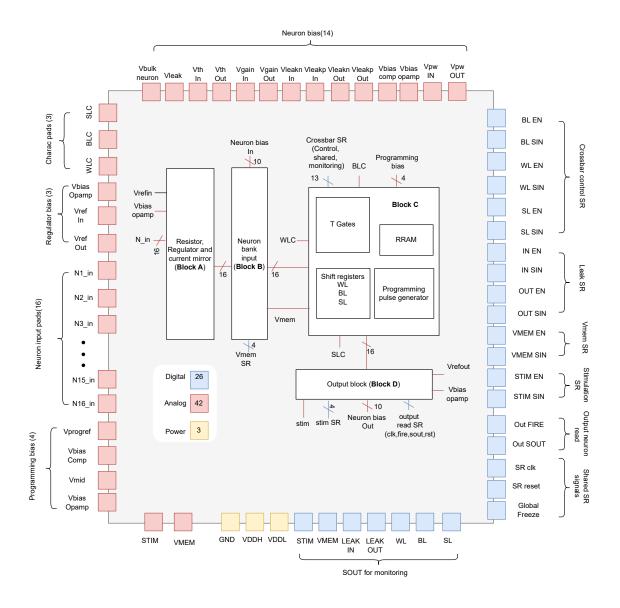

| 6.9  | Schematic block diagram of NBB                                                 | 132 |

|------|--------------------------------------------------------------------------------|-----|

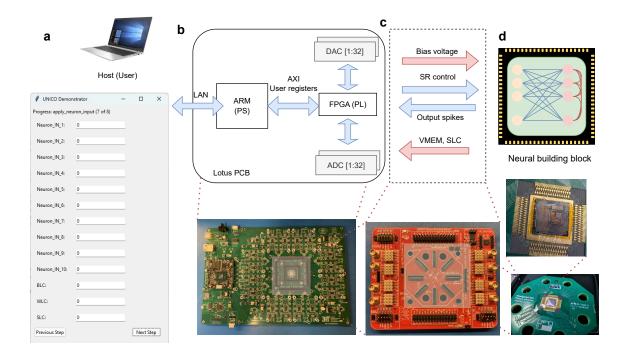

| 6.10 | Communication and control path from the PC to the UNICO chip via the           |     |

|      | Lotus testing system                                                           | 137 |

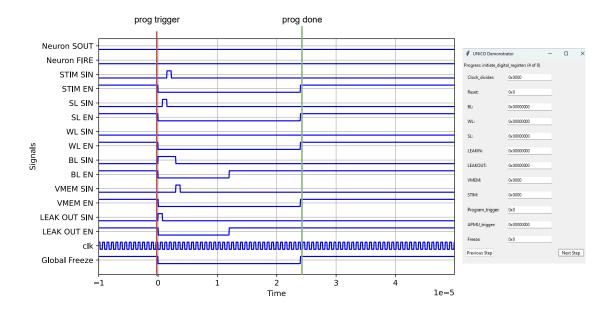

| 6.11 | Configuring on-chip shift registers. (left) Graphical user interface (GUI) for |     |

|      | custom configuration by user                                                   | 140 |

| 6.12 | Characterization results of the output neuron bank (left) and GUI param-       |     |

|      | eters for the parametric sweep of the output neuron bank (right)               | 142 |

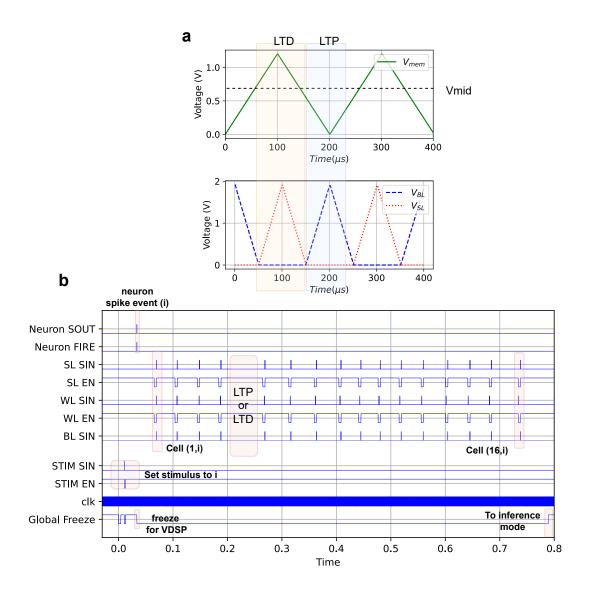

| 6.13 | VDSP programming results of amplifier and digital configuration logic          | 144 |

| 6.14 | UNICO ASIC for Back end of the line (BEOL) integration of synaptic             |     |

|      | memories through 1T1R architecture                                             | 146 |

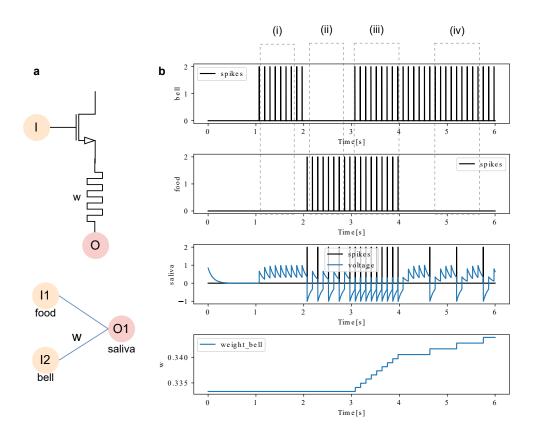

| 6.15 | Associative learning demonstration                                             |     |

|      | Pattern learning demonstration with synthetic images                           |     |

| 7.1  | Multi care architecture with plactic intercorports                             | 160 |

| -    | Multi-core architecture with plastic interconnects                             |     |

| 7.2  | Interfacing silicon and biological neural networks                             | 104 |

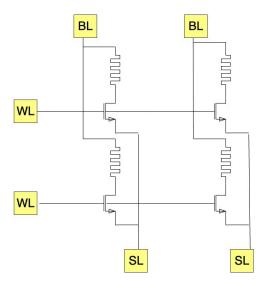

| A.1  | Single 1T1R                                                                    | 173 |

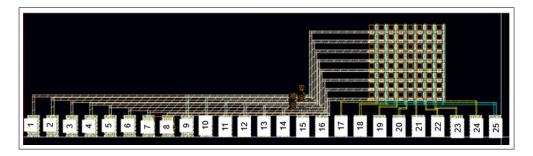

| A.2  | 2x2 representation of 8x8 parallel memory characterization array               | 173 |

| A.3  | 8x8 parallel memory characterization cell                                      | 174 |

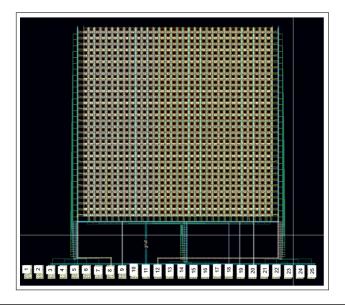

| A.4  | 32x32 memory characterization cell                                             | 175 |

| A.5  | Shift register for addressing a single row or column of 32x32 crossbar array   | 175 |

# LIST OF TABLES

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5   | Spike-based local synaptic plasticity rules: comparative table Neuromorphic circuits for spike-based local synaptic plasticity models Neuromorphic hardware systems using digital circuits                                                                                                                                                                                                                                                                                                                                          | 22<br>25<br>28<br>30 |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 3.1                               | In order to reproduce the results of this study, the same can be used in conjunction with proposed equations of the VDSP rule with a learning rate equal to $5 \times 10^{-2}$                                                                                                                                                                                                                                                                                                                                                      | FO                   |

| 3.2                               | The performance achieved by training SNN with the VDSP rule is tabulated for various network sizes (number of output neurons) and epochs. Each experiment was repeated with five different initial conditions, and the accuracies are reported as (Mean $\pm$ S.D.). Compared with the hardware-independent approach of pair based STDP, we achieved 84.74 $\pm$ 1.08% for a network of 100 output neurons trained over three epochs. For a network of 400 output neurons trained over three epochs, we achieved 89.26 $\pm$ 0.54%. | . 53                 |

| 4.1                               | Model parameters for $TiO_2$ , HZO, and CMO-HfO <sub>2</sub> devices along with the high resistance state (HRS) and low resistance state (LRS). Additionally, the table presents the root mean square error (RMSE) of $\Delta W$ , comparing characterization data with model predictions.                                                                                                                                                                                                                                          | 80                   |

| 4.2                               | Comparison of the current study with previous memristive-based online learning benchmarks with MNIST. Different device technologies, including Phase change (PCM), Magnetic tunnel junction (MTJ), and electrochemical metallization (ECM) with circuit configurations, are tabulated for classic, stochastic, and simplified versions of STDP with respective network architectures.                                                                                                                                               | 89                   |

| 5.1                               | Bias voltages used in circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 107                  |

| 6.1<br>6.2                        | Configuration Shift Registers and their Bit Widths in NBB                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 133                  |

| 6.3                               | Input and output pads with Analog and Digital Input/Output (IO) signals                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 199                  |

| 6.4                               | assigned to IDs of Lotus for IN1 to IN16, BLC, WLC, SLC, VMEM, and STIM Bias Voltages (Names in schematics) with identification and Analog and                                                                                                                                                                                                                                                                                                                                                                                      | 134                  |

| c r                               | 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 135                  |

| 6.5<br>6.6                        | AXI Slave Registers: ID, Name, Width, and Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 138<br>139           |

| <ul><li>6.7</li><li>6.8</li></ul> | Characterization of VDSP learning experiment: GUI parameters for stimulating a single neuron (crossbar column) to trigger the update sequence. User parameters for performing demonstration of online learning                                                                                                                                                                                                                                                                                                                      | 145                  |

| 0.0                               | oser parameters for performing demonstration of offine learning                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TOO                  |

LIST OF TABLES

| A.1 | 8x8 Parallel characterization cell: Pin Number and Name | 174 |

|-----|---------------------------------------------------------|-----|

| A.2 | HZO Serial: Pin Number, Name, A/D/P, and I/O            | 176 |

XX

# LIST OF ACRONYMS

| Acronym             | Definition                              |

|---------------------|-----------------------------------------|

| ADC                 | Analog to Digital Converter             |

| AER                 | Address Event Representation            |

| AI                  | Artificial Intelligence                 |

| ANN                 | Artificial Neural Network               |

| APMU                | Analog Pulse Measurement Unit           |

| ART                 | Adaptive Resonance Theory               |

| ASIC                | Application Specific Integrated Circuit |

| BDSP                | Burst-Dependent Synaptic Plasticity     |

| BCM                 | Bienenstock Cooper Munro                |

| BEOL                | Back End of Line                        |

| $\operatorname{BL}$ | Bit Line                                |

| BP                  | Back-Propagation                        |

| BPTT                | Back-Propagation Through Time           |

| CA                  | Current Attenuator                      |

| CAM                 | Content Addressable Memory              |

| C-MPDP              | Calcium-based MPDP                      |

| CNN                 | Convolutional Neural Network            |

| CMOS                | Complementary Metal-Oxide-Semiconductor |

| CPU                 | Central Processing Unit                 |

| C-STDP              | Calcium-based STDP                      |

| DAC                 | Digital to Analog Converter             |

| DPI                 | Differential Pair Integrator            |

| DPSS                | Dendritic Prediction of Somatic Spiking |

| DVS                 | Dynamic Vision Sensor                   |

| FDSOI               | Fully Depleted Silicon On Insulator     |

| FPGA                | Field Programmable Gate Array           |

| GPIO                | General-Purpose Input/Output            |

| GPU                 | Graphics Processing Unit                |

| GUI                 | Graphical User Interface                |

| HMPDP               | Homeostatic MPDP                        |

| ICA                 | Independent Component Analysis          |

| IC                  | Integrated Circuit                      |

| IoT                 | Internet of Things                      |

| LCA                 | Locally Competitive Algorithm           |

| LDO                 | Low Dropout Regulator                   |

| LIF                 | Leaky Integrate and Fire                |

| LTD                 | Long-Term Depression                    |

| LTP                 | Long-Term Potentiation                  |

| MPDP                | Membrane Potential Dependent Plasticity |

| Acronym             | Definition                             |

|---------------------|----------------------------------------|

| NBB                 | Neural Building Block                  |

| NEF                 | Neural Engineering Framework           |

| NLP                 | Natural Language Processing            |

| OpAmp               | Operational Amplifier                  |

| OTA                 | Operational Transconductance Amplifier |

| PCA                 | Principal Component Analysis           |

| PCM                 | Phase Change Memory                    |

| PCB                 | Printed Circuit Board                  |

| RAM                 | Random Access Memory                   |

| RBM                 | Restricted Boltzmann Machine           |

| RDSP                | Rate Dependent Synaptic Plasticity     |

| RRAM                | Resistive Random Access Memory         |

| RTRL                | Real-Time Recurrent Learning           |

| SDSP                | Spike-Driven Synaptic Plasticity       |

| $\operatorname{SL}$ | Source Line                            |

| SNN                 | Spiking Neural Network                 |

| SOA                 | State-of-the-art                       |

| SBCM                | Spiking BCM                            |

| SR                  | Shift Register                         |

| SRAM                | Static Random Access Memory            |

| SRDP                | Spike-Rate Dependent Plasticity        |

| STDP                | Spike-Timing Dependent Plasticity      |

| TA                  | Transconductance Amplifier             |

| TGATE               | Transmission Gate                      |

| TSTDP               | Triplet-based STDP                     |

| TPU                 | Tensor Processing Unit                 |

| VDSP                | Voltage Dependent Synaptic Plasticity  |

| VLSI                | Very Large Scale Integration           |

| VMM                 | Vector Matrix Multiplication           |

| V-STDP              | Voltage-based STDP                     |

| WL                  | Word Line                              |

| WTA                 | Winner-Take-All                        |

## **CHAPTER 1**

## Introduction

"All truths are easy to understand once they are discovered; the point is to discover them. The challenge in science is not just in understanding, but in finding the right questions to ask. Once the right question is asked, the path to discovery becomes clearer, and what once seemed impossible becomes within reach. " – Galileo Galilei

## TABLE OF CONTENTS

| 1.1 | Conte      | xt                                                                   | 2  |  |

|-----|------------|----------------------------------------------------------------------|----|--|

| 1.2 | Challenges |                                                                      |    |  |

| 1.3 | Resear     | rch question and objectives                                          | 6  |  |

|     | 1.3.1      | On device learning                                                   | 7  |  |

|     | 1.3.2      | Circuits                                                             | 7  |  |

| 1.4 | Organ      | nization of thesis                                                   | 8  |  |

|     | 1.4.1      | Background                                                           | 8  |  |

|     | 1.4.2      | Voltage dependent synaptic plasticity                                | 9  |  |

|     | 1.4.3      | Learning with memristive synapses                                    | 9  |  |

|     | 1.4.4      | CMOS neuron for memristor integrated neuromorphic circuits $\dots$ . | 10 |  |

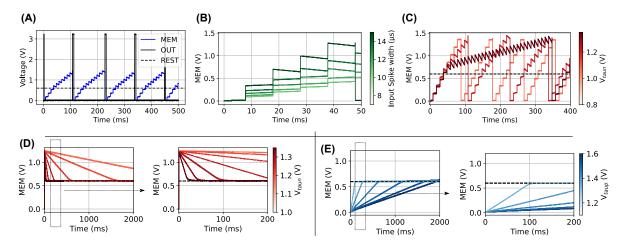

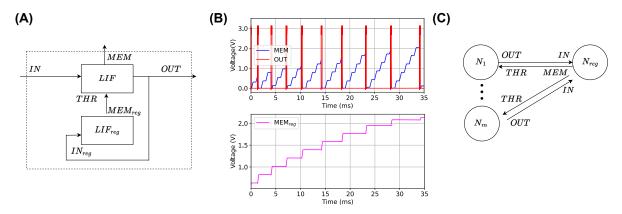

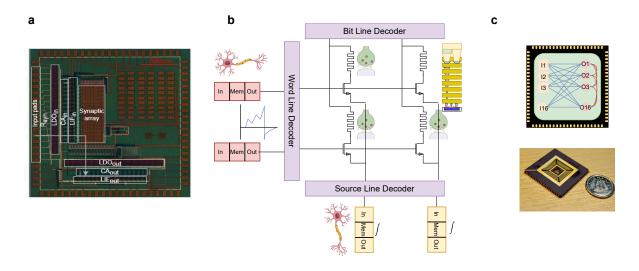

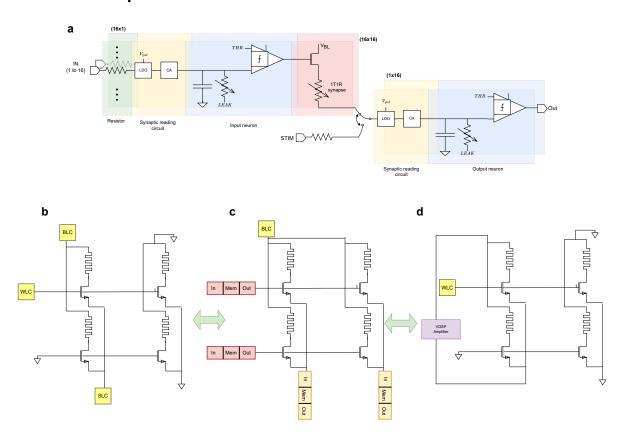

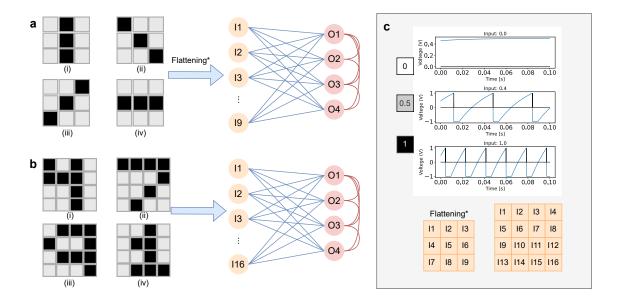

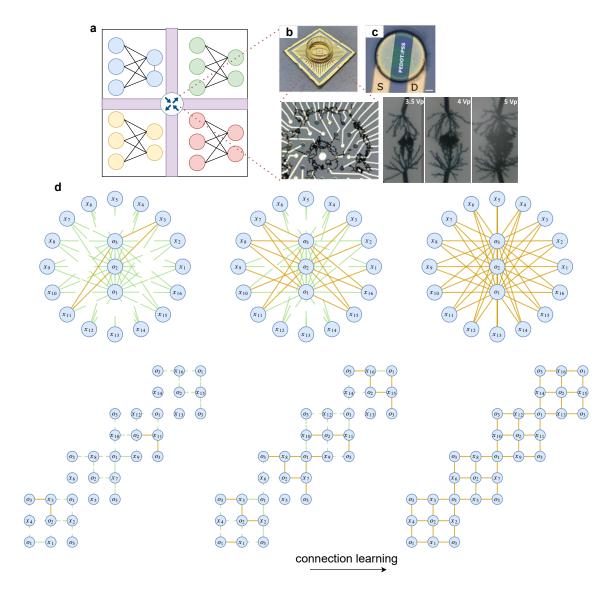

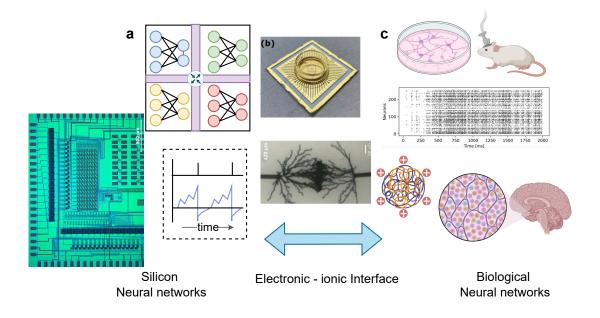

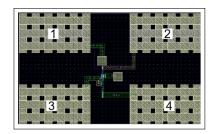

|     | 1.4.5      | Neural building block for 3D integrated CMOS-RRAM SNNs               | 11 |  |