## Université de Lille Coventry University

École doctorale ENGSYS-632

Unité de recherche Laboratoire d'Électrotechnique et d'Électronique de Puissance - L2EP

Thèse présentée par **Xuyang LU**Soutenue le **7 avril 2025**

En vue de l'obtention du grade de docteur de l'Université de Lille et de l'Coventry University

Discipline **Sciences Pour l'Ingénieur** Spécialité **Génie électrique**

# Analyse du comportement de commutation des transistors GaN-HEMTs dans les convertisseurs de puissance en tenant compte de la variation de Vth et de la configuration du driver de grille

Thèse dirigée par

Nadir Idir directeur

Petar Igic co-directeur

Arnaud Videt co-encadrant

Soroush Faramehr co-encadrant

Vlad Marsic co-encadrant

### Composition du jury

Rapporteurs Cyril Buttay directeur de recherche au CNRS à l'INSA de Lyon présidente du jury

Milijana Odavic professeur à l'University of Sheffield

Examinateurs Philip Mawby professeur à l'University of Warwick

Nicolas Rouger directeur de recherche au CNRS à l'ENSEEIHT de Toulouse

Invités Arnaud Videt McF à l'Université de Lille

Soroush Faramehr MCF au Coventry University

Directeurs de thèse Nadir Idir professeur à l'Université de Lille

Petar Igic professeur au Coventry University

# Université de Lille Coventry University

Doctoral School ENGSYS-632

University Department Laboratoire d'Électrotechnique et d'Électronique de Puissance - L2EP

Thesis defended by Xuyang LU

Defended on April 7, 2025

In order to become Doctor from Université de Lille and from Coventry University

Academic Field **Engineering Science** Speciality **Electrical Engineering**

# Switching behaviour analysis of GaN-HEMTs in power converters considering Vth shift and gate driver configuration

Thesis supervised by Nadir Idir Supervisor

Petar IGIC Co-Supervisor

Arnaud Videt Co-Monitor

Soroush Faramehr Co-Monitor

Vlad Marsic Co-Monitor

### Committee members

Referees Cyril Buttay Senior Researcher at CNRS à l'INSA de Lyon President of Jury

Milijana Odavic Professor at University of Sheffield

Examiners Philip Mawby Professor at University of Warwick

Nicolas Rouger Senior Researcher at CNRS à l'ENSEEIHT de Toulouse

Guests Arnaud Videt Associate Professor at Université de Lille

Soroush Faramehr Associate Professor at Coventry University

Supervisors Nadir Idir Professor at Université de Lille

Petar Igic Professor at Coventry University

# Switching behaviour analysis of GaN-HEMTs in power converters considering Vth shift and gate driver configuration

# by Xuyang Lu

A thesis submitted in partial fulfilment of the University's requirements for the Degree of Doctor of Philosophy

November 2024

This thesis is a collaborative work between the Coventry University and the University of Lille.

# **Certificate of Ethical Approval**

Applicant: Xuyang Lu

Project Title: Design of GaN-Based Power Converters for Electric Mobility

This is to certify that the above named applicant has completed the Coventry University Ethical Approval process and their project has been confirmed and approved as Low Risk

Date of approval: 04 Jan 2022

Project Reference Number: P130936

This thesis has been prepared at the following research units.

# Laboratoire d'Électrotechnique et d'Électronique de Puissance - L2EP

Bâtiment ESPRIT Avenue Henri Poincaré 59655 Villeneuve d'Ascq France

**a** 03 62 26 82 10

Web Site https://l2ep.univ-lille.fr/

Centre for E-Mobility and Clean Growth - CECG

Coventry Innovation Village Cheetah Rd Coventry CV1 2TL United Kingdom CENTRE FOR ADVANCED LOW-CARBON PROPULSION SYSTEMS

**a** (0)24 7765 7688

Web Site https://www.coventry.ac.uk/research/curie/clean-growth/

This thesis has been funded by

### Région Hauts-de-France

151 Avenue du président Hoover 59555 LILLE CEDEX France

**a** (0)3 74 27 00 00

Web Site https://www.hautsdefrance.fr/

**Keywords:** GaN power transistors, threshold voltage measurement, semiconductor transistors modelling, switching behaviour, circuit parasitic parameters.

**Mots clés:** GaN transistor de puissance, mesure de tension de seuil, modélisation des transistors semi-conducteurs, comportement de commutation, paramètres parasites du circuit.

Abstract

SWITCHING BEHAVIOUR ANALYSIS OF GAN-HEMTS IN POWER CONVERTERS CONSIDERING VTH SHIFT AND GATE DRIVER CONFIGURATION

### **Abstract**

This thesis investigates the influence of threshold voltage  $(V_{\rm th})$  shift and gate driver's output capacitance on the switching behaviour of gallium nitride high electron mobility transistors (GaN-HEMTs). Understanding these factors is crucial for accurate device modelling and switching performance estimation before employing the GaN-HEMTs in power converters. The first chapter of the thesis introduces the origin and characterisation methods of the  $V_{\rm th}$  shift phenomenon in GaN-HEMTs. In the second chapter, an in-situ  $V_{\rm th}$  measurement method is proposed to characterise the  $V_{\rm th}$  shift phenomenon under soft-switching conditions in both single- and multi-pulse modes. The third chapter studies the impact of  $V_{\rm th}$  shift on the switching behaviour of the transistors through theoretical analysis, demonstrated by simulation and experimental validation. In the final chapter, the influence of the gate driver's output capacitance on the switching behaviour of GaN-HEMTs is investigated in two common gate configurations: single and split outputs. Equivalent circuits for both configurations are presented to illustrate their effect on transistors driving performance. The results clearly show that both the positive  $V_{\rm th}$  shift and the output capacitance in the split output gate driver can slow down the turn-on commutation speed of GaN-HEMTs.

**Keywords:** GaN power transistors, threshold voltage measurement, semiconductor transistors modelling, switching behaviour, circuit parasitic parameters.

Analyse du comportement de commutation des transistors GaN-HEMTs dans les convertisseurs de puissance en tenant compte de la variation de Vth et de la configuration du driver de grille

### Résumé

Cette thèse s'intéresse à l'influence de la variation de la tension de seuil  $(V_{th})$  et de la capacité de sortie du driver de grille sur le comportement en commutation des transistors à haute mobilité d'électrons en nitrure de gallium (GaN-HEMTs). Comprendre ces facteurs est crucial pour une modélisation précise des dispositifs et pour une bonne estimation des performances en commutation avant d'employer les GaN-HEMTs dans les convertisseurs de puissance. La première partie de la thèse présente l'origine et les méthodes de caractérisation du phénomène de variation de  $V_{th}$  dans les GaN-HEMTs. Dans le deuxième chapitre, une méthode de mesure insitu de  $V_{th}$  est proposée pour caractériser le phénomène de variation de  $V_{th}$  dans des conditions de commutation douce, en modes mono-impulsion et multi-impulsion. Le troisième chapitre étudie l'impact de la variation de  $V_{\mathsf{th}}$  sur le comportement en commutation à travers une analyse théorique, démontrée par simulation et par validation expérimentale. Dans la dernière partie, l'influence de la capacité de sortie du driver de grille sur le comportement en commutation des GaN-HEMTs est examinée dans deux configurations de grille courantes : sortie unique et sortie séparée. Des circuits équivalents pour les deux configurations sont présentés pour illustrer leur effet sur les performances de commande rapprochée des transistors. Les résultats montrent qu'aussi bien l'augmentation de  $V_{th}$  que la capacité de sortie du driver de grille à sorties séparées peuvent ralentir la vitesse de commutation à la mise en conduction des GaN-HEMTs.

**Mots clés :** GaN transistor de puissance, mesure de tension de seuil, modélisation des transistors semi-conducteurs, comportement de commutation, paramètres parasites du circuit.

Laboratoire d'Électrotechnique et d'Électronique de Puissance - L2EP – Bâtiment ESPRIT – Avenue Henri Poincaré – 59655 Villeneuve d'Ascq – France Centre for E-Mobility and Clean Growth - CECG – Coventry Innovation Village – Cheetah Rd – Coventry CV1 2TL – United Kingdom

x Abstract

# Acknowledgement

This thesis is a collaborative work between the Laboratoire d'Électrotechnique et d'Électronique de Puissance de Lille (L2EP) at Université de Lille and the Centre for E-Mobility and Clean Growth (CECG) at Coventry University. After three years of effort, spanning multiple trips between two countries, I am finally at the end of my PhD journey. I would like to express my deepest gratitude to everyone who helped, supported, and encouraged me along the way.

First of all, I would like to express my sincere gratitude to all the members of my thesis defense jury for their time and effort in reviewing my work. I am deeply grateful to Mr. Cyril Buttay, Senior Researcher at the INSA de Lyon, for serving as the president and reporter of my defense. I also extend my thanks to Prof. Milijana Odavic from the University of Sheffield for her valuable evaluation report on my thesis. My sincere appreciation goes to Prof. Philip Mawby from the University of Warwick and Mr. Nicolas Rouger, Senior Researcher at the ENSEEIHT de Toulouse, for their thorough examination of my research.

I am profoundly grateful to my supervisor, Prof. Nadir Idir from the Université de Lille, and my co-supervisor, Prof. Petar Igic from Coventry University, for their trust in me and for welcoming me into two research teams with complementary expertise. I deeply appreciate their invaluable guidance, professional advice, and steadfast support throughout my thesis. My sincere thanks also go to Dr. Arnaud Videt from the Université de Lille, for his extensive knowledge of power electronics and his rigorous approach to scientific problems. His passion for research will continue to inspire me. Furthermore, I am immensely grateful to my director of studies at Coventry University, Dr. Soroush Faramehr, for introducing me to the world of semiconductor physics and for his comprehensive support during the entirety of my thesis. I would also like to express my thanks to Dr. Vlad Marsic from Coventry University, for his continuous assistance, insightful discussions, and critical perspective on this work.

I would also like to acknowledge Dr. Ke Li, my former supervisor, who was instrumental in shaping the research direction at the early stage of my thesis.

I am equally thankful to Mr. Thierry Duquesne, design engineer at L2EP, for his invaluable assistance with PCB fabrication and modification, and to Ms. Anouchka Loeuil for her professionalism and dedication in handling all of my administrative matters. The same thanks goes to the administrative staff of CECG.

I am also grateful to my colleagues in the L2EP power electronics team, Nicolas, Issa,

Morteza, Mehyeddine, Idriss, Maxime and Quyen, for the interesting discussions we had in the lab. A special thanks goes to Florentin, my friend and former colleague at L2EP, for his programming expertise and plenty of helpful discussions that helped shape my research in its early stages.

My heartfelt thanks also extend to my friends at L2EP — Caio, Lauro, Eduard, Wenjing, Ayoub, Hugo, Anthony, Zhi, and Ze, and my friends at CECG — Lu, Mehran, Safeer, Luke, Arun, Vartika, Wissam, Chongming, and Saud. Your friendship and camaraderie have made the journey of scientific research vibrant and memorable.

Lastly, I would like to express a deep gratitude to my family for their unwavering support and encouragement over the past three years. Thank you for providing me with a nurturing environment that has allowed me to pursue my dreams.

Finally, thank you, Qiuyu. Without your company and encouragement, I cannot imagine how hard this journey could be.

# Acronyms

| 2DEG (2-dimentional electron gas)                              | 9   |

|----------------------------------------------------------------|-----|

| ADC (analog to digital converter)                              | 46  |

| ADS (Advanced Design System)                                   | 150 |

| AI (artificial intelligence)                                   | 4   |

| AlN (aluminium nitride)                                        | 8   |

| BFOM (Baliga figure of merit)                                  | 7   |

| CTE (coefficient of thermal expansion)                         | 17  |

| DPT (double-pulse test)                                        | 36  |

| DUT (device under test)                                        | 21  |

| EMI (electromagnetic interference)                             | 34  |

| FOM (figure of merit)                                          | 7   |

| GaN (gallium nitride)                                          | 4   |

| GaN-HEMTs (gallium nitride high electron mobility transistors) | 4   |

| GNDU (ground unit)                                             | 65  |

| HVHC (high-voltage and high-current)                           | 97  |

| HVSMU (high voltage source/measure unit)                       | 65  |

| ICs (integrated circuits)                                      | 16  |

| IGBTs (insulated gate bipolar transistors)                     | 4   |

| JFETs (junction field-effect transistors)                      | 17  |

| JFOM (Johnson figure of merit)                                 | 7   |

| LLC (inductor-inductor-capacitor)                              | 5   |

| xiv | Acronyms |

|-----|----------|

|     |          |

| MCSMU (medium current source/measure unit)                   | 65  |

|--------------------------------------------------------------|-----|

| Mg (magnesium)                                               | 13  |

| MIS (metal insulator semiconductor)                          | 12  |

| MOSFETs (metal oxide semiconductor field effect transistors) | 12  |

| NMOS (N-channel MOSFETs)                                     | 133 |

| PFC (power factor correction)                                | 4   |

| PMOS (P-channel MOSFETs)                                     | 133 |

| PWM (pulse-width modulation)                                 | 50  |

| RF (radio frequency)                                         | 18  |

| Si (silicon)                                                 | 3   |

| SiC (silicon carbide)                                        | 4   |

| SiN (silicon nitride)                                        | 11  |

| SMT (surface mount technology)                               | 38  |

| SPICE (simulation program with integrated circuit emphasis)  | 97  |

| SPOGC (split output gate configuration)                      | 139 |

| TSEP (temperature sensitive electrical parameter)            | 33  |

| UID (unintentionally doped)                                  | 9   |

| UVLO (under voltage lockout)                                 | 147 |

| WBG (wide band-gap)                                          | 4   |

# Symbols

| t <sup>g</sup> <sub>r</sub> (rise time of gate driver)         | 138 |

|----------------------------------------------------------------|-----|

| C <sub>iss</sub> (input capacitance of power GaN-HEMTs)        | 135 |

| C <sub>oss</sub> (output capacitance of NMOS)                  | 133 |

| $V_{ m pl}^{ m off}$ (plateau voltage in turn-off commutation) | 90  |

| $V_{\rm pl}^{\rm on}$ (plateau voltage in turn-on commutation) | 90  |

| C <sub>oss</sub> (output capacitance of PMOS)                  | 133 |

| $T_{\rm c}$ (case temperature)                                 | 22  |

| $C_{ds}$ (drain-to-source capacitance)                         | 89  |

| C <sub>gd</sub> (gate-to-drain capacitance)                    | 36  |

| C <sub>gs</sub> (gate-to-source capacitance)                   | 36  |

| $L_{cs}$ (common-source inductance)                            | 37  |

| $L_{\rm d}$ (power loop parasitic inductance)                  | 37  |

| $V_{DD}$ (digital operating voltage)                           | 157 |

| $L_{\rm g}$ (gate loop parasitic inductance)                   | 37  |

| $g_{\rm m}$ (maximum transconductance)                         | 20  |

| C <sub>iss</sub> (input capacitance)                           | 36  |

| $T_{\rm j}$ (junction temperature)                             | 22  |

| $R_{\theta \text{jc}}$ (junction-to-case thermal resistance)   | 69  |

| $t_{\rm m}$ (measurement response time)                        | 20  |

| $E_{\rm cn}$ (turn-on switching energy)                        | 155 |

| xvi                                            | Symbols |

|------------------------------------------------|---------|

| $C_{\rm oss}$ (output capacitance)             | 36      |

| P <sub>on</sub> (turn-on switching power)      | 155     |

| $V_{\rm pl}$ (plateau voltage)                 | 90      |

| $t_{\rm r}$ (rise time)                        | 101     |

| $R_{\rm g}^{\rm off}$ (turn-off gate resistor) | 92      |

| $R_{\rm g}^{\rm on}$ (turn-on gate resistor)   | 92      |

| $R_{on}$ (on-state resistance)                 | 4       |

| $C_{rss}$ (reverse transfer capacitance)       | 36      |

| $V_{th}$ (threshold voltage)                   | 5       |

| $V_{\rm g}$ (gate voltage)                     | 10      |

| $Z_{in}$ (input impedance)                     | 151     |

# **Table of Contents**

| A  | bstract                                                                 | ix    |

|----|-------------------------------------------------------------------------|-------|

| A  | cknowledgement                                                          | xi    |

| A  | cronyms                                                                 | xiii  |

| S  | ymbols                                                                  | xv    |

| T  | able of Contents                                                        | xvii  |

| Li | st of Tables                                                            | xxi   |

| L  | st of Figures                                                           | xxiii |

| I1 | troduction                                                              | 1     |

| 1  | GaN transistors state-of-the art review                                 | 3     |

|    | 1.1 Research context                                                    | 4     |

|    | 1.1.1 Energy conversion efficiency                                      | 5     |

|    | 1.1.2 Power density and sustainability                                  | 5     |

|    | 1.2 GaN material and power transistors                                  | 6     |

|    | 1.2.1 Material properties comparison of Si, SiC and GaN                 |       |

|    | 1.2.2 Basic structure and operating principle of power GaN-HEMTs        | 8     |

|    | 1.2.3 p-GaN gate HEMTs                                                  | 14    |

|    | 1.2.4 Vertical GaN power transistors                                    | 17    |

|    | 1.2.5 Type of GaN transistors used in this study                        |       |

|    | 1.3 Trapping effect and parametric shift of GaN-HEMTs                   |       |

|    | 1.3.1 Trapping effect                                                   | 19    |

|    | 1.3.2 Dynamic on-state resistance                                       |       |

|    | 1.3.3 Threshold voltage shift                                           |       |

|    | 1.3.4 $V_{\text{th}}$ shift issues investigated in this work            |       |

|    | 1.4 Impact of parasitic parameters on GaN-HEMTs application             |       |

|    | 1.4.1 Small inter-electrode capacitance and fast switching speed        |       |

|    | 1.4.2 Influence of parasitic parameters on GaN-HEMTs switching behavior | ur 38 |

xviii Table of Contents

|   |      | 1.4.3 Parasitic parameters considered in this work                                                                                         | 42       |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------|----------|

|   | 1.5  | Summary of findings                                                                                                                        | 42       |

|   |      |                                                                                                                                            |          |

| 2 | Cha  | aracterisation of off-state $V_{\sf ds}$ bias induced $V_{\sf th}$ shift                                                                   | 45       |

|   |      | Half-bridge based $V_{th}$ shift measurement method                                                                                        | 46       |

|   |      | 2.1.1 Third quadrant characteristics of GaN-HEMTs                                                                                          | 46       |

|   |      | 2.1.2 Measurement schematic and principle                                                                                                  | 48       |

|   |      | 2.1.3 Experiment setup                                                                                                                     | 53       |

|   | 2.2  | Single pulse mode test                                                                                                                     | 54       |

|   |      | 2.2.1 Off-state $V_{ds}$ bias induced $V_{th}$ shift                                                                                       | 54       |

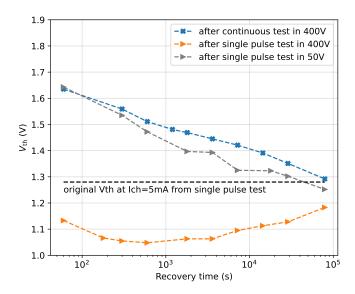

|   |      | 2.2.2 Recovery behaviour of the shifted $V_{\text{th}}$ for GaN-HEMTs                                                                      | 64       |

|   |      | 2.2.3 Summary of the single pulse test                                                                                                     | 70       |

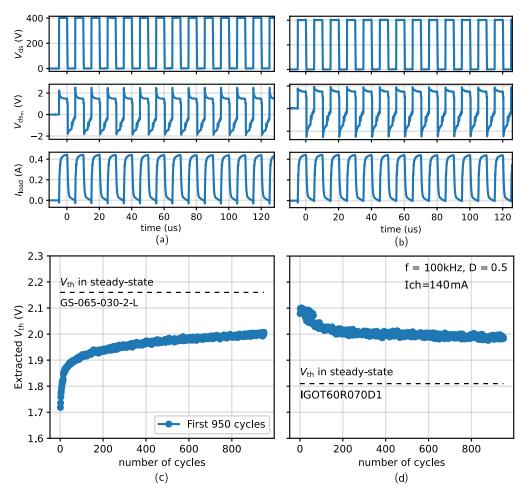

|   | 2.3  | Continuous mode test                                                                                                                       | 70       |

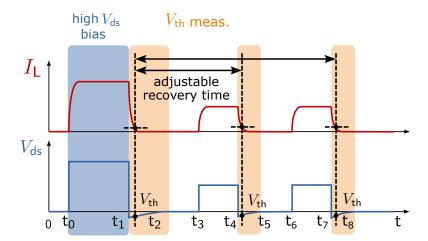

|   |      | 2.3.1 $V_{\text{th}}$ measurement principle in continuous mode                                                                             | 71       |

|   |      | 2.3.2 Measurement result of $V_{\text{th}}$ in steady-state                                                                                | 72       |

|   |      | 2.3.3 Summary of the continuous mode test                                                                                                  | 80       |

|   | 2.4  | Conclusion and discussion                                                                                                                  | 82       |

|   |      | 2.4.1 $V_{\text{th}}$ shift variation in single pulse and continuous test                                                                  | 82       |

|   |      | 2.4.2 Limitation and future work                                                                                                           | 83       |

|   |      | 2.4.3 Influence of the shifted $V_{th}$ on device performance                                                                              | 84       |

| 2 | Infl | wones of W. shift on the switching behaviour                                                                                               | 85       |

| 3 |      | luence of $V_{\text{th}}$ shift on the switching behaviour                                                                                 | 86       |

|   | 3.1  | $V_{th}$ shift phenomenon in double-pulse test                                                                                             | 87       |

|   |      | 3.1.2 Introduction of H-bridge based DPT                                                                                                   | 89       |

|   | 2 2  |                                                                                                                                            | 91       |

|   | 3.2  | Switching behaviour analysis considering the $V_{th}$ shift                                                                                | 91       |

|   |      | 3.2.2 Fast switching condition with whiler plateau                                                                                         | 95       |

|   |      |                                                                                                                                            | 93<br>97 |

|   | 2 2  | 3.2.3 Influence of $V_{th}$ shift on the switching behaviour                                                                               | 99       |

|   | 3.3  | High-voltage and high-current output characteristics                                                                                       | 99       |

|   |      | 3.3.1 Introduction of the HVHC output characteristics                                                                                      | 100      |

|   |      | 3.3.2 Proposed measurement method for the HVHC output characteristics                                                                      | 100      |

|   |      | 3.3.3 Error analysis for the measured HVHC output characteristics                                                                          | 110      |

|   |      | 3.3.4 $V_{ds}$ bias induced $V_{th}$ shift in the HVHC output characteristics 3.3.5 Evaluation of the $V_{th}$ bias induced $V_{th}$ shift | 110      |

|   | 2.4  | 3.3.5 Evaluation of the $V_{gs}$ bias induced $V_{th}$ shift                                                                               |          |

|   | 3.4  | SPICE device modelling considering $V_{ds}$ bias induced $V_{th}$ shift                                                                    | 117      |

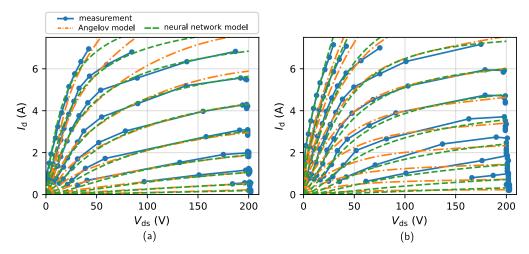

|   |      | 3.4.1 Modelling of HVHC output characteristics                                                                                             | 117      |

|   | 2 5  | 3.4.2 Construction of the device SPICE model                                                                                               | 121      |

|   | 5.5  | Simulation and experiment validation                                                                                                       | 122      |

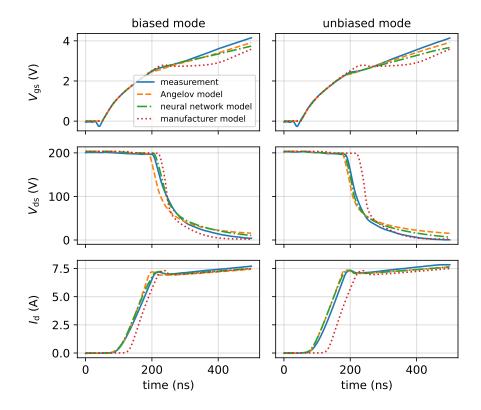

|   |      | 3.5.1 Model calibration in slow switching                                                                                                  | 122      |

|   |      | 3.5.2 Model prediction in fast switching                                                                                                   | 125      |

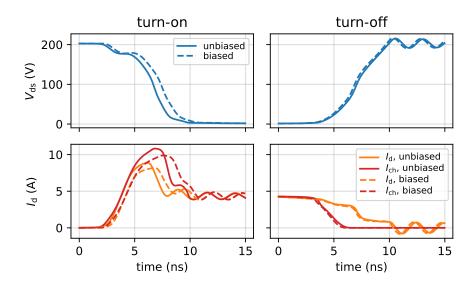

|   | 2 /  | 3.5.3 Experiment validation                                                                                                                | 127      |

|   | 3.6  | Conclusion and discussion                                                                                                                  | 131      |

| Table of Contents | xix |

|-------------------|-----|

|                   |     |

| 4 Influence of gate driver configuration on the switching behaviour   | 133 |  |

|-----------------------------------------------------------------------|-----|--|

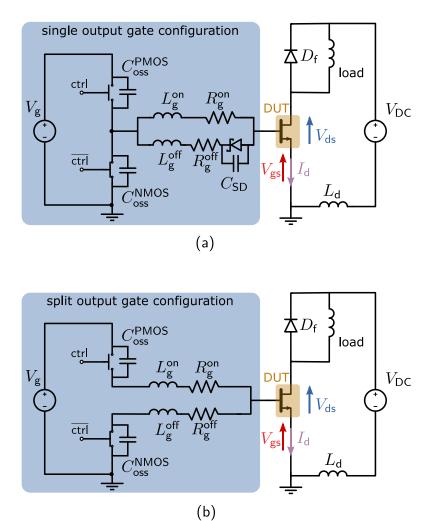

| 4.1 Single and split gate output configurations                       | 134 |  |

| 4.1.1 Split output gate configurations                                | 135 |  |

| 4.1.2 Driving of GaN-HEMTs using single and split gate configurations | 135 |  |

| 4.1.3 Driving variation using single and split gate configurations    | 139 |  |

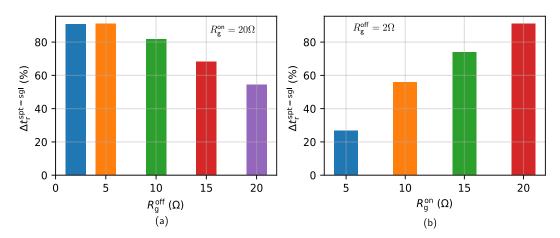

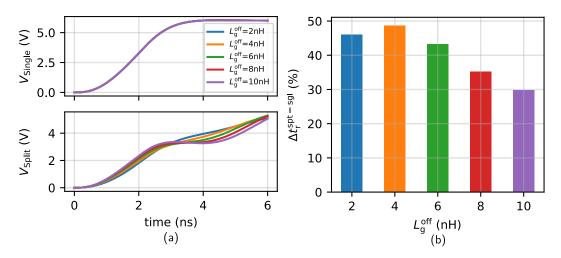

| 4.1.4 Influence of gate circuit parameters on the SPOGC effect        | 141 |  |

| 4.2 SPICE simulation of SPOGC effect on switching behaviours          | 148 |  |

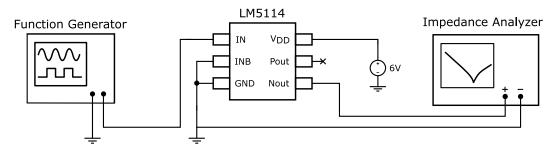

| 4.2.1 Circuit parasitic parameters extraction for SPICE simulation    | 148 |  |

| 4.2.2 SPICE simulation results                                        | 156 |  |

| 4.3 Experimental validation                                           | 161 |  |

| 4.3.1 Experiment setup                                                | 161 |  |

| 4.3.2 Measurement results                                             | 162 |  |

| 4.4 Discussion and conclusion                                         | 166 |  |

| Conclusion and perspectives                                           | 169 |  |

| Publications                                                          |     |  |

| Bibliography                                                          |     |  |

xx Table of Contents

# List of Tables

| 1.1 | Comparison of the material properties of Si, SiC, and GaN                                     |

|-----|-----------------------------------------------------------------------------------------------|

| 1.2 | Band gap and lattice constant of AlN and GaN materials                                        |

| 1.3 | Summary of normalised dynamic $R_{on}$ of commercial GaN-HEMTs 24                             |

| 1.4 | Mechanisms of $V_{gs}$ bias induced $V_{th}$ shift for GaN-HEMTs and GITs 28                  |

| 1.5 | Summary of the characterisation methods for $V_{ds}$ bias induced $V_{th}$ shift. 32          |

| 1.6 | Two types of $V_{ds}$ bias related $V_{th}$ shift                                             |

| 1.7 | Inter-electrode capacitance of Si- and SiC-MOSFETs and GaN-HEMTs 38                           |

| 2.1 | Simulation parameters for RL load based $V_{th}$ measurement 52                               |

| 2.2 | Measured original $V_{th}$ at different $I_{ch}$ for GaN-HEMTs and GITs 58                    |

| 3.1 | Parameter values for biased and unbiased transfer characteristics 98                          |

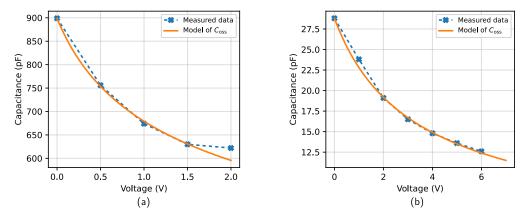

| 3.2 | Parameters used in $C_{oss}$ model                                                            |

| 3.3 | Experiment parameters when evaluating $V_{\rm th}$ shift under different $V_{\rm ds}$ 116     |

| 3.4 | Parameters used in biased and unbiased Angelov model                                          |

| 3.5 | All SPICE models and their inclusion of different types of $V_{\rm ds}$ bias 123              |

| 3.6 | $dV_{ds}/dt$ , $dI_{d}/dt$ and switching losses quantification results in slow switching. 124 |

| 3.7 | Absolute difference of $dV_{ds}/dt$ , $dI_{s}/dt$ and $E_{on}$ between the simulation and     |

|     | experiment in slow switching                                                                  |

| 4.1 | $C_{iss}$ of commercial power GaN-HEMTs                                                       |

| 4.2 | $C_{\text{oss}}$ of commercial low power Si-MOSFETs                                           |

| 4.3 | Commercial low-side gate drivers for power GaN-HEMTs                                          |

| 4.4 | Simulation parameters for investigating the SPOGC effect                                      |

| 4.5 | Comparison of the rise time of commercial gate drivers (for Si-MOSFETs                        |

|     | and GaN-HEMTs) under different test conditions                                                |

| 4.6 | Simulation parameters for investigating the influence of $R_g$ on the SPOGC                   |

|     | effect                                                                                        |

| 4.7 | Simulation parameters of investigating $L_{\rm g}$ distribution                               |

| 4.8 | SPICE simulation parameters for the DPT based hard-switching in slow                          |

|     | switching                                                                                     |

xxii List of Tables

# List of Figures

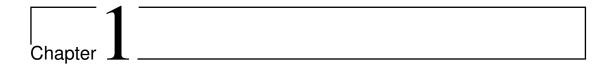

| 1.1  | Schematic of witching waveforms of the ideal switch and transistor                 | 6  |

|------|------------------------------------------------------------------------------------|----|

| 1.2  | Normalised JFOM and BFOM of Si and SiC to GaN                                      | 8  |

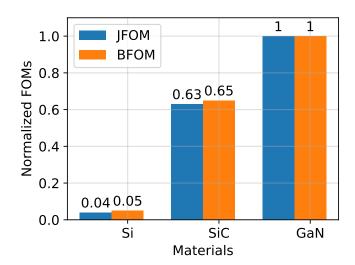

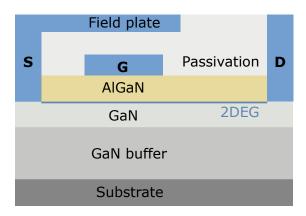

| 1.3  | Formation of 2DEG in AlGaN/GaN heterojunction                                      | 10 |

| 1.4  | Schematic of the power GaN-HEMTs structure (depletion-mode)                        | 11 |

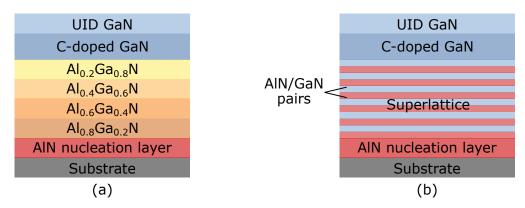

| 1.5  | Schematic of buffers for power GaN-HEMTs                                           | 12 |

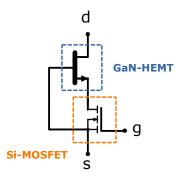

| 1.6  | Cascode structure for the normally-off GaN transistors                             | 13 |

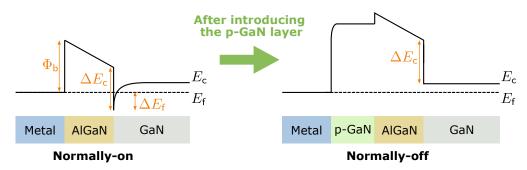

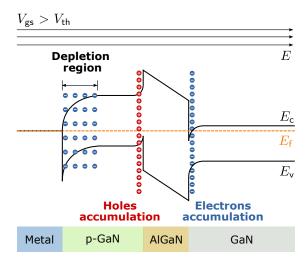

| 1.7  | The operation principle of p-GaN layer in normally-off device                      | 14 |

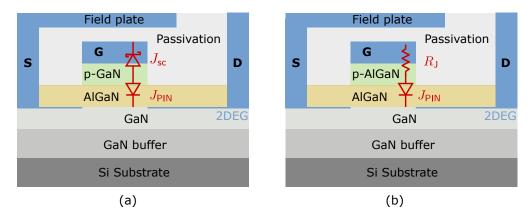

| 1.8  | Equivalent circuit of gate stack for GaN-HEMTs and GITs                            | 15 |

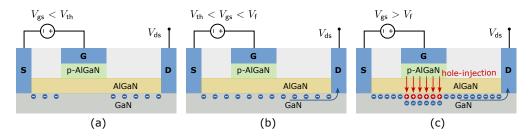

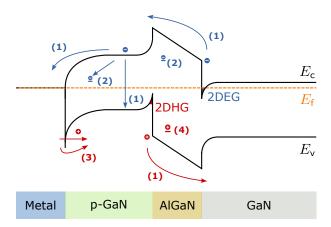

| 1.9  | The schematic of operation principle of GITs                                       | 15 |

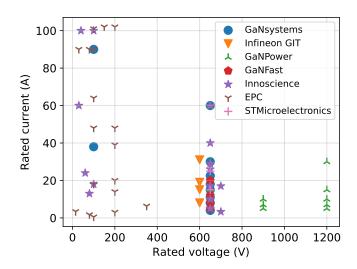

| 1.10 | Rated voltage and current for commercialised p-GaN gate HEMTs                      | 16 |

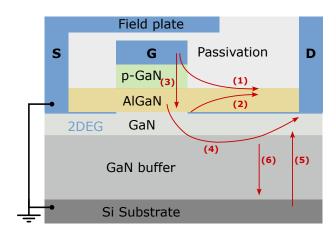

| 1.11 | Carrier trapping paths under different stresses in GaN-HEMTs                       | 20 |

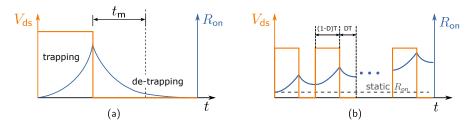

| 1.12 | Schematic of trapping and de-trapping related dynamic $R_{on}$                     | 22 |

| 1.13 | Schematic of structure and mechanism for HD-GITs                                   | 25 |

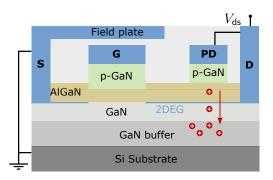

| 1.14 | Turn-on mechanism of p-GaN gate HEMTs                                              | 26 |

| 1.15 | Main mechanisms related to the $V_{\sf th}$ shift under $V_{\sf gs}$ bias          | 27 |

| 1.16 | Mechanisms of off-state high $V_{ds}$ voltage bias induced $V_{th}$ shift          | 29 |

| 1.17 | The maximum reported $V_{\sf ds}$ bias induced $V_{\sf th}$ shifts in Table 1.5    | 33 |

| 1.18 | Measurement sequence of $V_{\sf ds}$ induced $V_{\sf th}$ shift using curve tracer | 34 |

| 1.19 | Influence of trapping effect on $I - V$ characteristics                            | 35 |

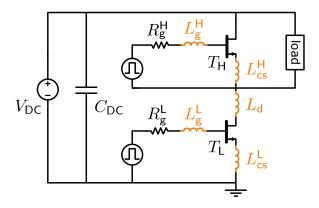

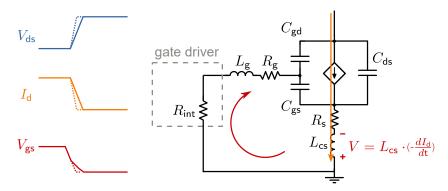

| 1.20 | Lumped parasitic inductance in the half-bridge                                     | 39 |

| 1.21 | Influence of $L_{cs}$ on the switching commutation speed                           | 40 |

| 1.22 | Measured turn-on and turn-off switching waveforms of a GaN-HEMT                    |    |

|      | 8                                                                                  | 40 |

| 1.23 | Schematic of false turn-on phenomenon                                              | 41 |

| 2.1  | Forward and reverse conduction mechanism of GaN-HEMTs                              | 47 |

| 2.2  | Comparison of measured $I_d - V_{gd}$ and $I_d - V_{gs}$ characteristics           | 48 |

| 2.3  | Measurement principle of the in-situ $V_{th}$ measurement method                   | 50 |

| 2.4  | Schematic of the in-situ $V_{th}$ shift measurement setup                          | 51 |

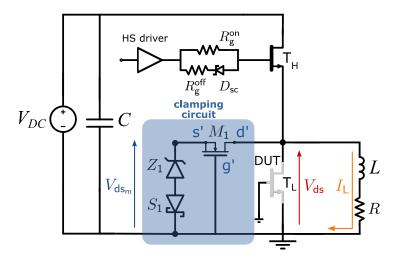

| 2.5  | Measured and modelled non-linear $C_{oss}$ of diodes in clamping circuit           | 52 |

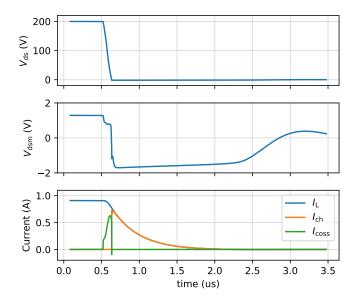

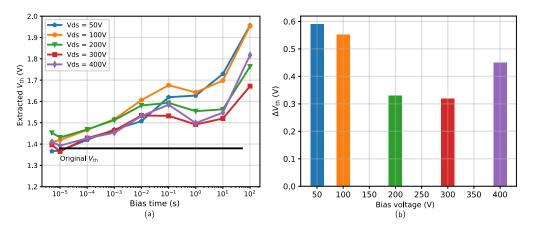

| 2.6  | Simulation result of the in-situ $V_{th}$ measurement setup                        | 53 |

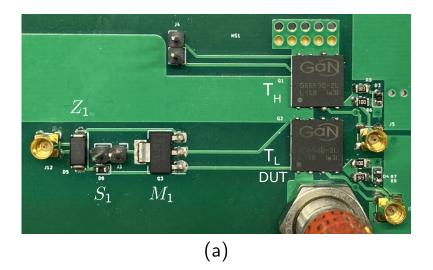

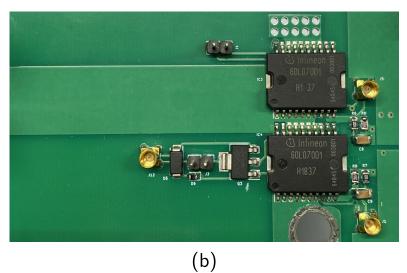

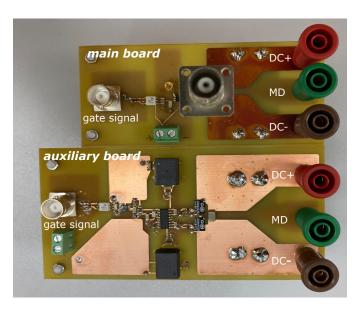

| 2.7  | Experiment boards for the in-situ $V_{th}$ measurement                             | 55 |

|      |                                                                                    |    |

xxiv List of Figures

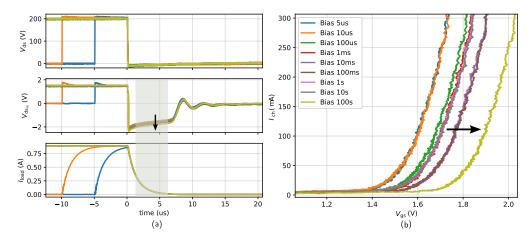

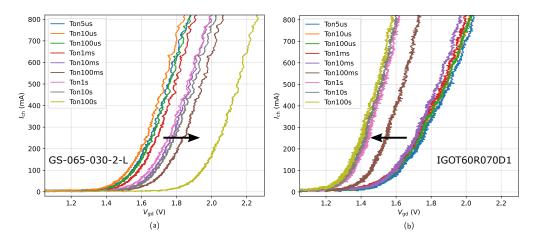

| 2.8  | Measured switching waveforms and $I_{ch} - V_{gd}$ characteristics of GS-065-                                                                                          |            |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | 030-2-L under different off-state $V_{ds}$ bias time                                                                                                                   | 56         |

| 2.9  | Measured switching waveforms and $I_{ch}-V_{gd}$ characteristics of C4D40120D                                                                                          |            |

|      | under different off-state $V_{ds}$ bias time                                                                                                                           | 57         |

| 2.10 | Measured switching waveforms and $I_{ch}$ – $V_{gd}$ characteristics of C4D40120D                                                                                      |            |

|      | under different off-state $V_{ds}$ bias amplitudes                                                                                                                     | 57         |

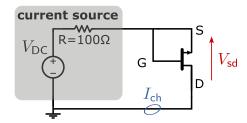

|      | Schematic of the original $V_{\text{th}}$ measurement circuit                                                                                                          | 58         |

| 2.12 | Measured $V_{\text{th}}$ for GS-065-030-2-L after different off-state $V_{\text{ds}}$ bias ampli-                                                                      |            |

|      | tudes and time.                                                                                                                                                        | 60         |

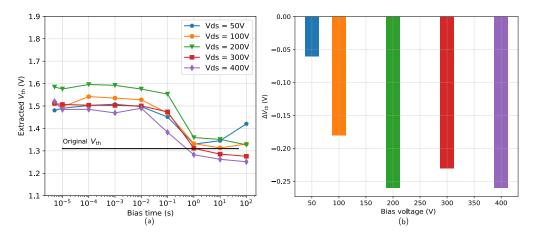

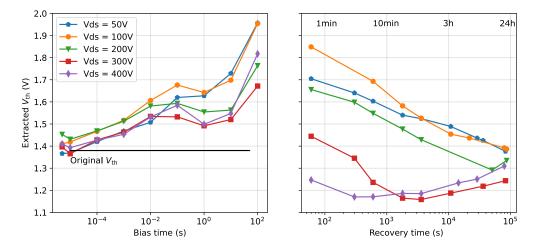

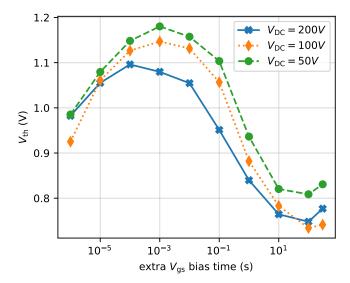

|      | Measured $V_{\text{th}}$ at various recovery time under different $V_{\text{DC}}$                                                                                      | 61         |

| 2.14 | Measured switching waveforms and $I_{ch} - V_{gd}$ characteristics of GS-065-                                                                                          |            |

| 0.45 | 030-2-L under different load current.                                                                                                                                  | 62         |

| 2.15 | Measured $V_{\text{th}}$ for IGOT60R07D1 after different off-state $V_{\text{ds}}$ bias ampli-                                                                         | <i>(</i> ) |

| 2.16 | tudes and time.                                                                                                                                                        | 63         |

| 2.16 | Comparison of measured $I_{\rm ch}$ – $V_{\rm gd}$ characteristics under 400 V of $V_{\rm ds}$ bias with various of bias time for GaN-HEMTs and GITs                   | <i>(</i> 1 |

|      |                                                                                                                                                                        | 64         |

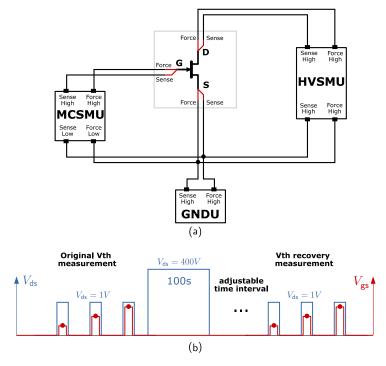

|      | Schematic of the measurement sequence for $V_{th}$ recovery phenomenon.                                                                                                | 65         |

| 2.18 | Recovered switching waveforms and $I_{ch} - V_{gd}$ characteristics of GS-065-                                                                                         | 66         |

| 2 10 | 030-2-L after 100 s of 100 V $V_{ds}$ bias                                                                                                                             | 66         |

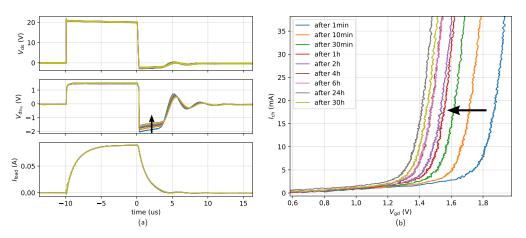

|      | Measured $V_{th}$ shift and recovery behaviour of GS-065-030-2-L                                                                                                       | 66         |

|      | V <sub>th</sub> recovery behaviour measurement setup in curve tracer                                                                                                   | 68         |

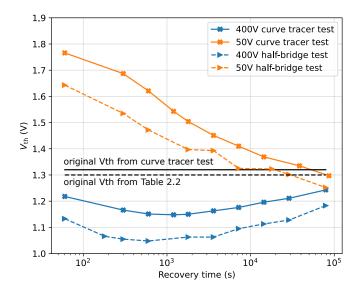

| 2.21 | Comparison of $V_{th}$ recovery behaviour from curve tracer and half-bridge based test                                                                                 | 69         |

| 2 22 |                                                                                                                                                                        | 71         |

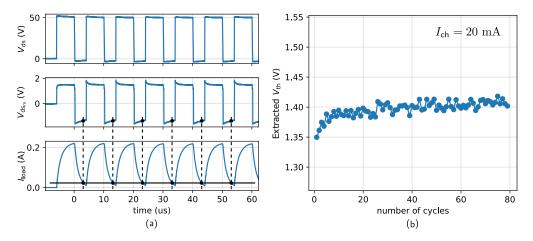

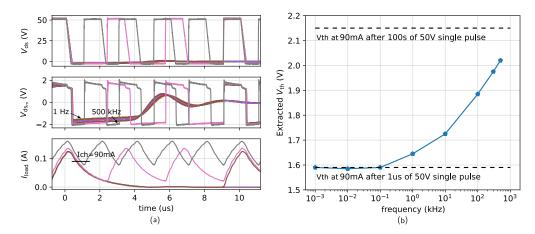

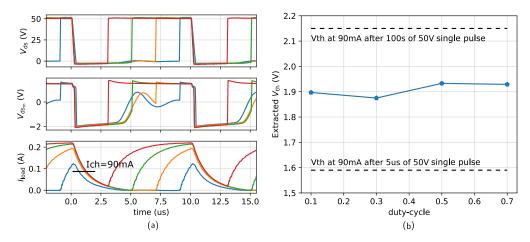

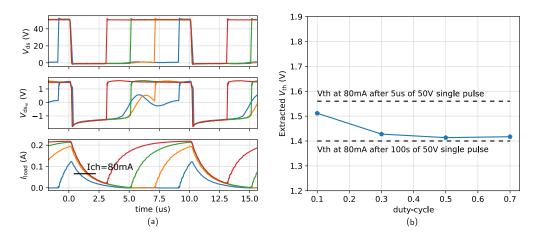

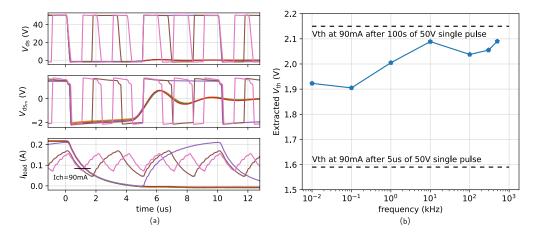

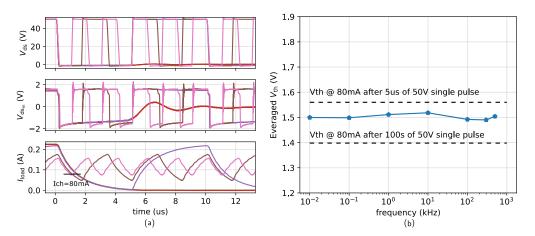

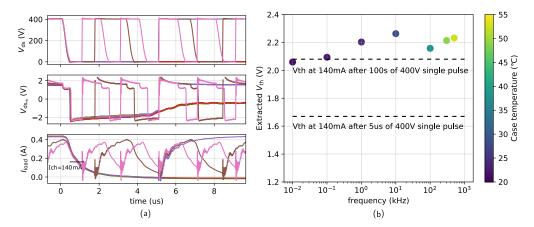

|      | V <sub>th</sub> measurement principle in continuous mode                                                                                                               | 73         |

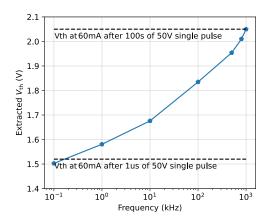

|      | Influence of the recovery time on the steady-state $V_{th}$ for GS-065-030-2-L. Influence of the recovery time on the steady state $V_{th}$ for C4D40120D              | 73         |

|      | Influence of the recovery time on the steady-state $V_{th}$ for C4D40120D Extracted steady state $V_{th}$ at $I_{th} = 60  \text{m}$ A versus operating frequency with | 73         |

| 2.23 | Extracted steady-state $V_{\rm th}$ at $I_{\rm ch} = 60\rm mA$ versus operating frequency with 500 ns of bias time in each switching cycle for GS-065-030-2-L          | 74         |

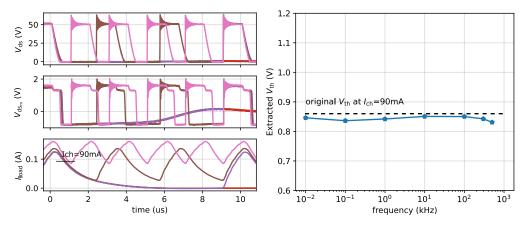

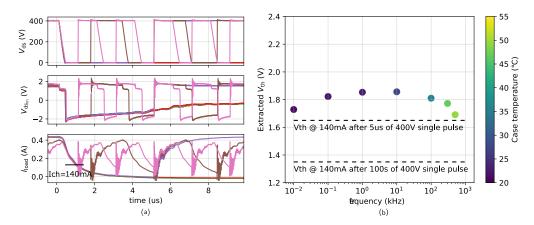

| 2 26 | Influence of the recovery time on the steady-state $V_{\rm th}$ for IGOT60R07D1.                                                                                       | 75         |

|      | Influence of the duty-cycle on the steady-state $V_{th}$ for GS-065-030-2-L.                                                                                           | 75         |

|      | Influence of the duty-cycle on the steady-state $V_{th}$ for IGOT60R07D1                                                                                               | 76         |

|      | Influence of the switching frequency on the steady-state $V_{th}$ under 50 V                                                                                           | 70         |

| 2.2) | of $V_{ds}$ for GS-065-030-2-L                                                                                                                                         | 77         |

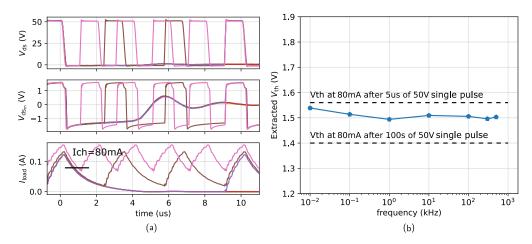

| 2 30 | Influence of the switching frequency on the steady-state $V_{\text{th}}$ under 50 V                                                                                    | ,,         |

| 2.00 | of $V_{ds}$ for IGOT60R07D1                                                                                                                                            | 78         |

| 2.31 | Influence of the switching frequency on the steady-state $V_{\text{th}}$ under 400 V                                                                                   |            |

|      | of $V_{ds}$ for GS-065-030-2-L                                                                                                                                         | 79         |

| 2.32 | Influence of the switching frequency on the steady-state $V_{\text{th}}$ under 400 V                                                                                   |            |

|      | of $V_{ds}$ for IGOT60R07D1                                                                                                                                            | 80         |

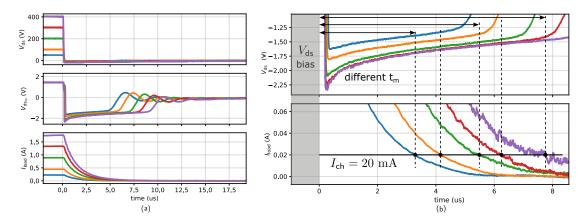

| 2.33 | Dynamic $V_{\text{th}}$ shift effect under 400 V of $V_{\text{DC}}$                                                                                                    | 81         |

|      | $V_{\text{th}}$ recovery behaviours after extended of single pulse and continuous                                                                                      |            |

|      | mode tests for GS-065-030-2-L.                                                                                                                                         | 83         |

List of Figures xxv

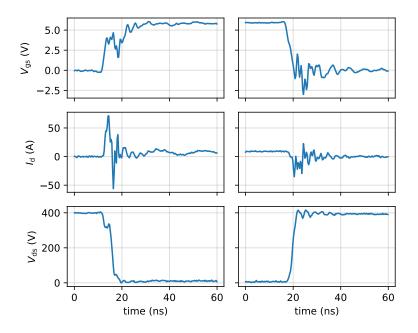

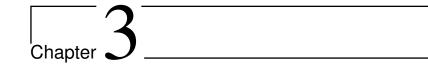

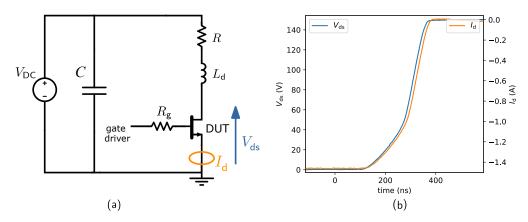

| 3.1  | Schematic and typical switching waveforms of conventional DPT                                          | 87   |

|------|--------------------------------------------------------------------------------------------------------|------|

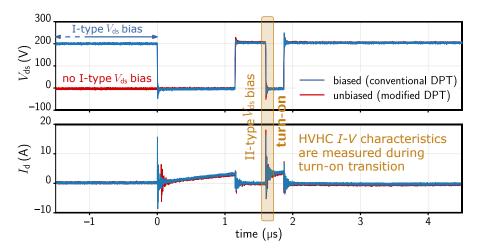

| 3.2  | II-type $V_{\rm ds}$ bias in the turn-on switching waveform from the DPT                               | 88   |

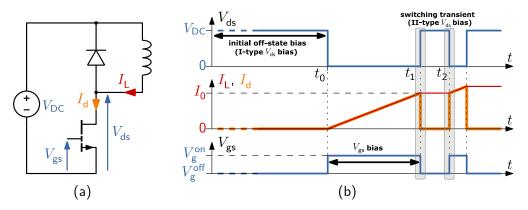

| 3.3  | Introduction of H-bridge based DPT                                                                     | 90   |

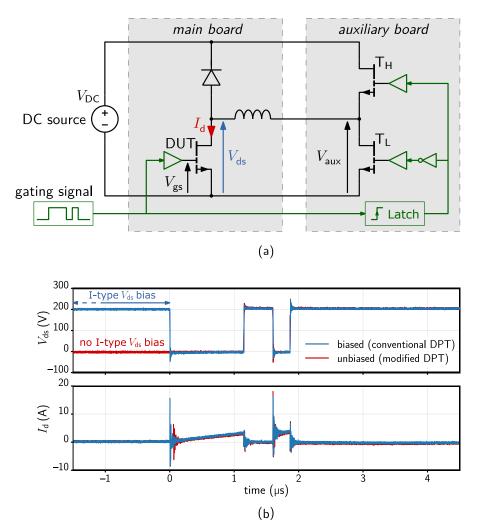

| 3.4  | Schematic of the switching cell for hard-switching transition analysis                                 | 92   |

| 3.5  | Simplified hard-switching transition and its relation to transfer character-                           |      |

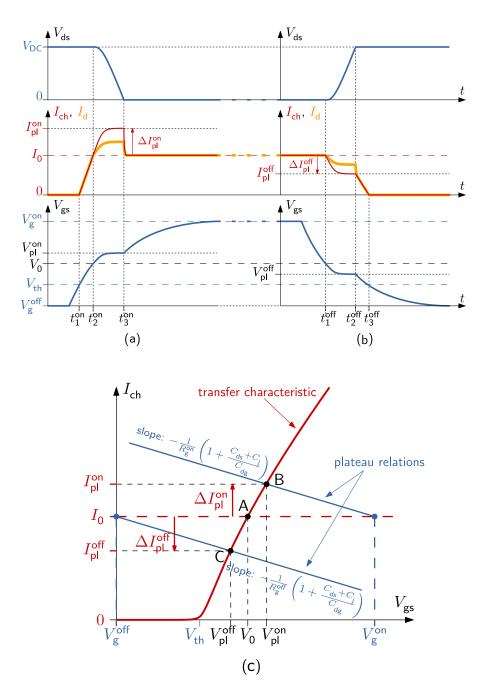

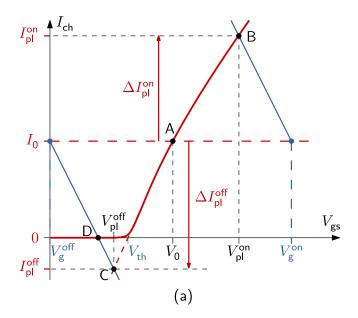

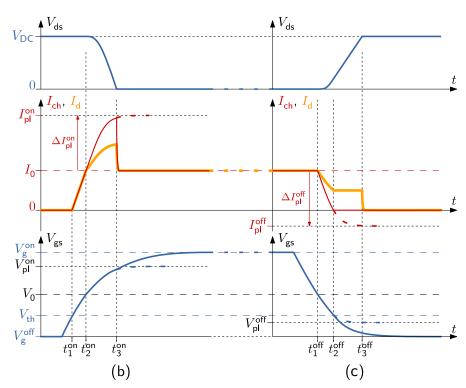

|      | istics in slow commutation condition                                                                   | 93   |

| 3.6  | Simplified hard-switching transition and its relation to transfer character-                           |      |

|      | istics in slow commutation condition                                                                   | 96   |

| 3.7  | Transfer characteristics in unbiased and biased modes considering Miller                               |      |

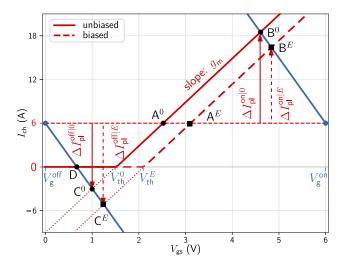

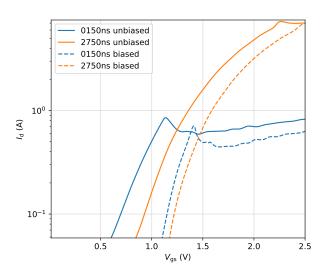

|      | plateau relation                                                                                       | 98   |

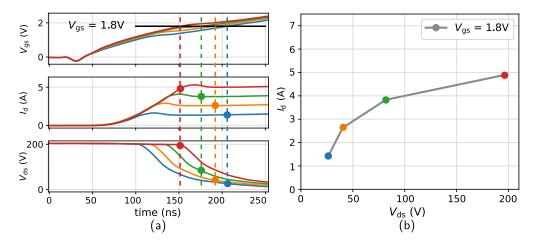

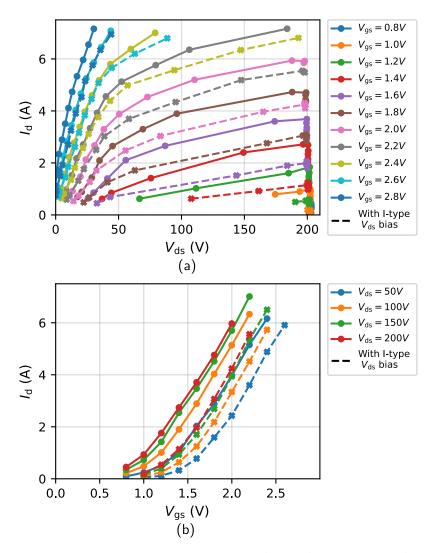

| 3.8  | HVHC output characteristics extraction through the turn-on switching                                   |      |

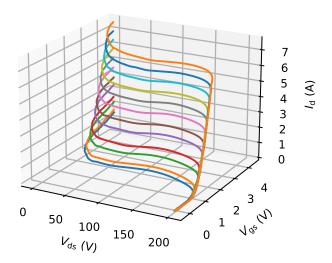

|      | waveforms form the H-bridge based DPT                                                                  | 101  |

| 3.9  | Experiment board for the H-bridge based DPT                                                            | 102  |

| 3.10 | The extraction method for HVHC output characteristics                                                  | 103  |

| 3.11 | Power resistor based probe de-skew method                                                              | 104  |

| 3.12 | Propagation delay for the probes used for HVHC $I-V$ characteristics                                   |      |

|      | measurement                                                                                            | 105  |

| 3.13 | Variation between the measured $V_{\rm gs}$ , $I_{\rm d}$ and intrinsic $V_{\rm Cgs}$ and $I_{\rm ch}$ | 105  |

|      | Comparison of the $C_{oss}$ of GS66502B between model and datasheet                                    |      |

| 3.15 | Comparison of HVHC output characteristics before and after the error                                   |      |

|      | compensation                                                                                           | 107  |

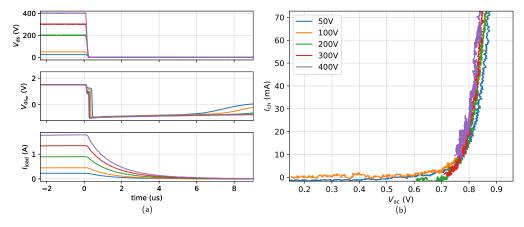

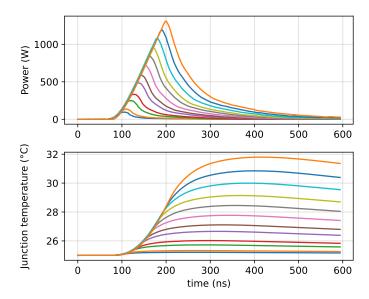

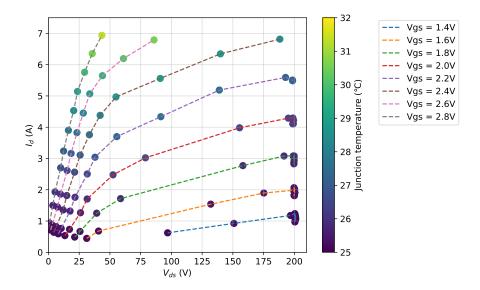

|      | Power and estimated $T_j$ during the turn-on transition                                                | 108  |

| 3.17 | HVHC output characteristics extracted with the distribution of $T_j$ through                           |      |

|      | the biased DPT switching waveforms                                                                     | 109  |

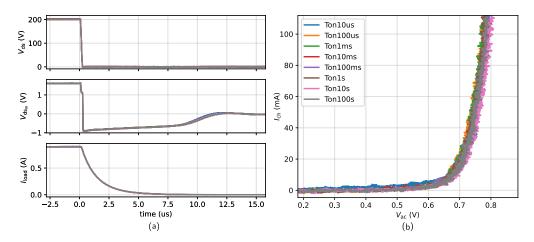

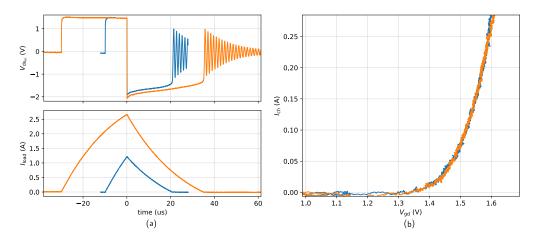

| 3.18 | Influence of $V_{\rm gs}$ bias time on the extracted transfer characteristics                          | 110  |

| 3.19 | The HVHC <i>I–V</i> characteristics with and without the influence of <i>I</i> -type                   |      |

|      | $V_{ds}$ bias                                                                                          |      |

|      | Influence of II-type $V_{ds}$ bias on the $V_{th}$ shift                                               |      |

|      | Measurement setup for the $V_{gs}$ bias time on the $V_{th}$ shift                                     | 114  |

| 3.22 | Measurement result of $V_{\text{th}}$ shift induced by different $V_{\text{gs}}$ bias time at          |      |

|      | $V_{\rm DC} = 200 \mathrm{V}.$                                                                         | 115  |

| 3.23 | Different voltage biases during the $V_{gs}$ bias induced $V_{th}$ evaluation using                    |      |

|      | the H-bridge based DPT                                                                                 | 115  |

|      | Measurement result of $V_{th}$ shift induced by different $V_{gs}$ bias time under                     |      |

|      | different $V_{\rm DC}$                                                                                 | 116  |

|      |                                                                                                        | 117  |

| 3.26 | Comparison of measured HVHC output characteristics and fitted Angelov                                  |      |

|      | model.                                                                                                 | 119  |

| 3.27 | Comparison of the biased HVHC output characteristics and fitted manu-                                  | 110  |

| 2.20 | facturer model                                                                                         | 119  |

| 3.28 | 3D switching trajectories of the slowed down turn-on commutation under                                 |      |

|      | 200 V of $V_{\rm DC}$ with 12 different width for the 1st DPT pulse form the biased                    | 1.00 |

|      | DPT                                                                                                    | 120  |

xxvi List of Figures

| 3.29        | Comparison of HVHC $I-V$ characteristics between experiment measurement and constructed models | 122  |

|-------------|------------------------------------------------------------------------------------------------|------|

| 3 30        | Comparison of turn-on switching waveforms from measurement and                                 | 122  |

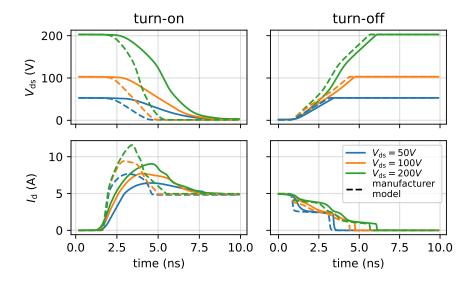

| 3.30        | simulation                                                                                     | 123  |

| 3.31        | Comparison of the switching waveforms from biased and unbiased neural                          | 120  |

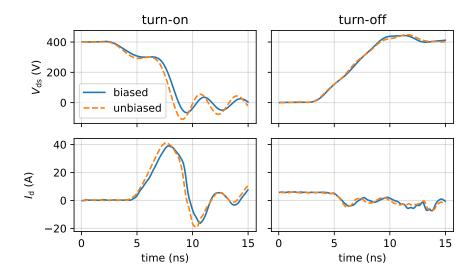

| 0.01        | network model                                                                                  | 126  |

| 3.32        | Switching waveforms at different $V_{ds}$ bias amplitudes from unbiased                        |      |

|             | neural network model                                                                           | 126  |

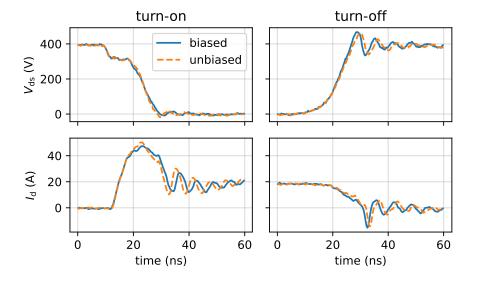

| 3.33        | Experimental switching waveforms from the biased and unbiased DPT in                           |      |

|             | fast switching                                                                                 | 128  |

| 3.34        | Schematic of the experiment setup for the biased and unbiased tests for                        |      |

|             | GIT                                                                                            |      |

|             | Measured biased and unbiased switching waveforms for GITs                                      | 130  |

| 3.36        | Biased and unbiased switching waveforms for GITs in turn-on and turn-                          |      |

|             | off switching transition                                                                       |      |

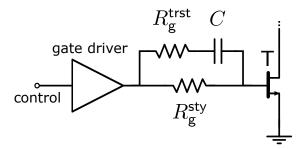

| 3.37        | Schematic of gate configuration for driving the GITs                                           | 131  |

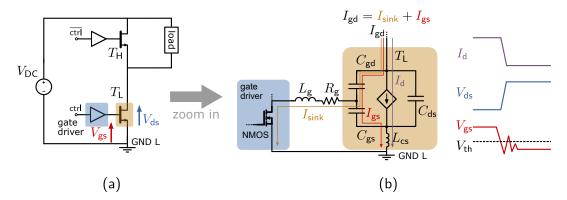

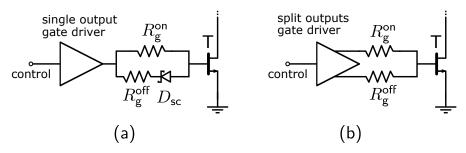

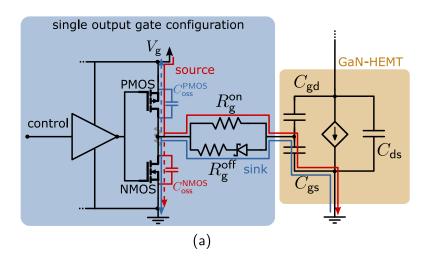

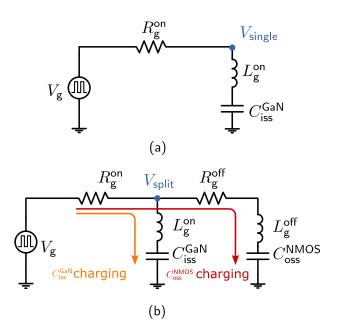

| 4.1         | Schematic of single and split output gate configurations                                       | 135  |

| 4.2         | Turn-on and turn-off loop of single and split output gate configurations                       |      |

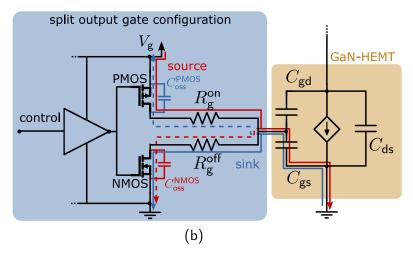

| 4.3         | Equivalent circuit of the single and spilt output gate configurations                          | 140  |

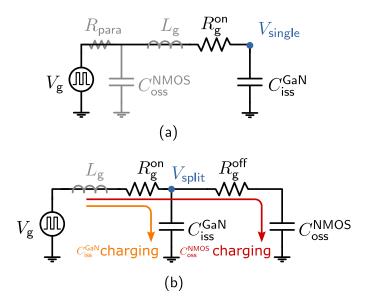

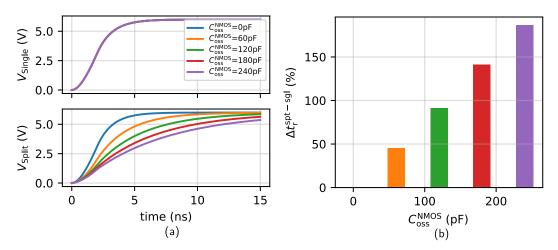

| 4.4         | Charging process of $C_{iss}$ of GaN-HEMTs from single and split output gate                   |      |

|             | configurations from simulation                                                                 | 141  |

| 4.5         | Charging process of $C_{iss}$ of GaN-HEMTs from single and split output gate                   |      |

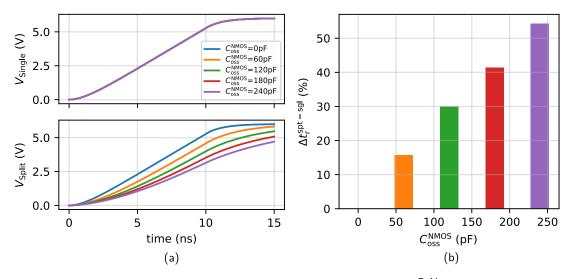

|             | configurations from simulation with fast gate driver rise edge                                 |      |

| 4.6         | Influence of different $R_{on}$ on the SPOGC effect                                            |      |

| 4.7         | Mechanism of turn off resistor influence on the SPOGC effect                                   |      |

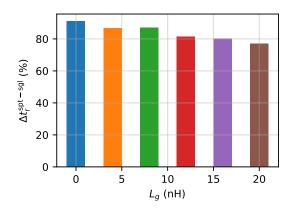

| 4.8         | Influence of lumped $L_g$ on the SPOGC effect                                                  | 146  |

| 4.9         | Equivalent charging circuit of single and split output gate configuration                      |      |

|             | considering the distributed $L_{\rm g}$                                                        | 147  |

| 4.10        | Charging process of $C_{iss}$ of GaN-HEMTs from single and split output gate                   | 4.45 |

| 111         | configurations from simulation with considering the distributed $L_{\rm g}$                    | 147  |

| 4.11        | Schematic of customised single and split output configuration for SPICE                        | 1.40 |

| 112         | simulation                                                                                     | 149  |

| 4.12        | Schematic of the measurement method for the $C_{oss}^{NMOS}$ in the gate driver LM5114         | 150  |

| <b>4</b> 13 | Measurement setup and measurement board for the $C_{oss}^{NMOS}$ in the gate                   | 150  |

| 4.13        | driver                                                                                         | 151  |

| 4.14        | Measured impedance of the gate driver LM5114 using impedance analyzer                          |      |

| 4.15        | Measurement and modelling results of $C_{oss}^{NMOS}$ in LM5114 gate driver                    | 152  |

| 4.16        | PCB layout of the utilised half-bridge.                                                        | 153  |

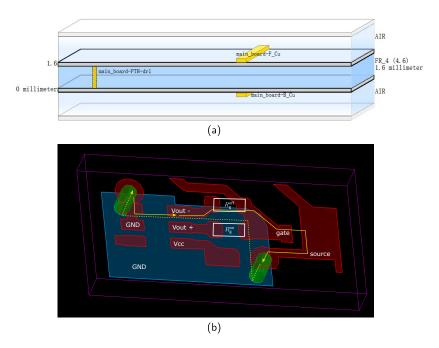

|             | PCB model used for EM momentum simulation in ADS                                               |      |

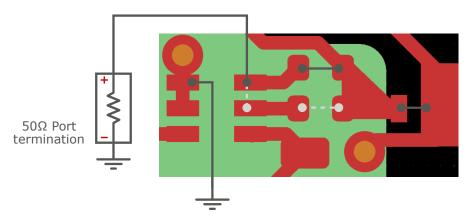

|             | Connection of gate loop layout for $L_g$ extraction in ADS                                     |      |

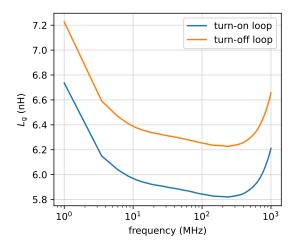

|             | Extracted $L_g^{on}$ and $L_g^{off}$ using S-parameter simulation in ADS                       |      |

|             |                                                                                                |      |

List of Figures xxvii

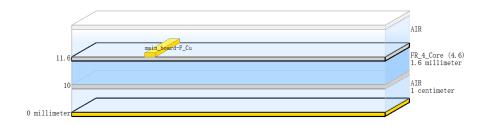

| 4.20 | Substrate setup for the power loop in the EM momentum simulation          | 156 |

|------|---------------------------------------------------------------------------|-----|

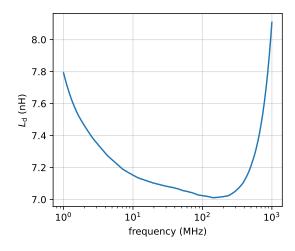

| 4.21 | Extracted $L_d$ using S-parameter simulation in ADS                       | 157 |

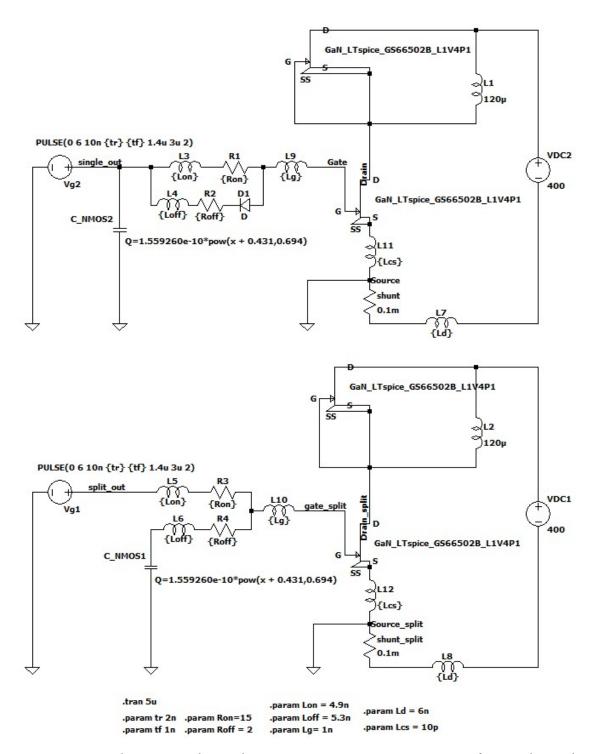

| 4.22 | Schematic and Simulation Parameters Setup in LTspice for Single- and      |     |

|      | Split-output Gate Driver Based Hard-switching                             | 158 |

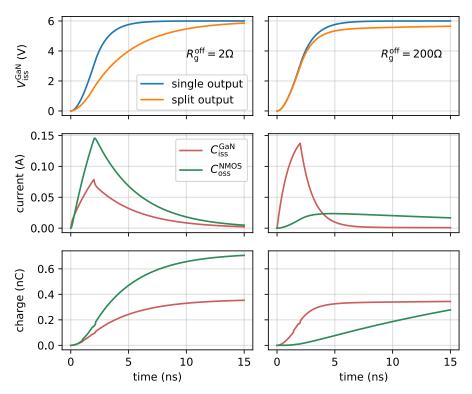

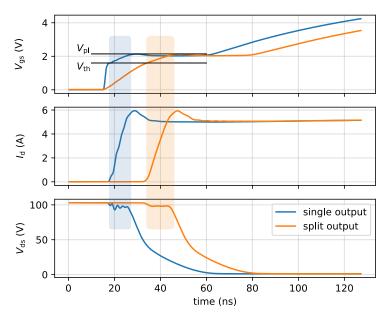

| 4.23 | Simulation analysis of the influence of SPOGC effect on the switching     |     |

|      | behaviour in slow commutation                                             | 159 |

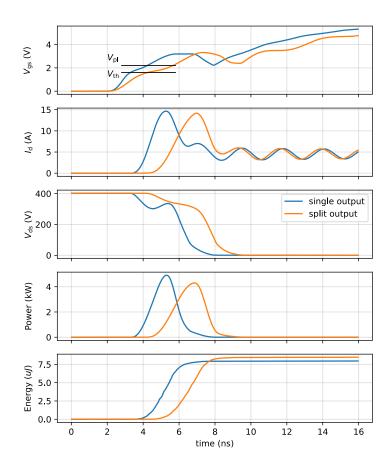

| 4.24 | Simulation analysis of the influence of SPOGC effect on the switching     |     |

|      | behaviour in fast commutation                                             | 160 |

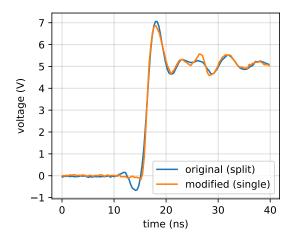

| 4.25 | Comparison of the output voltage of "Pout" pin from the original (split)  |     |

|      | and modified (single) LM5114                                              | 162 |

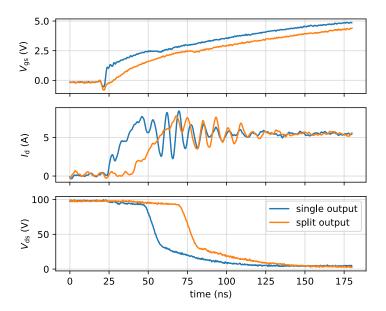

| 4.26 | Experimental validation of the influence of SPOGC effect on the switching |     |

|      | behaviour in slow commutation                                             | 163 |

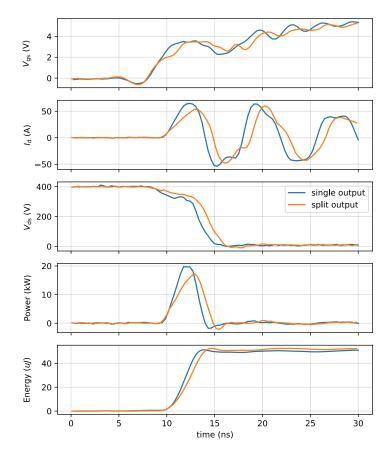

| 4.27 | Experimental validation of the influence of SPOGC effect on the switching |     |

|      | behaviour in fast commutation using LM5114                                | 164 |

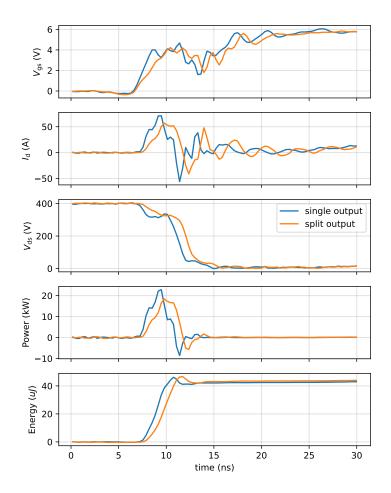

| 4.28 | Experimental validation of the influence of SPOGC effect on the switching |     |

|      | behaviour in fast commutation using 1EDN7511                              | 165 |

xxviii List of Figures

# Introduction

Electrification is essential in enabling the integration of renewable energy sources and reducing the carbon emission. This transition necessitates the widespread deployment of power converters, which can support the electrification of transportation and industrial sectors. The emergence of gallium nitride (GaN) semiconductor devices has elevated the operation frequency of power converters to unprecedented levels due to the fast commutation characteristics of new transistors. Although GaN transistors can significantly enhance the efficiency and power density of the power converters, they also introduce additional challenges, including device reliability concerns, high sensitivity of parasitic parameters, and electromagnetic compatibility (EMC) issues. Addressing these challenges requires a deep understanding of the trapping effect in GaN transistors, such as the related dynamic on-state resistance ( $R_{\rm on}$ ) and threshold voltage ( $V_{\rm th}$ ) shift phenomenon, and their influence on the switching performance of GaN devices. Additionally, the influence of circuit parasitic parameters on the application of GaN transistors should be carefully considered due to the high commutation speed of GaN transistors.

This thesis explores three research challenges derived from the GaN high electron mobility transistors (GaN-HEMTs) technology. The first one relates to the characterisation of the voltage bias induced  $V_{\rm th}$  shift phenomenon based on a customised circuit. The second one investigates the influence of  $V_{\rm th}$  shift on the switching behaviour of transistors, following the conclusion of the first challenge. Finally, the influence of gate driver configuration on the switching commutation of GaN-HEMTs is studied based on two regular gate loop topologies. This thesis comprises by four chapters.

The first chapter is dedicated to introducing the origins of the trapping effect and the high sensitivity of GaN-HEMTs to parasitic parameters, stemming from the material properties and device structure. It also reviews the state-of-the-art research on the dynamic  $R_{\rm on}$  and  $V_{\rm th}$  shift phenomena found in commercial GaN-HEMTs, highlighting the necessity for further characterisation of the voltage bias induced  $V_{\rm th}$  shift phenomenon and its impact on switching behaviour. Subsequently, the significantly reduced interelectrode capacitance of GaN-HEMTs is illustrated, emphasising the importance of considering the gate driver's output capacitance when driving the GaN-HEMTs.

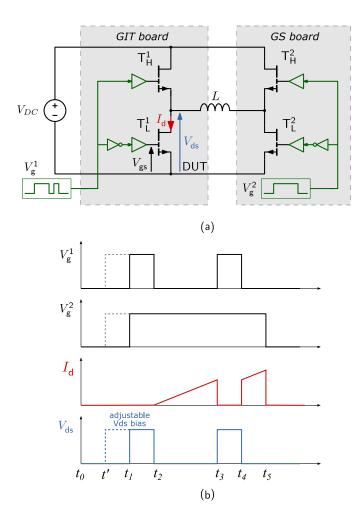

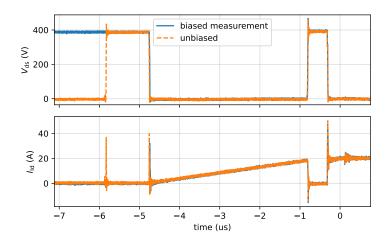

The second chapter describes an half-bridge based in-situ  $V_{\rm th}$  shift measurement method, enabling the characterisation of the off-state drain-to-source voltage ( $V_{\rm ds}$ ) induced  $V_{\rm th}$  shift for both Schottky-type and Ohmic-type p-GaN gate HEMTs. The  $V_{\rm ds}$

2 Introduction

bias induced  $V_{\rm th}$  shift phenomenon under various bias amplitudes and durations is characterised in the single pulse mode test. Subsequently, the recovery behaviour of the shifted  $V_{\rm th}$  after an extended high-voltage single-pulse bias is evaluated using the same setup, showing an hours level recovery time constant for the Schottky-type GaN-HEMTs, and this time constant is validated by the semiconductor curve tracer based test. Additionally, the influence of recovery time, duty cycle and switching frequency on the steady-state  $V_{\rm th}$  is evaluated for these two types of device in the continuous mode test. The significant positive  $V_{\rm th}$  shift and the prolonged recovery time suggests the potential impact of  $V_{\rm th}$  shift phenomenon on subsequent switching commutations after the voltage bias.

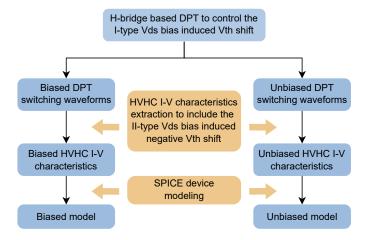

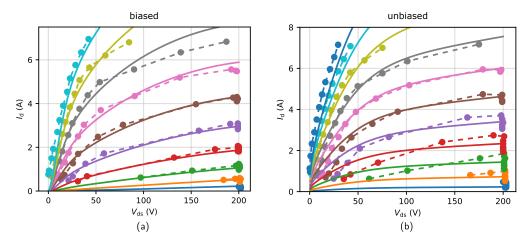

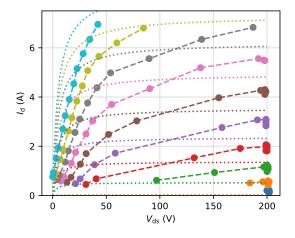

In the third chapter, the influence of  $V_{\rm th}$  shift on the switching behaviour of GaN-HEMTs is demonstrated. At first, the relationship between the transfer characteristics and switching transition is analysed to theoretically assess the impact of  $V_{\rm th}$  shift on the switching commutation. Subsequently, an H-bridge based double-pulse test (DPT) is employed to capture the I-V characteristics of GaN-HEMTs, incorporating the  $V_{\rm ds}$  bias induced  $V_{\rm th}$  shift phenomenon. Subsequently, GaN-HEMT models incorporating these I-V characteristics were developed and imported into simulations to investigate how the  $V_{\rm th}$  shift influences the switching behaviour of GaN-HEMTs. Finally, a DPT-based experiment is performed to further validate the theoretical analysis and simulation.

In the last chapter, the focus shifts to the output capacitance ( $C_{\rm oss}$ ) of metal oxide semiconductor field effect transistors (MOSFETs) inside the gate driver. Its impact on the switching behaviour of GaN-HEMTs is investigated based on two commonly used gate driver output topologies: single and split configurations. The equivalent circuits of these two gate configurations are proposed to analyse the influence of gate driver  $C_{\rm oss}$  on the charging and discharging process of GaN-HEMTs, indicating that this  $C_{\rm oss}$  could slow down the charging process of GaN-HEMTs in the split output gate configuration, this phenomenon is defined as the split output gate configuration (SPOGC) effect in this study. Subsequently, hard-switching simulation setups, with these two gate configurations, are constructed to evaluate the influence of SPOGC effect on the switching behaviour. Finally, the corresponding DPTs are conducted to validate this influence on the switching behaviour of GaN-HEMTs.

# GaN transistors state-of-the art review

# Outline of the current chapter

| 1.1 | Research context |                                                              |    |  |  |

|-----|------------------|--------------------------------------------------------------|----|--|--|

|     | 1.1.1            | Energy conversion efficiency                                 | 5  |  |  |

|     |                  | Power density and sustainability                             | 5  |  |  |

| 1.2 | GaN              | material and power transistors                               | 6  |  |  |

|     | 1.2.1            | Material properties comparison of Si, SiC and GaN            | 7  |  |  |

|     | 1.2.2            | Basic structure and operating principle of power GaN-HEMTs   | 8  |  |  |

|     |                  | 1.2.2.1 Polarisation effect                                  | 9  |  |  |

|     |                  | 1.2.2.2 AlGaN/GaN heterojunction and 2DEG channel            | 9  |  |  |

|     |                  | 1.2.2.3 Structures and technologies of power GaN-HEMTs .     | 10 |  |  |

|     |                  | 1.2.2.4 Enhancement-mode GaN-HEMTs technologies              | 12 |  |  |

|     | 1.2.3            | p-GaN gate HEMTs                                             | 14 |  |  |

|     |                  | 1.2.3.1 Schottky-type p-GaN gate HEMTs                       | 14 |  |  |

|     |                  | 1.2.3.2 Ohmic-type p-GaN gate HEMTs (GITs)                   | 15 |  |  |

|     |                  | 1.2.3.3 Power rating of commercialised p-GaN gate HEMTs      | 16 |  |  |

|     | 1.2.4            | Vertical GaN power transistors                               | 17 |  |  |

|     |                  | 1.2.4.1 Drawbacks of lateral GaN-HEMTs                       | 17 |  |  |

|     |                  | 1.2.4.2 Characteristics of vertical GaN power transistor     | 18 |  |  |

|     |                  | 1.2.4.3 Challenges in vertical GaN devices                   | 18 |  |  |

|     |                  | 1.2.4.4 Comparison between lateral and vertical GaN transis- |    |  |  |

|     |                  | tors                                                         | 19 |  |  |

|     | 1.2.5            | Type of GaN transistors used in this study                   | 19 |  |  |

| 1.3 | Trap             | ping effect and parametric shift of GaN-HEMTs                | 19 |  |  |

|     | 1.3.1            | Trapping effect                                              | 19 |  |  |

|     |                  | 1.3.1.1 Origin and locations of traps in GaN-HEMTs           | 19 |  |  |

|     |                  | 1.3.1.2 Leakage paths under different voltage stresses       | 20 |  |  |

|     | 1.3.2            | Dynamic on-state resistance                                  | 21 |  |  |

|     |       | 1.3.2.1 Characterisation methods                                       | 21 |

|-----|-------|------------------------------------------------------------------------|----|

|     |       | 1.3.2.2 Distribution of dynamic $R_{on}$ for commercialised GaN-       |    |

|     |       | HEMTs                                                                  | 23 |

|     | 1.3.3 | Threshold voltage shift                                                | 26 |

|     |       | 1.3.3.1 Turn-on mechanism of GaN-HEMTs                                 | 26 |

|     |       | 1.3.3.2 Mechanisms related to the $V_{gs}$ bias induced $V_{th}$ shift | 27 |

|     |       | 1.3.3.3 Characterisation method for the $V_{gs}$ bias induced $V_{th}$ |    |

|     |       | shift                                                                  | 29 |

|     |       | 1.3.3.4 Mechanisms related to the $V_{ds}$ bias induced $V_{th}$ shift | 29 |

|     |       | 1.3.3.5 Characterisation method for the $V_{ds}$ bias induced $V_{th}$ |    |

|     |       | shift                                                                  | 30 |

|     |       | 1.3.3.6 Two types of $V_{ds}$ bias induced $V_{th}$ shift              | 32 |

|     |       | 1.3.3.7 Influence of $V_{th}$ shift on device application              | 33 |

|     | 1.3.4 | $V_{th}$ shift issues investigated in this work                        | 35 |

| 1.4 | Impa  | ct of parasitic parameters on GaN-HEMTs application                    | 36 |

|     | 1.4.1 | Small inter-electrode capacitance and fast switching speed .           | 37 |

|     |       | 1.4.1.1 Origin of small inter-electrode capacitance in GaN-            |    |

|     |       | HEMTs                                                                  | 37 |

|     |       | 1.4.1.2 Inter-electrode capacitance comparison between MOS-            |    |

|     |       | FETs and GaN-HEMTs                                                     | 37 |

|     |       | 1.4.1.3 Fast switching speed of GaN-HEMTs                              | 37 |

|     | 1.4.2 | Influence of parasitic parameters on GaN-HEMTs switching               |    |

|     |       | behaviour                                                              | 38 |

|     |       | 1.4.2.1 Parasitic inductance in the half-bridge circuit                | 38 |

|     |       | 1.4.2.2 False turn-on and gate instability phenomenon                  | 39 |

|     | 1.4.3 | Parasitic parameters considered in this work                           | 42 |

| 1.5 | Sumr  | mary of findings                                                       | 42 |

### 1.1 Research context

It has been more than 70 years since the invention of the first silicon (Si)-based transistor. During this time period, researchers and engineers have diligently worked to enhance Si-based transistors, pushing the devices' performance to the limits of the Si material [1]. The limitation of conductivity and breakdown voltage of Si-based transistors have posed an obstacle to further enhancing the efficiency of the electrical energy conversion. In the past ten years, wide band-gap (WBG) semiconductors, silicon carbide (SiC) and gallium nitride (GaN), have become key candidates to deliver higher efficiency for energy conversion and contribute to meeting the net-zero goals for carbon emissions.

With the notable development of digital economy, the massive amounts of data create a surge energy demand, posing a new challenge for power supplies in data centres. Moreover, the rapid development of artificial intelligence (AI) could push the energy consumption to the next level. The utilisation of WBG semiconductor transistors comes in anticipation to address this challenge. For example, the replacement of Si-based

1.1. Research context 5

power supplies with GaN-based power supplies in the data centers worldwide from 2015 to 2021 could save  $21^3$  TWh of energy and reduce  $10^6$  Mt of  $CO_2$  [2].

Furthermore, the requirement of sustainability imposes a new set of rules for reducing the carbon footprint of power converters due to environmental considerations. It demands considering the environmental impact throughout the entire lifecycle of power converters, including reduced carbon emissions during fabrication, longer estimated lifetimes, and recyclability [3]. The utilisation of the GaN power transistors could enhance sustainability from various aspects, as illustrated the next subsection.

### 1.1.1 Energy conversion efficiency

Improving the efficiency of power converters is a significant challenge, as it contributes to reducing losses during the energy conversion. The main losses of power converters come from the transistors, which are primarily categorised into conduction losses and switching losses [4]. The simplified operation conditions of an ideal switch and a transistor (hard-switching) are depicted in Fig. 1.1. For the ideal switch, the current and voltage commutations occur instantaneously, resulting in zero switching losses. During the conduction state, there is no voltage drop across the switch due to the zero on-state resistance  $R_{on}$ , leading to no conduction losses. However, for real transistors, it takes time for the commutation of voltage and current, resulting in switching losses. The non-zero  $R_{\rm op}$  produces conduction losses during the on-state transistor functioning. Therefore, power transistors with fast commutation speed and low  $R_{on}$  are expected to be implemented in the high-efficiency power converters. Compared to the conventional Si devices, GaN power transistors have garnered increasing attention due to their characteristics, which more closely resemble the ideal switches. An example illustrative supporting the GaN transistor technology is the 900 W three-phase inverter, where under full load its efficiency have been improved from 98.2 % to 99.3 % by replacing the Si insulated gate bipolar transistors (IGBTs) with gallium nitride high electron mobility transistors (GaN-HEMTs) [5]. Moreover, a GaN-based 2.5 kW totem-pole power factor correction (PFC) with 99 % peak efficiency is reported in [6].

### 1.1.2 Power density and sustainability

High power density is another key objective in the power converter design, and it is defined as the amount of power per unit volume. The power density of power converters is mainly determined by the passive devices, such as transformers, capacitors and heat sinks. The volume of inductors or capacitors in power converter applications is mainly determined by the operating frequency, and it could be significantly reduced by increasing the frequency. However, the switching losses of power transistors become more prominent at higher operation frequencies. Therefore, it is highly recommended to use GaN transistors in high-frequency due to their fast switching speed, which results in lower switching losses compared to other power transistors. For example, in a GaN-based 1 MHz inductor-inductor-capacitor (LLC) resonant DC-DC converter, the size of transformer can be reduced 6 times compared to the Si transistor based 1 kHz design,

Figure 1.1: Schematic of operation conditions and switching waveforms of (a) an ideal switch and (b) a transistor.

and the power density can reach up to  $8.5 \,\mathrm{W}\,\mathrm{cm}^{-3}$  [7]. Moreover, the low  $R_{\mathrm{on}}$  contributes to decreasing the overall conduction losses, thereby reducing the size of the heat sink.

High power density contributes to improving space efficiency and reducing costs. More importantly, sustainability and the low carbon footprint of power converters can significantly benefit from it by requiring fewer materials and energy during fabrication. Therefore, GaN power transistors show significant advantages for achieving high efficiency and high power density converters, which in turn contribute to the sustainability of power conversion systems [8].

However, GaN-HEMTs exhibit unique characteristics, such as the dynamic  $R_{\rm on}$  and threshold voltage  $V_{\rm th}^{-1}$  shift phenomena, combined with a high sensitivity to parasitic parameters. These characteristics hinder further increases in the efficiency and power density of GaN-based power converters. Moreover, most driving technologies and evaluation standards for GaN-HEMTs are inherited from Si-based technology. To fully release the superior performance of GaN-HEMTs in power converters, it is necessary to understand and characterise these special features and evaluate their influence on device applications.

# 1.2 GaN material and power transistors

The typical characteristics of GaN power transistors will be reviewed in this section, starting from their material properties, followed by the structure and operation mechanisms of GaN-HEMTs, and concluding with the overview of the commercialised GaN-HEMTs and vertical power devices under development.

<sup>&</sup>lt;sup>1</sup>Refers to the minimum gate-to-source voltage that can turn the transistor to on-state.

### 1.2.1 Material properties comparison of Si, SiC and GaN

The performance of power transistors initially originate from the material properties. The material parameters of Si, SiC and GaN are compared in Table 1.1. The GaN material has a wide band gap ( $E_{\rm g}$ ), which means more energy is required to excite the valence electrons to the conduction band compared to the other two counterparts. Therefore, GaN transistors can work at high operating temperature. A good example supporting the GaN stability at high temperatures is reported in [9], where the basic I-V characteristics of an enhancement-mode GaN-HEMT is characterised under 500 °C in NASA Glenn Extreme Environment Rig to simulate the Venus environment, the device only showing a minor degradation after 10 days of continuous operation. Additionally, GaN has a very high critical electric field ( $E_{\rm crit}$ ), meaning that shorter drift region can be achieved for the same breakdown voltage. The relative high  $E_{\rm crit}$  combining with the lateral structure of GaN-HEMT reduces the size of the device. The  $E_{\rm crit}$  possesses a power-law dependence on the band gap, expressed as  $E_{\rm crit} \propto E_{\rm g}^{2.3}$  [10]. Therefore, the GaN material fits the technological profile for fabricating high-temperature and high-voltage power transistors.

| Material parameters                               | Unit               | Si   | 4H-SiC * | GaN            |

|---------------------------------------------------|--------------------|------|----------|----------------|

| Band gap $(E_g)$                                  | eV                 | 1.12 | 3.23     | 3.4            |

| Critical electric field $(E_{crit})$              | MV/cm              | 0.3  | 2.5      | 3.3            |

| Relative dielectric permittivity $(\epsilon_{r})$ |                    | 11.7 | 10       | 8.9            |

| Electron mobility $(\mu)$                         | $cm^2/(V \cdot s)$ | 1440 | 950      | 2000 (2DEG) ** |

| Electron saturation velocity $(v_s)$              | $10^7 \text{cm/s}$ | 1    | 2        | 2.4            |

| Thermal conductivity $(\kappa_{th})$              | $W/(m \cdot K)$    | 1.3  | 3.7      | 2.5            |

<sup>\* 4</sup>H-SiC is one of the major polytypes of SiC crystalline structure.

Table 1.1: Comparison of the material properties of Si, SiC, and GaN [11], [12].

The GaN material exhibits the lowest relative dielectric permittivity ( $\epsilon_r$ ), as shown in Table 1.1, which contributes to achieving smaller inter-electrode capacitances for power transistors. The small inter-electrode capacitance is one of the main reasons why GaN power transistors can achieve ultra-fast switching speeds, effectively reducing switching losses. To be noted that the electron mobility ( $\mu$ ) increases the conductivity of semiconductors, and the  $\mu$  of GaN materials is higher when compared to SiC and it contributes as well to reducing the conduction losses of GaN transistors. Since a single parameter is not relevant for a thorough comparison on material properties, several figure of merit (FOM) are proposed to further asses their performance as discussed below.

On the one hand, the high speed performance of high frequency transistors can be

<sup>\*\*</sup> The electron mobility of 1400 cm<sup>2</sup>/(V·s) is reported for bulk GaN materials in [11]. The 2DEG will be further explained in section 1.2.2.2.

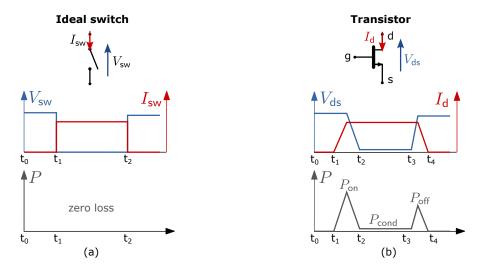

Figure 1.2: Normalised JFOM and BFOM of Si and SiC to GaN (materials' data is from Table 1.1).

described by the Johnson figure of merit (JFOM) that is defined as [11]:

$$JFOM = \frac{v_{s} \cdot E_{crit}}{2\pi} = f_{t,max} \cdot V_{ds,max}$$

(1.1)

where  $f_{\rm t,max}$  and  $V_{\rm ds,max}$  represent the maximum transient frequency and drain-to-source voltage respectively.

On the other hand, the Baliga figure of merit (BFOM) is used to evaluate the conduction losses for power semiconductors from the material perspective [13]. It is based on the assumption that the power losses solely originate from the  $R_{\text{on}}$  of power transistors, expressed as:

$$BFOM = \mu \cdot \epsilon_{r} \cdot E_{crit}^{3} \tag{1.2}$$

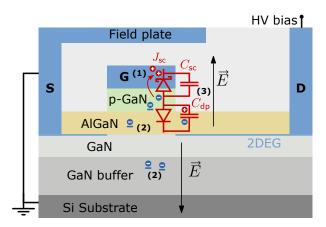

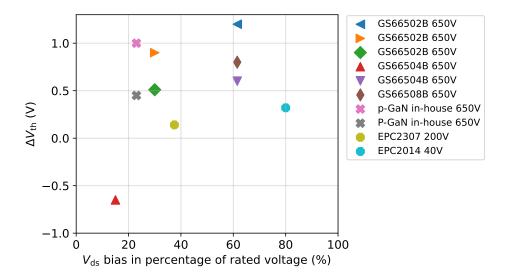

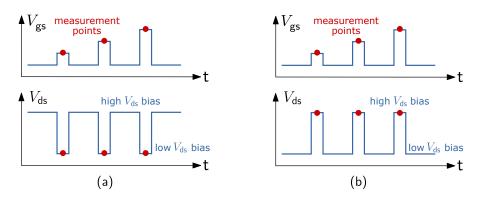

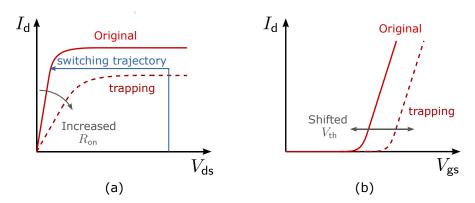

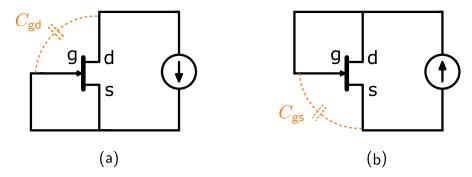

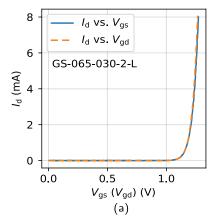

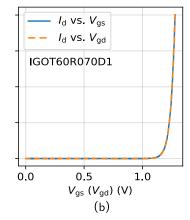

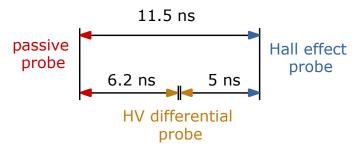

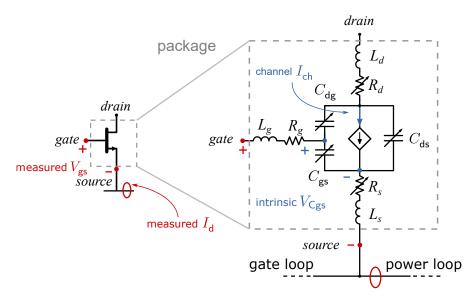

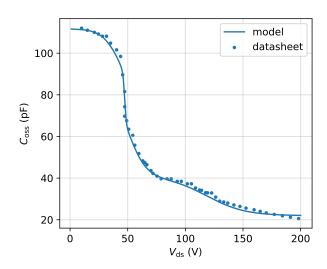

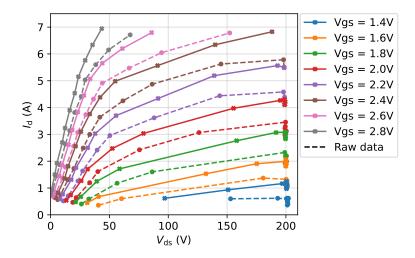

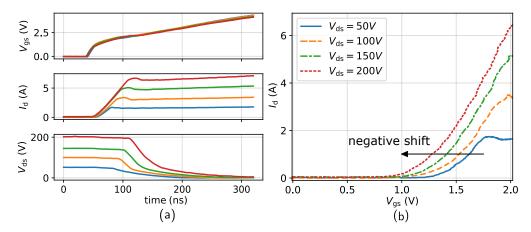

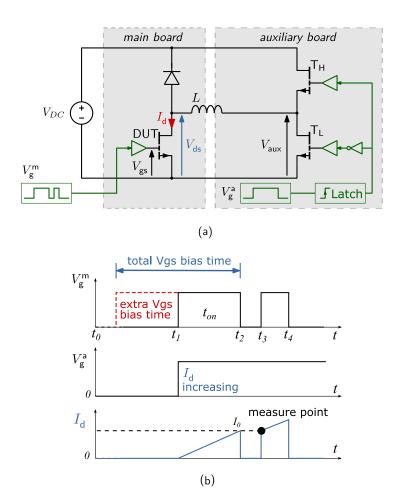

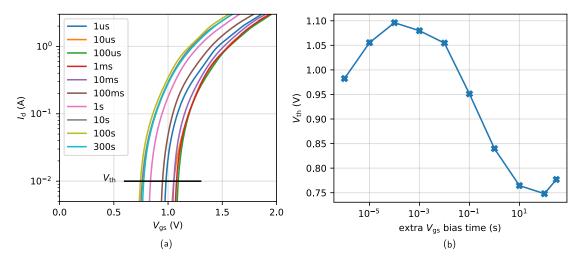

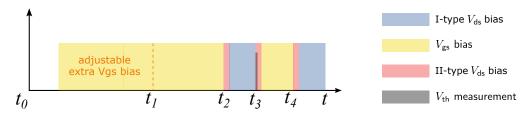

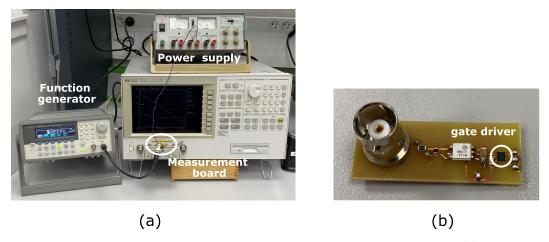

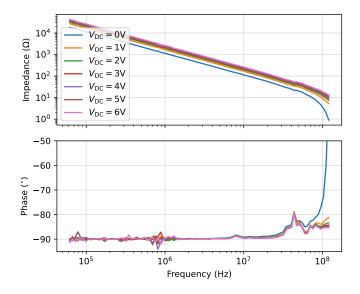

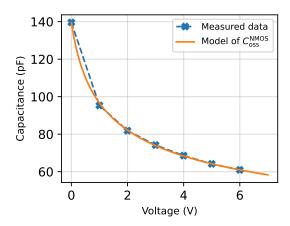

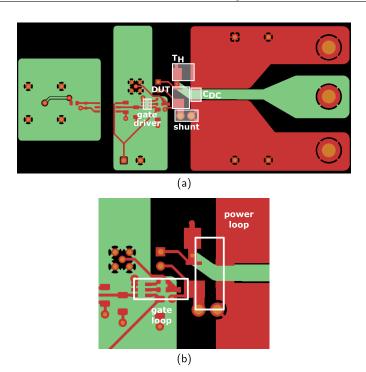

In a p-n junction, the  $R_{on}$  of the n-type semiconductor region is inversely proportional to the BFOM [10], therefore, high BFOM is helps to reduce the conduction losses.