## **THESE**

### Présentée à L'Université des sciences et technologies de Lille Ecole Doctorale Sciences pour L'Ingénieur

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITE

Spécialité: MICROONDES ET MICROTECHNOLOGIES

par

#### Baudouin MARTINEAU

Potentialités de la technologie CMOS 65nm SOI pour des applications sans fils en bande millimétrique

Soutenue le 16 Mai 2008 devant la commission d'examen

Membres du Jury : Alain CAPPY Président

François DANNEVILLE Directeur de thèse Andreia CATHELIN Tuteur industriel

Yann DEVAL Rapporteur

Thierry PARRA Rapporteur

Ali NIKNEJAD Examinateur

Christine RAYNAUD Examinateur

Andreas KAISER Examinateur

## Remerciements

Cette thèse s'est déroulée sur deux périodes et dans deux lieux. Cela m'a permis de lier des amitiés et des collaborations au laboratoire CNRS-IEMN de Lille 1 et au sein de la société STMicroelectronics à Crolles. Je tiens à remercier toutes les personnes sans qui ce travail n'aurait pas été possible.

Je remercie Monsieur Alain Cappy pour m'avoir accueilli dans son laboratoire et avoir accepté d'être le président du jury de cette thèse.

Je remercie Messieurs Yann Deval et Thierry Parra, rapporteurs de ces travaux. Je remercie Andreas Kaiser, Ali Niknejad et Christine Raynaud pour leur participation en tant qu'examinateurs.

Je remercie également mes encadrants de thèse. Andreia Cathelin pour sa disponibilité, sa confiance et son engagement pour la réussite de ces travaux. François Danneville pour sa sincérité, sa rigueur, ses connaissances et son amitié. Je remercie Gilles Dambrine pour m'avoir accueilli dans le groupe ANODE. J'ai également une pensée très chaleureuse pour Sylvie Lepillet sans qui les mesures figurant dans ce manuscrit n'auraient pu être possible. Je remercie Didier Belot pour m'avoir accueilli dans son équipe au sein de STMicroelectronics.

Je remercie tous les membres du groupe ANODE, Alexandre Siligaris, Jean-Marc Bethoux, Guillaume Pailloncy, Cristian Andrei, Cyrille Gardes, Andrey Shchepetov, Raphael Valentin, Nicolas Waldhoff Jean-Sébastien Galloo, ...Grace à vous j'ai découvert le nord, et bien d'autre pays!

Je remercie aussi tous les personnes avec qui j'ai pu lier de fortes relations au sein de STMicroelectronics: Thomas Finateu, Nicolas Seller, Franck Badets, Cyrille Tilhac, Jonathan Muller, Anna Asquini, David Marchaland, Ivan Miro Panades, Vincent Knopik, Olivier Richard, Stéphane Razafimandimby, Vincent Lagareste, David Chamla, Raphael Paulin, Sébastien Pruvost, Patrick Scheer, José-Luis Gonzalez et bien d'autre... Je remercie également Pascale Maillet Contoz pour sa disponibilité et sa gentillesse.

Je remercie particulièrement les membres de la ST SOI Team! Frederic Gianesello pour ses conseils toujours avisés, son amitié et sa bonne humeur indispensable pour traverser le désert Californien à 2h30 du matin. Christine Raynaud, sans qui tout ce travail n'aurait jamais existé, j'espère à mon tour avoir apporté ma pierre à l'édifice SOI. Et bien sur Carlo Tinella qui un dimanche soir m'a appelé en me disant qu'il me verrait bien faire une thèse sur la technologie CMOS SOI. Je ne pensais pas que ce coup de téléphone bouleverserait le cours de ma vie.

Enfin, je remercie Isabelle tour à tour collègue, amie, fiancée et bientôt ma femme pour son amour au quotidien.

Mon dernier merci est pour ma famille et mes parents qui ont toujours cru en moi et m'ont soutenu dans toutes mes décisions...

## Contents

| Introduction     | on                                                         | 1    |

|------------------|------------------------------------------------------------|------|

|                  | ny                                                         |      |

| C1               |                                                            | _    |

| •                | The CMOS Silicon On Insulator Technology                   |      |

|                  | SOI Substrate                                              |      |

|                  | SFET transistor on bulk and SOI                            |      |

| I.2.1.           | Comparison between bulk and SOI MOSFET                     |      |

| I.2.1.a          | 05                                                         |      |

| I.3. Pro         | perties and Behavior of SOI MOSFET                         |      |

| 1.3.1.           | 13                                                         | ЭГЕ1 |

| I.3.2.           | Floating Body effects                                      | 15   |

| I.3.2.a          |                                                            |      |

| I.3.2.b          | . Parasitic open based NPN bipolar effect in FD SOI MOSFET | 16   |

| I.3.3.           | Which SOI Device for which design?                         | 17   |

| I.4. FB a        | and BC MOSFET from the CMOS SOI 65nm technology            | 18   |

| I.4.1.           | Which PD SOI MOSFET for which design?                      | 19   |

| I.5. Sun         | nmary                                                      | 20   |

| I.6. Bibl        | liography                                                  | 21   |

| Chantar II       | Actives elements in SOI CMOS 65nm                          | 24   |

| •                |                                                            |      |

|                  | stor RF figures of merit                                   |      |

|                  | requency small signal model of the SOI MOSFET transistor   |      |

| II.2.1.          | Quasi static model                                         |      |

| II.2.2.          | Non quasi static model                                     |      |

| II.2.2. <i>a</i> | r - r                                                      |      |

| II.2.2.1         | , 8                                                        |      |

| II.3. Noise      | analysis of the MOSFET transistor                          | 29   |

| II.3.1.          | Flicker Noise                                              | 30   |

| II.3.2.          | Thermal noise                                              | 30   |

| II.3.3.          | Thermal noise from access resistances                      | 31   |

| II.4. Noise      | temperatures                                               | 32   |

| II.4.1.          | High Frequency noise measurements and associated models    |      |

| II.5. SOI M      | OSFET characterization                                     |      |

| II.5.1.          | DC performances                                            |      |

| II.5.2.          | RF performances                                            |      |

|                  | Transistors State of the Art                               |      |

|                  | FT Transistor Models                                       | 40   |

| II.      | 7.1.a.            | BSIM3 SOI Model                                                    | 40 |

|----------|-------------------|--------------------------------------------------------------------|----|

| II.7.2   | 2. BS             | IM4 model                                                          | 41 |

| II.8. Su | mmary.            |                                                                    | 43 |

|          | -                 | hy                                                                 |    |

|          |                   | Kes:                                                               |    |

| 11,10,11 | P P CTTOLES       |                                                                    |    |

| Chanter  | III - Pa          | assive elements in SOI CMOS 65nm                                   | 51 |

| III.1.   |                   | ve elements for RF and Millimeter wave frequencies                 |    |

| III.1.   |                   | ssives elements states of the art in industrial silicon technology |    |

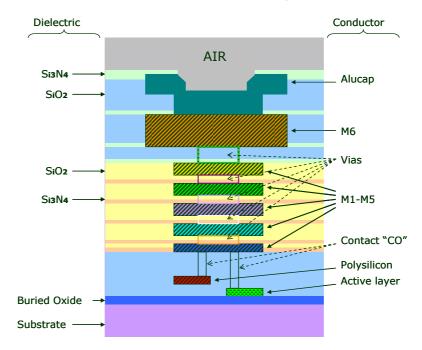

| III.1.   |                   | erconnects in 65nm SOI CMOS technology                             |    |

|          | <br>[.1.2.a.      | Multi-layer constraints of integration                             |    |

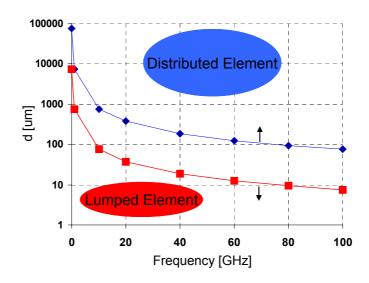

| III.1.   |                   | mped or distributed circuit elements?                              |    |

|          | [.1.3.a.          | Working Frequency                                                  |    |

|          | [.1.3.b.          | Self Resonant Frequency                                            |    |

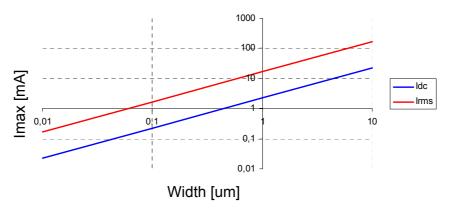

| III      | [.1.3.c.          | Current Density                                                    |    |

| III.1.   | 4. Inc            | ductors in SOI CMOS technology                                     |    |

| III      | [.1.4.a.          | SOI Inductors for RF applications                                  |    |

| III      | [.1.4.b.          | Millimeter Wave Inductance                                         |    |

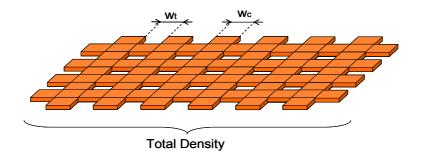

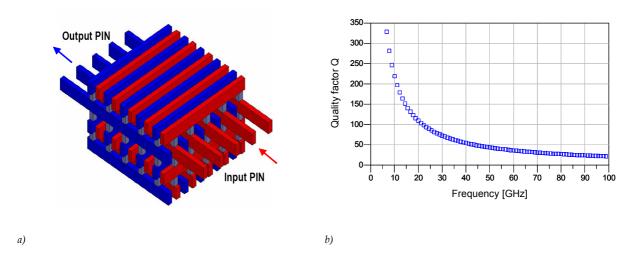

| III.1.   | 5. MO             | OM Capacitor in SOI CMOS technology                                | 63 |

| III.1.   |                   | aveguide components on silicon substrate                           |    |

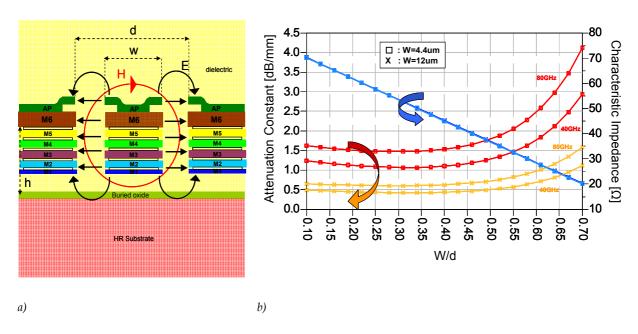

| III      | [.1.6.a.          | Transmission Lines                                                 |    |

| III      | [.1.6.b.          | Thin Film Microstrip Line                                          | 66 |

| III      | [.1.6.c.          | Coplanar Waveguide                                                 | 68 |

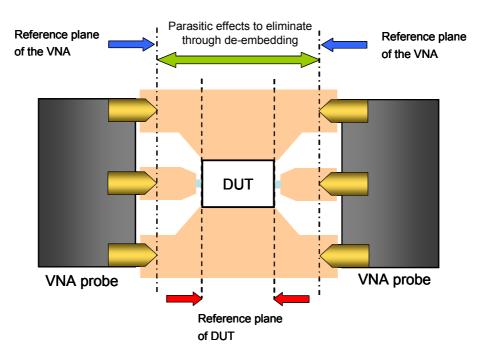

| III.2.   | Passi             | ve elements characterization                                       | 73 |

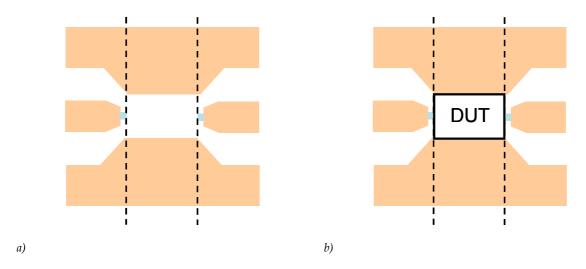

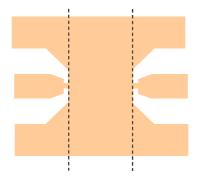

| III.2.   | 1. De             | -embedding methodology                                             | 73 |

| III      | [.2.1.a.          | Open Circuit de-embedding                                          | 74 |

| III      | [.2.1.b.          | Open-Short Circuit De-embedding                                    | 74 |

| III      | [.2.1.c.          | De-Embedding Comparison                                            | 75 |

| III.2.   |                   | ectromagnetic Simulation                                           |    |

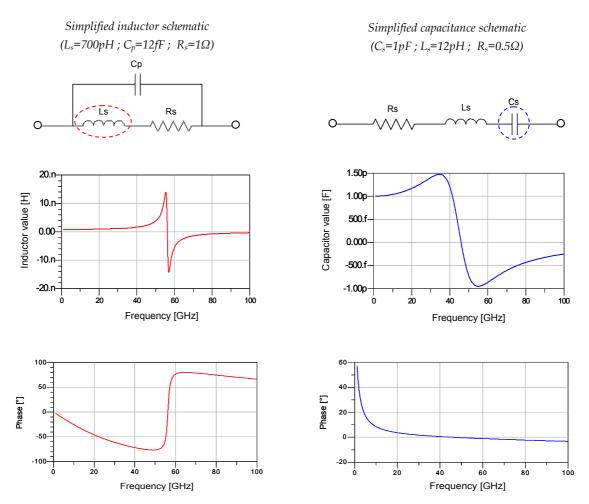

| III.3.   | Mode              | eling of passive elements                                          | 78 |

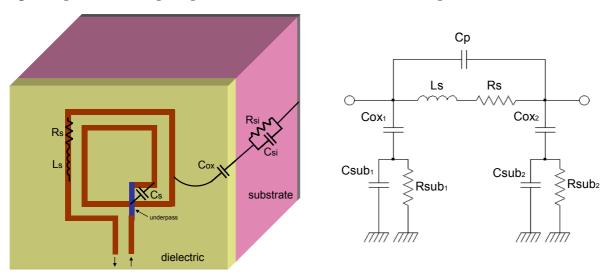

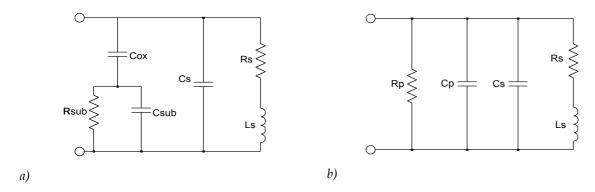

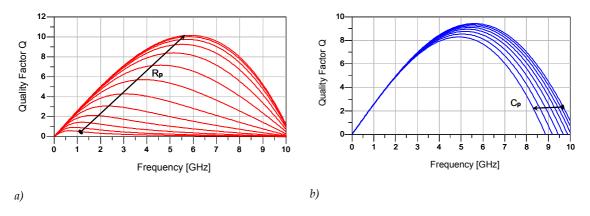

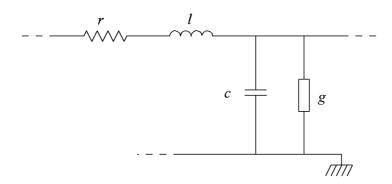

| III.3.   | 1. Inc            | luctance                                                           | 78 |

| III      | [.3.1.a.          | Analytical                                                         | 78 |

| III      | [.3.1.b.          | Model extraction from measurement                                  | 81 |

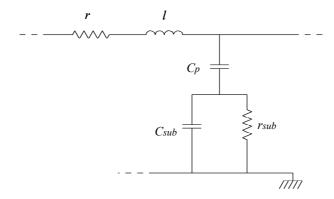

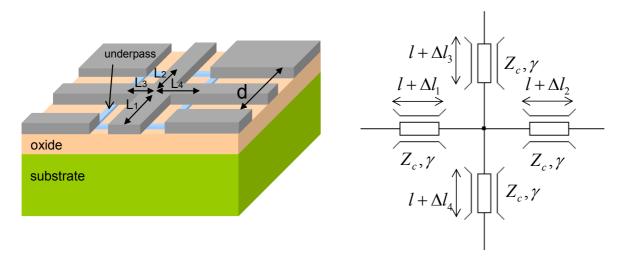

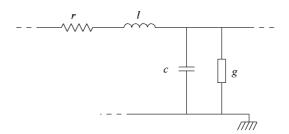

| III.3.   | 2. Co             | planar Lines                                                       |    |

| III      | [.3. <b>2</b> .a. | Analytical model                                                   |    |

| III      | [.3. <b>2</b> .b. | Model extraction from measurement                                  |    |

| III.4.   |                   | nary                                                               |    |

| III.5.   |                   | ography                                                            |    |

| III.6.   |                   | endixes:                                                           |    |

| A.       |                   | and $\epsilon_{r eff}$ calculation from S parameters measurement   |    |

| В.       |                   | ormal mapping                                                      |    |

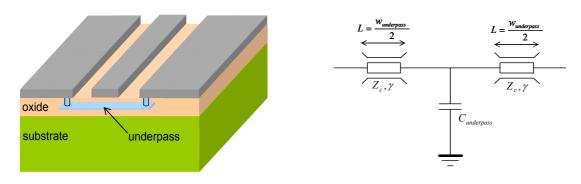

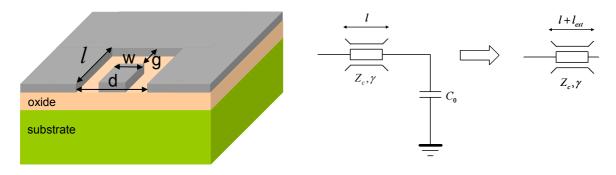

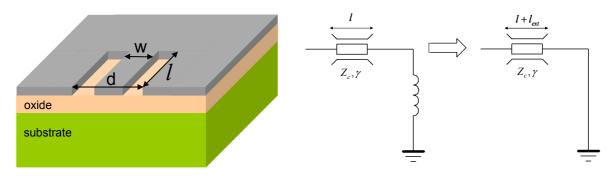

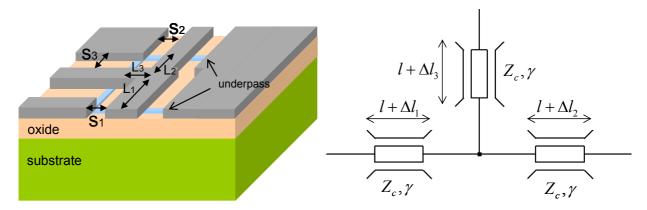

| C.       | Disco             | ntinuities modeling                                                | 96 |

| Chapter IV   | - D  | esign of millimeter wave receiver building blocks                     | 99    |

|--------------|------|-----------------------------------------------------------------------|-------|

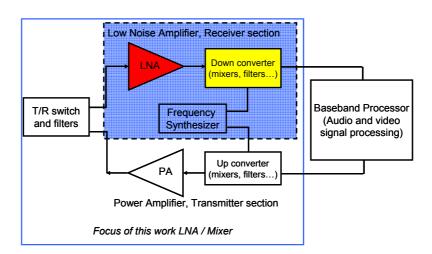

| •            |      | range specification for a receiver                                    | 100   |

| IV.1.1.      |      | ise Figure                                                            |       |

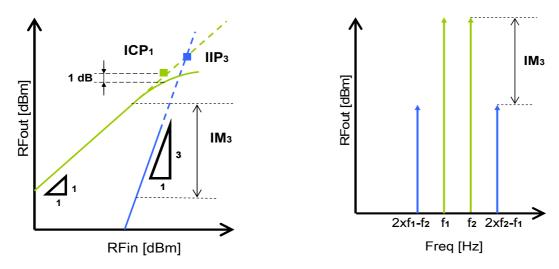

| IV.1.2.      |      | nearity                                                               |       |

| IV.1.3.      | Re   | ception sensitivity and dynamic range                                 | 103   |

| IV.2. Millin |      | r wave LNA and Mixer state of the art in industrial silicon technolog |       |

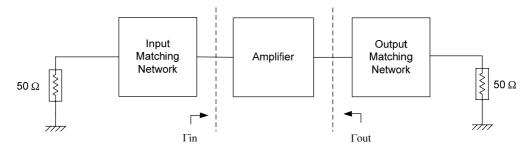

|              |      | r wave LNA Design considerations                                      |       |

| IV.3.1.      |      | [A stability                                                          |       |

| IV.3.1       |      | Techniques to achieve stability                                       |       |

| IV.3.1       | .b.  | Stability in multi-stages amplifiers                                  |       |

| IV.3.2.      | LN   | A design                                                              |       |

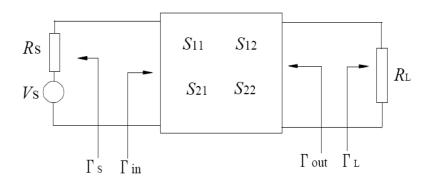

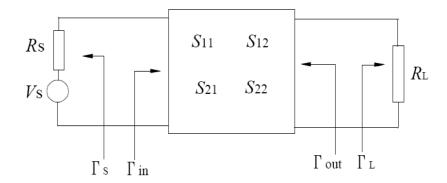

| IV.3.2       | 2.a. | Noise Figure for two ports network amplifier                          | 112   |

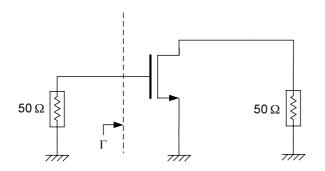

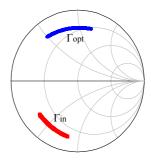

| IV.3.2       | 2.b. | Transistor impedance matching                                         |       |

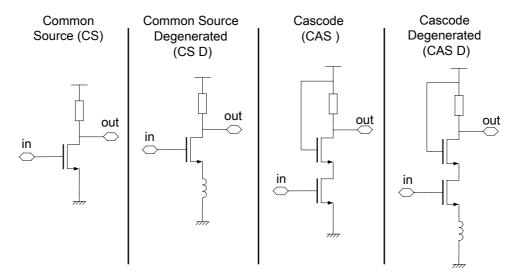

| IV.3.2       | 2.c. | LNA topologies                                                        |       |

| IV.3.2       | 2.d. | Millimeter wave matching network                                      | 118   |

| IV.3.3.      | LN   | A design methodology summary                                          | 121   |

| IV.4. Millir |      | r wave CMOS SOI building blocks                                       |       |

| IV.4.1.      |      | GHz and 94GHz CMOS SOI single stage common source amplifier           |       |

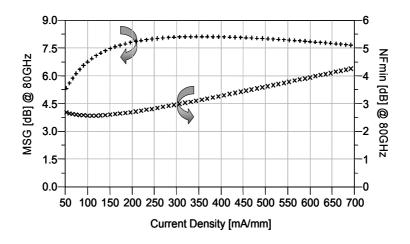

| IV.4.1       | .a.  | 80GHz CMOS SOI single stage amplifier simulations and measure         | ments |

|              |      | 125                                                                   |       |

| IV.4.1       | .b.  | 94GHz CMOS SOI single stage amplifier simulations and measure 125     | ments |

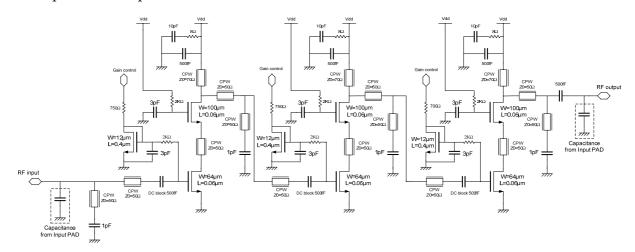

| IV.4.2.      | 800  | GHz CMOS SOI three stages LNA                                         | 127   |

| IV.4.2       |      | 80GHz CMOS SOI three stages LNA simulations and measuremen            |       |

| IV.4.3.      | 600  | GHz CMOS SOI three stages LNA                                         |       |

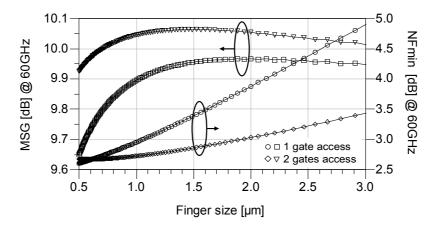

| IV.4.3       |      | 60GHz CMOS SOI three stages LNA simulations                           |       |

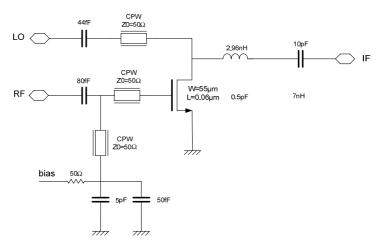

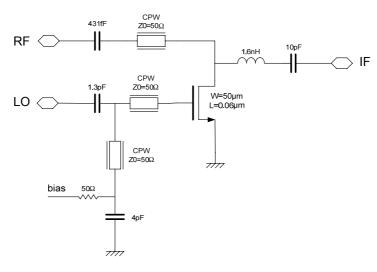

| IV.4.4.      | 600  | GHz CMOS SOI drain pumped mixer                                       |       |

| IV.5. Millir |      | r wave bulk CMOS 65nm building blocks                                 |       |

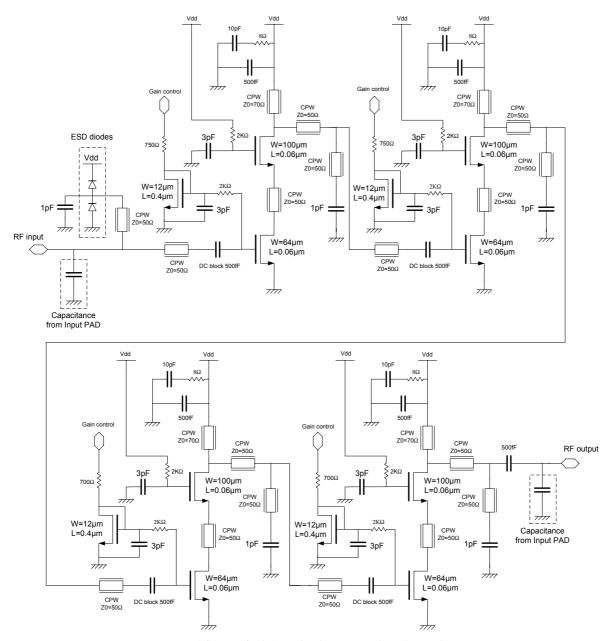

| IV.5.1.      |      | GHz 4 stages bulk CMOS LNA with ESD protections                       |       |

| IV.5.1       |      |                                                                       |       |

| IV.5.1       | .b.  | Performance summary of the 60GHz CMOS LNA for different pov           |       |

| consu        | mpt  | ions                                                                  | 141   |

| IV.5.2.      | 600  | GHz bulk CMOS resistive mixer                                         | 142   |

| IV.5.3.      | 600  | GHz bulk CMOS front-end co-integration                                | 143   |

| IV.5.4.      |      | mparison between CMOS bulk and SOI for mm-wave applications           |       |

| IV.5.4       |      | Circuits comparison                                                   |       |

| IV.6. Sumr   | nary |                                                                       |       |

|              |      | ohy                                                                   |       |

|              | -    | :                                                                     |       |

| Conclus      |      |                                                                       | 151   |

## Introduction

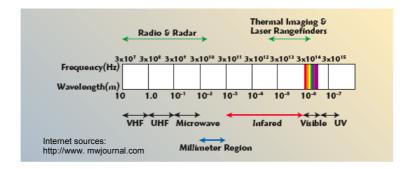

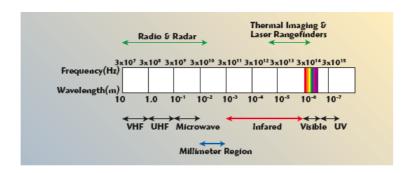

According to the *Figure 1*, the millimeter wave band is defined as the frequency band covering 30 to 300 GHz which means a wavelength between 1 and 10 mm. There are many advantages associated with increasing the operating frequency for already developed applications. They include the potential for increased available bandwidth and the directivity which can be obtained for a given antenna aperture. This implies smaller size systems offering increased transmission capacity in the case of communication systems or improved resolution for radar or imaging systems. In the latter case, millimeter wave systems are used to achieve useful resolution for image recognition, or identify explosive materials by their spectroscopic signatures [1].

Figure 1. Millimeter-wave region of the electromagnetic spectrum [2]

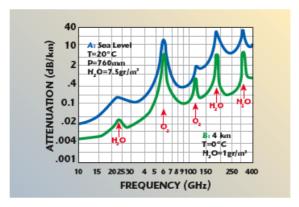

Additionally, there are unique features associated with the transmission properties of the atmosphere in the millimeter spectrum region. Figure 2 shows the effective zenith atmospheric transmission in dB/km for typical conditions at sea level and at an altitude of 4 km. The impact of the 60 and 120GHz  $O_2$  lines and multiple resonances of the  $H_2O$  molecule can be seen. The high attenuation of the 60GHz  $O_2$  allows high density unlicensed communication and covert systems.

Internet sources: http://www. mwjournal.com

Figure 2. Atmospheric attenuation within the millimeter-wave spectrum

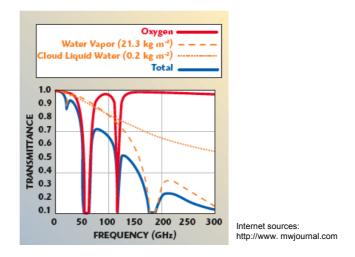

The window frequencies are better illustrated in *Figure 3*, which shows linear transmission at zenith with the contributions due to atmospheric gases and liquid water for a mid-latitude location.

Figure 3. Atmospheric transmission in the 30 to 300 GHz region.

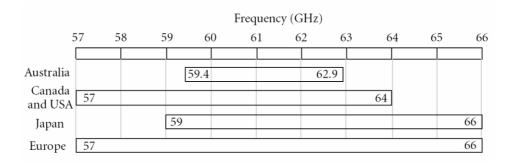

The 50 to 60 GHz band may be used at shorter ranges for high data rate communications (0.5 to 5... 10Gb/s) such as wireless uncompressed HD-video streaming (W-HDMI) and ultra fast file transfers (USB2.0, ...). The available unlicensed band extends from 57GHz to 66GHz depending on the geographic region (*Figure 4*). Four organizations drive the 60-GHz radios standardization. Among them, there are the IEEE standard body [1], [3] and the WiMedia alliance which is an industrial association [4]. The IEEE 802.15.3 Task Group 3c (IEEE 802.15.3c) is developing a millimeter wave based alternative physical layer (PHY) for the existing 802.15.3 WPAN Standard IEEE-Std-802.15.3-2003. With merging of former multiband OFDM alliance (MBOA), the WiMedia alliance is pushing a 60GHz WPAN industrial standard, likely based on orthogonal frequency division multiplexing (OFDM) technology. The shooting data rate is 2 Gb/s or higher. Among a large number of proposals, the majority of them can be categorized to either multi-carrier (meaning OFDM) or single-carrier types, where the former one is expected to support extremely high data rates (10 Gb/s).

Figure 4. Unlicensed band going from 57 to 66GHz

The second targeted application is automotive. Adaptive cruise control systems using 24GHz and 77GHz frequency bands sensors are now a reality. Initially based on Gunn diode technologies, it is becoming one of the main application areas for GaAs MMICs and a potential market for lower cost (Bi)CMOS/SOI¹ CMOS. These sensors are marketed as autonomous cruise control (ACC) radars. The last potential applications are the mm-wave imaging systems for medical and security applications. These topics have been the subject of intensive recent developments, responding to the security needs of airports and other establishments. In the middle 80s companies such as *Millitech* or *TRW* (now *NGST10*) had been prototyping millimeter wave cameras. Today, the targeted frequency bands for such applications are at 94GHz and above 100GHz.

The present thesis evaluates the 65nm CMOS SOI for millimeter wave design, in order to address the above applications. This work is built on four chapters which are decomposed as follows:

Chapter I reviews the SOI technology. After presenting the major industrial groups working on SOI, it highlights the major benefits of the SOI-MOSFETs in comparison with bulk transistors. Partially Depleted and Fully Depleted SOI transistors are also discussed.

Chapters II and III treat about the active and passives elements in CMOS SOI. Several figures of merit are introduced. The characterization and modeling methodologies developed in this thesis work are presented and discussed. The performances of the CMOS SOI and bulk 65nm technology are compared with the state of the art.

Chapter IV introduces and develops CMOS integrated millimeter wave receiver requirements. Special focus is put on LNAs and Mixers in 65nm CMOS node on bulk and SOI substrate. A robust industrial millimeter wave CMOS design methodology developed during this thesis is presented. Finally, LNA and mixer simulations and measurements for millimeter wave systems (77GHz and 60GHz) are presented and a comparison between CMOS bulk and SOI for these target frequencies is examined.

The *conclusion* summarizes the major contributions of this thesis and suggests topics which merit further work.

.

<sup>&</sup>lt;sup>1</sup> SOI: Silicon On Insulator

# Bibliography

- [1] A. Cathelin, et al., "Design for Millimeter-wave Applications in Silicon Technologies", *ESSCIRC2007*, Munich, Sept. 2007.

- [2] http://www.mwjournal.com

- [3] IEEE 802.15 Working Group for WPAN, http://www.ieee802.org/15/.

- [4] WiMedia alliance, http://www.wimedia.org/.

# Chapter I

# The CMOS Silicon On Insulator Technology

In this chapter, we present the Silicon on insulator technology (SOI) which refers to the use of a layered silicon-insulator-silicon substrate in place of conventional silicon substrates in semiconductor manufacturing. The SOI technology is already in use in the industry, for example in *AMD*'s 130 nm, 90 nm and 65 nm single, dual and quad core processors since 2001. *Freescale* has also adopted SOI in its PowerPC 7455 CPU in late 2001; currently Freescale is shipping SOI products in their 180nm, 130nm, 90nm and 65nm lines. *IBM* began to use SOI in *PowerPC G4 7455* chips since late 2000. The 90 nm PowerPC-based processors used in the *Xbox 360*, *PlayStation 3* and *Wii* use SOI technology as well. On the foundry side, *Chartered Semiconductor* devoted a whole fab to SOI.

Internet Sources: Silicon Strategies, EE Times & Enews

Figure I.1. SOI users with new factories or high production based on SOI 300 mm wafers

Recently, a group of companies have launched a silicon-on-insulator (SOI) consortium that is aimed at accelerating the technology in the marketplace [1].

The SOI Industry Consortium will also promote the benefits of SOI technology in the market. The founding membership in the group includes the following: *AMD*, *ARM*, *Cadence*

Design Systems, CEA-Leti, Chartered Semiconductor Manufacturing, Freescale Semiconductor, IBM, Innovative Silicon, KLA-Tencor, Lam Research, NXP, Samsung, Semico, Soitec, SEH Europe, STMicroelectronics, Synopsys, TSMC and UMC.

## I.1. The SOI Substrate

SOI-based devices differ from conventional silicon-built devices in that the silicon junction is above an electrical insulator, typically silicon dioxide. The choice of the insulator depends largely on intended application, with sapphire being used for radiation-sensitive applications and silicon oxide preferred for improved performance and diminished short channel effects in microelectronics devices. From a manufacturing perspective, SOI substrates are compatible with most of the conventional fab processes. In general, an SOI-based process may be implemented without special equipment or significant retooling of an existing process. The primary barrier to SOI implementation is the increase in substrate cost, which contributes an estimated 10 - 15% increase to total manufacturing costs.

Many techniques have been developed for producing a film of single-crystal silicon on top of the insulator. Some of them are based on the epitaxial growth of silicon on either a silicon wafer covered with an insulator (homo-epitaxial techniques) or on a crystalline insulator (hetroepitaxial techniques). Other techniques are based on recrystallization of thin silicon layer from the melt (laser recrystallization, e-beam recrystallization and zone-melting recrystallization). Silicon-on-insulator can also be produced from a bulk silicon wafer by isolating a thin silicon layer from the substrate through the formation and oxidation of porous silicon (FIPOS) or through the ion beam synthesis of a buried insulator layer (SIMOX¹, SIMNI and SIMON). Finally, SOI material can be obtained by thinning a silicon wafer bonded to an insulator and mechanical substrate (wafer bonding BESOI). Every approach has its advantages and its drawbacks, and the type of application to which the SOI materials is destined dictates the material to be used in each particular case. SIMOX and UNIBOND² seem to be the ideal candidates for VLSI CMOS application, while wafer bonding is more adapted to bipolar and power applications.

In the last decade, the dominant SOI technology was SIMOX, which is synthesized by internal oxidation during the deep implantation of oxygen ions into a silicon wafer. Annealing at high temperature restores the crystalline quality of the film. SIMOX wafers

<sup>&</sup>lt;sup>1</sup> Silicon Implanted Oxide

<sup>&</sup>lt;sup>2</sup> Trade name for SOI wafers using Smart Cut process

have good thickness uniformity, low defect density, sharp Si-SiO<sub>2</sub> interface, robust BOX<sup>3</sup>, and high carrier mobility.

Wafer bonding and etch back is another mature SOI technology. An oxidized silicon wafer is bonded to a second silicon wafer. When two flat, hydrophilic surfaces such as oxidized surfaces are placed against one another, bonding naturally occurs, even at room temperature, which forms the hydrogen bonds across the gap between two surfaces. After bonding, upper wafer is thinned down from 600µm to few microns to reach the target thickness of the silicon film. The thinning is usually done grinding followed by chemical polishing followed by etch-back process.

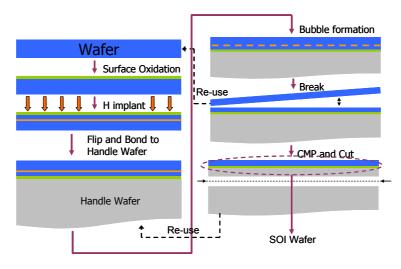

Unlike the wafer bonding method, in UNIBOND, the etch-back process is avoided. The Smart-Cut mechanism uses the deep implantation of hydrogen (*Figure I.2*) to generate microcavities [2]. After bonding and annealing, the wafers separate naturally at a depth defined by the location of hydrogen microcavities. The UNIBOND wafer is finished by CMP<sup>4</sup>. The smart-cut approach has several advantages:

- No etch-back step, with much better uniformity of surface (0.15nm).

- The prime-quality wafer is fully recyclable and UNIBOND reduces to a single wafer process, only conventional equipment is needed for mass production.

- Unlimited combinations of BOX and film thicknesses can be achieved in order to match most device configurations (ultra-thin CMOS or thick-film power transistors and sensors).

The following figure presents the Smart Cut process [2]:

Figure I.2. Smart Cut process

UNIBOND wafers using Smart Cut process are currently used for the CMOS SOI 65nm process.

<sup>&</sup>lt;sup>3</sup> BOX : Buried Oxide

<sup>&</sup>lt;sup>4</sup> Chemical Mechanical Polishing

# I.2. MOSFET transistor on bulk and SOI

The implementation of SOI technology is one of several manufacturing strategies employed to allow the continued miniaturization of microelectronic devices, commonly referred to the Moore's Law.

Figure I.3. MOS transistors ITRS roadmap

As CMOS devices scale down a lot of issues appear:

- As L is reduced, drain-to-channel capacitance increases.

- Therefore, gate-to-channel capacitance must also be raised, that is oxide must be thinner.

- Also V<sub>TH</sub> needs to be reduced along with V<sub>DD</sub>.

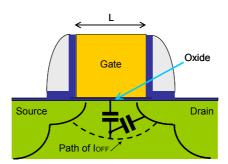

Figure I.4. Schematic cross section of a MOS transistor

Those issues imply new challenges:

- SiO<sub>2</sub> is too leaky bellow 1.2nm

- A thin oxide cannot control a current path far from the gate

The performances of bulk devices and circuits will not be able to follow the Moore's Law owing to the complexity of problems to be solved. But, as it has been shown, the use of SOI can help to increase the performances in term of figure of merit ( $f_T$  and  $f_{max}$ ) [3], [20], [23] and [24]. SOI technology has been demonstrated to be an alternative technology to

mainstream bulk silicon for the realization of high-speed, low-power digital [4] and analog CMOS circuits [5], as well as niche applications such as antenna switches [19], [30], [31], extreme high temperature [6] or radiation conditions.

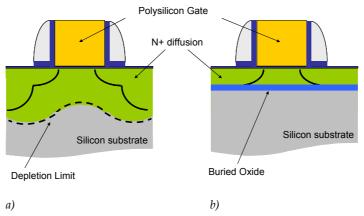

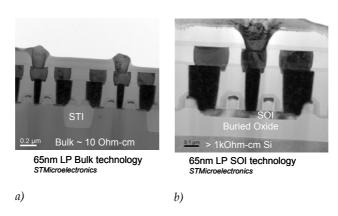

### I.2.1. Comparison between bulk and SOI MOSFET

The main differences between bulk and SOI transistors are:

- Bulk MOSFETs are built at the top of the surface of a monocristalline silicon wafer (*Figure I.5 a*)

- In SOI, the top active silicon region is separated from the under-laying mechanical substrate by a thick insulator layer called buried oxide (*Figure I.5 b*)

- The SOI mechanical substrate may as well be high resistivity or low resistivity.

Figure I.5. Cross section of bulk (a) and SOI MOSFET (b)

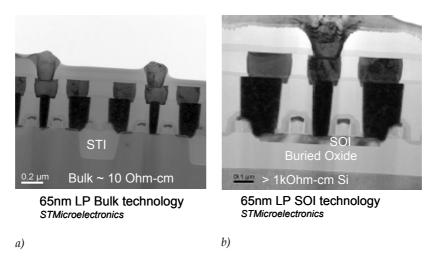

The following cross section structure illustrates how in SOI technology the buried oxide insulates the active silicon area with respect to the substrate:

Figure I.6. Cross section photograph of bulk (a) and SOI MOSFET (b) of the 65nm LP technology

#### I.2.1.a. Benefits of the SOI technology

Concerning the active devices, reported benefits of SOI technology relative to conventional silicon (bulk CMOS) processes include lower parasitic capacitances, no latch-up in small devices, a short channel effects reduction, a better inverse subthreshold slope and a better density integration.

#### I.2.1.a.i Lower parasitic capacitances

Due to isolation from the bulk silicon, smaller parasitic capacitances are observed in SOI, in this way the power consumption is improved for a given performance. In bulk devices, doping level in submicron technologies increases the parasitic source and drain to substrate capacitances. In SOI, capacitance between junctions is fixed by the thickness of the BOX. Since the relative permittivity of the oxide (~4.5) is smaller than the silicon one (~11.7) the junction capacitance in SOI is always smaller than in bulk.

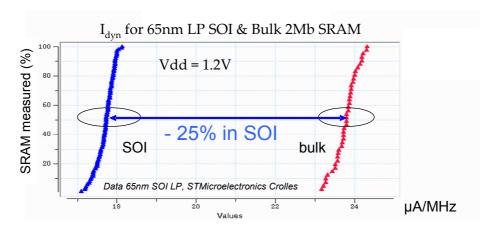

Figure I.7. Dynamic power consumption in CMOS 65nm SOI and bulk at same frequency

For digital devices, thanks to parasitic capacitances reduction, SOI offers 25% less dynamic power than bulk for the same operating frequency (cf. Figure I.7) and 40% higher maximum speed with respect to a bulk implementation, at constant power consumption [10].

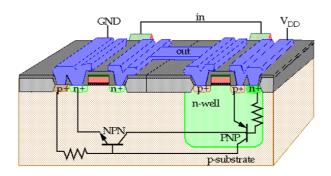

#### I.2.1.a.ii No latch-up effect

Another benefit reported in SOI is the resistance to latch-up due to complete isolation of the N- and P- well structures. This parasitic effect consists in the activation of the PNPN structure formed by two parasitic bipolar transistors (NPN and PNP) which are in the bulk structure. In a CMOS inverter this effect can short circuit  $V_{dd}$  and GND. This can result in a self-destruction or a malfunction of a circuit. The *Figure 1.8* illustrates the parasitic bipolar transistors formed between N and P MOS transistors [12].

Figure I.8. Parasitic bipolar transistors formed between n and p MOS transistors

#### I.2.1.a.iii Short channel effect reduction

A MOSFET device is considered to be short when the channel length is in the same order of magnitude as the depletion-layer widths of the source and drain junction. As the channel length is reduced to increase both the operation speed and the number of components per chip, the short-channel effects arise. The short channel effects are associated to the loss of control of the channel by the gate. In the case of Fully Depleted<sup>5</sup> SOI MOSFET, the space charge in the thin silicon film is well controlled by the gate. Thus, the short channel effects are reduced in comparison with bulk MOSFET.

#### I.2.1.a.iv Inverse subthreshold slope

In FD SOI MOSFET the  $I_d$ - $V_G$  characteristics exhibit a small subthreshold swing close to the ideal value of 60mV/decade [13]. This is because, thanks to the thin SOI layer and the thick buried oxide, the depletion capacitance in the channel region is too small to affect the surface potential. This allows the threshold voltage to be reduced without any increase in the leakage current, thereby making operation at ultra low voltage possible.

#### I.2.1.a.v Integration density and power consumption

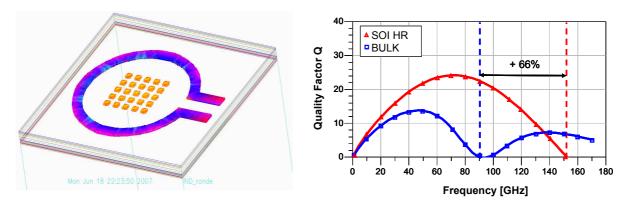

Since SOI MOSFET do not have a well or a fourth body terminal<sup>6</sup>, as bulk devices do, the isolation for n- and p- MOSFETs is smaller and the layout occupies about 30% less area than that of bulk devices. The small layout area implies a small output load capacitance, which helps to maintain the current drivability at ultra low supply voltages. This means that the threshold voltage does not have to be reduced excessively, which helps suppress the leakage current. The density integration is also improved in RF design, especially for inductor (*Chapter III.1.4.a*). Inductors made with HR<sup>7</sup> SOI occupy 40 % lower area for a given Q factor in comparison with bulk ones [32].

<sup>&</sup>lt;sup>5</sup> FD in literature

<sup>&</sup>lt;sup>6</sup> Except for body contacted SOI MOSFET

<sup>&</sup>lt;sup>7</sup> High Resistivity substrate

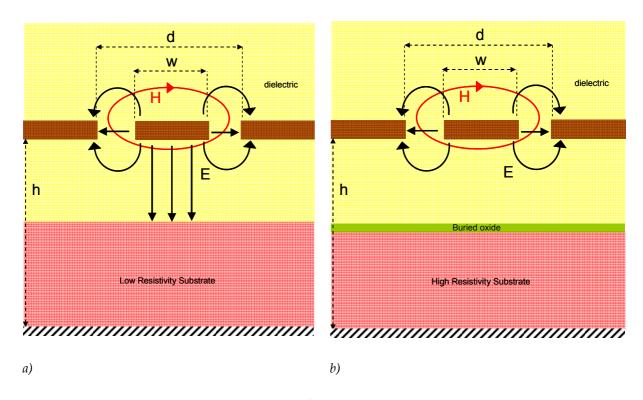

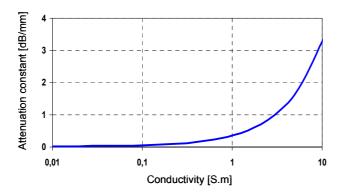

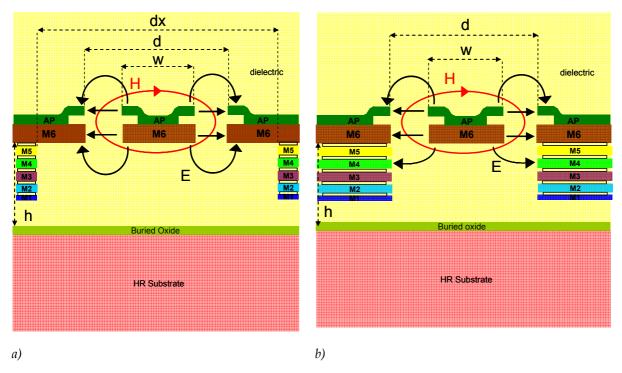

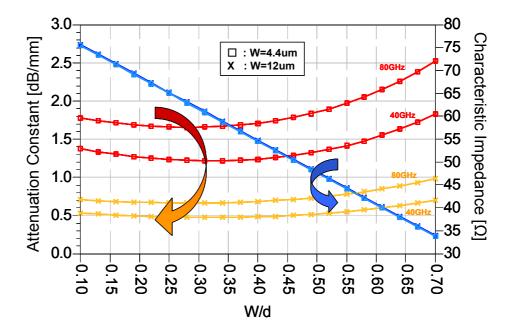

#### I.2.1.a.vi High resistivity substrate compatibility

Classical bulk CMOS wafer substrate resistivity has typically spanned from 5 mohm-cm on heavily doped epi substrates to 30 ohm-cm on polished wafers. Heavily doped substrates are necessary to prevent against latch-up. SOI technology offers a natural protection against latch-up (*I.2.1.a.ii*), thus it becomes possible to use high resistivity substrates. This type of substrate offers new possibilities for wireless technologies:

- Reduced substrate coupling [27]

- Digital & Analog/RF on the same die (suppress digital noise coming from substrate)

- o Multi-standards: RF diversity

- High quality factor inductances (more than 50% increasing have been observed)

[7], [32]

- Higher density metal to metal capacitors by using all metal layers with reduced substrate losses [10]

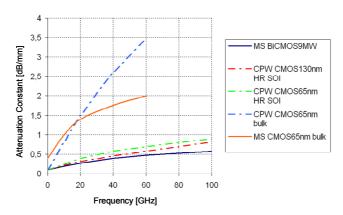

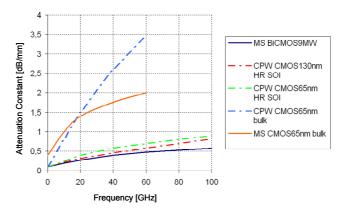

- Low attenuation constant transmission lines at RF and millimeter frequencies [18], [34] and [33].

# I.3. Properties and Behavior of SOI MOSFET

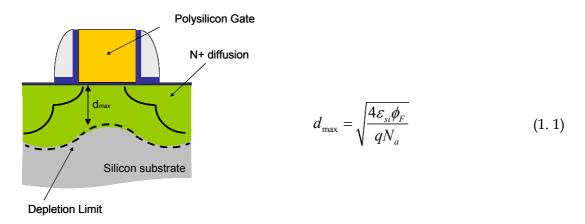

In a MOSFET transistor channel (*Figure 1.9*), the maximum depth of the depletion zone can be expressed by the following equation [3]:

Figure I.9. Cross section of a MOSFET

Where  $\phi_F$  and  $\varepsilon_{si}$  are the Fermi potential and the permittivity of the silicon, q is the charge of the electron, and  $N_a$  is the density of acceptor atoms.

# I.3.1. Comparison and properties of Fully and Partially Depleted SOI MOSFET

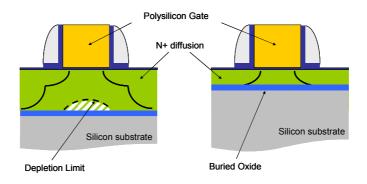

When the depletion limit extends over the entire thickness of the active film of silicon, the MOSFET is said to be fully depleted (FD). If a part of the silicon film is not depleted, the MOSFET is called partially depleted (PD). The following figure illustrates these two different structures:

Figure I.10. Partially (left) and Fully (right) Depleted MOSFET

To facilitate the distinction between PD and FD MOSFET, an ' $\alpha$ ' coefficient is introduced [14]. This coefficient is a function of the total gate capacitance  $C_{ox1}$ , the capacitance of the silicon film and the buried oxide capacitance. The values of ' $\alpha$ ' are given by the following equations for FD and PD MOSFET:

Where  $C_{OX1}$  and  $C_{OX2}$  are the gate and buried oxide capacitance,  $C_{depl}$  and  $C_{si}$  are the capacitances related to the depletion zone of the PD and the thin film silicon. The ' $\alpha$ ' coefficient measures the efficiency of the coupling between the gate potential and the MOSFET channel potential ( $\Phi_s$ ) at the Si-SiO<sub>2</sub> interface. The best coupling is achieved for a small alpha. Typically, for FD MOSFET alpha is close to zero and around 0.3-0.5 for PD and bulk MOSFET. Nevertheless, the value of alpha is increased for small devices, exhibiting the loss of gate control for the channel potential ( $\Phi_s$ ).

Using the classical space charge assumption, it is possible to develop the expression for the saturation current of the long channel SOI MOSFET:

$$I_D = \frac{W}{L} \cdot \frac{\mu C_{OX1}}{2(1+\alpha)} \cdot \left(V_{gs} - V_{th}\right)^2 \tag{1.4}$$

With W and L the width and the length of the transistor,  $\mu$  is the mobility,  $V_{gs}$  is the gate to source voltage, and  $V_{th}$  is the threshold voltage. From (1. 4) the transconductance is:

$$gm = \frac{\partial I_D}{\partial V_{gs}} = \frac{W}{L} \cdot \frac{\mu C_{OX1}}{(1+\alpha)} \cdot \left(V_{gs} - V_{th}\right) = \sqrt{2 \cdot I_D \cdot \frac{W}{L} \cdot \frac{\mu C_{OX1}}{1+\alpha}}$$

(1.5)

From these ideal equations and the equations (1. 2)(1. 3), it can be deduced that for a technology node, the FD MOSFET has a better transconductance and current drive than the PD or bulk MOSFET. This, because the alpha coefficient is smaller in the case of FD SOI. Nevertheless, the very fine silicon film thickness required in FD MOSFET is hard to process.

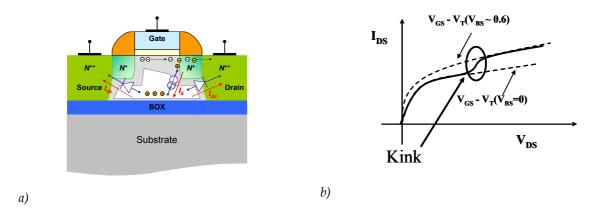

### I.3.2. Floating Body effects

In Partially Depleted MOSFET, silicon film thickness is larger than the depletion depth (1. 1). So there exists a piece of neutral silicon beneath the front depletion region. If this neutral piece of silicon, called "body", is connected to ground by a "body contact", the characteristics of the device is exactly same as the bulk device. But if this body is left electrically floating, the device will basically behave as a bulk device, but with the notable exception of two parasitic effects, the first one is kink effect or floating body effect, and second on is the presence of parasitic open based NPN bipolar transistor between source and drain.

#### I.3.2.a. The kink effect

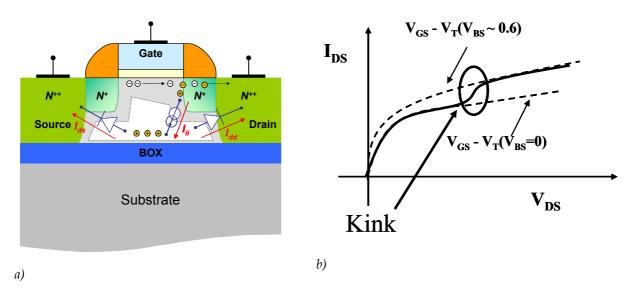

The kink effect is illustrated in the following figure:

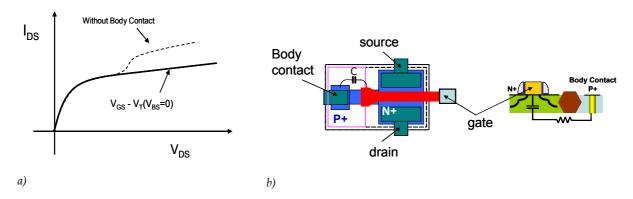

Figure I.11. kink mechanism illustration (a), I<sub>DS</sub>-V<sub>DS</sub> output characteristic of a PD MOSFET (b)

The kink effect mechanism can be explained as follows. For a NMOS transistor, when the drain potential is raised, the channel electrons can acquire sufficient energy in the high electric field zone near the drain to create electron-hole pairs. The generated electrons move into the channel while the holes migrate to the lowest potential, which is the floating body. When the current is reached (i.e. the level of holes is high enough), the diode between the floating body and the source becomes forward biased. The body potential increases. The effective threshold voltage of the MOSFET is reduced, as the potential of the body increases, inducing a higher current and conductance.

\_

<sup>&</sup>lt;sup>8</sup> Body Contacted MOSFET: BC in the literature

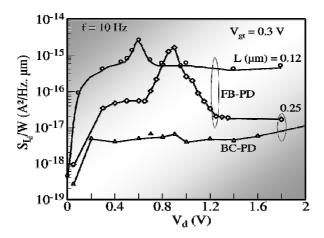

Kink effect also impacts the low frequency noise (1/f) [7]. The following figures illustrate this behaviour:

Data from STMicroelectronics CMOS SOI LP 0.13µm & 0.25µm

Figure I.12. Low frequency noise measurements of a PD MOSFET

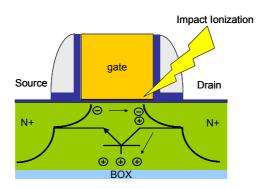

#### I.3.2.b. Parasitic open based NPN bipolar effect in FD SOI MOSFET

This effect occurs when the source, body, and drain of MOSFETs act as the emitter, base, and collector of parasitic transistor in which the base current consists of majority carriers produced by ionization [17]. The following figure illustrates this effect:

Figure I.13. Illustration of the bipolar effect

Since the body region is more depleted in FD than in PD SOI devices, the emitter injection efficiency for the parasitic bipolar transistor is higher, which makes these effects more likely to occur. When they do occur, they have a number of consequences, such as a reduction in the breakdown voltage between the source and the drain, abnormally steep subthreshold characteristics beyond the theoretical limit, a larger off current, and a smaller threshold voltage.

## I.3.3. Which SOI Device for which design?

In order to take advantages of the SOI devices in circuit performances, SOI MOSFET must be chosen taking into account some design considerations. First of all, let's have a look at the advantages and drawbacks of PD and FD MOSFET for a circuit design point of view:

#### Partially Depleted (PD) MOSFET (silicon thickness under the gate t<sub>si</sub>: >60nm):

|   | Benefits                                               |   | Drawbacks                     |  |

|---|--------------------------------------------------------|---|-------------------------------|--|

| ٠ | Reduced parasitic capacitances                         | • | Self-Heating compared to bulk |  |

| • | Possibility to leave transistor's body floating        |   | History effect [9], [8]       |  |

| • | Direct & easy derivability from CMOS bulk process flow |   |                               |  |

| ٥ | Availability of a body terminal to avoid FB9:          |   |                               |  |

|   | <ul> <li>Fixed body potential</li> </ul>               |   |                               |  |

|   | o Body driven design                                   |   |                               |  |

|   |                                                        |   |                               |  |

Table I.1. Benefits and Drawbacks of the PD SOI MOSFET

#### Fully Depleted (FD) MOSFET (silicon thickness under the gate $t_{si}$ < 50nm):

| Benefits                                                       | Drawbacks                                                                |

|----------------------------------------------------------------|--------------------------------------------------------------------------|

| Higher gm for undoped Si layer     Lower short channel effects | <ul><li>Higher self-heating compared to PD</li><li>Challenges:</li></ul> |

| • Quasi ideal sub-threshold slope (60 mV/dec.)                 | C                                                                        |

Table I.2. Benefits and Drawbacks of the FD SOI MOSFET

-

<sup>&</sup>lt;sup>9</sup> FB: Floating Body in the literature

Despite the attractive benefits of the FD transistor, from the industry point of view, it appears that PD SOI MOSFET is the best trade-off and ready to use SOI MOSFET in comparison with bulk. However, *Intel* exhibits some results of a 50nm FD SOI transistor demonstrating the benefit of using FD SOI transistor [16]. But, in the same time *STMicroelectronics* and *IBM* which are working on PD technologies, argue that FD transistors do not allow the use of multiple threshold voltages [10], [11]. Actually, higher threshold voltages are obtained by increasing the doping level of the channel (Na). The value of the maximum depletion depth ( $d_{max}$ ) is reduced (1. 1). It is then more difficult to keep the transistor Fully Depleted. Also, PD transistors, unlike FD transistors, allow using the technological solutions already developed for bulk transistors from the same technology node.

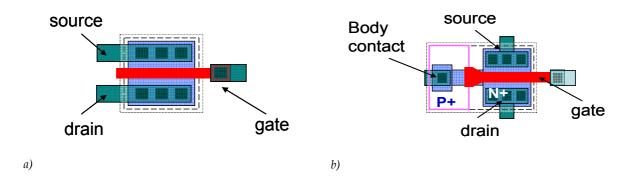

# I.4. FB and BC MOSFET from the CMOS SOI 65nm technology

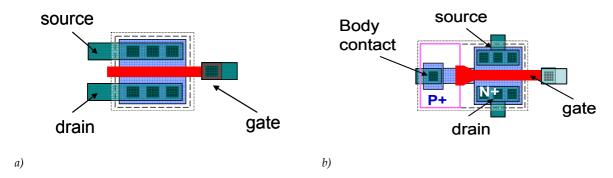

The CMOS SOI 65nm LP technology from *STMicroelectronics* has two SOI MOSFET topologies available. The body contacted and the floating body MOSFET.

Figure I.14. Floating Body a) and Body Contacted MOSFET

The *Figure I.14* illustrates the layout of the FB and BC device. By using a body contact the BC MOSFET does not suffer from the kink effect. Thus the DC characteristics of the device is exactly the same as the bulk device *Figure I.15 - a*). Nevertheless, the body contact added to the device has an impact on the size of the component which is not negligible for high integration circuit. Another drawback of the body contact is the additional capacitance created by the contact *Figure I.15 - b*). This capacitance increases, the drain-source coupling to the gate [19] and thus impacts the high frequency performances [10].

Figure I.15. a) I<sub>DS</sub>-V<sub>DS</sub> BC MOSFET Characteristic; b) illustration of the additional capacitance in the BC MOSFET

### I.4.1. Which PD SOI MOSFET for which design?

As for PD versus FD, the question is open for BC and FB MOSFETs. First of all, it is necessary to estimate which MOSFET figure of merit is targeted in each design. For analog design, the DC gain and the matching between devices (i.e. current variation between two identical devices) are two critical points. Thus, BC MOSFET are preferable since they do not suffer from kink effect and have a higher intrinsic gain [10]. For RF design the choice is more complex:

- If the design needs high gain, low drain-source coupling, low high frequency noise (LNA, MIXER, and SWITCH) the FB MOSFET is preferable [10], [18] and [19].

- If the design is sensitive to low frequency noise, typically a VCO, the BC MOSFET is preferable [7]. In case of high breakdown voltage (PA for instance), BC is also preferable.

## I.5. Summary

We have shown that the SOI technology is already used in the industry. The recent SOI consortium creation demonstrates the wish of numerous companies to develop the SOI technology for the mass market.

Several processes to fabricate SOI wafers were discussed in this chapter and finally both SIMOX and UNIBOND techniques are viewed as industrially scaled process.

We have seen the advantages of SOI-MOSFETs in comparison with bulk are important not only for the digital world but also for analog/RF design. Today, for RF applications, the SOI technology allows lowering the total power consumption in both RF and Digital circuits (key for mobile). SOI permits also an easier co-integration of analog/RF and Digital circuits (lower cost by reduced area).

We have exposed that the comparison between Fully Depleted and Partially Depleted SOI shows that despite the attractive benefits of the FD transistor, the currently manufacturable technology is the PD SOI MOSFET. We have also illustrated that for the cases in which floating-body effects must be completely eliminated, it is possible to form an electrical body contact in PD SOI, but not in FD. There are compelling reasons why the PD device design is preferable; these are summarized in *Table I.1* and *Table I.2*.

In the near future, SOI is one of the most promising solutions for applications at high frequencies (60 GHz WLAN...etc). As we have seen, wireless technologies require high-performance transistors and low-loss passive devices (inductors and capacitors). SOI allows the use of high-resistivity substrate (>3K $\Omega$ -cm), which can result in high Q for the passive elements. High device performance is manifested in SOI MOSFETs having unity current and power gain cut-off frequencies,  $f_T$  and  $f_{MAX}$ , of more than 150 GHz (for the 65nm generation).

## I.6. Bibliography

- [1] www.eetimes.com

- [2] www.soitec.com

- [3] J-P.Colinge, "Silicon-on-Insulator Technology: Materials to VLSI", *Kluwer Academic Publisher*, 1991.

- [4] A.G. Aipperspach et al., "A 0.2 µm 1.8 v soi 550 mhz 64-b powerpc microprocessor with copper interconnects," *IEEE Journal of Solid-State Circuits*, vol. 34, no. 11, pp. 1430–1435, 1999.

- [5] D.Flandre et al., "Fully-depleted soi cmos technology for low-voltage low power mixed digital/analog/microwave circuits," *Analog Integrated Circuits and Signal Processing*, vol. 21, pp. 213–228, 1999.

- [6] B.Rue, D.Flandre, "A SOI CMOS Smart High-Temperature Sensor," *IEEE International SOI Conference*, pp. 111-112, Oct 2007.

- [7] C. Tinella, "Etude des potentialités des technologies CMOS-SOI partiellement désertées pour des applications radiofréquence", Thèse de l'Institut de Microélectronique, d'Electromagnétisme et de Photonique de Grenoble, 2003.

- [8] M.R. Casu, P. Flateresse, "History Effect Characterization in PD-SOI CMOS Gates", *IEEE International SOI Conference*, pp. 63-63, Oct 2002.

- [9] F. Assaderaghi et al., "History Dependence of Non-Fully Depleted (NFD) Digital SOI circuits," *Symposium on VLSI Technology, Digest of Technical Papers*, pp. 122, 1996.

- [10] C.Raynaud, "Advanced SOI Technology for RF Applications," *IEEE International SOI Conference short course*, Oct 2007.

- [11] G. G. Shahidi, "SOI technology for the GHz era", *IBM Journal of Research and Development*, vol. 46, No. 2/3, 2002.

- [12] http://www.csee.umbc.edu

- [13] T. Douseki et al., "Ultralow-voltage MTCMOS/SOI Circuits for Battery-less Mobile System," *IEICE Trans. Electron*, Vol. E87-C, No. 4, pp. 437-447, Apr. 2004.

- [14] M. Dehan, "Characterization and Modeling of SOI RF Integrated components," *Catholic University of Louvain Thesis*, 2003.

- [15] J. R. Brews, "A Charge-Sheet Model of the MOSFET," *Solid States Electronics*, vol.21, pp. 345-355, 1978

- [16] R. Chau et al., "A 50nm depleted-substrate CMOS transistor (DST), " in IEDM Tech. Digest, pp.2911-2914, 2001.

- [17] J. Chen et al., "An Accurate Model of Thin Film SOI MOSFET Breakdown Voltage," *IEDM Tech. Dig.*, pp.671-674, 1991.

- [18] B. Martineau et al., "Millimeter wave design with 65 nm LP SOI HR CMOS technology" *IEEE International SOI Conference*, pp.123-124, Oct 2007.

- [19] C. Tinella et al., "A High-Performance CMOS-SOI Antenna Switch for the 2.5-5 GHz Band," *Journal of Solid State Circuits*, vol.38, No. 7, July 2003.

- [20] S.Lee et al, "SOI CMOS Technology with 360GHz fT NFET, 260 GHz fT PFET, and Record Circuit Performance for Millimeter-Wave Digital and Analog System-on-Chip Applications", Symposium on VLSI Technology Digest of Technical Papers, pp. 54-55, 2007.

- [21] H. Li et al, "Technology Scaling and Device Design for 350 GHz RF Performance in a 45nm Bulk CMOS Process, *Symposium on VLSI Technology Digest of Technical Papers*, pp. 56-57, 2007.

- [22] S. Lee et al, "Record RF Performance of sub-46nm Lgate NFETs in Microprocessor SOI CMOS Technologies", *IEDM Technical Dig.*, Dec. 2005

- [23] JO Plouchart et al, "A 243 GHz fT and 208GHz fmax, 90-nm SOI CMOS SoC Technology With Low Power mmWave Digital and RF Circuit Capability", *IEEE TED*, vol 52, n°7, July 2005

- [24] N. Zamder et al, "A 243 GHz fT and 208 GHz fmax, 90-nm SOI CMOS SoC Technology with Low Power Millimeter-Wave Digital and RF Circuit Capability", *Symposium on VLSI Technology Digest of Technical Papers*, pp. 98-99, 2004.

- [25] F. Gianesello et al, "65nm HR SOI CMOS Technology: emergence of Millimeter-Wave SoC", RFIC Symposium, pp.555-556, June 2007

- [26] F. Gianesello et al, "State of the art 200GHz passive components and circuits integrated in advanced thin SOI CMOS technology on High Resistivity substrate", *IEEE International SOI Conference*, pp.121-122, Oct 2006.

- [27] C. Raynaud et al, "Is SOI CMOS a promising Technology for SOCs in High Frequency range?", *in Proc.* 207th ECS, pp. 331-344, 2005.

- [28] G. Dambrine et al, "What are the limiting parameters of deep-submicron MOSFETs for high frequency applications?", *IEEE TED*, vol 24, n°3, Mar 2003.

- [29] M. Vanmackelberg et al, "90nm SOI-CMOS of 150 GHz fmax and 0.8dB NFmin @6GHz for SOC", *IEEE International SOI Conference*, pp. 153-154, Oct 2002.

- [30] J. Costa et al, "A Silicon RFCMOS SOI Technology for Integrated Cellular/WLAN RF TX Modules", *IEEE IEEE MTT-S*, pp 445-448, June 2007.

- [31] C. Tinella et al, "0.13µm CMOS SOI SP6T antenna switch for multi-standard handsets", Silicon Monolithic Integrated Circuits in RF Systems, Digest of paper, Jan 2006.

- [32] F. Gianesello et al, "Integrated Inductors in HR SOI CMOS Technologies: on the economic advantage of SOI technologies for the integration of RF applications", *IEEE International SOI Conference*, pp. 119-120, Oct 2007.

- [33] F. Gianesello et al, "1.8dB insertion loss 200GHz CPW band pass filter integrated in HR SOI CMOS Technology", *IEEE MTT-S*, pp. 453-456, June 2007.

- [34] B. Martineau et al, "80 GHz Low Noise Amplifiers in 65nm CMOS SOI", in: 33rd European Solid State Circuits Conference ESSCIRC, pp. 348-351, Sept 2007.

- [35] N. Zamder et al, "A 0.13μm SOI CMOS Technology for Low-Power Digital and RF Applications", Symposium on VLSI Technology Digest of Technical Papers, 2001.

- [36] O. Bon et al, "High Voltage Devices added to a 0.13μm High Resistivity Thin SOI CMOS Process for Mixed Analog-RF Circuits", *IEEE Int. SOI Conf.* pp. 171-173, Oct 2005.

# Chapter II

## Actives elements in SOI CMOS 65nm

In comparison to other technologies, CMOS is the most cost-effective solution to date for large scale digital applications and it enables ultra high level system-on-a-chip integration. Driven by high performance digital applications, high frequency performances in silicon technology have considerably increased with geometry scaling. Non digital figure of merits, such as  $f_T$ ,  $f_{max}$  or NF<sub>min</sub> show that silicon transistors become competitive with III-V transistors [1].

This chapter is built as follows. First, transistor RF figures of merit are discussed, then high frequency small signal model of the MOSFET transistor is presented. Next, the noise sources and their modeling in MOSFET transistors are developed. After that, SOI MOSFET characterization is presented and performances of the CMOS SOI and bulk 65nm technologies are compared with the state of the art. Finally, BSIM MOSFET model are detailed.

# II.1. Transistor RF figures of merit

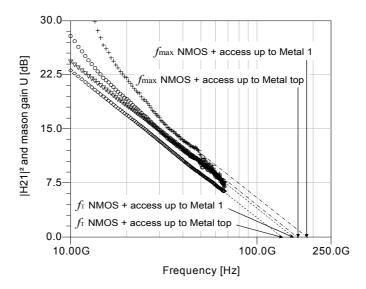

The two most important features of transistor are its ability to amplify (important for analog and RF) and its ability to act as a switch (important for digital electronics and mixers). These two characteristics are evaluated using the gain definition for analog RF and the  $I_{on}/I_{off}$  performances for digital electronics. Today CMOS technologies have to deal with these two important figures of merits. Unilateral gain is used to evaluate the figure of merit  $f_{max}$ . The maximum oscillation frequency is the frequency at which the unilateral power gain is equal to 1. The current gain is used to evaluate the figure of merit  $f_T$ . The device  $f_T$  is the frequency at which the short circuit current gain falls to unity (0dB). In this work, transistors are evaluated using the maximum stable gain (MSG), the maximum available gain (MAG), the unilateral power gain or Mason gain (U), the current gain (H<sub>21</sub>) and the associated gain (G<sub>ass</sub>) All these gain definitions are given in appendix.

# II.2. High Frequency small signal model of the SOI MOSFET transistor

One of the advantages of SOI transistors compared to bulk devices is that at millimeter wave frequencies, the substrate does not impact significantly the behaviour of transistors. Thanks to the thickness of the buried oxide, the body effect can be neglected at high frequency [2]. Thus, it is not necessary to develop a four terminal model for the SOI floating body transistor used at RF and millimeter wave frequencies.

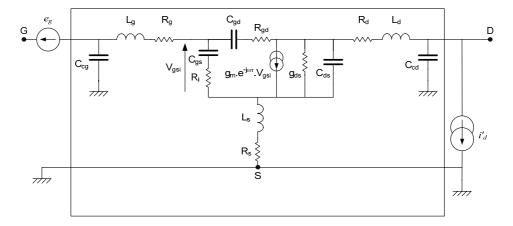

In the next two sections, a general small signal equivalent circuit of floating body SOI MOSFETs is presented, taking into account its intrinsic behavior and its physical structure. The model extraction methodology is not discussed here. The complete description of this methodology is given in [3] and [4]. An example of extracted small signal circuit elements is given in appendix.

#### II.2.1. Quasi static model

Small signal or linear models are used to evaluate the stability, gain, noise and bandwidth of designed circuits. A small-signal model is generated by taking derivatives of the current-voltage curves at biasing point. As long as the signal is small relative to the nonlinearity of the device, the derivatives do not vary significantly, and can be treated as standard linear circuit elements. A big advantage of small signal models is they can be solved directly, while large signal nonlinear models are generally solved iteratively, with possible numeric convergence or stability issues.

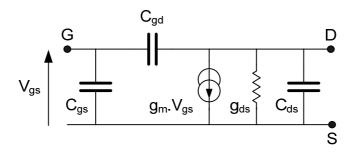

Figure II.1 Intrinsic quasi static small signal model of a (SOI) MOSFET

To get an understanding of the high-frequency properties of a MOSFET and to analyze them, the equivalent circuit should be simplified a lot. Quasi-static behavior of the channel charge is assumed under the hypothesis that the electron channel transit time is negligibly small. The transcapacitances are also neglected. *Figure II.1* described the intrinsic quasi static

model of the MOSFET. The bulk or substrate node has been neglected as explain previously (not necessary in SOI) as well as the  $g_{mbs}$ ,  $C_{gb}$  and  $R_B$  components. The transistor geometry affects each device terminals by capacitive coupling and can be modeled by capacitances added in the equivalent circuit as shown in *Figure II.1*. All these components are bias dependent and are related to variations of charges or currents when a small signal is applied around equilibrium on a terminal. The capacitances between the source, drain and gate are defined as follows:

$$C_{gd} = -\frac{\partial q_g}{\partial v_d}\Big|_{v_s = v_g = 0}$$

$$C_{gs} = -\frac{\partial q_g}{\partial v_s}\Big|_{v_d = v_g = 0}$$

$$C_{ds} = -\frac{\partial q_d}{\partial v_s}\Big|_{v_d = v_g = 0}$$

(2.1)

These relations can be used only in quasi-static operation. The applied small signal is varying slowly enough such as the charges respond instantaneously to the applied signal. The capacitances are the representations of the influence on the charges of a voltage applied on a terminal, with regards to the MOSFET physic. They are called intrinsic capacitances. Moreover, MOSFETs are imperfect current sources, thus an output conductance must be added in the model. It is defined by:

$$g_{ds} = \frac{\partial i_{ds}}{\partial v_{ds}}\bigg|_{v_s = v_g = 0} \tag{2.2}$$

### II.2.2. Non quasi static model

In the previous section, a MOSFET equivalent circuit has been presented, considering that charges respond without delay to the applied signal. But when the frequency increases, the charges are not able to follow the signal instantaneously. According to Tsividis, the frequency upper limit of the quasi-static model is proportional to  $1/L^2$ , where L is the channel length of the transistor [5]. To model the non-quasi-static effects, the MOSFET channel can be divided into several small transistors connected together. Then, quasi-static models are used for all sub-transistors. This solution can be used when the values of the intrinsic elements are obtained using formulae from the physical model. If they have to be extracted from measurements, this method cannot be used, because the number of

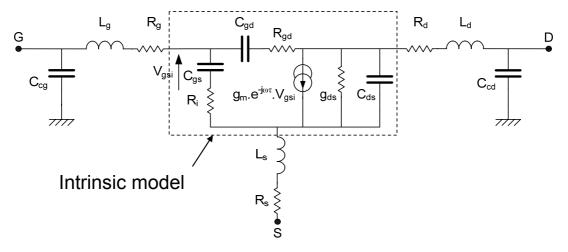

unknowns becomes too high. Instead of dividing the MOSFET into several small transistors, the non-quasi-static effects can be modeled by introducing new elements in the equivalent circuit ( $R_i$ ,  $R_{gd}$  and a time delay ( $\tau$ ) affecting the transconductance) [5]. These elements are represented in *Figure II.2*. The command of the voltage controlled current source is still the potential " $V_{gsi}$ " applied to the intrinsic capacitance  $C_{gs}$ .

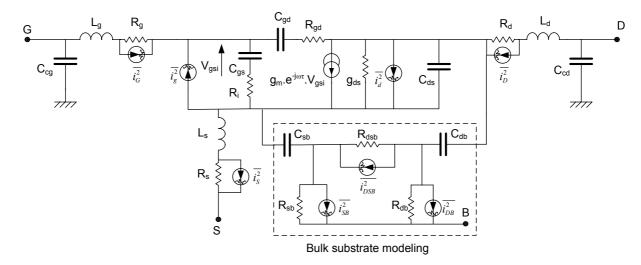

Figure II.2 Non quasi static RF small signal model of the MOSFET including extrinsic parasitic elements.

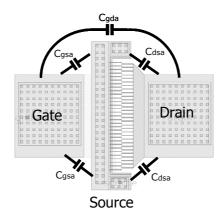

The extrinsic gate to source ( $C_{\rm gse}$ ), gate to drain ( $C_{\rm gde}$ ) and drain to source ( $C_{\rm dse}$ ) capacitances (not shown in schematic) are included into  $C_{\rm gs}$ ,  $C_{\rm gd}$  and  $C_{\rm ds}$ . They come from two different causes:

- C<sub>gse</sub> and C<sub>gde</sub> include overlap capacitances, located between the gate oxide and the source and drain diffusion under the gate. They also include the fringing capacitances from the gate sides to the source and drain implants.

- The capacitance  $C_{dse}$  is completely different from the two other extrinsic capacitances. It is the expression of the coupling between source and drain through the film of silicon, the buried oxide and the substrate.

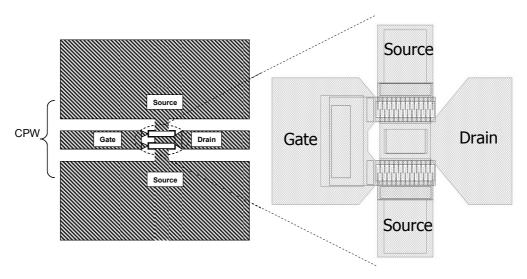

#### II.2.2.a. Extrinsic parasitic access models

The intrinsic gate, source and drain are connected to the Metal one of the BEOL¹ by the gate, source and drain finger contacts (also called CO). These fingers and contacts have a given resistivity. They are distributed elements but since the transistor is generally small compared to the wave length they are modeled by using lumped resistances called  $R_{\rm g}$ ,  $R_{\rm s}$  and  $R_{\rm d}$  connected to the gate, the source, and the drain respectively (*Figure II.2*). The resistances  $R_{\rm d}$  and  $R_{\rm s}$  include the metallic losses and the contact resistances between the metal and the source and drain implants. They are proportional to the inverse of the transistor width. The resistance  $R_{\rm g}$  includes the resistance of the gate fingers, which is proportional to the transistor width, and the resistance of the contacts and metallic lines. In

-

<sup>&</sup>lt;sup>1</sup> Back End Of Line

most of the cases, the resistance of the gate finger is much higher than the others. An equation of  $R_g$  taking into account all these parasitic can be obtain by combining [6] and [17]:

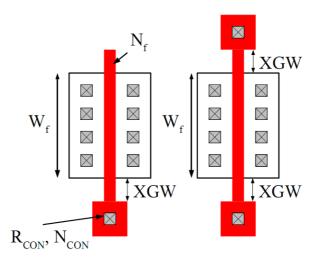

$$R_{g} = \frac{R_{\Box} \cdot W_{f}}{g_{a}^{2} L \cdot 3N_{f}^{2}} + \frac{R_{\Box} XGW}{g_{a}^{2} L \cdot 3N_{f}^{2}} + \frac{R_{cont}}{N_{cont} \cdot N_{f} \cdot g_{a}}$$

(2.3)

With is  $R_{\square}$  is the material sheet resistance,  $N_f$  is the number of fingers,  $g_a$  is the number of gate accesses (1 or 2), XGW the distance between the gate contacts and the active part of the transistor, L and  $W_f$  the length and the width of a unit finger and  $R_{cont}$  and  $N_{cont}$  the contact resistance and the number of contacts respectively.

Figure II.3 Geometrical aspect of the gate resistance with one (left) and two (right) gate accesses

Using the same methodology, parasitic inductances can be defined. They are called  $L_{\rm g}$ ,  $L_{\rm d}$  and  $L_{\rm s}$  in *Figure II.2*. For sub-micron MOSFETs, these inductances are usually a few pico Henry (up to metal one) and are nearly negligible within the frequency band of operation.

Finally the capacitances  $C_{cg}$  and  $C_{cd}$  represent the contact metallic interconnection capacitances from the gate and the drain.

#### II.2.2.b. $f_T$ , $f_{max}$ figures of merit from small signal model

$f_T$ ,  $f_{max}$  figures of merit described in section II.1 can be derived from the elements of the small signal model described in the previous section (*Figure II.2*). A first approximation for  $f_T$  is given by:

$$f_T \approx \frac{g_m}{C_{gs} \sqrt{1 + 2 \cdot \frac{C_{gd}}{C_{gs}}}}$$

(2.4)

A more complete expression of  $f_T$  is then given in [25]:

$$f_{T} \approx \frac{f_{c}}{1 + \frac{C_{gd}}{C_{gs}} \left(1 + \left(R_{s} + R_{d}\right)\left(g_{m} + g_{ds}\right)\right) + \left(R_{s} + R_{d}\right) \cdot g_{ds}}$$

$$with \quad f_{c} = \frac{g_{m}}{2\pi C_{gs}}$$

$$(2.5)$$

The  $f_{max}$  figure of merit is given by:

$$f_{\text{max}} \approx \frac{g_m}{2\pi \cdot C_{gs} \cdot 2\sqrt{\left(R_g + R_s + R_i\right) \cdot \left(g_{ds} + g_m \frac{C_{gd}}{C_{gs}}\right)}}$$

(2. 6)

A more complete expression of  $f_{max}$  has been also defined in [26]:

$$f_{\text{max}} \approx \frac{f_c}{\left(1 + \frac{C_{gd}}{C_{gs}}\right) \cdot \sqrt{4g_{ds}\left(R_g + R_s + R_i\right) + 2 \cdot \frac{C_{gd}}{C_{gs}} \cdot \left(g_m\left(R_s + R_i\right) + \frac{C_{gd}}{C_{gs}}\right)}}$$

(2.7)

Thanks to these expressions, the limiting factors of the MOSFET gain performances can be easily estimated [7].

# II.3. Noise analysis of the MOSFET transistor

Noise is a natural phenomenon that affects every electronic systems. Because noise may mask the desired signal, it is important to understand and minimize its effects on the performance of RF devices. In the following section the noise contribution in MOSFET transistor is investigated. To understand the noise mechanisms, a single MOSFET can be seen as a small circuit as depicted in *Figure II.4*. Thus different noise sources exist in a MOS transistor as shown in *Figure II.4*. They include access resistance thermal noise at the gate  $\overline{i_g^2}$ , access resistance thermal noise at the source  $\overline{i_s^2}$ , thermal noise and the flicker noise in the channel  $\overline{i_d^2}$  [11], [12], induced gate noise  $\overline{i_g^2}$  [9] and for CMOS bulk transistor, the substrate resistance thermal noise  $\overline{i_{SB}^2}$ ,  $\overline{i_{DSB}^2}$ ,  $\overline{i_{DSB}^2}$  [11]. In CMOS SOI body contacted transistors another noise source comes from the resistance of the body contact [13] (not depicted here).

Figure II.4 The different noise sources in a MOSFET transistor (bulk and SOI FB).

Channel resistance and all terminal resistances contribute to the thermal noise at high frequency, but typically channel resistance dominates in the contributions of the thermal noise from the resistances in the device. Induced gate noise is generated by the capacitive coupling of local noise sources within the channel to the gate, and usually it plays a more important role as the operation frequency goes much higher than the frequency at which channel thermal noise dominates.

#### II.3.1. Flicker Noise

In principle, flicker noise also called 1/f noise is a low frequency noise and it mainly affects the low frequency performance of the device, so it can be ignored at very high frequency. However, the contribution of flicker noise should be considered in designing some RF and millimeter wave circuits such as mixers, oscillators, or frequency dividers that up-convert the low-frequency noise to higher frequency. It is the dominant source for phase noise in silicon MOSFET circuits and it sets a lower limit on the level of signal detection. It is one of the factors limiting the achievable dynamic range of CMOS ICs (cf. *Chapter IV*). In this section this noise modeling is not developed but a modeling approach can be found in [5].

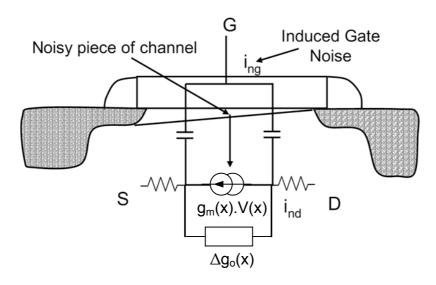

#### II.3.2. Thermal noise

The thermal noise of the MOSFET imposes a fundamental limitation on CMOS LNAs [14]. Based on the fact that the MOSFET is a modulated resistor capacitively coupled to the gate (*Figure II.5*), Van Der Ziel has proposed a thermal noise model for MOSFETs, which consists of drain current noise, induced gate current noise, and their cross-correlation coefficient [9]. This model has been improved by Pucel [15] and Cappy [15] and is called "PRC". The P, R, C coefficients are defined in the following equations:

$$\overline{i_g^2} = 4 \cdot k \cdot T_A \cdot R \cdot \frac{\omega^2 C_{gsi}^2}{g_{mi}} \Delta f \tag{2.8}$$

$$\overline{i_d^2} = 4 \cdot k \cdot T_A \cdot P \cdot g_{mi} \Delta f \tag{2.9}$$

$$\frac{\overline{i_g i_d^*}}{\sqrt{\overline{i_g^2 i_d^2}}} \approx j \frac{\Im(\overline{i_g i_d^*})}{\sqrt{\overline{i_g^2 i_d^2}}} = jC$$

(2. 10)

With  $T_A$  is the ambient temperature, k is the Boltzmann constant and P, R and C are dimensionless coefficients.

Using this model the intrinsic minimum noise factor may be defined as:

$$F_{\min} = 1 + 2\frac{f}{f_c} \sqrt{R.P.(1 - C^2)}$$

$$with \quad f_c = \frac{g_{mi}}{2\pi C_{gsi}}$$

(2. 11)

Figure II.5 Induced gate noise effects in MOSFET devices.

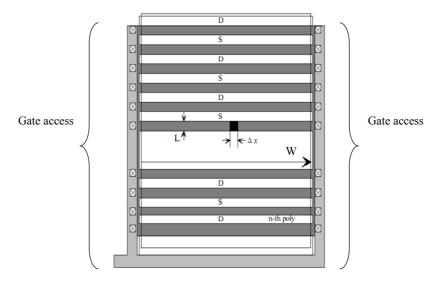

#### II.3.3. Thermal noise from access resistances

In order to fully evaluate the minimum noise factor of a MOSFET, thermal noise coming from the different terminal accesses of the device must be taken into account (Figure II.4). Contrary to the thermal noise and the induced gate noise, these noises are not depending on the applied voltage. Among these sources the poly gate resistance  $R_G$  is the main noise contributor.

Figure II.6 The finger structure of a MOS transistor.

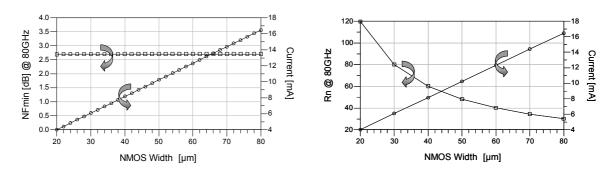

Taking into account the distributed aspect of this resistance (*Figure II.6*) the equivalent lumped resistance can be express using (2. 3). There is an optimum finger size that minimizes the NF<sub>min</sub> (*Chapter IV*). At first order, the smallest finger would be the best since the R<sub>G</sub> value is reduced. But for small finger size ( $<1\mu m$  in the CMOS 65nm technology) the fringing capacitance coming from the contacts become preponderant over the other capacitances reducing  $f_T$  and  $f_{max}$  and the minimum noise is not improved [19].

An expression taking into account the access resistances  $R_G$  and  $R_D$  and the extrinsic capacitances  $C_{gse}$  (gate-source capacitance) and  $C_{gde}$  (drain-source capacitance) has been given by Danneville [20]:

$$F_{\min} \approx 1 + 2\frac{f}{f_c} \left(\frac{C_{gd}}{C_{gs}}\right) \sqrt{PR + P(R_G + R_S)g_m}$$

(2. 12)

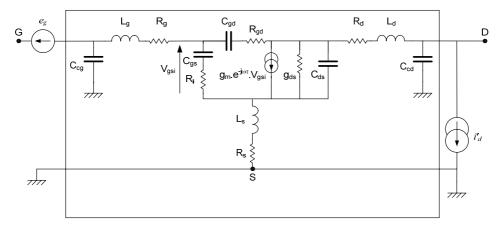

## II.4. Noise temperatures

In [21], Pospieszalski proposed an alternative high frequency noise model. This model dissociates the noise on the gate from the noise on the drain. In this way, the noisy equivalent circuit includes an input voltage noise source  $e_g$  and an output current source  $i'_d$  as shown *Figure II.7*:

Figure II.7 RF MOSFET small signal model including two uncorrelated noise sources.

The correlation between  $e_g$  and  $i'_d$ ,  $\overline{e_g}i_d^{i^*}$  is assumed to be equal to zero. From these two noise sources Pospieszalski defined two equivalent noise temperatures  $T_g$  and  $T_d$  as:

$$T_g = \frac{\overline{e_g^2}}{4k\Re([H_{11}])\Delta f}$$

(2.13)

$$T_d = \frac{\overline{i_d^2}}{4k\Re([H_{22}])\Delta f}$$

(2. 14)

With [H] the H extrinsic matrix of the quadripole. Even if this model has been developed for MESFET it is well suited for MOSFET devices because the high frequency noise mechanisms are similar [22].

# II.4.1. High Frequency noise measurements and associated models

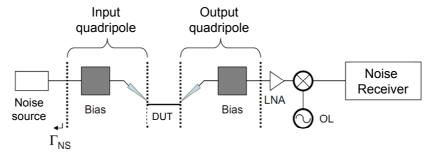

In this work, the noise measurement technique called NF50 (FET Noise characterization under  $50\Omega$  impedance) has been used. An illustration of this technique is given in *Figure II.8*.

Figure II.8 NF50 noise measurement bench

The four noise parameters are obtained from noise figure with a single  $50\Omega$  generator impedance measured versus frequency and the two uncorrelated noise parameters model described in *Figure II.7*. This measurement technique is described by Dambrine in [22]. By

adding two-uncorrelated noise sources, all the MOSFET's noise parameters  $\left(NF_{\min}, R_n, \left|\Gamma_{opt}\right| \text{ and } \arg\left(\Gamma_{opt}\right)\right)$  can be deduced.

## II.5. SOI MOSFET characterization

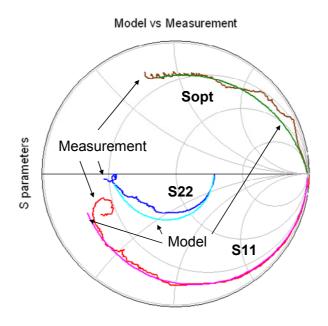

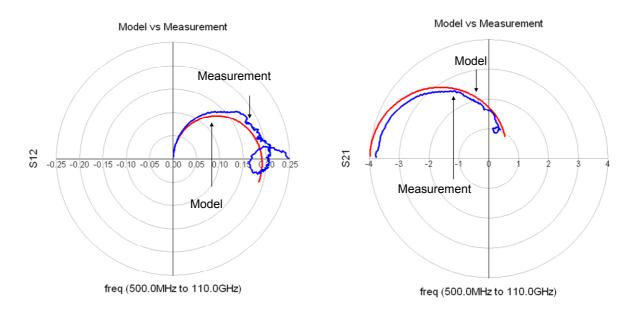

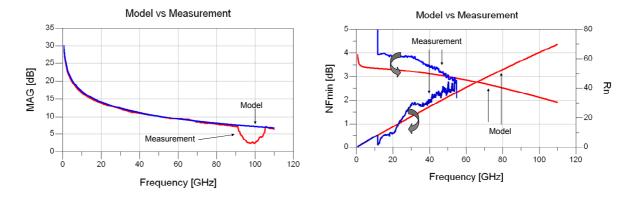

In this section, SOI CMOS n-MOSFET characterization results are presented. These transistors are floating body and body contacted (cf. *Chapter I*). The transistors are processed in STMicroelectronics manufacturing process SOI CMOS065 LP with a MOSFET physical gate length of 60nm. They were measured on wafer and all measurements were performed at a source and load impedance of  $50\Omega$ . S-parameters were measured using a 0-110GHz vectorial network analyzer. The noise figure test bench uses the NF50 method described previously and consists of a noise figure meter, a test set extension and a mixer allowing accurate measurement from 0 to 40GHz.

| Ref device | Lpoly (um) | Wfing um) | Nfing | Ngc | Ncell | Wtot (um) |

|------------|------------|-----------|-------|-----|-------|-----------|

| ZTM12 FB   | 0.06       | 2         | 4     | 2   | 8     | 64        |

| ZTM13 FB   | 0.06       | 1         | 8     | 2   | 8     | 64        |

| ZTS12 BC   | 0.06       | 2         | 4     | 2   | 8     | 64        |

| ZTS13 BC   | 0.06       | 1         | 8     | 2   | 8     | 64        |

Table II.1. Summary of the characterized devices

The *Table II.1* summarizes the measured devices which are NMOS Low Vt, Low Power (GO1), Floating Body (FB) and Body Contacted (BC) transistors. All transistors have a total width of  $64\mu m$  and  $0.06\mu m$  length with double gate access (Ngc=2). The unit finger size are 1 and  $2\mu m$  for both floating body and body contacted transistors.

## II.5.1. DC performances

The measured DC performances are summed up in the *Table II.2*. These results show that the floating body transistors offer a better transconductance  $g_m$ . However the DC gain is ~7% better for the Body Contacted transistor. The threshold voltage is the same for all transistors regardless of the geometry. These results illustrate that the DC gain is at first order not a function of the finger size contrary to the RF performances.

| Ref device    | V <sub>th</sub> (V)       | Gm <sub>max</sub> @   | Ids @                 | <u>Intrinsic</u> @V <sub>gs</sub> =0.8V |                         |        |  |  |

|---------------|---------------------------|-----------------------|-----------------------|-----------------------------------------|-------------------------|--------|--|--|

|               | <b>v</b> iii ( <b>v</b> ) | $V_{\rm gs}$ =0.8 $V$ | $V_{\rm gs}$ =0.8 $V$ | gm                                      | $\mathbf{g}_{	ext{ds}}$ | gm/gds |  |  |

| ZTM12 FB 0.48 |                           | 50.24 (mS)            | 21 (mA)               | 58 (mS) 11 (mS)                         |                         | 5.27   |  |  |

|               | 0.10                      | 785 (mS/mm)           | 328 (mA/mm)           | 906 (mS/mm)                             | 172 (mS/mm)             |        |  |  |

| ZTM13 FB      | 0.48                      | 52.42 (mS)            | 19.8 (mA)             | 60 (mS)                                 | 11 (mS)                 | 5.45   |  |  |

|               |                           | 819 (mS/mm)           | 310 (mA/mm)           | 937 (mS/mm)                             | 172 (S/mm)              |        |  |  |

| ZTS12 BC      | 0.48                      | 36.74 (mS)            | 13.8 (mA)             | 61 (mS)                                 | 11 (mS)                 | 5.55   |  |  |

|               | 0.10                      | 574 (mS/mm)           | 215 (mA/mm)           | 953 (mS/mm)                             | 172 (mS/mm)             | 0.00   |  |  |

| ZTS13 BC      | 0.48                      | 38.91 (mS)            | 14 (mA)               | 65 (mS)                                 | 11 (mS)                 | 5.91   |  |  |

|               |                           | 608 (mS/mm)           | 218 (mA/mm)           | 1016 (mS/mm)                            | 172 (mS/mm)             | 5.71   |  |  |

Table II.2. DC performances of the measured devices

## II.5.2. RF performances

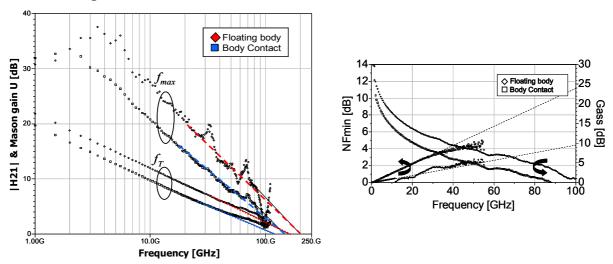

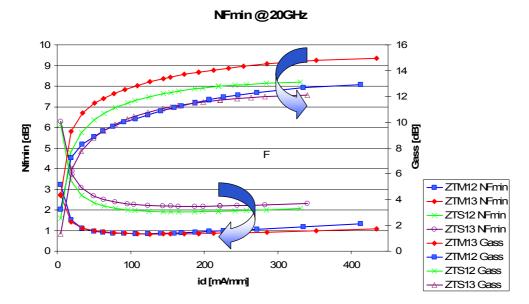

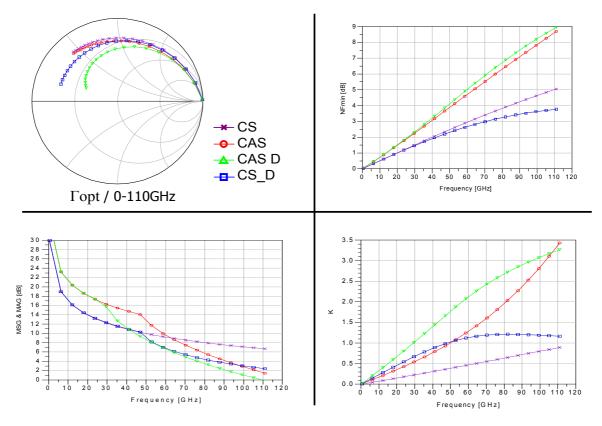

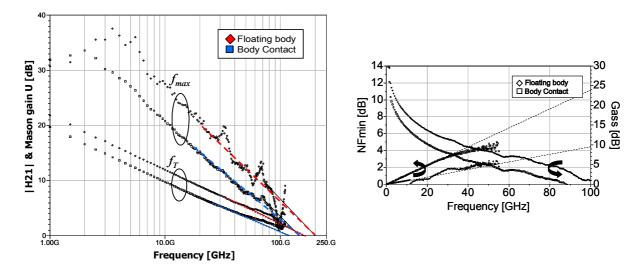

The following figures summarize the RF performances of FB and BC transistors. The Figure II.9 shows performances of the FB and BC transistors of  $64x1x0,06 \mu m^2$ . The  $f_T$  and  $f_{max}$  of the two transistors are 155/200 GHz and 108/126 GHz respectively. The NF<sub>min</sub> and the associated gain analysis shows that for millimeter wave low noise applications the floating body transistor is the more appropriate. It offers 3.5dB minimum noise figure at 80GHz with 5dB associated gain while body contacted transistor does not offer more than 2dB gain with 8.5dB noise figure.

Figure II.9  $f_{T}$ ,  $f_{max}$ ,  $NF_{min}$  and  $G_{ass}$  for a Floating body and a body contacted transistor; n-MOSFET ref ZTM13 & ZTS13 (cf.Table II.1), Vd=1.2V, Id=300mA/mm for  $(f_{T}/f_{max})$  and Id=100mA/mm for  $NF_{min}/G_{ass}$

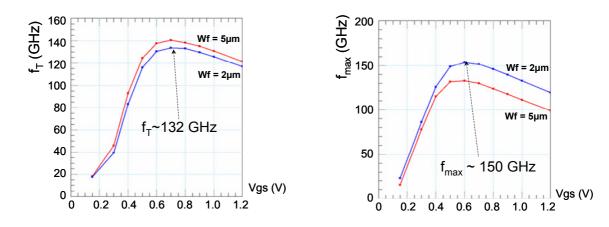

These performances differences come from the parasitic capacitance added by the body contact. Nevertheless, the optimum finger width is different between the floating body and the body contacted devices. When the finger width is over reduced, proportion of added parasitic capacitance is increased decreasing performances [8]. The following figure illustrates this effect:

Figure II.10  $f_T$ ,  $f_{max}$  of two body contacted transistors ;n-MOSFET L=0,063 $\mu m$ , Vd=1.2V [8]

These results show that even if the floating body device is preferred to avoid the parasitic capacitance added by the body contact, high  $f_{max}$  is also possible with body contacted devices by using an optimized layout.

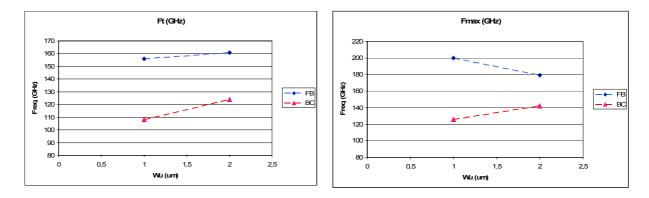

Figure II.11  $f_T$  and  $f_{max}$  trend for measured transistor versus unit finger size (Wu)

The Figure II.11 shows the trend for  $f_T$  and  $f_{max}$  with respect to the unit finger size. This trend is in line with the previous observation. The Figure II.12 summarizes the NF<sub>min</sub> and associated gain performances for the measured transistors. The best performance is achieved for the floating body transistor using unit finger size of 1 $\mu$ m and double gate access. This figure shows also that the optimum current density for noise performances is independent of the size and the type of transistor (BC or FB). The optimum biasing is always achieved for a drain current density of 150mA/mm.

Figure II.12 NF<sub>min</sub> and G<sub>ass</sub> at 20GHz summary for the measured devices

## II.6. CMOS Transistors State of the Art

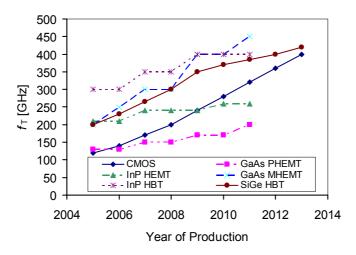

As CMOS technology continues to scale down allowing operation millimeter wave region, it provides the opportunity for low-cost integration of RF/digital/analog functions on the same chip. Today, CMOS performances ( $f_T/f_{max}$ ) are high enough to design circuits from analog to millimeter wave frequencies as shown in *Figure II.13*:

Figure II.13 Roadmap of the  $f_T$  according to the year of production for Silicon and III-V devices (from the 2006 ITRS[1]).

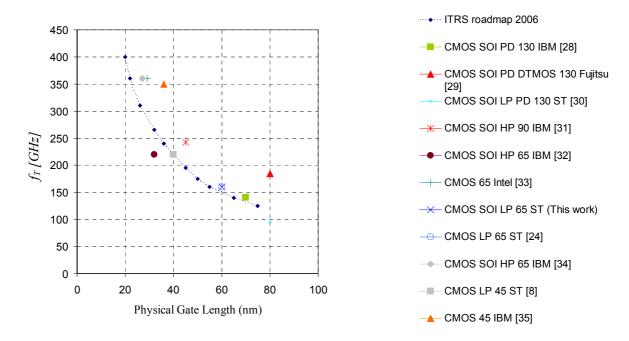

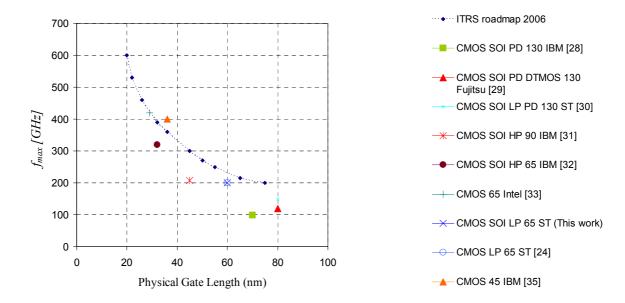

The following two figures give an overview of  $f_T$  and  $f_{max}$  performances according to physical gate length for different NMOS devices (LP and GP):

Figure II.14 f<sub>T</sub> ITRS road-map and several foundries' performances

Figure II.15 f<sub>max</sub> ITRS road-map and several foundries' performances

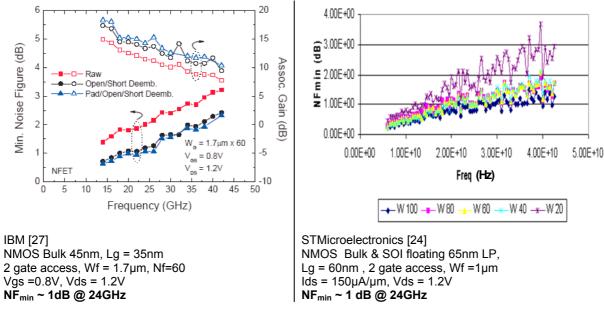

From the above figure it appears that to improve NF<sub>min</sub> as  $f_T$  and  $f_{max}$  the solution would be to reduce the gate length. But the gate length reduction does not always guarantee lower NF<sub>min</sub>. If by scaling down the gate length the gate or source/drain resistance is not reduced, NF<sub>min</sub> does not decrease as expected [8]. The following figure illustrates this phenomenon. The two devices from *IBM* and *STMicroelectronics* have the same NF<sub>min</sub> at 24GHz but a gate length of 35nm and 60nm respectively.

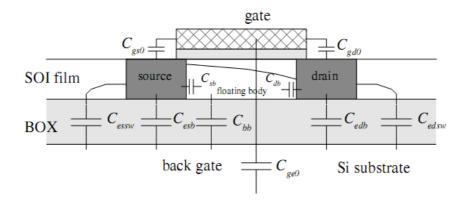

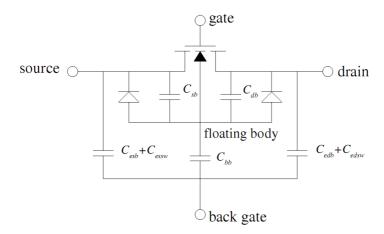

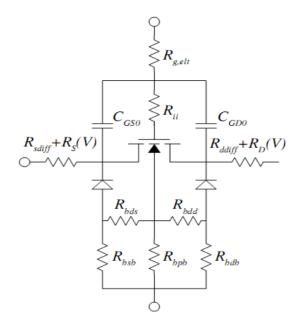

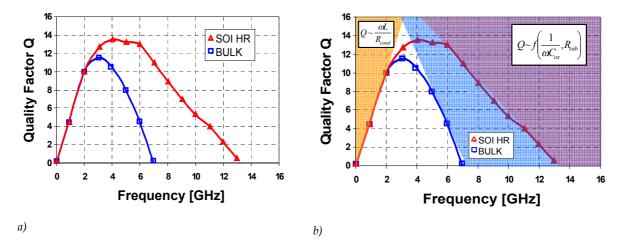

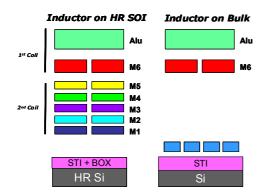

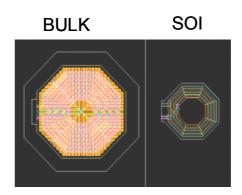

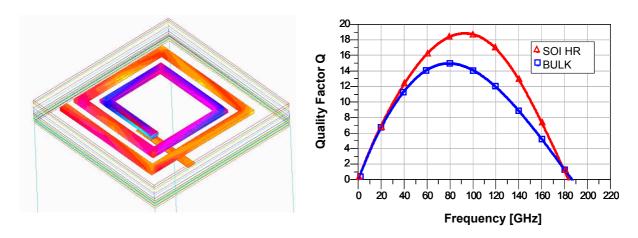

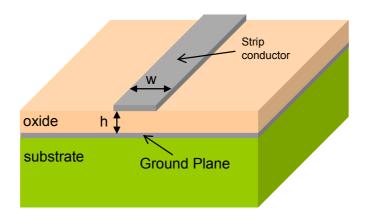

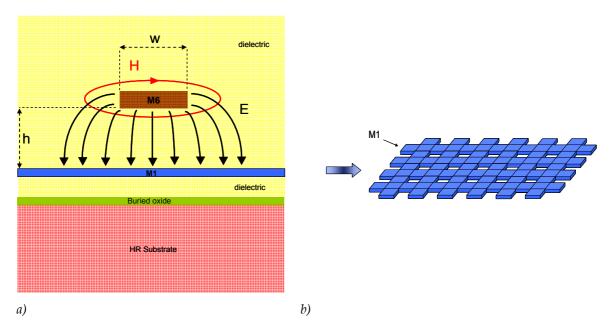

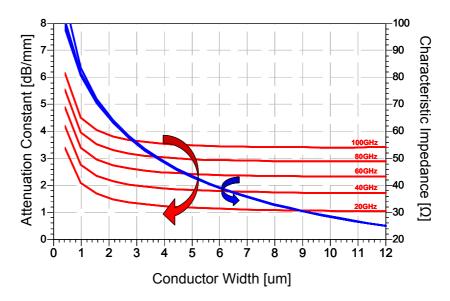

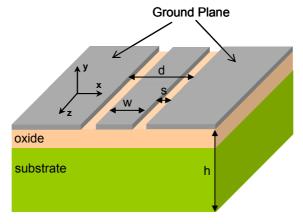

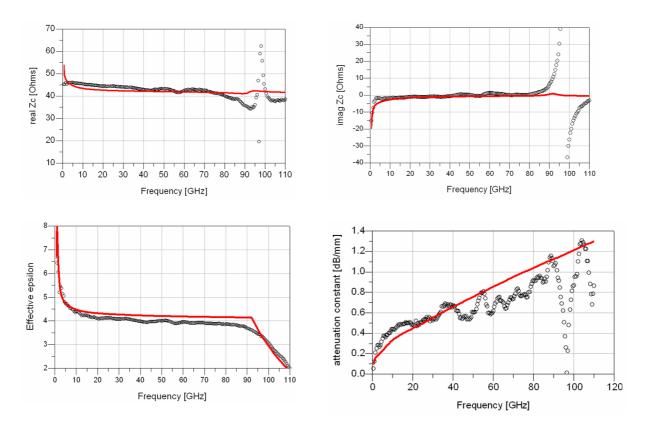

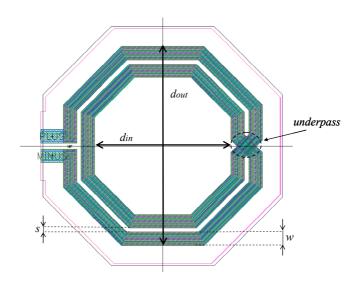

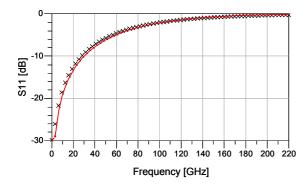

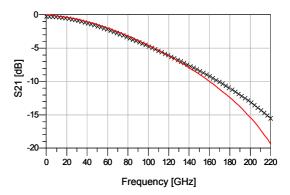

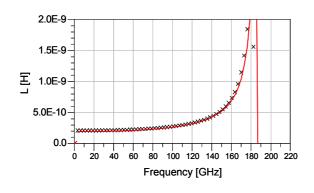

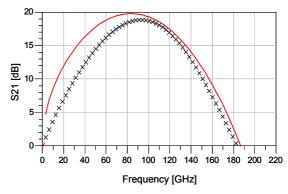

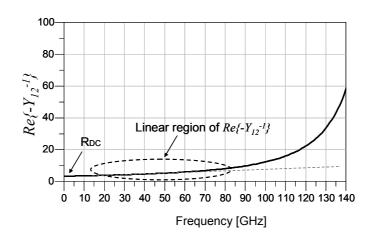

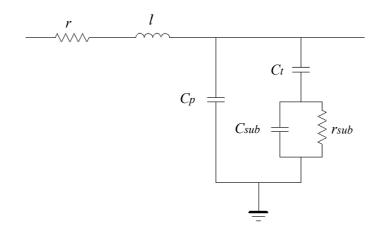

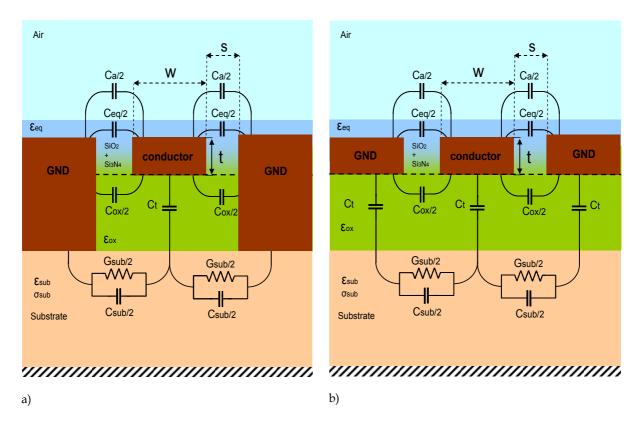

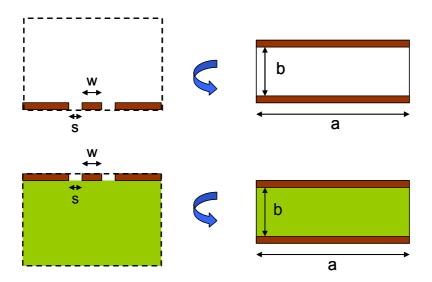

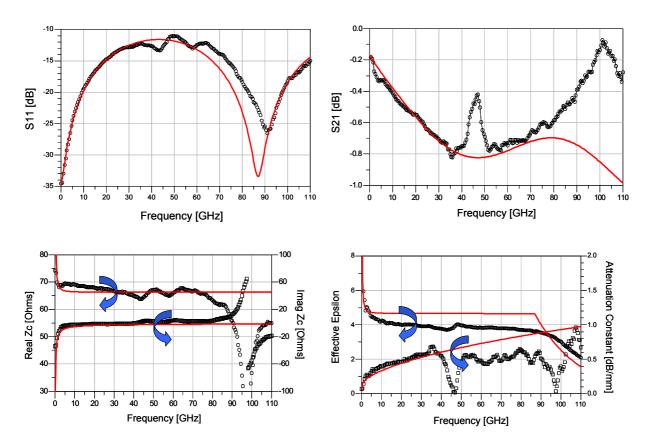

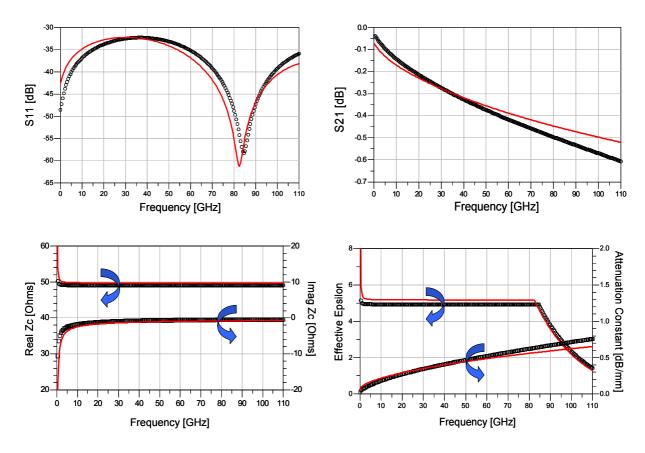

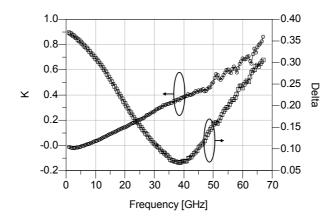

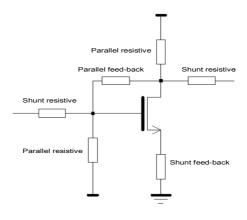

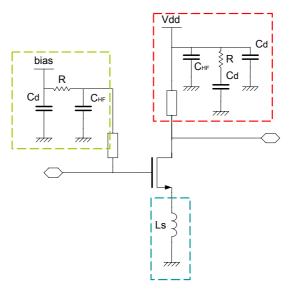

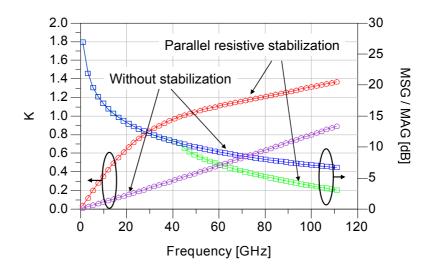

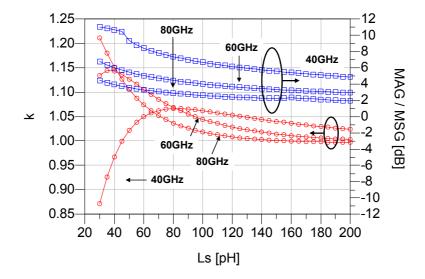

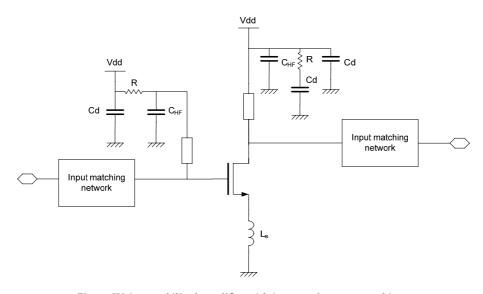

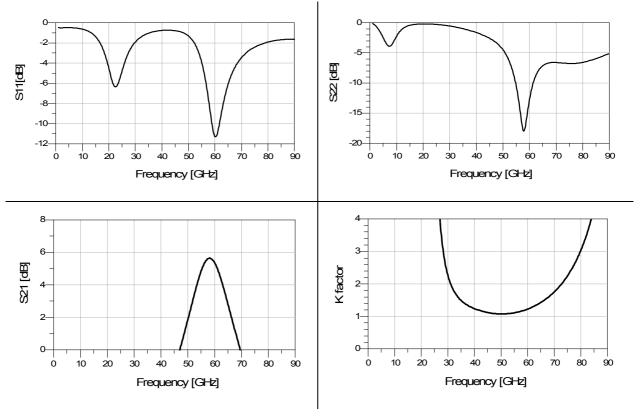

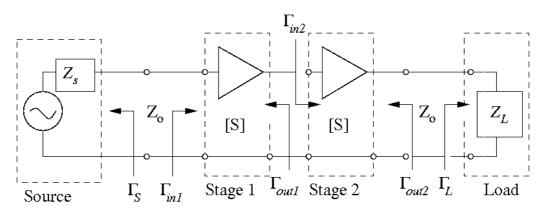

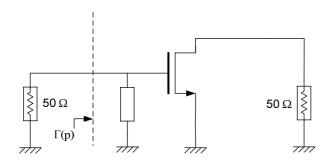

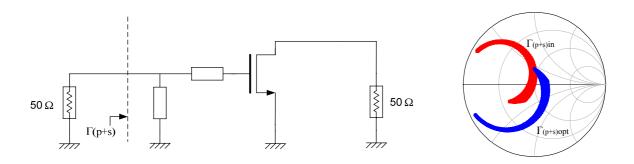

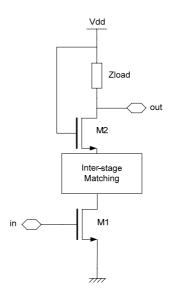

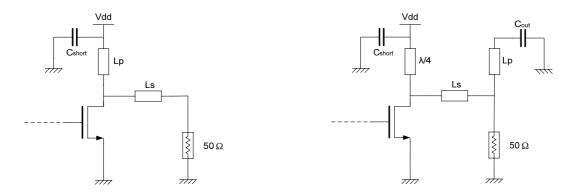

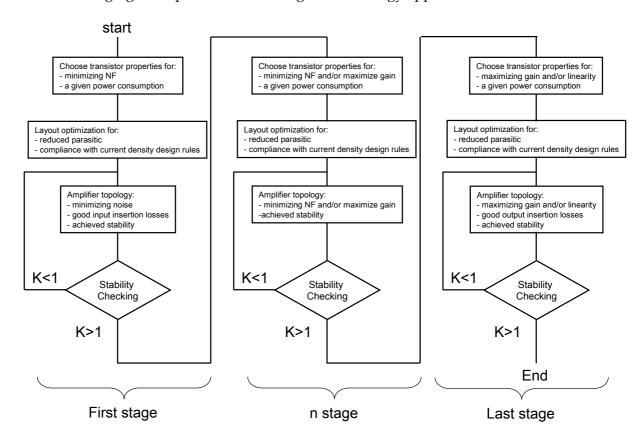

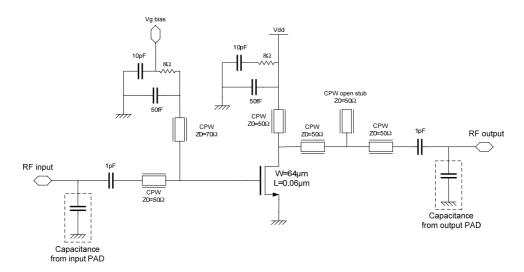

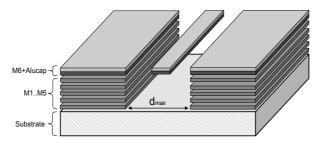

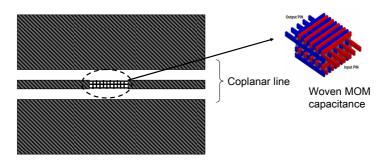

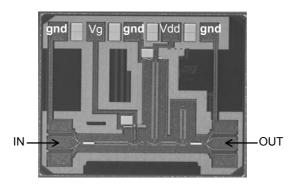

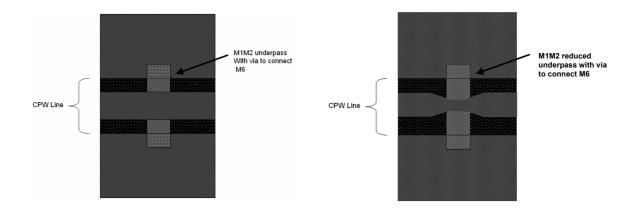

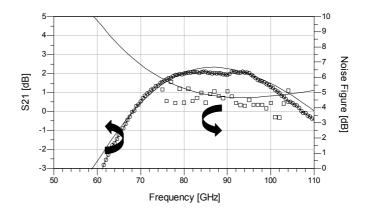

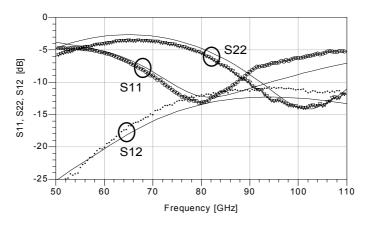

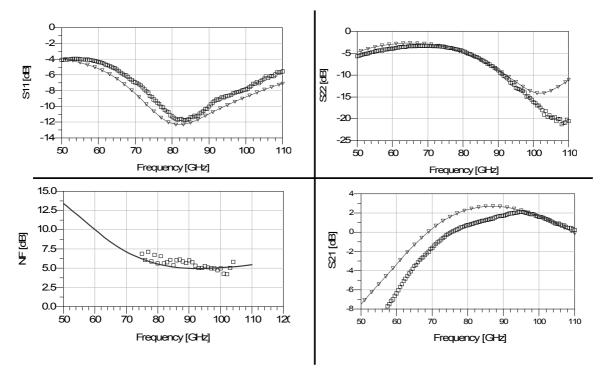

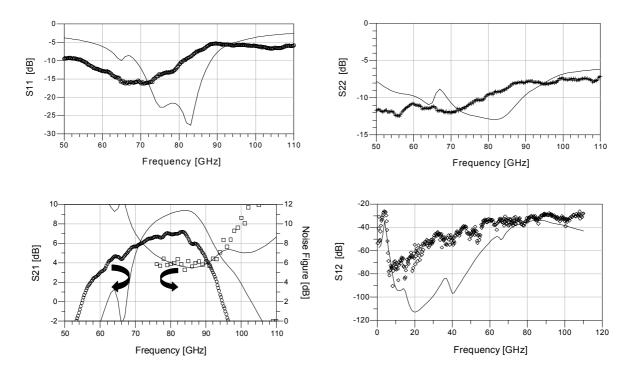

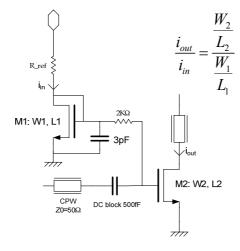

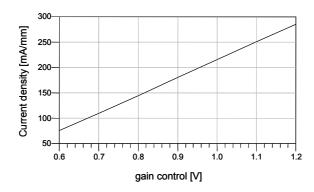

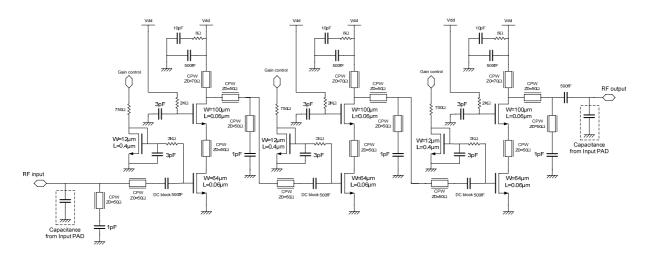

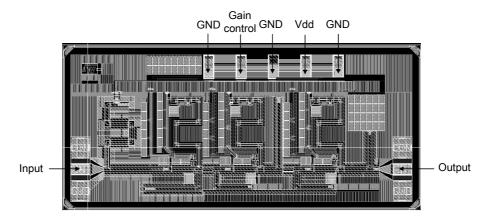

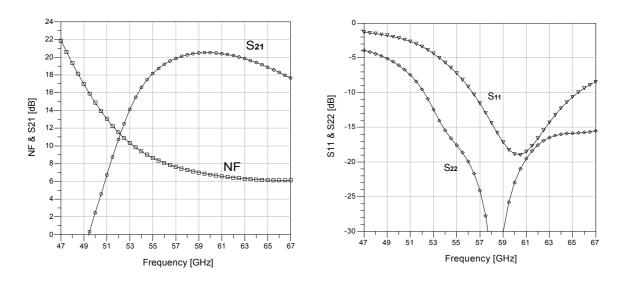

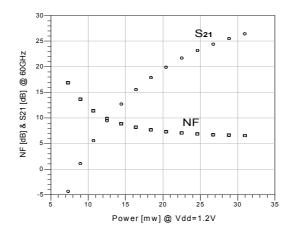

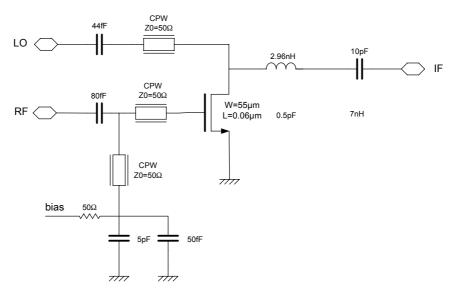

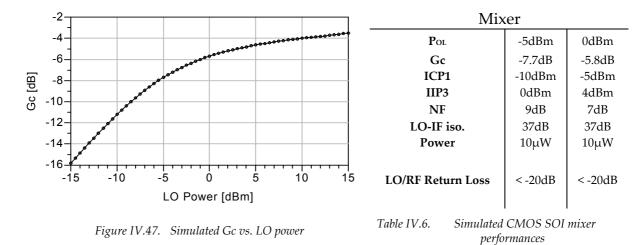

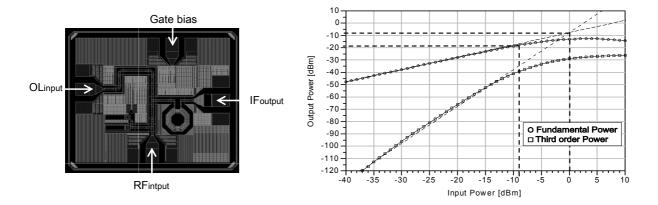

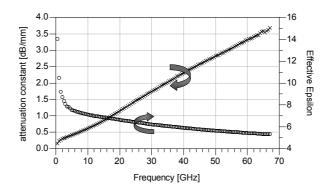

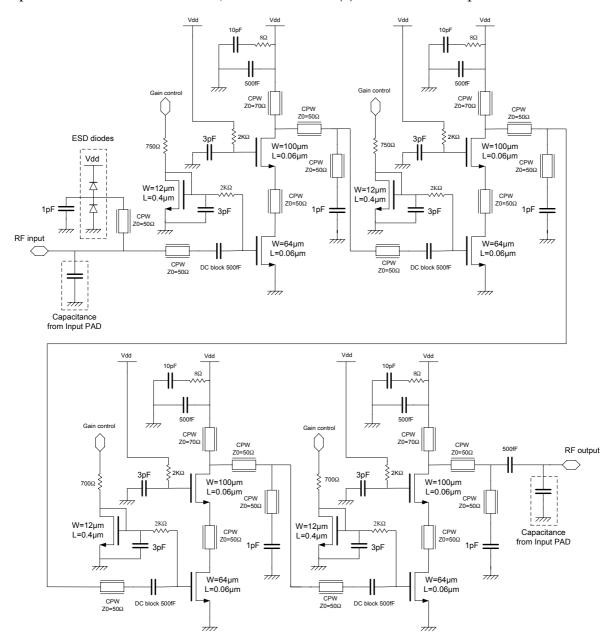

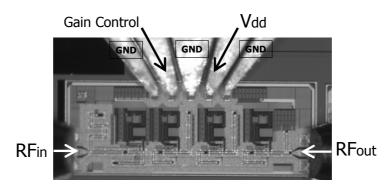

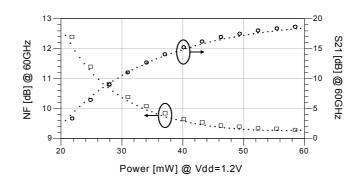

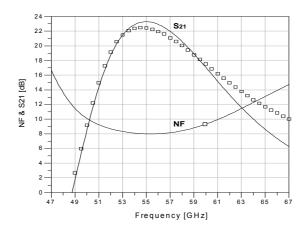

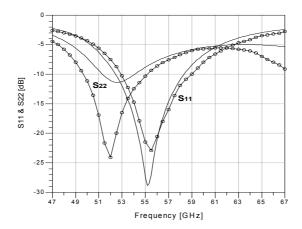

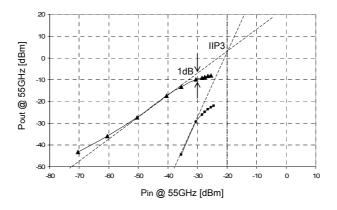

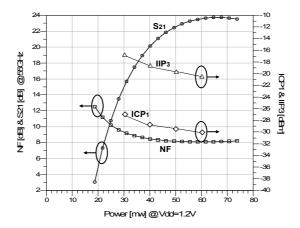

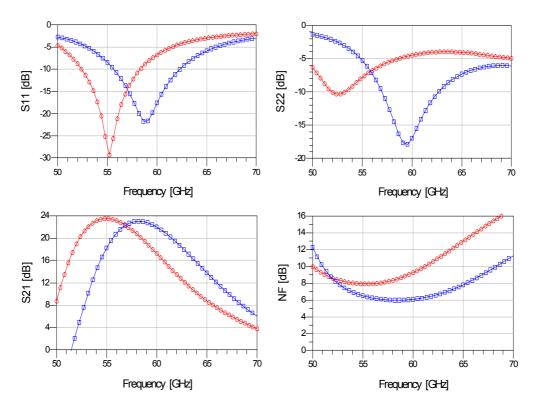

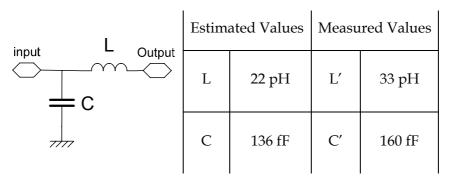

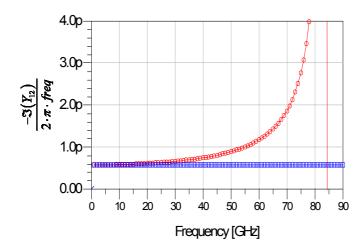

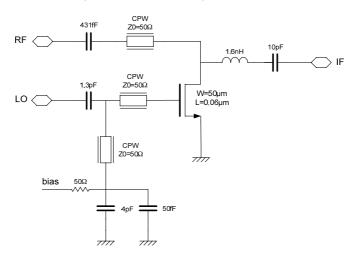

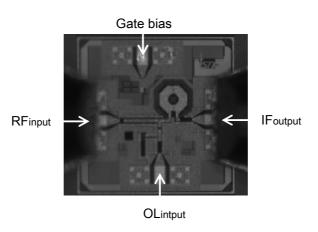

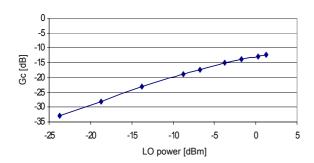

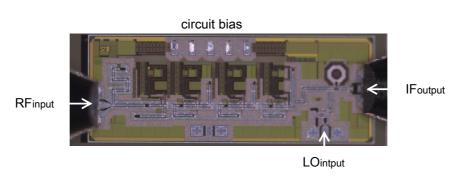

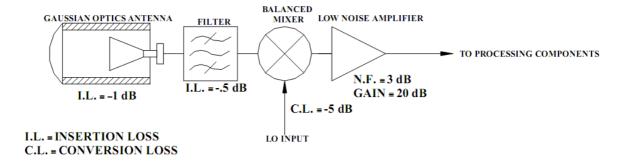

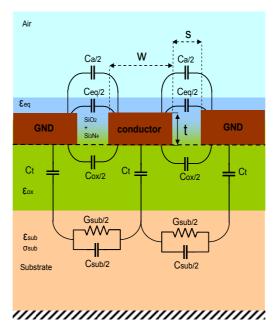

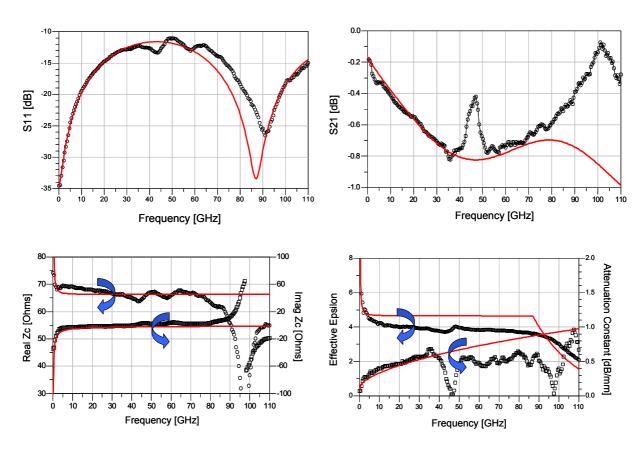

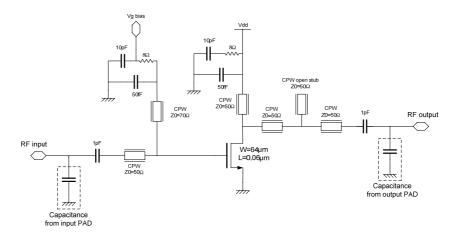

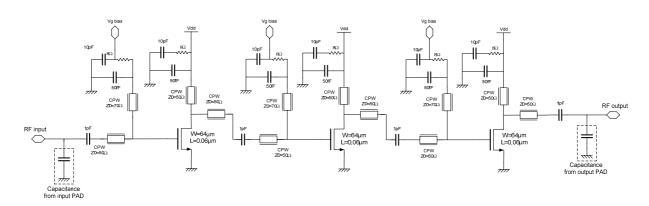

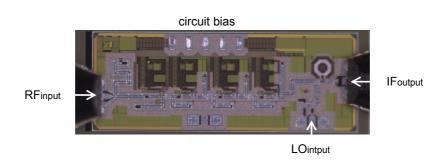

Figure II.16 NF<sub>min</sub> comparison for different gates length and technology[8]