## Processus de Conception Conjointe Logiciel Matériel Dirigés par les Modèles

## Thèse

Présentée à

L'Université des Sciences et Technologies de Lille

Pour obtenir le titre de

Docteur en Informatique

Par

#### Ali KOUDRI

Soutenue le 13 Juillet 2010

Devant la commission d'examen composée de :

LabSticc

Jean-Luc Dekeyser Directeur LIFL

François Terrier Rapporteur CEA LIST

Pierre-Alain Muller Rapporteur Université de Haute Alsace

Joël Champeau Examinateur ENSIETA

Denis Aulagnier Examinateur THALES

Président

Éric Senn

## Remerciements

Je remercie mon directeur, Jean-Luc Dekeyser, qui m'a donné l'opportunité de faire cette thèse dans une région lointaine, avec toutes les difficultés que cela entraı̂ne pour gérer l'encadrement. Mais c'était sans compter sur le support de mes deux tuteurs de choix, Denis Aulagnier et Joël Champeau, qui m'ont tant apportés. Un grand merci à vous.

Je remercie les équipes qui m'ont accueilli au sein de THALES et de l'EN-SIETA, je n'oublierai jamais les débats enflammés qui m'ont fait douter et qui ont permis de faire avancer la réflexion. Je remercie particulièrement Florence Cornic, responsable du laboratoire BTN à THALES, pour son accueil et sa bienveillance. Merci à Philippe Dhaussy, responsable du laboratoire DTN à l'ENSIETA pour son accueil et ses remarques pertinentes.

Je remercie tous les collaborateurs du projet MoPCoM : Philippe Soulard, Jean-Christophe Le Lann, Pierre-Laurent Lagalaye, Stéphane Lecomte, Frédéric Le Roy, Pierre Leray, Christophe Moy, Guy Gogniat, Jorgiano Vidal, Florent de Lamotte, Didier Vojtisek, Vincent Leilde et Onil Goubier. Merci pour toutes ces réunions riches en enseignements et qui sont pour beaucoup dans le contenu de cette thèse.

Je remercie mes rapporteurs, Pierre-Alain Muller et François Terrier, pour leurs remarques pertinentes qui m'ont permis d'améliorer la qualité de cette thèse.

Je remercie enfin ma famille et mes amis qui m'ont encouragé le long de cette thèse, en particulier mon épouse Yasmina, qui a eu le courage de supporter 3 longues années de séparation et mon fils Avicenne qui a su me tenir éveillé toutes les nuits durant les derniers mois de la rédaction.

J'adresse une pensée particulière à Joël Bohée et Bruno Bogaert sans qui rien de tout cela n'aurait pu arriver, à ma sœur Habiba et à ma tante Aïcha pour toutes ces années de galère traversées ensemble. Merci à toutes les autres personnes que je n'ai pas cité et qui se reconnaîtront dans ces lignes.

À ma mère, Fahima

#### Résumé

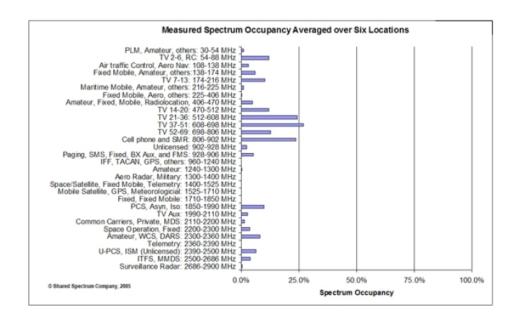

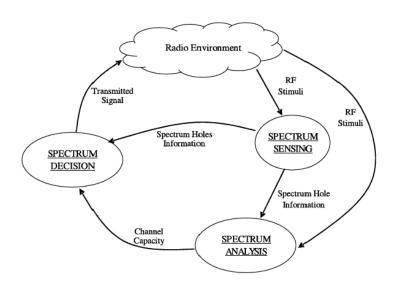

Aujourd'hui, les industries développant des systèmes sur puce doivent gérer le gap de productivité résultant de l'évolution rapide des technologies et de la pression croissante du temps de mise sur le marché. Dans ce contexte, la maîtrise des processus depuis la gestion des exigences jusque l'implantation du produit final est une nécessité pour favoriser la compétitivité. Les solutions pour traiter ce problème sont nombreuses et variées, et peuvent être de fait difficile à intégrer dans un processus. Dans cette thèse, nous proposons un processus formalisé de conception de système sur puce qui utilise les modèles pour mieux organiser les activités de l'ESL (Electronic System Level). Pour parvenir à ce résultat, nous proposons une contribution à la représentation des modèles de calculs, essentiel dans les activités de conception et d'analyse de l'ESL. Ces contributions sont validées par l'expérimentation sur un processus industriel de conception d'un système de "Cognitive radio" implanté sur une plateforme FPGA (Field Programmable Gate Array).

# Table des matières

| 1 | Inti | roduction                                                | 1  |

|---|------|----------------------------------------------------------|----|

|   | 1.1  | Problématique                                            | 2  |

|   | 1.2  | Solutions proposées                                      | 5  |

|   | 1.3  | Organisation du document                                 | 6  |

| 2 | Cor  | ntexte et motivations                                    | 9  |

|   | 2.1  | Introduction                                             | 11 |

|   | 2.2  | De la difficulté de concevoir des SoCs                   | 11 |

|   |      | 2.2.1 Les systèmes sur puce                              | 11 |

|   |      | 2.2.2 Les pratiques actuelles de conception de SoCs      | 14 |

|   |      | 2.2.3 Les problèmes posés par les pratiques actuelles    | 15 |

|   | 2.3  | Vers une meilleure maîtrise des processus                | 16 |

|   |      | 2.3.1 Les réponses de l'ESL aux pratiques actuelles      | 16 |

|   |      | 2.3.2 Apports de l'ingénierie des processus              | 23 |

|   |      | 2.3.3 Apports de l'IDM                                   | 26 |

|   | 2.4  | Les défis à relever                                      | 31 |

|   | 2.5  | Conclusion                                               | 32 |

| 3 | Éta  | t de l'art                                               | 34 |

|   | 3.1  | Introduction                                             | 36 |

|   | 3.2  | L'ingénierie Dirigée par les Modèles                     | 36 |

|   | 3.3  | IDM et codesign                                          | 40 |

|   |      | 3.3.1 Modélisation des plateformes d'exécution           | 41 |

|   |      | 3.3.2 Prise en compte de l'hétérogénéité des plateformes | 50 |

|   |      | 3.3.3 Modélisation des allocations et des analyses       | 52 |

|   | 3.4  | IDM et processus de développement                        | 56 |

|   |      | 3.4.1 Quelques définitions                               | 56 |

|   |      | 3.4.2 Modélisation des processus                         | 57 |

|   |     | 3.4.3    | Élicitation des processus à travers l'exécution de modèles 59 |

|---|-----|----------|---------------------------------------------------------------|

|   |     | 3.4.4    | Les composants de processus                                   |

|   | 3.5 | Concl    | usion                                                         |

| 4 | Cor | ntrôle ( | des processus par les modèles 67                              |

|   | 4.1 | Introd   | uction                                                        |

|   | 4.2 | MOD      | AL pour la modélisation des processus 69                      |

|   |     | 4.2.1    | Les intentions et les stratégies                              |

|   |     | 4.2.2    | Les modèles comme artefacts de processus                      |

|   |     | 4.2.3    | Les contraintes de processus 81                               |

|   |     | 4.2.4    | Les composants de processus "IDM" 83                          |

|   | 4.3 | COM      | ETA pour l'explicitation des MoCs 85                          |

|   |     | 4.3.1    | Principes                                                     |

|   |     | 4.3.2    | Concepts introduits                                           |

|   |     | 4.3.3    | Capitalisation des MoCs                                       |

|   | 4.4 | Concl    | usion                                                         |

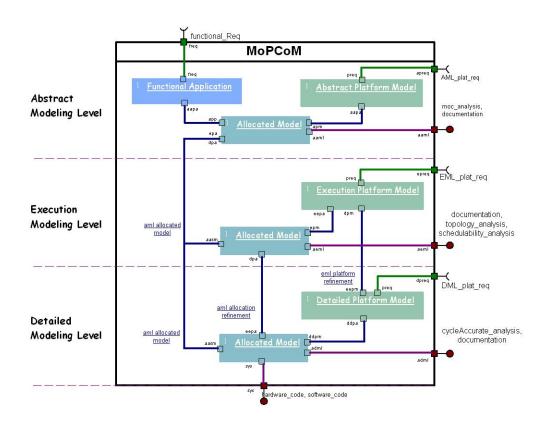

| 5 | Pro | cessus   | MoPCoM 104                                                    |

|   | 5.1 | Introd   | <u>uction</u>                                                 |

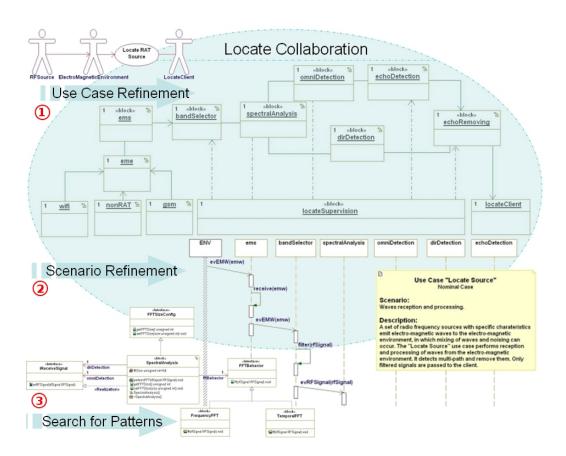

|   |     | 5.1.1    | Présentation de l'application de référence 109                |

|   |     | 5.1.2    | Résumé de la méthodologie MoPCoM                              |

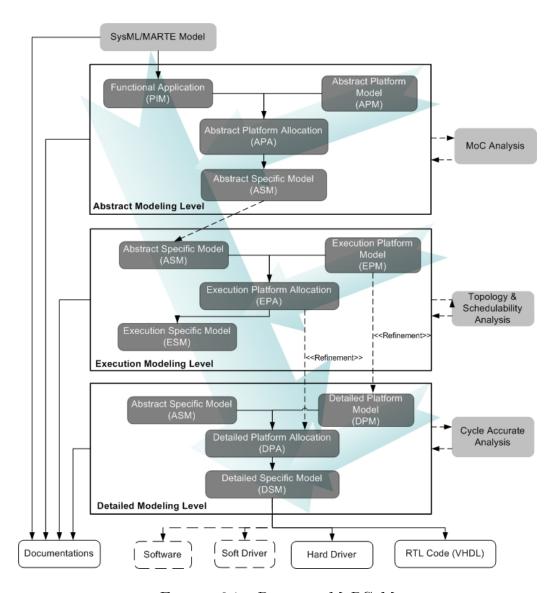

|   | 5.2 | Le niv   | r <mark>eau AML</mark>                                        |

|   |     | 5.2.1    | Présentation                                                  |

|   |     | 5.2.2    | Intentions et stratégies du niveau AML                        |

|   | 5.3 | Le niv   | r <mark>eau EML</mark>                                        |

|   |     | 5.3.1    | Présentation                                                  |

|   |     | 5.3.2    | Intentions et stratégies du niveau EML                        |

|   | 5.4 | Le niv   | r <mark>eau DML</mark>                                        |

|   |     | 5.4.1    | Présentation                                                  |

|   |     | 5.4.2    | Intentions et stratégies du niveau DML 129                    |

|   | 5.5 | Bilan    | des travaux                                                   |

|   |     | 5.5.1    | Bilan de l'utilisation de MARTE                               |

|   |     | 5.5.2    | Bilan de l'utilisation de COMETA                              |

|   |     | 5.5.3    | Bilan de l'utilisation de MODAL                               |

|   |     | 5.5.4    | Bilan du processus MoPCoM                                     |

|   | 5.6 | Concl    |                                                               |

| TA | BLE        | DES MATIÈRES                                                    | iv  |

|----|------------|-----------------------------------------------------------------|-----|

| 6  | 6.1<br>6.2 | Clusion Récapitulatif de la thèse Analyse critique Perspectives | 145 |

150

7 Annexes

# Table des figures

| 1.1  | Approche industrielle                                     | 3  |

|------|-----------------------------------------------------------|----|

| 1.2  | Nébuleuse ESL gérée par les langages SPEM et MARTE        | 5  |

| 1.3  | Nébuleuse ESL gérée par les extensions MODAL et COMETA    | 6  |

| 2.1  | Exemples d'application des SoCs                           | 11 |

| 2.2  | Structure typique d'un SoC                                | 13 |

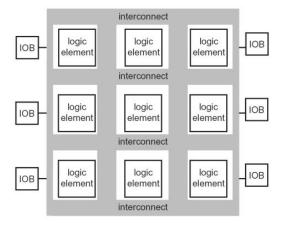

| 2.3  | Structure d'un FPGA                                       | 13 |

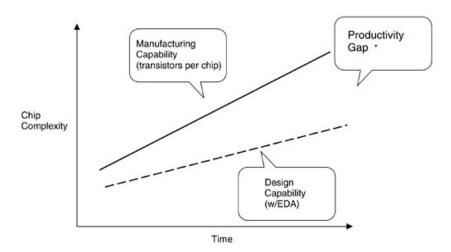

| 2.4  | Gap de productivité                                       | 15 |

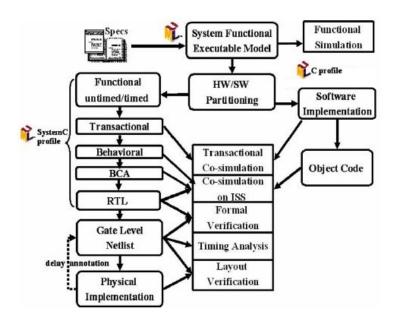

| 2.5  | Évolution des flots de codesign                           | 18 |

| 2.6  | Métamodèle Rugby                                          | 20 |

| 2.7  | Approche Platform Based Design                            | 22 |

| 2.8  | Allégorie de la tour de Babel                             | 24 |

| 2.9  | SPEM, concepts de base                                    | 28 |

| 2.10 | Architecture du langage MARTE                             | 30 |

| 3.1  | Utilisation d'UML pour la modélisation de systèmes        | 38 |

| 3.2  | Transformation de modèles                                 | 39 |

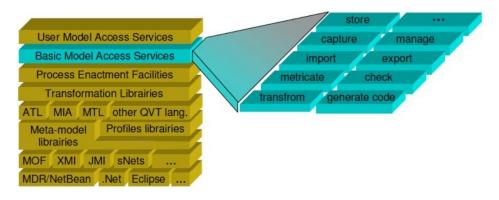

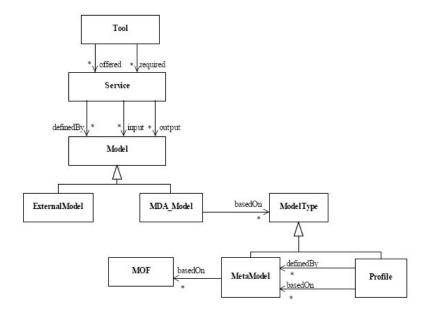

| 3.3  | Les modèles dans l'IDM                                    | 41 |

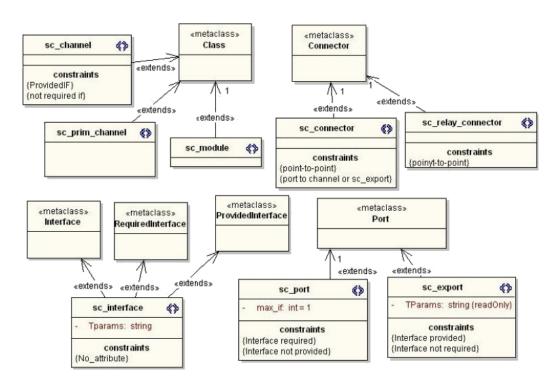

| 3.4  | Extrait du profil UML for SystemC                         | 43 |

| 3.5  | Méthodologie UPES                                         | 44 |

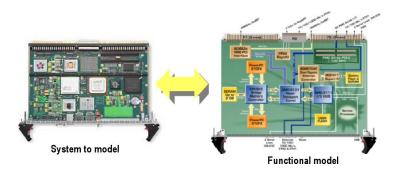

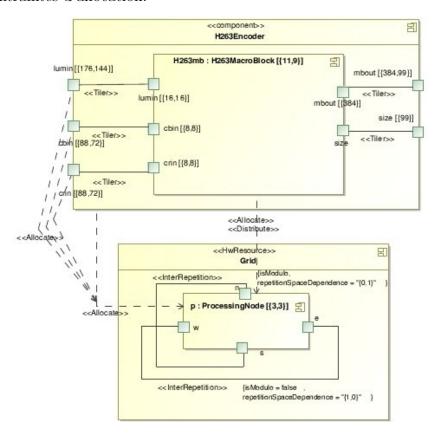

| 3.6  | Exemple de modèle fonctionnel d'un système complexe       | 45 |

| 3.7  | Exemple de modélisation de plateforme et d'allocation     | 46 |

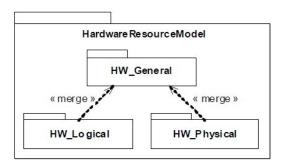

| 3.8  | Structuration du paquetage HRM de MARTE                   | 46 |

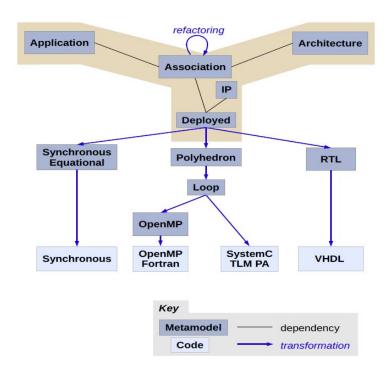

| 3.9  | Aperçu de la méthodologie Gaspard                         | 48 |

| 3.10 | Utilisation du profil UML for ESL                         | 49 |

| 3.11 | Capture d'un MoC hétérogène avec "UML Platform Profile" . | 51 |

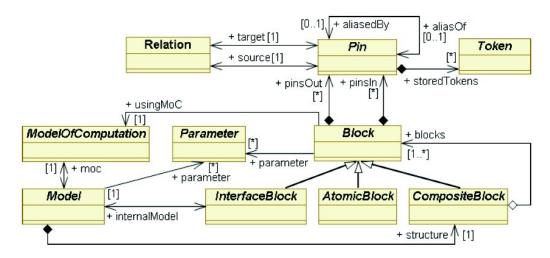

|      | Syntaxe abstraite de ModHel'X                             | 52 |

|      | Exemple d'allocation sur un MPSoC                         | 54 |

| 3.14 Modélisation des analyses dans MARTE                          | . 55  |

|--------------------------------------------------------------------|-------|

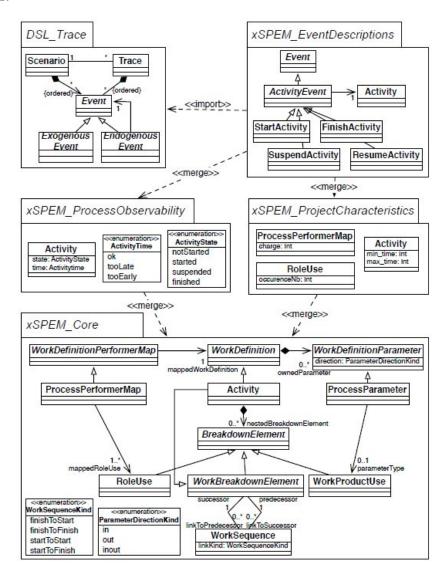

| 3.15 Extension xSPEM                                               | . 60  |

| 3.16 Gestion des données et rétro-annotations                      | . 61  |

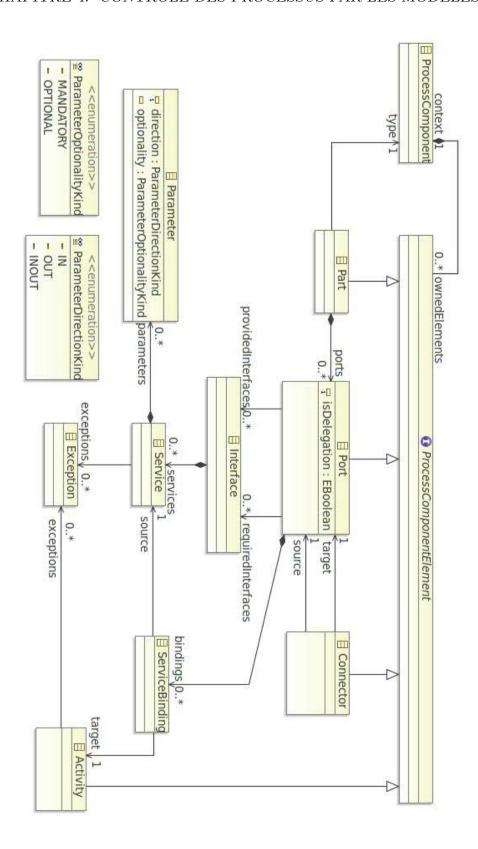

| 3.17 Composants de processus                                       | . 62  |

| 3.18 Classification des services                                   | . 63  |

| 3.19 Métamodèle "MDA Tool Component"                               | . 64  |

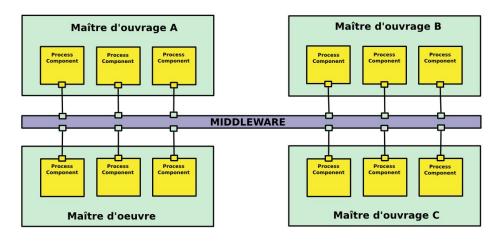

| 3.20 formalisation des rapports maître d'œuvre / maîtres d'ouvrage | 65    |

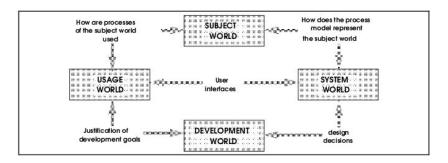

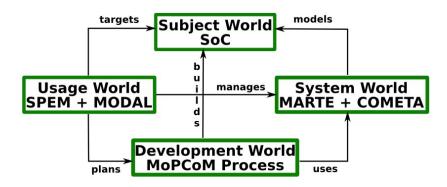

| 4.1 Four-Worlds Framework                                          | . 71  |

| 4.2 Spécialisation du Four-Worlds Framework                        | . 72  |

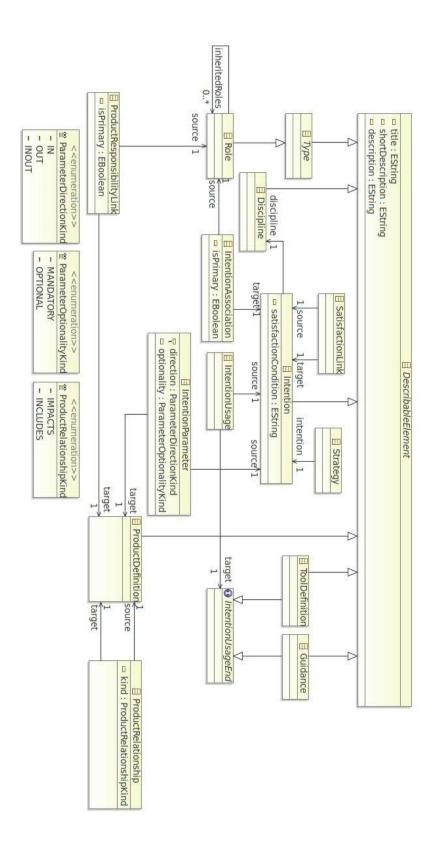

| 4.3 Syntaxe abstraite de la notion d'intention                     |       |

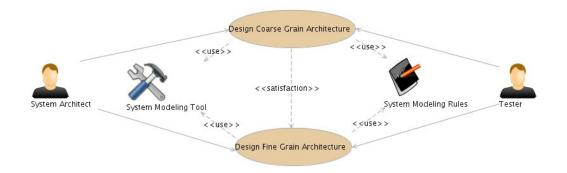

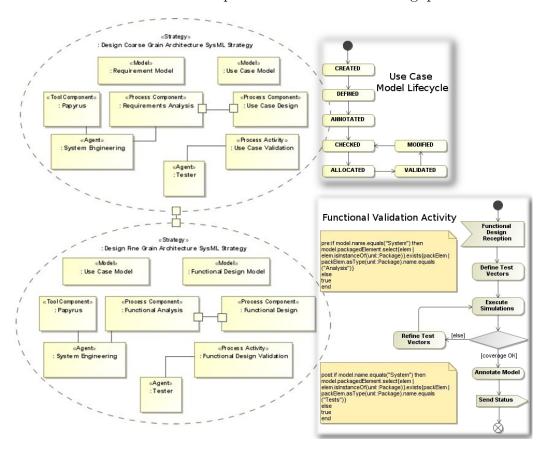

| 4.4 Exemple de carte d'intentions                                  |       |

| 4.5 Exemple de stratégie                                           |       |

| 4.6 Raffinement de la notion de produit                            |       |

| 4.7 Raffinements des paramètres des activités                      | . 80  |

| 4.8 Les contraintes de processus                                   | . 81  |

| 4.9 Les composants de processus SPEM                               | . 84  |

| 4.10 Les composants de processus MODAL                             | . 86  |

| 4.11 Composant de processus MoPCoM SoC/SoPC                        | . 87  |

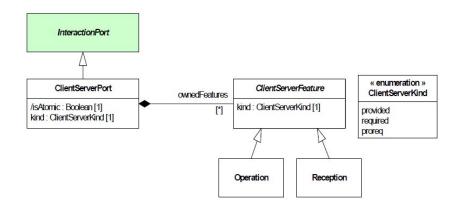

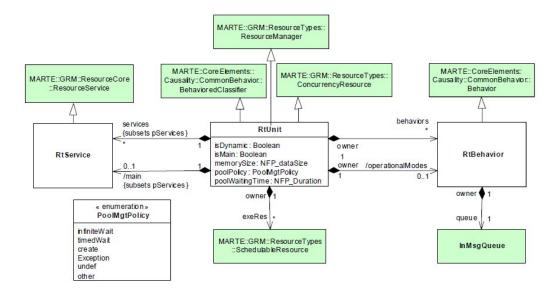

| 4.12 Composant générique MARTE                                     | . 89  |

| 4.13 Port de service MARTE                                         | . 89  |

| 4.14 Unité concurrente temps réel de MARTE                         | . 90  |

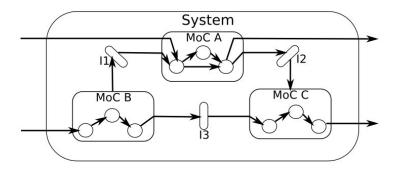

| 4.15 Exemple de MoC hétérogène                                     | . 92  |

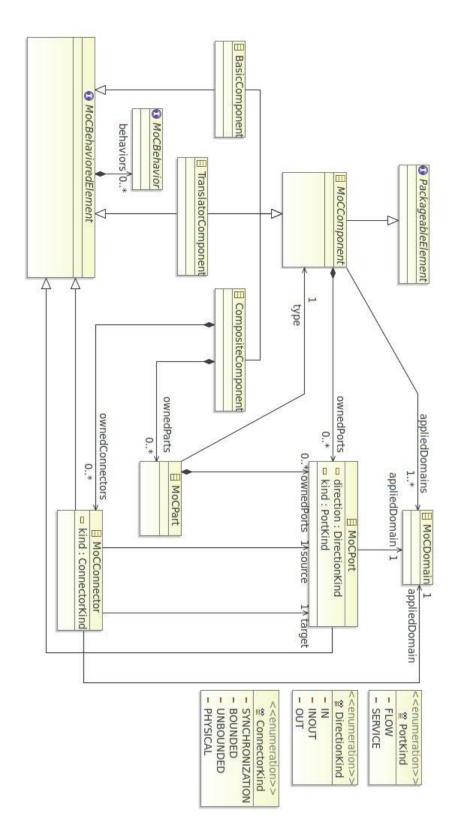

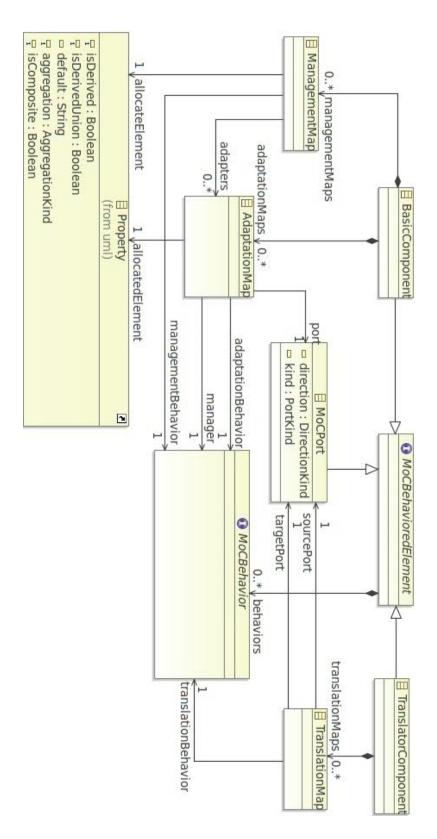

| 4.16 Syntaxe abstraite des Composants MoC                          | . 93  |

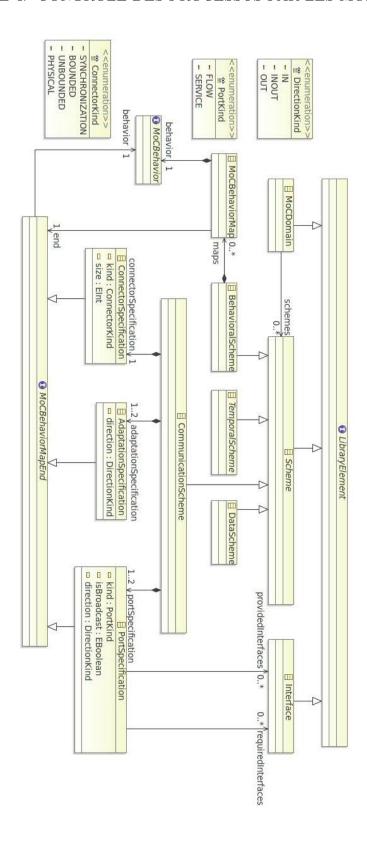

| 4.17 Syntaxe abstraite des domaines MoC                            | . 95  |

| 4.18 Composants d'adaptation et de traduction                      | . 97  |

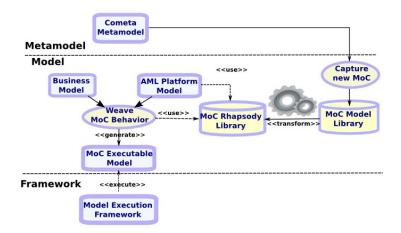

| 4.19 Flot pour l'outillage d'un nouveau MoC                        | . 99  |

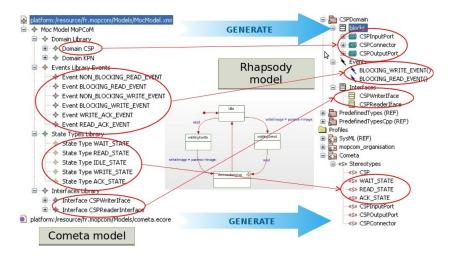

| 4.20 Transformation AML                                            | . 99  |

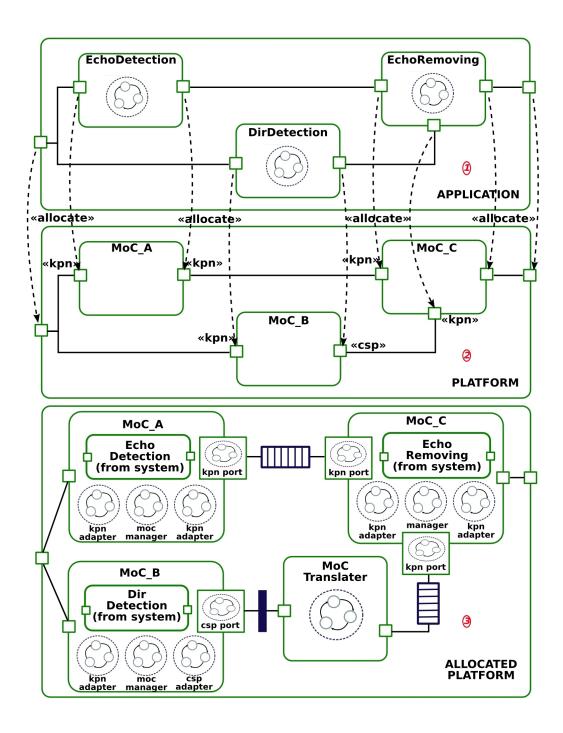

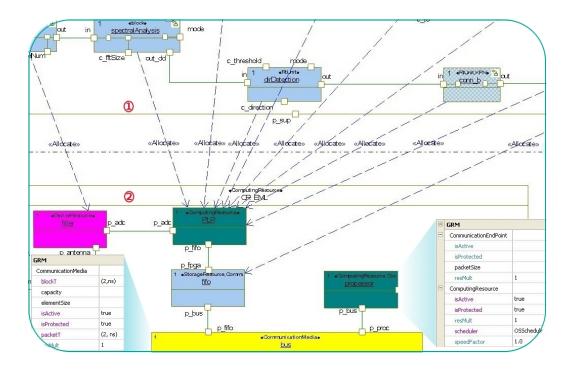

| 4.21 Exemple d'allocation sur une plateforme AML                   | . 101 |

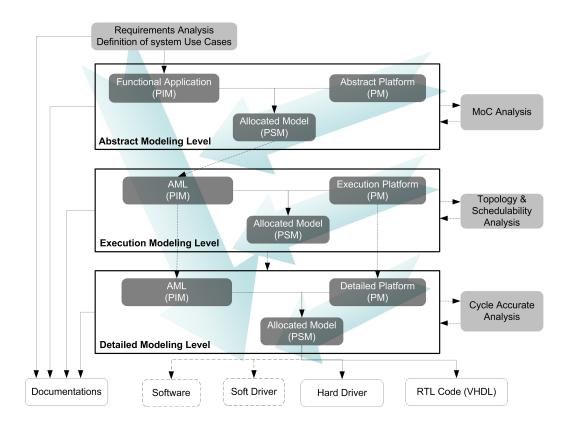

| 5.1 Vue générale de la méthodologie proposée                       | . 107 |

| 5.2 Occupation du spectre électromagnétique                        | . 110 |

| 5.3 Cognition Cycle                                                | . 110 |

| 5.4 Exemple de décomposition fonctionnelle                         | . 112 |

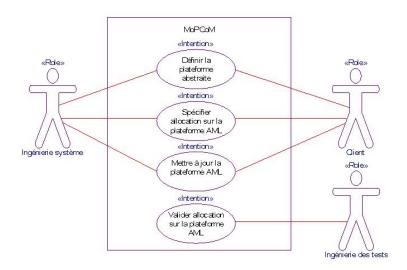

| 5.5 Intentions du niveau AML                                       | . 116 |

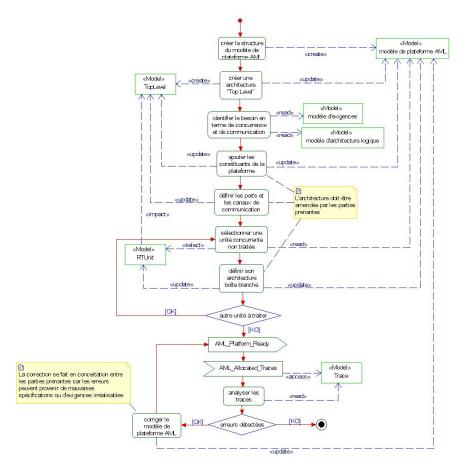

| 5.6 Stratégie pour la description de la plateforme AML             | . 116 |

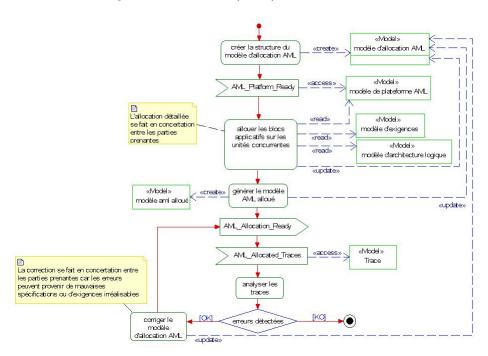

| 5.7 Stratégie pour l'allocation AML                                | . 117 |

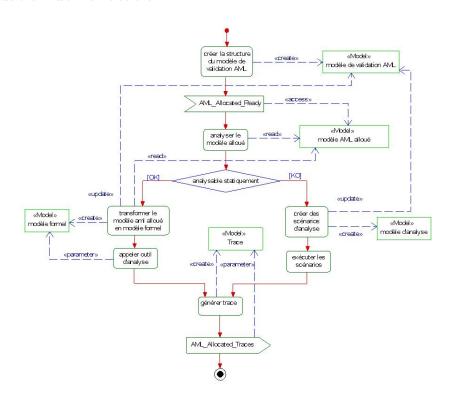

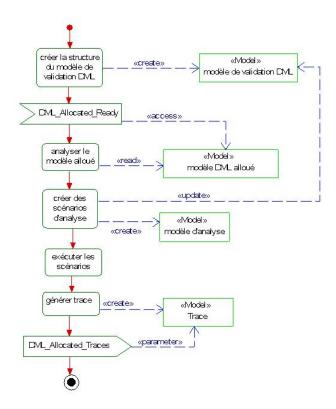

| 5.8 Stratégie de la validation de l'allocation                     | . 118 |

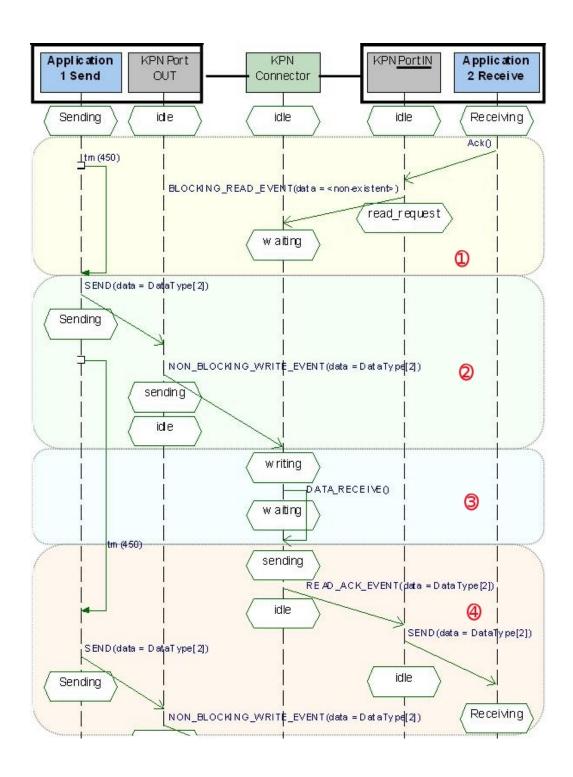

| 5.9  | Simulation KPN avec Rhapsody                                   |

|------|----------------------------------------------------------------|

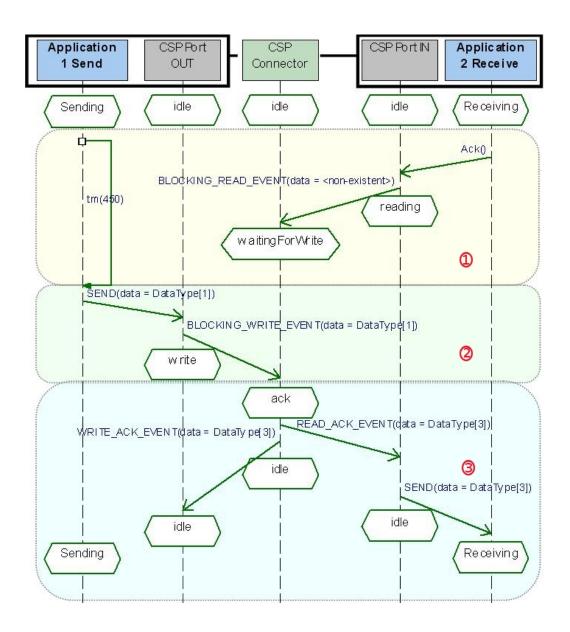

| 5.10 | Simulation CSP avec Rhapsody                                   |

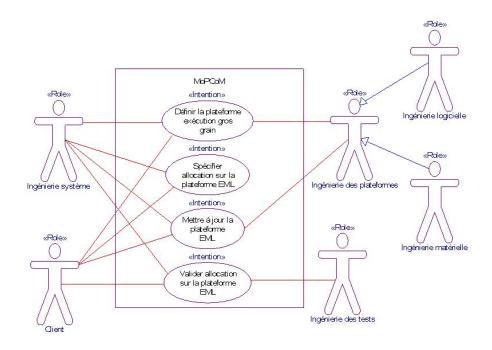

| 5.11 | Intentions du niveau EML                                       |

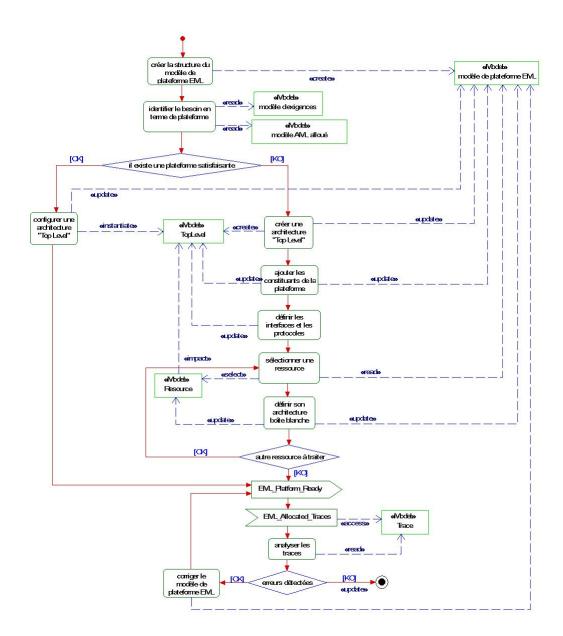

| 5.12 | Stratégie pour la description de la plateforme EML 124         |

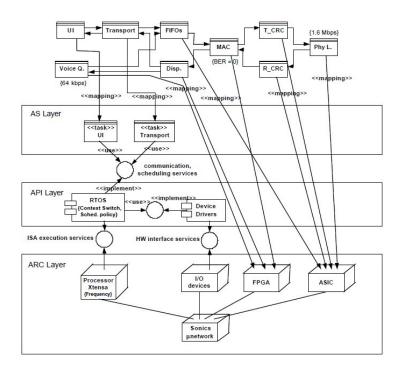

| 5.13 | Exemple description de la plateforme EML                       |

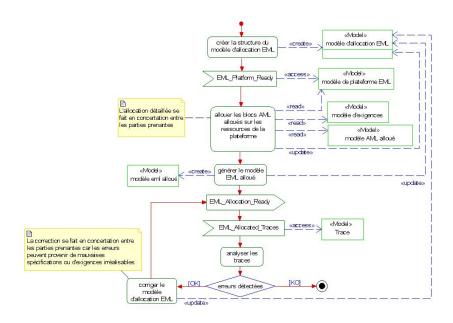

| 5.14 | Stratégie pour la description de l'allocation EML 126          |

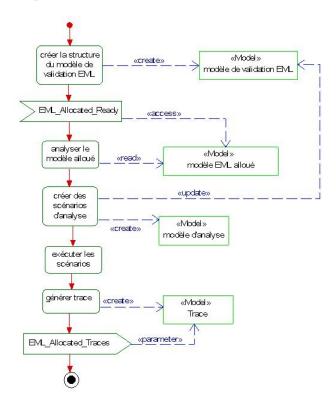

| 5.15 | Stratégie pour la validation EML                               |

| 5.16 | Exemple de scénario d'analyse basé sur l'utilisation du paque- |

|      | tage GQAM                                                      |

| 5.17 | Intentions du niveau DML                                       |

| 5.18 | Stratégie pour le raffinement de la plateforme                 |

| 5.19 | Stratégie pour la spécification de l'allocation DML 132        |

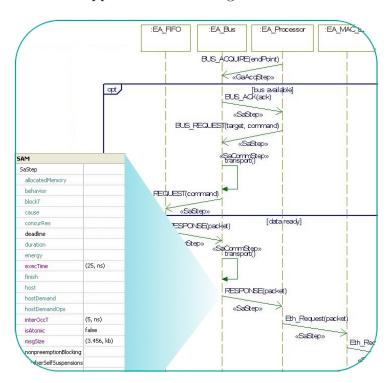

| 5.20 | Exemple d'allocation DML                                       |

| 5.21 | Stratégie pour la validation de l'allocation DML               |

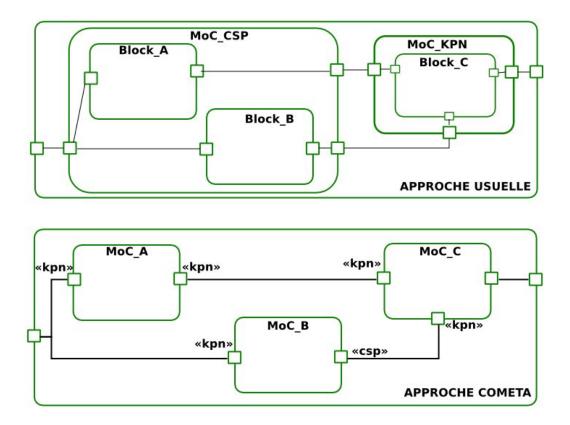

| 5.22 | Comparaison COMETA / Approche usuelle                          |

| 5.23 | MODAL pour une meilleure compréhension des processus $138$     |

| 6.1  | Processus MoPCoM                                               |

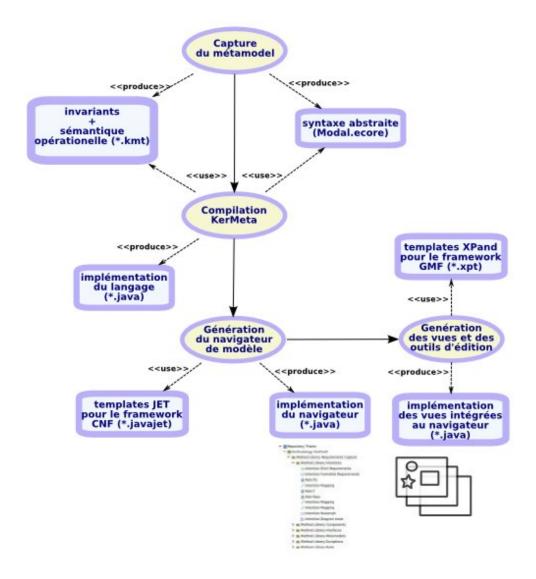

| 7.1  | Outillage du métamodèle MODAL                                  |

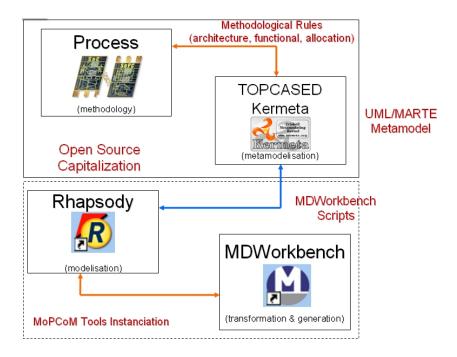

| 7.2  | Outillage MoPCoM                                               |

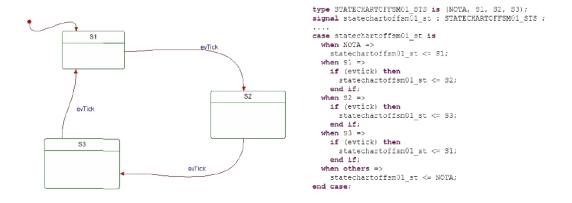

| 7.3  | Traitement des machines à état.                                |

## Chapitre 1

## Introduction

Les entreprises qui développent des systèmes sur puces sont de plus en plus confrontées à des problèmes de productivité liés à l'évolution rapide des technologies et la forte pression des marchés. Aujourd'hui, la maîtrise des développements de systèmes sur puce n'est majoritairement assurée que de manière ad-hoc : le savoir-faire de l'entreprise est capitalisé dans des documents textuels représentant le référentiel de l'entreprise, lequel accumule tous les savoirs des domaines transverses de l'entreprise (métier, gestion, qualité, etc.). L'ensemble du référentiel représente de fait une somme de documents importante, difficile à mettre à jour et à en garantir la cohérence face aux évolutions. En outre, la question du strict respect de ce référentiel, assurant la qualité des produits délivrés aux clients, reste difficile à établir du fait de la nature informelle des documents. Au delà du référentiel, le nécessaire respect de certains standards ou normes ajoute davantage de difficultés à la conduite des processus de développement de système en général et de systèmes sur puce en particulier. Ce type d'approche est aujourd'hui remis en cause dans les entreprises. Dans le but de relever le niveau des conceptions au niveau du système, plusieurs challenges scientifiques et techniques ont été posés. Parmi ces challenges, on retiendra en particulier la gestion de la complexité croissante et du changement d'échelle dans la conception mais aussi la nécessité de contrôler finement l'élicitation des processus.

C'est dans ce cadre que j'ai effectué ma thèse CIFRE au sein de l'entreprise Thales. Mon rôle a été d'investiguer la pertinence de l'utilisation de modèles pour améliorer la maîtrise des processus de conception de système sur puce et de proposer des solutions permettant d'améliorer la formalisation entre les parties hautes (exigences du système) et la partie basse des processus (implantation sur puce). Ce travail devait entre autres permettre de décharger au maximum les ingénieurs de tâches répétitives afin qu'ils puissent se focaliser davantage sur les problèmes d'analyses. Aussi, après une étude de l'état de l'art sur les propositions des communautés de l'ESL, de l'IDM (Ingénierie Dirigée par les Modéles) et de l'ingénierie des processus, j'ai pu identifier quelques points bloquants pouvant gêner l'adoption d'une approche IDM au sein des entreprises développant des systèmes sur puce.

## 1.1 Problématique

Ma première tâche lorsque je suis arrivé dans l'entreprise Thales a été d'observer les pratiques de conception d'applications du traitement du signal implanté sur des cartes FPGA (Plateforme reconfigurable matériellement). Ces activités constituent le cœur métier du laboratoire auquel j'étais rattaché.

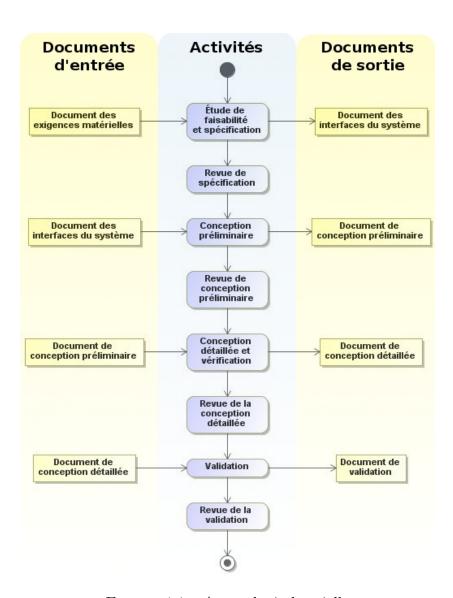

La figure 1.1 illustre le type de développement matériel constaté sur le terrain. En bref, les ingénieurs matériels, à partir des exigences reçues, appliquent de manière ad-hoc le savoir-faire du référentiel pour transformer manuellement les exigences en un produit fini. Le référentiel impose un travail fastidieux de documentation ou de mise à jour de matrices d'exigences devant être approuvés par les paires du domaine lors des activités de revue.

La mise en œuvre des spécifications du référentiel sont très laborieuses, sources de beaucoup d'incompréhensions et d'erreurs. Les difficultés rencontrées sont essentiellement dues au cloisonnement fort entre les activités de l'ingénierie matériel et l'ingénierie système. Finalement, cette approche dirigée par le code et la documentation laisse peu de place aux activités d'analyse. À cela, il faut ajouter le problème du respect des normes et des standards qui rend d'autant plus difficile le travail des ingénieurs. Par exemple, l'impact de l'application les normes DO-178B et DO-256 dans le domaine de l'avionique est considérable. Le respect de ces normes impose une lourdeur qui augmente de manière significative les temps et les coûts de développement.

Aussi, les principaux problèmes des approches classiquement employés dans l'industrie sont :

- Les processus appliqués impliquent un trop grand gap entre les exigences et les produits délivrés, rendant la gestion des exigences très difficile,

- L'application des processus du référentiel est prise en charge par les ingénieurs de développement alors qu'ils ne devraient en être que les

Figure 1.1 – Approche industrielle

acteurs,

- La maîtrise des artefacts de développement ne peut être assurée que de manière ad-hoc, conformément aux recommandations du référentiel,

- Il n'existe pas de séparation claire entre les aspects intentionnels des processus de leurs réalisations, ce qui rend le référentiel globalement dépendant des technologies et d'autant plus difficile à maintenir.

D'autres problèmes existent, comme par exemple celui du traitement des obsolescences, mais ils sont généralement considérés comme des effets de bords des problèmes mentionnés ci-dessus.

Il existe dans l'état de l'art un certain nombre de solutions traitant les problèmes mentionnés. À vrai dire, il existe même un grand nombre de solutions apportées par différentes communautés de recherche, quelles soient de l'ESL, de l'IDM ou de l'ingénierie des processus. Dans tout ce foisonnement de solutions, les choix sont difficiles car même si ces solutions se révèlent être efficaces pour traiter des problèmes précis, leur intégration au sein d'un processus de grande échelle peut poser des problèmes. L'interfaçage des métiers ou des activités du processus font partie des problèmes posés.

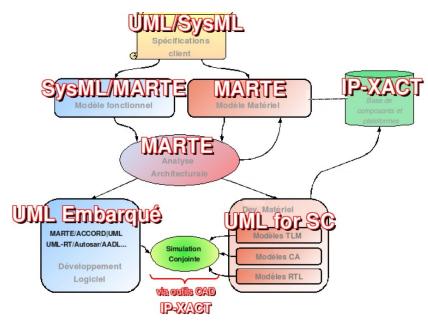

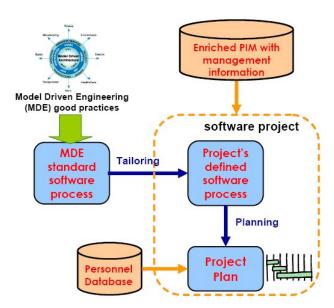

Dans un premier temps, j'ai proposé un processus qui fait la synthèse de techniques de l'ESL et de l'IDM. Dans cette proposition, je préconise l'utilisation de modèles en lieu et place des artefacts du processus décrit par le référentiel. Ce travail m'a permis de collaborer à la définition du profil UML MARTE pour la conception et l'analyse de systèmes temps réel embarqués, standardisé par l'OMG. Après avoir validé mon approche par l'expérimentation, je me suis posé la question de la capitalisation de mes propositions. Cette réflexion m'a amené à m'intéresser à la formalisation des processus.

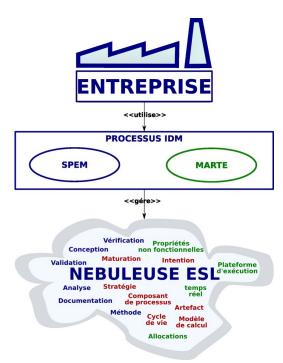

Pour résumer, mes propositions consistent en un processus formalisé, basé sur l'utilisation des profils SPEM (System and Software Process Engineering Modeling) et MARTE (Modeling and Analysis of Real Time Embedded Systems) afin de mieux organiser les activités et les artefacts de la nébuleuse ESL (figure 1.2). Mes travaux de synthèse et de modélisation ont fait apparaître des manques comme la représentation des MoCs (Models of Computation) ou la gestion fine du cycle de vie des processus (en rouge sur la figure 1.2) dans la mise en œuvre des solutions existantes. En effet, l'utilisation des langages SPEM et MARTE, dans leur spécification actuelle, ne convient pas à une bonne organisation des activités du processus et de ses artefacts. Pour y remédier, il est nécessaire de :

- étendre SPEM pour favoriser l'intégration des techniques IDM,

- étendre MARTE pour améliorer son adéquation aux concepts de l'ESL.

FIGURE 1.2 – Nébuleuse ESL gérée par les langages SPEM et MARTE

## 1.2 Solutions proposées

Les solutions que je propose visent à améliorer l'organisation des activités et des artefacts des processus de conception de systèmes sur puce par l'utilisation de modèles. Elles consistent en des extensions des langages SPEM et MARTE pour :

- Une meilleure intégration de l'ESL dans l'IDM,

- Une meilleure analyse des processus de codesign,

- Une meilleure intégration de l'IDM dans les modèles de processus.

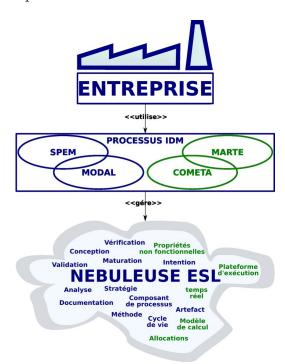

Nous verrons dans la suite de ce document de quelle manière ces extensions permettent de mieux traiter les problèmes mentionnées (figure 1.3). En particulier, nous verrons dans le chapitre 4 de quelle manière l'extension COMETA complète le langage MARTE pour répondre au premier point. Nous verrons également dans ce chapitre comment l'extension MODAL complète le langage SPEM pour répondre au second et au troisième point. En-

fin, nous proposons dans le chapitre 5 un modèle de processus formalisé, nommé MoPCoM SoC / SoPC, permettant de valider par l'expérimentation ces propositions. Le modèle de processus MoPCoM SoC / SoPC constitue une contribution originale validée par une expérimentation industrielle servant de référence aux futurs développements de FPGA au sein de l'entreprise Thalès. Ce modèle explicite le cheminement des conceptions de système sur puce depuis un ensemble d'exigences formalisées jusqu'à l'implantation finale du système. Aussi, sa formalisation et son outillage contribuent à garantir que les bons concepts seront utilisés au bon moment et que le code ou la documentation seront générés conformément aux règles métiers de l'entreprise ou aux règles imposées par les standards et les normes.

FIGURE 1.3 – Nébuleuse ESL gérée par les extensions MODAL et COMETA

## 1.3 Organisation du document

Le chapitre 2 présente de manière détaillée le contexte de cette thèse et les motivations de mes contributions. Le chapitre 3 présente l'état de l'art sur lequel je me suis basé pour proposer ces extensions. Ce chapitre présente un

rapide panorama des techniques IDM appliquées à la maîtrise des processus système et logiciel. Les chapitres 4 et 5 présentent les contributions de ma thèse qui sont :

- L'extension MODAL pour la représentation des processus,

- L'extension COMETA pour la représentation des modèles de calculs,

- Le modèle de processus MoPCoM SoC / SoPC dédié à la conception de systèmes sur puce.

Ces contributions font l'objet d'une analyse établissant la pertinence du travail réalisé dans le chapitre 5. Cette analyse permet de tirer un bilan de mes propositions et sur l'utilisation du profil MARTE pour le développement de systèmes sur puce. Enfin, la conclusion résume mes contributions, fait un point critique et ouvre de nouvelles perspectives sur le travail réalisé.

# Chapitre 2

## Contexte et motivations

## Sommaire

| 2.1 | Introduction                                          | 11 |

|-----|-------------------------------------------------------|----|

| 2.2 | De la difficulté de concevoir des SoCs                | 11 |

|     | 2.2.1 Les systèmes sur puce                           | 11 |

|     | 2.2.2 Les pratiques actuelles de conception de SoCs   | 14 |

|     | 2.2.3 Les problèmes posés par les pratiques actuelles | 15 |

| 2.3 | Vers une meilleure maîtrise des processus             | 16 |

|     | 2.3.1 Les réponses de l'ESL aux pratiques actuelles   | 16 |

|     | 2.3.2 Apports de l'ingénierie des processus           | 23 |

|     | 2.3.3 Apports de l'IDM                                | 26 |

| 2.4 | Les défis à relever                                   | 31 |

| 2.5 | Conclusion                                            | 32 |

## 2.1 Introduction

Je présente dans ce chapitre le contexte des travaux de la thèse et les définitions sur lesquelles je me suis basé pour construire ma réflexion. Dans un premier temps, je montre que la maîtrise de processus de conception sur puce représente un enjeu crucial. À cette fin, je présente un flot typique de conception de SoC qui permet de faire ressortir les problèmes traités dans cette thèse. Ensuite, je fais un tour d'horizon des solutions apportées par les communautés de l'ESL, de l'ingénierie des processus et de l'IDM à la maîtrise des processus. Cela me permettra d'établir, à la lumière des problèmes exposés et des solutions proposées, les défis à relever dans cette thèse.

#### 2.2 De la difficulté de concevoir des SoCs

#### 2.2.1 Les systèmes sur puce

Depuis quelques années, le marché des systèmes sur puce (SoC, Systemon-Chip) connait une forte croissance. Il est prévu par ailleurs que ce marché pèse la somme de 56 milliards de dollars en 2012, ce qui représente une croissance moyenne annuelle de 24%.

Figure 2.1 – Exemples d'application des SoCs

Le domaine des SoCs touche un nombre de secteurs croissant (figure 2.1) comme l'automobile, l'aérospatial, la téléphonie mobile ou même l'électroménager.

Il existe dans la littérature plusieurs définitions des SoCs (System-On-Chip – Systèmes sur puce). La définition que je choisis dans le cadre de cette thèse est celle proposée dans [NN03] :

"A SOC is a system on an IC that integrates software and hardware Intellectual Property (IP)"

Les systèmes sur puce sont des circuits intégrés qui implantent des systèmes complets. Ils sont constitués d'une hiérarchie de blocs hétérogènes, matériels ou logiciels, analogiques ou numériques, et qui représentent autant de sous-systèmes. Les blocs qui constituent la hiérarchie du système sont généralement désignés sous le terme de propriétés intellectuelles (IP – Intellectual Property).

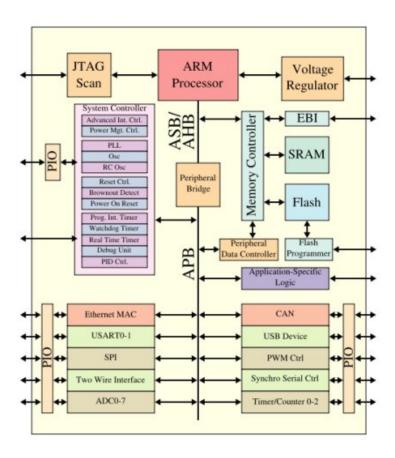

Dans le détail, un SoC est un circuit intégré typiquement constitué de ressources de (figure 2.2) :

- calcul (processeur, FPGA, DSP ou microcontrôleur),

- mémorisation (RAM, ROM ou Flash),

- communication (bus AMBA, PCI, ...)

- temps (horloges),

- conversion analogiques/numériques,

- entrées / sorties (Ethernet, FireWire, etc.),

- gestion de l'énergie.

Les FPGAs sont des cas particuliers de SoC qui intègrent des parties reprogrammables matériellement. Ils sont constitués d'un ensemble de blocs logiques organisés en matrice. Chacun de ces blocs contient des éléments de calcul, des registres et des mécanismes supportant la reprogrammation (LUT – Look-Up Table) (figure 2.3). La logique des programmes exécutés sur les FPGA est dite "câblée" car les programmes qui y sont implantés peuvent être représentés sous la forme d'un plan de blocs fonctionnels reliés par des fils.

L'implantation de systèmes sur du matériel reprogrammable présente un certain nombre d'avantages (minimisation des risques de développement, possibilité de faire du prototypage rapide, etc.) et d'inconvénients (consommation énergétique accrue, rapidité d'exécution plus limitée que celle des ASICs – Application Specific Integrated Circuit, etc.). De par leurs propriétés, les FPGAs sont généralement réservés à des marchés de niche ne nécessitant pas de grosses productions, comme le domaine militaire ou l'aérospatial.

FIGURE 2.2 – Structure typique d'un SoC

FIGURE 2.3 – Structure d'un FPGA

#### 2.2.2 Les pratiques actuelles de conception de SoCs

Dans les pratiques actuelles de conception de systèmes sur puce, les équipes système font l'interface entre les clients et les équipes de développement. Ils établissent avec le client le cahier des charges et les exigences du système (exigences de haut niveau). Les exigences peuvent être classées en trois catégories :

- Les exigences fonctionnelles, relatives aux fonctions du système ("détecter une cible"),

- Les exigences non-fonctionnelles, relatives aux contraintes du système ("le système doit consommer moins de 5kW/h"),

- les exigences de processus portant sur le processus de développement ("le système doit être développé dans un an et livré avec son guide d'utilisation").

À partir des exigences fonctionnelles, les équipes d'ingénierie système établissent les interfaces du système qu'ils valident avec le client. À partir des exigences non-fonctionnelles, ils discutent avec les équipes d'ingénierie logicielle ou matérielle pour établir des exigences dérivées (exigences de bas niveau) conformément à l'état de l'art des technologies du moment. L'activité qui consiste à faire un choix d'implantation en logiciel ou matériel pour chaque fonctionnalité du système est généralement désignée sous le terme de "partitionnement". Le choix du partitionnement dépend de plusieurs facteurs : la qualité de service, la sûreté de fonctionnement, le besoin en performance ou en flexibilité, etc.

Les exigences matérielles sont transformées en architecture RTL (Register Transfert Level) constituée d'une hiérarchie de blocs matériels, et identifiés par leurs interfaces et leurs protocoles de communication. Pour réaliser ces activités, l'ingénierie matérielle utilise un ou plusieurs langages de description matérielle (VHDL, Verilog) supportés par différents outils de conception, de simulation, de vérification et de synthèse. Les exigences logicielles sont quant à elles généralement traduites en artefacts de langages de haut niveau (C, C++) décrivant des architectures logicielles qui seront ensuite compilées pour les plateformes d'exécution retenues, y compris les plateformes d'abstraction matérielles telles que les systèmes d'exploitation (VxWorks, Linux) ou les middlewares (CORBA). À l'issu de l'implantation du système, un ensemble de tests (tests unitaires, tests d'intégration, tests de robustesse) sont exécutés afin de vérifier le bon comportement du logiciel et du matériel, et la correction

fonctionnelle. Dans la pratique, la partie test peut prendre plus de 70% du temps de développement. Enfin, des activités de validation ont pour but d'établir les équivalences entre les exigences et le produit.

Avec l'évolution des technologies et l'accroissement exponentiel du nombre de ressources disponibles, la validation de tels systèmes au bit près et au cycle près (cycle accurate bit accurate) est devenue très laborieuse et consommatrice de temps. Et si les analyses conséquentes aux choix d'un partitionnement ne sont pas jugés satisfaisantes, il faut choisir un autre partitionnement et s'engager dans un nouveau processus de vérification / validation consommateur en temps et en ressources.

#### 2.2.3 Les problèmes posés par les pratiques actuelles

Conformément à la loi de Moore, l'évolution rapide des technologies a permis aux fournisseurs de technologies de disposer d'un nombre croissant de ressources matérielles, toujours meilleur marché et plus rapide. Cette évolution a permis de proposer un plus grand nombre de fonctionnalités, toujours plus complexes.

Face à une telle évolution, les méthodologies classiques ne sont plus adaptées car elles n'ont su gérer convenablement la nécessaire montée en abstraction et il en résulte aujourd'hui une crise liée au gap de productivité (cf. figure 2.4) accentuée par la pression due à la forte compétitivité des entreprises [ITR07].

FIGURE 2.4 – Gap de productivité

La conception de SoCs nécessite l'exécution d'un ensemble d'activités de conception, d'analyse, de tests ou de certification depuis la capture des exigences du client jusqu'à la livraison, la maintenance du produit et son retrait. L'exécution de ces activités implique des interactions entre un ensemble de métiers, de compétences, de cultures, d'outils ou de langages qui rendent la conception très complexe. À cela, il faut ajouter le respect des standards et des normes de développement ou de gestion. Par exemple, dans le domaine de l'avionique, le problème de l'application des normes de certification provient de la lourdeur et le coût de leur mise en place. En effet, on estime que la mise en place d'un processus conforme à ces normes implique un surcoût financier de 75 à 150 % et des durées de développement d'autant plus longues. Il résulte de tous ces facteurs de grandes difficultés pour gérer de manière rationnelle les développements de SoCs.

Pour traiter ces problèmes, les ingénieurs appliquent généralement le référentiel d'entreprise dans lequel sont capitalisés les savoirs acquis au fil des expériences ou des formations. Ces référentiels sont constitués de guides, de méthodes ou de tutoriels spécifiés de manière informelle dans des documents textes. De fait, ces approches essentiellement dirigée par les documents ("Document Driven Approach") sont très lourdes à mettre en œuvre et à faire évoluer.

Afin de surmonter toutes ces difficultés, il est nécessaire d'appliquer des méthodologies de développements plus rigoureuses qui permettent de concevoir des SoCs conformes aux exigences du client dans les temps et les budgets requis. La définition de telles méthodologies doit prendre en compte les facteurs d'échecs récurrents afin de les anticiper. Dans ce contexte, l'adoption d'un processus formalisé [M.S03] permettrait de mieux gérer les activités de conception et d'analyse.

### 2.3 Vers une meilleure maîtrise des processus

### 2.3.1 Les réponses de l'ESL aux pratiques actuelles

Avant de présenter les propositions de la communauté ESL pour améliorer la maîtrise des processus de codesign, je me propose de choisir une définition de l'ESL (Electronic System Level). Dans [BGA07], l'ESL est définit comme suit :

"Utilization of appropriate abstractions in order to increase com-

prehension about a system, and enhance the probability of a successful implementation of functionality in a cost effective manner, while meeting necessary constraints"

L'ESL se définit par l'utilisation d'abstractions appropriées permettant d'améliorer la compréhension des systèmes et d'augmenter la probabilité d'implanter correctement leurs fonctionnalités au regard des contraintes de conception imposées. J'ai choisi cette définition car elle fait bien ressortir les relations entre la notion de système et les niveaux d'abstractions permettant de mieux gérer la complexité et les risques de conception.

L'ESL propose des techniques permettant de traiter le problème du gap de productivité et d'accélérer les développements conjoints de logiciel / matériel. Dans les paragraphes suivant, je présente les principales techniques de l'ESL qui sont exploitées dans l'approche IDM que je propose dans cette thèse.

#### Montée en abstraction

Les approches classiques de développement de SoC possèdent de nombreux inconvénients, en particulier dans la gestion des exigences. En effet, la compréhension du besoin et la validation des exigences dans ces approches ne se peut se faire qu'à travers les implantations du système. Aussi, dans la mesure où les choix de conception sont très vastes et les temps de vérification très long pour valider LA solution, les approches ESL se justifient par la proposition de techniques permettant d'explorer rapidement l'arbre des possibles afin d'éliminer un maximum de solutions inaptes à satisfaire complètement les exigences, tant fonctionnelles que non-fonctionnelles, dans les temps et les budgets requis.

Dans cet esprit, il est intéressant de pouvoir construire des systèmes par diverses représentations qui intègrent de plus en plus d'exigences, tant au niveau structurel qu'au niveau comportemental. Cette approche incrémentale nécessite l'utilisation de langages dédiés à chaque niveau d'abstraction. Elle permet en outre de fournir aux clients des modèles exécutables afin de mieux maîtriser les risques et d'éviter des dépenses inutiles liées à l'inadéquation ou la non-faisabilité des exigences [Kra03].

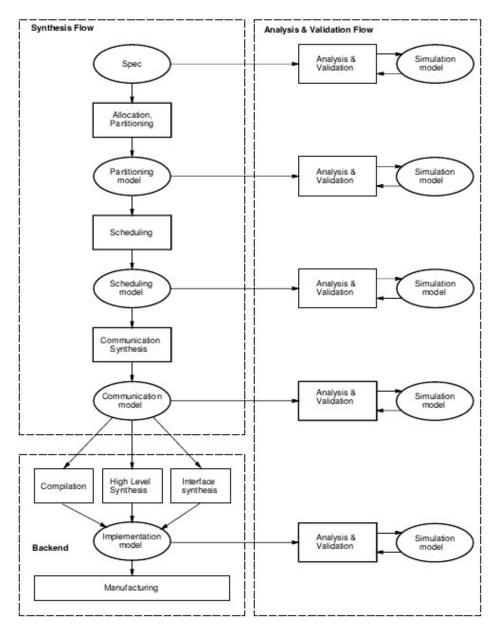

La figure 2.5 représente un flot typique ESL. Elle illustre bien les évolutions qui ont été apportées par la communauté de l'ESL. Entre autre, cette figure illustre un des principes de base de l'ESL qui est de retarder au maximum les choix du partitionnement. Cela permet d'une part d'éviter un effet

FIGURE 2.5 – Évolution des flots de codesign

boule de neige dû aux mauvais choix de partitionnement; et d'autre part d'unifier le développement conjoint de logiciel/matériel et de lever les verrous de communications entre les équipes de développement matériel et logiciel.

#### Orthogonalisation des préoccupations

Pour décrire un système, il existe plusieurs manières de procéder :

- on peut le décrire de manière informelle, par la parole ou par des descriptions textuelles,

- par des schémas ou des croquis,

- par un langage informatique compréhensible par une machine.

Loin de s'exclure, ces représentations sont en fait complémentaires : un homme pourra difficilement deviner l'architecture d'un système en regardant du code VHDL et il est difficile de faire interpréter un schéma griffonné sur un bout de table à un ordinateur.

Que ce soit dans l'IDM ou dans l'ESL, la description d'un système sert avant tout son analyse. Par ailleurs, le terme "analyse" signifie étymologiquement décomposition. On constate en effet dans la pratique qu'il est plus facile de gérer la complexité d'un système à travers sa décomposition. On peut constater également que les produits complexes vendus sur le marché ne sont finalement jamais que des assemblages de systèmes plus simples. Aussi, les problèmes rencontrés dans la construction de systèmes complexes proviennent essentiellement de la gestion de l'hétérogénéité des sous-systèmes et de leurs interactions. Par exemple, les retards pris sur la construction de l'airbus A380 étaient essentiellement dues à des problèmes d'interfaçage.

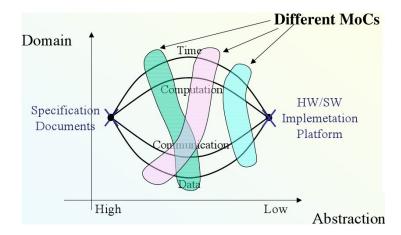

La gestion de l'hétérogénéité est un des plus importants problèmes identifiés par la communauté de l'ESL. Afin de favoriser l'analyse de systèmes complexes qui mêlent des sous-systèmes hétérogènes, il est nécessaire d'identifier les détails qui caractérisent l'hétérogénéité et d'orthogonaliser les préoccupations. Dans l'ESL, les détails relatifs à la caractérisation des MoCs sont liés à la représentation des données, du temps, du calcul ou des communications. Ces caractéristiques définissent ce que l'on nomme "le modèle de calcul".

Dans [Jan04], l'auteur propose un méta-modèle qui sert à caractériser les modèles de calcul suivant les axes du calcul, de la communication, des données et du temps. Ce méta-modèle, nommé rugby, est schématisé par la figure 2.6. Les critères d'orthogonalisation choisis permettent d'établir une taxonomie pertinente des modèles de calcul et des langages qui servent à les exprimer. Le principe de ce modèle consiste à considérer que durant le développement d'un système, depuis l'idée jusqu'à sa réalisation, un certain nombre de modèles exprimés par différents langages sont utilisés à différents niveaux d'abstraction. Le raffinement des modèles, qui est guidé par les besoins en analyses,

FIGURE 2.6 – Métamodèle Rugby

revient alors à détailler leurs caractéristiques suivant chacun de ces axes (domaines).

Le domaine du calcul, aussi désigné sous le terme fonction ou comportement, consiste à établir des relations entre les entrées et les sorties du système. Les relations peuvent être par exemple des fonctions mathématiques, des équations booléennes, une suite d'instructions machines (code assembleur) ou un algorithme.

Le domaine des données traite la représentation des données physiques ou logiques. Par exemple, au niveau du système, on parlera davantage de données physiques (20 kilogrammes, 36 km/h, 3 ms). Au niveau logique, on parle de types de donnée abstraits (entiers, réels sur 32 ou 64 bits). Au niveau matériel, on parle de vecteurs de bits représentant basiquement le nombre de fils nécessaires pour faire transiter les commandes et les données.

Le domaine du temps traite la représentation du temps, caractéristique dominante des systèmes embarqués temps réel. La forme la plus simple du temps est le temps causal qui établit des relations de précédence entre les événements. On distingue ensuite le temps discret (temps cadencé) par lequel les comportements du système sont reliés à des horloges de référence communes (synchrone) ou non (asynchrone) mesurant la progression du temps à intervalle régulier. Enfin, on distingue le temps réel au sens physique du terme et dont la définition dépasse tout simplement le cadre de cette thèse et du codesign en général. Cependant, on peut mentionner que certains langages, comme le profil UML MARTE ou MATLAB, choisissent de considérer le temps continu comme un temps discret dense.

Le domaine de la communication traite les mécanismes permettant de faire interagir plusieurs entités. Suivant le niveau d'abstraction où l'on se place, les communications revêtent différentes formes. Par exemple, au niveau logiciel, les communications se traduisent en appels de méthodes alors qu'au niveau matériel, elles se matérialisent sous la forme de bus de communication caractérisées par des propriétés physiques (longueur, dissipation énergétique, etc.) avec des accès gérés par des protocoles souvent complexes nécessitant des politiques d'arbitrage.

#### L'approche "Platform Based Design"

Une des manières de répondre aux besoins de productivité est de favoriser au maximum la réutilisation de blocs de nature ou de niveaux d'abstraction différents (systèmes, logiciels ou matériels). La notion de bloc réutilisable est généralement désignée sous le terme de "Intellectual Property". Les propriétés intellectuelles (IP) constituent des solutions sur étagères pouvant être réutilisées, vendues ou échangées.

Outre les aspects légaux associés à la réutilisation, l'assemblage d'IPs pose un certain nombre de problèmes techniques. En effet, les blocs IP ne peuvent être assemblés que si :

- ils sont de même nature (physique ou logique),

- ils sont définis au même niveau d'abstraction,

- ils possèdent des interfaces et des protocoles de communication compatibles.

Ces problèmes soulèvent la nécessité de standardiser les niveaux d'abstraction [Lah06], les interfaces ou les protocoles. Dans cette idée, il existe aujourd'hui 3 consortiums à but non-lucratif qui travaillent dans ce sens :

- Open SystemC Initiative (OSCI) [osc] œuvre à la standardisation des niveaux d'abstraction et est à l'origine du langage SystemC,

- Open Core Protocol International Partnership (OCP-IP) [ocp] œuvre à la définition un bus d'interconnexion matériel standard,

- SPIRIT [spi] Structure for Packaging, Integrating and Reusing IP within Tool-flows (SPIRIT) œuvre à la standardisation de la description des IPs afin de faciliter leur échange, leur configuration et leur intégration dans les outils (IP-XACT).

Dans [CCH<sup>+</sup>99], les auteurs poussent la réflexion sur la réutilisation plus loin et suggèrent la réutilisation de plateformes vérifiées et documentées com-

plètes : c'est l'approche "Platform Based Design". Une définition plus précise de cette approche est donnée dans [Bai05] :

"Integration oriented design approach emphasising systematic reuse, for developing complex products based upon platforms and compatible hardware and software virtual components, intended to reduce development risks, costs and time to market"

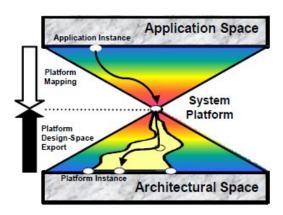

Figure 2.7 – Approche Platform Based Design

Comme le souligne cette définition, la réutilisation de plateformes et de composants matériels et logiciels vérifiés permet de limiter les risques et d'augmenter la productivité. De fait, une telle approche ne peut ni être de type "top-down" car les blocs matériels et logiciels existent déjà, ni même de type "bottom-up" car la plateforme d'exécution existe également. Dans ce cas, les méthodologies qui supportent cette approche sont de type "Meet in the middle" (figure 2.7).

Le principe de cette approche consiste essentiellement à rechercher une allocation spatiale et temporelle optimale des blocs logiciels ou matériels sur une plateforme contenant des composants reprogrammables en logiciel ou en matériel. Le choix d'une plateforme de déploiement est déterminé par le domaine d'application, les services et les qualités de service offerts par la plateforme et d'autres critères non fonctionnels tels que le prix, le poids ou la consommation. Le marché visé a également son importance. Par exemple, le marché militaire justifie largement le choix de plateformes FPGA pour ses applications. Outre les bénéfices apportés par cette approche, son application correspond dans les faits à une pratique industrielle bien ancrée.

#### 2.3.2 Apports de l'ingénierie des processus

Le Standish Group fournit dans son rapport de 2006 [sta06] des statistiques détaillées sur les résultats de la conduite de projets dans les entreprises.

Il ressort de ces études que :

- 31,1% des projets échouent durant leur exécution,

- 52,7% des projets coûtent en moyenne 189% plus cher que prévu,

- 16,2% des projets tiennent le budget et les délais mais seulement 42% des fonctionnalités demandées sont effectivement implantées.

Bien évidemment, ces statistiques sont à prendre avec précaution. La réalité montre que, généralement, plus la taille des organisations est grande, plus les risques sont élevés.

Toujours selon ce rapport, les principales raisons expliquant ces échecs sont :

- Un manque d'implication du client dans les processus,

- Une mauvaise vision des processus impliquant de mauvaises décisions,

- Une mauvaise gestion des exigences ou l'acceptation d'exigences irréalisables,

- Un manque de réalisme sur l'adéquation entre les ressources disponibles et la taille des projets.

À la lumière de ces études, il apparait que seul le choix d'une méthodologie claire et cohérente permettrait de garantir la qualité du produit, c'est à dire sa conformité aux spécifications établies avec le client, dans un temps et à un coût raisonnable. Une telle méthodologie permettrait non seulement de guider et de borner le cycle de développement du produit, mais également de gérer les risques de manière efficace et d'éviter ainsi les échecs liés à de mauvais choix comme cela se produit encore bien souvent.

Dans le cadre du codesign, le développement de produits complexes mêlant du matériel et du logiciel est un processus généralement long et coûteux faisant interagir un certain nombre de compétences, de langages ou d'outils. De fait, cela représente une activité compliquée, qui, si elle est mal gérée, peut amener d'une part à devoir renégocier les délais et les budgets avec le donneur d'ordre, et peut d'autre part générer des défauts de conception potentiellement catastrophiques (crashs aériens par exemple).

Les difficultés rencontrées dans l'élicitation des processus de codesign proviennent essentiellement de la gestion des interactions entre les parties prenantes du processus. En effet, la profusion des métiers, des langages et des

outils utilisés dans les développements de tels systèmes est source de beaucoup d'incompréhensions et d'erreurs. Aussi, une image classiquement utilisée pour illustrer ce propos est l'image de la tour de Babel (figure 2.8) : la tradition judéo-chrétienne raconte que le roi Nemrod voulait construire une tour assez haute pour côtoyer le divin mais que Dieu, ne le voyant pas du même œil, introduisit plusieurs langues afin que les hommes ne se comprissent plus et que la construction soit abandonnée. Dans le domaine de l'ingénierie des processus, cette allégorie souligne le risque de voir un projet échouer quand les différents métiers impliqués ne parlent que le seul jargon de leur discipline.

FIGURE 2.8 – Allégorie de la tour de Babel

La compréhension des attentes de chacun favorise les bonnes prises de décision et il est important de fluidifier les communications à travers une culture d'entreprise commune. Dans les pratiques actuelles, les communications entre les différents métiers se matérialisent généralement par des échanges d'artéfacts de différentes natures (documentation, code sources, schémas) et les efforts déployés pour maintenir de l'ensemble des données est généralement considérable et coûteux.

Ainsi, les efforts pour améliorer la productivité et la qualité des processus ont été à la source de l'avènement d'une nouvelle discipline : l'ingénierie des processus. Cette discipline a pour objectif de rationaliser ce qui était auparavant de l'ordre de l'intuition et permettre ainsi de répondre aux problèmes posés par la maîtrise des processus. Le but recherché par les travaux autour

de la formalisation des processus est leur rationalisation. À travers ce terme, il faut entendre l'ajout de propriétés garantissant de manière sûre et reproductible la construction de produits conformes aux attentes des clients. Par ailleurs, la satisfaction de ces propriétés est au cœur de la maturité des processus telle que définie par le CMMI [CKS03] et constitue un pari à relever par l'approche dirigée par les modèles.

La rationalisation des processus passent par leurs formalisations à travers des notations adaptées possédant une sémantique clairement définie. Bien évidemment, les détails de la capture des processus de développement dépendent du domaine visé. Par exemple, dans le domaine du développement logiciel, l'auteur de [Mad91] expose les détails pertinents devant obligatoirement être représentés dans les modèles de processus de développement logiciel :

- Les étapes du processus,

- Les responsabilités,

- Les entrées/sorties des activités,

- Les conditions d'activation/terminaison d'une activité (pré/post conditions),

- L'état d'un artéfact avant, pendant et après l'exécution d'une activité,

- L'ordonnancement des activités (séquencement, parallélisation),

- etc.

Ainsi, ces représentations permettent :

- Une meilleure maîtrise des processus intellectuels de conception et d'analyse par l'identification claire des activités, des artefacts d'entrée/sortie ou des responsabilités,

- L'assurance de la qualité des produits en adéquations avec l'amélioration des processus,

- Une gestion optimisée de l'utilisation des ressources dans l'espace et dans le temps comprenant un ordonnancement optimal des activités,

- Une amélioration continue des processus de développement par des analyses statiques ou dynamique grâce à l'exploitation des métriques collectées lors de précédentes exécutions,

- La vérification systématique de la cohérence et de la correction des processus au regard des objectifs à atteindre,

- L'automatisation des tâches routinières par leurs expressions en langage compréhensible par les machines,

- $-\,$  Une meilleure maîtrise de la complexité et du passage à l'échelle.

Les apports de l'ingénierie des processus ont surtout été démontrés dans

le domaine du développement logiciel [GMP+94, Mad91] et je suis convaincu que l'ingénierie des processus peut être étendue au processus de codesign avec le même succès. C'est ce que je m'efforcerai de montrer dans le reste de ce document.

#### 2.3.3 Apports de l'IDM

L'ingénierie des modèles (IDM) est un paradigme basé sur l'utilisation intensive de modèles et promouvant la séparation des préoccupations afin de mieux faire face à la complexité de la conception et de l'analyse des systèmes d'information. Dans l'IDM, les modèles sont au cœur des processus de développement car ils offrent des facilités pour la représentation et l'échange d'informations sur les caractéristiques pertinentes des systèmes étudiés. L'utilisation de modèles permet notamment de :

- Améliorer de manière significative la communication entre les différents métiers impliqués dans les développements,

- Fournir différents points de vue des systèmes étudiés (SUS System Under Study) suivant les préoccupations adressées,

- Favoriser les processus d'analyses par la représentation des SUS à différents niveaux d'abstraction,

- Traiter les problèmes de portabilité et d'interopérabilité par la séparation des aspects métiers et technologiques,

- Capitaliser les expertises à travers les transformations de modèles et réduire les points de rupture technologiques,

- Automatiser un maximum de tâches routinières (analyses, codage, documentation, etc.).

L'idée principale des approches IDM est que l'on peut utiliser des modèles pour représenter les systèmes étudiés ainsi que tous les aspects liés au développement d'un système, tant techniques que managériales. Par exemple, la difficulté de la mise en place d'un processus formalisé prenant en charge le respect des standards et la conformité aux différentes normes provient de la lourdeur et du surcoût que cela engendre. En adoptant une approche IDM, on peut envisager d'automatiser l'ensemble du processus par l'identification claire de toutes les étapes de conception et d'analyse, des méta-modèles et des règles de transformations pour passer d'une étape à une autre.

En effet, dans la mesure où les modèles et les transformations sont au cœur de la définition de l'ingénierie des modèles, ils sont à même de capitaliser les savoir-faire de l'entreprise. Mieux, ils peuvent être utilisés pour :

- gérer les interactions entre les parties prenantes du processus,

- gérer le cycle de vie des produits,

- évaluer les risques et de mettre en œuvre les actions de correction quand cela est nécessaire.

Par ailleurs, selon l'auteur de [Rol98], un processus de développement d'un système d'information peut être vu comme un chemin allant d'un point initial (expression des exigences) jusqu'au point final (produit final) en passant par les différentes positions intermédiaires (produits intermédiaires). Le passage d'un point à un autre correspond alors à une transformation.

Ainsi, l'approche IDM répond très clairement aux problématiques des processus de développement certifiables par le passage d'un monde informel, basé sur des documents de référence décrivant les règles permettant de gérer le processus de développement, à un monde formel où on réifie ces règles pour les incorporer dans des outils par l'utilisation de langages permettant de capturer les caractéristiques pertinentes du système en étude. Mais alors, les langages choisis doivent réifier les concepts nécessaires à la bonne conduite des activités de conception ou d'analyse du processus de développement. Dans les sections suivantes, nous présentons succinctement les langages de modélisation SPEM et MARTE que nous avons utilisés dans nos expérimentations et qui ont servi de base à nos contributions.

#### **SPEM**

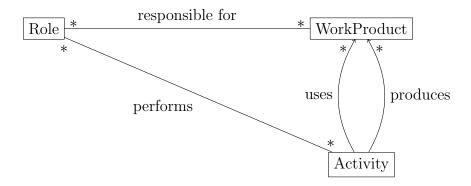

SPEM est un langage permettant de décrire des processus de développement système ou logiciel par un ensemble de notations graphiques. Il est standardisé par l'OMG sous la forme d'un méta-modèle et d'un profil UML. La définition de ce langage est basée sur le principe qu'un processus de développement est régi par la collaboration d'entités abstraites (process roles) qui effectuent des opérations (activities) sur des entités concrètes (work products) (figure 2.9). À la manière de la norme ISO 12207 dont elle s'inspire, cette spécification a été écrite pour supporter un large éventail de processus de développement système ou logiciel.

En bref, le langage SPEM est organisé autour de 7 paquetages dont nous donnons une rapide description dans les lignes qui suivent. Le paquetage *Core* regroupe les concepts abstraits de base du langage. Il offre notamment aux méthodologistes les mécanismes d'extension permettant l'addition de nou-

FIGURE 2.9 – SPEM, concepts de base

veaux types. Le paquetage Process Structure regroupe les définitions de base pour la représentation des processus (activités, rôles, artéfacts). Le paquetage Process Behavior offre les mécanismes de mise en relation des activités et permet leur spécification comportementale par la réutilisation des définitions des concepts d'UML. Le paquetage Managed Content définit les mécanismes permettant la gestion et la documentation des processus. La justification de ce paquetage est que, bien souvent dans la pratique, il est plus important de posséder une méthodologie bien documentée qui capitalise l'ensemble des bonnes pratiques qu'un modèle précis. Le paquetage Method Content permet de construire des bases de connaissances réutilisables et indépendantes du cycle de vie des processus. Il participe à la séparation entre les notions de méthodologie et de processus. Le paquetage Process With Methods fait le lien entre les méthodes et les processus. Enfin, le paquetage Method Plugin traite la gestion des processus à travers la notion de librairie de processus configurable mais aussi, et surtout, à travers la notion de composant de processus.

Les principaux cas d'utilisation du langage SPEM sont :

- Le support pour la représentation et la gestion de librairies de méthodologies réutilisables permettant de capitaliser les bonnes pratiques à l'intention des futurs développements. Cela englobe la définition de guides méthodologiques ou de procédures internes. Tous ces éléments représentent autant de bases de connaissances dont la représentation standard facilite la réutilisation ou l'échange.

- Le support pour la gestion des processus offre les mécanismes d'application des méthodes aux processus de développement incluant de

- possibles adaptations.

- Le support de la configuration des méthodes et des processus fournit la prise en compte du contexte des organisations et des affaires dans la configuration des méthodes et des processus.

- Le support pour l'élicitation des processus de développement guidant la mise en œuvre des modèles et son impact sur les pratiques quotidiennes dans la vie de l'entreprise.

Enfin, les principaux concepts définis par SPEM sont résumés dans le tableau 2.1.

| Concept               | Description                                              |  |  |

|-----------------------|----------------------------------------------------------|--|--|

| process performer     | permet de définir un responsable pour une activité       |  |  |

|                       | donnée                                                   |  |  |

| guidance              | fournit des informations plus détaillées à l'usage des   |  |  |

|                       | acteurs. Il peut s'agir de guides, de référentiels, de   |  |  |

|                       | techniques, de métriques, de méta-modèles,               |  |  |

| work product and work | artefact pouvant être produit, consommé, transformé      |  |  |

| product kind          | par un élément actif et son type.                        |  |  |

| work definition       | description d'un travail réalisé pendant le processus.   |  |  |

|                       | Il peut s'agir de la description d'une phase, d'une ité- |  |  |

|                       | ration, d'une activité décomposée en étapes,             |  |  |

| process component     | description d'une partie consistante d'un processus      |  |  |

|                       | pouvant être réutilisée.                                 |  |  |

Table 2.1 – Principaux concepts de SPEM

#### **MARTE**

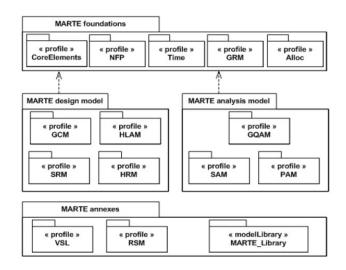

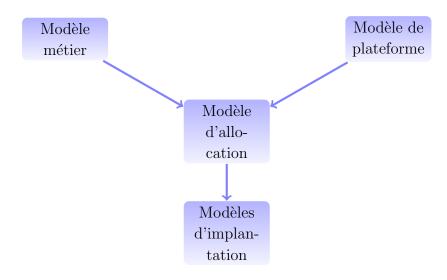

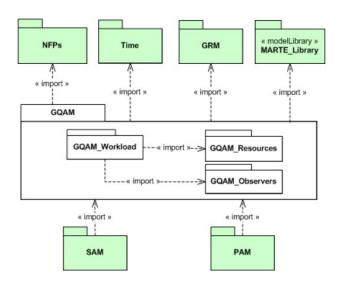

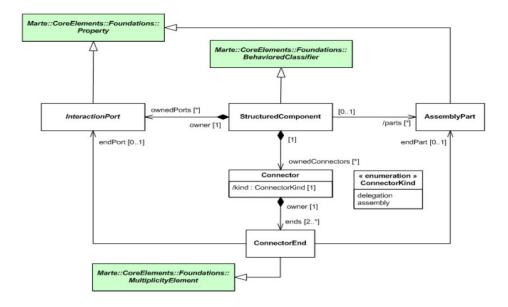

Le profil UML MARTE est un profil qui traite la modélisation et l'analyse de systèmes embarqués temps réel. Le langage est né suite à une RFP (Request For Proposal) de l'OMG. Le profil MARTE avait notamment pour objectif de combler les lacunes du profil standard SPT (Scheduling, Performance and Time) mais aussi de réutiliser et de simplifier les concepts présents dans d'autres profils. Par exemple, les notions de qualité de service présents dans MARTE sont issues du profil standard QoS&FT (Quality of Service and Fault Tolerance). Le profil MARTE est construit autour de 3 paquetages (2.10) favorisant la séparation des préoccupations :

- le paquetage "foundation" fournit les bases du langage qui traitent la modélisation des propriétés non-fonctionnelles, du temps, des ressources génériques et des allocations,

- le paquetage "design" permet de modéliser des plateformes d'exécution matérielles ou logicielles à différents niveaux d'abstraction,

- le paquetage "analysis" fournit les mécanismes permettant d'annoter les modèles à des fins d'analyse. Il fournit les concepts génériques pour couvrir tout type d'analyse et couvre nativement des analyses spécifiques comme les analyses d'ordonnançabilité ou de performance.

FIGURE 2.10 – Architecture du langage MARTE

#### En bref, le profil MARTE permet :

- une modélisation du temps plus fine (temps causal, continu ou discret),

- une modélisation des plateformes et leurs services à différents niveaux d'abstraction,

- une modélisation des allocations spatiales ou temporelles de modèles métiers sur des modèles de plateforme.

Enfin, le profil MARTE offre des mécanismes permettant d'annoter les modèles à des fins d'analyse par l'introduction, entre autres, d'un langage de spécification de valeur (VSL – Value Specification Language). Le langage VSL fournit une syntaxe concrète claire permettant de saisir les propriétés nonfonctionnelles des systèmes (poids, utilisation des ressources, consommation d'énergie, etc.) nécessaires aux analyses.

#### 2.4 Les défis à relever

Afin de rester compétitives, les entreprises du marché des SoCs ont pour objectifs de réduire le temps de mise sur le marché, des coûts de production et d'exploiter au maximum les apports de la technologie. Aussi, dans le contexte de la loi de Moore, plusieurs défis sont à relever :

- La maîtrise des processus de conception depuis la capture des exigences jusqu'au déploiement du produit, sa maintenance et son retrait,

- La réduction des temps de conception par l'adoption d'approches de plus haut niveau préconisant la séparation des préoccupations,

- La réduction des coûts liés aux outils, aux supports ou à l'application des standards,

- La gestion des risques liés à l'évolution du besoin, des technologies ou des standards.

Nous avons vu que pour traiter ces problèmes, les approches classiques ne peuvent être envisagées. Aussi, il existe plusieurs solutions proposées par la communauté de l'ESL. Bien que ces techniques apportent effectivement un gain de productivité, je montrerais dans la suite de ce document que l'utilisation de modèles permet une meilleure montée en abstraction et une meilleure séparation des préoccupations. En particulier, nous verrons que les modèles apportent plus de flexibilité dans la conception et l'analyse de SoCs.

La maîtrise des processus pourrait être grandement améliorée si leurs objectifs étaient clairement établis et s'il existait des mécanismes permettant d'encapsuler, de partager et d'appliquer de manière systématique les savoirfaire. Grâce aux grandes avancées faites dans le domaine de la modélisation ces dernières années, je pense que les modèles peuvent apporter des réponses aux problèmes de maîtrise et de maturation des processus.

Dans cette thèse, je propose d'utiliser les modèles afin de gérer les activités et les artefacts de l'ESL. Cette approche permet une meilleure maîtrise des processus de codesign et fournit aux développeurs un cadre formel les guidant dans leurs activités de conception et d'analyse. Entre autres, je préconise l'utilisation de modèles et de transformations afin de décharger les développeurs des activités fastidieuses telles que la documentation ou le codage. Par ailleurs, nous verrons que ce travail de formalisation est d'autant plus important quand les langages de modélisation utilisés possèdent parfois un champ d'application très large. Par exemple, le langage MARTE offre de nombreux concepts couvrant la conception et l'analyse des systèmes temps réel embar-

qués. En comptabilisant le nombre de concepts dans UML additionnés à ceux de MARTE, on arrive à plus de 400 concepts. Il est alors important de définir une méthodologie de conception qui indique très clairement quels concepts utiliser pour couvrir telle ou telle activité.

Aujourd'hui, avec l'avènement de l'ingénierie dirigée par les modèles, une étape supplémentaire peut être franchie par l'automatisation complète du processus de développement supporté par un seul et même outil. Le processus de développement, à la lumière de l'ingénierie dirigée par les modèles, est alors vu comme une suite de transformation de modèles qu'il est possible d'automatiser. La modélisation du processus permet ainsi ce qu'il était impossible de faire hier : générer des outils taillés sur mesure pour une organisation donnée.

#### 2.5 Conclusion

Dans ce chapitre, j'ai évoqué les principales difficultés rencontrées aujourd'hui dans l'élicitation des processus de codesign. J'ai passé en revue quelques une des solutions proposées par l'ESL afin de gérer les risques liés aux développements de systèmes sur puce. Puis, j'ai fait une présentation rapide de l'ingénierie des modèles et de l'ingénierie des processus pour améliorer la définition des processus. Ces présentations nous permettront de mieux comprendre les apports de l'état de l'art présentés dans le chapitre suivant.

## Chapitre 3

## État de l'art

## Sommaire

| 3.1        | Introduction                         |                                                    | 36        |

|------------|--------------------------------------|----------------------------------------------------|-----------|

| <b>3.2</b> | L'ingénierie Dirigée par les Modèles |                                                    |           |

| 3.3        | IDM                                  | I et codesign                                      | <b>40</b> |

|            | 3.3.1                                | Modélisation des plateformes d'exécution           | 41        |

|            | 3.3.2                                | Prise en compte de l'hétérogénéité des plateformes | 50        |

|            | 3.3.3                                | Modélisation des allocations et des analyses       | 52        |

| 3.4        | IDM                                  | I et processus de développement                    | <b>56</b> |

|            | 3.4.1                                | Quelques définitions                               | 56        |

|            | 3.4.2                                | Modélisation des processus                         | 57        |

|            | 3.4.3                                | Élicitation des processus à travers l'exécution de |           |

|            |                                      | modèles                                            | 59        |

|            | 3.4.4                                | Les composants de processus                        | 62        |

| 3.5        | Con                                  | clusion                                            | 65        |

#### 3.1 Introduction

Ce chapitre présente quelques travaux significatifs basés sur l'ingénierie des modèles pour résoudre les problèmes soulevés dans le chapitre précédent. Ce travail de synthèse me permet de positionner mes contributions dans l'état de l'art. Au préalable, je fais une rapide présentation de l'ingénierie des modèles et de ses principes. Cette présentation permettra de mieux comprendre les apports de l'IDM pour organiser les activités de l'ESL et pour gérer les processus de développement conjoint dans leur ensemble.

## 3.2 L'ingénierie Dirigée par les Modèles

L'ingénierie dirigée par les modèles est un paradigme basé sur l'utilisation intensive de modèles et promouvant la séparation des préoccupations afin de mieux faire face à la complexité de la conception et favoriser l'analyse des systèmes d'information.

La définition de l'IDM est basée sur trois notions clefs [mF04] : les notions de système, de modèle et de transformation. Il n'existe actuellement pas de consensus sur la définition de ces notions, ni même sur la nature de leur relation. Toutefois, je me propose ici de choisir une définition pour chacune de ces notions dans les paragraphes suivants.

Concernant la notion de système, la définition choisie est celle proposée par l'IEEE (Standard Dictionary of Electrical and Electronic Terms) :

"A system is a combination of components that act together to perform a function not possible with any of the individual parts"

Cette définition me semble pertinente car elle permet de mieux appréhender la complexité des systèmes par une décomposition structurelle / comportementale du système en sous-systèmes moins complexes : c'est le principe même de l'analyse. Dans cette définition, le comportement global du système est réalisé par les interactions entre les comportements de ses sous-systèmes. Cette définition fait ressortir trois notions orthogonales importantes déjà mentionnée dans le chapitre précédent : la structure, le comportement et la communication.

Concernant la notion de modèle, la définition choisie est celle proposée dans [Jan04]:

"A model is a simplification of another entity, which can be a physical thing or another model. The model contains exactly those characteristics and properties of the modeled entity that are relevant for a given task. A model is minimal with respect to a task if it does not contain any other characteristics than those relevant for a task"

Un modèle décrit un système quel qu'il soit, y compris un autre modèle. Par décrire, il faut entendre abstraire ou simplifier. Il ne s'agit pas de décrire de manière exhaustive un système complexe mais plutôt d'en faire ressortir les caractéristiques intéressantes pour mener des analyses pertinentes dans la résolution d'un problème donné. Il existe différents types de modèles (mathématique, physiques, fonctionnels, etc.) et chaque type de modèle permet de résoudre une famille de problèmes particuliers. Par ailleurs, il est généralement nécessaire d'avoir recours à plusieurs modèles (points de vue) pour permettre la construction correcte d'un système.

Le nombre et le type de modèle nécessaires à la réalisation d'un système, de même que la question de la pertinence d'un modèle sont difficiles à établir. Toutefois, dans [Sel03], des éléments de réponses sont donnés. Selon l'auteur, un modèle ne peut être pertinent que si il possède les caractéristiques suivantes :

- il supporte l'abstraction, dans le sens où il ne met en exergue que les aspects nécessaires et suffisants aux analyses du système étudié,

- il est exprimé dans une forme assez compréhensive pour être comprise de manière intuitive,

- il doit être précis, dans le sens où il représente fidèlement les aspects réel du système étudié et il proscrit les ambigüités,

- il doit être moins coûteux et plus facile à développer que le système qu'il représente.

Dans le cadre de l'ingénierie des modèles, l'expression d'un modèle passe par l'utilisation de langages permettant de capturer les caractéristiques pertinentes du système en étude. Les langages choisis doivent alors réifier les concepts nécessaires à la bonne conduite des activités de conception ou d'analyse des processus de développement.

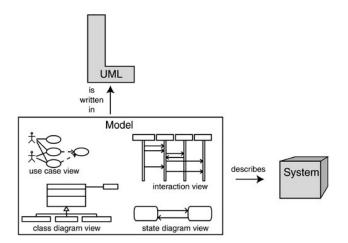

Par exemple, le langage UML (Unified Modeling Language [OMG05b]) est le langage de modélisation généraliste et extensible proposé par l'OMG. Il représente la synthèse des techniques d'analyse et de conception de systèmes à logiciel prépondérant depuis les années 70. Il intègre des mécanismes apportés

FIGURE 3.1 – Utilisation d'UML pour la modélisation de systèmes

par les approches objets (encapsulation, héritage, polymorphisme), et permet en particulier l'usage des patrons de conception [GHJV95] pour la résolution de problèmes récurrents.

Le langage UML est essentiellement utilisé dans les activités d'analyse permettant de mieux comprendre le besoin fonctionnel (figure 3.1). Il est ensuite complété par différents profils pour la gestion d'aspects spécifiques (exigences, qualité de service, propriétés non-fonctionnelles, plateformes, etc.). Par exemple, nous verrons dans le chapitre 5 de quelle manière le profil MARTE est utilisé dans la méthodologie de conception de SoC pour représenter les plateformes, les propriétés non-fonctionnelles ou les allocations.

Les avantages de l'utilisation de modèles dans les processus de développements logiciels sont nombreux et ont été démontrés à travers plusieurs expérimentations. Ils permettent notamment :

- D'améliorer de manière significative la communication entre les différents métiers impliqués dans les développements,

- De fournir différents points de vue des systèmes étudiés (SUS System Under Study) suivant les préoccupations adressées,

- De favoriser les processus d'analyses par la représentation des SUS à différents niveaux d'abstraction,

- De traiter les problèmes de portabilité et d'interopérabilité par la séparation des aspects métiers et technologiques,

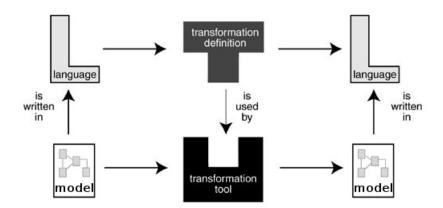

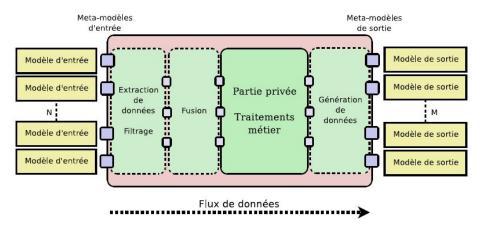

Enfin, alors que les modèles permettent de saisir les caractéristiques pertinentes des systèmes en étude, les transformations représentent un ensemble de spécifications non-ambigües (règles de transformation) décrivant la manière de créer un modèle (source) à partir d'un autre (cible). Dans [KWB03], les auteurs définissent les transformations, les définitions de transformation et les règles de transformation comme respectivement :

"A transformation is the automatic generation of a target model from a source model, according to a transformation definition."

"A transformation definition is a set of transformation rules that together describe how a model in the source language can be transformed into a model in the target language."

"A transformation rule is a description of how one or more constructs in the source language can be transformed into one or more constructs in the target language."

FIGURE 3.2 – Transformation de modèles

La figure 3.2 illustre les définitions données ci-dessus : une transformation de modèles est réalisée par un outil de transformation. Il prend en entrée un modèle exprimé dans un langage source et applique des règles de transformation, exprimées dans un langage dédié, afin de générer un nouveau modèle exprimé dans un langage cible. Une transformation peut être endogène (le langage source et le langage cible sont les mêmes) ou exogène (le langage source et le langage cible sont différents).

Associé au standard de modélisation UML, on peut citer le langage QVT (Query View Transformation) [OMG05a], également standardisé par l'OMG, comme langage de référence pour exprimer des transformations, créer des requêtes pour interroger les modèles (à la manière de SQL pour les bases de données) ou créer des vues spécifiques. On retiendra principalement des transformations de modèles qu'elles permettent avant tout de :

- Capitaliser les expertises

- Réduire les points de rupture technologiques,

- Automatiser un maximum de tâches routinières (analyses, codage, documentation, etc.).

### 3.3 IDM et codesign

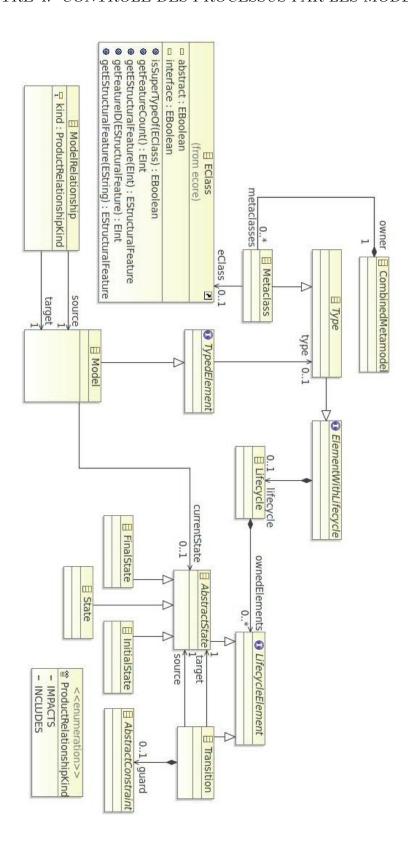

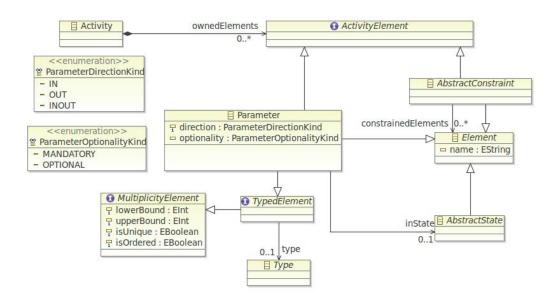

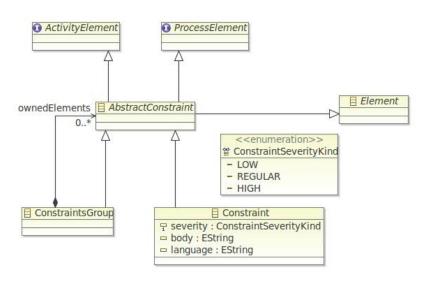

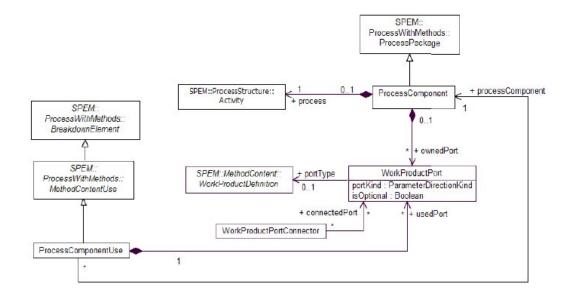

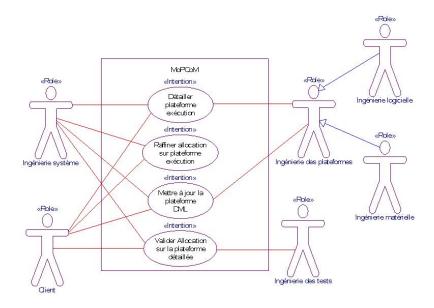

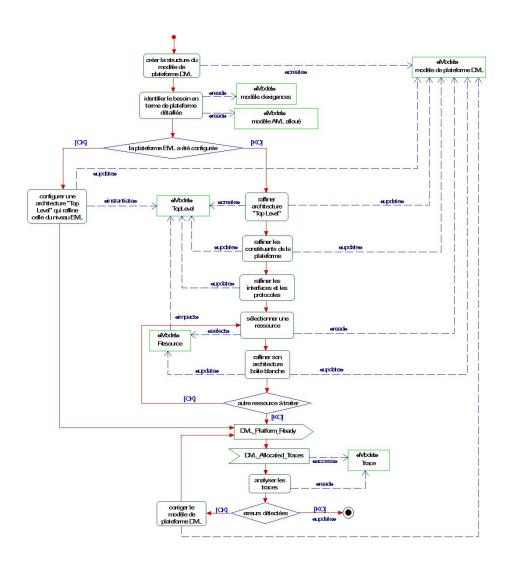

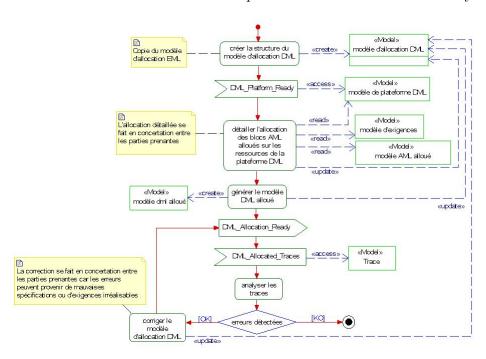

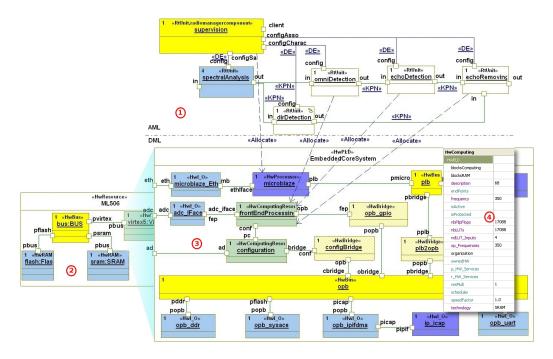

Dans le domaine des systèmes sur puce, la transformation des exigences en un système faisant les bons compromis entre les performances, les coûts ou les délais est un processus très long. Il est constitué de diverses activités de conception et d'analyse. Ce qui caractérise en premier lieu la conception des systèmes sur puce est l'hétérogénéité : hétérogénéité des sous-systèmes, hétérogénéité des activités, hétérogénéité des métiers impliqués, etc. La complexité engendrée par cette hétérogénéité accroît de manière exponentielle les risques. Aussi, l'introduction de niveaux d'abstraction doit permettre de mieux gérer cette complexité et les risques associés [GVNL94].