N° d'ordre : 40580 Ann & 2011

# **THÈSE**

# Présentée à

# L'UNIVERSITE DE LILLE 1 SCIENCES & TECHNOLOGIES

pour obtenir le grade de

# **DOCTEUR DE L'UNIVERSITE**

Sp écialit é: Micro et Nano Technologies, Acoustique et T él écommunications

# Réalisation et caract érisation de dispositifs MOSFET nanom étriques à base de réseaux denses de nanofils verticaux en silicium

# par

# Xiang-Lei HAN

# Soutenance devant la commission d'examen :

Pr ésident Didier Stievenard Rapporteurs Jean-Pierre Raskin

**Christophe Vieu**

Examinateur Filadelfo Cristiano

Directeurs de thèse Guilhem Larrieu

**Emmanuel Dubois**

# Table des matières

| Introduction                                                                                                    | 4 -           |

|-----------------------------------------------------------------------------------------------------------------|---------------|

| Chapitre 1                                                                                                      |               |

| Principe de fonctionnement du transistor MOSFET : et                                                            | ffets         |

| <del>-</del>                                                                                                    |               |

| physiques et parasites li & à la miniaturisation et motiv                                                       | ation de la   |

| thèse.                                                                                                          |               |

|                                                                                                                 |               |

| 1.1 G én éralit ésur le transistor MOSFET.                                                                      | 8 -           |

| 1.1.1 Pr ésentation du transistor MOS.                                                                          |               |

| 1.1.2 Principe de fonctionnement d'un transistor MOS idéal                                                      |               |

| 1.1.3 Caract éristique électrique id éale du transistor MOS                                                     |               |

| 1.1.4 Miniaturisation des composants et effets parasites associ és                                              |               |

| 1.2 Am dioration des performances de MOSFETs                                                                    |               |

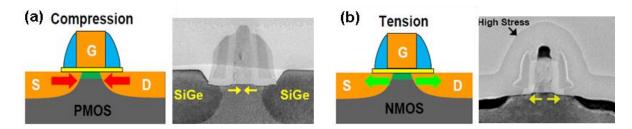

| 1.2.1 Introduction de contraintes m écaniques.                                                                  | 20 -          |

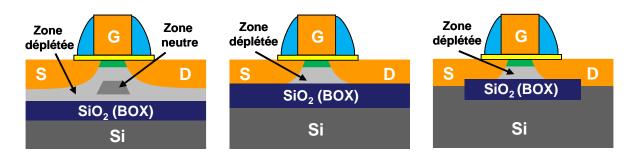

| 1.2.2 Transistors sur substrat SOI.                                                                             | 21 -          |

| 1.2.3 Introduction de grilles m étalliques.                                                                     | 22 -          |

| 1.3 Transistors à base d'architecture non-planaire.                                                             | 23 -          |

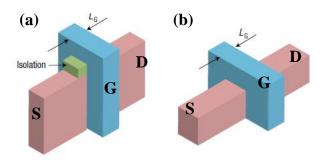

| 1.3.1 Physique du MOSFET à grilles multiples.                                                                   |               |

| 1.3.2 Dispositifs MOSFET à multi-grilles.                                                                       |               |

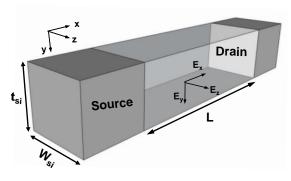

| 1.3.3 Transistors à base de structures unidimensionnelles                                                       | 28 -          |

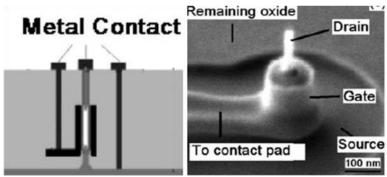

| 1.3.3.1 Les premiers transistors à base de nanofils de silicium                                                 |               |

| 1.3.3.2 Transistors à base de nanofils à grille entourante                                                      | 31 -          |

| 1.3.3.3 Transistors à base de nanofils en multi-canaux à grille ento                                            |               |

| 1.3.3.4 Transistors à base de réseaux de nanofils en structure vertie                                           | cale à grille |

| entourante.                                                                                                     |               |

| 1.3.4 Challenges technologiques associ & à la r éalisation de transistor r éseaux denses de nanofils verticaux. |               |

| 1 Sedua denses de nanoms verticada.                                                                             |               |

| Chapitre 2                                                                                                      |               |

| Réalisation de réseaux ultra denses de nanofils verticau                                                        | ıx en         |

|                                                                                                                 | ix cii        |

| silicium et étude des phénomènes d'effondrement de                                                              |               |

| nanostructures.                                                                                                 |               |

| 2.1 R éalisation du masque pour la fabrication de r éseaux denses de pili                                       |               |

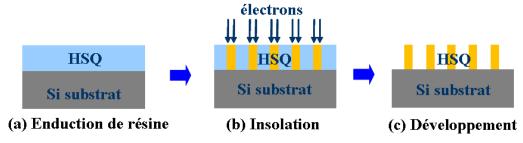

| 2.1.1 La lithographie dectronique.                                                                              |               |

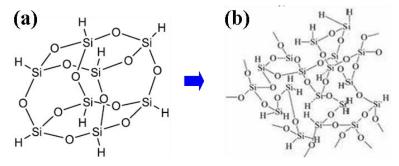

| 2.1.1 La nulographie dectromque.  2.1.2 Le polymère hydrogen silsesquioxane comme résine négative à             |               |

| r solution.                                                                                                     |               |

| i gotaton.                                                                                                      | 31 -          |

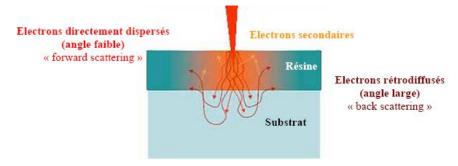

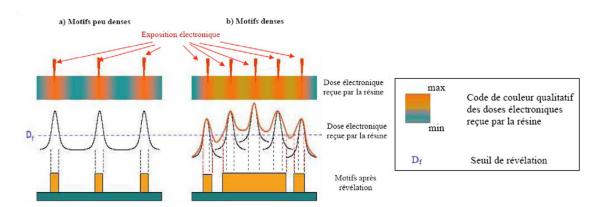

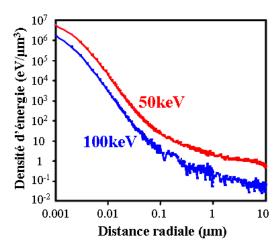

| 2.1.3 Insolation par lithographie dectronique.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | - 52 -                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

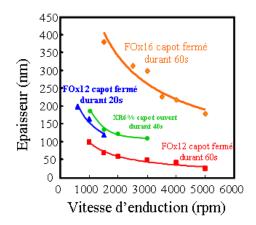

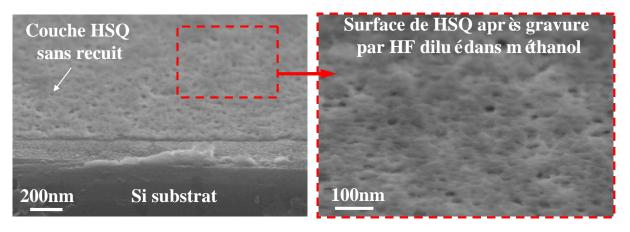

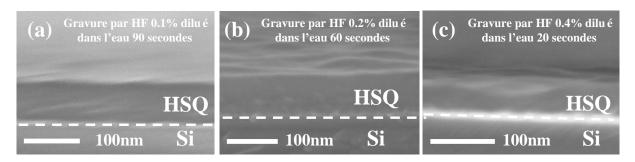

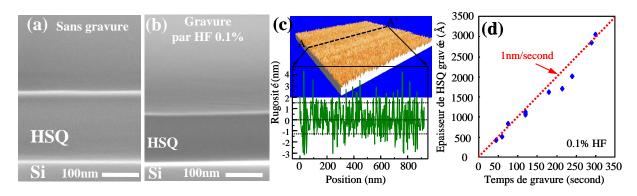

| 2.1.4 R év élation de la r ésine HSQ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - 56 -                                                                                                                             |

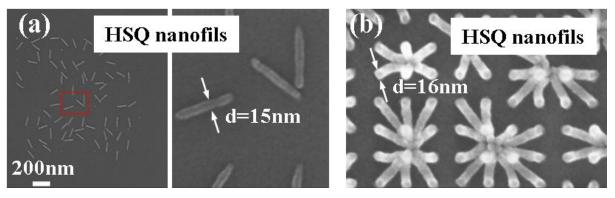

| 2.1.5 D émonstration exp érimentale de motifs en forme de nanoailettes et de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                    |

| nanopiliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - 56 -                                                                                                                             |

| 2.2 Transfert du masque par la gravure ionique r éactive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | - 59 -                                                                                                                             |

| 2.2.1 Gravure des ailettes de silicium isol és.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                    |

| 2.2.1.1 Choix de la chimie de gravure plasma.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | - 59 -                                                                                                                             |

| 2.2.1.2 Impact de paramètres de gravure sur l'anisotropie du profil et ph énor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                    |

| de microtranch é.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                    |

| 2.2.1.3 S dectivit éde la gravure du silicium par rapport au masque de HSQ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                    |

| 2.2.2 Impact de la densit édes motifs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                    |

| 2.2.3 Analyse de l'état du réseau de nanofils verticaux réalisés                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                    |

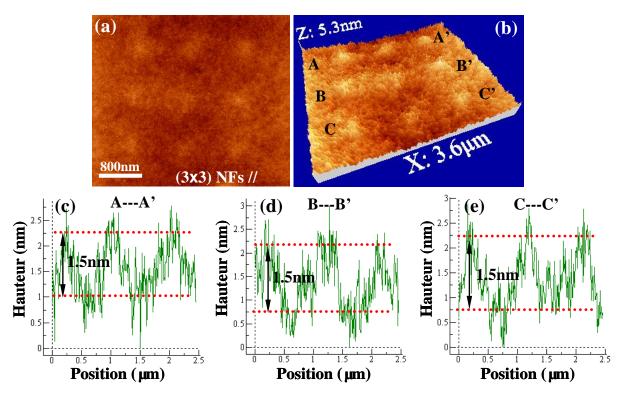

| 2.2.3.1 Reproductibilit édes nanofils verticaux grav és par microscope à force                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                    |

| atomique.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                    |

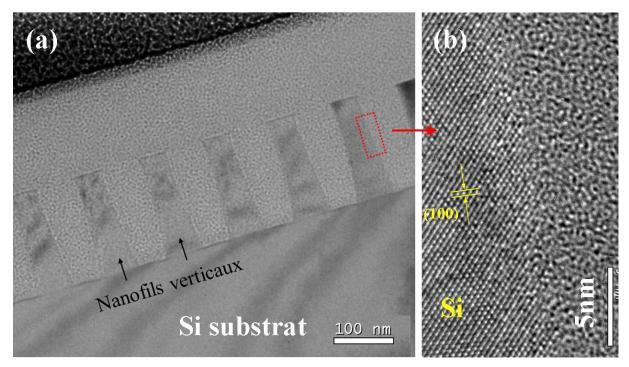

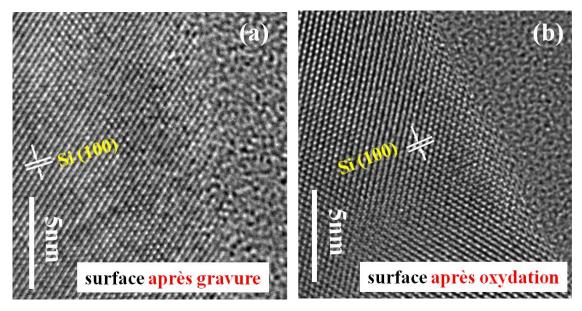

| 2.2.3.2 Etat de surface des flancs des nanofils par microscopie dectronique à                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                    |

| transmission.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                    |

| 2.2.4 Limitation ultime du proc éd étechnologique.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                    |

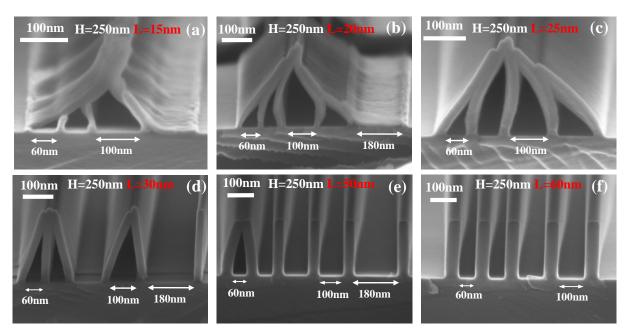

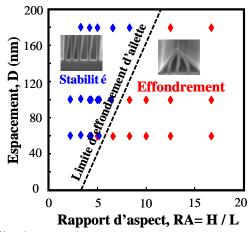

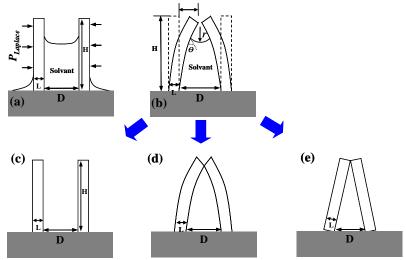

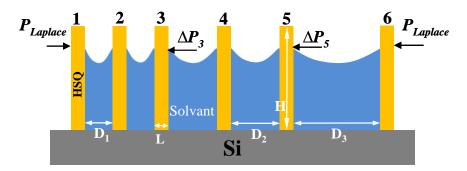

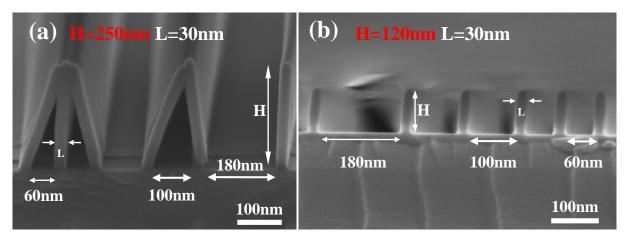

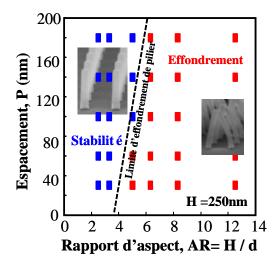

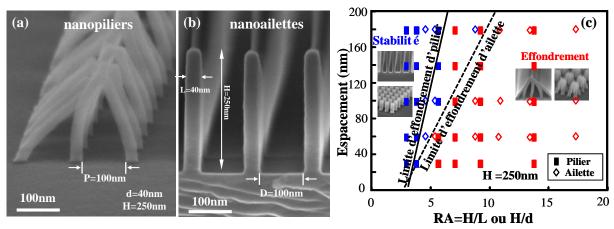

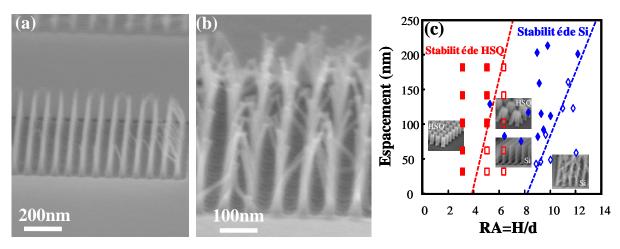

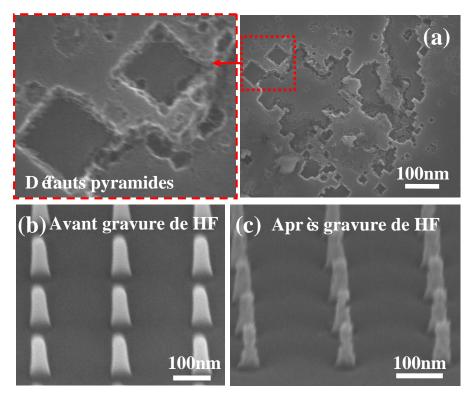

| 2.3 Phénomènes d'effondrements des nanostructures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                    |

| 2.3.1 Phénomènes d'effondrements sur nanostructures de type ailettes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                    |

| 2.3.2 Phénomènes d'effondrements sur nanostructures unidimensionnelles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                    |

| 2.3.3 Impact de la g éom étrie des nanostructures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                    |

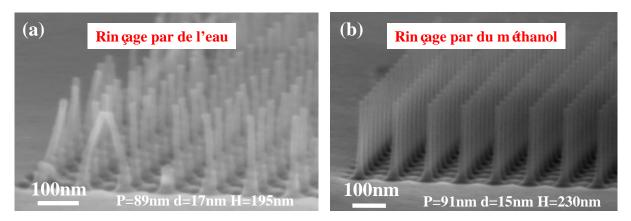

| 2.3.4 Impact de la tension de gurface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                    |

| 2.3.5 Impact de la tension de surface. 2.3.6 R éalisation des nano-masques par l'effet d'effondrement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                    |

| Chapitre 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                    |

| Chapitre 3 Oxydation et siliciuration de nanostructures en silicium.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                    |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                    |

| Oxydation et siliciuration de nanostructures en silicium.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | - 94 -                                                                                                                             |

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                    |

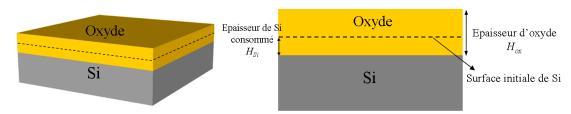

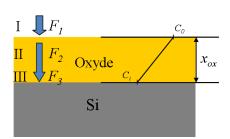

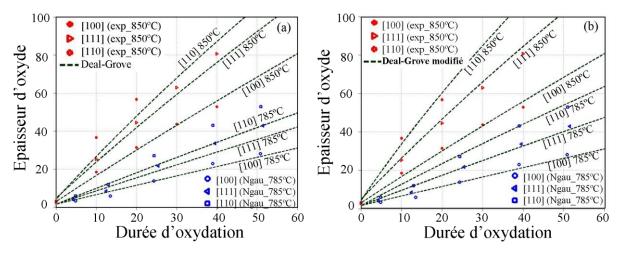

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium.  3.1.1 Croissance de l'oxyde de silicium sur substrat massif.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - 95 -                                                                                                                             |

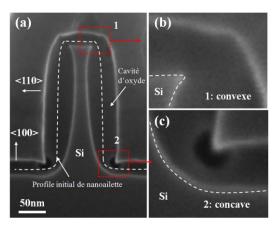

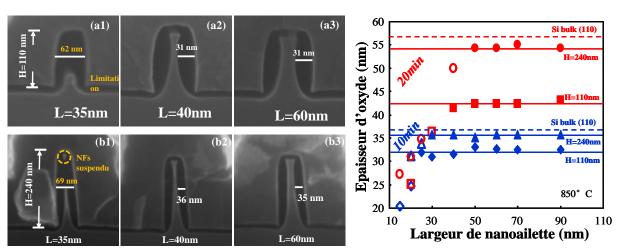

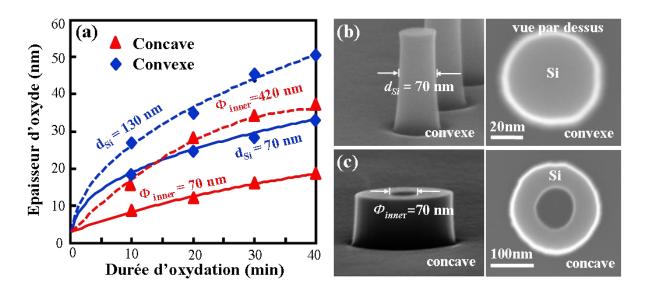

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium.  3.1.1 Croissance de l'oxyde de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - 95 -<br>- 99 -                                                                                                                   |

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium.  3.1.1 Croissance de l'oxyde de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description exp érimentale.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | - 95 -<br>- 99 -<br>- 99 -                                                                                                         |

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium.  3.1.1 Croissance de l'oxyde de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description exp érimentale.  3.1.2.2 Influence de la hauteur de nanoailettes sur la contrainte compressive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | - 95 -<br>- 99 -<br>- 99 -                                                                                                         |

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium.  3.1.1 Croissance de l'oxyde de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description exp érimentale.  3.1.2.2 Influence de la hauteur de nanoailettes sur la contrainte compressive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | - 95 -<br>- 99 -<br>- 99 -<br>101 -                                                                                                |

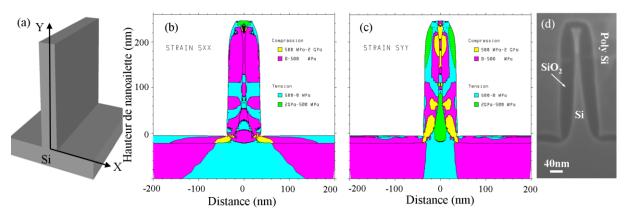

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium.  3.1.1 Croissance de l'oxyde de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description exp érimentale.  3.1.2.2 Influence de la hauteur de nanoailettes sur la contrainte compressive.  3.1.3 Oxydation des nanostructures unidimensionnelles de silicium.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - 95 -<br>- 99 -<br>- 99 -<br>101 -<br>103 -                                                                                       |

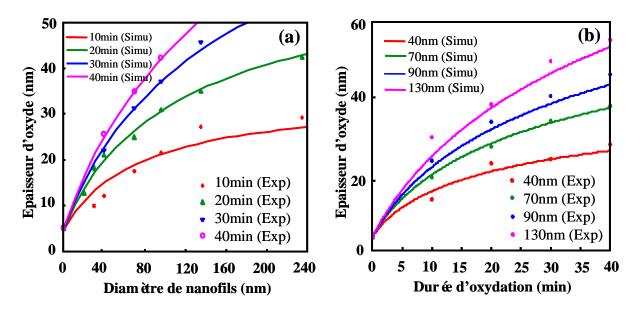

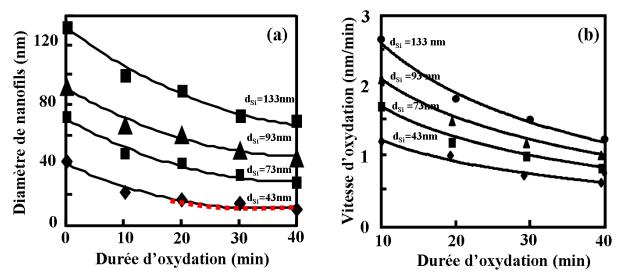

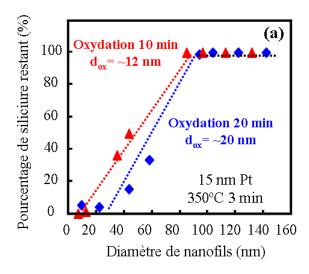

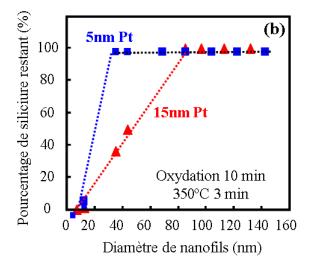

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium.  3.1.1 Croissance de l'oxyde de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description exp érimentale.  3.1.2.2 Influence de la hauteur de nanoailettes sur la contrainte compressive.  3.1.3 Oxydation des nanostructures unidimensionnelles de silicium.  3.1.3.1 Description expérimentale de l'oxydation autolimitée.                                                                                                                                                                                                                                                                                                                                                                                                                                      | - 95 -<br>- 99 -<br>- 99 -<br>101 -<br>103 -<br>103 -                                                                              |

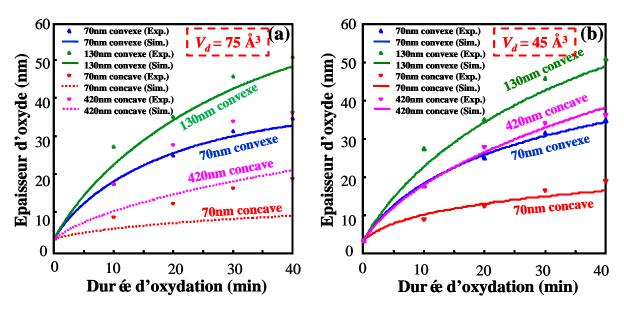

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium.  3.1.1 Croissance de l'oxyde de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description exp érimentale.  3.1.2.2 Influence de la hauteur de nanoailettes sur la contrainte compressive.  3.1.3 Oxydation des nanostructures unidimensionnelles de silicium.  3.1.3.1 Description expérimentale de l'oxydation autolimitée.  3.1.3.2 Analyse des contraintes par simulation.                                                                                                                                                                                                                                                                                                                                                                                     | - 95 -<br>- 99 -<br>- 99 -<br>101 -<br>103 -<br>103 -<br>106 -                                                                     |

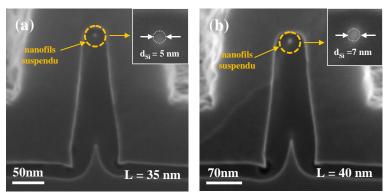

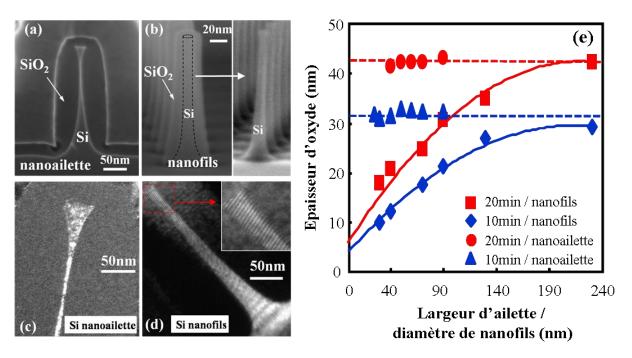

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium.  3.1.1 Croissance de l'oxyde de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description exp érimentale.  3.1.2.2 Influence de la hauteur de nanoailettes sur la contrainte compressive.  3.1.3 Oxydation des nanostructures unidimensionnelles de silicium.  3.1.3.1 Description expérimentale de l'oxydation autolimitée.  3.1.3.2 Analyse des contraintes par simulation.  3.1.3.3 Comparaison d'oxydation des nanoailettes et nanofils de silicium.                                                                                                                                                                                                                                                                                                          | - 95 -<br>- 99 -<br>- 99 -<br>101 -<br>103 -<br>106 -<br>109 -                                                                     |

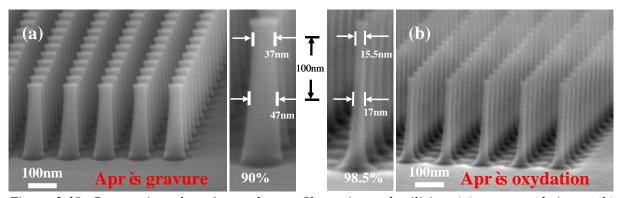

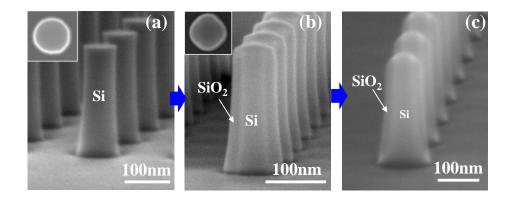

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium.  3.1.1 Croissance de l'oxyde de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description exp érimentale.  3.1.2.2 Influence de la hauteur de nanoailettes sur la contrainte compressive.  3.1.3 Oxydation des nanostructures unidimensionnelles de silicium.  3.1.3.1 Description expérimentale de l'oxydation autolimitée.  3.1.3.2 Analyse des contraintes par simulation.  3.1.3.3 Comparaison d'oxydation des nanoailettes et nanofils de silicium.  3.1.4 Am dioration du profil et de la rugosit éde surface des nanofils par oxydat                                                                                                                                                                                                                       | - 95 -<br>- 99 -<br>- 99 -<br>101 -<br>103 -<br>103 -<br>106 -<br>109 -<br><b>ion</b>                                              |

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium.  3.1.1 Croissance de l'oxyde de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description exp érimentale.  3.1.2.2 Influence de la hauteur de nanoailettes sur la contrainte compressive.  3.1.3 Oxydation des nanostructures unidimensionnelles de silicium.  3.1.3.1 Description expérimentale de l'oxydation autolimitée.  3.1.3.2 Analyse des contraintes par simulation.  3.1.3.3 Comparaison d'oxydation des nanoailettes et nanofils de silicium.  3.1.4 Am dioration du profil et de la rugosit éde surface des nanofils par oxydat auto-limit ée.                                                                                                                                                                                                        | - 95 -<br>- 99 -<br>- 99 -<br>101 -<br>103 -<br>103 -<br>106 -<br>109 -<br><b>ion</b>                                              |

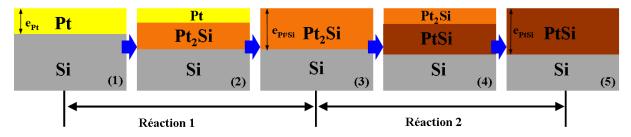

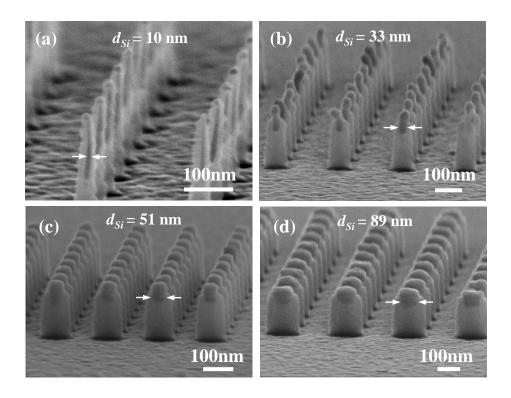

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description expérimentale.  3.1.2.2 Influence de la hauteur de nanoailettes sur la contrainte compressive.  3.1.3 Oxydation des nanostructures unidimensionnelles de silicium.  3.1.3.1 Description expérimentale de l'oxydation autolimitée.  3.1.3.2 Analyse des contraintes par simulation.  3.1.3.3 Comparaison d'oxydation des nanoailettes et nanofils de silicium.  3.1.4 Am dioration du profil et de la rugosit éde surface des nanofils par oxydat auto-limit ée.  3.2 Siliciuration de nanostructures de silicium : l'exemple du siliciure de platine.                                                                                                                                                             | - 95 -<br>- 99 -<br>- 99 -<br>101 -<br>103 -<br>103 -<br>106 -<br>109 -<br><b>ion</b><br>110 -                                     |

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium.  3.1.1 Croissance de l'oxyde de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description exp érimentale.  3.1.2.2 Influence de la hauteur de nanoailettes sur la contrainte compressive.  3.1.3 Oxydation des nanostructures unidimensionnelles de silicium.  3.1.3.1 Description expérimentale de l'oxydation autolimitée.  3.1.3.2 Analyse des contraintes par simulation.  3.1.3.3 Comparaison d'oxydation des nanoailettes et nanofils de silicium.  3.1.4 Am dioration du profil et de la rugosit éde surface des nanofils par oxydat auto-limit ée.  3.2 Siliciuration de nanostructures de silicium : l'exemple du siliciure de platine.                                                                                                                  | - 95 -<br>- 99 -<br>- 99 -<br>101 -<br>103 -<br>106 -<br>109 -<br><b>ion</b><br>110 -                                              |

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description exp érimentale.  3.1.2.2 Influence de la hauteur de nanoailettes sur la contrainte compressive.  3.1.3 Oxydation des nanostructures unidimensionnelles de silicium.  3.1.3.1 Description expérimentale de l'oxydation autolimitée.  3.1.3.2 Analyse des contraintes par simulation.  3.1.3.3 Comparaison d'oxydation des nanoailettes et nanofils de silicium.  3.1.4 Am dioration du profil et de la rugosit éde surface des nanofils par oxydat auto-limit ée.  3.2 Siliciuration de nanostructures de silicium : l'exemple du siliciure de platine.                                                                                                                                                            | - 95 -<br>- 99 -<br>- 99 -<br>101 -<br>103 -<br>106 -<br>109 -<br><b>ion</b><br>110 -<br>112 -<br>113 -                            |

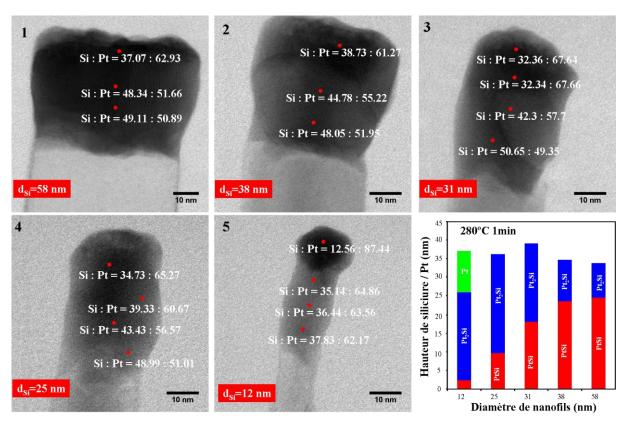

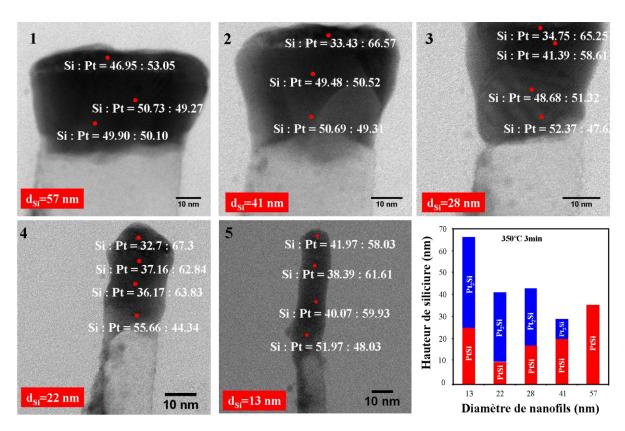

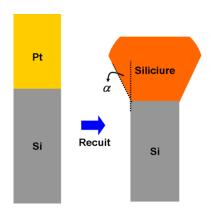

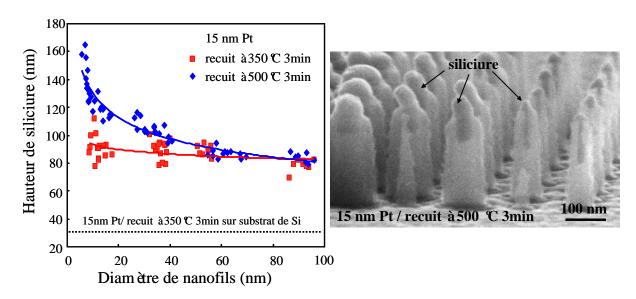

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description exp érimentale.  3.1.2.2 Influence de la hauteur de nanoailettes sur la contrainte compressive.  3.1.3 Oxydation des nanostructures unidimensionnelles de silicium.  3.1.3.1 Description expérimentale de l'oxydation autolimitée.  3.1.3.2 Analyse des contraintes par simulation.  3.1.3.3 Comparaison d'oxydation des nanoailettes et nanofils de silicium.  3.1.4 Am dioration du profil et de la rugosit éde surface des nanofils par oxydat auto-limit ée.  3.2 Siliciuration de nanostructures de silicium : l'exemple du siliciure de platine.  3.2.1 M écanisme de formation du siliciure de platine.  3.2.2 Siliciuration sur nanofils de silicium.                                                     | - 95 -<br>- 99 -<br>- 99 -<br>101 -<br>103 -<br>103 -<br>106 -<br>109 -<br><b>ion</b><br>110 -<br>112 -<br>113 -<br>114 -          |

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description exp érimentale.  3.1.2.2 Influence de la hauteur de nanoailettes sur la contrainte compressive.  3.1.3 Oxydation des nanostructures unidimensionnelles de silicium.  3.1.3.1 Description expérimentale de l'oxydation autolimitée.  3.1.3.2 Analyse des contraintes par simulation.  3.1.3.3 Comparaison d'oxydation des nanoailettes et nanofils de silicium.  3.1.4 Am dioration du profil et de la rugosit éde surface des nanofils par oxydat auto-limit ée.  3.2 Siliciuration de nanostructures de silicium : l'exemple du siliciure de platine.  3.2.1 M écanisme de formation du siliciure de platine.  3.2.2 Siliciuration sur nanofils de silicium.  3.2.3 Siliciuration dans un environnement confin é | - 95 -<br>- 99 -<br>- 99 -<br>101 -<br>103 -<br>106 -<br>109 -<br><b>ion</b><br>110 -<br>112 -<br>113 -<br>114 -<br>120 -          |

| Oxydation et siliciuration de nanostructures en silicium.  3.1 Oxydation de nanostructures de silicium sur substrat massif.  3.1.2 Oxydation de nanostructures bidimensionnelles de silicium.  3.1.2.1 Description exp érimentale.  3.1.2.2 Influence de la hauteur de nanoailettes sur la contrainte compressive.  3.1.3 Oxydation des nanostructures unidimensionnelles de silicium.  3.1.3.1 Description expérimentale de l'oxydation autolimitée.  3.1.3.2 Analyse des contraintes par simulation.  3.1.3.3 Comparaison d'oxydation des nanoailettes et nanofils de silicium.  3.1.4 Am dioration du profil et de la rugosit éde surface des nanofils par oxydat auto-limit ée.  3.2 Siliciuration de nanostructures de silicium : l'exemple du siliciure de platine.  3.2.1 M écanisme de formation du siliciure de platine.  3.2.2 Siliciuration sur nanofils de silicium.                                                     | - 95 -<br>- 99 -<br>- 99 -<br>101 -<br>103 -<br>106 -<br>109 -<br><b>ion</b><br>110 -<br>112 -<br>113 -<br>114 -<br>120 -<br>121 - |

# **Chapitre 4**

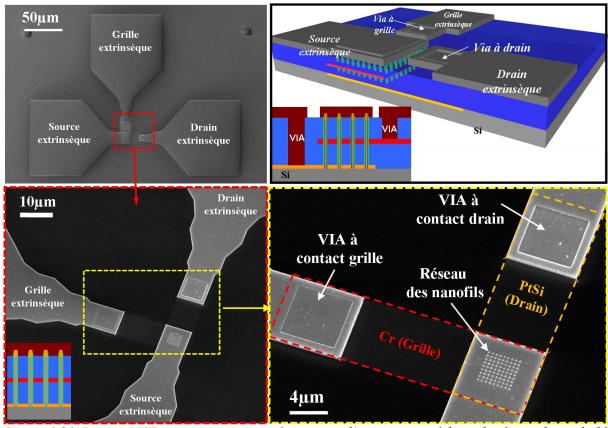

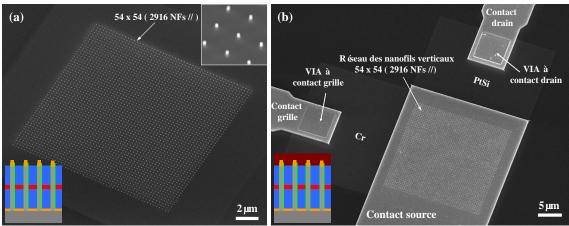

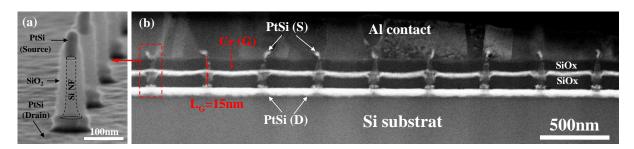

Réalisation et caractérisation électrique de dispositifs à base de réseaux de nanofils verticaux en silicium.

| 4.1 La diode Schottky.                                                                                                     | 132 -   |

|----------------------------------------------------------------------------------------------------------------------------|---------|

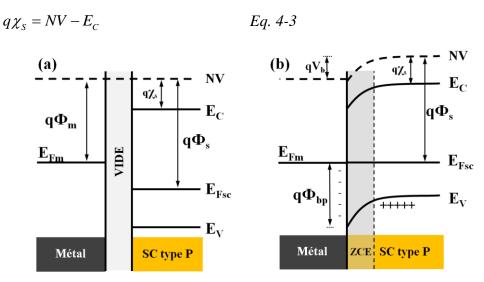

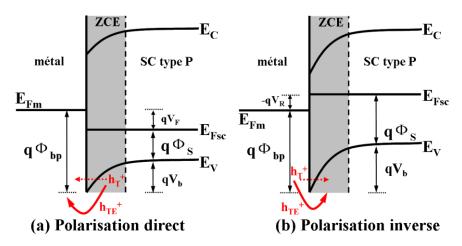

| 4.1.1 La diode Schottky non polaris &                                                                                      |         |

| 4.1.2 La diode Schottky polaris & en direct et inverse.                                                                    |         |

| 4.2 Int égration et caract érisation électrique de r éseaux denses de nanofils ver                                         |         |

| silicium.                                                                                                                  | 134 -   |

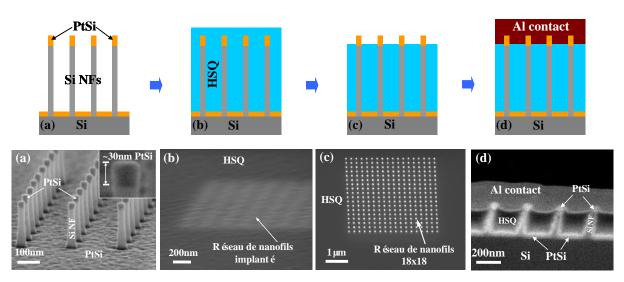

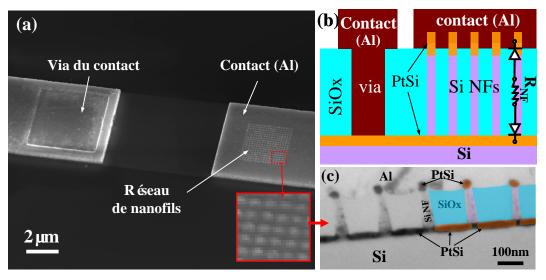

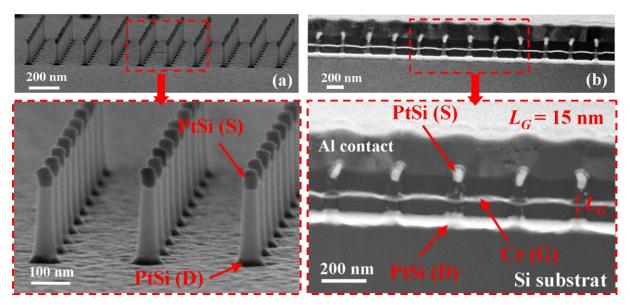

| 4.2.1 Proc éd é de r éalisation de contacts verticaux.                                                                     | 135 -   |

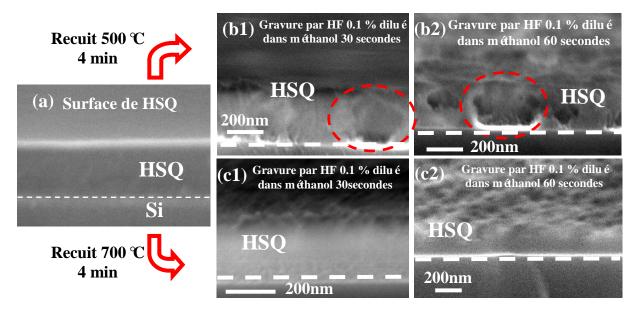

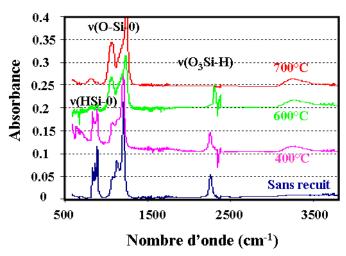

| 4.2.1.1 Technique de planarisation par amincissement d'une couche de l                                                     | _       |

|                                                                                                                            |         |

| 4.2.1.2 R éalisation des contacts m étalliques sur un r éseau de nanofils ve                                               |         |

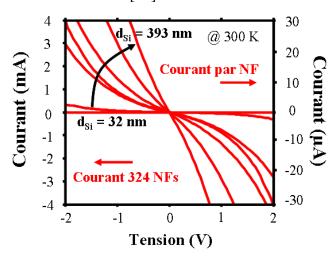

| 4.2.2 Caract érisation dectrique de r éseaux de nanofils verticaux                                                         |         |

| 4.2.2 Caract disation dectrique de l'éseaux de nanoms verticaux                                                            |         |

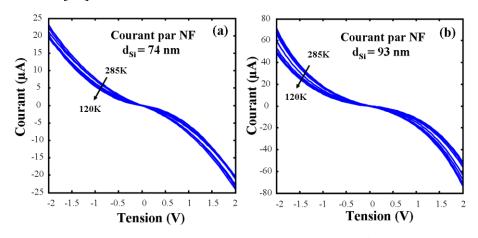

| 4.2.2.2 Variabilit édans un nanofil unique.                                                                                |         |

| 4.2.2.3 Impact de la d épl étion de surface de nanofils sur la conductivit é                                               |         |

| 4.3 Int égration et caract érisation dectrique des transistors à base de réseaux                                           |         |

| de nanofils verticaux de silicium.                                                                                         |         |

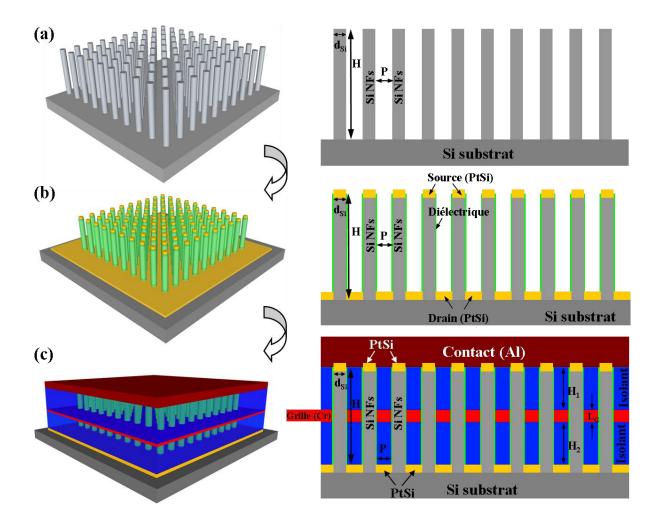

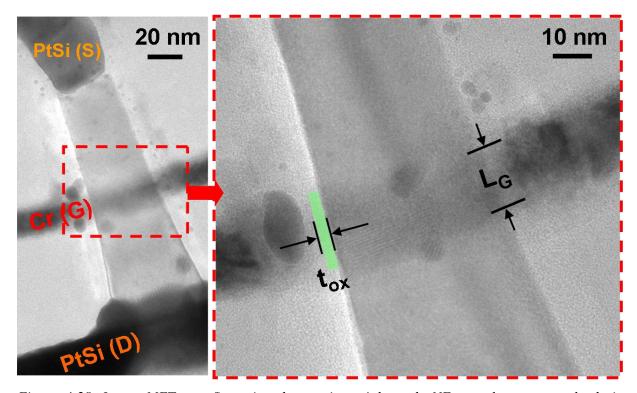

| 4.3.1 Procédé d'intégration des transistors à base de réseaux denses de nar                                                | ofils   |

| verticaux.                                                                                                                 |         |

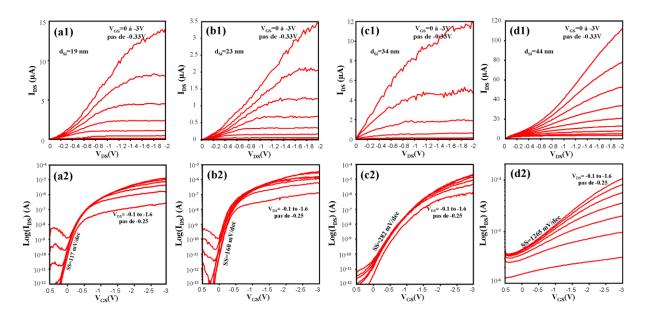

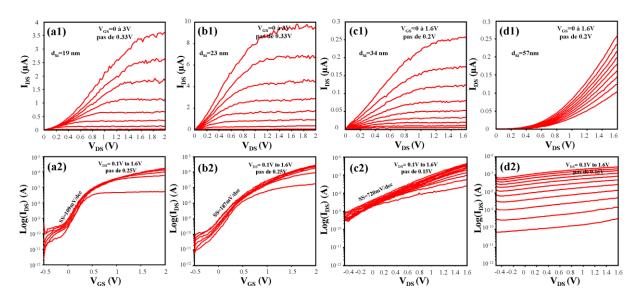

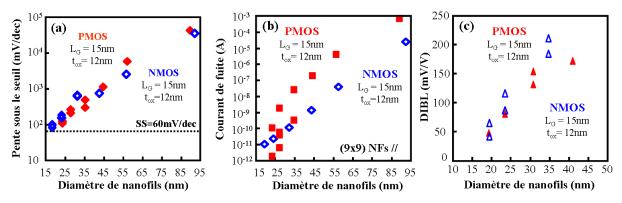

| 4.3.2 Caract érisation dectrique des transistors à base de r éseaux denses de                                              |         |

| verticaux.                                                                                                                 |         |

| 4.3.2.1 Caract érisation dectrique des transistors à base de nanofils verti                                                |         |

| silicium avec couche de di dectrique épaisse.                                                                              |         |

| 4.3.2.2 Caract érisation dectrique des transistors à base de nanofils verti silicium avec une couche de di dectrique fine. |         |

| 4.3.2.3 Am dioration de la performance de transistors par diminution de                                                    |         |

| d'interface.                                                                                                               |         |

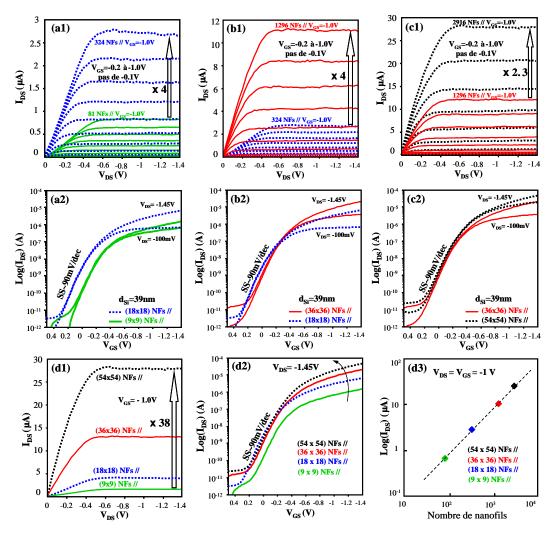

| 4.3.2.4 Corr dation entre le courant d doit éet le nombre de nanofils du r                                                 |         |

|                                                                                                                            |         |

| 4.3.2.5 Etat de l'art des transistors à base de nanofils verticaux                                                         | 161 -   |

|                                                                                                                            |         |

| Conclusions et perspectives                                                                                                | - 165 - |

| Conclusions et perspectives                                                                                                | . 103   |

|                                                                                                                            | 4       |

| Annexe 1 : Proc éd étechnologique                                                                                          | 169 -   |

# Introduction

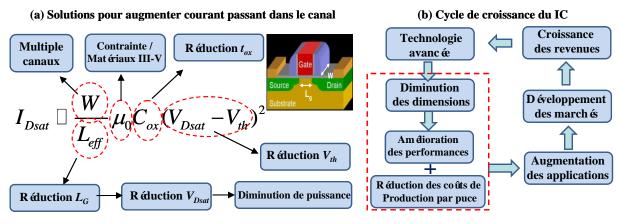

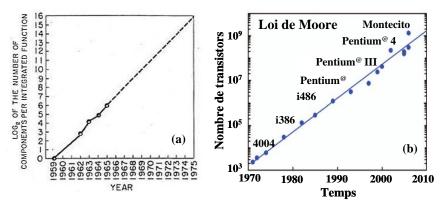

Les produits issus de la micro dectronique sont omnipr sents dans notre vie quotidienne. Elles changent et am diorent notre niveau de vie. La valeur du march é des semiconducteurs en 2010 était d'environ 300 milliards de dollars selon les experts du cabinet d'analyse Gartner. Depuis la premi ère création du microprocesseur 4004 (2300 transistors) en 1971 par l'intreprise Intel, l'industrie du semi-conducteur a permis une véritable révolution dans le traitement de l'information grâce à une évolution technologique fulgurante et la réduction d'échelle des transistors tout en conservant une fabrication à moindre co ût. Ceci a permis l'évolution de la microélectronique au rythme dicté par la loi de « Moore », qui prévoit le doublement de la densit é d'intégration des composants tous les deux ans depuis l'année 1965. Le processeur Core i7 980X présent éen 2010 par Intel poss ède environ 1.17 milliard de transistors sur une surface de 248 mm². Selon les prévisions de l'ITRS (de l'anglais «International Technology Roadmap for Semiconductors »), la génération de composant CMOS (de l'anglais « Complementary metal–oxide–semiconductor ») correspondant au nœud technologique 22 nm entrera en production à l'horizon 2016 avec une longueur de grille de 13 nm.

La réduction des dimensions physiques des dispositifs MOS (de l'anglais « metal-oxide-semiconductor ») a provoqué l'apparition d'effets parasites, tels que les effets canaux courts (forts couplages électrostatiques entre les électrodes de source et de drain et limitation du contrôle de la grille sur le potentiel du canal), l'augmentation du courant de fuite de grille ou encore une grande variabilité des performances. Afin de continuer la miniaturisation des composants tout en améliorant leurs performances, des innovations importantes dans l'architecture des dispositifs sont nécessaires, telles que l'introduction de contraintes dans le canal, l'introduction d'isolant à haute constante diélectrique (oxyde high-k) et de grilles méalliques, l'intégration de transistors sur substrat à film mince avec des architectures multigrilles, l'utilisation de matériaux à mobilité élevée (semiconducteur III-V, graph ène ou nanotube de carbone) et la fabrication de transistors à base de nanofils avec une grille entourante. Cette derni ère architecture a étéidentifi ée [1] [2] [3] [4] comme un des candidats le plus prometteus, malgré la limitation du courant à l'état passant inhérent à la faible surface de conduction de nanofils.

Dans cette thèse, une structure de transistors à base de réseau dense de nanofils verticaux avec une grille entourante est proposée afin d'am diorer le courant à l'état passant

tout en conservant un courant de fuite très faible et en utilisant un procédé compatible avec la technologie CMOS conventionelle.

Le premier chapitre présente de manière générale le fonctionnement du transistor MOSFET (de l'anglais « metal-oxide-semiconductor field-effect transistor ») et s'intéresse aux effets parasites liés à la réduction des dimensions physiques du composant. Plusieurs solutions sont proposées afin de poursuivre l'évolution des transistors MOS. L'état de l'art concernant la réalisation et la caractérisation de transistors à base de nanofils en structure horizontale et verticale est décrit. Les limitations identifi ées dans les procédés technologiques de réalisation des dispositifs à base de nanofils verticaux conduisent à l'introduction d'un procédéoriginal et compatible CMOS.

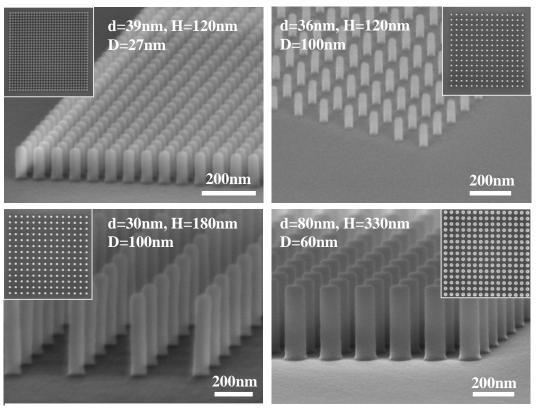

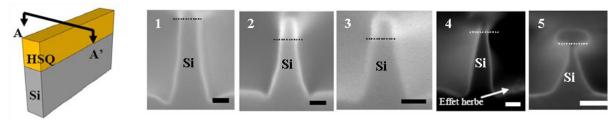

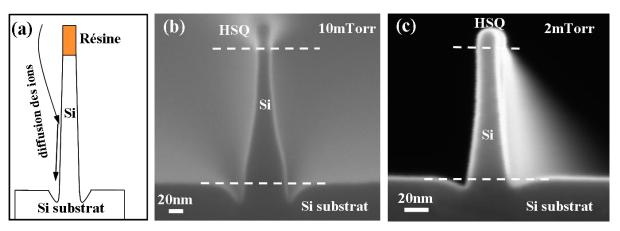

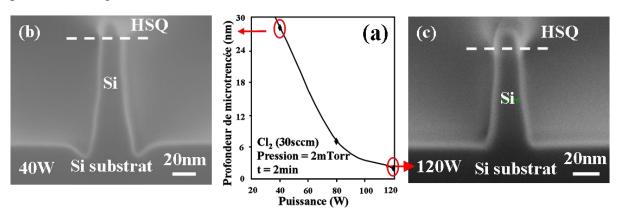

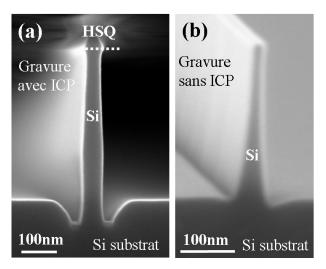

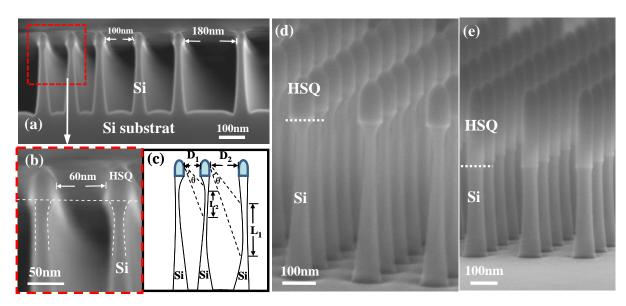

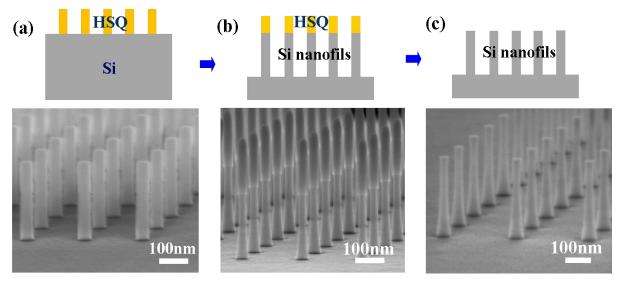

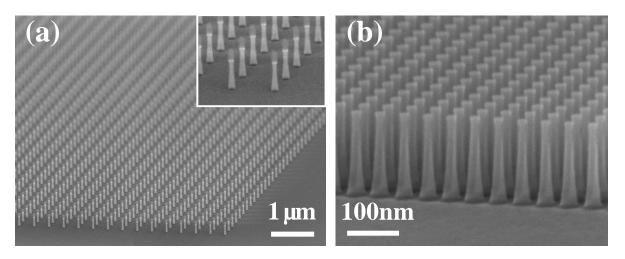

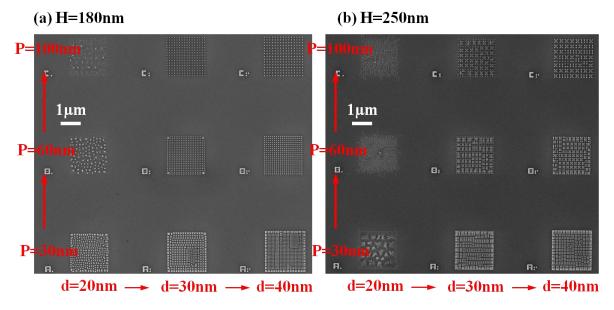

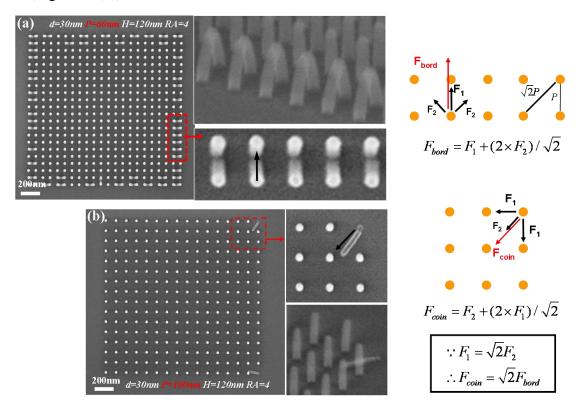

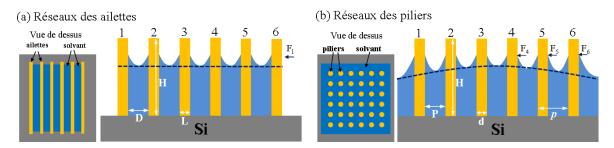

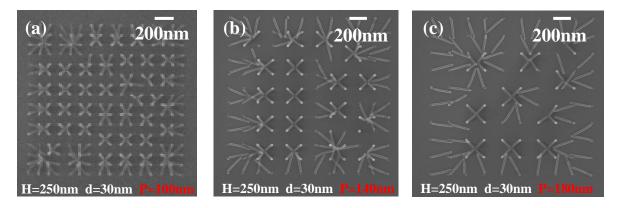

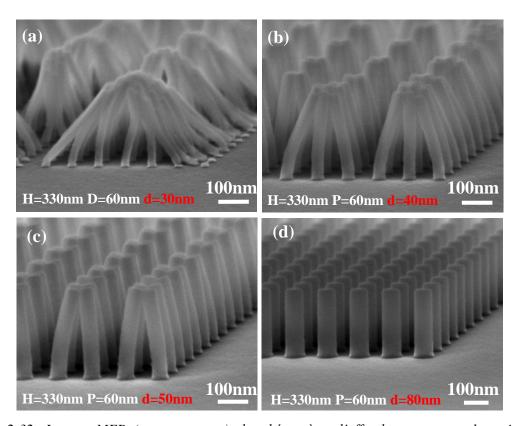

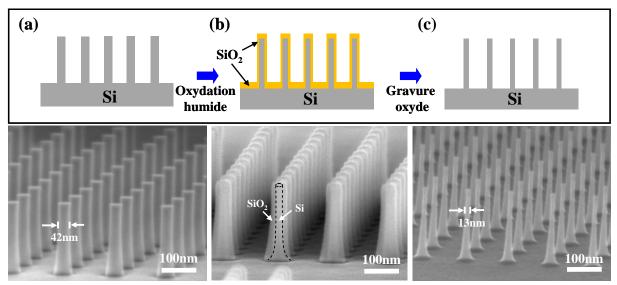

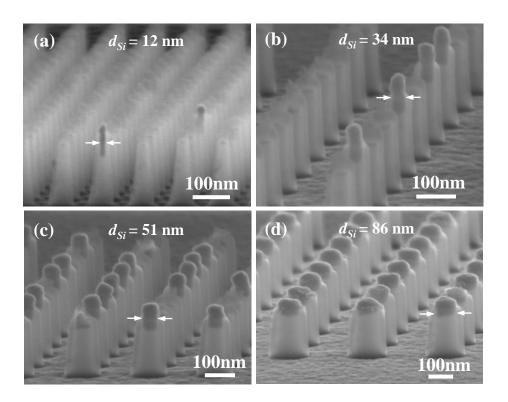

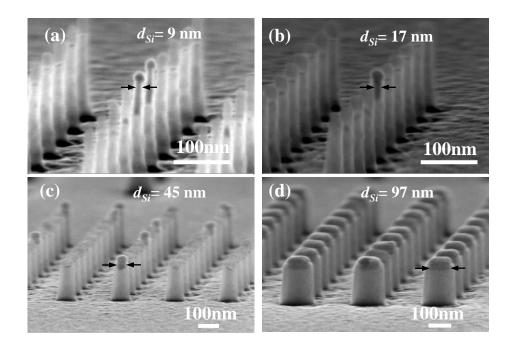

Dans un deuxième chapitre, des masques de résine formant réseaux de nanopiliers verticaux sont fabriqués par lithographie dectronique à l'aide d'une résine inorganique HSQ (Hydrogen SilsesQuioxane). Ces masques sont ensuite transférés au niveau du substrat de silicium par une gravure ionique réactive avec des conditions optimisées pour réaliser des réseaux ultra-denses de nanofils verticaux avec un diamètre decananométrique et une excellente anisotropie. Enfin, les phénomènes d'effondrement de nanostructures induits par les forces de capillaritéont étéanalysée en déail.

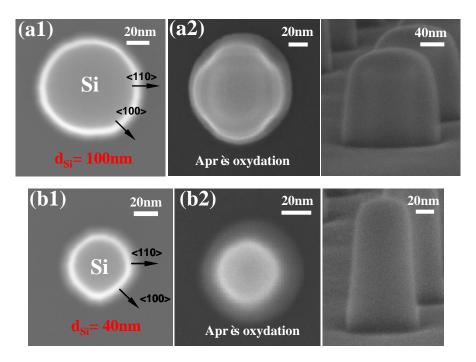

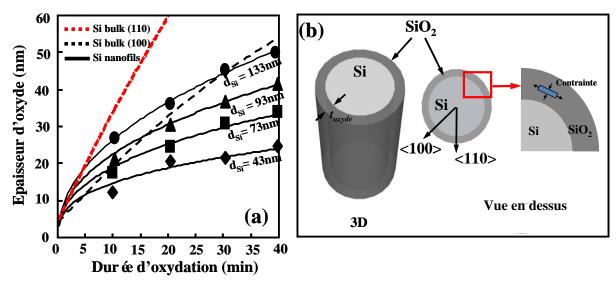

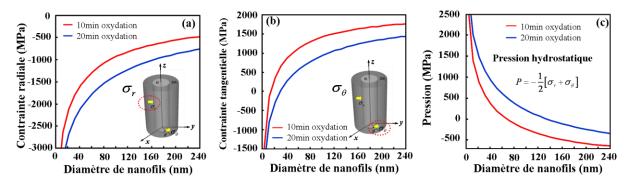

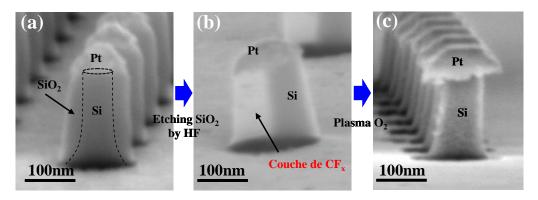

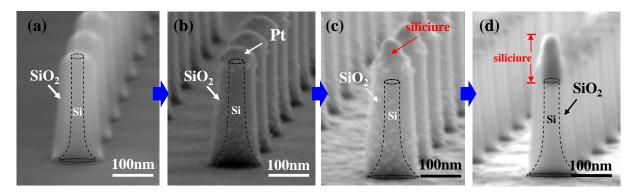

Dans un troisième chapitre, les phénomènes d'oxydation et de siliciuration dans les niveaux de nanofils mais également dans différentes nanostructures sont étudiés et analysés d'une manière systématique. En utilisant l'oxydation thermique de silicium dans un régime où les cinétiques sont retardées voire autolimitées par les contraintes mécaniques, des nanofils avec un diamètre ultrafin ont étéréalisés. L'anisotropie des profils de nanofils et la rugosité de surface a également étéam diorée par ce procédé

Le dernier chapitre débute par une étude de la technologie de planarisation à base de gravure chimique de résine inorganique. Puis, la réalisation et la caractérisation de nanocontacts implément és sur des structures à 2 terminaux à base de réseaux de nanofils verticaux sont effectu ées. Une parfaite reproductibilité des caractéristiques courant-tension (*I-V*) est démontr ée quand un grand nombre de nanofils est considér é De plus, l'impact de la surface d'injection des contacts sur la conduction est discut é Enfin, des transistors à base de réseaux denses de nanofils verticaux avec une grille entourante sont démontr és et s'avère être une architecture intéressante contre les effets aux canaux courts.

# **Bibliographie**

- [1] H. Iwai, "Roadmap for 22 nm and beyond (Invited Paper)," Microelectronic Engineering, vol. 86, no. 7-9, pp. 1520-1528, July. 2009.

- [2] C. Thelander et al., "Development of a Vertical Wrap-Gated InAs FET," Electron Devices, IEEE Transactions on, vol. 55, no. 11, pp. 3030-3036, 2008.

- [3] N. Singh et al., "Si, SiGe Nanowire Devices by Top–Down Technology and Their Applications," Electron Devices, IEEE Transactions on, vol. 55, no. 11, pp. 3107-3118, 2008.

- [4] Kyoung Hwan Yeo, Sung Dae Suk, Ming Li, Yun-young Yeoh, Keun Hwi Cho, Ki-Ha Hong, SeongKyu Yun, Mong Sup Lee, Nammyun Cho, Kwanheum Lee, Duhyun Hwang, Bokkyoung Park, Dong-Won Kim, Donggun Park and Byung-Il Ryu, "Gate-All-Around (GAA) Twin Silicon Nanowire MOSFET (TSNWFET) with 15 nm Length Gate and 4 nm Radius Nanowires," in Electron Devices Meeting, Technical Digest. International, pp. 1-4. 2006,

# Chapitre 1

Principe de fonctionnement du transistor MOSFET : effets physiques et parasites li és à la miniaturisation et motivation de la th èse.

#### Introduction.

D'une manière générale, le premier chapitre présente l'architecture de base des circuits logiques modernes à savoir le transistor de type métal-oxyde-semiconducteur à effet de champs (de l'anglais «Metal-Oxide-Semiconductor field-effect transistor», MOSFET). Ensuite, les règles de miniaturisation associées à la technologie CMOS (de l'anglais «Complementary metal—oxide—semiconductor») sont expos ées et les challenges li és à cette course à la réduction des dimensions sont explicit és. Plusieurs innovations sont présent ées, telles que des MOSFETs à base de structure multi-grilles, le remplacement du silicium par des mat ériaux à haute mobilit é au niveau du canal ou encore les transistors à base de nanofils. Dans cette thèse, une nouvelle structure de transistor implément ée sur des réseaux denses de nanofils verticaux en silicium, sera propos ée comme une solution alternative pour des composants très avanc és.

#### 1.1 G én éralit ésur le transistor MOSFET.

#### 1.1.1 Pr ésentation du transistor MOS.

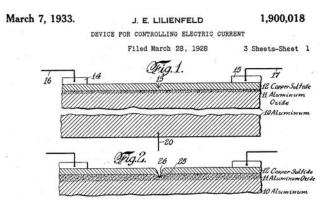

Le MOSFET est le dispositif semi-conducteur le plus utilisé à la base du cœur de chaque circuit num érique. Il est présent en forte densité dans des circuits intégrés comme les microprocesseurs ou les ménoires. Le principe du transistor à effet de champ de surface a été proposé dans le début des années 1930 par Julius Edgar Lilienfeld et Oskar Heil [1] [2] puis a ensuite été étudié par William Bradford Shockley et Roger Pearson [3] au cours de la fin des années 1940 aux Bell Labs. En 1960, Joseph R. Ligenza et W.G. Spitzer [4] ont réalisé le premier dispositif de qualité qui a utilisé le système Si-SiO<sub>2</sub> par oxydation thermique. La structure MOSFET basée sur ce système a été proposée par Martin M. Atalla [5] et déclaré par D. Kahng et Martin M Atalla en 1960 [6].

Figure 1-1. Brevet du transistor MOSFET par J. E. Lilienfeld, 'Dispositif pour le contrôle du courant électrique' [2].

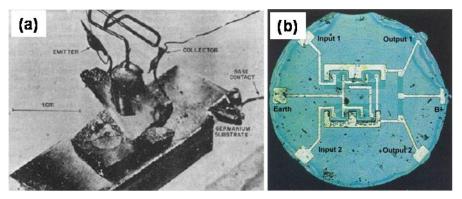

En 1947, trois chercheurs des laboratoires Bell Labs, John Bardeen, Walter Brattain et Shockley Robert, ont expérimentalement démontré un transistor bipolaire à l'aide d'un substrat de germanium (Voir le Fig. 1-2 (a)) [7] et furent colaur éats du prix Nobel de physique en 1956 pour leurs recherches sur les semiconducteurs et leurs découvertes de l'effet transistor. Durant les ann ées cinquante, les technologies des semi-conducteurs ont rapidement progress é en termes de proc éd é de diffusion, de techniques lithographiques ainsi que de méhodes de dépât. Robert Noyce a présent éle premier transistor planaire en 1959 à Fairchild, alors que le premier circuit int égré utilisant cette technique a vu le jour deux ans plus tard, en 1961 [8]. (Fig. 1-2(b))

Figure 1-2. Image du (a) premier transistor bipolaire réalis é dans les laboratoires Bell en 1947 [9] et (b) premier circuit planaire int égr é par Fairchild Semiconducteur en 1961 [8].

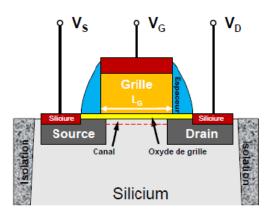

La structure conventionnelle d'un transistor MOSFET est présent ée (Fig. 1-3), La structure MOS est constituée d'une électrode de grille, déposée sur un isolant (couche d'oxyde de grille), recouvrant un substrat semi-conducteur (canal de conduction). De part et d'autre de la structure MOS sont placées les électrodes de source et drain, qui sont deux réservoirs de charges permettant la circulation du courant. Deux types de transistors sont

détermin és selon le type de porteur qui constitue le courant dans le canal : transistor NMOS où le canal n est constitué d'électrons et le PMOS où le canal p est constitué de trous.

Lorsque la polarisation de la grille  $V_{GS}$  est nulle, il n'y a pas de champ électrique et ni de charge dans le canal. Le courant ne peut donc pas circuler de la source vers le drain, le transistor est alors en mode bloqué Il est important de décrire l'état du transistor sans polarisation de la grille où  $V_{GS}$  est nulle. Dans le cas où la grille est non-polarisée, la conductivité du canal est très faible et une tension de grille doit être appliquée pour former un canal conducteur, (régime d'accumulation). Au contraire, si le canal est conducteur dans le cas où la grille n'est pas polarisée, une tension de grille doit etre appliquée pour couper ce canal, le transistor à effet de champ est dit en régime déplété

Lorsqu'un champ électrique non nul est appliqué, la charge dans le semi-conducteur au niveau de l'interface oxyde / semi-conducteur est modul ée par le champ électrique et un canal de conduction se forme. Le courant peut alors circuler entre l'électrode de la source et du drain, le transistor fonctionne alors à l'état passant.

Le passage du mode bloqué au mode passant n'est pas abrupt. Il existe un régime d'inversion faible pour une barrière de drain  $\Phi_d$  importante. Un courant faible peut circuler dans le canal, car quelques porteurs peuvent franchir cette barrière  $\Phi_d$  par activation thermique. Ce courant augmente exponentiellement avec une polarisation de la grille jusqu'à atteindre une tension limite, appel ét tension de seuil  $V_{th}$ .

Figure 1-3. Représentation schématique d'un MOSFET classique où sont décrits les déments principaux du dispositif, tels que la grille, la source, le drain, l'oxyde de grille, le canal, le contact de siliciure, la longueur de grille  $(L_G)$ , l'espaceur et le caisson d'isolation.

## 1.1.2 Principe de fonctionnement d'un transistor MOS idéal.

Cette partie s'attache à décrire les mécanismes physiques d'un transistor MOS durant ses différents régimes de fonctionnement. Le dispositif choisi comme exemple est un

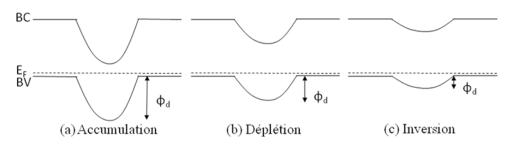

transistor de type PMOS. La conduction du transistor est contrôl ée par la polarisation de la grille. Les trois régimes de fonctionnement, accumulation, inversion, déplétion, sont dérits ci dessous. On suppose que le travail de sortie du métal  $\Phi_m$  est égal à celui du semi-conducteur  $\Phi_s$ , de manière à se placer en situation de bandes plates à une tension de grille nulle.

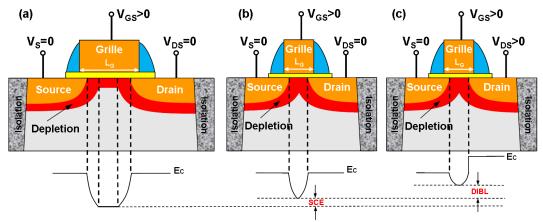

#### (a) Accumulation

Lorsque la grille est polaris  $\acute{e}$  positivement ( $V_{GS} > 0$ ), les dectrons sont attir  $\acute{e}$  et s'accumulent à la surface du canal et c'est le régime d'accumulation. L'énergie potentielle du canal est sup  $\acute{e}$  ieure à celle de la source et constitue une barri  $\acute{e}$  de hauteur  $\varPhi_d$ , emp  $\acute{e}$ chant ainsi la circulation de charges (Fig. 1-4 (a)).

### (b) D épl étion

La tension appliqu ée sur la grille est négative mais inférieure à la tension de seuil ( $V_{GS}$   $< V_{th} < 0$ ), les électrons sous la grille sont repouss és laissant uniquement des charges fixes dans le canal. Ainsi, une zone de déplétion (zone vide de toute charge mobile) se forme sous la grille et à proximit é des zones de source et de drain. De ce fait, la hauteur de barrière  $\Phi_d$  entre la source et le canal diminue mais ne laisse toutefois pas encore passer de courant. (Fig.1-4 (b))

#### (c) Inversion

Lorsque le transistor est polarisé dans l'état passant ( $V_{th} < V_{GS} < 0$ ), les trous sont attirés au niveau de l'interface de canal / oxyde, formant ainsi une couche d'inversion, et diminuant le potentiel entre le canal et le drain. Dans ce régime, une tension n'égative appliqu'ée entre le drain et la source ( $V_{DS}$ ) permet alors le passage du courant ( $I_{DS}$ ). La variation de potentiel entre la source et le drain induit une variation de la distribution de charges le long du canal. (Fig. 1-4 (c)).

Figure 1-4. Description schénatique des différents diagrammes énergétiques d'un transistor PMOS pour différents régimes : (a) accumulation, (b) déplétion et (c) inversion.

## 1.1.3 Caract éristique dectrique id éale du transistor MOS.

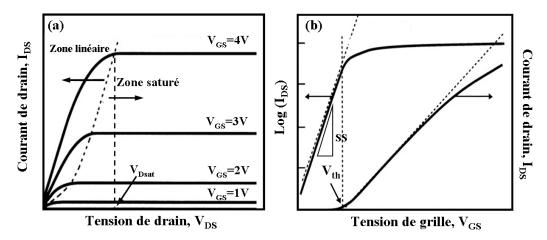

Les transistors MOSFET peuvent être caractérisés électriquement par des mesures statiques en courant – tension au niveau du drain,  $I_{DS} = f(V_{DS})$  et courant – tension de grille,  $I_{DS} = f(V_{GS})$ , comme présentéFig. 1-5. Il s'agit de caractéristiques idéales souvent associées à des dispositifs à canal long.

Figure 1-5. Caract éristique statique d'un transistor MOSFET: (a)  $I_{DS}$  -  $V_{DS}$  et (b)  $I_{DS}$  -  $V_{GS}$ .

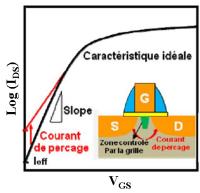

# (a) Inversion faible ou mode bloqu $\acute{e}(V_{GS} < V_{th})$ .

La polarisation de la grille permet de moduler la concentration des porteurs en surface dans le canal ainsi que la hauteur de barri ère drain / source. Quand  $V_{GS} < V_{th}$ , (mode bloqu é), le transistor est en régime de déplétion ou d'inversion faible. Le courant de drain,  $I_{DS}$  est défini par l'équation suivante :

$$I_{DS} = \frac{W}{L_{eff}} \cdot C_{dep} \cdot \mu_0 \left(\frac{kT}{q}\right)^2 \cdot \left(1 - \exp\left(-\frac{qV_{DS}}{kT}\right)\right) \cdot \exp\left(q\frac{V_{GS} - V_{th}}{\alpha kT}\right)$$

Eq. 1-1

Où W est la largeur du canal,  $L_{eff}$  est la longueur effective du canal,  $\mu_0$  est la mobilit é des porteurs,  $\alpha$  étant égal à  $(I+C_{dep}/C_{ox})$ ,  $C_{ox}$  est la capacité de l'oxyde de grille,  $C_{dep}$  est la capacité de la zone d'éplétion, k est la constante de Boltzmann, q est la charge éténentaire et T est la température. En régime de faible inversion, le courant de drain est exponentiellement proportionnel à  $(V_{GS} - V_{th})$ . On d'éfinit alors la pente sous le seuil, SS (de l'anglais «Subthreshold Slope »), par l'équation suivante :

$$SS = \frac{\partial V_{GS}}{\partial (\log I_{DS})} = \left(1 + \frac{C_{dep}}{C_{ox}}\right) \cdot \frac{kT}{q} \ln 10 \quad \text{(en mV/dec)}$$

Eq. 1-2

$C_{dep}$  et  $C_{ox}$  sont respectivement la capacité de la zone de déplétion et la capacité de l'oxyde de grille. La pente sous le seuil correspond à la tension de grille nécessaire pour

augmenter le courant de drain d'une décade. Dans le cas d'un transistor id éal à temp érature ambiante (300 K), la pente sous le seuil est de 60 mV/dec.

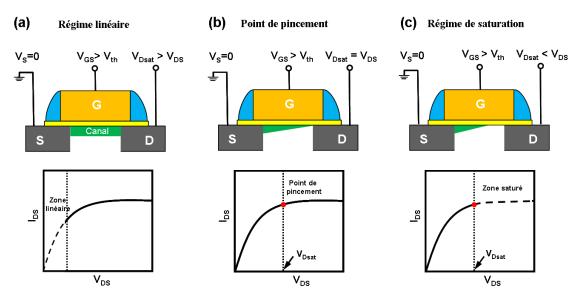

# (b) Inversion forte ou mode passant $(V_{GS} > V_{th})$ .

Quand  $V_{GS} > V_{th}$ , le transistor est en régime d'inversion forte, le schéma de régime lin éaire est montré au niveau de la Fig1-6 (a). Pour les faibles polarisations de drain, la charge d'inversion dans le canal est totalement contrôlée par la grille. Le courant passant dans le transistor est quasi-lin éaire et s'exprime par :

$$I_{DS} = \frac{W}{L_{eff}} \mu_0 C_{ox} \left[ V_{GS} - V_{th} - \frac{1}{2} V_{DS} \right] V_{DS}$$

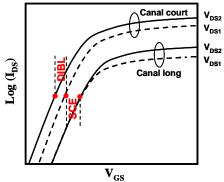

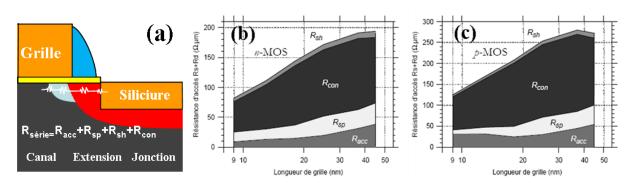

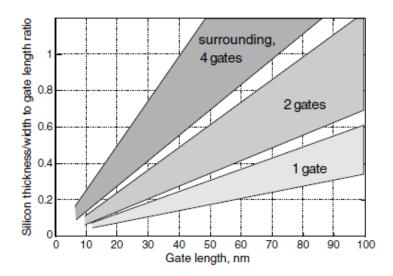

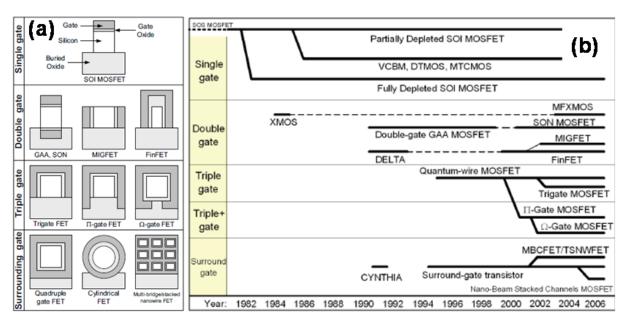

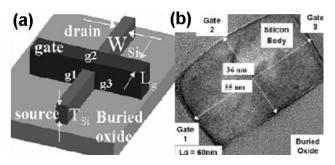

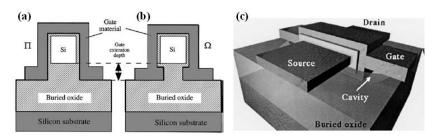

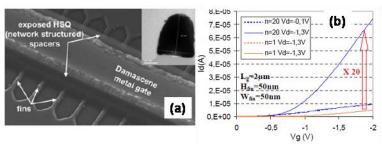

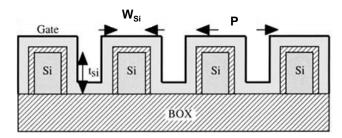

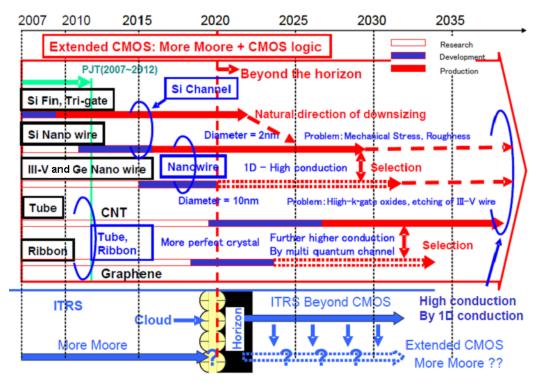

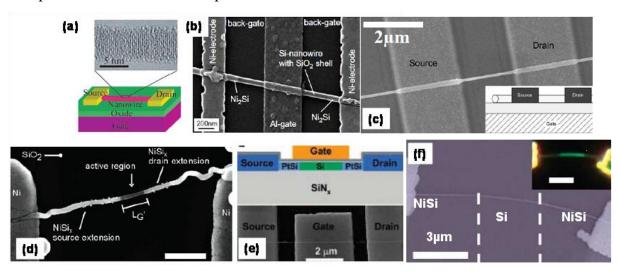

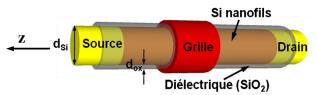

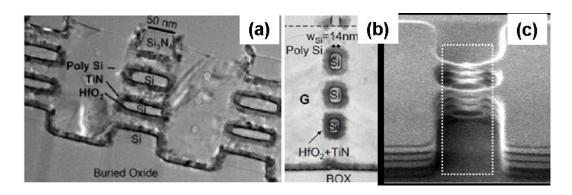

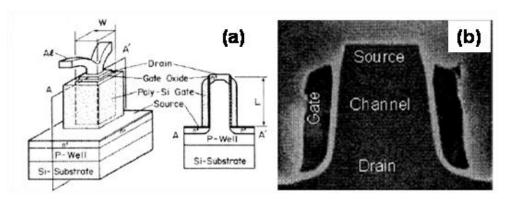

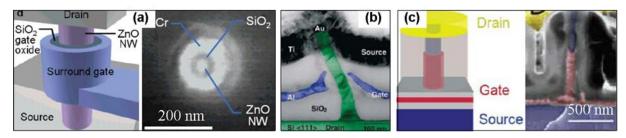

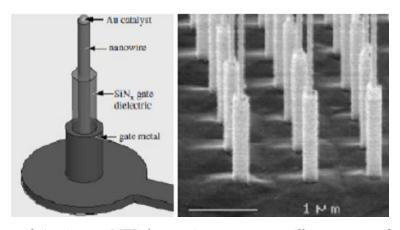

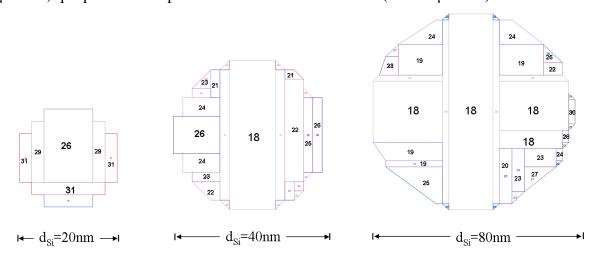

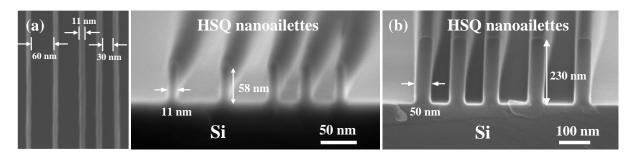

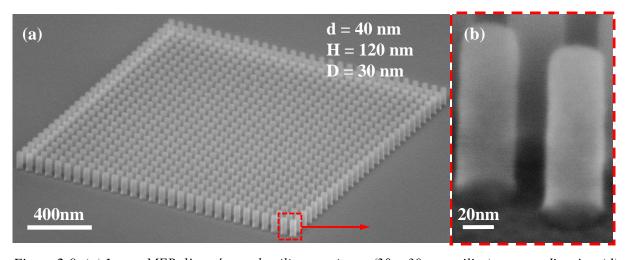

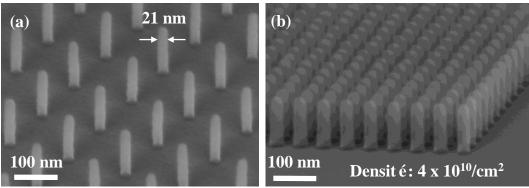

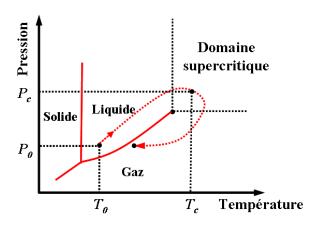

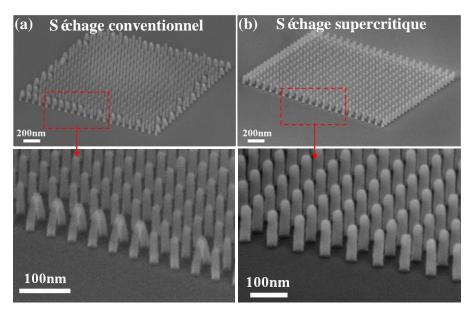

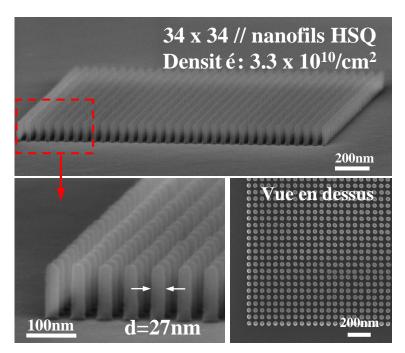

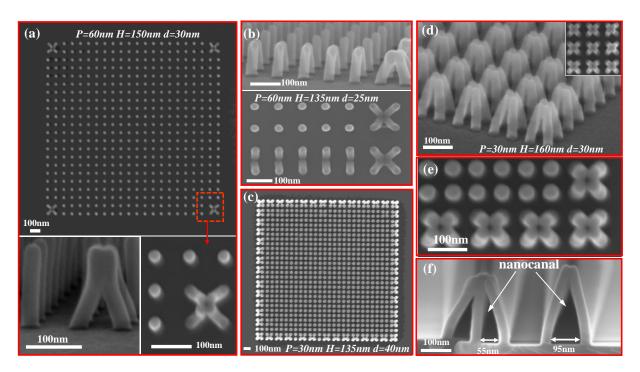

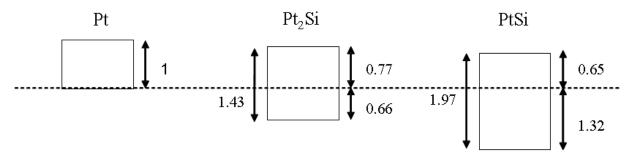

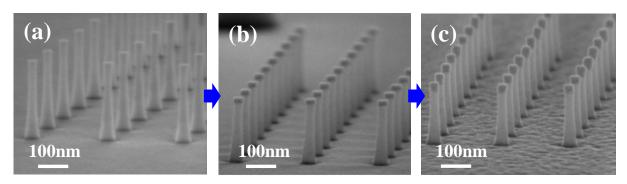

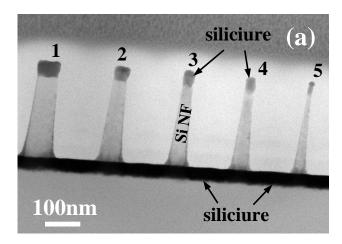

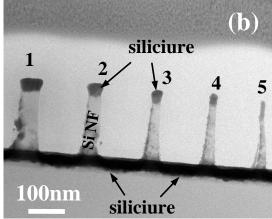

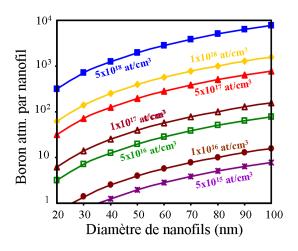

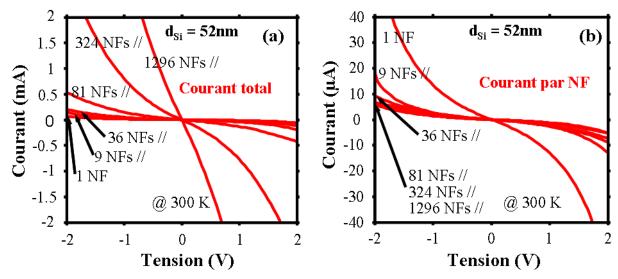

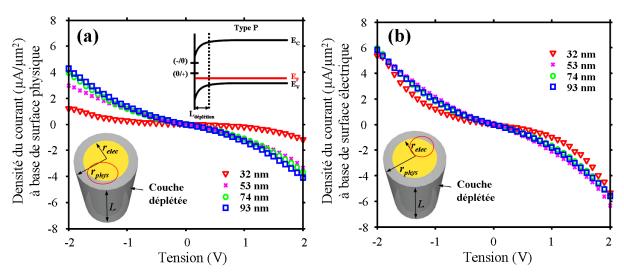

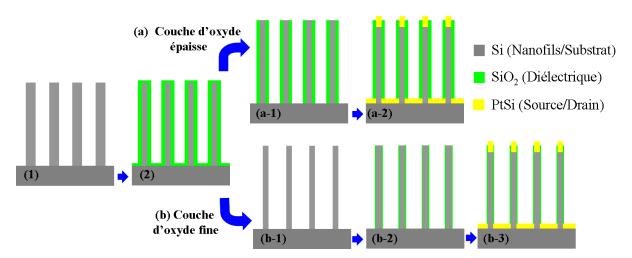

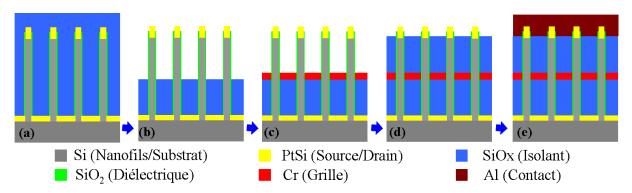

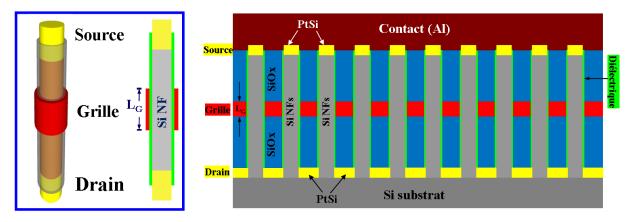

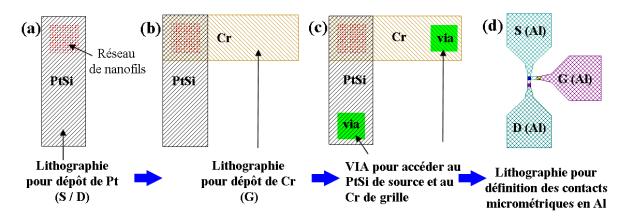

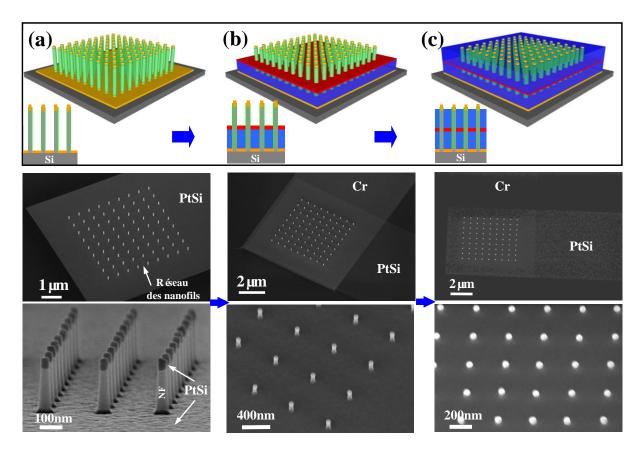

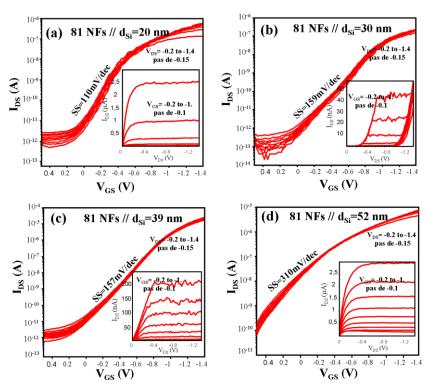

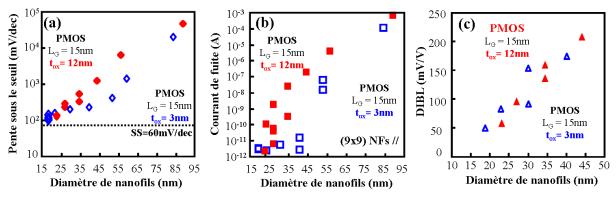

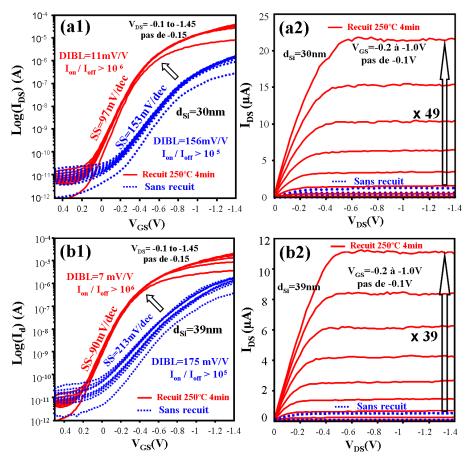

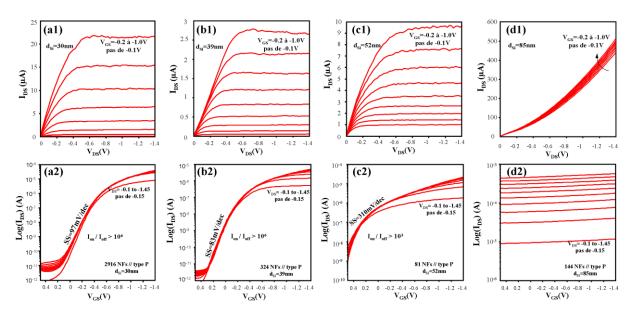

Eq. 1-3