Thèse présentée pour obtenir le grade de docteur Université Lille 1 - Sciences et Technologies

# 50

École Doctorale Sciences Pour l'Ingénieur Université Lille Nord-de-France Laboratoire d'Informatique Fondamentale de Lille (UMR CNRS 8022) Centre de Recherche INRIA Lille Nord Europe Numéro d'ordre: 40705

Discipline : Informatique

# Métaheuristiques parallèles sur GPU

PAR : Thé Van Luong

Membres du jury:

Rapporteur : Pascal Bouvry, Professeur des Universités, Luxembourg

Rapporteur : Pierre Manneback, Professeur des Universités, Mons (Belgique)

Examinateur : Didier El Baz, Chargé de Recherche HDR, LAAS CNRS Toulouse

Président : Pierre Boulet, Professeur des Universités, Lille 1

Directeur : Nouredine Melab, Professeur des Universités, Lille 1

Co-directeur : El-Ghazali Talbi, Professeur des Universités, Lille 1

Date de soutenance : 1/12/2011

# Remerciements

Je souhaite tout d'abord remercier mes directeurs de thèse, Nouredine Melab et El-Ghazali Talbi. Je tiens à leur exprimer toute ma profonde reconnaissance pour leur soutien, leurs encouragements et leurs précieux conseils, tout au long de ce doctorat.

Mes vifs remerciements vont également à tous les membres du jury : Pierre Boulet, président, Pierre Manneback et Pascal Bouvry, rapporteurs, ainsi que Didier El Baz, examinateur de cette thèse.

Je remercie tous les membres de l'équipe DOLPHIN avec qui j'ai pris énormément de plaisirs à travailler durant ces trois années de thèse. Un merci en particulier aux doctorants, ingénieurs et stagiaires de l'équipe : Marie-Éléonore (alias mon petit boudin), Yacine (alias Yaya), Mathieu (alias petit Mathieu), Nadia, Karima, Mostepha, Ahcène, Tuan, Moustapha, Martin, les deux Julie, Imen, Sezin, Ines, Clive et François Legillon. Un remerciement aux permanents de l'équipe : Arnaud, Sébastien, Bilel, Clarisse, Laetitia, François, Luce et Dimo. Mais également aux anciens membres de l'équipe : Mahmoud, Waldo, Mathieu (alias le Breton), Mohand, Jean-Charles Boisson (comme la boisson), Rémy Chevrier, Feryal, Salma, Emilia, Alexandru, Ali, Jérôme, Gaël, Antonio, Jérémie (merci pour SC2), Loukil et Malika Mehdi. Sans oublier les différentes assistantes : Malika et Julie Jonas.

Par ailleurs, je tiens également à exprimer ma gratitude auprès d'Éric Taillard pour m'avoir chaleureusement accueilli en Suisse dans le cadre d'un postdoctorat.

De plus, je voudrais adresser mes profonds remerciements à tous mes amis de Nice pour le témoignage de leur amitié : David (alias Dav la frite), Cédric (alias Debeaume), Sarco (ou Elium le tombeur d'Idra), Aurélie, Rivière, Stéphane, Christophe, Christopher, Oliv, Guitou, Savino et Julien. Je tiens également à rendre hommage aux différentes femmes qui ont partagé une partie de ma vie, et qui m'ont apporté un certain équilibre tout au long de cette thèse : Jo Ferrari, Fleur, Eva, Caroline Gastaldi, Héléna et Isabelle.

Et enfin, un grand merci à ma mère, mon père et mes deux frères Vinh et Phuc, pour leur affection et leur soutien tout au long de mon doctorat, mais aussi lors de ces vingt-huit dernières années.

# Contents

| In | trod | uction           |                                                                                 | 1  |

|----|------|------------------|---------------------------------------------------------------------------------|----|

| 1  | GP   | U Con            | nputing for Parallel Metaheuristics                                             | 5  |

|    | 1.1  | Parall           | el Metaheuristics                                                               | 6  |

|    |      | 1.1.1            | Optimization Context                                                            | 6  |

|    |      | 1.1.2            | Principles of Metaheuristics                                                    | 7  |

|    |      |                  | 1.1.2.1 Solution Representation                                                 | 7  |

|    |      |                  | 1.1.2.2 Evaluation Function $\ldots$                                            | 8  |

|    |      |                  | 1.1.2.3 Principles of S-metaheuristics                                          | 8  |

|    |      |                  | 1.1.2.4 Principles of P-metaheuristics                                          | 10 |

|    |      | 1.1.3            | Parallel Models of Metaheuristics                                               | 11 |

|    | 1.2  | Metah            | euristics and GPU Computing                                                     | 13 |

|    |      | 1.2.1            | GPU Architecture                                                                | 13 |

|    |      | 1.2.2            | GPU Challenges for Metaheuristics                                               | 15 |

|    |      | 1.2.3            | General GPU Model: CPU-GPU Cooperation                                          | 16 |

|    |      | 1.2.4            | GPU Threads Model: Parallelism Control                                          | 16 |

|    |      | 1.2.5            | Kernel Management: Memory Management                                            | 17 |

|    | 1.3  | Relate           | ed Works on Parallel Metaheuristics                                             | 20 |

|    |      | 1.3.1            | Metaheuristics on Parallel and Distributed Architectures                        | 20 |

|    |      | 1.3.2            | Research Works on GPU-based Metaheuristics                                      | 21 |

|    | 1.4  | imental Protocol | 26                                                                              |    |

|    |      | 1.4.1            | Optimization Problems                                                           | 26 |

|    |      |                  | 1.4.1.1 Permuted Perceptron Problem                                             | 27 |

|    |      |                  | 1.4.1.2 The Quadratic Assignment Problem                                        | 27 |

|    |      |                  | 1.4.1.3 The Weierstrass Continuous Function                                     | 27 |

|    |      |                  | 1.4.1.4 The Traveling Salesman Problem                                          | 28 |

|    |      |                  | 1.4.1.5 The Golomb Rulers $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 28 |

|    |      |                  | 1.4.1.6 Problem Characteristics                                                 | 29 |

|    |      | 1.4.2            | Machines Configuration                                                          | 30 |

|    |      | 1.4.3            | Metric and Statistical Tests                                                    | 31 |

| <b>2</b> | Effi | cient C                                    | CPU-GPU Cooperation                                              | <b>35</b> |  |  |  |  |

|----------|------|--------------------------------------------|------------------------------------------------------------------|-----------|--|--|--|--|

|          | 2.1  | Task Repartition for Metaheuristics on GPU |                                                                  |           |  |  |  |  |

|          |      | 2.1.1                                      | Model of Parallel Evaluation of Solutions                        | 37        |  |  |  |  |

|          |      | 2.1.2                                      | Parallelization Scheme on GPU                                    | 37        |  |  |  |  |

|          | 2.2  | Data 7                                     | Transfer Optimization                                            | 38        |  |  |  |  |

|          |      | 2.2.1                                      | Generation of the Neighborhood in S-metaheuristics               | 39        |  |  |  |  |

|          |      | 2.2.2                                      | The Proposed GPU-based Algorithm                                 | 40        |  |  |  |  |

|          |      | 2.2.3                                      | Additional Data Transfer Optimization                            | 42        |  |  |  |  |

|          | 2.3  | Perfor                                     | mance Evaluation                                                 | 43        |  |  |  |  |

|          |      | 2.3.1                                      | Analysis of the Data Transfers from CPU to GPU                   | 43        |  |  |  |  |

|          |      | 2.3.2                                      | Additional Data Transfer Optimization                            | 49        |  |  |  |  |

|          | 2.4  | Comp                                       | arison with Other Parallel and Distributed Architectures         | 50        |  |  |  |  |

|          |      | 2.4.1                                      | Parallelization Scheme on Parallel and Distributed Architectures | 52        |  |  |  |  |

|          |      | 2.4.2                                      | Configurations                                                   | 52        |  |  |  |  |

|          |      | 2.4.3                                      | Cluster of Workstations                                          | 54        |  |  |  |  |

|          |      | 2.4.4                                      | Workstations in a Grid Organization                              | 55        |  |  |  |  |

| 3        | Effi | Efficient Parallelism Control 59           |                                                                  |           |  |  |  |  |

|          | 3.1  | Threa                                      | d Control for Metaheuristics on GPU                              | 61        |  |  |  |  |

|          |      | 3.1.1                                      | Execution Parameters at Runtime                                  | 61        |  |  |  |  |

|          |      | 3.1.2                                      | Thread Control Heuristic                                         | 62        |  |  |  |  |

|          | 3.2  | Efficie                                    | nt Mapping of Neighborhood Structures on GPU                     | 64        |  |  |  |  |

|          |      | 3.2.1                                      | Binary Encoding                                                  | 64        |  |  |  |  |

|          |      | 3.2.2                                      | Discrete Vector Representation                                   | 65        |  |  |  |  |

|          |      | 3.2.3                                      | Vector of Real Values                                            | 65        |  |  |  |  |

|          |      | 3.2.4                                      | Permutation Representation                                       | 66        |  |  |  |  |

|          |      |                                            | 3.2.4.1 2-exchange Neighborhood                                  | 66        |  |  |  |  |

|          |      |                                            | 3.2.4.2 3-exchange Neighborhood                                  | 68        |  |  |  |  |

|          |      |                                            | 3.2.4.3 Mapping Tables for General Neighborhoods                 | 69        |  |  |  |  |

|          | 3.3  | First I                                    | Improvement S-metaheuristics on GPU                              | 69        |  |  |  |  |

|          | 3.4  | Perfor                                     | mance Evaluation                                                 | 71        |  |  |  |  |

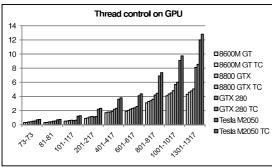

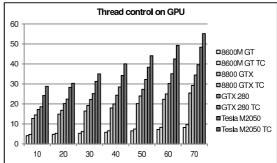

|          |      | 3.4.1                                      | Thread Control for Preventing Crashes                            | 71        |  |  |  |  |

|          |      |                                            | 3.4.1.1 Application to the Traveling Salesman Problem            | 71        |  |  |  |  |

|          |      |                                            | 3.4.1.2 Thread Control Applied to the Traveling Salesman Problem | 73        |  |  |  |  |

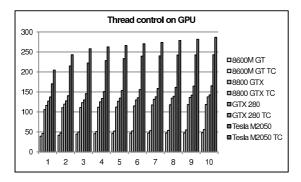

|          |      | 3.4.2                                      | Thread Control for Further Optimization                          | 74        |  |  |  |  |

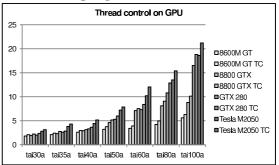

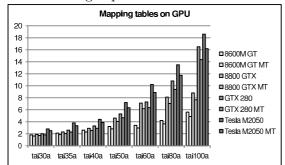

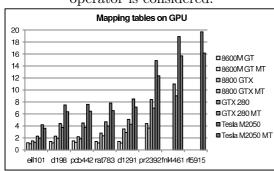

|          |      | 3.4.3                                      | Performance of User-defined Mappings                             | 74        |  |  |  |  |

|          |      | 3.4.4                                      | First Improvement S-metaheuristics on GPU                        | 77        |  |  |  |  |

|          | 3.5  | Large                                      | Neighborhoods for Improving Solutions Quality                    | 80        |  |  |  |  |

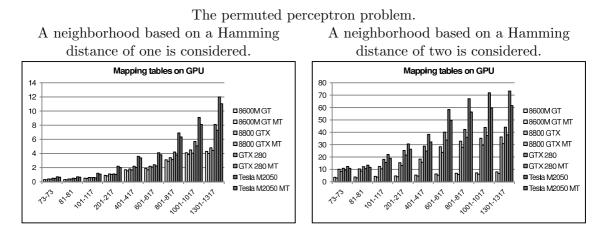

|          |                | 3.5.1   | Application to the Permuted Perceptron Problem             | 81  |  |  |  |

|----------|----------------|---------|------------------------------------------------------------|-----|--|--|--|

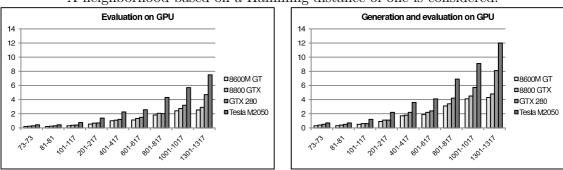

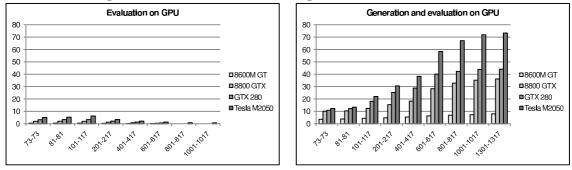

|          |                |         | 3.5.1.1 Neighborhood based on a 1-Hamming Distance         | 81  |  |  |  |

|          |                |         | 3.5.1.2 Neighborhood based on a 2-Hamming Distance         | 82  |  |  |  |

|          |                |         | 3.5.1.3 Neighborhood based on a 3-Hamming Distance         | 82  |  |  |  |

|          |                |         | 3.5.1.4 Performance Analysis                               | 83  |  |  |  |

| 4        | Effi           | cient N | Jemory Management                                          | 87  |  |  |  |

|          | 4.1            | Comm    | non Concepts of Memory Management                          | 89  |  |  |  |

|          |                | 4.1.1   | Memory Coalescing Issues                                   | 89  |  |  |  |

|          |                | 4.1.2   | Coalescing Transformation                                  | 90  |  |  |  |

|          |                | 4.1.3   | Texture Memory                                             | 91  |  |  |  |

|          |                | 4.1.4   | Memory Management                                          | 92  |  |  |  |

|          | 4.2            | Memo    | ry Management in Cooperative Algorithms                    | 94  |  |  |  |

|          |                | 4.2.1   | Parallel and Cooperative Model                             | 94  |  |  |  |

|          |                | 4.2.2   | Parallelization Strategies for Cooperative Algorithms      | 96  |  |  |  |

|          |                |         | 4.2.2.1 Parallel Evaluation of Populations on GPU          | 96  |  |  |  |

|          |                |         | 4.2.2.2 Full Distribution of Cooperative Algorithms on GPU | 98  |  |  |  |

|          |                |         | 4.2.2.3 Full Distribution Using Shared Memory              | 100 |  |  |  |

|          |                | 4.2.3   | Issues Related to the Fully Distributed Schemes            | 101 |  |  |  |

|          | 4.3            | -       |                                                            |     |  |  |  |

|          |                | 4.3.1   | Coalescing accesses to global memory                       | 106 |  |  |  |

|          |                | 4.3.2   | Memory Associations of Optimization Problems               |     |  |  |  |

|          | 4.4            | Perfor  | mance of Cooperative Algorithms                            |     |  |  |  |

|          |                | 4.4.1   | Configuration                                              |     |  |  |  |

|          |                | 4.4.2   | Measures in Terms of Efficiency                            | 109 |  |  |  |

|          |                | 4.4.3   | Measures in Terms of Effectiveness                         |     |  |  |  |

| <b>5</b> | $\mathbf{Ext}$ | ension  | of ParadisEO for GPU-based Metaheuristics                  | 115 |  |  |  |

|          | 5.1            |         | aradisEO Framework                                         | 117 |  |  |  |

|          |                | 5.1.1   | Motivations and Goals                                      | 117 |  |  |  |

|          |                | 5.1.2   | Presentation of the Framework                              | 117 |  |  |  |

|          | 5.2            | GPU-0   | enabled ParadisEO                                          |     |  |  |  |

|          |                | 5.2.1   | Architecture of ParadisEO-GPU                              | 119 |  |  |  |

|          |                | 5.2.2   | ParadisEO-GPU Components                                   | 120 |  |  |  |

|          |                | 5.2.3   | A Case Study: Parallel Evaluation of a Neighborhood        |     |  |  |  |

|          |                | 5.2.4   | Automatic Construction of the Mapping Function             |     |  |  |  |

|          | 5.3            |         | mance Evaluation                                           |     |  |  |  |

|          |                | 5.3.1   | Experimentation with ParadisEO-GPU                         |     |  |  |  |

|        |          | 5.3.1.1    | Application to the Permuted Perceptron Problem 120                                             |

|--------|----------|------------|------------------------------------------------------------------------------------------------|

|        |          | 5.3.1.2    | Application to the Quadratic Assignment Problem 129                                            |

| Conclu | usion an | nd Futu    | re Works 133                                                                                   |

| Apper  | ndix     |            | 133                                                                                            |

| .1     | Mappir   | ng Proofs  | 5                                                                                              |

|        | .1.1     | Two-to-    | one Index Transformation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 13'$  |

|        | .1.2     | One-to-t   | wo Index Transformation                                                                        |

|        | .1.3     | One-to-t   | hree Index Transformation                                                                      |

|        | .1.4     | Three-to   | p-one index transformation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 14$ |

| .2     | Statisti | ical Tests | 5                                                                                              |

| Biblio | graphy   |            | 158                                                                                            |

| Intern | ational  | Publica    | tions 160                                                                                      |

# Introduction

In the optimization field, both academic and industrial problems are often complex and NP-hard. In practice, their modeling is continuously evolving in terms of constraints and objectives. Thereby, a large number of real-life optimization problems in science, engineering, economics, and business are complex and difficult to solve. Their resolution cannot be performed in an exact manner within a reasonable amount of time, and their resource requirements are ever increasing. To deal with such an issue, the design of resolution methods must be based on the joint use of advanced approaches from combinatorial optimization, large-scale parallelism and engineering methods.

In the last decades, metaheuristics are approximate algorithms that have been successfully applied to solve optimization problems. Indeed, this class of methods allows to produce near-optimal solutions in a reasonable time. Metaheuristics may solve instances of problems that are believed to be hard in general, by exploring the usually large solution search space of these instances. These algorithms achieve this by reducing the effective size of the search space and by exploring that space efficiently. However, although metaheuristics allow to reduce the temporal complexity of problems resolution, they remain unsatisfactory to tackle large problems. Experiments using large problems are often stopped without any convergence being reached. Thereby, in designing metaheuristics, there is often a trade-off to be found between the size of the problem instance and the computational complexity to explore it. As a result, only the use of parallelism allows to design new methods to tackle large problems.

Over the last decades, parallel computing has been revealed as an unavoidable way to deal with large problem instances of difficult optimization problems. The design and implementation of parallel metaheuristics are strongly influenced by the computing platform. Many contributions have been proposed for the design and implementation of parallel metaheuristics using massively parallel processors [CSK93], networks or cluster of workstations [CTG95, BSB<sup>+</sup>01], and shared memory machines [JRG09, Bev02]. The proposed approaches are based on three parallel models: parallel evaluation of a single solution, parallel evaluation of solutions and parallel (cooperative or independent) execution of several metaheuristics. These parallel approaches have been later revisited for large-scale computational grids [TMT07]. Indeed, grid computing is an impressively powerful way to solve challenging instances in combinatorial optimization. However, computational grids providing a huge amount of resources are not easily available and accessible for any user. Recently, graphics processing units (GPU) have emerged as a new popular support for massively parallel computing [RRS<sup>+</sup>08, OML<sup>+</sup>08]. Such resources supply a great computing power, are energy-efficient, and unlike grids, they are highly available everywhere: laptops, desktops, clusters, etc. During many years, the use of GPU computing was dedicated to graphics and video applications. Its utilization has recently been extended to other application domains [CBM<sup>+</sup>08, GLGN<sup>+</sup>08] (e.g. scientific computing) thanks to the publication of the CUDA (Compute Unified Device Architecture) development toolkit that allows GPU programming in C-like language [NBGS08]. In some areas such as numerical computing [TSP<sup>+</sup>08], we are now witnessing the proliferation of software libraries such as CUBLAS for GPU. However, in other areas such as combinatorial optimization, in particular metaheuristics, the utilization of GPU does not grow at the same pace. With the arrival of open standard programming languages on GPU and the arrival of future compilers for these languages, like other application areas, combinatorial optimization on GPU will generate a growing interest.

Indeed, GPU computing has emerged in the recent years as an important challenge for the parallel computing research area. This new emerging technology is believed to be extremely useful to speed up many complex algorithms. One of the major issues for metaheuristics is to rethink existing parallel models and programming paradigms to allow their deployment on GPU accelerators. In other words, the challenge is to revisit the parallel models and paradigms to efficiently take into account the characteristics of GPUs. However, the exploitation of parallel models is not trivial, and many issues related to the GPU memory hierarchical management of this architecture have to be considered. Generally speaking, the major issues we have to deal with are: the distribution of data processing between CPU and GPU, the thread synchronization, the optimization of data transfer between the different memories, the memory capacity constraints, etc.

The contribution of this thesis is to deal with such issues for the redesign of parallel models of metaheuristics to allow solving of large scale optimization problems on GPU architectures. Our objective is to rethink the existing parallel models and to enable their deployment on GPUs. In this purpose, we propose in this document a new generic guideline for building efficient parallel metaheuristics on GPU. Our challenge is to come out with the GPU-based design of the whole hierarchy of parallel models. Different contributions and salient issues in this document are dealt with: (1) an effective cooperation between the CPU and the GPU, which requires to optimize the data transfers between the CPU and the GPU; (2) an efficient parallelism control to associate working units with threads, and to meet the memory constraints; (3) efficient mappings of data structures of the different models on the hierarchy of memories (with different access latencies) provided by the GPU; (4) software framework-based implementations to make the GPU as transparent as

possible for the user.

Very efficient approaches are proposed for CPU-GPU data transfer optimization, thread control, mapping of solutions to GPU threads or memory management. These approaches have been exhaustively experimented using five optimization problems and four GPU configurations. Compared to a CPU-based execution, accelerations up to  $\times 80$  are reported for large combinatorial problems and up to  $\times 2000$  for a continuous problem. The different works related to this thesis have been accepted in a dozen of publications, including the IEEE Transactions on Computers journal.

### **Document Organization**

#### Chapter 1

The first chapter describes general concepts for parallel metaheuristics and GPU computing. In this purpose, we will first introduce parallel models of metaheuristics. Thereafter, we will present the general GPU architecture, and highlight the different challenges that appear when dealing with metaheuristics. The rest of the chapter is dedicated to all the definitions and protocols required to the general comprehension of the document.

#### Chapter 2

The next chapter contributes to the efficient cooperation between the CPU and the GPU. Thereby, we will highlight how the optimization of data transfers between the two components has a crucial impact on the performance of metaheuristics on GPU. Furthermore, extensive experiments demonstrate the strong potential of GPU-based metaheuristics compared to cluster or grid-based parallel architectures.

#### Chapter 3

In the third chapter, the focus is on the efficient control of parallelism when designing metaheuristics on GPU. On the one hand, such a step allows to establish a clear association of the elements to be processed according to the spatial thread organization of GPUs. On the other hand, controlling the generation of threads will introduce some robustness in GPU applications. Therefore, it may prevent applications from crashing, and it may lead to some performance improvements.

#### Chapter 4

In the fourth chapter, we will describe different memory associations of optimization structures to deal with different GPU-based metaheuristics. As an illustration, the scope of this chapter is to redefine parallel and cooperative algorithms, in which this memory management is prominent. We will investigate on how the redesign of a same algorithm using different memory associations has an impact on the global performance.

#### Chapter 5

The final chapter introduces an extension of the ParadisEO framework for the transparent deployment of metaheuristics on GPU. In this purpose, conceptual aspects are exposed to allow the user to program GPU-based metaheuristics, while minimizing his or her involvement in its management.

# GPU Computing for Parallel Metaheuristics

This first chapter presents all the background and prerequisites necessary to the general comprehension of the global document.

First, we will describe the principles of metaheuristics within the optimization context. An overview is made on the parallel models of metaheuristics to accelerate the search process. Thereafter, GPU computing is introduced in the context of metaheuristics. In this purpose, we will present the different advantages and the challenges associated with this emergent technology. Furthermore, a review of different works of the literature for metaheuristics on parallel and GPU architectures will be made. Finally, we will emphasize on the experimental protocol used for the experiments performed in this manuscript.

#### Contents

| 1.1                       | Para  | allel Metaheuristics                                     | 6         |  |  |  |

|---------------------------|-------|----------------------------------------------------------|-----------|--|--|--|

|                           | 1.1.1 | Optimization Context                                     | 6         |  |  |  |

|                           | 1.1.2 | Principles of Metaheuristics                             | 7         |  |  |  |

|                           | 1.1.3 | Parallel Models of Metaheuristics                        | 11        |  |  |  |

| 1.2                       | Met   | aheuristics and GPU Computing                            | <b>13</b> |  |  |  |

|                           | 1.2.1 | GPU Architecture                                         | 13        |  |  |  |

|                           | 1.2.2 | GPU Challenges for Metaheuristics                        | 15        |  |  |  |

|                           | 1.2.3 | General GPU Model: CPU-GPU Cooperation                   | 16        |  |  |  |

|                           | 1.2.4 | GPU Threads Model: Parallelism Control                   | 16        |  |  |  |

|                           | 1.2.5 | Kernel Management: Memory Management                     | 17        |  |  |  |

| 1.3                       | Rela  | ted Works on Parallel Metaheuristics                     | 20        |  |  |  |

|                           | 1.3.1 | Metaheuristics on Parallel and Distributed Architectures | 20        |  |  |  |

|                           | 1.3.2 | Research Works on GPU-based Metaheuristics               | 21        |  |  |  |

| 1.4 Experimental Protocol |       |                                                          |           |  |  |  |

|                           | 1.4.1 | Optimization Problems                                    | 26        |  |  |  |

|                           | 1.4.2 | Machines Configuration                                   | 30        |  |  |  |

|                           | 1.4.3 | Metric and Statistical Tests                             | 31        |  |  |  |

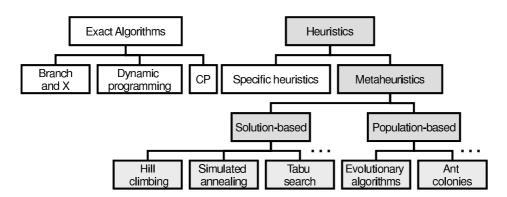

Figure 1.1: Taxonomy of resolution methods for optimization problems.

### **1.1** Parallel Metaheuristics

#### 1.1.1 Optimization Context

An optimization problem can be formulated as an optimization (minimization or maximization) of a cost function (monoobjective optimization) or a vector of cost functions (multiobjective optimization). This (these) function(s) is (are) called *objective function(s)*. In this document, minimization problems are considered, without loss of generality. An optimization problem (OP) can be formulated as follows:

$$(OP) = \begin{cases} Min & F(x) = (f_1(x), f_2(x), \dots, f_n(x)) \\ s.t. & x \in S \end{cases}$$

where n is the number of objectives,  $x = (x_1, \ldots, x_k)$  is the vector representing the decision variables, and S represents the set of feasible solutions associated with equality and inequality constraints and explicit bounds.  $F(x) = (f_1(x), f_2(x), \ldots, f_n(x))$  is the vector of objectives to be optimized. For n = 1 (respectively  $n \ge 2$ ), monoobjective (respectively multiobjective) optimization is considered.

Thereby, the resolution of a monoobjective optimization problem consists in finding the feasible solution that minimizes the objective function. In the multiobjective context, the problem resolution aims at finding a set of Pareto optimal solutions, which is called the *Pareto front*.

Following the complexity of the problem, two main families of resolution methods can be used: *exact methods* and *heuristics*. Figure 1.1 illustrates the different methods of resolution. Exact methods (e.g. branch-and-x, dynamic programming or constraints programming) allow to find optimal solutions and guarantee their optimality. However, they become impractical for large problems.

Conversely, heuristics produce high-quality solutions in a reasonable time practical use on

large-size problem instances. Heuristics can be *specific* i.e. designed to solve a particular problem and/or instance. They can also be generic and applicable to different problem types. In this case, they are called *metaheuristics*. These latter are based on the iterative improvement of either a single solution (e.g. hill climbing, simulated annealing or tabu search) or a population of solutions (e.g. evolutionary algorithms or ant colonies) of a given optimization problem. In this document, the focus will be exclusively on metaheuristics.

#### 1.1.2 **Principles of Metaheuristics**

Unlike exact methods, metaheuristics allow to tackle large-size problem instances by delivering satisfactory solutions in a reasonable time. There is no guarantee to find global optimal solutions or even bounded solutions. Metaheuristics have received more and more popularity in the past 20 years. Their use in many applications shows their efficiency and effectiveness to solve large and complex problems. Metaheuristics fall into two categories: *single-solution based metaheuristics* (S-metaheuristics) and *population-based metaheuristics* (P-metaheuristics).

S-metaheuristics manipulate and transform a single solution during the search, while in P-metaheuristics a whole population of solutions is evolved. These two families have complementary characteristics: S-metaheuristics are exploitation oriented; they have the ability to intensify the search in local regions. P-metaheuristics are exploration oriented; they provide a better diversification in the entire search space. In the next chapters of this document, we will mainly use this classification.

#### 1.1.2.1 Solution Representation

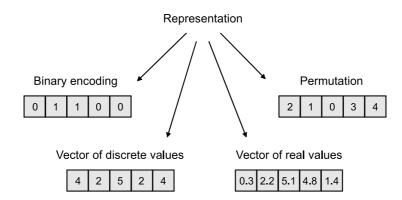

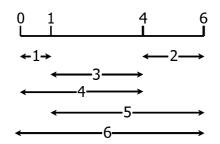

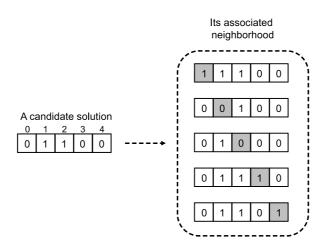

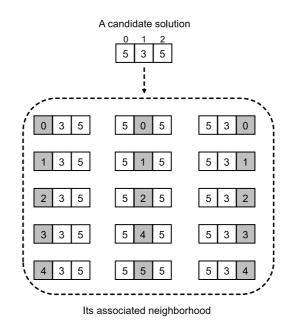

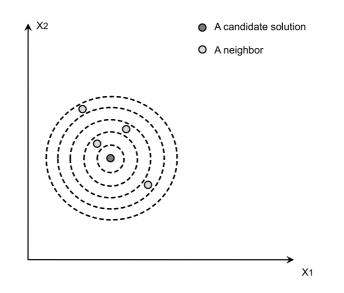

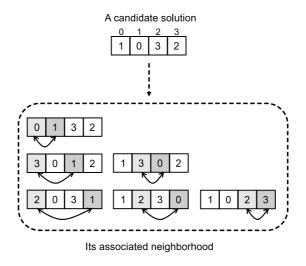

Designing any iterative metaheuristic requires an encoding (representation) of a solution. The encoding plays a major role in the efficiency and effectiveness of any metaheuristic, so it constitutes an essential step in designing a metaheuristic. The encoding must be suitable and relevant to the optimization problem at hand. Moreover, the quality of a representation has a considerable influence on the efficiency of the search operators applied on this representation. Four major encodings in the literature can be highlighted: binary encoding (e.g. knapsack, satisfiability), vector of discrete values (e.g. location problem, assignment problem), permutation (e.g. traveling salesman problem, scheduling problems) and vector of real values (e.g. continuous functions). Figure 1.2 illustrates an example of each representation.

Figure 1.2: Major encodings for optimization problems.

#### 1.1.2.2 Evaluation Function

The objective function f formulates the goal to be achieved. It associates with each solution of the search space a real value that gives the quality or the *fitness* of the solution,  $f: S \to \mathbb{R}$ . Then, it represents an absolute value and allows a complete ordering of all solutions of the search space. The objective function is an essential element in designing a metaheuristic. It guides the search toward "good" solutions of the search space. If the objective function is improperly defined, it can lead to non-acceptable solutions whatever is the used metaheuristic.

#### 1.1.2.3 Principles of S-metaheuristics

S-metaheuristics are iterative techniques that have been successfully applied for solving many real and complex problems. These methods could be viewed as "walks through neighborhoods" meaning search trajectories through the solutions domains of the problems at hand. The walks are performed by iterative procedures that allow to move from a solution to another one in the solution space (see Algorithm 1).

A S-metaheuristic usually starts with a randomly generated solution. At each iteration of the algorithm, the current solution is replaced by another one selected from the set of its neighboring candidates, and so on. An evaluation function associates a fitness value to each solution indicating its suitability to the problem (selection criterion). Many strategies related to the considered S-metaheuristic can be applied in the selection of a move: best improvement, first improvement, random selection, etc.

The simplest S-metaheuristic is the hill climbing algorithm (see Algorithm 2). It starts with at a given solution. At each iteration, the heuristic replaces the current solution by a neighbor that improves the objective function. The search stops when all candidate neighbors are worse than the current solution, meaning a local optimum is reached. Another widespread method is the tabu search algorithm [Glo89, Glo90] (see Algorithm

Algorithm 1 S-metaheuristic pseudo-code.

```

1: Generate(s_0);

2: Specific S-metaheuristic pre-treatment

3: t := 0;

4: repeat

5: m(t) := \text{SelectMove}(s(t));

6: s(t+1) := \text{ApplyMove}(m(t), s(t));

7: Specific S-metaheuristic post-treatment

8: t := t + 1;

```

9: **until** Termination\_criterion(s(t))

Algorithm 2 Hill climbing pseudo-code

1: Generate $(s_0)$ ; 2: t := 0; 3: **repeat** 4: m(t) := SelectBestMove(s(t)); 5: s(t+1) := ApplyMove(m(t), s(t)); 6: t := t + 1; 7: **until** Local\_optimum(s(t))

3). In this local search, the best solution in the neighborhood is selected as the new current solution even if it is not improving the current solution. This policy may generate cycles, i.e. previous visited solutions could be selected again. To avoid these cycles, the algorithm manages a memory of the moves recently applied, which is called the *tabu list*. This list is a short-term memory which contains the solutions (moves) that have been visited in the recent past.

#### Algorithm 3 Tabu search pseudo-code

1: Generate $(s_0)$ ; 2: InitTabuList $(l_0)$ ; 3: t := 0; 4: repeat 5: m(t) := SelectBestAdmissibleMove(s(t)); 6: s(t+1) := ApplyMove(m(t), s(t)); 7: l(t+1) := UpdateTabuList(l(t)); 8: t := t + 1; 9: until Termination\_criterion(s(t))

Other popular examples of S-meheuristics are simulated annealing, iterative local search and variable neighborhood search. A survey of the history and a state-of-the-art of Smetaheuristics can be found in [DPST06, Tal09].

#### 1.1.2.4 Principles of P-metaheuristics

P-metaheuristics are recognized as promising methods for solving complex problems in science and industry. They start from an initial population of solutions. Then, they iteratively apply the generation of a new population and the replacement of the current population. In the generation phase, a new population of solutions is created. In the replacement phase, a selection is carried out from the current and the new populations. This process iterates until a given stopping criterion is satisfied. Popular examples of P-metaheuristics are evolutionary algorithms, and colony optimization, scatter search and particle swarm optimization. A review of these methods is available in [Tal09]. Algorithm 4 illustrates the high-level template of P-metaheuristics.

#### Algorithm 4 P-metaheuristics pseudo-code.

1: Generate( $P_0$ ); 2: t := 0; 3: **repeat** 4: Generate(P'(t)); 5: P(t+1) := Replace(P(t), P'(t)); 6: t := t + 1; 7: **until** Termination\_criterion(P(t))

One of the best-known P-metaheuristics concerns evolutionary algorithms. These latter are stochastic search techniques that have been successfully applied for solving many real and complex problems. An evolutionary algorithm is an iterative technique that applies stochastic operators on a pool of individuals (see Algorithm 5). Every individual in the population is the encoded version of a tentative solution. Initially, this population is usually generated randomly. At each generation of the algorithm, solutions are selected, paired and recombined in order to generate new solutions that replace worse ones according to some criteria, and so on. An evaluation function associates a fitness value to every individual indicating its suitability to the problem (selection criterion).

#### Algorithm 5 Evolutionary algorithms pseudo-code.

1: Generate( $P_0$ ); 2: t := 0; 3: **repeat** 4: P'(t) := Selection(P(t));5: P'(t) := ApplyReproductionOps(P'(t));6: P(t+1) := Replace(P(t), P'(t));7: t := t + 1;8: **until** Termination\_criterion(P(t))

There exists several well-accepted subclasses of evolutionary algorithms depending on rep-

resentation of the individuals or how each step of the algorithm is designed. The main subclasses of evolutionary algorithms are the genetic algorithms, genetic programming, evolution strategies, etc. A large review of these evolutionary computation techniques is done in [BFM97].

#### 1.1.3 Parallel Models of Metaheuristics

Although the use of metaheuristics allows to considerably reduce the computational complexity of the search process, the latter remains time-consuming for many problems in diverse domains of application. In particular, in the case where the objective function and the constraints associated with the problem are resource-intensive, and the size of the search space is huge. For nontrivial problems, executing the iterative process of a simple S-metaheuristic on large neighborhoods requires a large amount of computational resources. The same phenomenon occurs when executing the reproductive cycle of a simple P-metaheuristic on long individuals and/or large populations.

In general, evaluating a fitness function for each solution is frequently the most costly operation of the metaheuristic. Consequently, a variety of algorithmic issues is being studied to design efficient heuristics. These issues commonly consist of defining new move operators, hybrid algorithms, parallel models, and so on. Parallelism arises naturally when dealing with a population of solutions (or a neighborhood), since each of the solutions belonging to it is an independent unit. Due to this, the performance of metaheuristics is significantly improved when running in parallel.

Parallel and distributed computing can be used in the design and implementation of metaheuristics for the following reasons:

- Speed up the search: One of the main goals of parallelizing a metaheuristic is to reduce the search time. This helps designing real-time and interactive optimization methods. This is a crucial aspect for some class of problems where there are hard requirements on the search time.

- Improve the quality of the obtained solutions: Some parallel models for metaheuristics allow to improve the quality of the search. Indeed, exchanging information between cooperative metaheuristics will alter their behavior in terms of searching in the landscape associated with the problem. The main goal of a parallel cooperation between metaheuristics is to improve the quality of solutions.

- *Improve the robustness:* A parallel metaheuristic may be more robust in terms of solving in an effective manner different optimization problems and different instances of a given problem. Robustness may also be measured in terms of the sensitivity of the metaheuristic to its parameters.

Figure 1.3: Parallel models of local search metaheuristics.

• Solve large-scale problems: Parallel metaheuristics allow to solve large-scale instances of complex optimization problems. An issue is to solve very large instances that cannot be solved by a sequential machine. Another similar challenge is to solve more accurate mathematical models associated with different optimization problems.

In this purpose, three major parallel models for metaheuristics can be distinguished: solution-level, iteration-level and algorithmic-level (see Figure 1.3).

- Solution-level Parallel Model. The focus is on the parallel evaluation of a single solution. Problem-dependent operations performed on solutions are parallelized. That model is particularly interesting when the evaluation function can be itself parallelized as it is CPU time-consuming and/or IO intensive. In that case, the function can be viewed as an aggregation of a given number of partial functions.

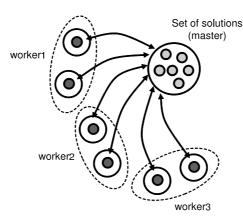

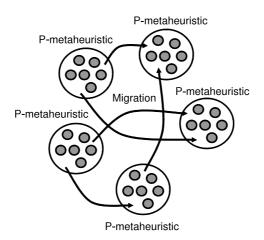

- Iteration-level Parallel Model. This model is a low-level Master-Worker model that does not alter the behavior of the heuristic. The evaluation of solutions is performed in parallel. At the beginning of each iteration, the master duplicates the solutions to be evaluated between parallel nodes. Each of them manages some candidates, and the results are returned back to the master. An efficient execution is often obtained especially when the evaluation of each solution is costly.

- Algorithmic-level Parallel Model. Several metaheuristics are simultaneously launched for computing better and robust solutions. They may be heterogeneous or homo-

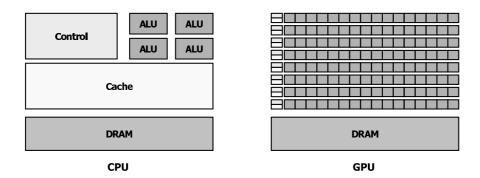

Figure 1.4: Repartition of transistors for CPU and GPU architectures.

geneous, independent or cooperative, start from the same or different solution(s), configured with the same or different parameters.

From a parallelization point of view, the solution-level model is problem-dependent and does not present many generic concepts. As a consequence, in this document, we will not deal with this parallel model.

### **1.2** Metaheuristics and GPU Computing

Most personal computers integrated with GPUs are usually far less powerful than their add-in counterparts. That is the reason why it would be very interesting to exploit this enormous capacity of computing to implement parallel metaheuristics. In this section, the focus is on the description of GPU computing. A clear understanding of GPU characteristics is required to provide an efficient implementation of parallel metaheuristics.

#### 1.2.1 GPU Architecture

For years, the use of graphics processors was dedicated to graphics applications. Driven by the demand for high-definition 3D graphics on personal computers, GPUs have evolved into a highly parallel, multithreaded and many-core environment. Indeed, this architecture provides a tremendous computational horsepower and a very high memory bandwidth compared to traditional CPUs. Figure 1.4 illustrates the repartition of transistors between the two architectures.

One can see that a CPU does not have a lot of arithmetic-logic units (ALU), but a large cache and an important control unit. As a result, the CPU is specialized to manage multiple and different tasks in parallel that require lots of data. Thereby, data are stored within a cache to accelerate its accesses. The control unit will handle the instructions flow to maximize the occupation of arithmetic-logic units, and to optimize the cache management.

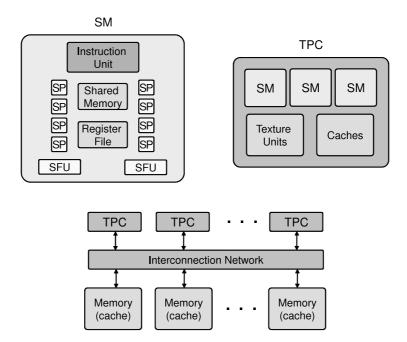

Figure 1.5: General GPU architecture composed of streaming multiprocessors.

Conversely, a GPU has a large number of arithmetic units with a limited cache and few control units. This allows the GPU to calculate in a massive and parallel way the rendering of small and independent elements, while having a large flow of data processed. Since more transistors are devoted to data processing rather than data caching and flow control, GPU is specialized for compute-intensive and highly parallel computations.

Figure 1.5 depicts the general GPU architecture. It is composed of streaming multiprocessors (SMs), each containing a certain number of streaming processors (SPs), or processor cores. Each core executes a single thread instruction in a SIMD (single-instruction multiple-data) fashion, with the instruction unit distributing the current instruction to the cores. Each core has one multiply-add arithmetic unit that can perform single-precision floating-point operations or 32-bit integer arithmetic. In addition, each SM has special functional units (SFUs), which execute more complex floating-point operations such as reciprocal sine, cosine and square root with low cycle latency.

The SM contains other resources such as shared memory and the register file. Groups of SMs belong to thread processing clusters (TPCs). The latter also contain resources (e.g. caches and texture fetch units) that are shared among the SMs. The GPU architecture comprises the collection of TPCs, the interconnection network, and the memory system (DRAM memory controllers).

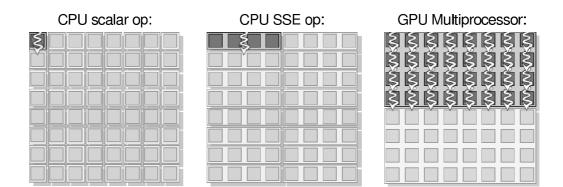

Figure 1.6 gives a comparison of the execution model for both CPU and GPU architectures. Basically, a CPU thread proceeds one data element per operation. With the extension of

CHAPTER 1: GPU COMPUTING FOR PARALLEL METAHEURISTICS

Figure 1.6: Comparison of CPU and GPU execution models.

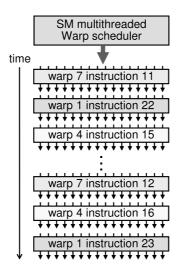

SSE (streaming SIMD execution) instructions, such a CPU thread can operate between two and four data elements. Regarding a GPU multiprocessor, 32 threads proceed 32 data elements. These groups of 32 threads are called *warps*. They are exposed as individual threads but execute the same instruction. Therefore, a divergence in the threads execution provokes a serialization of the different instructions.

A complete review of GPU architectures can be found in [RRS<sup>+</sup>08, ND10].

#### **1.2.2** GPU Challenges for Metaheuristics

Parallel combinatorial optimization on GPU is not straightforward and requires a huge effort at design as well as at implementation level. Indeed, several scientific challenges mainly related to the hierarchical memory management have to be achieved. The major issues are the efficient distribution of data processing between CPU and GPU, the thread synchronization, the optimization of data transfer between the different memories, the capacity constraints of these memories, etc. Such issues must be taken into account for the redesign of parallel metaheuristic models in order to solve large scale optimization problems on GPU architectures.

We aim at identifying such issues for building efficient parallel metaheuristics on GPU:

- 1. Cooperation between the CPU and the GPU. Such a step requires defining the task repartition in metaheuristics. In this purpose, the optimization of data transfer between the two components is necessary to achieve the best performance.

- 2. **Parallelism control**. GPU computing is based on massively parallel multi-threading, and the order in which the threads are executed is not known. Therefore, on the one hand, an efficient thread control must be applied to meet the memory constraints. On the other hand, an efficient mapping has to be defined between each candidate solution and a thread designated by a unique identifier assigned at GPU runtime.

3. Memory management. Optimizing the performance of GPU applications often involves optimizing data accesses which includes the appropriate use of the various GPU memory spaces. The different optimization structures have to be placed efficiently on the different memories taking into account their sizes and access latencies.

The contribution of this document is to deal with these challenges. Throughout this manuscript, we will mainly use this classification. The next sections provide more details about these different challenges.

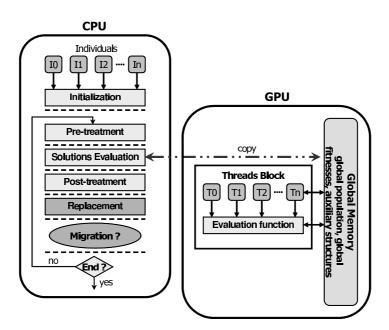

#### 1.2.3 General GPU Model: CPU-GPU Cooperation

In general-purpose computing on graphics processing units, the CPU is considered as a host and the GPU is used as a device coprocessor. This way, each GPU has its own memory and processing elements that are separate from the host computer. Data must be transferred between the memory space of the host and the memory of GPU during the execution of programs.

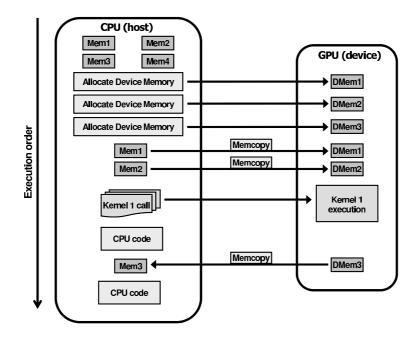

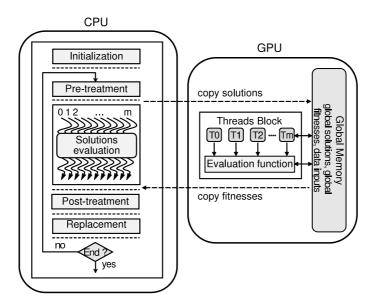

Each processor device on GPU supports the single program multiple data (SPMD) model, i.e. multiple autonomous processors simultaneously execute the same program on different data. For achieving this, the concept of kernel is defined. The kernel is a function callable from the host and executed on the specified device simultaneously by several processors in parallel. Figure 1.7 illustrates an example of the general GPU model.

Memory transfer from the CPU to the device memory is a synchronous operation which is time consuming. Indeed, PCI-e bus bandwidth and latency between CPU and GPU can significantly reduce the performance of the search. As a result, one objective when programming GPU applications is to establish an efficient task repartition. In this purpose, the optimization of data transfer between CPU and GPU is clearly an issue to be tackled.

#### 1.2.4 GPU Threads Model: Parallelism Control

The kernel handling is dependent of the general-purpose language. For instance, CUDA [NVI11] or OpenCL [Gro10] are parallel computing environments which provide an application programming interface for GPU architectures. Indeed, these toolkits introduce a model of threads which provides an easy abstraction for SIMD architectures. The concept of a GPU thread does not have exactly the same meaning as a CPU thread. A thread on GPU can be seen as an element of data to be processed. Compared to CPU threads, GPU threads are lightweight. It means that changing the context between two threads is not a costly operation.

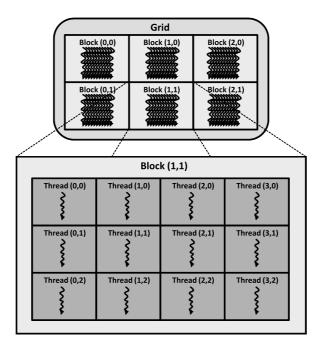

Regarding their spatial organization, threads are organized within so called thread blocks (see Figure 1.8). A kernel is executed by multiple equally threaded blocks. Blocks can be

Figure 1.7: Illustration of the general GPU model. The GPU can be seen as a coprocessor where data transfers must be performed between the CPU and the GPU.

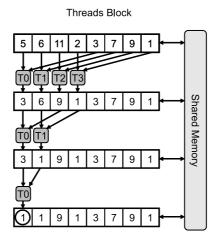

organized into a one-dimensional or two-dimensional grid of thread blocks, and threads inside a block are grouped in a similar way. Each thread is provided with a unique *id* that can be used to compute on different data. The advantage of grouping is that the number of blocks processed simultaneously by the GPU is closely linked to hardware resources. All the threads belonging to the same thread block will be assigned as a group to a single multiprocessor, while different thread blocks can be assigned to different multiprocessors. Hence, a major issue is to control the threads parallelism to meet the memory constraints.

#### 1.2.5 Kernel Management: Memory Management

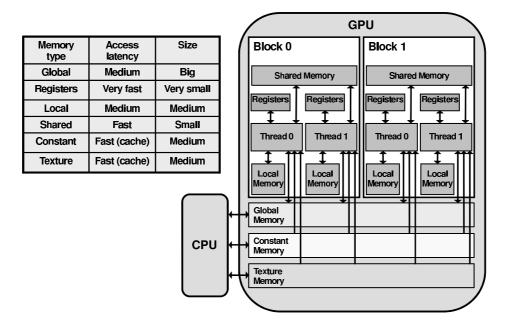

From a hardware point of view, graphics cards consist of streaming multiprocessors, each with processing units, registers and on-chip memory. Since multiprocessors are organized according to the SPMD model, threads share the same code and have access to different memory areas. Figure 1.9 illustrates these different available memories and connections with thread blocks.

Communication between the CPU host and its device is done through the global memory. Since in some GPU configurations, this memory is not cached and its access is slow, one needs to minimize accesses to global memory (read/write operations) and reuse data within the local multiprocessor memories. Graphics cards provide also read-only texture memory to accelerate operations such as 2D or 3D mapping. Texture memory units are provided to

Figure 1.8: GPU threads model. GPU threads are organized into block structures.

Figure 1.9: GPU memory model. Different on-chip memories and connections with thread blocks are available.

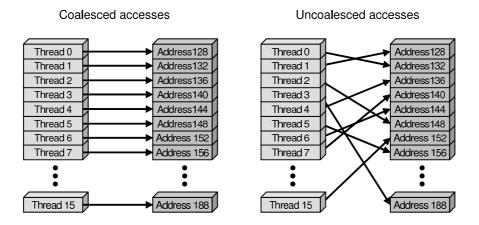

Figure 1.10: Illustration of accesses patterns that lead to coalesced and uncoalesced accesses to the global memory.

allow faster graphic operations. This way, binding texture on global memory can provide an alternative optimization. Indeed, it improves random accesses or uncoalesced memory access patterns that occur in common applications. Constant memory is read only from kernels and is hardware optimized for the case where all threads read the same location. Shared memory is a fast memory located on the multiprocessors and shared by threads of each thread block. This memory area provides a way for threads to communicate within the same block. Registers among streaming processors are exclusive to an individual thread; they constitute a fast access memory. In the kernel code, each declared variable is automatically put into registers. Local memory is a memory abstraction and is not an actual hardware component. In fact, local memory resides in the global memory allocated by the compiler. Complex structures such as declared arrays will reside in local memory.

Regarding the execution model, each block of threads is split into SIMD groups of threads called warps. At any clock cycles, each processor of the multiprocessor selects a warp that is ready to execute the same instruction on different data. For being efficient, global memory accesses must be coalesced. This means that a memory read by consecutive threads in a warp is combined by the hardware into several memory reads. The requirement is that threads of the same warp must read global memory in an order manner (see Figure 1.10). Global memory accesses patterns that are non-coalesced may significantly decrease the performance of a program. As a result, an efficient management of the optimization structures with the different available memories has to be considered.

## **1.3** Related Works on Parallel Metaheuristics

#### 1.3.1 Metaheuristics on Parallel and Distributed Architectures

The rapid development of technology in designing processors (e.g. multicore processors and dedicated architectures), networks (e.g. local area networks such as Myrinet and Infiniband or wide area networks such as optical networks), and data storage, has made the use of parallel computing more and more popular. Such evolution raises new challenges for the design and implementation of parallel metaheuristics. Indeed, sequential architectures are reaching physical limitation. Nowadays, even laptops and workstations are equipped with multicore processors, which represent a given class of parallel architectures. Moreover, the cost/performance ratio is constantly decreasing. The proliferation of powerful workstations and fast communication networks has shown the emergence of clusters of processors (COWs), networks of workstations, and large-scale network of machines (grids) as platforms for high-performance computing.

During these two last decades, many parallel approaches and implementations have been proposed for metaheuristics [ABR03, ALNT04, AT02, AK96, BHX00, CB96, CG02, CGHM04, GrTA99, GLMBMPMV03, HL00, LL96, RL02, PDB10, SBA97]. Some of them using massively parallel processors [CSK93], clusters of workstations [CTG95, GPR94, BSB<sup>+</sup>01] and shared memory or SMP machines [JRG09, Bev02]. These contributions have been later revisited for large-scale computational grids [TMT07].

These architectures often exploit the coarse-grained asynchronous parallelism based on work-stealing. This is particularly the case for computational grids. To overcome the problem of network latency, the grain size is often increased, limiting the degree of parallelism.

Recently, GPU accelerators have emerged as a powerful support for massively parallel computing. Indeed, these architectures offer a substantial computational horsepower and a remarkably high memory bandwidth compared to CPU-based architectures. For instance, the parallel evaluation of the solutions (iteration-level) is a Master-Worker and a problem-independent, regular data-parallel application. Therefore, GPU computing may be highly efficient in executing such synchronized parallel algorithms that involve regular computations and data transfers.

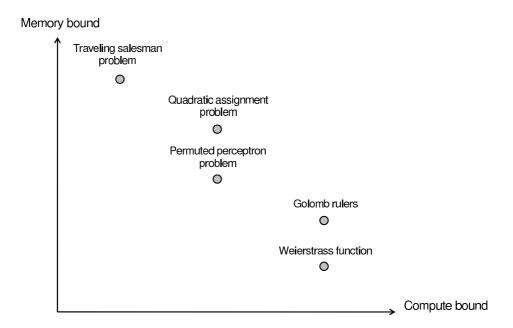

In general, for distributed architectures, the global performance in metaheuristics is limited by high communication latencies whilst it is just bounded by memory access latencies in GPU architectures. Indeed, when evaluating solutions in parallel, the main obstacle in distributed architectures is the communication efficiency. GPUs are not that versatile.

However, since the execution model of GPUs is purely SIMD, it may not be well-adapted for few irregular problems in which the execution time cannot be predicted at compile time and varies during the search. For instance, this happens when the evaluation cost of the objective function depends on the solution. When dealing with such problems in which the computations or the data transfers become irregular or asynchronous, parallel and distributed architectures such as COWs or computational grids may be more appropriate.

#### **1.3.2** Research Works on GPU-based Metaheuristics

With the emergence of standard programming languages on GPU and the arrival of compilers for these languages, combinatorial optimization on GPU has generated a growing interest. Historically, due to their embarrassingly parallel nature, P-metaheuristics such as evolutionary algorithms have been the first subject of parallelization on GPU architectures. One of the first pioneering works on genetic algorithms was proposed by Wong et al. [WWF05, WW06, FWW07]. In their works, the population evaluation and a specific mutation operator (Cauchy mutation) are performed on GPU. However, since replacement and selection operators are implemented on CPU, massive data transfers are performed between the CPU and the GPU. Such techniques limit the performance of the algorithm. Concurrently, to deal with this drawback, Yu et al. [YCP05] were the first authors to establish a full parallelization of the genetic process on GPU. To achieve this, the population is organized into a 2D toroidal grid, which allows to apply selection operators similar to those ones used for cellular genetic algorithms. However, the implementation is only specific to a vector of real values. Later, Li et al. [LWHC07] extended this work for binary representations, and implemented further specific genetic operators. In a similar manner, Luo et al. [LL06] were among the first authors to implement a cellular genetic algorithm on GPU for the 3-SAT problem. To perform this, the semantics of the original cellular algorithm are completely modified to meet the GPU constraints.

The previous implementations quoted above are based on a transformation of evolutionary structures into a series of raster operations on GPU using shader libraries based on Direct3D or OpenGL. In other words, to implement metaheuristics with such libraries, one needs to solve the problem of texture storage of relevant information in arrays.

The following works on GPU are implemented with the CUDA development toolkit, which allows programming on GPUs in a more accessible C-like language. In addition to this, such a thread-based approach is easier in terms of reproducibility in comparison with shader libraries.

Zhu suggested in [Zhu09] an evolution strategy algorithm to solve a bench of continuous problems using the CUDA toolkit. In his implementation, multiple kernels are designed for some evolutionary operators such as the selection, the crossover, the evaluation and the mutation. The rest of the search process is handled by the CPU.

Later, Arora et al. presented a similar implementation in [ATD10] for genetic algorithms.

In addition, the contribution of their work is to investigate the effect of a bench of parameters (e.g. threads size, problem size or population size) on the acceleration of their GPU implementation in regards with a sequential genetic algorithm.

Tsutsui *et al.* were among the first authors to establish memory management concepts of combinatorial optimization problems [TF09]. In their implementation for the quadratic assignment problem, accesses to the global memory (the population) are coalesced, the shared memory is used to store as many individuals as possible, and matrices are associated with the constant memory. Their approach is based on a full parallelization of the search process to deal with data transfers. For doing that, the global genetic algorithm is divided into multiple independent genetic algorithms, where each sub-population represents a thread block. The obtained speed-ups are of course less convincing than for continuous problems, due to the management of data structures in combinatorial problems.

In [MBL<sup>+</sup>09], Maitre *et al.* submitted a framework tentative for the automatic parallelization of the evaluation function on GPU. In this purpose, the user does not need to know about any CUDA keywords and only the evaluation function code must be specified. Such a strategy allows to evaluate the population in a transparent way on GPU. However, this automatic parallelization presents some drawbacks. Indeed, it lacks flexibility due to the data transfers and non-optimized memory accesses. Moreover, the application is restricted to problems which do not require any data structures (e.g. continuous problems).

Another framework tentative were introduced in [SBPE10] by Soca *et al.* for cellular genetic algorithms. Multiple kernels are used for each evolutionary operator. The platform offers a collection of predetermined operators (three crossovers and two mutations) that the user must instantiate. In addition, management of problem structures in global memory seems to be taken into account since an application to the quadratic assignment problem is done. Unfortunately, unless the previous one, the framework seems to remain in the design step since no link is available for downloading.

Another implementation of a cellular evolutionary algorithm is provided by Vidal *et al.* in [VA10a]. It is based on a full parallelization of the search process on GPU. An application of the approach is made for continuous and discrete problems without any problem structures. Later, the authors submitted a multi-GPU implementation of their algorithm in [VA10b]. Nevertheless, due to the challenging issue of the context management (e.g. two separate GPU global memories), their multi-GPU implementation does not provide any significant benefits in terms of performance.

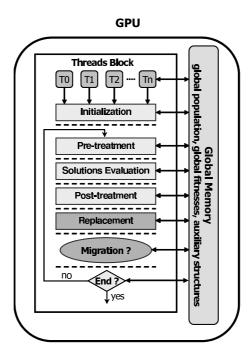

Zhang *et al.* introduced a design of an island model on GPU in [ZH09]. The parallelization of the entire algorithm is performed on GPU. Each sub-population is stored on the shared memory. Regarding the topology of the different islands, they are similar to the exchange topology present in cellular evolutionary algorithm (toroidal grid). Unfortunately, the model only remains in the design step since the authors did not produce any experimental results.

Pospichal *et al.* performed an implementation similar to the previous model for continuous optimization problems in [PJS10]. Each sub-population is stored on the shared memory and organized according to a ring topology. The obtained speed-ups are impressive in comparison with a sequential algorithm (thousands of times). However, the implementation is only dedicated to few continuous optimization problems.

Since no general methods can be outlined from the two previous works, we investigated the parallel island model on GPU in [6]. We addressed its redesign, implementation, and associated issues related to the GPU execution context. In this purpose, we designed three parallelization strategies involving different memory managements. We demonstrated the effectiveness of the proposed approaches and their capabilities to fully exploit the GPU architecture.

Regarding S-metaheuristics, Janiak *et al.* implemented a multi-start tabu search algorithm applied to the traveling salesman problem and the flowshop scheduling problem [JJL08]. Using shader libraries, the parallelization is entirely performed on GPU, and each thread process is associated with one tabu search. However, such a parallelization is not effective since a large number of local search algorithms is required to cover the memory access latency.

Concurrently, a similar approach based on the CUDA toolkit was proposed by Zhu *et al.* [ZCM08]. The implementation has been applied to the quadratic assignment problem, where the memory management of optimization structures is made on the global memory. Nevertheless, the global performance is limited to the instance size, since each thread is associated with one local search.

Although the multi-start model has already been applied in the context of the tabu search on GPU, it has never been widely investigated in terms of reproducibility and memory management. We provided in [5] a general methodology for the design of multi-start algorithms applicable to any local search algorithms such as hill climbing, tabu search or simulated annealing. Furthermore, we contributed with efficient associations between the different available memories and the data commonly used for these algorithms.

However, as quote above, the application of the multi-start model on GPU is limited since a large number of local search algorithms is required at launch time to be effective. As a matter of fact, the parallelization of the evaluation of neighborhood on GPU might be more valuable. In this purpose, we came up with the pioneering work in [9] on the redesign of the parallel evaluation of the neighborhood on GPU. We introduced the generation of neighbors on the GPU side to minimize the data transfers. Furthermore, we proposed to manage the commonly used structures in combinatorial optimization with the different available memories.

Munawar *et al.* introduced a hybrid genetic algorithm on GPU in [MWMA09a]. In their implementation, an island model is implemented where each population represents a cellular genetic algorithm. In addition to this, a hill climbing algorithm follows the mutation step of the hybrid genetic algorithm. Each sub-population is associated with the shared memory and traditional code optimization such as memory coalescing is performed. The implementation is performed for the maximum satisfiability problem.

Since a full parallelization is investigated, the previous work requires that the hill climbing must be combined with the island model. To perform a hybridization with a local search in the general case, we contributed with the redesign of hybrid evolutionary algorithms on GPU in [7]. In this purpose, the focus is on the generation of the different neighborhoods on GPU, corresponding to each individual of the evolutionary process to be mutated. Such a mechanism guarantees more flexibility since any local search algorithms can be broached with any evolutionary algorithms.

Wong was the first author to introduce a multiobjective evolutionary algorithm on GPU in [Won09]. In his implementation, most of the multiobjective algorithm (NSGA-II) is implemented on GPU except the selection of non-dominated solutions.

In a similar manner, we contributed in [3] with the first multiobjective local search algorithms on GPU. The parallelization strategy is based on the parallel evaluation of the neighborhood on GPU using a set of non-dominated solutions to generate the neighborhood.

Table 1.1 reports the major works on GPU according to the classification proposed in Section 1.2.2. Basically, most approaches of the literature are based on either the parallel evaluation of solutions on GPU (iteration-level) or the execution of simultaneous independent/cooperative algorithms (algorithmic-level). Regarding the CPU-GPU cooperation, for the first category, some implementations also consider the parallelization of other treatments on GPU (e.g. selection or variation operators in evolutionary algorithms). One may argue on the validity of these choices since an execution profiling may show that such treatments are negligible in comparison with the evaluation of solutions. As quoted above, a full parallelization of metaheuristics on GPU may be also performed to reduce the data transfers between the CPU and the GPU. In this case, the original semantics of the metaheuristic are modified to fit the GPU execution model. This can explain the reason why an important group of works only deals with concurrent independent/cooperative algorithms. For the parallelism control, most implementations associate one thread with one solution. In addition, some cooperative algorithms may take advantage of the threads model by associating one threads block with one sub-population. However, to the best of our knowledge, no work has been investigated to efficiently manage the threads parallelism to

| Authors                               | CPU-GPU                                       | Parallelism                                       | Memory                                | Optimization                                       |

|---------------------------------------|-----------------------------------------------|---------------------------------------------------|---------------------------------------|----------------------------------------------------|

|                                       | cooperation                                   | control                                           | management                            | problems                                           |

| Wong et al.<br>[WWF05, WW06, FWW07]   | evaluation and<br>mutation on GPU             | panmictic<br>one thread per individual            | texture                               | continuous                                         |

| Yu et al. [YCP05]                     | full parallelization<br>on GPU                | 2D toroidal grid<br>one thread per individual     | texture                               | continuous                                         |

| Li et al. [LWHC07]                    | full parallelization<br>on GPU                | 2D toroidal grid<br>one thread per individual     | texture                               | continuous<br>and binary                           |

| Luo et al. [LL06]                     | full parallelization<br>on GPU                | cellular<br>one thread per individual             | texture                               | 3-SAT                                              |

| Zhu [Zhu09]                           | evaluation, selection<br>and variation on GPU | 2D toroidal grid<br>one thread per individual     | global, shared<br>and texture memory  | continuous                                         |

| Arora et al. [ATD10]                  | evaluation, selection<br>and variation on GPU | 2D toroidal grid<br>one thread per individual     | global and<br>shared memory           | continuous<br>and binary                           |

| Tsutsui et al. [TF09]                 | full parallelization<br>on GPU                | 2D toroidal grid<br>one block per population      | global, constant<br>and shared memory | quadratic assignment<br>problem                    |

| Maitre $et al.$ [MBL <sup>+</sup> 09] | evaluation<br>on GPU                          | panmictic<br>one thread per individual            | global memory                         | continuous                                         |

| Soca et al. [SBPE10]                  | evaluation and<br>variation on GPU            | cellular<br>one thread per individual             | global and<br>shared memory           | quadratic assignment<br>problem                    |

| Vidal et al. [VA10a]                  | full parallelization<br>on GPU                | cellular<br>one thread per individual             | global and<br>shared memory           | continuous<br>and discrete                         |

| Zhang et al. [ZH09]                   | full parallelization<br>on GPU                | island model<br>one block per population          | global and<br>shared memory           | -                                                  |

| Pospichal et al. [PJS10]              | full parallelization<br>on GPU                | island model<br>one block per population          | global and<br>shared memory           | continuous                                         |

| Luong et al. [6]                      | evaluation and<br>full parallelization on GPU | island model<br>one block per population          | global and<br>shared memory           | continuous                                         |

| Janiak et al. [JJL08]                 | full parallelization<br>on GPU                | multi-start<br>one thread per algorithm           | texture                               | traveling salesman problem<br>and flowshop problem |

| Zhu et al. [ZCM08]                    | full parallelization<br>on GPU                | multi-start<br>one thread per algorithm           | global memory                         | quadratic assignment<br>problem                    |

| Luong $et al.$ [5]                    | full parallelization<br>on GPU                | multi-start<br>one thread per algorithm           | global and<br>texture memory          | quadratic assignment<br>problem                    |

| Luong et al. [9]                      | generation and<br>evaluation on GPU           | neighborhood<br>one thread per neighbor           | global and<br>texture memory          | permuted perceptron<br>problem                     |

| Munawar <i>et al.</i> [MWMA09a]       | full parallelization<br>on GPU                | island model+cellular<br>one block per population | global and<br>shared memory           | maximum satisfiability<br>problem                  |

| Luong et al. [7]                      | generation and<br>evaluation on GPU           | neighborhood<br>one thread per neighbor           | global and<br>texture memory          | quadratic assignment<br>problem                    |

| Wong [Won09]                          | evaluation, selection<br>and variation on GPU | panmictic<br>one thread per individual            | global and<br>shared memory           | continuous                                         |

| Luong $et al.$ [3]                    | generation and<br>evaluation on GPU           | neighborhood<br>one thread per neighbor           | global and<br>texture memory          | flowshop scheduling<br>problem                     |

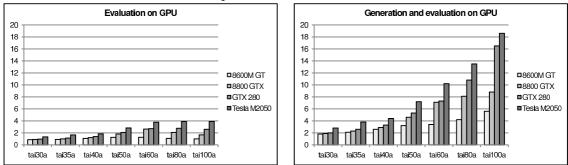

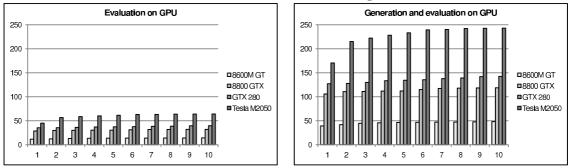

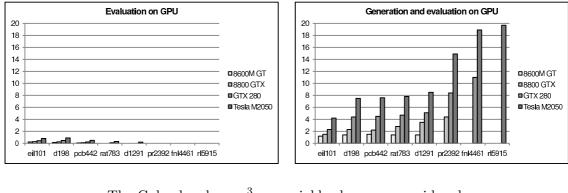

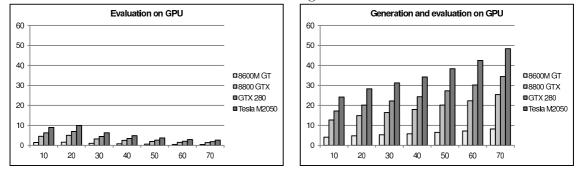

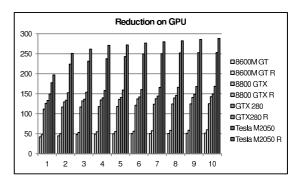

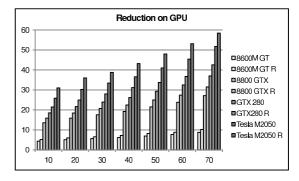

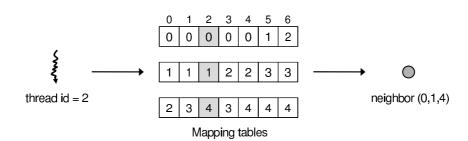

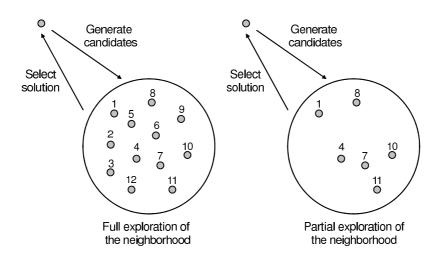

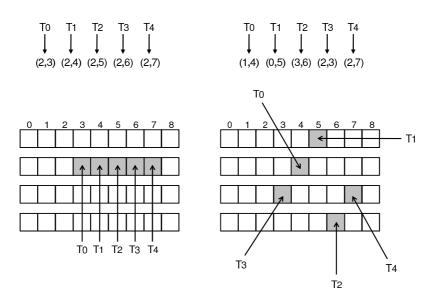

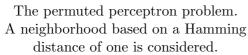

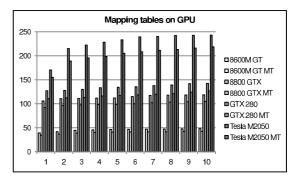

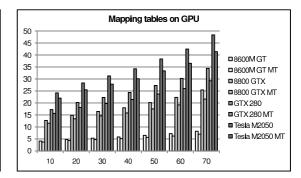

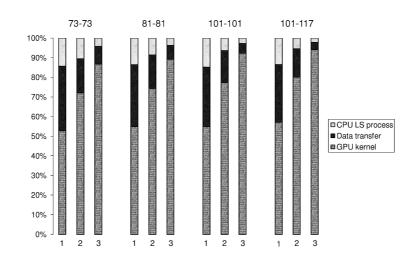

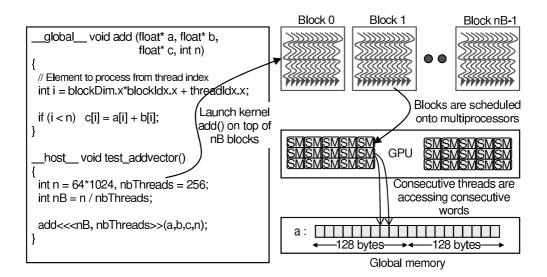

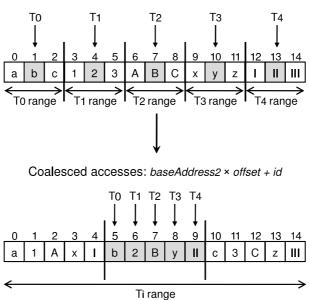

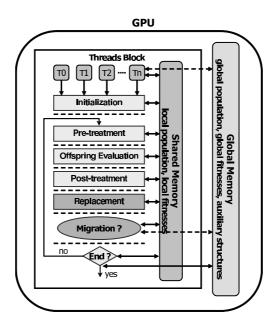

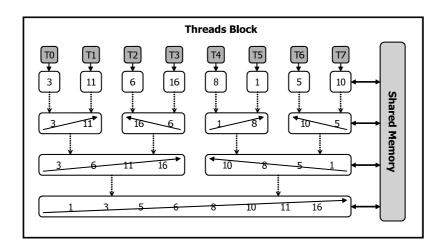

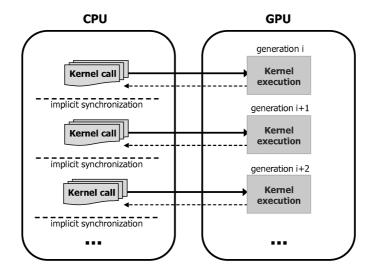

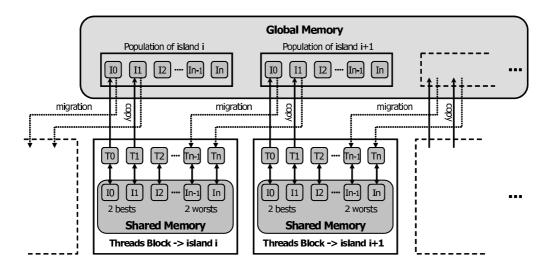

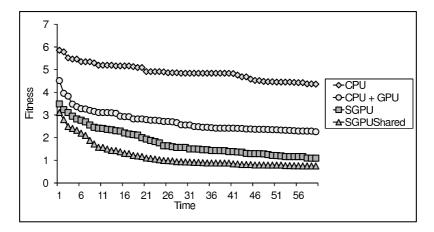

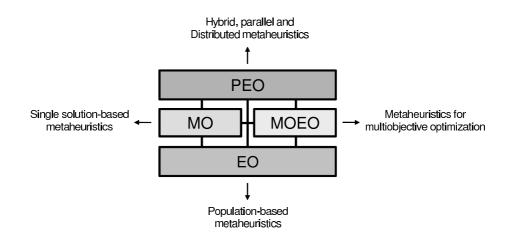

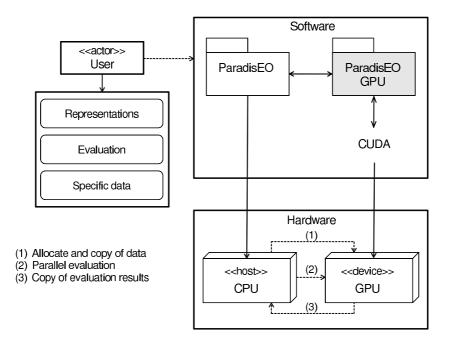

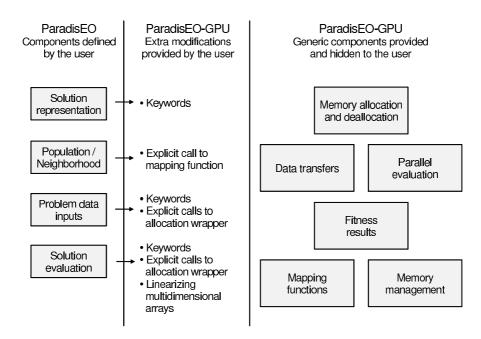

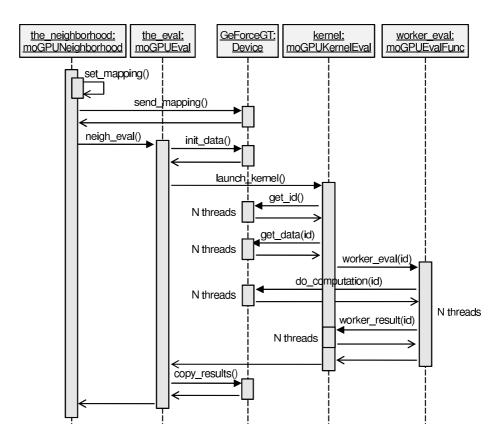

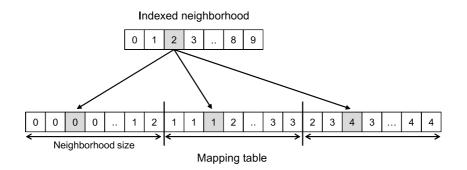

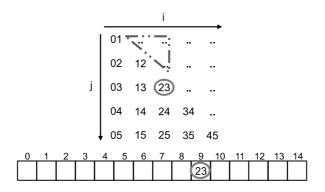

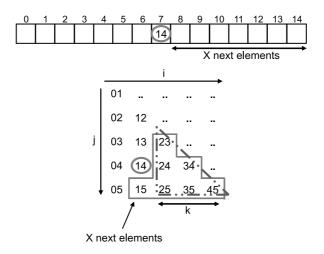

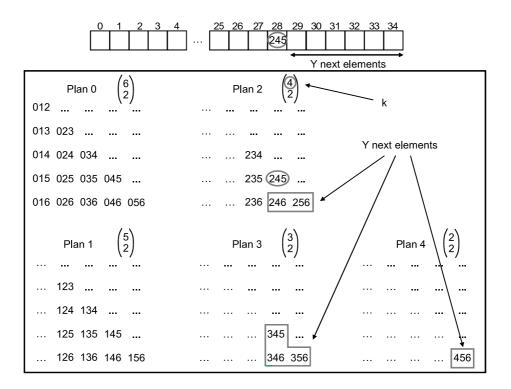

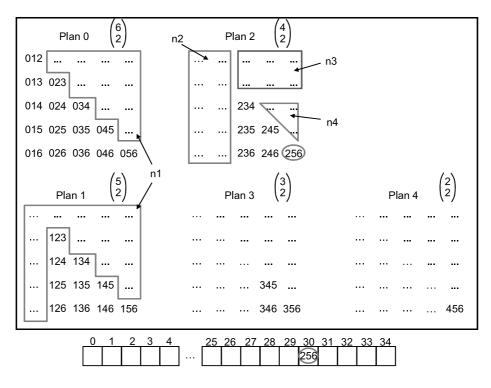

meet the memory constraints. When dealing with a large set of solutions or large problem instances, the previous implementations might not be robust. We will show in Chapter 3 how an efficient thread control allows to introduce fault-tolerance mechanisms in GPU applications.