Département de formation doctorale en informatique UFR IEEA

École doctorale SPI Lille

# Exécution d'applications stockées dans la mémoire non-adressable d'une carte à puce

## **THÈSE**

présentée et soutenue publiquement le 13 décembre 2012

pour l'obtention du

## Doctorat de l'Université des Sciences et Technologies de Lille (spécialité informatique)

par

Geoffroy Cogniaux

#### Composition du jury

Président: Pierre BOULET – LIFL, Université Lille 1 Sciences et Technologies

Rapporteurs: Didier Donsez – LIG, Université Joseph Fourier Grenoble 1

Gaël THOMAS – LIP6, UPMC Sorbonne Universités Paris

Examinateur: Guillaume Salagnac – CITI, INSA de Lyon

Directeur de thèse : Gilles Grimaud – LIFL, Université Lille 1 Sciences et Technologies

Co-Encadrant de thèse: Michael Hauspie – LIFL, Université Lille 1 Sciences et Technologies

Invité: François-Xavier Marseille – Gemalto, Technology & Innovation France

Laboratoire d'Informatique Fondamentale de Lille Université Lille 1 - Sciences et Technologies Gemalto Technology and Innovation, France

Numéro d'ordre: XXXXX

« Nous ne savons jamais où nos actions nous mèneront.

Mais nous savons que si nous ne faisons rien,

elles ne nous mèneront nulle-part. »

Gandhi

## Table de matières

| Ir                     | itroduct           | ion                                                             |  |  |  |  |  |

|------------------------|--------------------|-----------------------------------------------------------------|--|--|--|--|--|

| É                      | tat de l'          | art                                                             |  |  |  |  |  |

| 2.                     | 1 Emba             | arquer du logiciel dans une carte à puce                        |  |  |  |  |  |

|                        | 2.1.1              | Architecture processeur d'une carte à puce                      |  |  |  |  |  |

|                        | 2.1.2              | Architecture mémoire d'une carte à puce                         |  |  |  |  |  |

|                        |                    | 2.1.2.1 Une mémoire non-volatile adressable : la Flash NOR      |  |  |  |  |  |

|                        |                    | 2.1.2.2 Une mémoire non-volatile non-adressable : la Flash NAND |  |  |  |  |  |

|                        |                    | 2.1.2.3 Limites de la flash NAND                                |  |  |  |  |  |

|                        | 2.1.3              | Modèle applicatif maître-esclave                                |  |  |  |  |  |

|                        |                    | 2.1.3.1 Protocole de communication                              |  |  |  |  |  |

|                        |                    | 2.1.3.2 Applications événementielles                            |  |  |  |  |  |

|                        | 2.1.4              | Ajouter du logiciel à une carte à puce                          |  |  |  |  |  |

|                        |                    | 2.1.4.1 Mutations successives                                   |  |  |  |  |  |

|                        |                    | 2.1.4.2 Nouvelles plateformes applicatives                      |  |  |  |  |  |

|                        | 2.1.5              | Les défis de la <i>post-issuance</i>                            |  |  |  |  |  |

|                        |                    | 2.1.5.1 Le défi de la sécurité                                  |  |  |  |  |  |

|                        |                    | 2.1.5.2 Machines défensives et analyseurs de code               |  |  |  |  |  |

|                        |                    | 2.1.5.3 Le défi du stockage                                     |  |  |  |  |  |

|                        | 2.1.6              | Embarquer plus de logiciels dans une carte à puce               |  |  |  |  |  |

| 2.2 De Java à JavaCard |                    |                                                                 |  |  |  |  |  |

|                        | 2.2.1              | Le langage Java et sa machine virtuelle                         |  |  |  |  |  |

|                        |                    | 2.2.1.1 Processus virtuels d'exécution                          |  |  |  |  |  |

|                        |                    | 2.2.1.2 Processus de gestion de la mémoire                      |  |  |  |  |  |

|                        |                    | 2.2.1.3 Classes, objets et méta-données                         |  |  |  |  |  |

|                        | 2.2.2              | La plate-forme JavaCard 2.2: Java dans une tête d'épingle       |  |  |  |  |  |

|                        |                    | 2.2.2.1 Une Machine Virtuelle scindée                           |  |  |  |  |  |

|                        |                    | 2.2.2.2 Conversion                                              |  |  |  |  |  |

|                        |                    | 2.2.2.3 Briques logicielles                                     |  |  |  |  |  |

|                        |                    | 2.2.2.4 JavaCard2: Un sous-ensemble du langage Java             |  |  |  |  |  |

|                        | 2.2.3              | Synthèse                                                        |  |  |  |  |  |

| 2.                     | 3 Cache            | e mémoire                                                       |  |  |  |  |  |

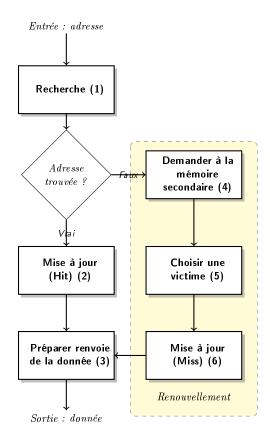

|                        | 2.3.1              | Fonctionnement général                                          |  |  |  |  |  |

|                        | 2.3.2              | Stratégies de placement                                         |  |  |  |  |  |

|                        |                    | 2.3.2.1 Placement par allocation                                |  |  |  |  |  |

|                        |                    | 2.3.2.2 Placement par segmentation                              |  |  |  |  |  |

|                        | 2.3.3              | Stratégies de renouvellement                                    |  |  |  |  |  |

| 2.                     | 4 Synth            | ièse                                                            |  |  |  |  |  |

| ъ                      |                    |                                                                 |  |  |  |  |  |

|                        | robléma<br>1 - Ct- |                                                                 |  |  |  |  |  |

| 3.                     |                    | exte et opportunités                                            |  |  |  |  |  |

|                        | 3.1.1              | Post-issuance massive                                           |  |  |  |  |  |

| 6                      | 3.1.2              | Bénéfices potentiels                                            |  |  |  |  |  |

| 3.                     |                    | ématique : le mur des temps de latence                          |  |  |  |  |  |

|                        | 3 7 1              | IN A DEL Vorgue DELR. La comparat da la realita                 |  |  |  |  |  |

iv Table de matières

|   |     | 3.2.2   | Insuffisa         | nce de l'approche par tampon $\dots \dots \dots$ | 3 |

|---|-----|---------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   | 3.3 | Appro   | $ches \dots$      | 29                                                                                                                                               | ) |

|   |     | 3.3.1   | Première          | e approche : un cache mémoire                                                                                                                    | ) |

|   |     |         | 3.3.1.1           | Un cache d'instructions en logiciel                                                                                                              | ) |

|   |     |         | 3.3.1.2           | Les clés de l'efficacité d'un cache                                                                                                              | ) |

|   |     |         | 3.3.1.3           | Limitations d'un cache                                                                                                                           | L |

|   |     | 3.3.2   | Deuxièm           | ne approche : le recouvrement d'opérations                                                                                                       | 2 |

|   |     |         | 3.3.2.1           | Présentation                                                                                                                                     | 2 |

|   |     |         | 3.3.2.2           | Recouvrement par ré-ordonnancement                                                                                                               | ) |

|   |     |         | 3.3.2.3           | Pré-chargement sans matériel                                                                                                                     | 2 |

|   |     | 3.3.3   | Notre ap          | proche: regroupement d'accès au cache                                                                                                            | í |

|   |     |         | 3.3.3.1           | Contraintes structurelles d'un cache                                                                                                             | 5 |

|   |     |         | 3.3.3.2           | Vers une découverte dynamique de groupes d'accès 36                                                                                              | j |

|   |     |         | 3.3.3.3           | Méthode de découverte dynamique des groupes                                                                                                      | 7 |

|   | 3.4 | Métho   | dologie .         | 38                                                                                                                                               | 3 |

|   |     | 3.4.1   |                   | d'évaluation                                                                                                                                     |   |

|   |     | 3.4.2   |                   | mes de tests                                                                                                                                     |   |

|   |     | 3.4.3   | _                 | es expérimentaux                                                                                                                                 |   |

|   |     | 0.1.0   | 1 1000001         | os enpermioneaux                                                                                                                                 | • |

| 4 | Cac | hes log | ciciels po        | our cartes à puce 43                                                                                                                             | 3 |

|   | 4.1 | _       | _                 | faible empreinte mémoire                                                                                                                         | 3 |

|   |     | 4.1.1   |                   | és généralisables des blocs de données                                                                                                           | 5 |

|   |     |         | 4.1.1.1           | Taille                                                                                                                                           | 5 |

|   |     |         | 4.1.1.2           | Degré de séquentialité                                                                                                                           |   |

|   |     |         | 4.1.1.3           | Points chauds                                                                                                                                    |   |

|   |     | 4.1.2   |                   | es de placement et empreinte mémoire                                                                                                             |   |

|   |     | 1.1.2   | 4.1.2.1           | Impact sur l'allocation par taille variable                                                                                                      |   |

|   |     |         | 4.1.2.2           | Impact sur l'allocation par taille fixe                                                                                                          |   |

|   |     |         | 4.1.2.3           | Impact sur la segmentation                                                                                                                       |   |

|   |     | 4.1.3   |                   | héorique du renouvellement                                                                                                                       |   |

|   |     | 4.1.4   |                   | es d'accès au contenu d'un cache                                                                                                                 |   |

|   |     | 7.1.7   | 4.1.4.1           | Algorithmes de recherche                                                                                                                         |   |

|   |     |         | 4.1.4.2           | Empreinte mémoire des algorithmes de recherche                                                                                                   |   |

|   |     |         | 4.1.4.3           | Débit pour des empreintes mémoires comparables 54                                                                                                |   |

|   |     | 4.1.5   |                   | xécution d'un cache logiciel                                                                                                                     |   |

|   |     | 4.1.0   |                   | Coût des stratégies de placement                                                                                                                 |   |

|   |     |         | 4.1.5.1 $4.1.5.2$ | <u> </u>                                                                                                                                         |   |

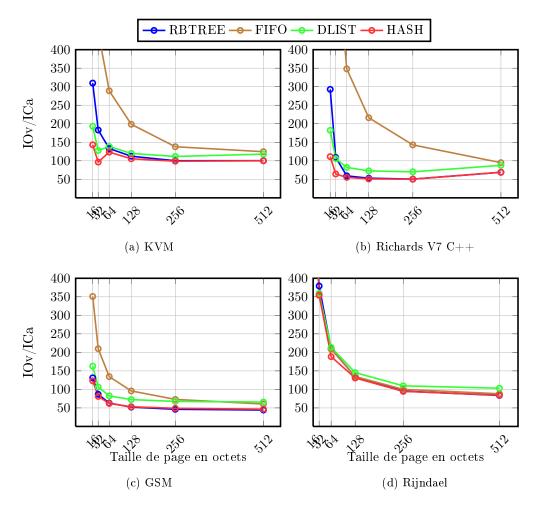

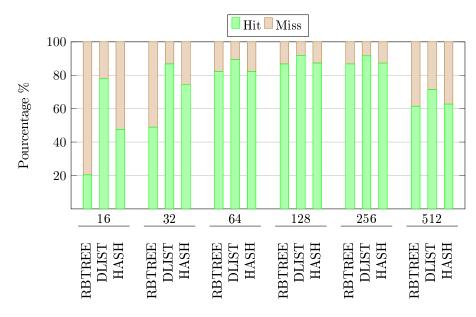

|   |     |         |                   | Coût en instructions                                                                                                                             |   |

|   | 4.0 | O 1     | 4.1.5.3           | Analyse des coûts en instructions                                                                                                                |   |

|   | 4.2 |         |                   | tions logiciel pour cartes à puce                                                                                                                |   |

|   |     | 4.2.1   |                   | nt de blocs de base                                                                                                                              |   |

|   |     |         | 4.2.1.1           | Principe de localité                                                                                                                             |   |

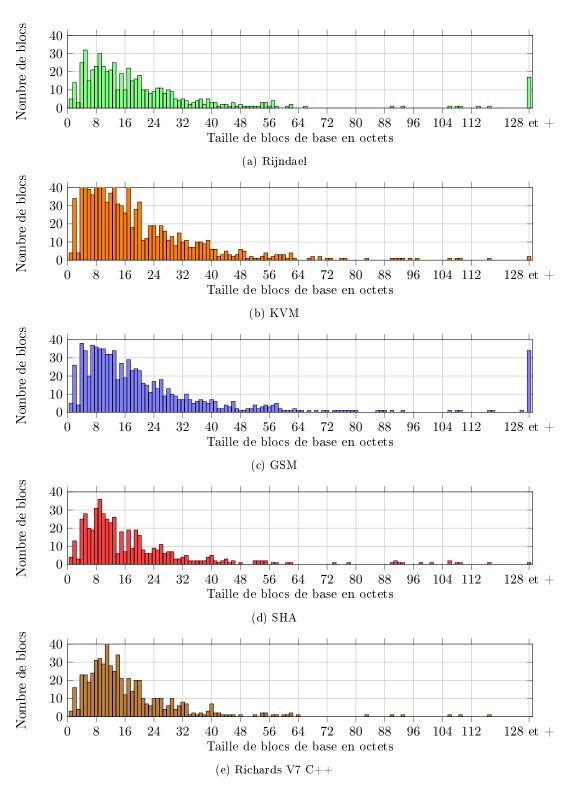

|   |     |         | 4.2.1.2           | Tailles des blocs de base                                                                                                                        |   |

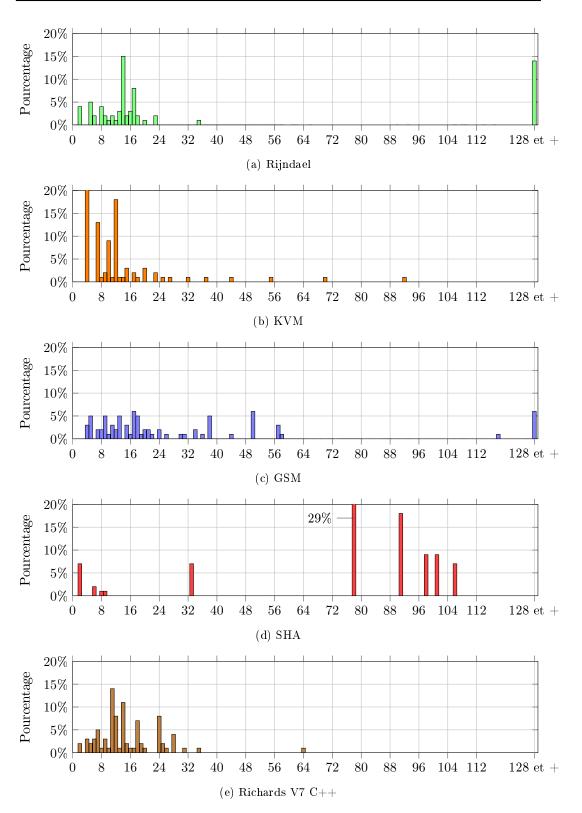

|   |     |         | 4.2.1.3           | Fréquences de réapparition de tailles de bloc 59                                                                                                 |   |

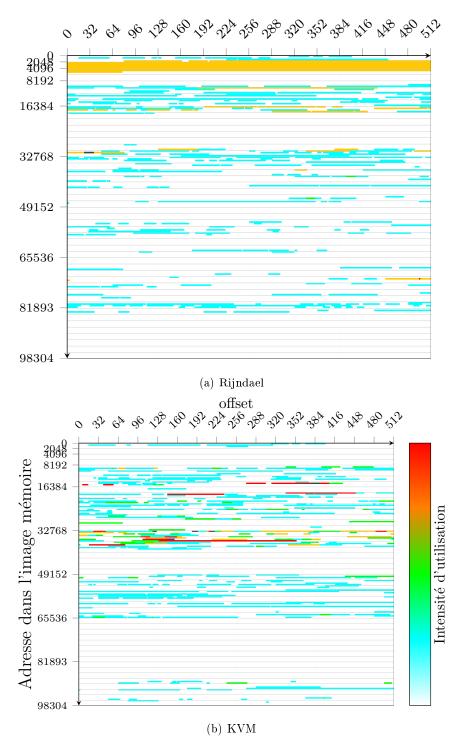

|   |     |         | 4.2.1.4           | Dispersion des points chauds 61                                                                                                                  |   |

|   |     |         | 4.2.1.5           | Synthèse                                                                                                                                         |   |

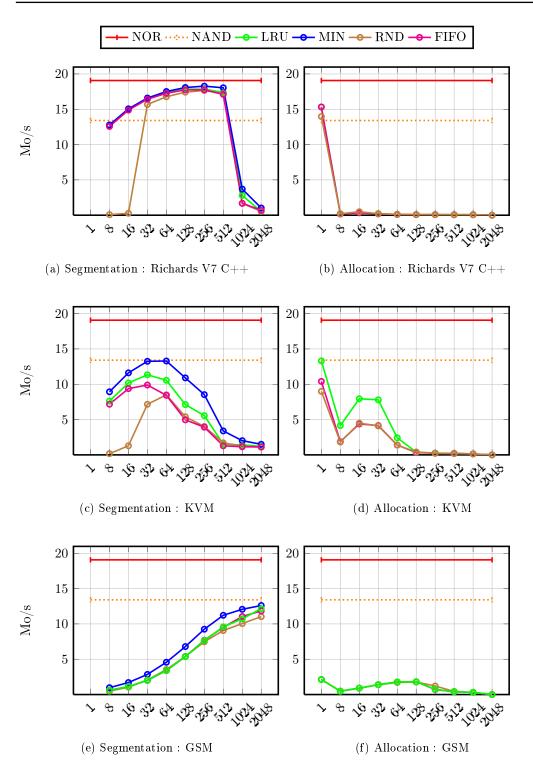

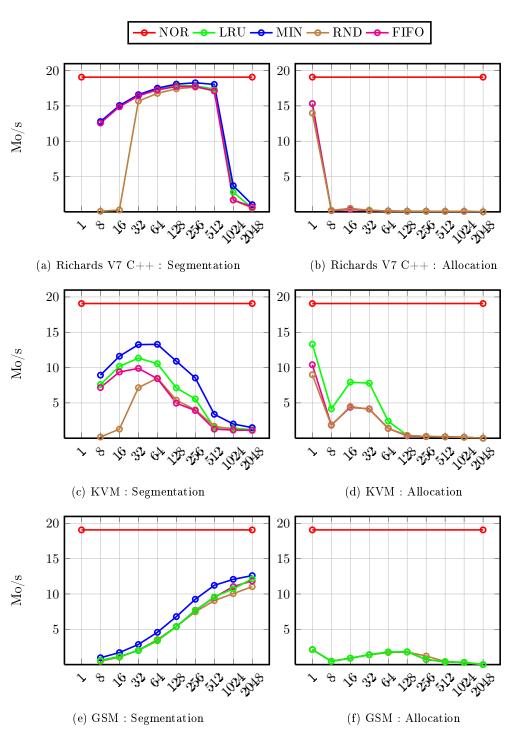

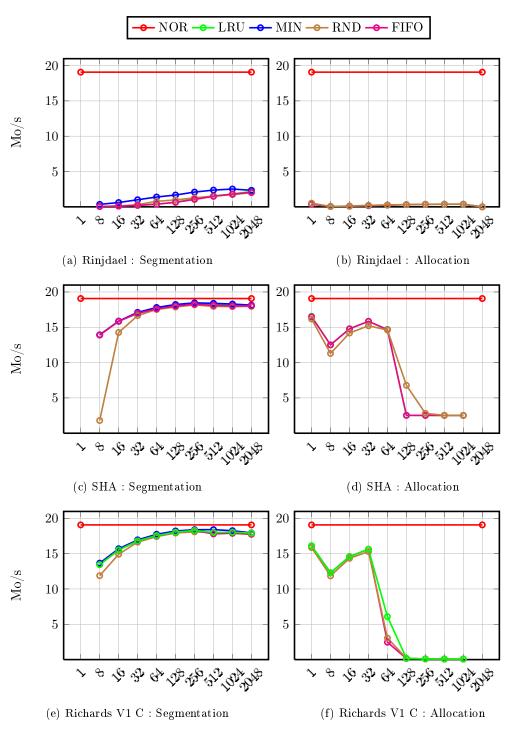

|   |     | 4.2.2   |                   | on croisée du placement et du renouvellement 65                                                                                                  |   |

|   |     | 4.2.3   |                   | xécution d'un cache d'instructions logiciel 67                                                                                                   |   |

|   |     |         | 4.2.3.1           | Unification des paramètres                                                                                                                       |   |

|   |     |         | 4.2.3.2           | Résultats expérimentaux                                                                                                                          |   |

|   |     |         | 4.2.3.3           | Évaluation et analyse du coût global                                                                                                             | 3 |

Table de matières

|   | 4.3        | Synthèse et  | conclusions                                        | 70                   |

|---|------------|--------------|----------------------------------------------------|----------------------|

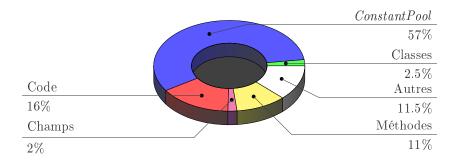

| 5 | Cac        | he logiciel  | de méta-données Java et JavaCard                   | 73                   |

|   | 5.1        | Introduction | n au modèle de méta-donnée Java                    | 73                   |

|   |            | 5.1.1 Désa   | ambigüisation                                      | 73                   |

|   |            | 5.1.2 Obje   | ectif et méthode                                   | 74                   |

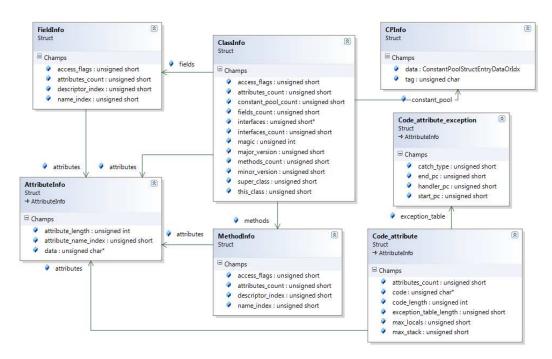

|   |            | 5.1.3 Fich   | ier de classe : méta-données brutes                | 75                   |

|   | 5.2        | Chargemen    | t des méta-données Java                            | 77                   |

|   |            | 5.2.1 Cha    | rgement de classes                                 | 78                   |

|   |            | 5.2.1        |                                                    | 78                   |

|   |            | 5.2.1        | <u>-</u>                                           | 78                   |

|   |            | 5.2.1        |                                                    | 79                   |

|   |            | 5.2.2 Pré-   |                                                    | 79                   |

|   |            | 5.2.2        | 8                                                  | 79                   |

|   |            | 5.2.2        | 0 1                                                | 80                   |

|   |            | =            | 1 0                                                | 30<br>80             |

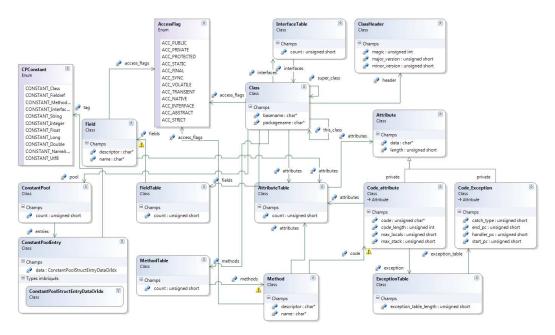

|   | 5.3        |              |                                                    | 30<br>80             |

|   | 0.0        |              |                                                    | 30<br>81             |

|   |            |              |                                                    | 31<br>82             |

|   |            |              |                                                    | 34<br>84             |

|   | 5.4        |              |                                                    | 3 <del>4</del><br>85 |

|   | 9.4        |              |                                                    | 35<br>85             |

|   |            |              |                                                    | วย<br>85             |

|   | <b>.</b> . |              |                                                    |                      |

|   | 5.5        |              |                                                    | 88                   |

|   |            | _            | *                                                  | 88                   |

|   |            | 5.5.1        |                                                    | 88                   |

|   |            | 5.5.1        |                                                    | 88                   |

|   |            | <del>-</del> |                                                    | 89                   |

|   |            | 5.5.2        | <u>.</u>                                           | 89                   |

|   |            | 5.5.2        | <u>.</u>                                           | 90                   |

|   |            | 5.5.2        | 1                                                  | 90                   |

|   |            |              |                                                    | 91                   |

|   | 5.6        |              | 0                                                  | 93                   |

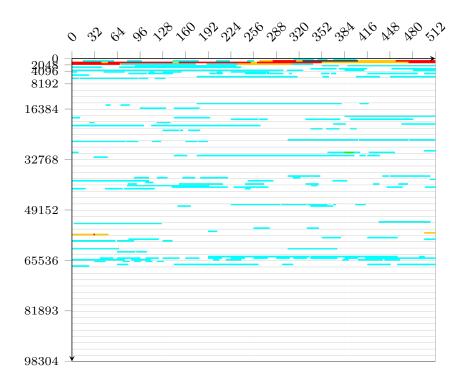

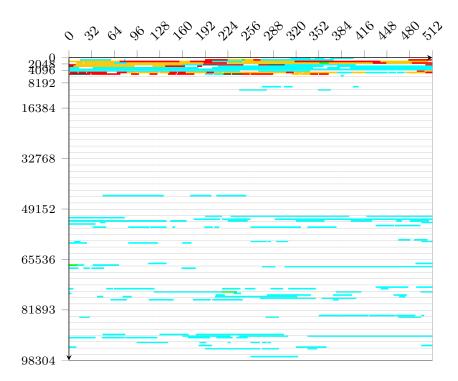

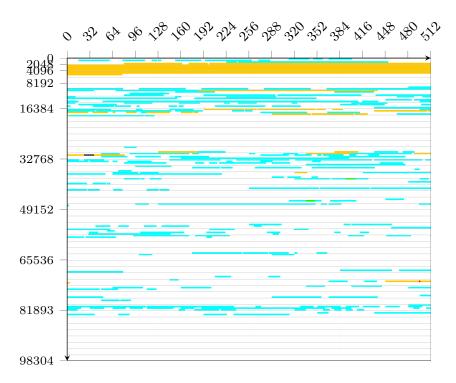

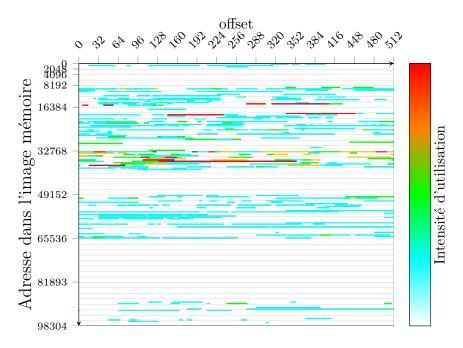

|   |            | 5.6.1 Cart   | 0 1                                                | 93                   |

|   |            | 5.6.1        | 0 1                                                | 93                   |

|   |            | 5.6.1        | 1.2 Cartographie de JavaCard                       | 95                   |

|   |            | 5.6.1        | 1.3 Dilution spatiale                              | 96                   |

|   |            | 5.6.2 Cacl   | he de méta-données                                 | 96                   |

|   | 5.7        | Synthèse .   |                                                    | 98                   |

| 6 | Pré-       | interpréta   | tion de code JavaCard                              | 99                   |

|   | 6.1        | Vers une pr  | é-interprétation de code                           | 99                   |

|   |            | 6.1.1 Inter  | ractions entre l'interpréteur et le cache logiciel | 99                   |

|   |            |              |                                                    | 02                   |

|   |            |              | · · ·                                              | 02                   |

|   |            | 6.1.3        | · -                                                | $0^{-}$              |

|   |            | 6.1.3        |                                                    | 03                   |

|   |            |              |                                                    | 03                   |

|   |            | 6.1.4        |                                                    | 03                   |

|   |            | 6.1.4        | •                                                  | 04                   |

|   |            | U.I.         | = = = = = = = = = = = = = = = = = =                | <i>)</i> =           |

vi Table de matières

|              |                           |        | 6.1.4.3 Préparation précoce de l'interprétation concrète 10           | 4 |  |  |

|--------------|---------------------------|--------|-----------------------------------------------------------------------|---|--|--|

|              | 6.2                       | Conce  | ption d'un pré-interpréteur                                           | 5 |  |  |

|              |                           | 6.2.1  | Architecture générale                                                 | 5 |  |  |

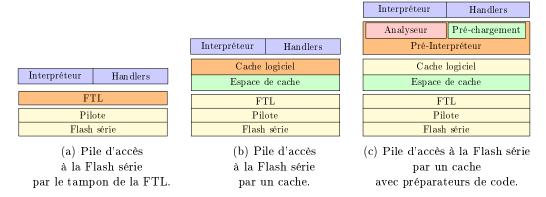

|              |                           |        | 6.2.1.1 Surcharge de la pile d'accès à la mémoire non-adressable . 10 | 5 |  |  |

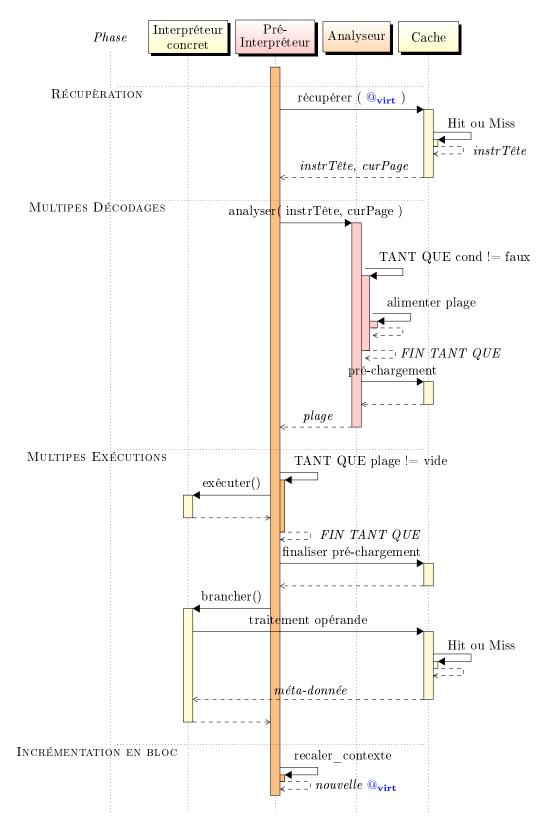

|              |                           |        | 6.2.1.2 Principe de fonctionnement                                    | 6 |  |  |

|              |                           | 6.2.2  | Objectif: maîtriser le coût d'exécution                               | 9 |  |  |

|              | 6.3                       | Pré-in | terprétation de code JavaCard                                         | 9 |  |  |

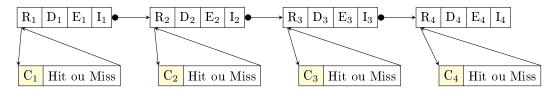

|              |                           | 6.3.1  | Code JavaCard 2.2                                                     | 9 |  |  |

|              |                           | 6.3.2  | Pré-décodages : mode opératoire                                       | 0 |  |  |

|              |                           |        | 6.3.2.1 Support d'analyse                                             |   |  |  |

|              |                           |        | 6.3.2.2 Éviter la redondance des décodages                            | 1 |  |  |

|              |                           | 6.3.3  | Analyse et rupture de flots                                           | 3 |  |  |

|              |                           |        | 6.3.3.1 Preuve d'une analyse bornée                                   | 3 |  |  |

|              |                           |        | 6.3.3.2 Pré-décodage de méta-données                                  | 4 |  |  |

|              |                           | 6.3.4  | Pilotage actif du cache                                               | 6 |  |  |

|              |                           |        | 6.3.4.1 Forcer la politique de remplacement                           | 6 |  |  |

|              |                           |        | 6.3.4.2 Pré-chargements                                               | 6 |  |  |

|              |                           | 6.3.5  | Synthèse                                                              |   |  |  |

|              | 6.4                       | Confro | ontation du gain et du coût                                           | 7 |  |  |

|              |                           | 6.4.1  | Maîtrise du coût d'exécution                                          |   |  |  |

|              |                           | 6.4.2  | Évaluation expérimentale de la pré-interprétation                     |   |  |  |

|              |                           |        | 6.4.2.1 Protocole expérimental                                        |   |  |  |

|              |                           |        | 6.4.2.2 Évaluation de la pré-interprétation                           |   |  |  |

|              |                           |        | 6.4.2.3 Évaluation du pré-chargement                                  |   |  |  |

|              |                           | 6.4.3  | Preuve de concept                                                     |   |  |  |

|              | 6.5                       |        | isions                                                                |   |  |  |

|              |                           |        |                                                                       |   |  |  |

| 7            | Con                       | clusio | $_{ m 12}$                                                            | 5 |  |  |

|              | 7.1                       | Synthe | ${ m \hat{e}se}$                                                      | 5 |  |  |

|              | 7.2                       | Perspe | ectives : transposer la pré-interprétation                            | 6 |  |  |

| ъ.           | 1. 1*                     | 1. •   | 10                                                                    | ^ |  |  |

| Bı           | bliog                     | raphie | $^{-12}$                                                              | 9 |  |  |

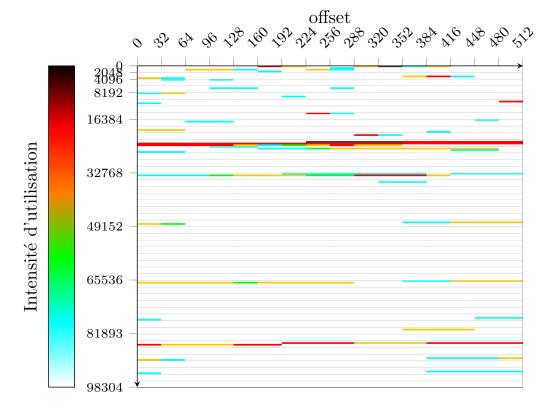

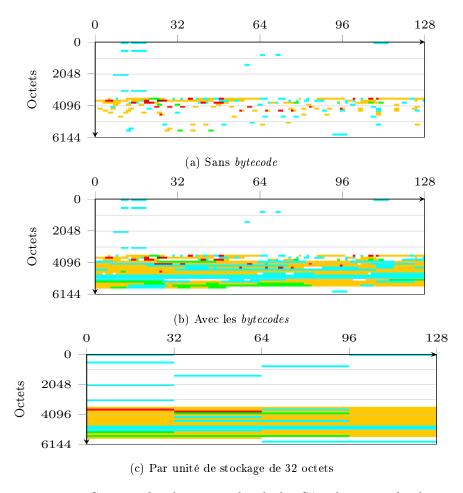

| A            | Con                       | npléme | ents cartographiques 13                                               | 7 |  |  |

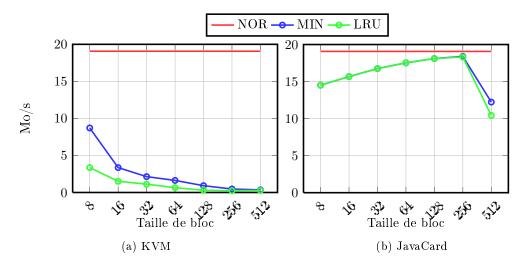

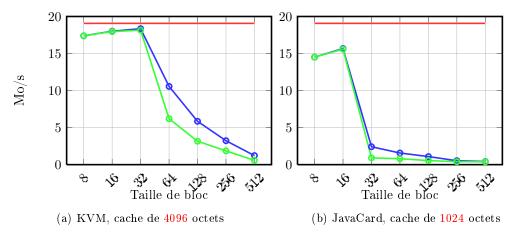

| В            | Con                       | npléme | ents graphiques sur les débits 14                                     | 1 |  |  |

| $\mathbf{C}$ | Structures de données 145 |        |                                                                       |   |  |  |

### Introduction

#### Contexte

Les cartes à puce sont des systèmes informatiques miniatures principalement dédiés à la sécurité. Elles sont ainsi connues pour être des systèmes fermés embarquant du logiciel opaque. Néanmoins, ces dernières années ont vu ces systèmes s'ouvrir sur l'extérieur en proposant désormais la possibilité d'y installer des applications après leur mise en circulation. Cette mutation n'est toutefois pas intervenue sans introduire de nouvelles problématiques de sécurité et de génie logiciel, alors que le matériel n'a quant à lui que très peu évolué. Dans ces circonstances, la capacité de stockage mémoire d'une carte à puce reste un frein à la quantité d'applications embarquables.

Dans ces conditions, il apparait alors opportun de stocker ces nouvelles applications dans la mémoire Flash série que les carte à puce possèdent de plus en plus souvent. Cependant cette mémoire bien que large est non-adressable par la processeur et n'est donc pas propice à l'exécution de code en place comme la Flash interne. De plus, ces mémoires ont un temps de latence très élevé.

Plusieurs approches sont alors envisageables mais la plus efficace est sans conteste l'utilisation d'un cache d'instructions. Mais malheureusement, une carte à puce n'a pas de support matériel pour ce type d'actions.

#### Thèse

Dans ce mémoire, nous défendons la thèse qu'il est possible d'exécuter des applications, natives ou Java, stockées dans la mémoire non-adressable d'une carte à puce, sans support matériel couvrant la latence de celle-ci. Nous présentons donc dans ce document une étude sur les caches logiciels, en revisitant l'état de l'art sur ceux-ci par le prisme d'une empreinte mémoire faible, condition sine qua none d'une solution encartable.

La faiblesse connue et admise de cette thèse réside justement dans l'empreinte mémoire qui est le facteur de performances communément acquis d'un cache, qu'il soit matériel ou logiciel, comme le montrent les tailles des caches processeurs, des disques durs,s des bases de données ou des serveurs web. D'autre part, le simple fait de parler de cache logiciel sousentend un coût d'exécution de celui-ci bien supérieur à celui d'un cache matériel, rendant la récupération d'une instruction prohibitive par rapport à son exécution pure.

Dans ce mémoire, nous appliquons notre étude des caches logiciels dans un premier temps à la problématique des caches d'instructions, puis aux caches de méta-données Java/JavaCard, une autre famille de données exécutables. Enfin, nous montrerons comment les faiblesses des caches logiciels peuvent être dépassées par une préparation précoce de données exécutables contenues dans l'espace de cache.

#### Structure de ce mémoire

Le chapitre 2 présente un état de l'art des plateformes applicatives pour cartes à puces, puis présente les spécificités et fonctionnalité de la plateforme la plus répandue qu'est JavaCard2. Enfin, dans une troisième partie est présenté un état de l'art sur les cache mémoires, fil conducteur de tout ce document.

Le **chapitre 3** présente le contexte des travaux présentés dans ce mémoire, puis en extrait la problématique. Il présente ensuite les principales approches qui peuvent être suivies pour la résoudre. Enfin, nous présentons notre méthodologie, basée sur une approche phénoménologique du problème.

Le **chapitre 4** présente notre étude sur les caches logiciels contraints par une faible empreinte mémoire. Puis dans un second temps, nous évaluons nos constats et conclusions sur le cas d'un cache d'instructions logiciel, pour en montrer les forces mais aussi malheureusement les faiblesses, préjudiciables pour une carte à puce.

Le **chapitre 5** se focalise sur l'étude des méta-données Java/JavaCard qui sont à leur niveau également des données exécutables sans être du code ni des données pures. Nous montrons comment la construction d'un modèle de méta-données influencent directement les performances de la JVM, puis dans un second temps, celles d'un cache de méta-données logiciel.

Le **chapitre 6** présente l'approche que nous proposons pour améliorer suffisamment les performances d'un cache logiciel à faible empreinte pour qu'il puisse être embarqué dans une carte à puce.

Enfin, le **chapitre 7** apporte une synthèse de ces travaux et en donne quelques perspectives.

## État de l'art

Les cartes à puce autrefois fermées s'ouvrent aujourd'hui au monde extérieur en permettant de télécharger de nouvelles application alors que la carte a déjà été mise en circulation. Cette nouvelle approche ouvre sur plusieurs problémes comme la sécurité et l'espace disponible pour stocker ces applications, alors que dans le même temps, le support matériel n'a quant à lui que peu évolué.

Dans ce chapitre, nous présentons un état de l'art de ces nouvelles problématiques, en trois temps. Nous commençons par aborder l'aspect embarquement sécurisé d'applications tiers dans une carte à puce. Puis nous décrivons la plateforme technologique Java Card, qui est le support de génie logiciel le plus répandu à ce jour pour ces nouvelles cartes à puce. Enfin, nous abordons l'aspect espace de stockage de code et d'applications en revenant sur la technologie des caches mémoires, solution la plus commune pour étendre un espace mémoire principal en s'aidant d'une mémoire secondaire, bien que beaucoup plus lente.

#### 2.1 Embarquer du logiciel dans une carte à puce

Les cartes à puce sont des petits objets informatiques dont la vocation est d'avoir à portée de la main en toutes circonstances des données personnelles sensibles et/ou secrètes. Le couple matériel/logiciel formant une carte à puce est ainsi conçu d'une part pour la sécurisation de ces données et d'autre part pour l'extrême portabilité d'un objet discret et nomade. Mais glisser une clé cryptographique et des données bancaires ou médicales dans une poche de veston ou un porte-feuille implique à l'origine des choix de conception radicaux.

Dans le matériel d'abord, qui doit allier coût de production unitaire extrêmement faible avec robustesse, fiabilité, et sécurité. L'information secrète ne doit ni être altérée dans le temps, ni fuir du matériel par un dysfonctionnement de celui-ci, ni être transmise sous une forme erronée.

Pendant longtemps, le logiciel a quant à lui été conçu par co-conception avec le matériel. Car cette approche permet une convergence de la performance, de la sécurité et du coût de production dans un système dédié à une tâche bien précise. Toutefois aujourd'hui, la politique applicative des cartes à puce est à l'ouverture sur le monde extérieur avec la possibilité pour le porteur de carte de pouvoir ajouter lui-même de nouvelles applications dans certaines de ses cartes à puce. Ce nouveau mode d'utilisation de la carte à puce, s'il n'a pas réellement entraîné de modifications dans la conception du matériel, a largement modifié l'architecture logicielle pour offrir un support à la personnalisation.

Bien évidemment, cette capacité à pouvoir modifier à volonté le contenu applicatif, implique de nouvelles problématiques de sécurité à résoudre. Cet aspect est aujourd'hui un des domaines de recherche les plus animés dans la catégorie de ces cartes à puce dites « ouvertes ». Néanmoins, la personnalisation connait une autre limite que nous adressons dans cette thèse. Cette limite est le volume applicatif que les cartes ouvertes sont capables d'accepter. En effet, le matériel n'ayant pas beaucoup évolué, la quantité d'espace

mémoire disponible pour le stockage et l'exécution de nouvelles applications n'a ainsi que peu augmenté.

Dans cette section, nous présentons un état des lieux de l'architecture matérielle puis logicielle des cartes à puces « ouvertes » actuelles. Nous regarderons plus particulièrement quels sont les freins à la personnalisation massive et les opportunités qui restent offertes avec le matériel existant.

#### 2.1.1 Architecture processeur d'une carte à puce

L'unité centrale d'une carte à puce est de la taille d'un micro-contrôleur. C'est cette unité centrale qui rend la carte à puce programmable et « intelligente » <sup>1</sup>. Ce micro-contrôleur intègre également un peu de mémoire volatile pour l'exécution et plusieurs types de mémoires non-volatiles détaillées un peu plus bas. Tous ses composants communiquent entre eux au travers d'un bus. Les cartes recourant au chiffrement possèdent généralement un co-processeur cryptographique gérant au niveau matériel des algorithmes de chiffrement symétrique comme DES ou AES, ou asymétrique comme RSA [Eisenbarth 2007].

Si tout ceci est à l'image de n'importe quel système informatique, la différence fondamentale se trouve dans les tailles et puissances de chaque composant. Historiquement, les processeurs des cartes à puce sont des processeurs 8 bits connus pour produire des applications très compactes et être peu gourmands en énergie. Mais les besoins évoluant, on trouve maintenant des processeurs 32 bits suffisamment légers pour convenir aux cahiers des charges d'une carte à puce. La plupart d'entre elles sont cadencées à des fréquences allant de 4 à 20 MHz (voir tableau 2.1). Côté mémoire, une carte à puce est tout aussi limitée, car essentiellement conditionnée par la taille restreinte du silicium qui ne peut dépasser quelques millimètres-carrés. La quantité de RAM d'une carte à puce peut commencer à seulement 512 octets et ne dépassent que rarement les 48 Ko. Les cartes à puce modernes contiennent par contre maintenant jusqu'à 256 Ko de Flash interne adressable (i.e. incluse dans l'espace d'adressage du CPU). À l'heure actuelle, cet espace mémoire est le seul contenant des binaires exécutables, du système d'exploitation aux applications.

| TELL 01 TELL            | 11 1 1 1        | 11          | 1 .      | . ^1         |      |          |        |

|-------------------------|-----------------|-------------|----------|--------------|------|----------|--------|

| Tableau 2.1: Exemples   | d'architectures | materialles | do miere | -controlaure | nour | cartee a | nuco   |

| Tableau Z.I. Excilibles | a arcmiccuarca  | mattititi   | uc micro | -commoncurs  | DOUL | cartes a | b Ducc |

|                         |                 |             |          |              |      |          |        |

| Modèle   | Architecture | Taille Bus | Registres      | Fréquence           |

|----------|--------------|------------|----------------|---------------------|

| 68H05    | CISC         | 8 bits     | 2 * 8 bits     | 4,77 Mhz            |

| 80xx51   | CISC         | 8 bits     | 6 * 8/16 bits  | 4,77 Mhz            |

| AVR AT90 | RISC/CISC    | 8 bits     | 32 * 8/16 bits | 4,77 Mhz - 44,7 Mhz |

| ARM7xx   | RISC         | 32 bits    | 16 * 32 bits   | 4,77 Mhz - 30 Mhz   |

| R4KSC    | RISC         | 32 bits    | 32 * 32 bits   | 4,77 Mhz - 100 Mhz  |

#### 2.1.2 Architecture mémoire d'une carte à puce

Une carte à puce embarque plusieurs types de composant mémoire. Le premier bien évidement est de la mémoire vive,  $RAM^2$  ou  $SRAM^3$ . Elle contient principalement la pile d'exécution. On trouve également un peu de mémoire morte ( $ROM^4$ ) pour le stockage de

<sup>&</sup>lt;sup>1</sup>Le terme désignant une carte en anglais est d'ailleurs encore plus explicite, puisqu'elle se traduit par SmartCard, la carte intelligente.

<sup>&</sup>lt;sup>2</sup>Random Access Memory

<sup>&</sup>lt;sup>3</sup>Static Random Access Memory

<sup>&</sup>lt;sup>4</sup>Read-Only Memory

code critique et le code de démarrage<sup>5</sup>, ainsi que de la mémoire Flash pour le stockage du code exécutable, de données applicatives, et parfois d'un système de fichiers.

Les mémoires Flash sont des mémoires à stockage persistant et effaçables électriquement inventées par Toshiba vers le milieu des années 80. Leur principale caractéristique par rapport à l'EEPROM<sup>6</sup>, et leur mode d'effacement qui se fait par blocs et non plus par octets, ce qui rend les écritures plus rapides que dans cette dernière.

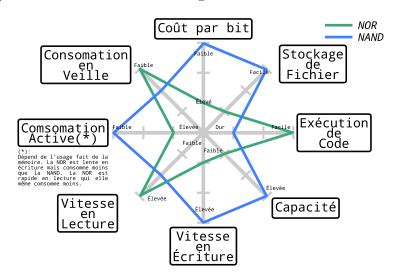

Il existe aujourd'hui deux types de mémoire Flash: la NOR et la NAND (figure 2.1). Elles tirent chacune leur nom de la manière dont sont utilisées les portes logiques de leurs transistors. Bien qu'ayant une origine commune, elles ont toutefois plusieurs différences majeures qui les renvoient chacune à des usages bien différents.

Figure 2.1: Comparaison entre NOR et NAND - source [Toshiba 2003], traduite en français.

#### 2.1.2.1 Une mémoire non-volatile adressable : la Flash NOR

La NOR est inscriptible par blocs mais permet un accès en lecture à la taille d'un mot machine, permettant une performance remarquable pour des accès aléatoires. Cette caractéristique fait d'elle depuis son invention une mémoire idéale pour le stockage de code dans un micro-contrôleur en remplacement des anciennes ROM, moins souples, et autres EEPROM plus lentes. Si, comme dans un micro-contrôleur, la RAM et la NOR sont sur le même bus, lire un octet en NOR se fait à la même vitesse que dans la RAM. Le réel handicap de la flash NOR est son temps d'écriture qui reste tout de même très lent. Écrire un bloc peut prendre jusqu'à 900 milli-secondes dans les modèles bas de gamme.

#### 2.1.2.2 Une mémoire non-volatile non-adressable : la Flash NAND

La Flash NAND est accessible par blocs, que se soit en lecture ou en écriture. La NAND est en fait une NOR dont on a réduit le nombre de portes par cellule de stockage [Micron 2006], ce qui l'a rendu plus dense. Cette technologie permet donc de stocker plus de données que la

<sup>&</sup>lt;sup>5</sup>Bootloader en anglais

$<sup>^6\</sup>mathrm{Electrically}\text{-}\mathrm{Erasable}$  Programmable Read-Only Memory, une autre mémoire effaçable électriquement, plus ancienne.

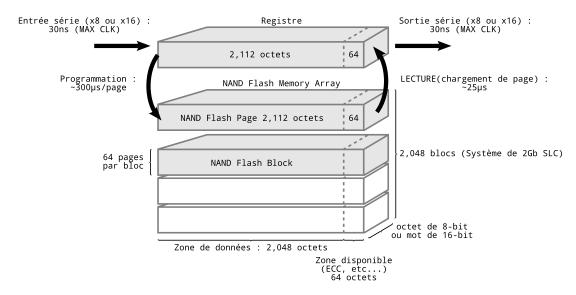

Figure 2.2: Organisation interne de la flash NAND - source [Micron 2006]

NOR à surface de silicium équivalente. L'autre avantage de cette réduction est de diminuer fortement les temps d'écriture et d'effacement.

Du fait de sa densité plus élevée, la NAND a un coût par octet plus faible de 30 à 40 % par rapport à la NOR [Toshiba 2003].

#### 2.1.2.3 Limites de la flash NAND

La flash NAND est organisée en blocs, un bloc étant la plus petite unité d'effacement. Chaque bloc est lui même découpé en pages, la plus petit unité d'écriture et de lecture. Ces lectures et écritures se font par un registre matériel de la taille d'une page. Une demande d'accès se déroule en deux étapes. Tout d'abord, le contrôleur de NAND charge la page demandée dans le registre. Ensuite et seulement lorsque la page est complète dans le registre, chaque octet peut y être lu séquentiellement par l'applicatif.

Une page de NAND supporte un nombre limité d'écritures, au-delà duquel la cohérence des données de la page n'est plus garantie. La lecture est elle aussi non-fiable et quelques bits peuvent être mal positionnés. Ces deux défauts ont amené l'ajout d'une étape intermédiaire de calcul d'un code de correction d'erreur (ECC). Dans la plupart des NAND, ce calcul se fait dans le matériel pour ne pas être trop pénalisant, mais doit être vérifié au niveau logiciel. Ces données de contrôle sont stockées dans une extension de la page (ou *spare*), ce qui augmente le volume de données lues par page (figure 2.2).

Dans les NAND de petite taille prévues pour fonctionner sur des micro-contrôleurs, la gestion des blocs défectueux est complètement ignorée par la NAND et doit donc être gérée au niveau logiciel. La technique utilisée s'appelle le wear-levelling dans une couche d'abstraction logicielle de la NAND appelée Flash Translation Layer (FTL, couche de traduction de la Flash). L'objectif du wear-leveling est de prolonger la durée de vie de chaque bloc en répartissant le plus uniformément possible les écritures et les effacements sur tout l'espace physique disponible. Des informations contenues dans une page physique P peuvent ainsi être déplacées vers la page P+i. La FTL pilote donc le wear-leveling par un algorithme cartographiant ces déplacements et mémorisant une association 1 vers 1 entre

<sup>&</sup>lt;sup>7</sup>mise à niveau de l'usure

une localisation logique immuable et une localisation physique modifiable à l'intérieur de la NAND. Pour un approfondissement de ce sujet, le lecteur peut se référer à la veille technologique de Chung et al [Chung 2006].

L'information à retenir ici sur ce point est que le temps de latence des lectures dans la NAND ne se limite pas à la seule latence du matériel, mais comprend également la traversée de cette couche logicielle qu'est la FLT.

#### 2.1.3 Modèle applicatif maître-esclave

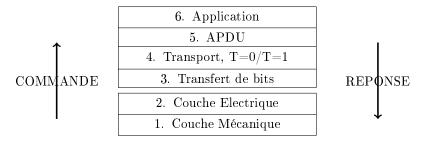

Les cartes à puce sont normalisées selon le standard ISO-7816. La taille du substrat en plastique et le positionnement du connecteur sont définis dans les documents 7816-1 (caractéristiques physiques) et 7816-2 (dimensions et positionnement des contacts). Cette norme définit également une pile de communication (figure 2.3) basée sur une architecture à commande/réponse. Une carte à puce, bien que dotée d'un microprocesseur n'en reste pas moins passive par rapport au terminal. Lui seul peut envoyer des commandes, la carte n'envoyant que des réponses. Si des données sont à renvoyer au terminal, elle ne pourra le faire que si celui-ci le lui demande.

Figure 2.3: Pile de communication ISO-7816

#### 2.1.3.1 Protocole de communication

Au dessus des couches physiques (mécanique, électrique) se trouve la couche de transfert de bits, cadencée au niveau signal. Ce signal est à faible fréquence, rendant la communication relativement lente. La fréquence de ce signal est négociée entre le lecteur et la carte à puce au moment de la mise sous-tension (démarrage à froid) ou d'un redémarrage à chaud (RESET). Cette négociation, ou  $ATR^8$ , comporte ensuite une phase de négociation portant sur le type de protocole de transport qui sera utilisé. Il existe actuellement deux protocoles possibles, définis dans ISO-7816-3. Le premier, T=0, est un protocole série orienté octet. Le second, T=1, est orienté bloc pour une transmission en rafale.

Au dessus de la couche transport, la norme ISO-7816-4 définit le format d'échange de messages qui est indifféremment l'enveloppe d'une commande ou d'une réponse. Ce format de message appelé APDU<sup>9</sup>, comporte une entête et optionnellement un corps de message de longueur variable. L'entête contient : la commande sous forme de code normalisé, les paramètres pour cette commande, une indication concernant la présence de données dans le corps de l'APDU et sa longueur. La carte répond en envoyant deux octets de status. La réponse ne contient pas immédiatement des données. Le code de retour doit indiquer soit une erreur, soit un succès soit signifier au lecteur que des données sont disponibles en envoi.

<sup>&</sup>lt;sup>8</sup>Answer To Reset

<sup>&</sup>lt;sup>9</sup>Application Protocol Data Unit

#### 2.1.3.2 Applications événementielles

La plupart des systèmes embarqués fonctionnent sur un mode dit événementiel. Dans ces systèmes dont l'objectif n'est pas le calcul mais l'interaction avec un environnement, la notion d'événement est omniprésente. Un événement comme la réception d'une trame réseau, un changement de température, le déclenchement d'une alarme, provoque l'exécution d'une routine associée qui ne se serait jamais exécutée d'elle-même.

Dans ce genre de systèmes, les applications embarquées sont donc conçues sur ce modèle de ré-exécution périodique. Elles doivent établir clairement un début et une fin de traitement de l'événement et gérer de possibles réentrances pour traiter des événements concourants.

Le mode maître-esclave des cartes à puce pousse le modèle événementiel vers un mode unidirectionnel où l'application s'exécutant sur la carte à puce doit réagir à un seul type d'événement : la réception d'une commande. La différence est qu'une carte à puce peut être mise hors-tension entre deux réceptions de commande. Les applications doivent donc être conçues pour être capables de gérer de la corrélation d'événements entre-coupés d'arrêt du système.

#### 2.1.4 Ajouter du logiciel à une carte à puce

L'intégration de logiciels dans une carte à puce a évolué au fil du temps suivant les besoins utilisateurs et les contraintes du marché. Elle a commencé par le tout intégré et figé à la fabrication pour aboutir aujourd'hui à la possibilité d'ajout d'applications après mise en circulation de la carte.

Pour comprendre la situation actuelle, cette sous-section décrit les tournants majeurs dans le mode de conception des systèmes d'exploitation et supports applicatifs des cartes à puce.

#### 2.1.4.1 Mutations successives

Première génération Dans la première génération de cartes à puce, l'utilisateur n'avait accès à aucune donnée ni aucune application de la carte. Il devait se « contenter » d'utiliser ce que le fabricant avait bien voulu y mettre. En l'occurrence, il s'agissait le plus souvent de données à usage unique qui étaient la plupart du temps confidentielles, connues seulement du fournisseur, gérées par des systèmes d'exploitation minimalistes.

Deuxième génération La deuxième génération de carte à puce a eu pour objectif de réduire le time-to-market<sup>10</sup> inhérent à un succès commercial comme celui de la carte à puce. Dans ce type de nouvelle carte, l'application était toujours dédiée, mais l'espace de données était devenu accessible et était organisé en interne sous forme de système de fichier, ce qui permettait un contenu modifiable dans le temps. Le système d'exploitation devient alors un peu plus sophistiqué pour pouvoir gérer ces nouveaux types d'accès. On peut citer comme exemple les cartes vitales ou les premières générations de carte SIM permettant à leurs utilisateurs de personnaliser leur base de données de contacts, un agenda, etc...

Troisième génération La troisième génération permet désormais le téléchargement d'applications sur la carte. Cette génération de systèmes d'exploitation a clairement été conçue pour séparer l'aspect fabrication et industrialisation, de l'aspect développement d'applications

$<sup>^{10}\</sup>mathrm{D}$ élai de mise sur le marché.

et donc de personnalisation. C'est ce qu'on appelle la *post-issuance*, cette possibilité de modifier le contenu de la carte à puce, même après sa mise en circulation.

Cette génération de carte est aussi celle qui a vu des langages de haut niveau comme le Java ou le C# franchir le barrière de la miniaturisation. L'objectif de cette nouvelle approche est alors d'offrir une grande souplesse dans le développement de nouveaux contenus grâce à des technologies réputées pour leur agilité.

#### 2.1.4.2 Nouvelles plateformes applicatives

Avec la possibilité de télécharger de nouvelles applications sur une carte post-issuance, la coupure est désormais nette entre les deux rôles de fournisseur de supports physiques et fournisseur de logiciels. Le co-conception matériel/logiciel au niveau systèmes d'exploitation existe toujours du fait des spécificités d'une carte à puce, mais même là, de plus en plus de solutions basées sur des systèmes d'exploitation sur l'étagère voient le jour (Aspect, IBM JCOP, Ecebs Multfile,...).

Idem au niveau applicatif où l'offre en plateformes de développement s'est beaucoup élargie. Si la plateforme JavaCard basée sur la technologie Java reste dominante, d'autres plateformes comme Microsoft .NET, Multos, et d'autres ont rejoint désormais cette offre.

Ces plateformes sont à la fois des environnements de développement et des environnements d'exécution. Dans ce cadre, une application est construite sur station de travail à l'aide de framework et de bibliothèques, qu'elle pourra retrouver à l'identique sur la carte, dans la version exécutable du même environnement. Cette approche allège la taille des applications et le volume des téléchargements, offrant ainsi énormément de souplesse et répondant aux contraintes des cartes à puce.

Dans ce contexte, la conception d'applications pour carte à puce est désormais bien loin des boites noires inaccessibles, et difficiles à programmer par les non-spécialistes.

#### 2.1.5 Les défis de la post-issuance

#### 2.1.5.1 Le défi de la sécurité

Si la *post-issuance* ajoute indéniablement de la flexibilité et une mise sur le marché accélérée, cela ne se fait malheureusement pas sans introduire de nouvelles problématiques, et notamment des problématiques de sécurité.

Les générations de cartes « fermées » garantissaient un haut niveau de sécurité car le système complet pouvait être validé *in-vitro* par le fabricant, par l'utilisation de méthodes formelles par exemple. Même si cette preuve n'était pas fourni au grand public, la clôture définitive du système juste avant sa mise en circulation garantissait de manière tacite que le système ne pourrait plus faillir.

De ce point de vue, la post-issuance a complètement changé la donne. Cette garantie tacite d'un système stable et fiable est brisée par la possibilité d'ajouter de nouvelles applications, potentiellement malveillantes, même involontairement. En effet, dans l'absolu, rien ne prouve à l'utilisateur de la carte ni à son système d'exploitation que la nouvelle application provient d'une source fiable. De plus, et même si c'était le cas, rien ne garantit que la nouvelle application prouvée fiable d'une manière ou d'une autre soit à 100 % compatible avec ce que la carte contient déjà.

Dans ces circonstances, la nécessité d'analyser puis vérifier, voire « prouver » l'application est obligatoire et ne peut être réalisé que par le système d'exploitation de la carte lui-même. C'est à dire en toute fin de déploiement, entre le moment où la carte a entièrement récupéré le binaire de la nouvelle application et l'instant de sa première exécution. Il peut toutefois se passer un certain temps entre ces deux moments.

Une machine virtuelle (VM) est un logiciel reproduisant le comportement d'une machine réelle. L'application s'exécutant dans la machine virtuelle est appelée *invité* (guest), tandis que la machine réelle sur laquelle s'exécute la VM est appelée hôte (host). Le terme « machine » signifie qu'une VM donne l'illusion à guest d'évoluer sur un matériel typique mais qui est en fait différent du matériel sur lequel s'exécute host. Ce matériel est donc virtuel car il n'existe que du point de vue de guest. Il comprend un espace mémoire, des registres virtuels, un jeu d'instructions, etc. à l'image d'une machine Von Neumann classique.

Une VM peut s'insérer dans un système existant à plusieurs endroits. Entre le matériel physique et un système d'exploitation (OS), entre un OS host et un autre OS guest, ou alors sous un langage dit de haut niveau - dans le sens de « éloigné des problématiques d'accès au matériel ». Les deux premiers types de VM, ou VM systèmes, permettent d'exécuter en même temps plusieurs OS de manière concourante sur une même plateforme matérielle. La dernière, ou VM processus, est un processus utilisateur classique. Ce type de VM émule un système générique et s'assure que guest reste isolé du système hôte.

**Portabilité** Pour un langage de haut niveau, ce type d'approche par VM offrant la vision d'un système complet et « générique » , permet d'assurer une entière portabilité de l'application guest sur des machines hôtes hétérogènes. Seule la VM doit être portée et compilée sur l'architecture hôte, ce qui simplifie le développement d'applications multi-plateformes.

Isolation Développée dans un langage sans VM, l'application guest serait un processus utilisateur classique. L'utilisation d'une VM permet également d'isoler l'application guest du reste des applications s'exécutant sur host. Cette approche permet de protéger host de toutes fautes logicielles générées par guest et notamment les erreurs liées à un mauvais usage de la mémoire (pointeurs nuls, dépassement de capacité, fuites,...). C'est pourquoi, ce type de VM utilise des gestionnaires automatiques de mémoire, libérant le développement d'applications d'une étape complexe et délicate.

Jeu d'instructions Un langage de haut niveau basé sur une VM, comme par exemple le Java, n'est pas compilé dans le jeu d'instructions natif de la machine hôte mais dans une jeu d'instructions intermédiaires propre à la VM (ex: bytecodes pour le Java). C'est pourquoi ces langages sont aussi appelés à code semi-compilé. Tel un processeur exécutant du micro-code pour une instruction assembleur, la VM exécute une routine spécifique à une instruction intermédiaire ou handler. Cette routine est l'interprétation d'une instruction intermédiaire.

Figure 2.4: Machines Virtuelles

La vérification ne peut pas se faire *a priori* sur du code partiel, et le système ne peut exécuter que du code vérifié. De plus, le système doit également garantir que la fiabilité soit encore vraie à l'exécution. Telles sont les nouvelles garanties de sécurité que doivent offrir les cartes supportant la *post-issuance*.

#### 2.1.5.2 Machines défensives et analyseurs de code

L'introduction de machines virtuelles (Encadré 2.4) en même temps que la *post-issuance* facilite la résolution de cette nouvelle problématique car le code intermédiaire qu'elles utilisent

est généralement plus facile à analyser que le code compilé. Ce dernier subit en effet les optimisations parfois agressives du compilateur qui entraînent des graphes de flots d'instructions plus difficiles à construire et à suivre. Son autre inconvénient est la quasi-absence de typage des variables une fois compilé qui ne permet pas une analyse stricte du flot d'informations et donc la validation de la bonne utilisation des données qu'il manipule. Beaucoup de travaux se basent donc sur l'analyse d'applications interprétées par une machine virtuelle car comme nous allons le voir par la suite, la connaissance du type est une information primordiale.

Dans le cas des machines virtuelles, la protection contre les applications malveillantes peut se faire sur plusieurs plans, qui peuvent bien évidemment se cumuler. Le premier est la vérification du code intermédiaire [Rose 1998, Deville 2002, Bernardeschi 2008], le deuxième est l'analyse du flot d'informations [Ghindici 2007, Fontaine 2011] et le dernier la mise en œuvre de machines virtuelles dites défensives [Stärk 2001].

L'objectif commun de ces stratégies de sécurisation est de s'assurer que :

- 1. le programme fait ce qu'il doit faire,

- 2. le programme ne fait pas ce qu'il n'est pas autorisé à faire.

Cette assurance dépend alors des propriétés à vérifier, qui doivent être définies à l'avance, comme par exemple l'absence de débordement sur la pile d'exécution, le passage de type autorisé à une méthode, la non-divulgation d'un secret, etc.

Voici quelques définitions et une brève description des principaux mécanismes de protection de l'état de l'art :

Un bloc de base est une séquence d'instructions exécutables consécutivement et dont la condition d'arrêt est une instruction de branchement conditionnel ou inconditionnel, ou la fin du programme. La première instruction d'un bloc de base, ou instruction de tête, est quant à elle déterminée de la façon suivante :

- 1. La première instruction d'un programme est une instruction de tête.

- 2. Toute instruction pouvant être atteinte par un branchement est une instruction de tête.

- 3. Toute instruction suivant immédiatement un branchement est une instruction de tête.

Le graphe de flot de contrôle est un graphe orienté utilisé pour représenter tous les chemins pouvant être suivis par un programme lors de son exécution. Dans ce graphe, chaque nœud représente un bloc de base et un arc représente un saut menant d'un bloc de base à un autre. Ce saut et sa destination sont déterminés par une instruction de branchement clôturant le bloc de base. De ce cas, l'instruction de branchement est aussi appelée « rupteur de flot de contrôle » .

L'interprétation abstraite formalisée par [Cousot 1977], suit le graphe de flot de contrôle d'une application, à la recherche d'informations sémantiques dans et sur le code. Les différences avec une interprétation classique sont qu'un interpréteur abstrait manipule des types et non pas des valeurs et que son interprétation est sans exécution concrète de code. Dans cette approche, tous les arcs du graphe doivent être parcourus. Comme la terminaison d'un programme est indécidable, l'interprétation abstraite doit donc trouver des conditions de sortie pour espérer se terminer, en cherchant ce qu'on appelle des points fixes (i.e. lorsque

les valeurs abstraites<sup>11</sup> des variables découvertes ne changent plus quand l'interprétation revient dans un nœud du graphe déjà visité au moins une fois). Dans l'optique de la protection contre les applications malveillantes, l'utilisation de l'interprétation abstraite est très utile car elle s'approche du vrai comportement d'une application mais sans réellement l'exécuter. Donc en dehors de tout effet de bord qui serait provoqué par l'exécution de code malicieux.

La vérification du code est une analyse par interprétation abstraite du programme à installer pour valider son innocuité avant utilisation. Cette analyse s'effectue méthode par méthode, et sur toutes les méthodes contenues dans l'application. Chaque instruction est déclarée valide si elle respecte la sémantique décrite dans les spécifications du langage (binaire), voir [Lindholm 1999] pour le langage Java. Une méthode n'est déclarée valide que si toutes ses instructions le sont.

En Java, la vérification s'accompagne également d'un contrôle de types, pour s'assurer que les instructions manipulant des objets et des types primitifs le font en fonction des règles de typage du langage. Si nous prenons l'exemple du bytecode Java, les types stricts des variables locales ne sont pas tous explicités par le bytecode car la pile Java ne contient que des entiers 32 bits ou des références d'objets (elles aussi sur 32 bits).

Il est donc nécessaire de vérifier le code en évaluant au fil des instructions les contenus possibles de la pile d'exécution et en comparant les types découverts. Dans une méthode en cours de vérification, un type peut être placé sur la pile par le retour d'une autre méthode, la vérification doit alors se faire également sur tous les types possibles retournés par cette méthode. De la même manière, les branchements conditionnels à l'intérieur d'une méthode sont autant de chemins dans le graphe de flot de contrôle et autant de versions de pile possibles qui doivent également être vérifiées, une par une, jusqu'à trouver des points fixes et un typage correct et valide.

Preuve accompagnant le code Cette autre technique de vérification de code<sup>12</sup> a été proposée par [Necula 1997], adaptée au Java par [Rose 1998] et implémentée avec succès par [Grimaud 1999] dans une carte à puce. Dans cette approche, une preuve est générée au moment de la compilation de l'application et accompagne celle-ci sur sa cible de déploiement. À l'arrivée, l'installateur de la VM n'a plus qu'à vérifier le code par rapport à sa preuve. Cette approche est très utilisée et souvent recommandée. Elle a néanmoins deux inconvénients. Le premier est la taille de la preuve qui augmente de 10 à 30 % la taille de l'application téléchargée. Le second est l'impossibilité de charger une application fiable si elle ne possède pas de preuve.

L'analyse de flots d'informations consiste à analyser les dépendances entre les entrées et les sorties d'un programme de manière à vérifier qu'il satisfait certaines propriétés de confidentialité et/ou d'intégrité vis-à-vis des données qu'il manipule. L'analyse du flot d'informations a, comme la vérification, besoin de connaître les types. Cette fois, le but est d'identifier qu'une application A ne tente pas d'accéder à une donnée secrète contenu dans B, ou à un niveau plus complexe, que B puisse partager son secret avec C, sans que C ne puisse le partager avec A. Ces contraintes formelles sont les propriétés que l'interprétation abstraite doit identifier en parcourant tous les chemins possibles qui pourraient conduire A à accéder au secret de B.

<sup>&</sup>lt;sup>11</sup>Union de tous les types possibles que peut prendre une variable

<sup>&</sup>lt;sup>12</sup>En anglais, Proof-Carrying Code.

Machines défensives À l'inverse des solutions statiques par interprétations abstraites, construire une machine virtuelle défensive consiste à attendre le temps de l'exécution de l'application et à mettre en place des procédures de contrôles actifs de chaque instruction interprétée. Les défenses de la VM ont ainsi une vue nette de l'état applicatif à un instant T pour juger si une action est malicieuse ou non. Dans ce contexte, l'utilisation de machines défensives ajoute un haut niveau de sécurité et divise la complexité de la protection en la répartissant. Mais elles introduisent forcément un surcoût d'exécution en surchargeant les instructions à interpréter, ce qui détériore les performances de la VM. Tandis que l'autre approche par vérification réalisée à l'installation nécessite une charge importante à un instant précis du cycle de vie de la VM puis plus rien.

Status actuel de la post-issuance Dans le cas d'applications déployées post-issuance, l'enjeu majeur est de par exemple protéger une application bancaire de toutes fuites de données dans un environnement d'exécution qui ne lui est plus dédié. Toutes les solutions et approches présentées dans cette sous-section ont été montrées viables pour le monde des cartes à puce et surtout embarquables. Une carte peut donc être autonome dans la vérification des applications qui lui sont ajoutées.

La principale information qui nous servira par la suite est que l'analyse de code bien que d'apparence complexe peut être utilisée, au prix de quelques efforts, dans une carte à puce. Les travaux sur la sécurité le prouvent. Il est donc tout à fait envisageable d'utiliser cette approche pour réaliser d'autres opérations en-ligne (i.e. sur carte).

#### 2.1.5.3 Le défi du stockage

Au-delà de la sécurité, la *post-issuance* est également un défi aux contraintes physiques de la carte à puce. D'une part à cause de son interface de communication relativement lente et d'autre part par sa faible capacité de stockage applicative. Ces deux contraintes obligent alors à avoir autant que possible des applications téléchargeables compactes.

Toutefois, la compacité n'est pas une réponse définitive car cette approche a elle-même sa limite. L'espace de stockage des applications, natives et semi-compilées, est aujourd'hui encore cantonné à un espace mémoire limité. De plus, cet espace de stockage doit être accessible à un coût faible car une machine virtuelle reste un opérateur d'exécution lent. Elle ne peut donc pas être encore un peu plus ralentie lorsqu'elle accède au code qu'elle doit interpréter. C'est pourquoi, les applications téléchargées sont stockées en NOR, l'espace mémoire le plus rapide disponible, et donc à côté du système d'exploitation et de la VM qui y occupent déjà un large espace. Tout ceci limite donc le volume total d'applications téléchargées, dans une mémoire qui n'est pas très large.

#### 2.1.6 Embarquer plus de logiciels dans une carte à puce

En résumé de cette section, il est important de noter que la volonté d'accélérer les processus de mise en circulation de nouveaux modèles de cartes à puce a modifié radicalement la philosophie jusque là attachée à celles-ci. La post-issuance, cette capacité de personnaliser le contenu applicatif de la carte, a remplacé l'ancienne philosophie où la sécurité était principalement basée sur un monde fermé et opaque. Certes, la sécurité reste un point primordial pour un objet dont c'est la principale vocation. Nous avons vu toutefois que les failles à combler se sont déplacées en suivant le même mouvement, vers les couches applicatives plus hautes.

Cependant, l'utilisation d'un intergiciel comme une machine virtuelle, placée entre le système d'exploitation et l'application, permet d'avoir à la fois des applications plus faciles

à développer et mais aussi un haut niveau de protection contre les fautes. De plus, les recherches très actives dans le domaine de la sécurité embarquée permettent de plus en plus facilement de valider les impératifs de sécurité requis par de puissants acteurs exigeants comme les vendeurs de cartes bancaires.

Nous avons aussi noté que l'engouement grandissant pour ces cartes « ouvertes » se voit désormais limité par les contraintes inhérentes à une carte à puce et principalement le peu de mémoire dont elle dispose pour le stockage de code exécutable.

#### 2.2 De Java à JavaCard

Dans cette section, nous présentons JavaCard 2.2, la plateforme applicative pour cartes à puce ouvertes la plus répandue. Cette plateforme est basée sur la technologie Java et s'articule donc autour d'une machine virtuelle. Nous commencerons par présenter la technologie Java puis nous verrons comment celle-ci a pu être introduite dans un système aussi petit qu'une carte à puce grâce à la technologie JavaCard.

#### 2.2.1 Le langage Java et sa machine virtuelle

Le langage Java [Gosling 2005] est de nos jours l'un des langages de programmation les plus répandus. Ce langage tire sa popularité des avantages apportés par l'utilisation sous-jacente d'une machine virtuelle.

La devise du langage Java imaginée par ces concepteurs est « compile once, run every-where »  $^{13}$ . Pour que cette compilation unique et indépendante du système soit possible, le code Java n'est pas compilé en langage machine mais dans un langage intermédiaire qui sera interprété par la machine virtuelle.

Il existe autant de façons de concevoir une machine virtuelle Java (JVM) que de JVM, mais toutes se doivent de respecter la signification propre à chaque instruction, qui sont définies dans les spécifications de la machine virtuelle Java [Lindholm 1999]. En interne, une JVM se compose généralement de plusieurs sous-systèmes qui forment trois grands groupes ; un groupe dédié à l'exécution et l'ordonnancement de code, un groupe dédié à la gestion automatique de la mémoire et un groupe garantissant le chargement dynamique et sécurisé du code.

#### 2.2.1.1 Processus virtuels d'exécution

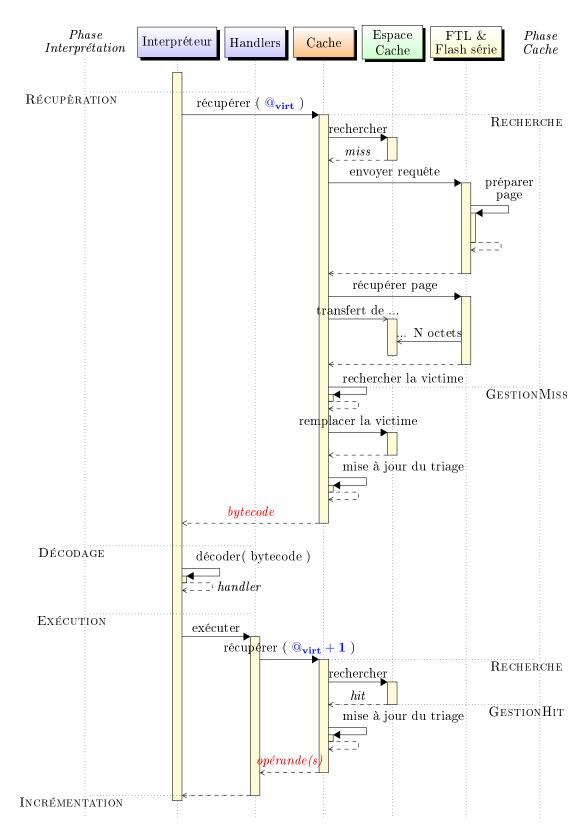

Interpréteur Le cœur de la machine virtuelle est son interpréteur. Cet interpréteur est une boucle infinie qui récupère, décode et exécute des instructions Java (Listing 6.1, page 100).

Ce listing présente la récupération d'une instruction dans un tableau d'octets en mémoire adressable. Cependant, ce code peut être stocké ailleurs, dans une mémoire série par exemple, et peut donc exiger un mode d'accès plus complexe. D'où le terme communément utilisé de « récupération » plutôt que lecture, trop réducteur.

**Définition.** Dans un interpréteur, l'étape de **décodage** consiste à trouver la correspondance entre l'instruction récupérée depuis l'espace de code et la routine implémentant l'action de cette instruction.

Une fois cette routine trouvée, celle-ci est exécutée et le processus d'interprétation recommence au début après avoir avancé le pointeur d'instruction vers le bytecode suivant.

$<sup>^{13}</sup>i.e.$  compiler une fois, exécuter (tel quel) n'importe où

Listing 2.1: Implémentation basique d'un interpréteur

Compilateur Pour des raisons de performances, les machines virtuelles Java modernes embarquent de plus en plus souvent un compilateur de code à la volée [Adl-Tabatabai 1998, Krall 1998, Arnold 2000]. Dans l'absolu, un interpréteur standard est très lent, de 5 à fois 20 plus lent que du code natif. La compilation à la volée permet de transformer et surtout d'optimiser pour la plate-forme cible une instruction ou un groupe d'instructions Java en blocs d'instructions machine directement exécutées par le processeur et non plus par l'interpréteur.

Des travaux comme [Grimaud 1999] ont montré qu'une telle infrastructure pouvait être transposée dans des systèmes aussi petits qu'une carte à puce.

Ordonnanceur L'ordonnanceur de tâches est un autre processus d'exécution commun à bon nombre de machines virtuelles. Il est présent dans une machine virtuelle supportant les processus légers pour répartir la charge et le temps alloué entre des processus applicatifs concourants. Il peut prendre une autre forme lorsque le modèle d'exécution est événementiel comme dans le cartes à puce. Dans ce cas, il active ou désactive une application sur la base d'événements qu'il aura attrapé puis envoyé à l'application destrinatrice. Il peut s'agir d'une interruption matérielle, d'une alarme programmée, la réception d'une APDU, etc.

#### 2.2.1.2 Processus de gestion de la mémoire

Une machine virtuelle permet également une gestion automatique de la mémoire. Automatique signifie que la machine virtuelle ne laisse pas les applications, allouer ou libérer des données en mémoire mais prend en charge cette gestion, évitant ainsi certaines erreurs de développement aux conséquences désastreuses à l'exécution. Deux processus sont chargées de cette mission, un alloueur et un collecteur.

L'alloueur<sup>14</sup> de mémoire est chargé comme son nom l'indique d'allouer des espaces mémoires à la demande d'une application Java. Cette allocation se fait généralement dans un espace mémoire dévolu et appelé le tas<sup>15</sup>. Lorsque la tas est plein, l'alloueur passe la main au collecteur ou « ramasse-miette ».

Le ramasse-miette est le pendant de l'alloueur et se charge de la libération de données stockées dans le tas. Généralement, le ramasse-miette fonctionne en deux étapes. La première consiste à identifier toutes les données encore présentes dans le tas qui ne sont plus utilisées. La deuxième étape consiste quant à elle à effectivement libérer la mémoire de ces données inutiles. Un ramasse-miette inclut parfois une troisième étape consistant à

<sup>&</sup>lt;sup>14</sup>Parfois aussi appelé allocateur

<sup>&</sup>lt;sup>15</sup>Heap en anglais

compacter le tas en regroupant au début de celui-ci toutes les données encore présentes dans le tas. Ce rassemblement permet de retrouver un plus grand espace contigüe de mémoire libre.

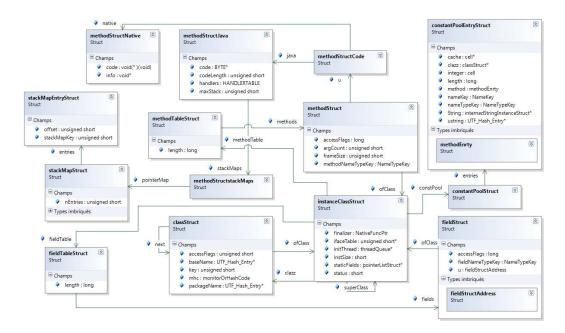

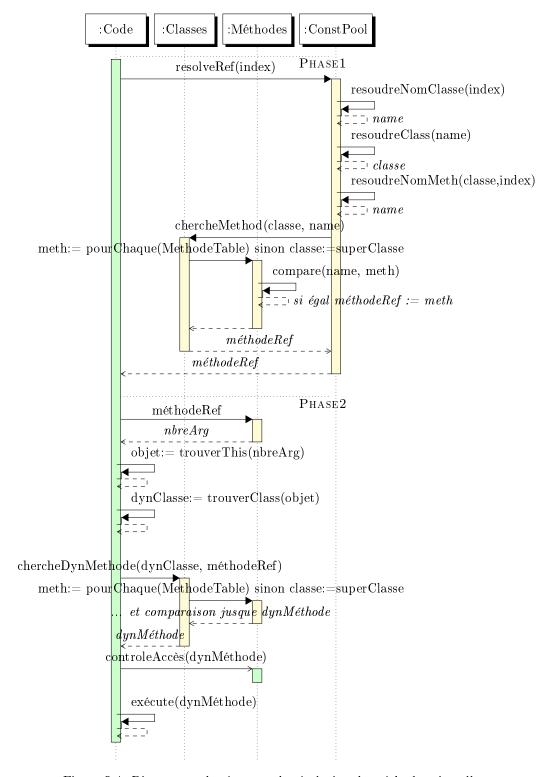

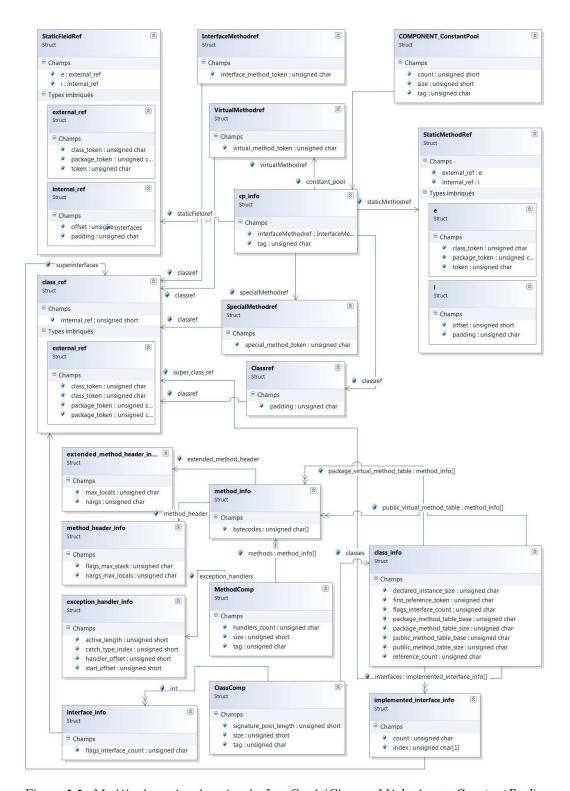

#### 2.2.1.3 Classes, objets et méta-données

La conception et la mise en œuvre d'une machine virtuelle Java se doit de respecter les spécifications du format du fichier binaire exécutable Java, le fichier de classe, et la sémantique de chaque instruction du langage intermédiaire (bytecode). Ces spécifications sont définies dans [Lindholm 1999], 2nd Édition. Cet impératif est pris en charge par le processus de chargement de classes.

Le langage Java est un langage orienté objet où un objet représente un concept de la vie courante ou applicatif, plus ou moins concret. En programmation orienté objet, un objet est le résultat de l'instanciation d'une classe. Cette classe est la structuration précise du sens que veut donner un programmeur à un objet lorsqu'il sera créé à l'exécution. La classe est donc dotée d'attributs représentants les propriétés et l'état de l'objet, ainsi que son comportement par le biais de méthodes. Une méthode a principalement trois usages : décrire le comportement de l'objet une fois instancié, modifier les propriétés de l'objet et permettre son interaction avec d'autres objets ou avec le système.

En conséquence, une classe est l'entité contenant les informations utiles, nécessaires et suffisantes pour que la VM puisse créer une ou plusieurs instances de cette classe lorsqu'elle en reçoit l'instruction. Ces informations constituent les méta-données du langage.

\*

**Définition.** Une **méta-donnée** est une donnée valuée, statique et a priori constante fournie par une classe et décrivant un comportement, une propriété et/ou une capacité d'un objet, instanciation de cette classe.

\*

Suivant cette définition, un *objet* est donc une donnée volatile qui n'existe qu'à l'exécution, et une classe est un ensemble de méta-données définissant champs, méthodes, et tout autres attributs propres de ces derniers. Dans le fichier de classe, ces méta-données sont reliées entre elles sous formes de références symboliques textuelles.

Dans la technologie Java, les méta-données sont acquises par la JVM lors du processus de chargement de classe, préalable à toutes exécutions. Cette étape, ré-itérée pour chaque classe, peut avoir lieu à plusieurs moments, durant l'exécution de la JVM. Cette phase se produit en premier lieu lors du démarrage de la JVM pour charger les classes de base, puis intervient au lancement d'une application pour charger les classes de cette application et leurs dépendances, et enfin lors d'appels explicites au chargement dynamique de classes pendant l'exécution.

L'acquisition des méta-données s'étale sur trois étapes. Ce processus commence par une vérification qui contrôle l'intégrité des méta-données à charger, bytecodes inclus, et leur respect des spécifications du langage. Dans une deuxième étape, les références symboliques<sup>16</sup> sont résolues, généralement en adresses physiques, en validant au passage que toutes les dépendances entre classes sont satisfaites. Enfin, la JVM peut engager l'initialisation de certaines données, notamment les champs statiques.

<sup>&</sup>lt;sup>16</sup>Ce processus est abordé en détail dans notre étude approfondie des méta-données section 5.2.1.2, page 78.

Ces étapes ne sont pas nécessairement effectuées immédiatement à la suite des précédentes, et peuvent n'intervenir qu'au moment utile. Toutefois, l'ordre de ces trois étapes se doit d'être respecté. Une fois celles-ci terminées, la classe passe dans l'état « chargé » et est prête à être instanciée sous forme de nouveaux objets, et le code à être exécuté par la JVM.

#### 2.2.2 La plate-forme JavaCard 2.2: Java dans une tête d'épingle

JavaCard [JCVM.2.2.1 2003] est une plate-forme de développement et d'exécution ayant pour objectif de permettre à des applications écrites en Java de s'exécuter sur des cartes à puce. Le grand challenge de JavaCard est d'intégrer une machine virtuelle dans ces matériels contraints, malgré sa réputation d'être gourmande en ressource.

Dans cette section, nous allons aborder les différences qui existent entre les plateformes Java standard et JavaCard. Ces différences se trouvent réparties sur trois niveaux : d'abord au niveau langage, puis au niveau environnement d'exécution, et enfin dans les caractéristiques propres au format binaire de JavaCard.

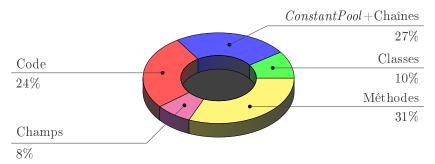

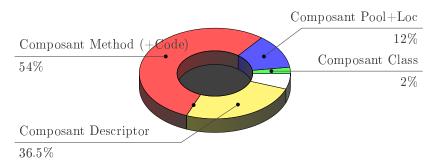

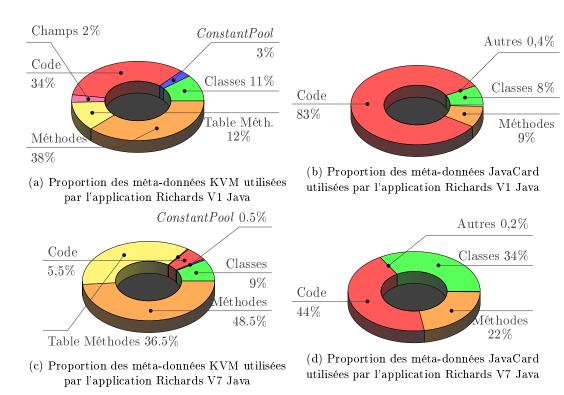

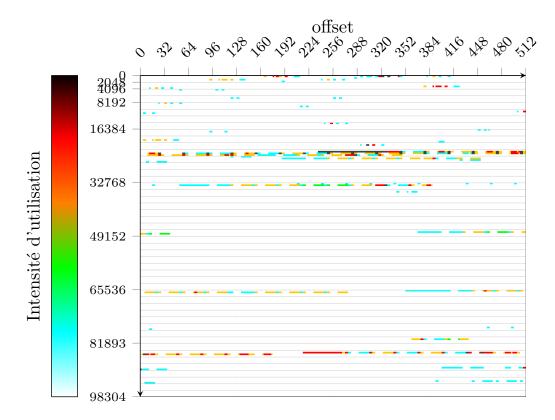

#### 2.2.2.1 Une Machine Virtuelle scindée