Numéro d'ordre: 40762

# Université des Sciences et Technologies de Lille École Doctorale Sciences pour l'Ingérnieur

# THÈSE

présentée pour obtenir le titre de docteur spécialité Informatique

par

# ANTONIO WENDELL DE OLIVEIRA RODRIGUES

# UNE MÉTHODOLOGIE POUR LE DÉVELOPPEMENT D'APPLICATIONS HAUTES PERFORMANCES SUR DES ARCHITECTURES GPGPU: APPLICATION À LA SIMULATION DES MACHINES ÉLÉCTRIQUES

Thèse soutenue le 26 Janvier 2012, devant la commission d'examen formée de :

| 1 | Pierre Manneback    | Rapporteur/Président |

|---|---------------------|----------------------|

| 2 | Sven-Bodo Scholz    | Rapporteur           |

| 3 | Yvonnick Le Menach  | Examinateur          |

| 4 | Mamy Rakotovao      | Examinateur          |

| 5 | Frédéric Guyomarc'h | Co-Directeur         |

| 6 | Jean-Luc Dekeyser   | Directeur            |

|   |                     |                      |

Université des Sciences et Technologies de Lille LIFL - Cité Scientifique, Bat. M3 - 59655 Villeneuve d'Ascq Cedex

Number : 40762

Université des Sciences et Technologies de Lille École Doctorale Sciences pour l'Ingérnieur

# THESIS

submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science

by

## ANTONIO WENDELL DE OLIVEIRA RODRIGUES

# A METHODOLOGY TO DEVELOP HIGH PERFORMANCE APPLICATIONS ON GPGPU ARCHITECTURES: APPLICATION TO SIMULATION OF ELECTRICAL MACHINES

### January 26, 2012 Commitee in charge

| 1 | Pierre Manneback    | Reviewer/President |

|---|---------------------|--------------------|

| 2 | Sven-Bodo Scholz    | Reviewer           |

| 3 | Yvonnick Le Menach  | Examiner           |

| 4 | Mamy Rakotovao      | Examiner           |

| 4 | Frédéric Guyomarc'h | Co-advisor         |

| 6 | Jean-Luc Dekeyser   | Advisor            |

UNIVERSITÉ DES SCIENCES ET TECHNOLOGIES DE LILLE LIFL - Cité Scientifique, Bat. M3 - 59655 Villeneuve d'Ascq Cedex

# A METHODOLOGY TO DEVELOP HIGH PERFORMANCE APPLICATIONS ON GPGPU ARCHITECTURES: APPLICATION TO SIMULATION OF ELECTRICAL MACHINES

### ANTONIO WENDELL DE OLIVEIRA RODRIGUES

Doctorate Thesis January 2012

Antonio Wendell de Oliveira Rodrigues: *A Methodology to Develop High Performance Applications on GPGPU Architectures: Application to Simulation of Electrical Machines,* Doctorate Thesis © January 2012 *This thesis is dedicated to my parents.* For their endless love, support and encouragement

### RESUMÉ

Les phénomènes physiques complexes peuvent être simulés numériquement par des techniques mathématiques basées souvent sur la discrétisation des équations aux dérivées partielles régissant ces phénomènes. Ces simulations peuvent mener ainsi à la résolution de très grands systèmes. La parallélisation des codes de simulation numérique, c'est-à-dire leur adaptation aux architectures des calculateurs parallèles, est alors une nécessité pour parvenir à faire ces simulations en des temps non-exorbitants. Le parallélisme s'est imposé au niveau des architectures de processeurs et les cartes graphiques sont maintenant utilisées pour des fins de calcul généraliste, aussi appelé "General-Purpose computation on Graphics Processing Unit (GPGPU)", avec comme avantage évident l'excellent rapport performance/prix.

Cette thèse se place dans le domaine de la conception de ces applications hautes-performances pour la simulation des machines électriques. Nous fournissons une méthodologie basée sur l'Ingénierie Dirigées par les Modèles (IDM) qui permet de modéliser une application et l'architecture sur laquelle l'exécuter afin de générer un code OpenCL. Notre objectif est d'aider les spécialistes en algorithmes de simulations numériques à créer un code efficace qui tourne sur les architectures GPGPU. Pour cela, une chaine de compilation de modèles qui prend en compte les plusieurs aspects du modèle de programmation OpenCL est fournie. De plus, pour rendre le code raisonnablement efficace par rapport à un code développé à la main, nous fournissons des transformations de modèles qui regardent des niveaux d'optimisations basées sur les caractéristiques de l'architecture (niveau de mémoire par exemple).

Comme validation expérimentale, la méthodologie est appliquée à la création d'une application qui résout un système linéaire issu de la Méthode des Éléments Finis pour la simulation de machines électriques. Dans ce cas nous montrons, entre autres, la capacité de la méthodologie de passer à l'échelle par une simple modification de la multiplicité des unités GPU disponibles.

**Mots-clés:** MDE, UML, MARTE, Transformation de Modéles, Génération Automatique de Code, GPGPU, OpenCL, Simulation Numérique, Machines Électriques

### ABSTRACT

Complex physical phenomena can be numerically simulated by mathematical techniques. Usually, these techniques are based on discretization of partial differential equations that govern these phenomena. Hence, these simulations enable the solution of large-scale systems. The parallelization of algorithms of numerical simulation, i.e., their adaptation to parallel processing architectures, is an aim to reach in order to hinder exorbitant execution times. The parallelism has been imposed at the level of processor architectures and graphics cards are now used for purposes of general calculation, also known as "General-Purpose computation on Graphics Processing Unit (GPGPU)". The clear benefit is the excellent performance/price ratio.

This thesis addresses the design of high-performance applications for simulation of electrical machines. We provide a methodology based on Model Driven Engineering (MDE) to model an application and its execution architecture in order to generate OpenCL code. Our goal is to assist specialists in algorithms of numerical simulations to create a code that runs efficiently on GPGPU architectures. To ensure this, we offer a compilation model chain that takes into account several aspects of the OpenCL programming model. In addition, to get a code fairly efficient compared to a code developed manually, we provide model transformations that analyze some levels of optimizations based on the characteristics of the architecture (e. g. memory issues).

As an experimental validation, the methodology is applied to the creation of an application that solves a linear system resulting from the Finite Element Method (FEM) for simulation of electrical machines. In this case, we show, among other things, the ability of the methodology of scaling by a simple modification of the number of available GPU devices.

**Keywords:** MDE, UML, MARTE, Model Transformation, Automatic Code Generation, GPGPU, OpenCL, Numerical Simulation, Electrical Machines

### PUBLICATIONS

Some proposals and figures have appeared previously in the following publications:

### JOURNALS

- Antonio Wendell De Oliveira Rodrigues, Frédéric Guyomarc'h, Yvonnick Le Menach, and Jean-Luc Dekeyser. Automatic Multi-GPU Code Generation applied to Simulation of Electrical Machines. *Magnetics, IEEE Transactions on*, 48(2):831–834, Feb. 2012. ISSN 0018-9464. doi: 10.1109/TMAG.2011.2179527

- 2. Antonio Wendell De Oliveira Rodrigues, Frédéric Guyomarc'h, and Jean-Luc Dekeyser. An MDE Approach for Automatic Code Generation from UML/MARTE to OpenCL. *IEEE Computer in Science & Engineering - Special Edition on GPUs, Journal*, Jan 2012 (to appear)

### CONFERENCES AND WORKSHOPS

- Antonio Wendell De Oliveira Rodrigues, Frédéric Guyomarc'h, Yvonnick Le Menach, and Jean-Luc Dekeyser. Parallel Sparse Matrix Solver on the GPU Applied to Simulation of Electrical Machines. In *Compumag 2009*, Florianopolis, Brazil, November 2009

- 2. Antonio Wendell De Oliveira Rodrigues, Frédéric Guyomarc'h, and Jean-Luc Dekeyser. Programming Massively Parallel Architectures using MARTE: a Case Study. In *2nd Workshop on Model Based Engineering for Embedded Systems Design (M-BED) on Date Conference 2011*, Grenoble, France, March 2011

- 3. Antonio Wendell De Oliveira Rodrigues, Frédéric Guyomarc'h, and Jean-Luc Dekeyser. Using ArrayOL to Identify Potentially Shareable Data in Thread Work-Groups of GPUs. In *Designing for Embedded Parallel Computing Platforms: Architectures, Design Tools, and Applications on DATE 2011*, Grenoble, France, March 2011. Work in-Progress Poster

- 4. Antonio Wendell De Oliveira Rodrigues, Frédéric Guyomarc'h, and Jean-Luc Dekeyser. A Modeling Approach based on UM-L/MARTE for GPU Architecture. In Symposium en Architectures nouvelles de machines (SympA'14), Saint Malo, France, May 2011

- 5. Jing Guo, Antonio Wendell De Oliveira Rodrigues, Jerarajan Thiyagalingam, Frédéric Guyomarc'h, Pierre Boulet, and Sven-Bodo Scholz. Harnessing the Power of GPUs without Losing Abstractions in SaC and ArrayOL: A Comparative Study. In *HIPS* 2011, 16th International Workshop on High-Level Parallel Programming Models and Supportive Environments, Anchorage (Alaska), United States of America, May 2011

- Antonio Wendell De Oliveira Rodrigues, Frédéric Guyomarc'h, Jean-Luc Dekeyser, and Yvonnick Le Menach. Automatic Multi-GPU Code Generation applied to Simulation of Electrical Machines. In *Compumag 2011*, Sydney, Australia, July 2011

### RESEARCH REPORT

- Antonio Wendell De Oliveira Rodrigues, Frédéric Guyomarc'h, and Jean-Luc Dekeyser. An MDE Approach for Automatic Code Generation from MARTE to OpenCL. Research Report RR-7525, INRIA, February 2011. Research Report RR-7525 in http: //hal.inria.fr/inria-00563411

- 2. Antonio Wendell De Oliveira Rodrigues, Vincent Aranega, Anne Etien, Frédéric Guyomarc'h, and Jean-Luc Dekeyser. Enabling Traceability in an MDE Approach to Improve Performance of GPU Applications. Rapport de recherche RR-7720, INRIA, August 2011. Research Report RR-7720 in http://hal.inria.fr/inria-00617912

### ACKNOWLEDGMENTS

First and foremost, I have to thank my father, Antonio, and specially my beloved mother, Francisca, for their love and support throughout my life. Thank you both for giving me strength to reach for the stars and chase my dreams. My sisters, Weidina, Weidiany, and Weidinara, deserve my wholehearted thanks as well. To my dearly loved fiancée (and future wife) Kamila, thank you for your assistance, your encouragement, and your company (even if sometimes virtual). I am very happy by your side. I owe this thesis to all of you.

I would like to sincerely thank my supervisors, Jean-Luc Dekeyser and Frédéric Guyomarc'h (the best co-advisor ever), for their guidance and support throughout this study, and especially for their confidence in me. I hope to continue working with you in the future. To all researchers from DaRT team, above all, Anne Etien, Abdoulave Gamatié, and Pierre Boulet, people with whom I discussed many points of my work concerning their research field. I would like also to thank Alexis Muller and Thomas Legrand, for so many times that I bothered them to help me to fix some issues on the Gaspard's tools, and they kindly always helped me. To all colleagues and PhD students from the office 111bis, the former ones: Imran, Adolf, Calin, and Meriem, also the current ones: Chiraz, Sana, Amine, and Pamela, my sincere thanks. Furthermore, I would like to express my gratitude to Karine Lewandowski for her administrative support always well done. I cannot forget to thank you, Vincent Aranega, for sharing ideas during our researches, the pleasure working together, and foremost, your friendship.

This thesis relies on industrial applications. I have to thank Yvonnick Le Menach, Francis Piriou, both from L2EP laboratory, and Mamy Rakotovao from Valeo, for giving me examples, opinions, and assistance to do the experimental validation of my results.

Halfway through the journey of my thesis, I had the great opportunity to work with the SAC's team at the University of Hertfordshire. This was really valuable to my work. In particular, thanks go to Sven-Bodo, Jing Guo, Nil, Dan, and Jeyarajan.

Living in France allowed me to meet some new and old friends. Raquel and Ludovic, you do not know how important you were and are when you give me the warmest welcomes at your home, thank you. Thanks go also to you, Alexis Deneux, Joelia (I cannot get count how many times you gave me a hand), Cariza, Mariusa, and Nizar. Your friendship and support were essential to my stay. Thank you very much, Carina e Reinaldo, my former students, and now two great friends who gave me a good time in Grenoble and Dublin. Furthermore, to Carina's father and my previous advisor, Mauro Oliveira, who has a valuable role in my life as a researcher, thanks.

I have to express my gratitude to the Federal Institute of Ceara (IFCE) and my country, Brazil. I am very grateful to all my friends from the Telematica Department for replacing me while I was absent. Thanks to my friend César Olavo, who gave me the opportunity to meet the DaRT team, and consequently to work with them. I have to mention yet some special friends that always believed in the success of this thesis. Thank you, Joesito and Bené, for being such a good "big brother/sister" to me. Thank you, Janaina, I know you a long time, and I feel our friendship growing more and more, this makes me happy. By the way, thank you for undertaking all administrative stuff at IFCE. I am very pleased to work with you again soon.

In 2011, I lost a big friend. He was directly responsible for me deciding to do a doctorate. Thank you, Valdson. My dear friend Nayara, who always asked me how my work was going, and who gave me the right words to keep my motivation, my humble thank you. Furthermore, thanks to my dear friends Corneli Jr. and Italo for being there whenever I took a break of my works and left to Brazil.

Thank you, Lord, for always being there for me.

Thanks to Valeo and Région Nord-Pas de Calais for supporting this thesis with total confidence in my works.

This thesis was written in English by a Brazilian. However, I am lucky that it had been conducted by researchers who showed me the best principles of the French research.

Finally, I would like to thank everybody who was important to the successful realization of this thesis, as well as expressing my apology that I could not mention personally one by one.

### CONTENTS

| Lı | ST OF | Figure     | 2S                                     | xxiii |

|----|-------|------------|----------------------------------------|-------|

| Lı | ST OF | TABLES     | )<br>)                                 | xxiv  |

| Lı | ST OF | LISTIN     | GS                                     | xxv   |

| Ac | CRONY | ΥMS        |                                        | xxvi  |

| In | TROD  | UCTION     |                                        | 1     |

|    |       |            |                                        |       |

| Ι  |       |            | HE ART                                 | 15    |

| 1  | HIG   |            | EL MODELING AND CODE GENERATION ON HPO | C 17  |

|    | 1.1   | High-l     | Level Specification Approaches         | 18    |

|    |       | 1.1.1      | Gaspard2: OpenMP Branch                | 18    |

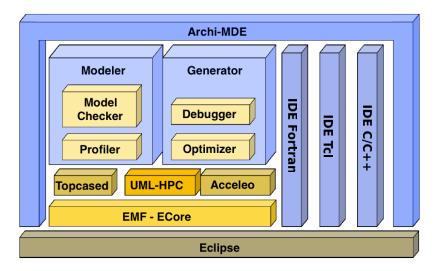

|    |       | 1.1.2      | Archi-MDE                              | 19    |

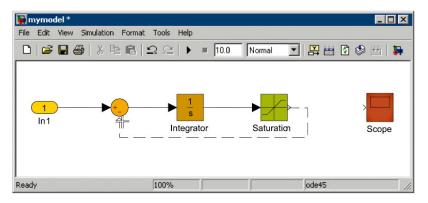

|    |       | 1.1.3      | Simulink                               | 19    |

|    |       | 1.1.4      | OpenModelica                           | 20    |

|    |       | 1.1.5      | Syntony                                | 22    |

|    | 1.2   | Extens     | sions for Programming Languages        | 23    |

|    |       | 1.2.1      | Mint Programming Model                 | 23    |

|    |       | 1.2.2      | OpenHMPP                               | 24    |

|    |       | 1.2.3      | Java OpenCL Bindings                   | 26    |

|    |       | 1.2.4      | Matlab and Matlab-like on GPU          | 27    |

|    |       | 1.2.5      | PyOpenCL                               | 27    |

|    |       | 1.2.6      | SAC                                    | 29    |

|    | 1.3   | Other      | Contributions                          | 30    |

|    | 1.4   | Comp       | arative Table of Features              | 31    |

|    | 1.5   | Conclu     | usion                                  | 31    |

| 2  | GAS   | PARD2      | AS CODE GENERATION FRAMEWORK           | 33    |

|    | 2.1   | Introd     | luction to the Framework               | 35    |

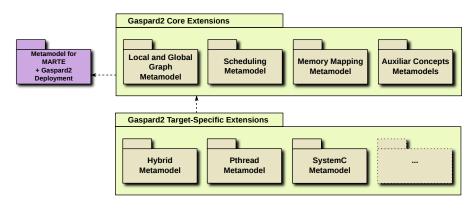

|    |       | 2.1.1      | Gaspard2 Extensions                    | 36    |

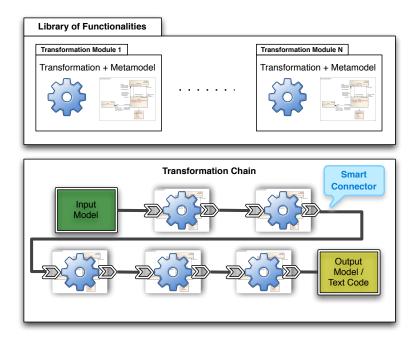

|    | 2.2   | Transf     | formation Chain                        | 37    |

|    | 2.3   | Target     | Platforms                              | 37    |

|    |       | 2.3.1      | Sequential C                           | 38    |

|    |       | 2.3.2      | Pthread                                | 38    |

|    |       | 2.3.3      | OpenMP (Fortran and C)                 | 39    |

|    |       | 2.3.4      | SystemC                                | 39    |

|    |       | 2.3.5      | LUSTRE and SIGNAL                      | 39    |

|    |       | 2.3.6      | VHDL                                   | 40    |

|    | 2.4   | 0          | yment and IPs                          | 40    |

|    | 2.5   |            | Î Refactoring                          | 40    |

|    | 2.6   |            | bility                                 | 42    |

|    | 2.7   |            | d Tools                                | 42    |

|    | •     | 2.7.1      | Eclipse                                | 43    |

|    |       | ,<br>2.7.2 | Papyrus Modeling Tool                  | 43    |

|   |     | 2.7.3  | MDFactory                                                                         | 44 |

|---|-----|--------|-----------------------------------------------------------------------------------|----|

|   |     | 2.7.4  | QVTO                                                                              | 44 |

|   |     | 2.7.5  | Acceleo Code Generation                                                           | 44 |

|   | 2.8 | Conclu | usion                                                                             | 44 |

|   |     |        |                                                                                   |    |

| Π | MET | HODOL  | OGY APPROACH                                                                      | 45 |

| 3 | DEV |        | NG APPLICATIONS                                                                   | 47 |

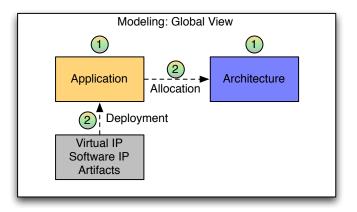

|   | 3.1 |        | uction to Modeling Methodology                                                    | 47 |

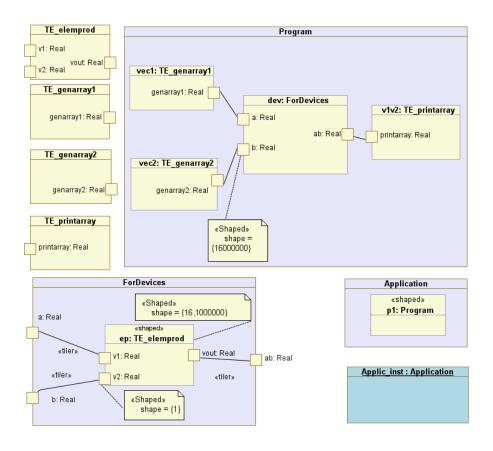

|   | 3.2 | Matrix | Multiplication                                                                    | 48 |

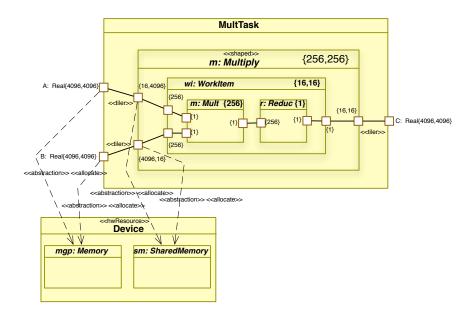

|   |     | 3.2.1  | Modeling the Matrix Multiplication                                                | 51 |

|   |     | 3.2.2  | Generating Code                                                                   | 57 |

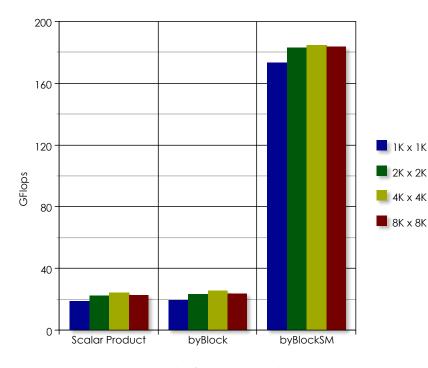

|   |     | 3.2.3  | Results and Benchmarks                                                            | 57 |

|   | 3.3 | Signal | Processing                                                                        | 58 |

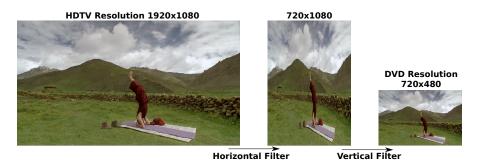

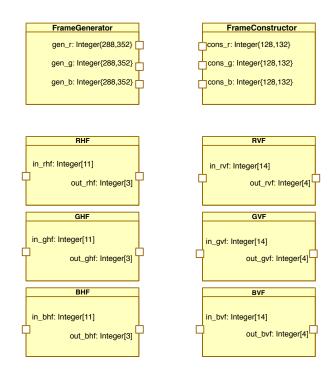

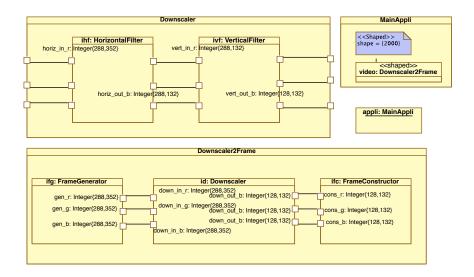

|   |     | 3.3.1  | Modeling the Downscaler                                                           | 59 |

|   |     | 3.3.2  | Results and Benchmarks                                                            | 61 |

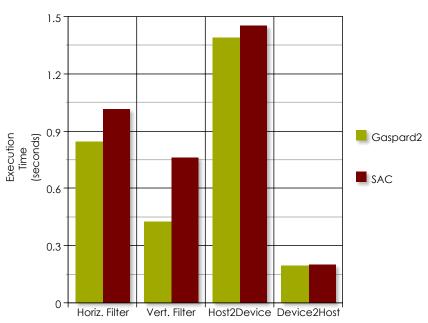

|   |     | 3.3.3  | Comparing to SAC                                                                  | 62 |

|   | 3.4 | Conclu | usion                                                                             | 65 |

| 4 | MET | AMOD   | ELS AND GPUS                                                                      | 67 |

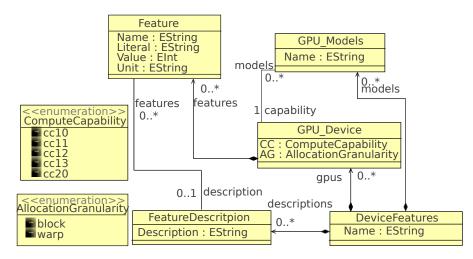

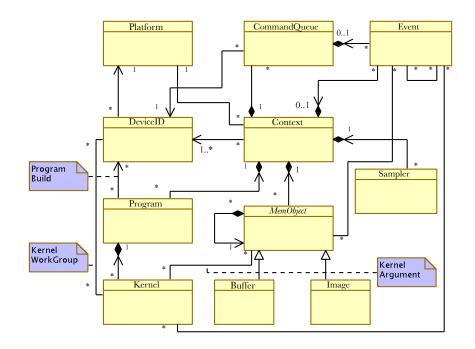

|   | 4.1 | Metan  | nodels for the GPU Programming Model                                              | 68 |

|   |     | 4.1.1  | Coprocessor                                                                       | 68 |

|   |     | 4.1.2  | Host and Device Memories                                                          | 68 |

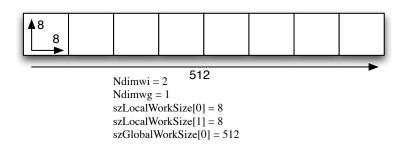

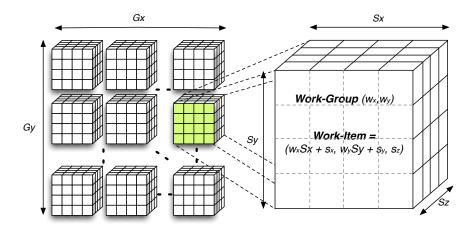

|   |     |        | Work-Groups and Work-Items Topology                                               | 68 |

|   |     | 4.1.4  | Optimizations                                                                     | 69 |

|   | 4.2 | Sched  | uling                                                                             | 69 |

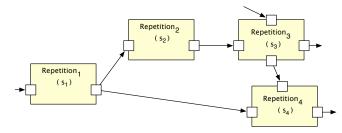

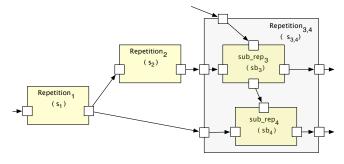

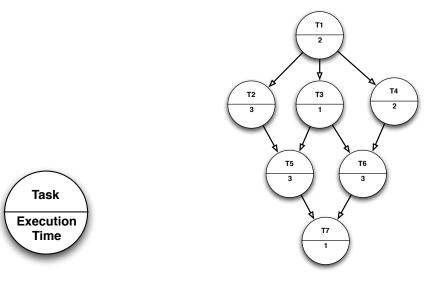

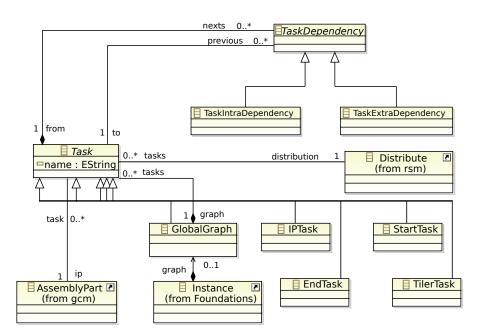

|   |     | 4.2.1  | Building a Task Graph                                                             | 69 |

|   |     | 4.2.2  | Choosing the Execution Order                                                      | 74 |

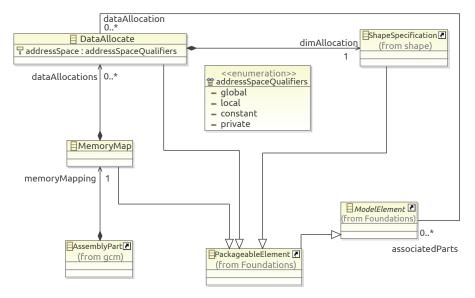

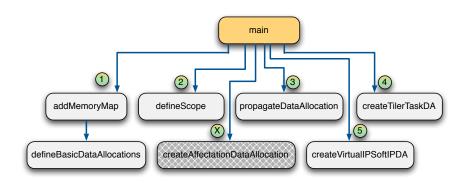

|   | 4.3 |        | ory Mapping                                                                       | 74 |

|   | 4.4 | 5      | d                                                                                 | 76 |

|   | 4.5 | Conclu | usion                                                                             | 80 |

| 5 | MOI |        | OWARDS CODE                                                                       | 81 |

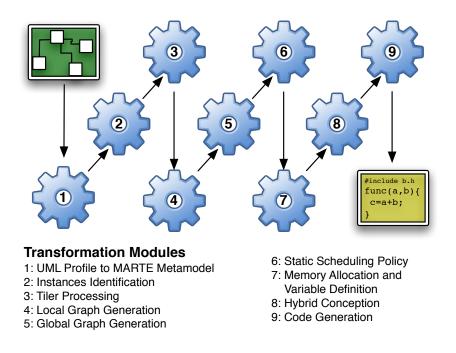

|   | 5.1 |        | ng a Transformation Module                                                        | 82 |

|   | 5.2 | Chain  | ing Model Transformations                                                         | 83 |

|   | 5.3 | Gener  | ic Transformation Modules                                                         | 84 |

|   |     | 5.3.1  | UML Profile to MARTE Metamodel (1)                                                | 84 |

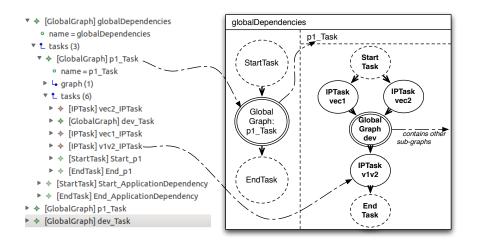

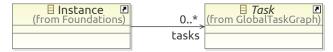

|   |     | 5.3.2  | Instances Identification (2)                                                      | 85 |

|   |     | 5.3.3  | Tiler Processing $(3)$                                                            | 86 |

|   |     | 5.3.4  | Task Graph and Scheduling (4,5,6)                                                 | 86 |

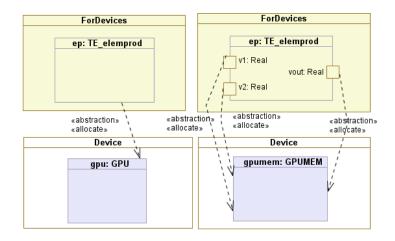

|   | 5.4 |        | bry Allocation and Variable Definitions (7)                                       | 87 |

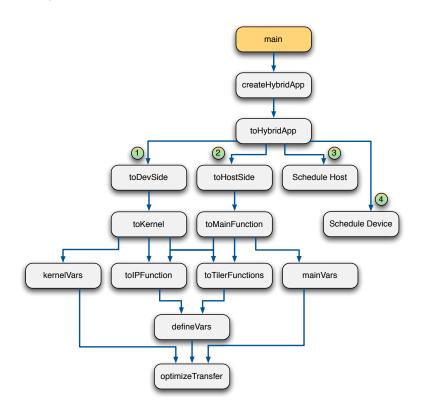

|   | 5.5 | Hybri  | d Conception (8)                                                                  | 88 |

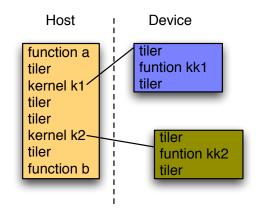

|   |     | 5.5.1  | General Structure                                                                 | 88 |

|   |     | 5.5.2  | Identifying Kernels                                                               | 89 |

|   |     | 5.5.3  | Functions and Variables                                                           | 90 |

|   |     | 5.5.4  | The Main Function                                                                 | 91 |

|   |     | 5.5.5  | The Relationship among Variables                                                  | 91 |

|   |     | 5.5.6  | Summarizing the Scheduling                                                        | 91 |

|   | 5.6 | Code   | $Generation (9)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 92 |

|     |     | 5.6.1 Creating the makefile and header files    | 93  |

|-----|-----|-------------------------------------------------|-----|

|     |     | 5.6.2 Creating OpenCL Kernels Files             | 93  |

|     |     | 5.6.3 Creating C/C++ Files                      | 95  |

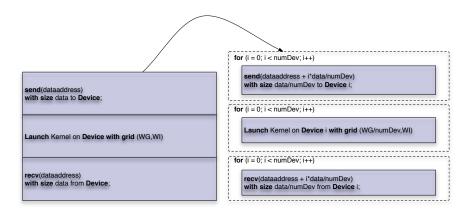

|     |     | 5.6.4 Extending the number of available devices | 97  |

|     | 5.7 | Conclusion                                      | 99  |

| 6   | ОРТ | TIMIZATIONS                                     | 101 |

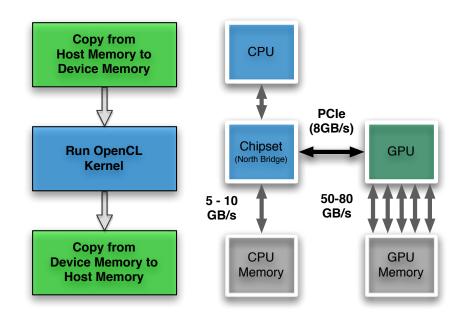

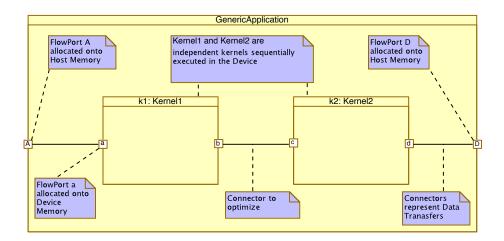

|     | 6.1 | Memory Copies                                   | 102 |

|     |     | 6.1.1 Avoiding Unnecesary Transfers             | 104 |

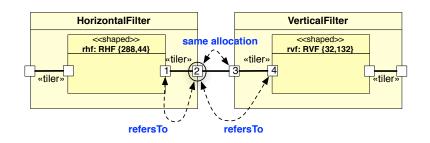

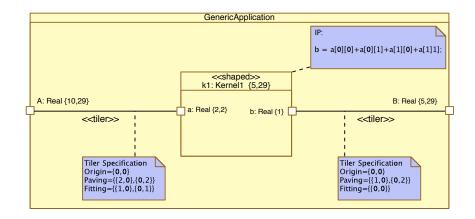

|     | 6.2 | Tiler Analysis                                  | 104 |

|     |     | 6.2.1 Observing data reuse                      | 104 |

|     |     | 6.2.2 Detecting data reuse                      | 105 |

|     |     | 6.2.3 Deciding which data to transfer           | 106 |

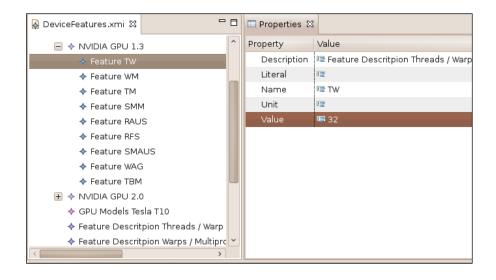

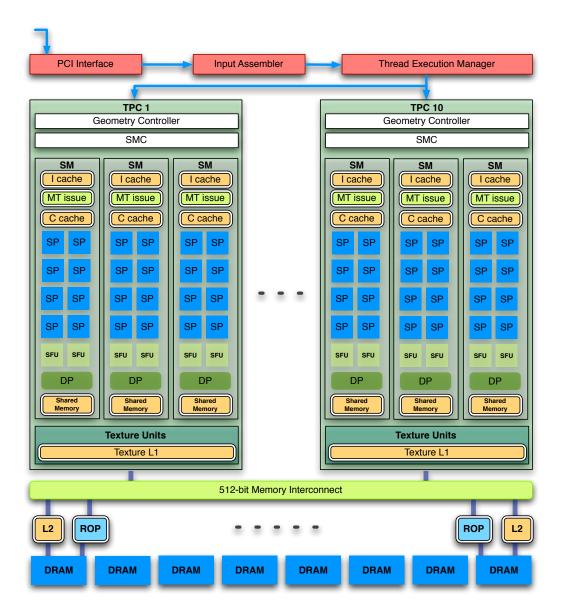

|     | 6.3 | Profiling Analysis                              | 107 |

|     |     | 6.3.1 Managing The Whole Chain Traceability and |     |

|     |     | Avoiding Model-to-Text Traceability             | 109 |

|     |     | 6.3.2 From Execution to Smart Advices           | 110 |

|     |     | 6.3.3 Backtracking Advices in the Input Models  | 112 |

|     |     | 6.3.4 Example and Benchmarks                    | 112 |

|     | 6.4 | Conclusion                                      | 121 |

|     |     |                                                 |     |

| III | SIM | IULATION OF ELECTRICAL SYSTEMS                  | 123 |

| 7   | ELE | CTROMAGNETIC PHENOMENON AND CODE_CARMEL         | 125 |

|     | 7.1 | Laws of Electromagnetism                        | 126 |

|     |     | 7.1.1 Continuous-time Maxwell's Equations       | 126 |

|     | 7.2 | Discretization: FEM                             | 129 |

|     |     | 7.2.1 Method                                    | 130 |

|     |     | 7.2.2 Assembly and Solvers                      | 130 |

|     | 7.3 | The Code_CARMEL                                 | 131 |

|     |     | 7.3.1 Introduction to CODE_CARMEL               | 131 |

|     |     | 7.3.2 Formulations                              | 131 |

|     |     | 7.3.3 Running CODE_CARMEL in Parallel           | 132 |

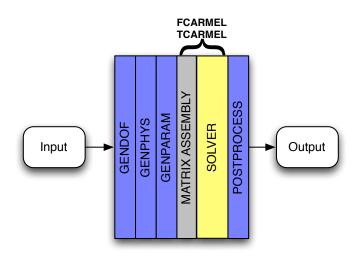

|     |     | 7.3.4 Global Structure                          | 133 |

|     | 7.4 | Conclusion                                      | 135 |

| 8   |     | NJUGATE GRADIENT SOLVER                         | 137 |

|     | 8.1 | Introduction to Conjugate Gradient              | 138 |

|     |     | 8.1.1 Sparse Matrix                             | 138 |

|     | 8.2 | Case Study                                      | 139 |

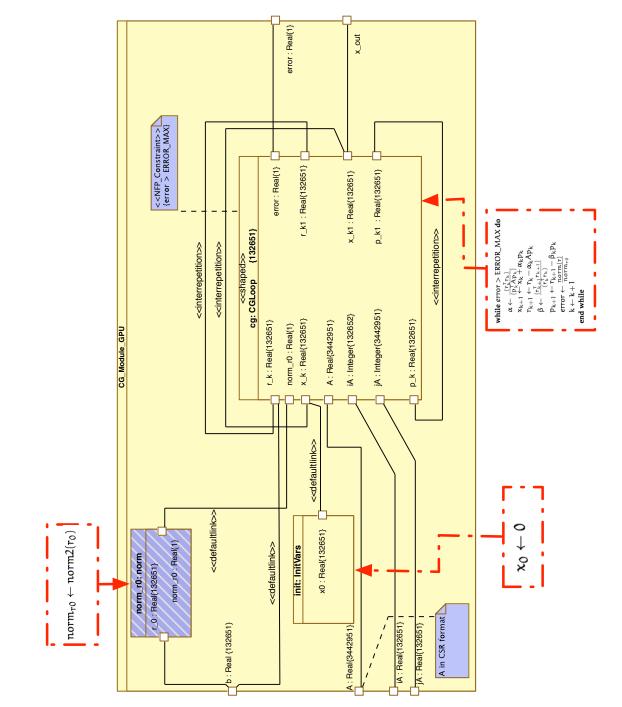

|     |     | 8.2.1 High-Level Specification                  | 139 |

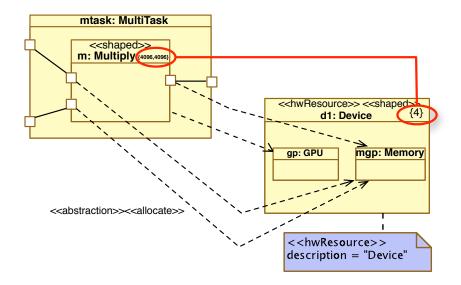

|     |     | 8.2.2 Expressing the Device Multiplicity        | 144 |

|     |     | 8.2.3 Generated Code                            | 146 |

|     |     | 8.2.4 Tests                                     | 146 |

|     |     | 8.2.5 Results                                   | 147 |

|     |     | 8.2.6 Automotive Alternator Example             | 157 |

|     | _   | 8.2.7 Overall Comparisons                       | 158 |

|     | 8.3 | Conclusion                                      | 159 |

|     |     |                                                 |     |

Conclusion and Perspectives

| IV | APP   | ENDIX                                                                         | 167 |

|----|-------|-------------------------------------------------------------------------------|-----|

| Α  | HIG   | H PERFORMANCE COMPUTING                                                       | 169 |

|    | A.1   | History                                                                       | 169 |

|    | A.2   | Existing Approaches                                                           | 170 |

|    |       | A.2.1 Architecture                                                            | 171 |

|    |       | A.2.2 Parallel Programming                                                    | 173 |

|    | A.3   | Massively Parallel Processing (MPP)                                           | 176 |

|    | A.4   | General-Purpose computing on Graphics Processing                              |     |

|    |       | Unit (GPGPU)                                                                  | 177 |

|    |       | A.4.1 Architecture of a Modern GPU                                            | 177 |

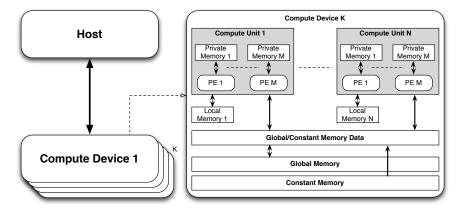

|    |       | A.4.2 OpenCL <sup><math>TM</math></sup> as Programming Model for MPP $\ldots$ | 180 |

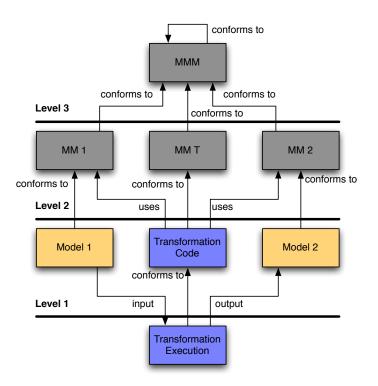

| В  | моі   | DEL-DRIVEN ENGINEERING                                                        | 187 |

|    | B.1   | Models and Metamodels                                                         | 187 |

|    |       | B.1.1 Abstraction and Refinement of Models                                    | 188 |

|    | B.2   | UML and Profiles                                                              | 188 |

|    |       | B.2.1 Introduction to MARTE                                                   | 191 |

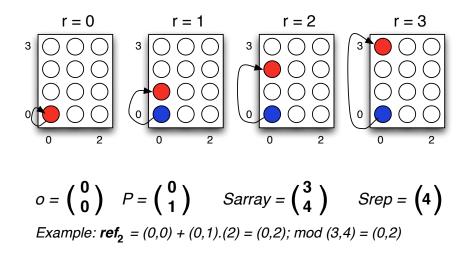

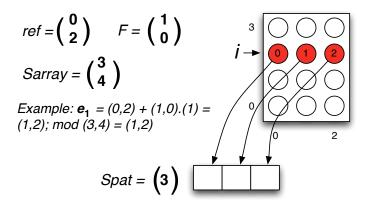

|    |       | B.2.2 RSM Package and Array Oriented Language                                 |     |

|    |       | (ArrayOL)                                                                     | 193 |

|    | в.3   | Model Transformation                                                          | 197 |

|    |       | B.3.1 Model Refactoring                                                       | 199 |

|    |       | B.3.2 Model Merge                                                             | 199 |

|    |       | B.3.3 M2M QVT Operational Mapping Language                                    | 199 |

|    | в.4   | Code Generation                                                               | 200 |

| BI | BLIOG | GRAPHY                                                                        | 203 |

# LIST OF FIGURES

| Figure 0.1  | Performance gap between GPU and CPU              | 4  |

|-------------|--------------------------------------------------|----|

| Figure 0.2  | Scope of Work                                    | 6  |

| Figure 1.1  | Architecture of the plug-in Archi-MDE            | 19 |

| Figure 1.2  | Designing Models on Simulink                     | 20 |

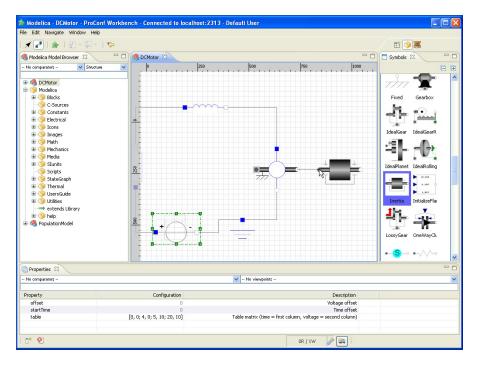

| Figure 1.3  | Modeling a DC Motor in OpenModelica IDE          | 21 |

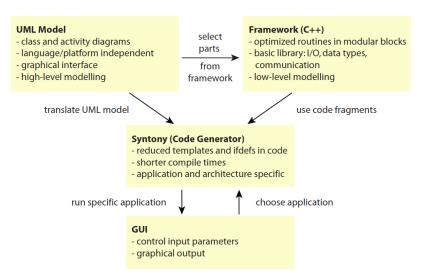

| Figure 1.4  | Syntony Process                                  | 22 |

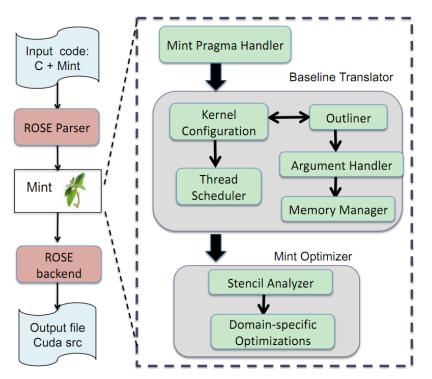

| Figure 1.5  | Mint: C-to-CUDA Translation                      | 24 |

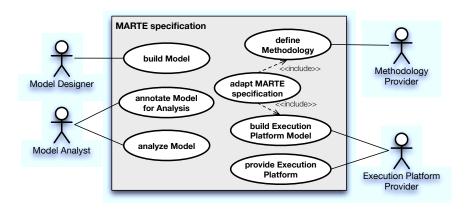

| Figure 2.1  | MARTE Use Case                                   | 35 |

| Figure 2.2  | GASPARD2 Extensions for MARTE                    | 37 |

| Figure 2.3  | Gaspard2 Library of Functionalities and Chain-   |    |

|             | ing Process                                      | 38 |

| Figure 2.4  | An example of refactoring                        | 41 |

| Figure 2.5  | Global Tracce: Traceability Approach on Gaspard2 | 43 |

| Figure 3.1  | Model Creation Process : Global View             | 48 |

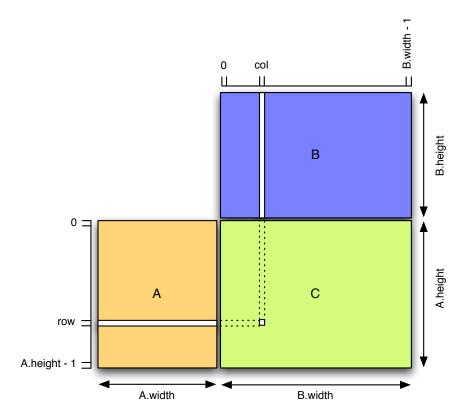

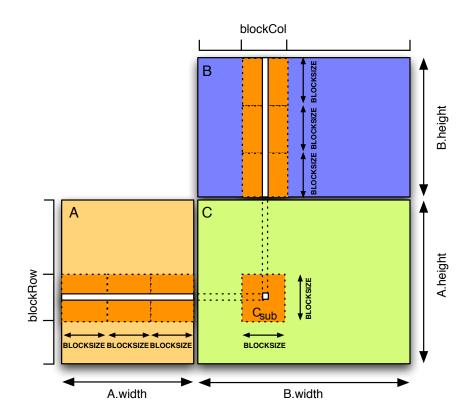

| Figure 3.2  | Matrix Multipliation without Shared Memory .     | 49 |

| Figure 3.3  | Matrix Multiplication with Shared Memory         | 50 |

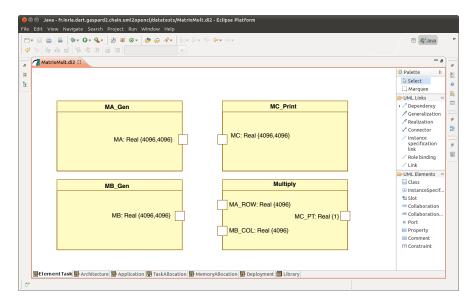

| Figure 3.4  | Elementary Tasks in the Eclipse Environment      |    |

|             | with Papyrus Modeling Tool                       | 52 |

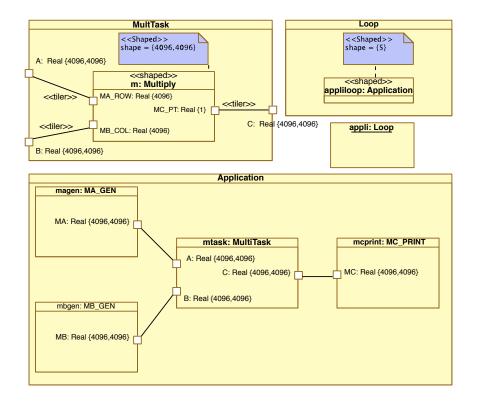

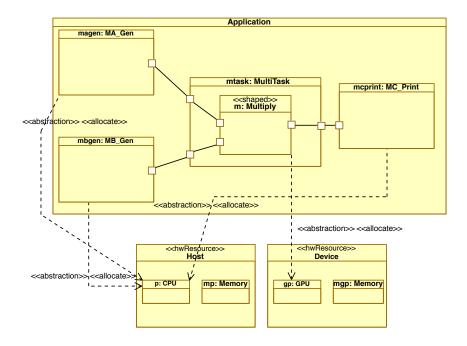

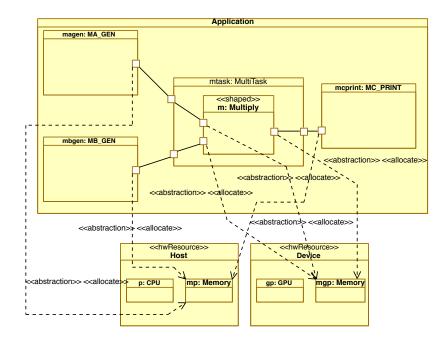

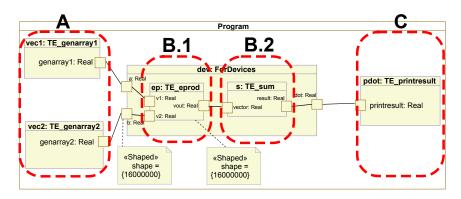

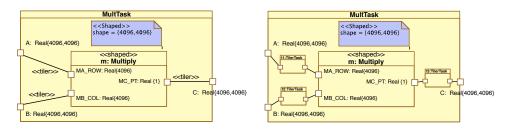

| Figure 3.5  | Application Model for Matrix Multiplication      | 53 |

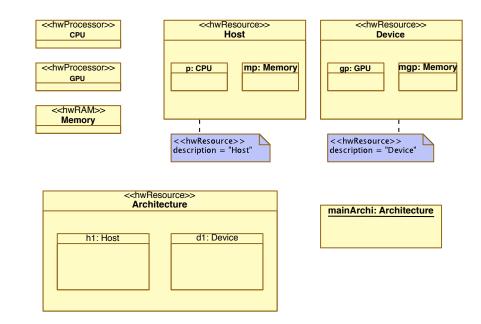

| Figure 3.6  | Architecture Model                               | 54 |

| Figure 3.7  | Task Allocation                                  | 55 |

| Figure 3.8  | Data Allocation                                  | 56 |

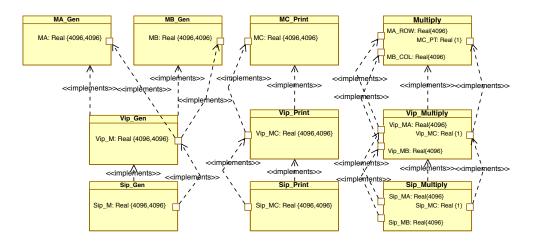

| Figure 3.9  | Deployment Phase: Virtual IP and Software IP .   | 56 |

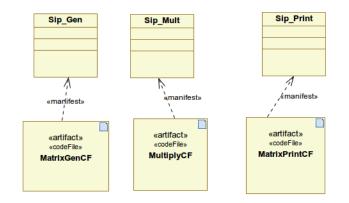

| Figure 3.10 | Deployment Phase: Artifacts Manifestation        | 57 |

| Figure 3.11 | Results for Matrix Multiplication Example        | 57 |

| Figure 3.12 | Blocked Version Model                            | 58 |

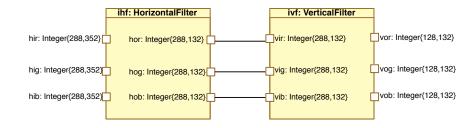

| Figure 3.13 | Horizontal and Vertical Filter Processes         | 59 |

| Figure 3.14 | Elementary Tasks for the Downscaler              | 60 |

| Figure 3.15 | Overall Downscaler Application                   | 61 |

| Figure 3.16 | Detail of Horizontal and Vertical Filters        | 61 |

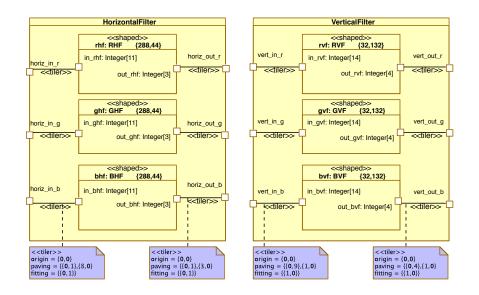

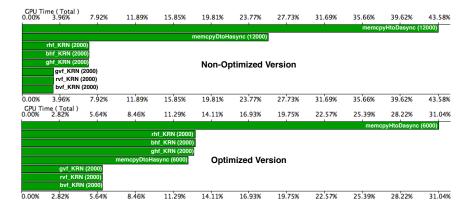

| Figure 3.17 | Profiling results for Downscaler Application     | 62 |

| Figure 3.18 | SAC versus Gaspard2 Comparison                   | 64 |

| Figure 4.1  | Tasks and Allocation                             | 70 |

| Figure 4.2  | General form of task graph representation        | 70 |

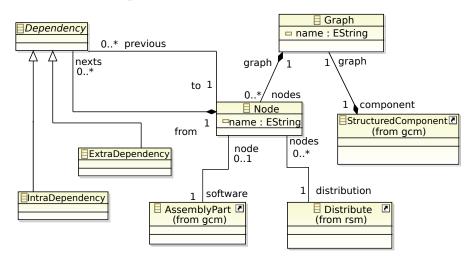

| Figure 4.3  | Local Task Graph Metamodel                       | 71 |

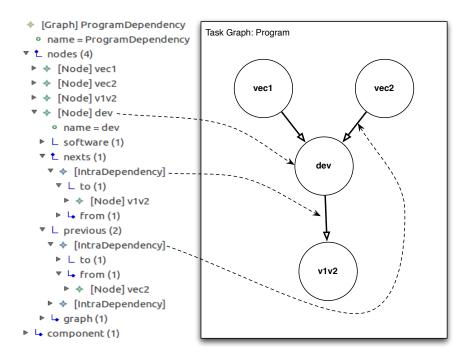

| Figure 4.4  | XMI Model Sample for Local Graph                 | 72 |

| Figure 4.5  | Global Task Graph Metamodel                      | 73 |

| Figure 4.6  | XMI Model Sample for Global Graph                | 73 |

| Figure 4.7  | Scheduling Metamodel                             | 74 |

| Figure 4.8  | Memory Mapping Metamodel                         | 75 |

| Figure 4.9  | XMI Model Sample for Memory Mapping              | 75 |

| Figure 4.10 | Hybrid Metamodel                                   | 78  |

|-------------|----------------------------------------------------|-----|

| Figure 4.11 | XMI Model Sample for Hybrid Application            | 79  |

| Figure 5.1  | Gaspard2 Library of Functionalities and Chain-     |     |

| 0 0         | ing Process                                        | 82  |

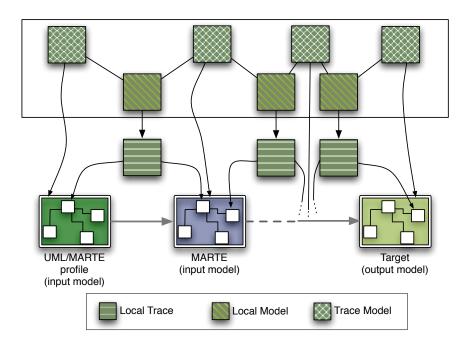

| Figure 5.2  | Model Transformation Scheme used in Gaspard2       | 83  |

| Figure 5.3  | The UML/MARTE-to-OpenCL Transformation             | 5   |

| 0 00        | Chain                                              | 84  |

| Figure 5.4  | Instances Identification Metamodel                 | 86  |

| Figure 5.5  | Transforming Tiler Connectors to Tiler Tasks       | 86  |

| Figure 5.6  | Memory Mapping Transformation                      | 88  |

| Figure 5.7  | Hybrid Conception Transformation                   | 89  |

| Figure 5.8  | Distinct task allocation onto available processors | 90  |

| Figure 5.9  | Scheduling lists and their interconnections        | 92  |

| Figure 5.10 | Samples of IP and header files for the matrix      |     |

| 0           | multiplication application                         | 94  |

| Figure 5.11 | Grid Example                                       | 96  |

| Figure 5.12 | References for Memory Transfers                    | 96  |

| Figure 5.13 | Multi-GPU Example                                  | 98  |

| Figure 5.14 | Multi-GPU Task Distribution Process                | 99  |

| Figure 6.1  | Typical Approach with Memory Copy                  | 102 |

| Figure 6.2  | Generic Application to illustrate Memory Trans-    |     |

| -           | fers Suppression                                   | 103 |

| Figure 6.3  | Generic Application for Local Memory Opti-         |     |

|             | mization                                           | 105 |

| Figure 6.4  | Input and Output Arrays and Patterns for Work-     |     |

|             | Group o                                            | 107 |

| Figure 6.5  | Different Polygons depending on Work-Groups        | 108 |

| Figure 6.6  | Performance and Profiling Integration Overview     | 109 |

| Figure 6.7  | Profiling Metamodel                                | 110 |

| Figure 6.8  | GPU Device Features Metamodel                      | 111 |

| Figure 6.9  | Vector Product Application Model                   | 114 |

| Figure 6.10 | Task and Memory Allocations onto GPU               | 114 |

| Figure 6.11 | GPU Device Features Database Model                 | 118 |

| Figure 6.12 | Sample profiling results in CSV format             | 118 |

| Figure 6.13 | Profiling Results Model                            | 119 |

| Figure 6.14 | Annotated Model                                    | 120 |

| Figure 6.15 | Occupancy by Varying Block Size                    | 120 |

| Figure 6.16 | Comparison Summary Plot from Visual Profiler       | 121 |

| Figure 7.1  | Continuous problem domain ΩxT. Source: Eu-         |     |

|             | ler's Thesis [53]                                  | 127 |

| Figure 7.2  | Electromagnetism Division                          | 128 |

| Figure 7.3  | An Element in a Triangular Mesh                    | 130 |

| Figure 7.4  | code_CARMEL3D Use Case                             | 134 |

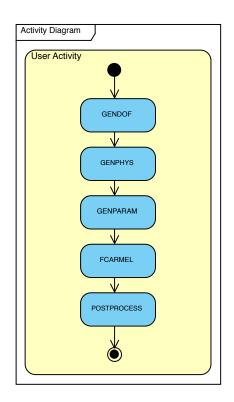

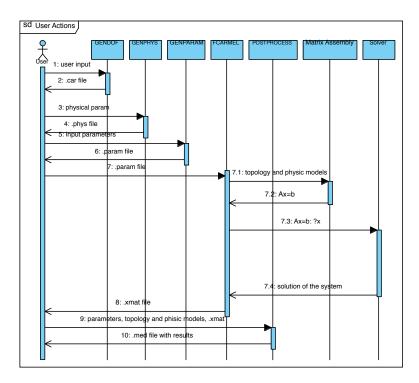

| Figure 7.5  | code_CARMEL3D Activity Diagram                     | 134 |

| Figure 7.6  | code_CARMEL3D Sequence Diagram                     | 135 |

| Figure 8.1  | Usual Modules of Code_CARMEL                       | 140 |

| Figure 8.2  | Conjugate Gradient Global View                            | 141 |

|-------------|-----------------------------------------------------------|-----|

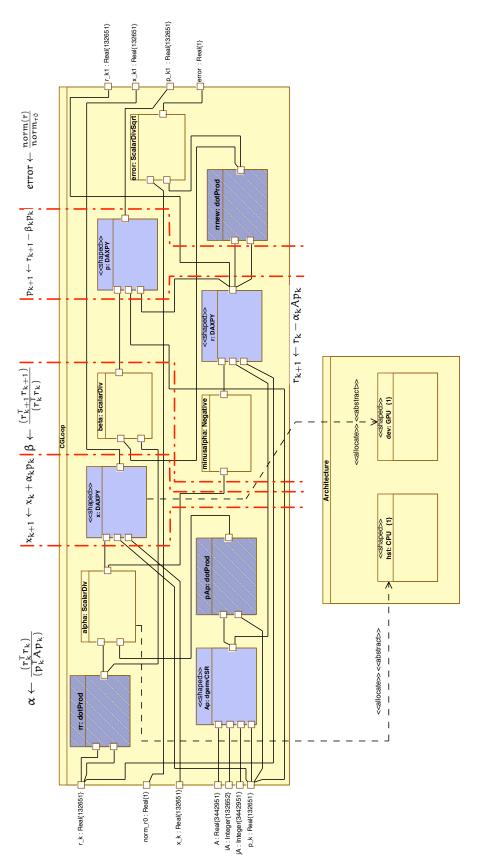

| Figure 8.3  | Hybrid Metamodel                                          | 143 |

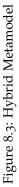

| Figure 8.4  | Dot Product Task                                          | 144 |

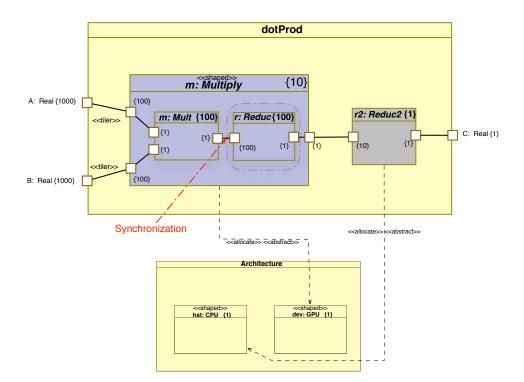

| Figure 8.5  | Sparse Matrix in ELLPACK-R Format                         | 145 |

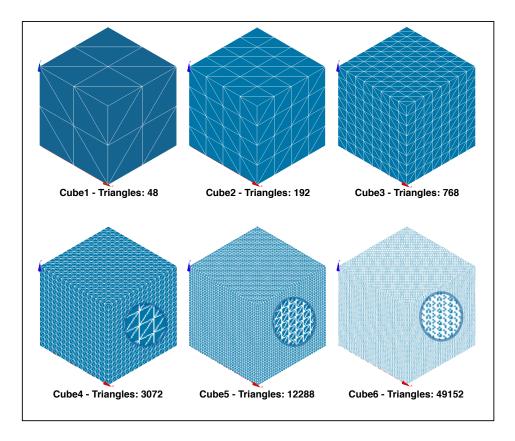

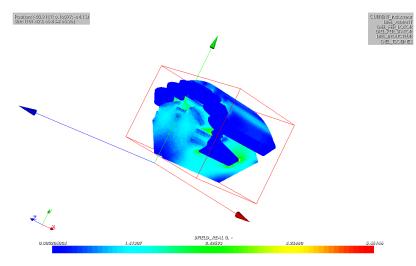

| Figure 8.6  | Mesh Models used in the Simulation                        | 148 |

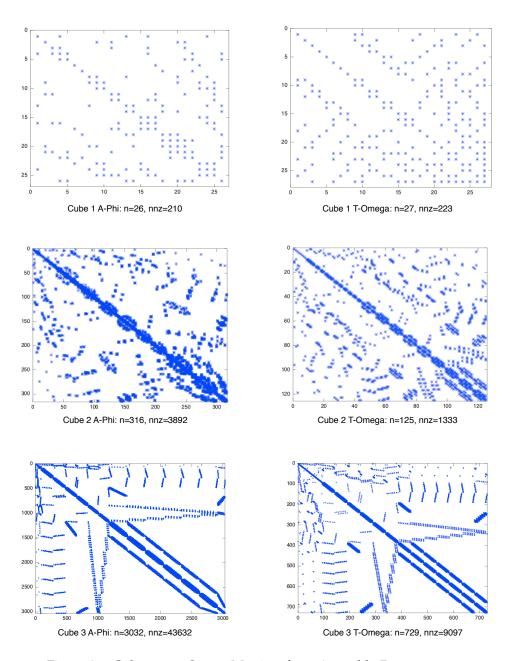

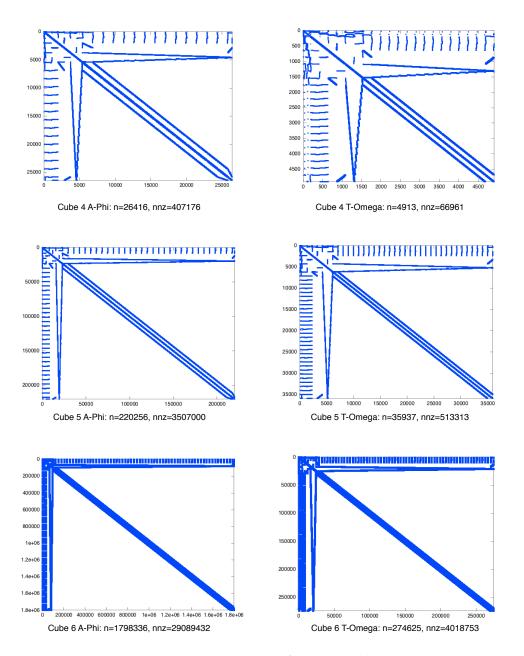

| Figure 8.7  | Cube 1 to 3: Sparse Matrices from Assembly                |     |

|             | Process                                                   | 149 |

| Figure 8.8  | Cube 4 to 6: Sparse Matrices from Assembly                |     |

|             | Process                                                   | 150 |

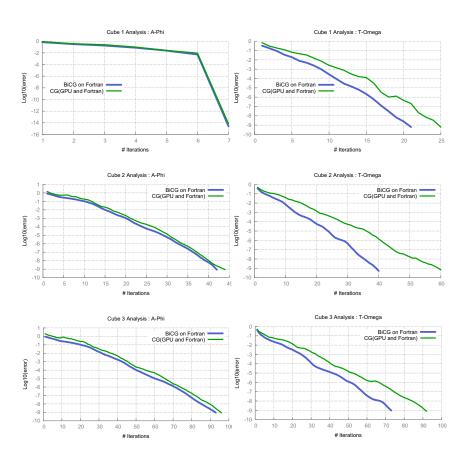

| Figure 8.9  | Convergence Charts for Cube 1 to 3                        | 151 |

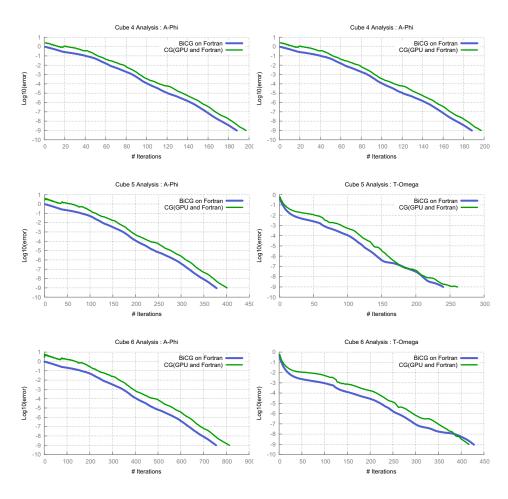

| Figure 8.10 | Convergence Charts for Cubes 4 to 6                       | 152 |

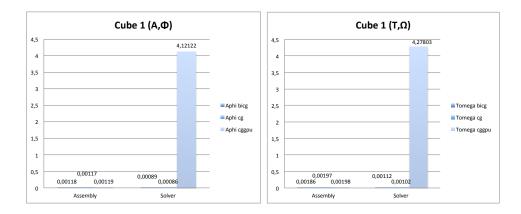

| Figure 8.11 | Results for Cube 1                                        | 153 |

| Figure 8.12 | Results for Cubes 2 and 3                                 | 154 |

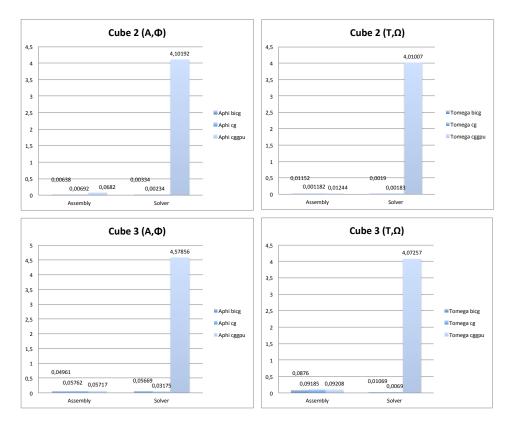

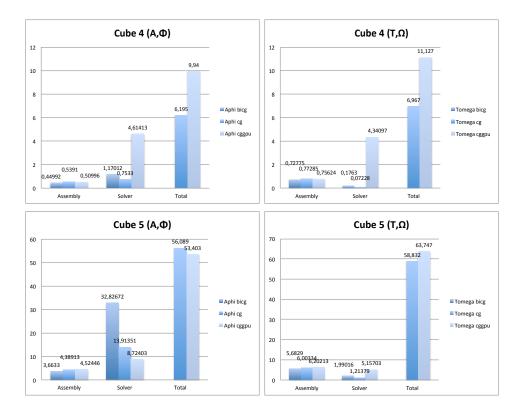

| Figure 8.13 | Results for Cubes 4 and 5                                 | 155 |

| Figure 8.14 | Results for Cubes 6                                       | 155 |

| Figure 8.15 | Speedup Evolution according to Problem Size .             | 156 |

| Figure 8.16 | Cube Post-processing                                      | 157 |

| Figure 8.17 | Automotive Alternator from Valeo <sup>TM</sup> $\ldots$ . | 157 |

| Figure 8.18 | Alternator Post-processing                                | 158 |

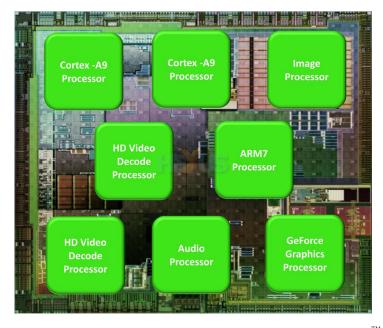

| Figure A.1  | NVIDIA's Tegra 2 Architecture                             | 174 |

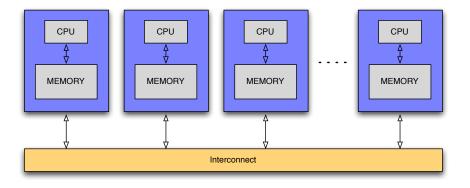

| Figure A.2  | Nodes in a Distributed Memory System                      | 176 |

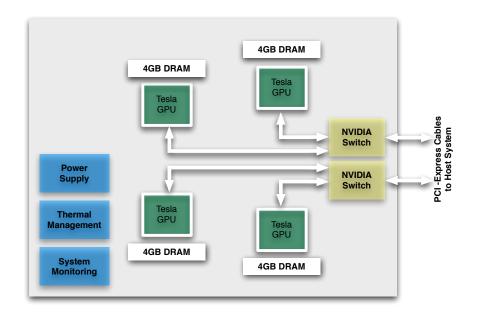

| Figure A.3  | Tesla S1070 Card Architecture Overview                    | 178 |

| Figure A.4  | T10 GPU Architecture                                      | 179 |

| Figure A.5  | OpenCL Platform and Memory Model                          | 180 |

| Figure A.6  | OpenCL UML Class Diagram                                  | 181 |

| Figure A.7  | OpenCL 3D Kernel of size Gx Gy                            | 182 |

| Figure B.1  | System, Model, and Metamodel Relationships .              | 189 |

| Figure B.2  | MARTE Use-Case                                            | 192 |

| Figure B.3  | MARTE Architecture                                        | 192 |

| Figure B.4  | RSM Package Overview                                      | 193 |

| Figure B.5  | ArrayOL and Downscaler                                    | 195 |

| Figure B.6  | Paving Example in ArrayOL                                 | 196 |

| Figure B.7  | Pattern Distribution in ArrayOL                           | 197 |

| Figure B.8  | Model Transformation Pattern                              | 198 |

|             |                                                           |     |

# LIST OF TABLES

| Table 1.1 | Approaches Comparison                            | 32  |

|-----------|--------------------------------------------------|-----|

| Table 3.1 | Downscaler Results                               | 62  |

| Table 3.2 | Kernel execution and data transfer times of GAs- |     |

|           | PARD2 implementation                             | 63  |

| Table 3.3 | Kernel execution and data transfer times of SAC  |     |

|           | implementation                                   | 63  |

| Table 6.1 | Profiling results for the non-optimized code     | 119 |

| Table 6.2 | Profiling results for the new code               | 121 |

| Table 8.1 | Generated Files for the CG                       | 146 |

| Table 8.2 | Cube 1 and 6: GPU Times Analysis                 | 156 |

| Table 8.3 | Multi-GPU: N=132,651, NNZ=3,442,951, tol=1e-     |     |

|           | 10. <i>Source:</i> [41]                          | 157 |

| Table A.1 | Memory and Access Policy                         | 183 |

| Table B.1 | Modeling Languages Architecture according to     |     |

|           | MDA                                              | 188 |

### LISTINGS

| Listing 1.1 | OpenHMPP example 1                              | 25  |

|-------------|-------------------------------------------------|-----|

| Listing 1.2 | OpenHMPP example 2                              | 26  |

| Listing 1.3 | JOCL example                                    | 26  |

| Listing 1.4 | Matlab GPU example                              | 27  |

| Listing 1.5 | PyOpenCL example                                | 28  |

| Listing 1.6 | Example CUDA-WITH-loop with data transfers      |     |

|             | inserted                                        | 29  |

| Listing 1.7 | Translating example CUDA-WITH-loop to ker-      |     |

|             | nel function                                    | 29  |

| Listing 3.1 | Usual Matrix Multiplication Program             | 49  |

| Listing 3.2 | Block Matrix Multiplication Program             | 50  |

| Listing 5.1 | QVTO snippet from UML to MARTE Metamodel        |     |

|             | Transformation                                  | 85  |

| Listing 5.2 | launchtopology computation                      | 91  |

| Listing 5.3 | launchtopology computation directly from task's |     |

|             | shape                                           | 92  |

| Listing 5.4 | CL Code Template                                | 93  |

| Listing 5.5 | CL Code Template                                | 94  |

| Listing 5.6 | Launch Topology to Grid definition              | 95  |

| Listing 5.7 | Memory Transfers                                | 96  |

| Listing 5.8 | Setting Kernel Arguments                        | 97  |

| Listing 6.1 | clCreateBuffer() function call example 1        | 103 |

| Listing 6.2 | Code Sample for Vector Product                  | 113 |

| Listing 6.3 | Generated Kernel for Vector Product             | 115 |

| Listing B.1 | Launchtopology Computation directly from Task's |     |

|             | Shape                                           | 200 |

# ACRONYMS

| ATL         | Atlas Transformation Language                                       |

|-------------|---------------------------------------------------------------------|

| ArrayOL     | Array Oriented Language                                             |

| BiCGCR      | BiConjugate Gradient Conjugate Residual                             |

| Code_CARMEL | Code Avancé de Recherche pour les Machines<br>Électriques           |

| CG          | Conjugate Gradient                                                  |

| CPU         | Central Processing Unit                                             |

| CSR         | Compressed Sparse Row                                               |

| DAG         | Directed Acyclic Graph                                              |

| DSL         | Domain-Specific Language                                            |

| EDF         | Électricité de France                                               |

| EMF         | Eclipse Modeling Framework                                          |

| FEM         | Finite Element Method                                               |

| FFT         | Fast Fourier Transform                                              |

| Gaspard2    | Graphical Array Specification for Parallel and Distribute Computing |

| GPGPU       | General-Purpose computation on Graphics<br>Processing Unit          |

| GPU         | Graphics Processor Unit                                             |

| HD-CIF      | High Definition Common Intermediate Format                          |

| HPC         | High Performance Computing                                          |

| HPF         | High Performance Fortran                                            |

| HRM         | Hardware Resources Modeling                                         |

| IP          | Intellectual Property                                               |

| L2EP        | Laboratory of Electrical and Power Electronics of Lille             |

| M2M         | Model-to-Model Transformation                                       |

| M2T         | Model-to-Text Transformation                                        |

| MARTE       | Modeling and Analysis of Real-Time and Embedded Systems             |

| MDA         | Model-Driven Architecture                                           |

| MDE         | Model-Driven Engineering                                            |

| MIMD        | Multiple Instruction, Multiple Data                                 |

| MoC         | Model of Computation                                                |

|             |                                                                     |

| MOF    | MetaObject Facility                                  |

|--------|------------------------------------------------------|

| MPI    | Message Parsing Interface                            |

| MPP    | Massively Parallel Processing                        |

| MUMPS  | MUltifrontal Massively Parallel sparse direct Solver |

| PDE    | Partial Differential Equations                       |

| OCL    | Object Constraint Language                           |

| OMG    | Object Management Group                              |

| OML    | Operational Mapping Language                         |

| OpenCL | Open Computing Language                              |

| OpenMP | Open Multi-Processing                                |

| QVT    | Query/View/Transformation                            |

| QVTO   | Query/View/Transformation Operational                |

| RSM    | Repetitive Structure Modeling                        |

| SMP    | Symmetric Multi-Processing                           |

| SIMD   | Single Instruction, Multiple Data                    |

| SPMD   | Single Program, Multiple Data                        |

| UML    | Unified Modeling Language                            |

| XMI    | XML Metadata Interchange                             |

### INTRODUCTION

#### CONTEXT

In the recent decades, numerical simulation has become a valuable and successful method for solving complex problems in almost all areas of physics and human sciences. Indeed, numerical simulations are a useful part of mathematical modeling of many natural systems in physics, astrophysics, economics, psychology, social science, biochemistry, and engineering.

Numerical simulation is fundamental to engineering advances specially in the electromagnetic fields. The application range extends from low frequency industrial applications up to ultra-high frequency applications. However, there are many problems that simply do not have analytical solutions, and there are those whose exact solution is beyond the current state of knowledge. Indeed, for many of these real-world electromagnetic problems like scattering, radiation, wave guiding, there is no analytical computable solution due to the complexity and multitude of irregular geometries found in actual devices. Most of these problems can not be solved manually. Therefore, developers have implemented a number of advanced numerical algorithms specifically designed for those applications. For example, numerical simulation techniques can overcome the inability to derive closed form solutions of Maxwell's equations under various constitutive relations of media, and boundary conditions.

Throughout the years, software developers have worked on the transformation of numerical algorithms into useable programs. There are several options available to developers, both in terms of language and overall approach. Often, the programming solution of numerical simulations can become as intricate and involved as the original problems and requires almost as much refinement and care to obtain a solution. This usually requires a twofold skill from developers (or developing team): knowledge of the problem's domain and the programming language. The former belongs to physicists that have an in-depth knowledge of physical phenomena and thus are able to propose suitable solutions according to the problem, e.g. mathematical interpretation of physical phenomena. The latter lies in programming languages and execution platforms, where developers are able to exploit the architecture computing power aiming high performances. In order to promote the rapid development, many numerical libraries have emerged in different programming languages, such as Fortran, Java, C/C++ [122, 103, 86]. Most of these libraries relate to linear algebra where classical functions are often used in the implementa-

#### 2 INTRODUCTION

tion of numerical algorithms. Moreover, there are dedicated software packages that increase developing productivity for mathematical algorithms. Packages such as Matlab [99] and Scilab [30] integrate computation, visualization, and programming in an easy-to-use environment where problems and solutions are expressed in familiar mathematical notation.

In numerical simulations, scientific computing programs often produce a large amount of simulation data. Consequently, this requires more computing power than provided by sequential computers. Otherwise, many of these programs can take very long time to solve a problem. Current hardware architectures offering high performance do not only exploit parallelism within a single processor via multiple CPU cores but also apply a medium to large number of processors concurrently to a single computation. However, switching from sequential approaches to parallel approaches has been a recurring issue in programming paradigm. Traditional *de facto* standards, such as Message Parsing Interface (MPI) [56] and Open Multi-Processing (OpenMP) [121], are often used as parallel approaches to implement high performance applications. Nevertheless, new parallel architectures are often proposed. Consequently, new programming models for those architectures will require new skills from developers.

#### ISSUES AND MOTIVATIONS

Within the context described above, we take into account some concerns related to parallel programming, emerging parallel technologies and high-level specification of numerical simulation algorithms. Under these three aspects, we emphasize the challenges still to be faced, and that we consider necessary for scientific and industrial community.

### Parallel Programming Paradigm

In modern execution platforms, parallelism appears at various levels both in hardware and software: signal, circuit, component, and system levels. For instance, at a higher level, SMP systems have multiple CPUs that work in parallel. At an even higher level of parallelism, one can connect several computers together and make them work as a single machine, popularly known as cluster computing. Nevertheless, the main challenge to developers is deciding the lumps of code, i. e., the code granularity, that can be a potential candidate for parallelism. Several solutions to granularity decision process have already been proposed, such as those in [33, 67]. However, these solutions deal with idealized systems and most of the overhead parameters, e. g. communication, are ignored. Thus, we do not consider it optimal to

An overview on HPC systems and clusters is provided in Appendix A. automatically define the code granularity. Hence, developers must undertake this process.

Matson et al. [101] identify the top 10 issues concerning parallel programming. Among these issues, we considered some major ones as essential such as:

- ④ Supporting scalability, hardware: bandwidth and latencies to memory plus interconnects between processors to help applications scale. Although a software development methodology does not allow changing the hardware architecture, it is possible to take advantage of the available resources according to applications.

- (5) Supporting scalability, software: libraries, scalable algorithms, and adaptive runtimes to map high-level software onto platform details.

- Tools, API's and methodologies to support the debugging process.

For instance, mechanisms for optimization and fine-tuning of parallel applications.

- *Support for good software engineering practices: composability, incremental parallelism, and code reuse.* Furthermore, support for a compact expression of parallelism at higher levels.

- Support for portable performance. What are the right models (or abstractions) so programmers can write code once and expect it to execute well on the important parallel platforms?

All these issues are challenges in parallel programming. Researchers have constantly proposed solutions to bridge existing gaps.

#### Massively Parallel Architectures

Massively parallel architectures are computing systems that consist of many individual nodes. The term *massive* is wide and connotes hundreds if not thousands of such units. However, growth in this area has been driven by the development of graphics cards with massively parallel processors, resulting in commodity hardware that is widely available, scalable and cost-effective. The adoption of generalpurpose hardware for graphics applications has opened the door for non-graphics applications to use the potential of the graphics card (or GPUs). Graphics Processor Unit (GPU)s, from this point, is our aimed platform. They have led the *many-core* performances since 2003. Particularly, we focus on the OpenCL programming and execution models. In OpenCL, there is a host system that manages one or more devices. In order to define our architecture scope, a host system is performed by a mono-processor CPU, as well as devices are performed by up to 4 GPUs that each one contains about two or three hundred processor elements.

In summary, the two main benefits of GPUs are the following:

#### 1. Computing Performance versus Price

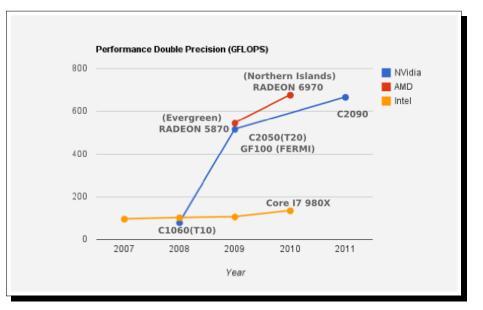

Figure 0.1 shows the performance comparison between modern GPUs and Central Processing Units (CPUs). The ratio for peak floatingpoint (double precision <sup>1</sup>) calculation throughput is about 8 to 1. This ratio is merely the raw speed that the execution resources can potentially support in both GPU and CPU chips. Moreover, the price is a key aspect to consider. GPUs are graphics cards and their cost is about a few hundred dollars <sup>2</sup> and they are found even in notebooks. Some cases report an average of between 10x and 100x speed increase using General-Purpose computation on Graphics Processing Unit (GPGPU) for the same computations, depending on the algorithms and the hardware used for comparison <sup>3</sup>.

Figure 0.1: Performance gap between GPU and CPU

### 2. Green Computing versus Price

By their nature GPU processor cores can be aggregated readily into very dense multicore applications. There are GPUs with 1,000 cores in a single processor package with very low power consumption factor, maximizing performance per watt (optimizing overall costs). This factor is more important when we deal with clusters. Thus, GPGPU aims to use the environment efficiently and effectively. This is called *Green Computing* [108].

Here, we emphasize rather double precision than single precision due to our main application domain. If we consider single precision calculation, the difference presented in the chart is fairly larger.

2. More expensive HPC cards based on GPU can reach a few thousand dollars.

3. http://developer. nvidia.com/ cuda-action-research-apps

#### Issues on GPGPU

According to [104] the adoption of GPGPU is driven by 7 issues. Some of these issues include:

- Lack of developer expertise. Even though GPGPU is based on existing programming languages, it requires a different model of programming concerning general purpose processors. Currently, developers are aiming to acquire necessary skills in order to adapt their programs to GPGPU.

- C/C++ being the dominant starting point for GPGPU programming.

Vendor's API is usually based on C/C++; however, bindings for other languages have largely been disseminated.

- *Half of those considering GPGPU expect a 10x increase in performance.* Many available benchmarks show speed-up of about 10x. This is an attractive result though not always true for all applications. On the other hand, some benchmarks show better performance.

- Debugging and designing parallel algorithms are the most difficult development task with GPGPU. Available tools have constraints to interact with GPU processors. Debugging programs at runtime is hard to implement. Moreover, depending on the developing tool, it is not simple to integrate the vendor's profilers and programming environment.

### High-Level Specification

There is a lack of high-level specification for GPGPU applications. However, the specification of parallel applications at higher levels is not recent. Indeed, in 1992, Jong et al. [32] proposed an approach that separates the algorithm specifications and the allocation of hardware resources to data and computations. In their approach, algorithms are formulated at an abstract level in a specification language having its own ideal virtual machine, thus preserving the parallelism inherent to the algorithm. Many others approaches appeared, and the high-level specification world has evolved. Today, there are several standards available to abstract specification of software depending on the application domain. Proprietary solutions as seen in Matlab Simulink® and Labview®, or standards as provided by Object Management Group (OMG) are alternatives to classical software specification based on hand written code. Therefore, the main issue, in this context, is to find the high-level specification solution that suits well to GPGPU developing. In summary, a solution that meets our objectives need to provide the means to specify an application, the expression of its parallelism, the platform architecture, and the link between logical and physical parts. Regarding the parallelism, an interesting aspect is conciseness. Thus, dozens as well as thousands of instances of a task must be expressed in a compact way with minimal complexity.

#### SCOPE AND CONTRIBUTIONS

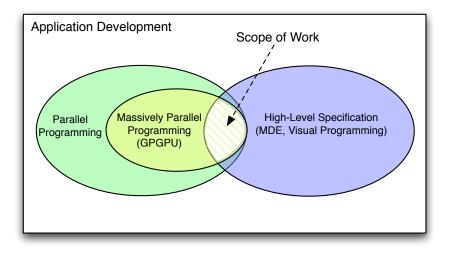

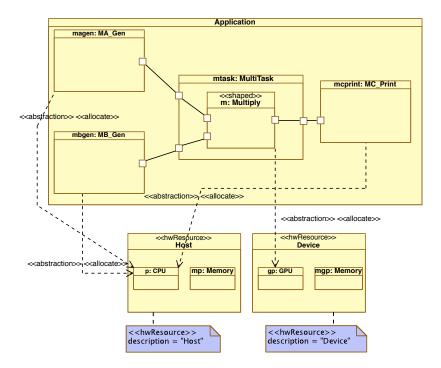

Although parallel programming has a wide application range, we focus the work on simulation of electrical machines. More specifically, we focus on all operations that depend on linear algebra. Most of these operations can run in parallel and suit well to many-core architectures. Indeed, vector and matrix operations are data independent and do not require synchronization instructions. In addition, similar tasks as seen in intensive signal processing applications are also met by the same development methodology. In summary, our scope of work lies in introducing high-level specification into GPGPU development as seen in Figure 0.2.

Figure 0.2: Scope of Work

Therefore, the contribution of this thesis addresses the following aspects:

### An MDE Methodology for GPGPU Architectures

How to specify the models of application and platform for our target software and hardware?

We have chosen Model-Driven Engineering (MDE) as overall solution to our methodology because it aims to increase the benefit of the software development. In summary, this benefit is delivered in two basic ways:

1. *short-term productivity*: using rapid prototyping as part of a planned iteration in establishing application requirements;

2. *long-term productivity*: growing software organically, adding more function to systems or modifying them as they are run, used, and tested and according to running platform.

#### Modeling

In the MDE context, we have found in the standard Unified Modeling Language (UML) and its profile Modeling and Analysis of Real-Time and Embedded Systems (MARTE) the elements that meet the earlier discussed concerns regarding high-level specification. MARTE is increasingly being used in academic and industrial tools to support hardware and software development. Among the features of UML and MARTE, the following ones are taken into account as reasons for our choice:

- Clear separation between hardware and software specifications. It enables the specialization of each component, providing a common way of modeling both hardware and software aspects of a whole system in order to improve communication between developers.

- *Existing tools and experienced developers for high-level modeling in UML*. It enables interoperability among development tools used for specification, design, verification, and code generation.

- *Parallel expressiveness available in MARTE*. With support to ARRAYOL, it is able to express in compact form the potential parallelism of tasks and data and parallel hardware architectures, enabling factorization of repeated elements.

#### Code Generation

Besides modeling, we define also the strategy to analyze a model specified with MARTE in order to produce a source code for the target platform. This process is not monolithic and is made by various layers, which take into account aspects previously designed.

### • Optimization

We aim a methodology that produces an efficient code. In GPGPU, different programming practices, we are able to achieve higher performances. These practices include explicit cache handling, and attain speedup of about 10x<sup>1</sup> with respect to non-optimized codes. Thus, we integrate within the code generation engine some resources aiming at generating efficient code.

#### Metamodel for Data Allocation and Distribution

How to specify the data allocation onto different memory address space?

We have to set a memory space and to define allocations for a host

<sup>1</sup> It is important to note that this is not always true. Usually, analysis by human obtains better results than automatic one.

### 8 INTRODUCTION

and different devices without neglecting their intercommunication. Moreover, we have to gather all data elements defined in the application model that share the same memory address. To organize those aspects, we define a specific metamodel for memory handling.

Metamodel for Hybrid Applications

How to clearly separate CPU and GPU roles in the whole application?

We propose this metamodel as being the last one in our hierarchy of metamodels. It sums up all previous analyses aiming at creating a model with components that match elements in a real program. More precisely, it takes into account the hybrid structure (host and device) found in GPGPU architecture.

### Model Transformations

How to transform higher level models to lower level models in order to attain the target code?

The core of our code generation approach lies mainly in the model transformations. We have defined several model transformations modules, which now, along with other ones, compose a complete chain of transformations for generating a functional and efficient code. These transformations analyse the model, and define or modify structures based on available metamodels that regard aspects such as data handling, scheduling, etc.

UML/MARTE-to-OpenCL Branch for Gaspard2

How to integrate the whole methodology into a single development environment?

Our methodology is inserted within a wider approach called GASPARD2. Indeed, we propose a new branch that allows transforming a model designed in UML/MARTE to a source code in OpenCL. The choice of OpenCL can be summarized in one reason: it is standard and independent of hardware vendor<sup>2</sup>.

Increasing Performance on Heavy Simulation Applications

What benefits are observed in the whole application?

Performance is our main goal. Along with hardware price and a low curve learning methodology to develop applications, we contribute

<sup>2</sup> CUDA is the programming model for NVidia's GPU. It is older and has a higher number of tools and case studies. However, it remains a proprietary solution and, at the moment, it cannot be used with other vendor's GPU. to a solution to accelerate numerical algorithms on heavy problems. Indeed, we show that is not interesting to apply GPGPU on lightweight problems, and the turning point can be seen on benchmark results.

Fast Adaptation of Applications on Multiple Devices

How scalable is the code generation?

Those who already developed applications on GPGPU know that raising scale on devices implies complex changes on code. This is more noticeable in OpenCL programming model. We propose task allocations onto mono or multi-devices. Therefore, the complexity of the overhead to attain the multi-GPU feature is undertaken by the model compiling process.

Optimization Techniques taking advantage of MPP and MDE

How efficient is the generated application?

At model compiling time, we are able to take into account aspects that can be optimized. At first, knowing the GPGPU architecture allows us checking bottlenecks in performance and providing changes to overcome them. Second, enabling the integration between running results (profiling) and high-level models allows us tuning our models aiming at better results. Even if an optimized code depends mainly on the algorithm and the way in which the designer has specified it, we give resources to optimize the code to designers.

Application of the Methodology on Simulation of Electrical Machines

How much impact is achieved on simulation of electrical machines?

The methodology hides details about programming GPGPU at low level. Therefore, we focus on designers that know well their algorithms and not necessarily the GPGPU programming model. Specifically for simulation of electrical machines, we provide a methodology that relies on replacing sequential implementation in existing simulation tools by parallel implementations. Also, replacing heavy computation modules by parallel solutions increases fairly performance and consequently decreases the time-to-market of the whole project.

# Comparing to the OpenMP branch of GASPARD2

There is a previous work developed within GASPARD2 that also aims to provide a methodology to develop high performance applications in order to improve numerical simulation applications. This work involves an OpenMP transformation chain and is part of the Julien Taillard's thesis [137]. We present an overview of his work in Chapter 1. However, in order to emphasize some concerns that make our work stands out, we describe them as follow:

- 1. **Programming Model:** We focus on the OpenCL programming model. OpenCL has wider application and target architectures than OpenMP. Therefore, it brings new issues not addressed by OpenMP. The main issues are related to the explicit handling of data transfers and the grid of threads. However, Taillard did not address this concern. Furthermore, to a certain extent, OpenCL is capable to meet the application field of OpenMP, expanding it to other architectures that may integrate, for instance, hardware accelerators.

- 2. High-level Specification: Taillard's work proposes the usage of a non-standard UML profile to specify applications and architecture. Even though most concepts from this profile are now part of the standard MARTE profile for UML, MARTE provides a larger number of stereotypes related to embedded system domain. It includes the previous concepts required by the Taillard's approach and many other concepts aiming other applications. Moreover, MARTE is increasingly present in modeling tools, and its community and applications ensure future support and maintainability.

- 3. **Transformation Chain:** Despite the fact that Taillard's transformation chain is not defined by standard languages for specification of transformations, it is not structured in layers. Indeed, his transformations keep a monolithic structure and do not involve well defined functionalities (e.g. scheduling). In our approach, we were able to identify his contributions in common fields, such as task graph and task distribution. From these contributions, we redefined the structure of transformations in layers and added all common functionalities. Then, in order to meet the requirements of a GPGPU approach, we had to add other essential functionalities. These functionalities address specially data handling, performance, and the hybrid aspect of OpenCL applications that defines roles of host and device.

The concerns discussed above justify the need to address the problem in a different way. This is not simply due to differences between aimed execution platforms. This is above all due to choices and specific goals defined for implementation of the proposal. As a result, we offer a better approach that takes into account its evolution and adaptability to future execution platforms.

#### OUTLINE

This dissertation is structured into four main portions.

# Part I: State of the Art

The first part deals with related works to code generation, high-level specification for parallel programming, and basic concepts related to the framework used as a basis for developing our methodology.

# • Chapter 1: High-Level Modeling and Code Generation on HPC

In this chapter, some important approaches in the state of the art on high-level modeling and code generation to High Performance Computing (HPC) systems are presented regarding the features relevant to our proposed approach.

#### • Chapter 2: Gaspard2 as Code Generation Framework

We have found in GASPARD2 framework important features which can benefit our proposal. Therefore, in this chapter, we present the design framework GASPARD2 as a solution to the development of high performance systems and which addresses MDE challenges.

# Part II: Methodology Approach

Initially, in this part, we present the methodology itself. Moreover, the remaining chapters deal directly with the technical details related to code generation from a designed model.

# • Chapter 3: Creating Applications

In this chapter, we seek to clarify our methodology to develop OpenCL applications from high-level models. Indeed, after presenting related works and GASPARD2 as framework for our approach, we analyze here two examples that use MARTE to specify them. Nevertheless, the examples are generic applications and aim only to describe how the methodology works.

#### • Chapter 4: Metamodels and GPU

In this chapter, we begin to explain technically the process behind the methodology. Basically, we point out principles of operation of GPUs, and then we present the main metamodels that statically provide a structure that supports these principles. We have proposed three novel metamodels. These metamodels focus on the different GPU features.

The chapter does not deal with all metamodels necessary to the whole code generation but only the proposed ones, and those related to GPU domain.

# • Chapter 5: Models towards Code

In this chapter, we present several model transformations modules which now, along with other ones, are part of that we call GASPARD2 Model Transformation Library. As an MDE approach, the new branch proposed for Gaspard2 comprehends all models, metamodels, transformation modules, and, foremost, how to determine the compiling process layers in order to achieve all necessary model element analysis. In this chapter, we present our model transformation chain and how it works regarding the metamodels previously depicted in the earlier chapter as well as metamodels introduced in this chapter.

• **Chapter 6: Optimizations** Even if our proposal is based on abstract models in a very high-level programming, in this chapter, we present some key points used to optimize the generated code. These points are strongly linked to the running platform, i. e., CPU, GPU under OpenCL programming. We emphasize basically two strategies to try to optimize the code: memory issues and profiling integration.

# Part III: Simulation of Electrical Systems

Our main goal is to allow creating high performance applications to simulate electrical systems. This part is composed of two chapters that present the simulation system CARMEL and a case study that replaces one of its modules (solver) with a GPGPU module.

#### • Chapter 7: Electromagnetic Phenomenon and CARMEL

This chapter present the scientific computation associated to the solution of electromagnetism problems that requires numerical methods in the discrete domain. So, in order to assure a better understanding of the decision taken in the case study, at first, we present part of the theory of the mathematical modeling of these problems in the continuous domain. Then, we introduce the Finite Element Method (FEM) as numerical method to solve these problems. Having this basic theory, we present the CODE\_CARMEL, a software that implements numerical methods for simulation of electrical machines.

# • Chapter 8: Conjugate Gradient Solver

In this chapter, we present the direct application of the methodology to the parallelism of a solver in the context of Code\_CARMEL. The objectives can be summarized into two main aspects: first, the high-level specification of the solver's algorithm using MARTE; second, the expected results by applying our solver module into the Code\_CARMEL.

# Part IV: Appendices

This thesis deals with a twofold research domain: computer science and electromagnetic phenomenon. For this reason, we added two appendices that have basic concepts of High Performance Computing (HPC) and Model-Driven Engineering (MDE). Those concepts are often referenced in the main text whenever their definitions are necessary.

# • Appendix A: High Performance Computing

This appendix does not intend to be a complete study on HPC. However, the basic theory and specially the GPGPU and OpenCL worlds are presented here as a quick reference.

# • Appenidx B: Model-Driven Engineering

Similar to Appendix A for HPC, this appendix presents basic concepts on MDE. More precisely, it deals with MDE philosophy and MARTE profile for UML. Again, those concepts are referenced in the main text and they enlighten some of MARTE packages.

Part I

# STATE OF THE ART

# HIGH-LEVEL MODELING AND CODE GENERATION ON HPC

# CHAPTER CONTENTS

- 1.1 High-Level Specification Approaches

- 1.1.1 Gaspard2: OpenMP Branch

- 1.1.2 Archi-MDE

- 1.1.3 Simulink

- 1.1.4 OpenModelica

- 1.1.5 Syntony

- 1.2 Extensions for Programming Languages

- 1.2.1 Mint Programming Model

- 1.2.2 OpenHMPP

- 1.2.3 Java OpenCL Bindings

- 1.2.4 Matlab and Matlab-like on GPU

- 1.2.5 PyOpenCL

- 1.2.6 SAC

- 1.3 Other Contributions

- 1.4 Comparative Table of Features

- 1.5 Conclusion

Before presenting our approach, in this chapter, we discuss some important approaches in the state of the art on high-level modeling and code generation dedicated to HPC systems. There are many programming solutions available to create high performance applications. We emphasize here a twofold category for those solutions. On the one hand, we have languages that hide the low level from developers. In this case, developers specify their intentions at a high abstraction level and then a Domain-Specific Language (DSL) compiler is able to create automatically code for the desired platform. On the other hand, there are approaches that enable developers to use the power of languages for parallel applications based on templates or through directives simplifying the complex command syntax. In this chapter, we present some of those solutions, enlightening their advantages and drawbacks regarding the objectives seen in the introductory chapter.

# 1.1 HIGH-LEVEL SPECIFICATION APPROACHES

In this section, we emphasize 5 approaches based on high abstraction level specification. Some of them aim at creating highperformance applications, while others address modeling of systems.

# 1.1.1 Gaspard2: OpenMP Branch

Based on a previous version of Gaspard2, the OpenMP branch is a result of the Taillard's thesis [137]. His thesis' work focuses on parallel application development from its specification, maintenance, and code generation for the target platform. As our proposal, this work is result of a Model-Driven Engineering (MDE) methodology taking an application specification from a high-level abstraction UML model to a parallel code automatically generated by model transformations.

One of our aims is extending the Taillard's work. However, we are obliged to take into account some limitations of his approach, as follow:

- 1. It does not use the standard Modeling and Analysis of Real-Time and Embedded Systems (MARTE) profile to specify the application.

- Even if OpenMP is a parallel programming model, it has many differences from GPU's programming model, mainly the distributed memory aspect of CPU and GPU; OpenMP is oriented to shared memory and usually it is not suitable to thousands of threads management<sup>3</sup>.

- 3. The device multiplicity for OpenMP implies on a new available processor (or a few cores) to allocate new threads. In GPGPU, a new device implies on, for instance, 240 new cores with their own independent memory to allocate possible thousands of tasks instance (threads).

- 4. Even if every produced application can be always optimized, the compiler within model transformations takes into account just the model as it was designed (even if a memory management is proposed), the model designer is responsible for possible necessary changes in the model in order to attain a better performance level.

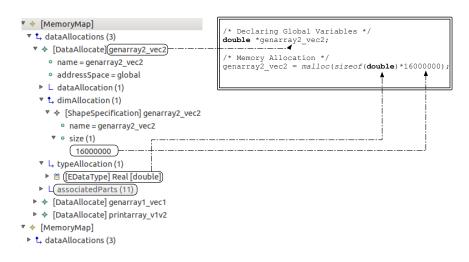

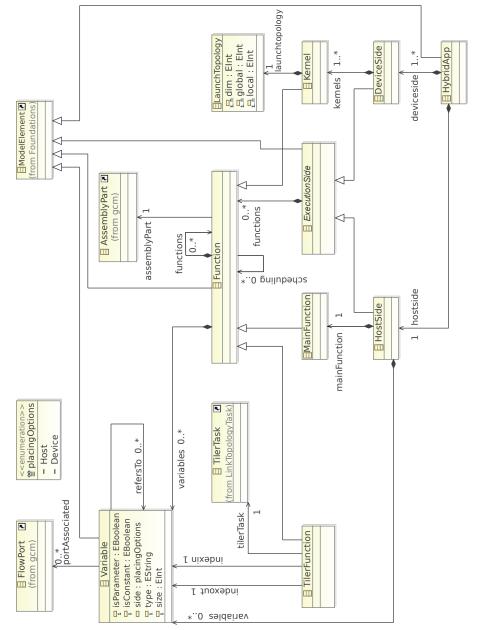

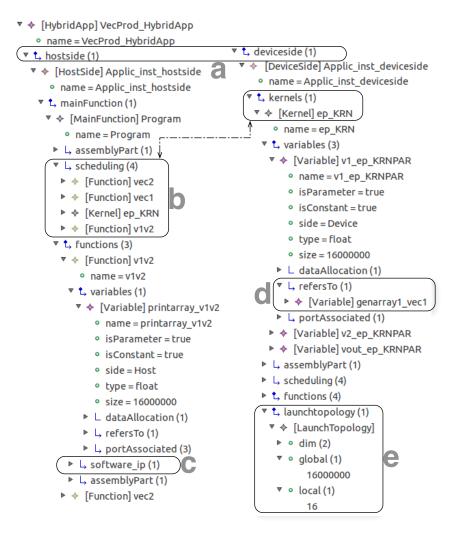

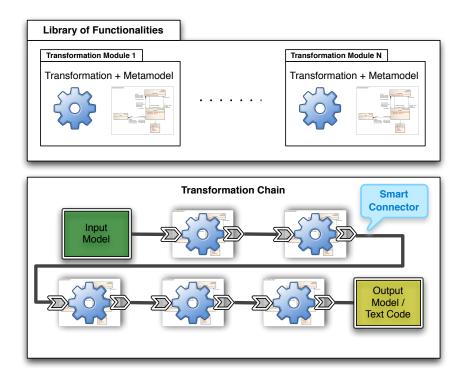

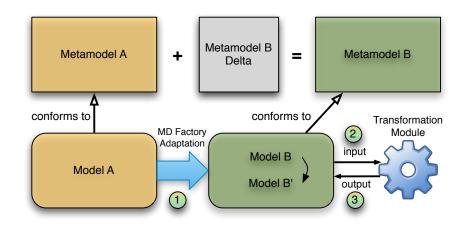

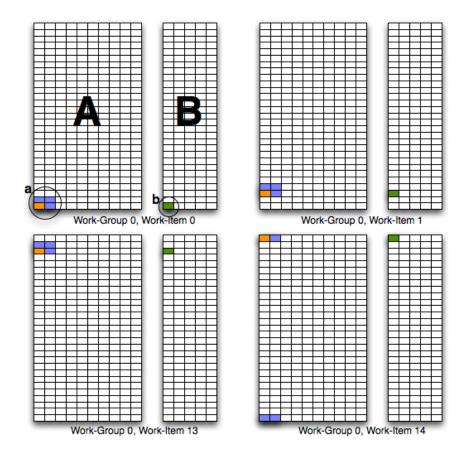

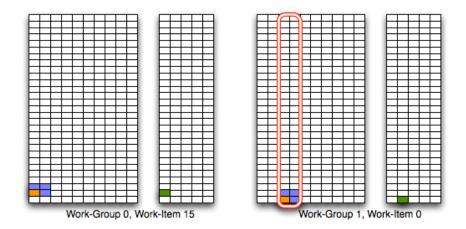

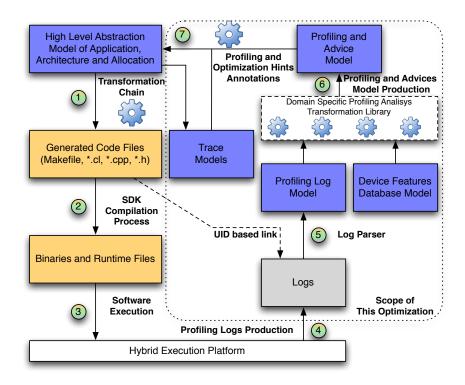

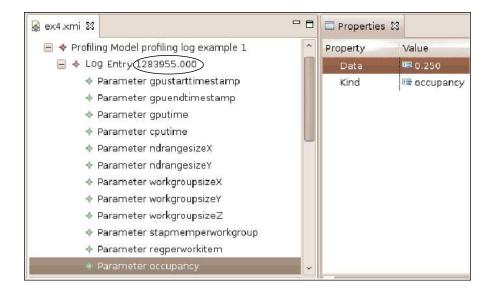

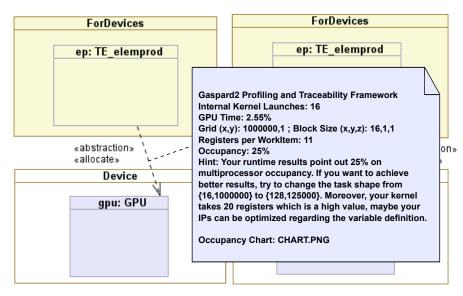

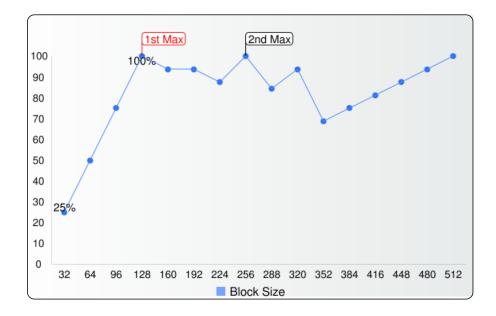

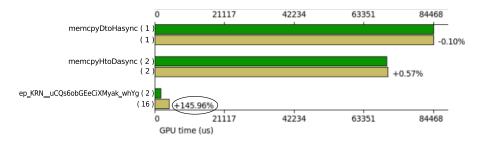

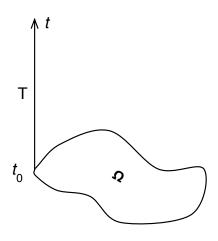

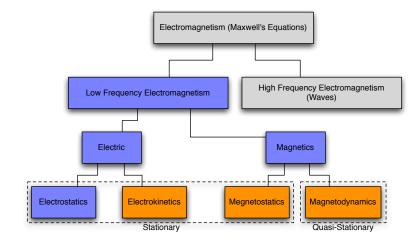

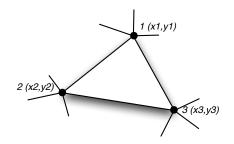

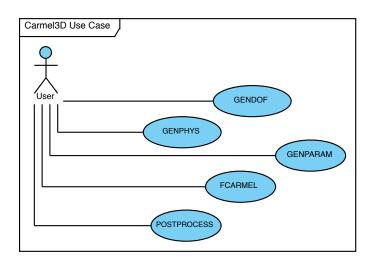

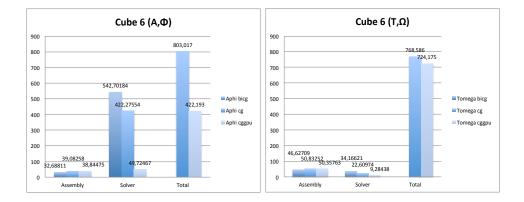

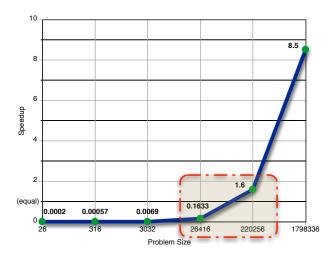

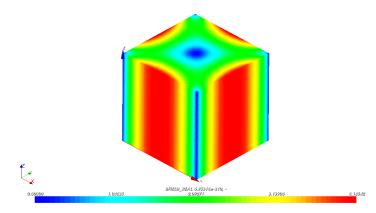

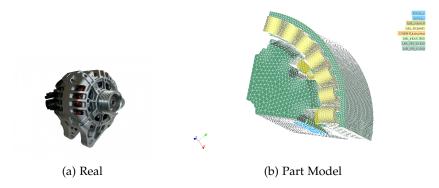

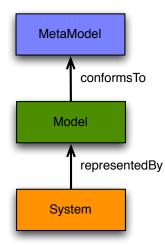

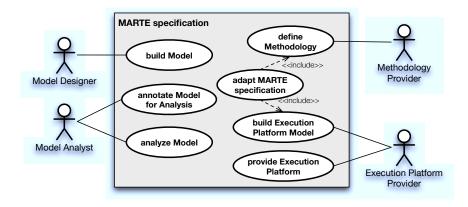

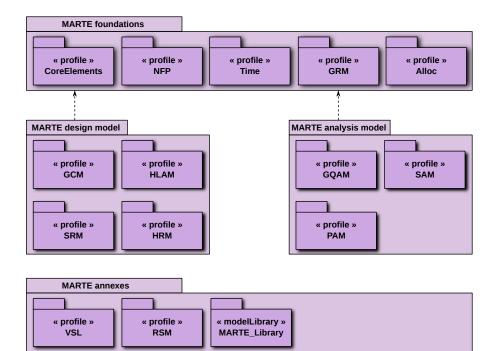

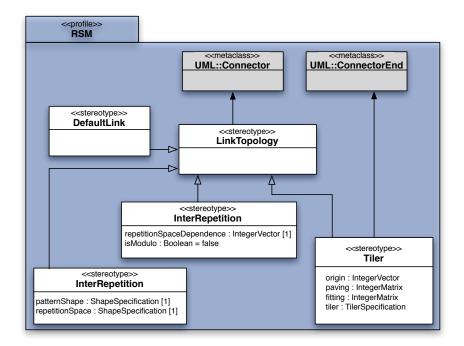

- 5. Except for the thread grid definition, the management of threads dispatching is entirely made by the GPU controller. Differently, Taillard makes use of polyhedron models to optimize loops and distribute sub-tasks in OpenMP.