# Multi-Dimensional Analysis of Software Power Consumptions in Multi-Core Architectures

## **THÈSE**

pour l'obtention du

### DOCTORAT Informatique

École doctorale Sciences Pour l'Ingénieur (Lille)

## Écrite par

#### **Maxime Colmant**

présentée et soutenue publiquement le 24 Novembre 2016

#### devant le jury composé de :

| Mr.  | Olivier     | Barais     | Université Rennes 1     | Rapporteur   |

|------|-------------|------------|-------------------------|--------------|

| Mr.  | Rüdiger     | Kapitza    | Université Braunschweig | Rapporteur   |

| Mr.  | Giuseppe    | Lipari     | Université Lille 1      | Président    |

| Mme. | Anne-Cécile | Orgerie    | CNRS                    | Examinatrice |

| Mr.  | Romain      | Rouvoy     | Université Lille 1      | Directeur    |

| Mr.  | Lionel      | Seinturier | Université Lille 1      | Directeur    |

| Mr.  | Alain       | Anglade    | ADEME                   | Invité       |

## **Acknowledgements**

First of all, I would like to really thank my supervisors, Romain and Lionel. More particularly Romain without whom I would never have started a PhD after my master degree. Thank you for taking me under your wing and taking my wish into consideration. Thank you again for your constant support, your everyday precious advices, all our interesting discussions over a coffee and, for being patient when I missed (a few) deadlines. Even if I still have a long way to go, I am now a young researcher thanks to you.

Next, I would like to thank the members of my thesis committee. Rüdiger Kapitza and Olivier Barais, thanks for having accepted to review my manuscript and for the valuable comments you gave me. I really appreciated your feedbacks. Moreover, I would like to thank Giuseppe Lipari and Anne-Cécile Orgerie to have accepted to be part of the committee, I am very honored.

I also would like to really thank all the members of the Spirals team. It was a great pleasure to share ideas and discussions with you. Special dedications to the other PhD students who have started their thesis at the same time as me: Geoffrey, María, and Bo. We started together, now we end together! Thanks all for your support, especially the last few months where we supported each other during the tedious process of the thesis writing. Special thanks to Geoffrey that I know for more than 5 years now, I really appreciate your hospitality and your time when I came to Montréal. We shared a lot of "last-minute" student projects together. Even if it is was hard sometimes, we did it and we can be proud to be where we are today. I hope we will continue to share beers together, you are the master and I still have a lot of "homework" to do before to surpass you. Another special thanks to María, it was a great pleasure to meet you and to share these three years with you. I would like to apologize for the bad advice on the activity tracker you bought, I hope the bugs will be fixed soon! I will not forget all members of the team with whom we share a lot of interesting discussions (Loïc, Julien, Antoine, Christophe (x2), Fawaz, Clément, Nicolas, Matis ...). Sorry for those I forgot :-) For all, I wish you all the best for the future.

Thanks to the French Environment & Energy Management Agency (ADEME) and the University of Lille 1 for financially supporting this thesis, and to Alain Anglade who followed and advised me during these three years.

Finally, I would like to thank my family. Lot of thanks to my parents, Myriam and Jean, to my sister Laetitia, to my brother-in-law Olivier, my fresh air breathes, my nephew Nathan and my goddaughter Romane. Thanks for believing me during these three years, I would not be who I am without you. Many thanks to my partner's family, René for the swimming pool sessions and discussions, Corinne for her delicious dishes, Coralie,

Anthony, Clarisse, Sébastien, Mickaël for all the good times we shared together. Thanks to my friends, Angélique, Dona, Nicolas, and Alexis, who encouraged me when I took the decision to start a PhD.

Last but not least, I would like to say a special thank to my beloved girlfriend, Mélanie. Thanks for supporting me, believing in me, and to loving me for more than 2 years now. I really appreciate all the efforts you made, and I am very grateful for that. You are the person who makes me smile every day, who inspiring me.

## **Abstract**

Energy represents one of the largest cost factors when operating data centers, largely due to the consumption of air conditioning, network infrastructure, and host machines. Energy-efficient computing is becoming increasingly important. Among the reasons, one can mention the massive consumption of large data centers that consume as much as 180,000 homes. This trend, combined with environmental concerns, makes energy efficiency a prime technological and societal challenge. Currently, widely used power distribution units (PDUs) are often shared amongst nodes to deliver aggregated power consumption reports, in the range of hours and minutes. However, in order to improve the energy efficiency of software systems, we need to support process-level power estimation in real-time, which goes beyond the capacity of a PDU. In particular, the CPU is considered by the research community as the major power consumer within a node and draws attention while trying to model the system power consumption. Software power estimation of CPUs is therefore a central concern for energy efficiency and resource management in data centers. It is hence required to provide critical indicators for driving scheduling policies or power capping heuristics.

Over the last few years, a dozen of ad hoc power models have been proposed to cope with the wide diversity and the growing complexity of modern CPU architectures. However most of these CPU power models rely on a thorough expertise of the targeted architectures, thus leading to the design of hardware-specific solutions that can hardly be ported beyond the initial settings. We therefore promulgate in this thesis, POWERAPI, a middleware toolkit that implements learning techniques that automatically learn the power models of a CPU, independently of the features and the complexity it exhibits. The aforementioned learning techniques are not limited to CPUs and we therefore extend these techniques for other hardware components, such as SSD disks.

PowerAPI is built as a modular solution to assemble software-defined power meters "à la carte", thus fostering the wide adoption of power models. These solutions are customizable and can deliver power estimation reports at various frequencies upon user requirements. Furthermore, PowerAPI is designed to monitor concurrent applications on modern architectures, thus allowing accurate and efficient energy analysis.

With the emergence of cloud computing, the research community already proposed several solutions to monitor the power consumption of virtualized environments. State-of-the-art solutions fail to propose a required per-process power estimation inside VMs and rather propose to only consider the overall power estimation of VMs (as black boxes). Yet, VM-based systems are nowadays commonly used to host multiple applications for cost savings and better use of energy by sharing common resources and assets. We therefore

propose a middleware toolkit, BITWATTS, built on top of POWERAPI that paves the way to a better monitoring and provides real-time and accurate power estimation of software processes running at any level of virtualization. In addition, we propose WATTSKIT to better understand how the power consumption of processes can be distributed across the nodes of a cluster.

Even if software-defined power meters are the first step to better understand and optimize the software power consumption, a finer level of estimation may be required to further evaluate the effectiveness (or ineffectiveness) of the software optimizations. One may want, for example, to compare 2 versions of a same software and thus observe the energy leaks or improvements brought by the modifications. To address these shortcomings, we develop an approach, CODENERGY, that leverages the use of dynamic and interactive reports to better help the developers to analyze the energy distribution of methods and to easily detect deterioration and/or improvements.

All the aforementioned approaches and tools are deeply assessed in this thesis, thus demonstrating the usefulness of PowerAPI to better understand the software power consumption on modern architectures.

## Résumé

L'Energie représente l'un des principaux postes de dépense pour un centre de données, et est principalement liée à l'air climatisé, à l'infrastructure complexe du réseau sous-jacent et au grand nombre de machines utilisées. L'Informatique "verte" est dorénavant un enjeu majeur. Parmi les raisons principales, nous pouvons mentionner les centres de données qui consomment autant que 180 000 foyers en électricité. Associé aux préoccupations énergétiques, cet enjeu représente un challenge technologique et sociétal de premier ordre. Des wattmètres sont actuellement utilisés et partagés pour récupérer un ensemble agrégé de rapports énergétiques sur plusieurs heures ou minutes. Pour améliorer l'efficacité énergétique des logiciels, nous devons donc dépasser ces limitations et proposer des estimations plus fines, c'est-à-dire au niveau processus. Plus particulièrement, la communauté scientifique considère le CPU comme étant le composant le plus énergivore et est donc principalement considéré lors de la modélisation énergétique d'un système. L'estimation énergétique du processeur au niveau logiciel représente donc un enjeu majeur pour améliorer l'efficience énergétique et l'allocation des ressources des centres de données. Il est donc crucial de proposer des indicateurs critiques pour permettre l'application de nouvelles politiques d'ordonnancement ou de limitation énergétique.

Durant les dernières années, des dizaines de modèles de consommation ont été proposées pour prendre en compte la grande diversité et la complexité grandissante des architectures récentes de CPU. Cependant, la plupart de ces modèles se basent sur de profondes connaissances des architectures sous-jacentes, conduisant ainsi à la création de solutions spécifiques non évolutives. Nous proposons donc dans cette thèse, POWERAPI, un intergiciel qui implémente des techniques d'apprentissage permettant d'inférer les modèles de consommation d'un processeur, indépendamment de ses technologies et de sa complexité interne. Ces techniques ne sont cependant pas limitées au CPU et nous avons d'ores et déjà démontré leur applicabilité sur d'autres composants, comme les disques SSDs.

PowerAPI est une solution modulaire permettant d'assembler des wattmètres logiciels à la carte, favorisant ainsi l'adoption des modèles de puissance. Ces solutions sont configurables et peuvent délivrer des estimations énergétiques à des fréquences variées, répondant ainsi au mieux aux besoins des utilisateurs. De plus, PowerAPI a été conçu pour suivre énergétiquement des applications concurrentiels s'exécutant sur des architectures modernes, permettant ainsi des analyses énergétiques efficaces et précises.

Avec l'émergence de l'Informatique dématérialisée, la communauté scientifique propose déjà plusieurs solutions pour permettre de suivre la consommation énergétique au sein d'environnement virtualisé. Ces solutions échouent cependant quant à estimer la consommation à grain fin, c'est-à-dire au niveau applicatif, et se limitent à la consommation globale de ces environnements. Cependant, ce type d'environnement est déjà couramment utilisé pour héberger plusieurs applications, minimisant ainsi les coûts et les ressources utilisées. Nous proposons pour cela, BITWATTS, développé en complément de POWERAPI, pour permettre un meilleur suivi énergétique en estimant en temps réel la consommation des applications s'exécutant à différents niveaux de virtualisation. Nous proposons également une autre extension, WATTSKIT, permettant de mieux comprendre la consommation énergétique de services distribués au sein d'un ensemble de machines.

Les wattmètres logiciels sont la première étape pour mieux comprendre et optimiser la consommation des logiciels. Cependant, il est parfois nécessaire d'avoir un niveau encore plus fin pour mieux comprendre ce qu'il se passe au sein du logiciel. Par exemple, on pourrait vouloir comparer différentes versions d'un même logiciel pour mettre en évidence des fuites (ou optimisations) énergétiques induites par certaines modifications. Nous avons développé CODENERGY pour pallier à ce problème. CODENERGY favorise l'utilisation de rapports interactifs et dynamiques pour aider les développeurs à mieux analyser la répartition énergétique entre les différents composants d'un logiciel et ainsi détecter plus rapidement les améliorations et/ou détériorations énergétiques.

Toutes ces approches et outils susmentionnés ont été validés durant cette thèse, démontrant ainsi l'utilité de POWERAPI pour mieux analyser et comprendre les consommations logicielles sur les architectures modernes.

# **Table of Contents**

| Tak      | ole o                                   | f Contents                         |                       |

|----------|-----------------------------------------|------------------------------------|-----------------------|

| Acı      | ony                                     | ms                                 |                       |

| List     | t <b>of</b> 2                           | Figures                            |                       |

| List     | t of                                    | $\Gamma$ ables                     |                       |

| List     | t of                                    | Snippets                           |                       |

| 1        | Inti<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Contributions                      | 1<br>2<br>3<br>4<br>4 |

| I        | Sta                                     | ate-of-the-Art                     | 7                     |

| <b>2</b> | Lea                                     | rning Power Models                 | ç                     |

|          | 2.1<br>2.2<br>2.3                       | VM Power Models                    | 9<br>14<br>15         |

| 3        | Pov                                     | ver Measurement Granularities 1    | 7                     |

|          | 3.1                                     | Hardware-Level Granularity         | L 7                   |

|          | 3.2                                     | Process-Level Granularity          | L8                    |

|          | 3.3                                     | Code-Level Granularity             | [6                    |

| II       | Co                                      | ntributions 2                      | 3                     |

| 4        | Lea                                     | rning Power Models Automatically 2 | ) =                   |

| _        | 4.1                                     | v                                  | 26                    |

|          |                                         |                                    | 27                    |

|     |     | 4.1.2 Architecture-Agnostic Approach                |                  |

|-----|-----|-----------------------------------------------------|------------------|

|     | 4.2 | Learning SSD Power Models                           |                  |

|     |     | 4.2.1 Empirical Approach                            | 34               |

| 5   |     | 8                                                   | 37               |

|     | 5.1 |                                                     | 38               |

|     | 5.2 | POWERAPI, a Middleware Toolkit                      | 39               |

|     | 5.3 |                                                     | 45               |

|     | 5.4 | PowerAPI's Assemblies                               | 46               |

| III | Eva | aluations 5                                         | 51               |

| 6   | Pro | cess-Level Power Estimation in Multi-Core Systems 5 | 53               |

|     | 6.1 | v                                                   | 54               |

|     | 0.2 |                                                     | 54               |

|     |     | 1                                                   | -<br>55          |

|     | 6.2 | ě č                                                 | 59               |

|     | ·-  |                                                     | 59               |

|     | 6.3 | 1 0                                                 | 61               |

|     | 0.0 |                                                     | 62               |

|     |     | 1                                                   | 63               |

|     |     | e e e e e e e e e e e e e e e e e e e               | 63               |

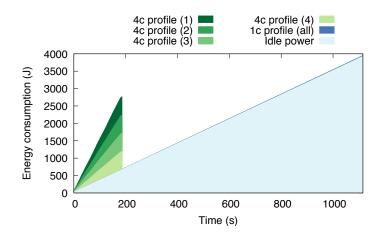

|     |     | <u> </u>                                            | 64               |

|     |     |                                                     | 65               |

| 7   | Saa | S-Level Power Estimation                            | 39               |

|     | 7.1 |                                                     | 69               |

|     | ,   | 7.1.1 BITWATTS, Middleware Toolkit for VMs          |                  |

|     |     | ·                                                   | <br>72           |

|     |     | -                                                   | . <u>-</u><br>73 |

|     |     |                                                     |                  |

|     |     | 1                                                   | 75               |

|     |     |                                                     | . o<br>76        |

|     | 7.2 | <u> </u>                                            | 79               |

|     | 1.2 | · · · · · · · · · · · · · · · · · · ·               | 80               |

|     |     |                                                     | 81               |

|     |     |                                                     | 82               |

|     |     |                                                     | 32<br>83         |

|     |     | ·                                                   | 84               |

|     |     |                                                     | 54<br>85         |

|     |     | 7.2.0 Analyzing the Lower Consumption Let Service   | 30               |

| 8   |     | Ü                                                   | 3 <b>7</b>       |

|     | 8.1 | , 1                                                 | 88<br>88         |

|     |     | 9 ,                                                 |                  |

|     |     | ,                                                   | 90               |

|     |     | ,                                                   | 90               |

|     | 0.0 | ,                                                   | 91<br>93         |

|     | 8.2 | CODENERGY'S Overhead                                | っく               |

#### TABLE OF CONTENTS

|         | 8.3   | 8.3 Study the Methods Energy Distribution of redis            |    |  |  |  |

|---------|-------|---------------------------------------------------------------|----|--|--|--|

|         |       | 8.3.1 Comparing the Energy Evolution of redis Over Versions 9 | 4  |  |  |  |

|         |       | 8.3.2 Comparing the Energy Impacts of redis Configurations 9  | 6  |  |  |  |

| 9       | Cor   | nclusion & Perspectives 9                                     | 9  |  |  |  |

|         | 9.1   | Summary of the Dissertation                                   | 9  |  |  |  |

|         | 9.2   | Contributions                                                 | 0  |  |  |  |

|         | 9.3   | Short-Term Perspectives                                       | 2  |  |  |  |

|         | 9.4   | Long-Term Perspectives                                        | 4  |  |  |  |

| Bil     | oliog | raphy                                                         | i  |  |  |  |

| Αp      | pend  | lices                                                         | x  |  |  |  |

| ${f A}$ | Hai   | rdware Architectures                                          | αi |  |  |  |

## **Acronyms**

ACPS Active Cycles Per Second

**BLKIO** Block IO Controller

**CMOS** Complementary Metal-Oxide Semiconductor

**CS** C-States

**DVFS** Dynamic Voltage/Frequency Scaling

**DWARF** Debugging With Attributed Record Formats

**HPC** Hardware Performance Counters

**HT** Hyper-Threading

ICT Information and Communications Technology

**IPC** Instruction Per Ccyle

IaaS Infrastructure-as-a-Service

**JIT** Just-In-Time

JVM Java Virtual Machine

MSD Mean Square Deviation

MPI Message Passing Interface

NPB NAS Parallel Benchmark

NRMSD Normalized Root Mean Square Deviation

PaaS Platform-as-a-Service

**PDU** Power Distribution Unit

**PMU** Performance Monitoring Unit

**RAPL** Running Average Power Limit

RHEL Red Hat Enterprise Linux

#### TABLE OF CONTENTS

**RMS** Recognition, Mining, and Synthesis

**RTT** Round Trip Time

**SMT** Simultaneous Multi-Threading

SaaS Software-as-a-Service

SS SpeedStep

**TB** TurboBoost

**TDP** Thermal Design Power

TLP Thread-Level Parallelism

**TSC** TimeStamp Counter

YCSB Yahoo! Cloud Serving Benchmark

# **List of Figures**

| 4.1          | Example of Modern CPU architecture                                                                                                                                            | 27         |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.2          | Empirical CPU power modeling approach                                                                                                                                         | 28         |

| 4.3          | Power models for the highest frequencies on an Intel Xeon W3520 processor                                                                                                     | 30         |

| 4.4          | Architecture-agnostic CPU power modeling approach                                                                                                                             | 30         |

| 4.5          | Pearson coefficients of the Top-30 correlated events for the PARSEC benchmarks on an Intel Xeon W3520                                                                         | 31         |

| $4.6 \\ 4.7$ | Average error per combination of events for $R_3$ on an Intel Xeon W3520 processor.<br>Comparison of power consumptions between CPU and SSD by varying the                    | 32         |

|              | throughput with the fio tool                                                                                                                                                  | 33         |

| 4.8<br>4.9   | Empirical SSD power modeling approach                                                                                                                                         | 34<br>36   |

| 5.1          | PowerAPI's architecture & deployment                                                                                                                                          | 40         |

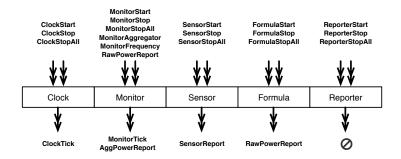

| 5.2          | Overview of internal messages exchanged between the PowerAPI's actors                                                                                                         | 41         |

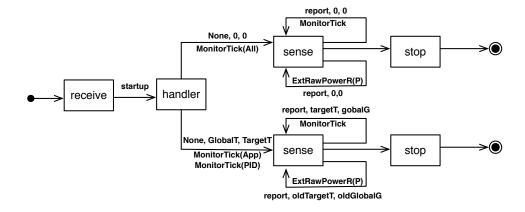

| 5.3          | Clock actor state diagram                                                                                                                                                     | 42         |

| 5.4          | ExternalSensor actor state diagram                                                                                                                                            | 43         |

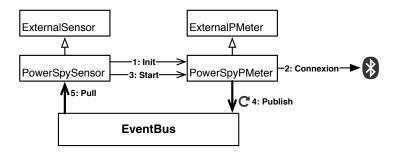

| 5.5          | Link description between PowerAPI and the PowerSpy bluetooth power meter.                                                                                                     | 44         |

| 5.6          | PowerAPI's repository statistics                                                                                                                                              | 45         |

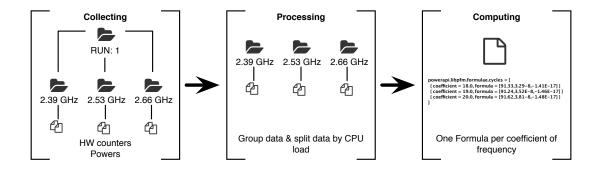

| 5.7          | Phases used by PowerAPI to generate the power models and generate the configuration file                                                                                      | 48         |

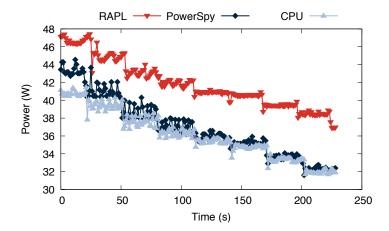

| 6.1          | Decreasing load of stress on the Intel i3 2120 processor, compared to running average power limit (RAPL)                                                                      | 54         |

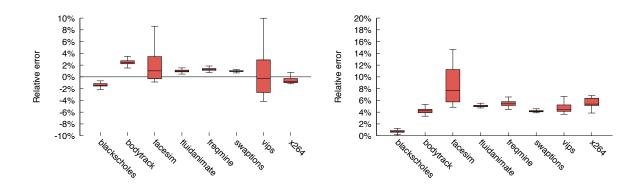

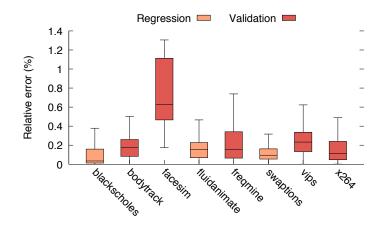

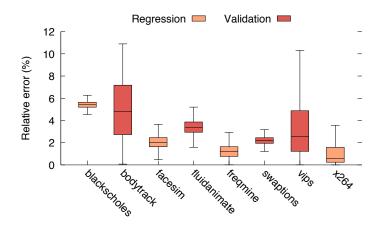

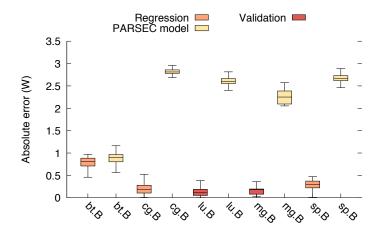

| 6.2          | Relative error distribution of the PARSEC benchmark suite on 2 Intel processors.                                                                                              | 55         |

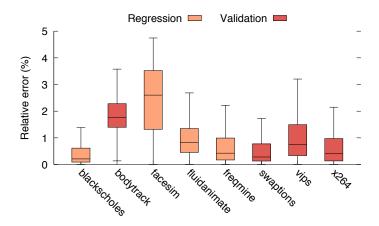

| 6.3          | Relative error distribution of the PARSEC benchmarks on the Intel Xeon                                                                                                        | 56         |

| 6.4          | W3520 processor ( $P_{idle} = 92 W$ )                                                                                                                                         | 90         |

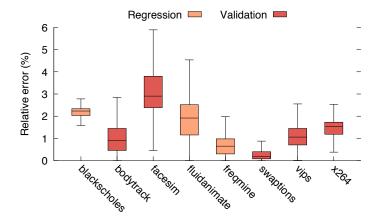

|              | processor $(P_{idle} = 30 \ W)$                                                                                                                                               | 57         |

| 6.5          | Relative error distribution of the PARSEC benchmarks on the AMD Opteron 8354 processor ( $P_{idle} = 390 W$ )                                                                 | 57         |

| 6.6          | Relative error distribution of the PARSEC benchmarks on the ARM Cortex                                                                                                        | <b>F</b> 0 |

| c 7          | A15 processor $(P_{idle} = 3.5 W)$                                                                                                                                            | 58         |

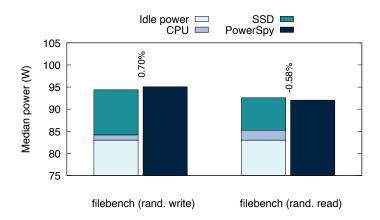

| 6.7          | Power consumption of the Intel Xeon E5-2630 host when executing the filebench benchmark configured to perform random write and read operations ( $P_{idle} = 0.2 \text{ M}$ ) | 60         |

|              | 83 $W$ )                                                                                                                                                                      | 60         |

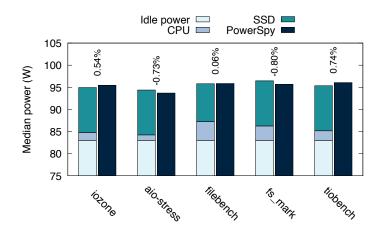

| 0.8        | Power consumption of the Intel Xeon E5-2630 when executing 5 different workloads: iozone, aio-stress, filebench, fs_mark, and tiobench ( $P_{idle} = 83 W$ )                                                                                     | 61       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 6.9        | Absolute error distribution of the NAS parallel benchmark (NPB) benchmarks on the ARM Cortex A15 processor by using the PARSEC and NPB power models ( $P_{idle} = 3.5 W$ )                                                                       | 62       |

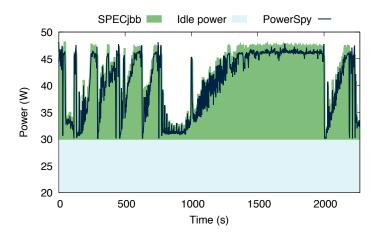

| 6.10       | Power estimation delivered by PowerAPI in real-time (4 Hz) for SPECjbb 2013 on the Intel i3 2120 processor ( $P_{idle} = 30 W$ )                                                                                                                 | 63       |

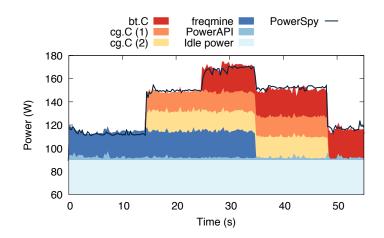

| 6.11       | Process-level power estimation delivered by PowerAPI in real-time (4 Hz) on                                                                                                                                                                      |          |

| 6.12       | the Intel Xeon W3520 processor ( $P_{idle} = 92 W$ )                                                                                                                                                                                             | 64       |

| 6.13       | ARM Cortex A15 processor and cg.b ( $P_{idle} = 3.5 W$ ) Avg. power consumption of the Intel Xeon W3520 in UBUNTU, CENTOS with default settings ( $P_{idle} = 92 W$ ) and CENTOS with latency-performance profile enabled ( $P_{idle} = 125 W$ ) | 66       |

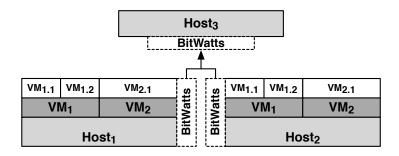

| 7.1        | Example for BITWATTS acting in a multi-tenant virtual environment                                                                                                                                                                                | 70       |

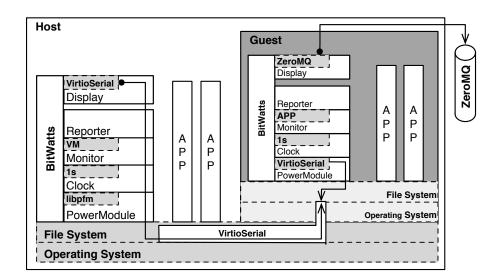

| 7.2        | BITWATTS middleware overview                                                                                                                                                                                                                     | 71       |

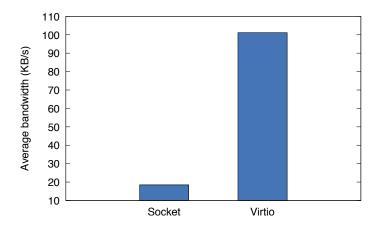

| 7.3<br>7.4 | BITWATTS middleware implementation                                                                                                                                                                                                               | 72<br>73 |

| 7.4        | Average bandwidth (KB/s) for communication using Socket and VirtioSerial virtio-pci interface in action                                                                                                                                          | 73       |

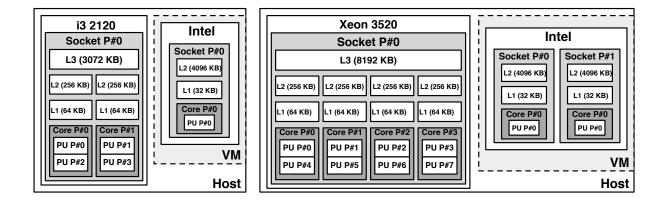

| 7.6        | Intel i3 2120 and Intel Xeon W3520 VM topologies                                                                                                                                                                                                 | 74       |

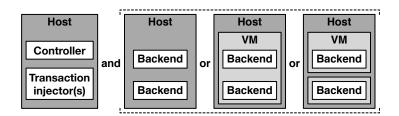

| 7.7        | Possible setup of SPECjbb (only backends are part of the evaluation)                                                                                                                                                                             | 75       |

| 7.8        | Distributed SPECjbb setup                                                                                                                                                                                                                        | 75       |

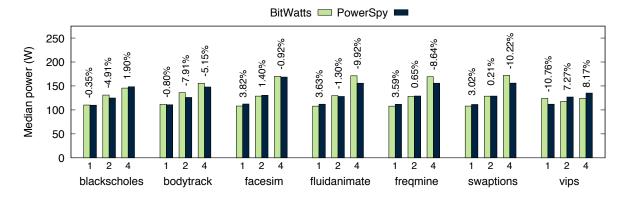

| 7.9        | Power consumption of the host when scaling PARSEC on multiple VMs                                                                                                                                                                                | 76       |

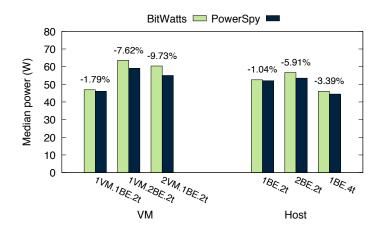

| 7.10       | Median power consumption for SPECjbb on an Intel i3 2120 server with different resources assigned to a single or multiple VMs on one host                                                                                                        | 77       |

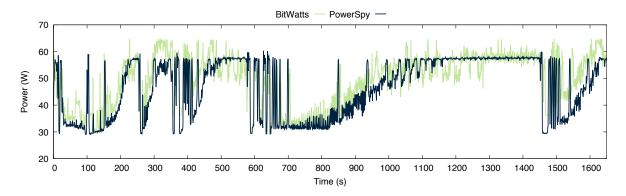

| 7.11       | Power consumption during the execution of SPECjbb on the Intel i3 2120 processor with 2 threads                                                                                                                                                  | 78       |

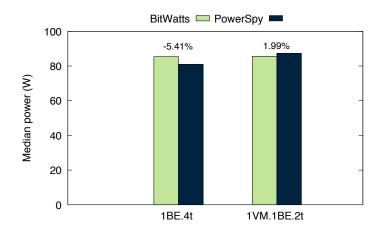

| 7.12       | Median power consumption for SPECjbb on Intel i3 2120 servers for a distributed setup, virtualized and non-virtualized.                                                                                                                          | 79       |

| 7.13       | Overview of the distributed search engine based on Elasticsearch                                                                                                                                                                                 | 81       |

|            | Power consumption of the distributed search engine based on ${\tt ELASTICSEARCH}.$                                                                                                                                                               | 82       |

|            | Software-defined power meter built with WATTSKIT                                                                                                                                                                                                 | 83       |

|            | Overview of the experimental deployment of WATTSKIT                                                                                                                                                                                              | 84       |

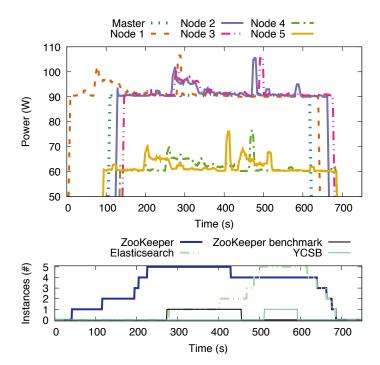

|            | Monitoring the distribution of the power consumption of a distributed system in a cluster                                                                                                                                                        | 85       |

| 7.18       | Analyzing the distribution of the power consumption of ZooKeeper across nodes                                                                                                                                                                    | 86       |

| 8.1        | General overview of the proposal for analyzing the energy distribution of software methods                                                                                                                                                       | 88       |

| 8.2        | Overview of the codEctor architecture                                                                                                                                                                                                            | 90       |

| 8.3        | Data registered for the flushAppendOnlyFile method of a redis execution while querying the INFLUXDB service.                                                                                                                                     | 91       |

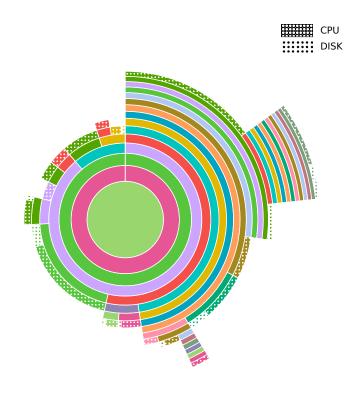

| 8.4        | Sunburst chart available via codVizu for a redis execution                                                                                                                                                                                       | 91       |

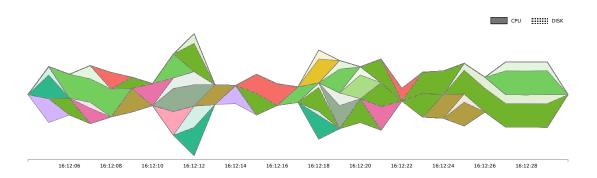

| 8.5        | Streamgraph chart available via codVizu for a redis execution                                                                                                                                                                                    | 92       |

| 8.6        | Impacts of CODENERGY on the power consumption and time completion of a                                                                                                                                                                           |          |

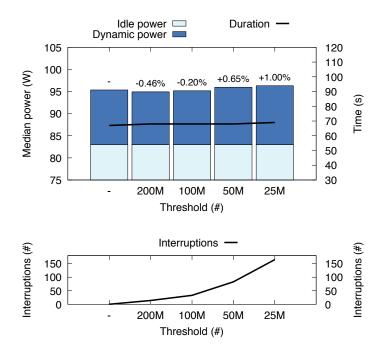

|            | fio workload while decreasing the codAgent's threshold                                                                                                                                                                                           | 93       |

#### LIST OF FIGURES

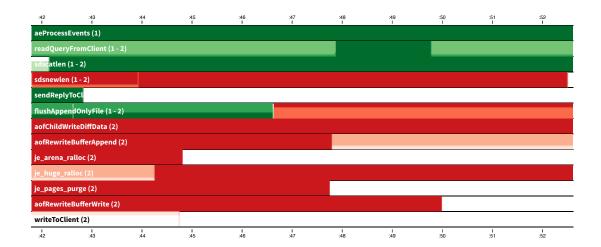

| 8.7 | Energy comparison of methods between redis $(2.2)$ and redis $(3.2)$       | 95 |

|-----|----------------------------------------------------------------------------|----|

| 8.8 | Energy comparison of methods between 2 configurations of redis (3.2) while |    |

|     | sending acks after each command or after 50 commands respectively          | 96 |

# **List of Tables**

|     | Summary of existing CPU power models                                                                                        |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Summary of power monitoring solutions                                                                                       | 21 |

| 7.1 | Experiments performed using SPECjbb (BE: backend, VM: virtual machine, t: threads)                                          | 77 |

|     | Examples of PMUs detected for 5 processors from 3 manufacturers, including numbers of generic counters and available events |    |

# List of Snippets

| 5.1 | Supervisor definition                                                            | 41 |

|-----|----------------------------------------------------------------------------------|----|

| 5.2 | Clock supervisor implementation                                                  | 41 |

| 5.3 | Clock actor implementation                                                       | 43 |

| 5.4 | Base implementation to establish a connexion between PowerAPI and an             |    |

|     | external probe                                                                   | 45 |

| 5.5 | Code used in Section 6.3.3 to demonstrate that PowerAPI is able to achieve       |    |

|     | accurate per-process power estimation                                            | 47 |

| 5.6 | CLI command to create the software-defined power meter described in Snippet 5.5. | 47 |

| 5.7 | Code used in Section 6.1.1 to prove the performance of POWERAPI compared         |    |

|     | to RAPL                                                                          | 47 |

| 5.8 | Example of configuration file generated by PowerAPI that can directly be         |    |

|     | used at runtime.                                                                 | 48 |

| 5.9 | Command to launch the CPU power models learning                                  | 48 |

| 8.1 | Payload message definition.                                                      | 89 |

## Introduction

#### **Table of Contents**

| 1.1 | Problem Statement | 2 |

|-----|-------------------|---|

| 1.2 | Thesis Goals      | 3 |

| 1.3 | Contributions     | 4 |

| 1.4 | Publications      | 4 |

| 1.5 | Outline           | 6 |

Energy-efficient computing is becoming increasingly important. Among the reasons, one can mention the massive power consumption of large data centers, estimated to account for about 2% of global greenhouse gas and some of which consume as much as 180,000 homes [The08; Coo12]. This trend, combined with environmental concerns, makes energy efficiency a prime technological and societal challenge.

Researchers and operators have been proposing solutions to increase energy efficiency at all levels, from application to runtime and to hardware. As surveyed by Surgerie *et al.* [ODL14], examples include methods for energy-based task scheduling, energy-efficient software, dynamic frequency and voltage scaling, and energy-aware workload consolidation using virtualization.

While trying to improve the intrinsic power consumption of runtime applications, one needs to have a powerful and lightweight energy monitoring solution. Such solution has to fulfill all system and user requirements, and must help developers and designers to build energy efficient software. To limit hardware investments, such solutions are often based on the design of power models. Since decades, researchers have already been proposed a dozen of ad hoc power models that fit a specific type of hardware components. How ever, every time a new architecture is released, one has to propose a new power model that fits its requirements. So far, the research community mainly paid a careful attention to the CPU hardware component that contributes for the most part of the overall power consumption of a system [ERK06; NRS15].

We introduce in this thesis different automatic approaches to learn automatically the CPU power models, regardless of their underlying architectures. Beyond CPU, one of these techniques has been reused to learn SSD power models and can therefore be extended to learn any kind of hardware power models. Beyond the learning techniques, we offer an open-testbed to foster the research on green computing and to offer a tool for building software-defined power meters "à la carte". This solution can be then used to support the design of energy-aware scheduling heuristics in homogeneous systems [Bam+13;

Bel00; Mog+13; Ras15], or in heterogeneous data centers [KOS16], to serve the energy-proportional computing [BH07; Kri+10; Mei+11; Pre+15] or to evaluate the effectiveness of optimizations applied on binaries [Sch+14]. It also targets system administrators and software developers alike in monitoring and better understanding the power consumption of their software assets [NRS14; NRS15; Ste13].

On top of these approaches, we developed a toolkit, named POWERAPI, for assembling software-defined power meters upon needs. We define a software-defined power meter as a software solution that can achieve runtime power measurements or estimation at different granularities and frequencies.

Different scenarios are then described to demonstrate the effectiveness of POWERAPI to build accurate software power meters that can next be used for energy monitoring or optimizations.

Among the effervescence of virtualized environments, we propose an extension of POWERAPI, called BITWATTS, to virtually hide all the levels of virtualization and to allow per process energy monitoring inside VMs. As services can now be distributed among several nodes which are not necessarily homogeneous, we define WATTSKIT to monitor and analyze the power consumption of a distributed systems spanning several nodes and thus proposing a finer granularity than observing the overall power consumption of nodes.

To better analyze the energy consumption of software assets, one may need to go deeper and get insights about how the energy is distributed among software assets. We describe in this purpose CODENERGY as a scalable solution to build an interactive cartography of the software energy distribution among source-code and thus allowing developers to focus their efforts on energy hotspots.

This chapter is organized as follows. Section 1.1 introduces the problem statements extracted from the state-of-the-art. Section 1.2 exposes the goals of this thesis and shows how our contributions bring new solutions to face these problems. Section 1.3 describes all contributions detailed in this manuscript. Section 1.4 reports on all the papers and articles (published, under evaluation or to be published) contributed as part of this thesis. And finally, Section 1.5 summarizes the content of this thesis.

#### 1.1 Problem Statement

Software power estimation of CPUs is a central concern for energy efficiency and resource management in data centers. Over the last decade, a dozen of ad hoc power models have been especially designed to cope with the wide diversity and the growing complexity of modern CPU architectures. However, most of CPU power models rely on a thorough expertise of the targeted architectures, thus leading to the design of hardware-specific solutions that can hardly be ported beyond the initial settings. More specifically, the state-of-the-art in this domain faces several key limitations, such as a simplified CPU architecture [Bir+05], the deprecation of the CPU model [IM03], the unavailability of the selected metrics [Zha+14], the handcrafted power models [LJ03], the unavailability of the benchmarks [Zha+14], and the limited diversity of tested workloads [Ber+10] to name a few. These limitations prevent from a wider adoption and deployment of power models, thus limiting the power monitoring of software.

Power monitoring is usually achieved by hardware measurement equipments, such as power meters or specialized integrated circuits. This solution is obviously not suitable at a larger scale, thus requiring costly hardware investments. Furthermore, this kind of power monitoring only provides power measurements at a coarse-grained level—*i.e.*, at

1.2. THESIS GOALS 3

machine-level. However, one needs to have a finer level for better optimizing the energy of the whole system by targeting the applications that are running on it. Consequently, several solutions have been proposed over the years to estimate the power consumption at software-level [FS99; DRS09; Int15b], and even at code-level [CV16; INB16; NRS15]. Nevertheless, most of existing solutions require hardware investments [Bed+10; Ge+10; LPD13; Ras+15], are not suitable while targeting concurrent applications [Ge+10; Ras+15] or lack of modularity [CV16; IM03; INB16; FS99; LBL07; NRS15; NIB16; Int15b].

Power estimation of software processes provide critical indicators to drive scheduling or power capping heuristics. State-of-the-art solutions are facing several key limitations and are often limited to specific hardware components and are not suitable while monitoring concurrent applications.

While considering virtualized environments, we can find solutions that propose coarse-grained power estimation in virtualized environments, typically treating *virtual machines* (VMs) as black boxes. Yet, VM-based systems are nowadays commonly used to host multiple applications for cost savings and better use of energy by sharing common resources and assets.

The design of energy-efficient distributed systems is a challenging task, which requires software engineers to consider all layers of a system, from hardware to software. In particular, monitoring and analyzing the power consumption of a distributed system spanning several—potentially heterogeneous—nodes becomes particularly tedious when aiming at a finer granularity than observing the power consumption of hosting nodes. The state-of-the-art fails to deliver adaptive solutions to offer this perspective and to cope with the diversity of architectures.

New kinds of diagnosis tools are required to better analyze the energy consumed by the software assets. Such level of monitoring requires to retrieve critical runtime informations about the software's call graph while running. These tools need to minimize the instrumentation of the target application in order to be as lightweight as possible and minimize the overhead and disruption.

#### 1.2 Thesis Goals

The first goal of this thesis is to propose automatic learning approaches for hardware power models that do not rely on an *a priori* knowledge of the underlying architecture. With these approaches, everyone can build power models with minimal hardware investments. Once learned, power models can be coupled together with software-defined power meters for learning more about the software energy usages.

Next, we want to propose an efficient toolkit to build these software-defined power meters upon needs. We therefore believe of a solution that can bring the required modularity to end-users for fulfilling all their requirements. With such tool, one can imagine several use cases to better analyze the power consumed by concurrent applications or to find out which parameters can impact the software power consumption.

This thesis aims also to answer several new challenges raised by the diversity of dimensions that can be exploited by modern software systems. In particular, we go beyond the state-of-the-art by proposing an innovative way for better handling processes that run inside VMs and thus do not see them as black-boxes anymore. Moreover, we also propose an approach to allow the energy monitoring of distributed services, where no solutions exist for this problem. We finally describe a new approach for creating a wider

energy cartography of the software source-code and thus helping developers to build energy efficient software.

#### 1.3 Contributions

This thesis first proposes an open testbed to leverage the research on power models. More specifically, 3 techniques that accurately learn the power models of CPU and SSD hardware components are described. Our CPU learning approaches have been assessed on the main CPU manufacturers—i.e., Intel, AMD, ARM—and exhibits an average accuracy greater than 95% at runtime when compared to power measurements. We extend one of the CPU learning approach to SSD component and thus demonstrating the generalization of our techniques. This extended technique for SSDs exhibit an average accuracy of 99%. We believe that these approaches can therefore be extended to other power consuming components, such as GPU [JSM12], in order to incrementally learn their power model and thus provide a wider cartography of the power consumption of a software system.

These learning approaches described in this manuscript are combined to build accurate component power models. They can furthermore be used to produce accurate per-process power estimation upon requirements. We therefore propose PowerAPI, a middleware toolkit for building software-defined power meters "à la carte". A software-defined power meter is defined as a software solution that allows to propose several power estimation (or measurements) granularities at different frequencies. The main purpose of PowerAPI is to be as modular as possible in order to fit all user requirements. PowerAPI can be thus used on top of various power models to build software-defined power meters. Several scenarios are presented in this thesis, thus demonstrating the modularity and the usability of PowerAPI to monitor multiple concurrent processes at runtime in various situations.

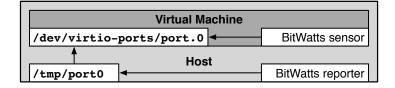

Based on these power models, we propose a fined-grained monitoring middleware that provides real-time and accurate power estimation of software processes running at any virtualized level. Our middleware implementation, BITWATTS, is built on top of POWERAPI, and uses high-throughput communication channels to spread the power consumption across the VM levels and between machines. This non-invasive monitoring solution therefore paves the way for scalable energy accounting that takes into account the dynamic nature of virtualized environments.

To better understand how the power consumption of the system's processes is distributed across nodes at runtime, we define a new specific software-defined power meter, WATTSKIT. Beyond the demonstrated capability of covering a wide diversity of nodes with high accuracy, we show the benefits of adopting software-defined power meters to analyze the power consumption of legacy complex distributed systems.

We finally propose a novel approach, CODENERGY, for building fined-grained interactive energy reports about the software energy usages. This approach paves the way for better analyzing the software power consumption and thus allowing to observe energy improvements or decreases during the development process.

#### 1.4 Publications

Several works presented in this manuscript are under evaluation, not yet published or about to be submitted while writing this manuscript. We present below all published, submitted and upcoming papers related to the work presented through this manuscript.

#### Conferences

- [Col+15b] M. Colmant, M. Kurpicz, P. Felber, L. Huertas, R. Rouvoy, and A. Sobe. "Process-level Power Estimation in VM-based Systems". In: Proceedings of the 10th European Conference on Computer Systems (EuroSys). 2015.

- [CRS14] M. Colmant, R. Rouvoy, and L. Seinturier. "Improving the Energy Efficiency of Software Systems for Multi-Core Architectures". In: Middleware 2014 Doctoral Symposium. 2014.

- [CRS15a] M. Colmant, R. Rouvoy, and L. Seinturier. "Estimation de la consommation des systèmes logiciels sur des architectures multi-coeurs". In: Conférence d'informatique en Parallélisme, Architecture et Système (Compas). 2015.

- [Hav+ar] A. Havet, V. Schiavoni, P. Felber, M. Colmant, R. Rouvoy, and C. Fetzer. "GENPACK: A Generational Scheduler for Cloud Data Centers". In: *IEEE International Conference on Cloud Engineering (IC2E)*. 2017. (To appear).

#### Posters

- [Col+14] M. Colmant, M. Kurpicz, P. Felber, L. Huertas, R. Rouvoy, and A. Sobe. BitWatts: A Process-level Power Monitoring Middleware. Middleware- Poster session. 2014.

- [Col+15a] M. Colmant, M. Kurpicz, P. Felber, L. Huertas, R. Rouvoy, and A. Sobe. Process-level Power Estimation in VM-based Systems. European Conference on Computer Systems (EuroSys) - Poster session. 2015.

- [CRS15b] M. Colmant, R. Rouvoy, and L. Seinturier. Process-level Power Estimation in Multi-core Architectures. Conférence d'informatique en Parallélisme, Architecture et Système (Compas) - Poster session. 2015.

- [Kur+14] M. Kurpicz, M. Colmant, L. Huertas, A. Sobe, P. Felber, and R. Rouvoy. *How energy-efficient is your cloud app?* Conférence d'informatique en Parallélisme, Architecture et Système (Compas) Poster session. 2014.

#### **Under Evaluation**

#### Journals

[Col+16] M. Colmant, R. Rouvoy, M. Kurpicz, P. Felber, A. Sobe, and L. Seinturier. "The Next 700 CPU Power Models". In: ACM Trans. Model. Perform. Eval. Comput. Syst. (ACM TOMPECS) (2016).

#### **Future Submissions**

#### Conferences

- [Col+17] M. Colmant, R. Rouvoy, M. Kurpicz, P. Felber, A. Sobe, and L. Seinturier. "WattsKit: Software-Defined Power Monitoring of Distributed Systems". In: To be chosen. 2017.

- [CRS17] M. Colmant, R. Rouvoy, and L. Seinturier. "codEnergy: an Approach For Leveraging Source-Code Level Energy Analysis". In: *To be chosen.* 2017.

#### 1.5 Outline

The remainder of the document is organized as follows. We first present the research background that motivates this thesis in Part I. Chapter 2 introduces all recent research approaches for learning power models, while Chapter 3 present different tools that can estimate or measure the power consumption at different granularities.

Secondly, Part II describes our contributions to address the state-of-the-art limitations. In Chapter 4, we propose 2 learning approaches for modern CPU power models, and 1 for SSD power models. All the described approaches aim to build efficient and non-invasive runtime power models that can be used at runtime to estimate the power consumption at software-level in real-time. In Chapter 5, we describe our middleware toolkit, PowerAPI, that builds on top of the state-of-the-art solutions and is as modular as possible. The learned power models can be used together with PowerAPI to compute runtime power estimation of concurrent processes.

Next, Part III validates the contributions of this thesis. Chapter 6 assesses the learning approaches detailed in Part II, and demonstrates the applicability of PowerAPI in various monitoring scenarios. We next propose to go beyond the state-of-the-art in Chapter 7 and Chapter 8. Chapter 7 proposes to extend PowerAPI for estimating the power consumption of applications that run inside virtualized environments and thus seeing VMs as white boxes—i.e., virtualization becomes transparent. In addition, we describe another extension for building a finer view of the power consumed by distributed services that run inside a cluster of heterogeneous nodes. Chapter 8 reports on our proposal for better understanding the power consumption drawn by the software and therefore proposes an energy diagnosis tool for building interactive energy source-code reports.

We finally conclude and present new research perspectives in Chapter 9.

# ${f Part\ I}$ State-of-the-Art

# **Learning Power Models**

#### Table of Contents

| 2.1 | CPU Power Models  | 9         |

|-----|-------------------|-----------|

| 2.2 | VM Power Models   | 14        |

| 2.3 | Disk Power Models | <b>15</b> |

As current multi-core platforms do not provide fine-grained power measurement capabilities, McCullough *et al.* [McC+11] argue that power models are the first step towards enabling dynamic power management for power proportionality at all levels of a system. Power modeling often consider learning techniques—for example based on sampling [Ber+12]—that assume the proportionality of the system events to power consumption. Measurements of a hardware power meter are gathered and subsequently used, together with a set of normalized estimated values, in various regression models.

The remainder of this chapter is organized as follows. Section 2.1 discusses the state-of-the-art of CPU power models, while Section 2.2 describes the VM power models and Section 2.3 the disk power models.

#### 2.1 CPU Power Models

Along the last decade, the design of CPU power models has been regularly considered by the research community [Bel00; Col+15b; Kan+10; McC+11; VWT13]. Currently, the closest approach to hardware-based monitoring is RAPL, introduced with the Intel "Sandy Bridge" architecture to report on the power consumption of the entire CPU package. As this feature is not available on other architectures and is not always accurate [Col+15b], CPU power models are generally designed based on a wider diversity of raw metrics.

Standard operating system metrics (CPU, memory, disk, or network), directly computed by the kernel, tend to exhibit a large error rate due to their lack of precision [Kan+10; VWT13]. Contrary to usage statistics, hardware performance counters (HPC) can be obtained from the processor (e.g., number of retired instructions, cache misses, non-halted cycles). Modern processors provide a variable number of HPC, depending on architectures and generations. As shown by Bellosa [Bel00] and Bircher [BJ07], some HPC are highly correlated with the processor power consumption whereas the authors in [RRK08] conclude that several performance counters are not useful as they are not directly correlated with dynamic power. Nevertheless, this correlation depends on the processor architecture and

Table 2.1: Summary of existing CPU power models.

| Author(s)               | s)                 | Processor(s)                                                        | Feature(s)                             | Regression(s)                   | Benchmarks                                                  | Error(s)            |

|-------------------------|--------------------|---------------------------------------------------------------------|----------------------------------------|---------------------------------|-------------------------------------------------------------|---------------------|

| A.Aroca et al.          | [Arj+14]           | Xeon W3530                                                          | HW sensors                             | polynomial,<br>multiple linear  | eval.: Hadoop App.                                          | <7% of total energy |

| Bertran et al.          | [Ber+10]           | Core 2 Duo                                                          | 14 HPCs regrouped<br>by component      | multiple linear<br>by component | $sampl.: \mu$ -benchs $eval.: SPEC CPU 06$                  | 2%                  |

| Bircher et al.          | [Bir+05]           | Pentium 4                                                           | $\mu$ -ops trace-cache, micro-code ROM | multiple linear                 | sampl.: SPEC CPU 00 eval.: SPEC CPU 00                      | 2.5%                |

| Contreras et al. [CM05] | [CM05]             | XScale<br>PXA255                                                    | 5 HPCs                                 | multiple linear                 | eval.: SPEC CPU 00,<br>Java CDC/CLDC                        | 4%                  |

| Dolz et al.             | [Dol+15]           | Xeon<br>E3-1275                                                     | 3 HPCs<br>HW sensors                   | linear                          | sampl.: linpack, stream, iperf, IOR eval.: Quantum Espresso | 3 W<br>70 W max.    |

| Economou et al. [ERK06] | $[\mathrm{ERK06}]$ | Turion,<br>Itanium 2                                                | HW sensors                             | multiple linear                 | sampl.: Gamut eval.: SPECs, Matrix, Stream                  | 2%                  |

| Isci et al.             | [IM03]             | Pentium 4                                                           | 15 HPCs                                | multiple linear                 | eval.: $\mu$ -benchs, AbiWord, Mozilla, Gnumeric            | 3~W                 |

| Li et al.               | [LJ03]             | 8-way issue<br>superscalar                                          | IPC                                    | linear                          | sampl./eval.: DB, email,<br>SPEC JVM 98, SPEC INT 95        | 1% off.<br>6% run.  |

| Rivoire et al.          | [RRK08]            | Core 2 Duo & Xeon,<br>Itanium 2, Turion                             | HW sensors<br>HPCs                     | multiple linear                 | sampl.: calibration suite eval.: SPECs, stream, Nsort       | <5%                 |

| Yang et al.             | [Yan+14]           | $\begin{array}{c} \text{Xeon} \\ \text{E5620 \& E7530} \end{array}$ | 7 components<br>91 preselected         | support vector                  | sampl.: NPB, IOzone, CacheBench eval.: SPEC CPU 06, IOzone  | 4.7%                |

| Zamani et al.           | [ZA12]             | Opteron                                                             | 3 to 5 HPCs                            | ARMAX                           | sampl./eval.: BT.C, CG.C,<br>LU.C, SP.C                     | 0.1%-0.5% offline   |

| Zhai et al.             | [Zha+14]           | Sandy Bridge                                                        | non-halted cycles                      | linear                          | eval.: Google, SPEC CPU 06                                  | 7.5%                |

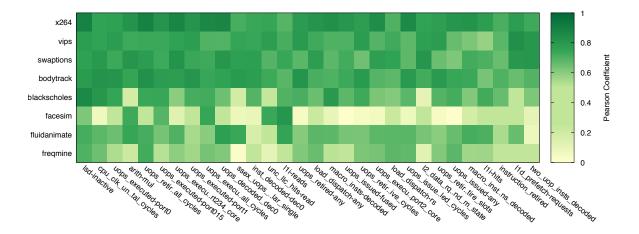

the CPU power model computed using some HPCs may not be ported to different settings and architectures. Furthermore, the number of HPC that can be monitored simultaneously is limited and depends on the underlying architecture [Int15a], which also limits the ability to port a CPU power model on a different architecture. Therefore, finding an approach to select the relevant HPC represents a tedious task, regardless of the CPU architecture.

Power modeling often builds on these raw metrics to apply learning techniques—for example based on sampling [Ber+10]—to correlate the metrics with hardware power measurements using various regression models, which are so far mostly linear [McC+11].

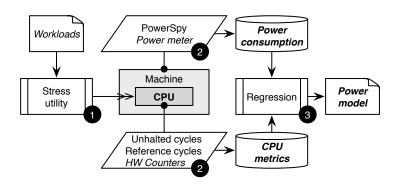

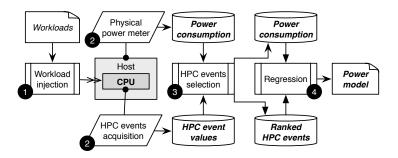

A.Aroca et al. propose to model several hardware components (CPU, disk, network). It is the closest approach of our empirical learning method describes in Section 4.1.1. They use the lookbusy tool to generate a CPU load for each available frequency and a fixed number of active cores. They capture active cycles per second (ACPS) and raw power measurements while loading the CPU. A polynomial regression is used for proposing a power model per combination of frequency and number of active cores. They validate their power models on a single processor (Intel Xeon W3520) by using a map-reduce Hadoop application. During the validation, the authors have not been able to correctly capture the input parameter of their power model—i.e., the overall CPU load—and they use an estimation instead. The resulting "tuned" power model with all components together exhibits an error rate of 7% compared to total amount of energy consumed.

Bertran et al. [Ber+10] model the power consumption of an Intel Core2 Duo by selecting 14 HPCs based on an a priori knowledge of the underlying architecture. To compute their model, the authors inject both selected HPCs and power measurements inside a multivariate linear regression. A modified version of perfmon2<sup>1</sup> is used to collect the raw HPC values. In particular, the authors developed 97 specific micro-benchmarks to stress each component identified in isolation. These benchmarks are written in C and assembly, and cannot be generalized to other architectures. They assess their solution with the SPEC CPU 2006 benchmark suite, reporting an error rate of 5% on a multi-core architecture.

Bircher et al. [Bir+05] propose a power model for an Intel Pentium 4 processor. They provide a first model that uses the number of fetched  $\mu$ -operations per cycle, reporting on an average error rate of 2.6%. As this model was performing better for benchmarks inducing integer operations, the authors refine their model by using the definition of a floating point operation. As a consequence, their second power model builds on 2 HPC: the  $\mu$ -operations delivered by the trace cache and the  $\mu$ -operations delivered by the  $\mu$ -code ROM. This model is assessed using the SPEC CPU 2000 benchmark suite, which is split in 10 groups. One benchmark is selected per group to train the model and the remaining ones are used to assess their estimation. Overall, the resulting CPU power model reports on an average error of 2.5%.

In [CM05], Contreras et al. propose a multivariate linear CPU power model for the Intel XScale PXA255 processor. They additionally consider different CPU frequencies on this processor to build a more accurate power model. They carefully selected the HPCs with the best correlation while avoiding redundancy, resulting in the selection of only 5 HPCs. In their paper, they also consider the power drawn by the main memory using 2 HPCs already used in the CPU power model. However, given that this processor can only monitor 2 events concurrently, they cannot implement an efficient and usable runtime power estimation. They test their solution on SPEC CPU 2000, Java CDC, and Java

<sup>1</sup>http://perfmon2.sourceforge.net

CLDC, and they report an average error rate of 4% compared to the measured average power consumption.

The authors in [Dol+15] propose an approach to build linear power models for hardware components (CPU, memory, network, disk) by applying a per component analysis. Their technique uses 4 benchmarks during the training phase and collect various metrics gathered from hardware performance counters, OS statistics, or sensors. They build a correlation matrix on all gathered metrics (including power measurements) and then apply a clustering algorithm on top of it. The power models presented in this article are manually extracted from these groups. Without considering the power models which include directly power measurements, the best one exhibits an absolute error of 3 W on average with a maximum absolute error of 70 W.

Economou et al. [ERK06] model the power consumption of 2 servers (Turion, Itanium) as a multiple linear regression that uses various utilization metrics as input parameters. The authors use the CPU utilization, the off-chip memory access count, the hard-disk I/O rate, and the network I/O rate. The input parameters are learned by using Gamut that emulates applications with varying levels of CPU, memory, hard disk, and network utilization. In order to retrieve raw power measurements, the authors uses board-level modifications and 4 "power planes" (extracted from the paper), which is heavy for endusers and represents a major hardware investment. On average, their power models exhibit an error rate less than 5% (varying between 0% and 15% in all cases) while using SPEC benchmarks, matrix and stream.

Isci and Martonosi [IM03] use an alternative approach to estimate the power consumption of an Intel Pentium 4 processor. They isolate 22 processor subunits with the help of designed micro-benchmarks and live power measurements. For each subunit, they use simple linear heuristics, which can include one or more HPC. For the others (trace cache, allocation, rename...), they use a specific piecewise linear approach. They selected 15 different HPC to model all subunits, some of them are reconfigured or rotated when needed. At the end, they express the CPU power consumption as the sum of all subunits. They train their model on designed micro-benchmarks, SPEC CPU 2000 and some desktop tools (AbiWord, Mozilla, Gnumeric) and they report on an average error of 3 W.

Li and John [LJ03] rely on per OS-routines power estimation to characterize at best the power drawn by a system. They simulate an 8-way issue, out-of-order superscalar processor with function unit latency. The authors use 21 applications, including SPEC JVM 98 and SPEC INT 95. During their experiments, they identify instruction per ccyle (IPC) to be very relevant to model the power drawn by the OS routines invoked by the benchmarks. The resulting CPU power model exhibits an average error of up to 6% in runtime testing conditions.

Rivoire et al. [RRK08] propose an approach to generate a family of high-level power models by using a common infrastructure. In order to choose the best input metrics for their power models, they compare 5 types of power models that vary on their input metrics and complexity. The first 4 power models are defined in the literature and use basic OS metrics (CPU utilization, disk utilization) [FWB07; Hea+05; RRK08]. They propose the fifth power model that uses HPC in addition to CPU and disk utilizations. The last proposed power model exhibits a mean absolute error less than 4% over 4 families of processors (Core2 Duo, Xeon, Itanium, Turion) by using SPECfp, SPECint, SPECjbb, stream, and Nsort. The authors do not detail the underlying architectures of the testbed CPU, making thus a fair comparison difficult.

iMeter [Yan+14] covers not only CPU, but also memory and I/O. To get a practical model, the authors need to select the proper number of counters. After benchmarking the

VMs under different loads, they empirically extract 91 out of 400 HPCs. In a second step, a principal components analysis is applied to identify a statistical correlation between the power consumption and the performance counters. With this method, highly correlated values are clustered into a smaller set of principal components that are not correlated anymore. The selection of the principal components depends on the cumulative contribution to the variance of the original counters, which should reach at least 85%. The final model is derived by the usage of support vector regression and 3 manually selected events per principal component [VGS97] and reports an average error of 4.7%.

In [ZA12], Zamani et al. study the relationship between HPC and power consumption. They use 4 applications from NAS parallel benchmarks (BT.C, CG.C, LU.C, SP.C) running on 8 threads in a 2 quad-core AMD Opteron processors. Given the limitation of events that they can open simultaneously, the authors first show that the measurement variability other different executions is not significantly large, enabling different runs for sampling all events. This article proposes a deep analysis for HPC selection (single or multiple). The authors demonstrate that a collinearity can exist between events and then propose a novel method to find the best combination of HPC with good performance. They use the ARMAX technique to build their power models. They evaluate their solution by producing a model per application and exhibit a mean absolute error in signal between 0.1%-0.5% for offline analysis.

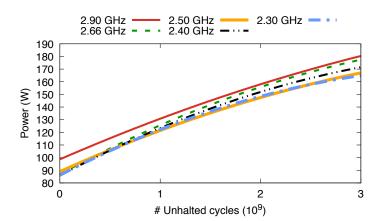

HaPPy [Zha+14] introduces a hyperthread-aware power model that uses only the non-halted cycles event. The authors distinguish different cases where either single or both hardware threads of a core are in use. This power model is linear and contains a ratio computed according to their observations. They demonstrate that when both threads of a core are activated, they share a small part of non-halted cycles. They extend the perf<sup>2</sup> tool to access to RAPL. Their model is tested on a Intel "Sandy Bridge" server with private benchmarks provided by Google, that cannot be reused, and 10 benchmarks taken from SPEC CPU 2006. To assess their power estimation, they used the RAPL interface reachable on this server. Compared to RAPL, they manage to have an average error rate of 7.5%, and a worst case error rate of 9.4%. Nevertheless, as demonstrated in [Col+15b], these error rates can be exceeded in scenarios where only single cores of a CPU are monitored.

#### Summary

As a summary of the current state of practice, the existing CPU power models found in the literature cannot be reproduced because *i*). the details of the selected HPC events are not provided [WCS11] or sufficiently documented [Zha+14], *ii*). they are tailored to a specific processor architecture (including a limited set of power-aware features) [LPF10], or *iii*). they are built on private workloads that cannot be reused to assess alternative power models [Zha+14]. The state-of-the-art is resumed in Table 2.1.

The main contributions of this thesis for overcoming these limitations are: *i*). proposing an in-depth description of our contributions, *ii*). defining architecture-agnostic and automatic learning approaches, *iii*). assessing our approaches on a large set of CPUs that exhibit different architectures and features and, *iiii*). to use real and public workloads. All our contributions are described in Chapter 4.

<sup>&</sup>lt;sup>2</sup>https://perf.wiki.kernel.org

#### 2.2 VM Power Models

In data centers, the efficiency of VM consolidation, power dependent cost modeling, and power provisioning are highly dependent on accurate power models [VAN08]. Such models are particularly needed because it is not possible to attach a power meter to a virtual machine [Kri+11]. In general, VMs can be monitored as black-box systems for coarse-grained scheduling decisions. If we want to be able to do fine-grained scheduling decisions—i.e., with heterogeneous hardware—we need to be able to consider finer-grained estimation at sub-system level and might even need to step inside the VM.

So far, fine-grained power estimation of VMs require profiling each application separately. One example is WATTAPP [KVN10], which relies on application throughput instead of performance counters as a basis for the power model. The developers of PMAP-PER [VAN08] argue that application power estimation is not feasible and instead perform resource mapping using a centralized step-wise decision algorithm.

To generalize power estimation, some systems like JOULEMETER [Kan+10] assume that each VM only hosts a single application and thus treat VMs as black boxes. In a multi-VM system, they try to compute the resource usage of each VM in isolation and feed the resulting values in a power model.

Bertran et al. [Ber+12] use a sampling phase to gather data related to HPCs and compute energy models from these samples. With the gathered energy models, it is possible to predict the power consumption of a process, and therefore apply it to estimate the power consumption of the entire VM. Their work does neither consider modern CPU features.

Another example is given by Bohra et al. in [BC10], where the authors propose a tool named VMETER that estimates the consumption of all active VMs on a system. A linear model is used to compute the VMs power consumption with the help of available statistics (processor utilization and I/O accesses) from each physical node. The total power consumption is subsequently computed by summing the VMs consumption with the power consumed by the infrastructure.

Janacek et al. [Jan+12] use a linear power model to compute the server consumption with postmortem analysis. The computed power consumption is then mapped to VMs depending on their load. This technique is not effective when runtime information is required.

In Stoess et al. [SLB07] the authors argue that, in virtualized environments, energy monitoring has to be integrated within the VM as well as the hypervisor. To that end, they use the L4 micro-kernel as hypervisor and adapt a guest OS to run on L4. They assume that each device driver is able to expose the power consumption of the corresponding device as well as an energy-aware guest operating system and is limited to integer applications. For application level power monitoring, the VM connects to the hypervisor and maps virtualized performance counters to the hardware counters.

#### Summary

State-of-the-art solutions provide no or limited support for fine-grained monitoring of applications running within a VM. The few existing approaches either consider the VM as a black-box running a single application, or require extensions to the hypervisor or

<sup>&</sup>lt;sup>3</sup>VM as a Black-Box

<sup>&</sup>lt;sup>4</sup>VM as a White-Box

| Author(s)      |          | Processor(s)                       | VMaaBB <sup>3</sup> | $VMaaWB^4$ | Error(s)      |  |

|----------------|----------|------------------------------------|---------------------|------------|---------------|--|

| Bertran et al. | [Ber+12] | Core2 Duo T9300                    | <b>///</b>          | Х          | < 5%          |  |

| Bohra et al.   | [BC10]   | Opteron                            | <b>//</b>           | Х          | 6% - 7%       |  |

| Janacek et al. | [Jan+19] | $2 \times \text{Intel Xeon X5560}$ | 11                  | X          | X             |  |

| Sanacck Ct at. |          | $2 \times \text{Intel Xeon X5550}$ |                     |            | <b>,</b>      |  |

| Kansal et al.  | [Kan+10] | Nehalem L5520                      | 11                  | X          | 0.4 W - 2.4 W |  |

| Koller et al.  | [KVN10]  | $2 \times \text{Xeon}$ , Core2 Duo | 11                  | X          | 5%            |  |

| Stoess et al.  | [SLB07]  | Pentium D830                       | 11                  | ✓          | Х             |  |

| Verma et al.   | [VAN08]  | Simulator                          | ✓                   | X          | Х             |  |

Table 2.2: Summary of existing VM power models.

to the host and guest operating systems for being operational. All these approaches are summarized in Table 2.2.

For answering these challenges, we propose in Chapter 7, a middleware solution, BITWATTS, that considers the VM as a white-box and thus allowing to estimate the power consumption of software processes in virtualized environments. Moreover, our middleware framework can work in a distributed setup (multi-tenant environment) and can go through all the levels of virtualization—*i.e.*, can estimate the power consumption of a process that runs inside a VM of another VM, etc.).

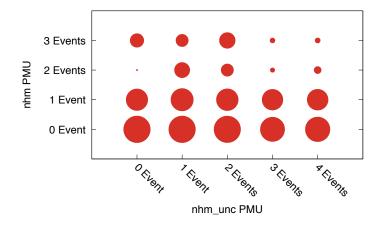

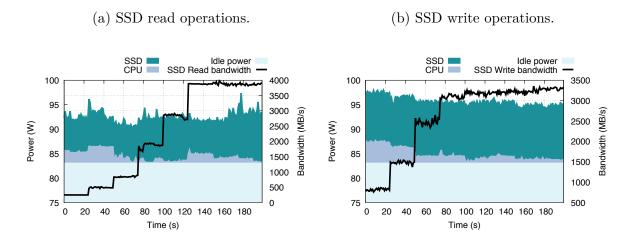

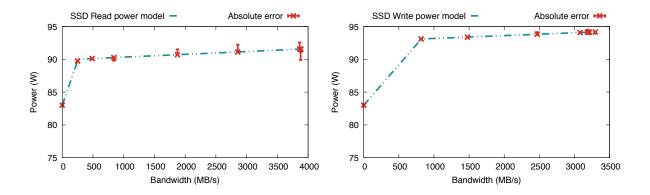

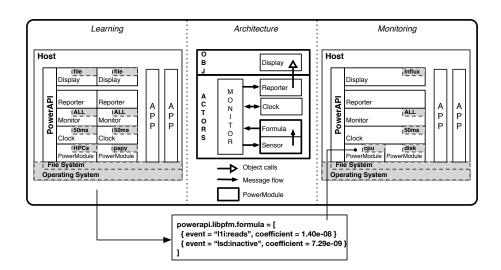

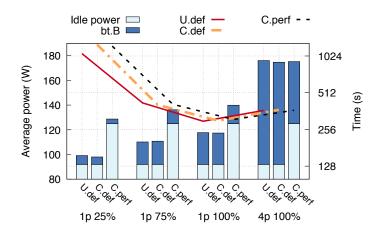

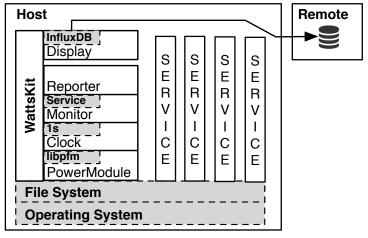

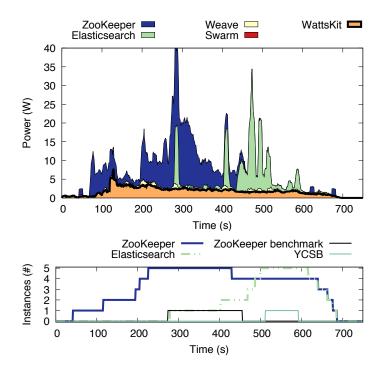

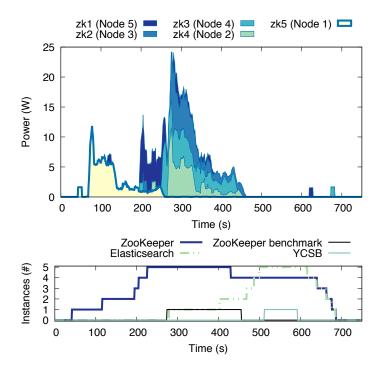

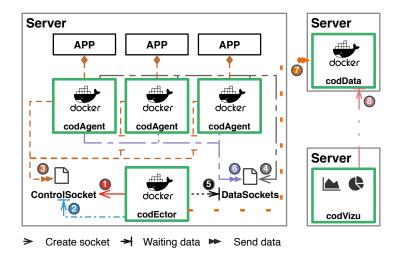

#### 2.3 Disk Power Models