# **UNIVERSITÉ DE LILLE 1**

École Doctorale Sciences Pour l'Ingénieur

# THÈSE

En vue de l'obtention du grade de

## DOCTEUR DE L'UNIVERSITÉ DE LILLE

DISCPLINE: MICRO ET NANOTECHNOLOGIE, ACOUSTIQUE ET TÉLÉCOMMUNICATION

Présentée et soutenue publiquement le 19 Décembre 2016 par

FIKRE TSIGABU GEBREYOHANNES

PROCESSEUR NUMÉRIQUE/RF ADAPTATIF POUR ÉMETTEUR SANS FIL MULTI-BANDES Multi-standard Faible Consommation à 5 GHz et 60 GHz

Scalable Digital-to-RF Processor for Multi-standard and Multi-band Low Power Wireless Transmitter in 5 GHz and 60 GHz

#### JURY :

| Président du Jury :  | M. Christophe GAQUIERE | Professeur à Université Lille 1, IEMN, Lille       |

|----------------------|------------------------|----------------------------------------------------|

| <b>RAPPORTEURS</b> : | M. Yann Deval          | Professeur à Université de Bordeaux, IMS, Bordeaux |

|                      | M. Hassan Aboushady    | Maître de Conférences à UPMC, LIP6, Paris          |

| Examinateurs :       | Mme Patricia Desgreys  | Professeur à Télécom ParisTech, LTCI, Paris        |

|                      | M. Didier Belot        | HDR, CEA-Leti, Grenoble                            |

| Encadrant :          | M. Antoine Frappé      | Enseignant-Chercheur, ISEN Lille                   |

| Directeur de thése : | M. Andreas KAISER      | Directeur de Recherche CNRS, IEMN, Lille           |

# Abstract

Proliferation of application specific wireless communication standards have resulted in the multiple standards, multiple devices for one user scenario of today. Consequently, research in multi-standard, and multi-band systems, architectures, and circuits has been a popular theme. The vision is to have devices which can hope seamlessly from one network to the other while delivering excellent functionality on different radio access technologies.

Configurable transmitter architectures targeting complementary use cases of the multi-Gb/s WiFi-WiGig standards have been studied. Novel approaches based on high speed configurable semi-digital FIR DACs are proposed and published in international journal. In this architectures, transmitter mask and linearity requirements are respected because the single-bit FIR DAC is inherently linear and combines in its functionality both digital-to-analog conversion and filtering of noise. A delta-sigma modulator can be employed for resolution conversion so that baseband signals with wide range of bandwidths and resolutions are processed.

FIR DACs require long filters with high resolution coefficients to achieve stopband attenuation levels that meet out-of-band noise requirements. Normally, this limits high speed multi-standard operation, and results in large silicon area and complex layout. In this work, circuit techniques are developed so that a unit circuit element realizing a coefficient of one transfer function can be re-used in realizing a different-valued coefficient of another transfer function. This multi-modal hardware-sharing capability of the FIR DAC is maximized by system-level coefficient optimization.

The work also proposes topologies that exploit digital signal processing at advanced nodes to implement quadrature modulation while realizing up conversion, digital-to-analog conversion and image and quantization filtering in one configurable passband FIR DAC block.

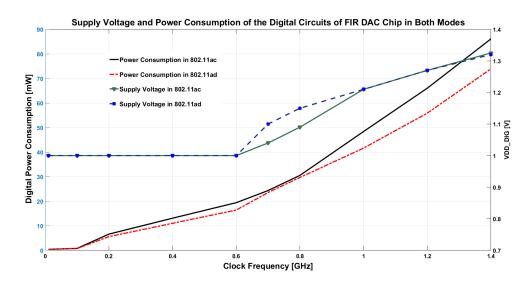

A prototype high pass filter FIR DAC chip which can be configured for the operation of the IEEE 802.11ac and IEEE 802.11ad standards was implemented in STMicroelectronics<sup>®</sup> CMOS 28nm FDSOI technology. The test of this chip has demonstrated the validity of the proposed transmitter architectures. The prototype chip can process passband OFDM signals as wide as 136 MHz at a clock frequency of 3 GHz and reaches an output carrier frequency of 1.5 GHz in the 802.11ac mode. It also can channelize random SC signals as wide as 700 MHz at a clock frequency of 1.4 GHz and reaches an output carrier frequency of 700 MHz. The chip has a total power consumption 103.07 mW in the 802.11ac and 86.89 mW in the 802.11ad modes at 1.4 GHz clock frequency. It is supplied with three separate voltage

supplies: the digital circuits work from 0.6 V to 1.55 V, the analog output network requires a supply of 1.2 V and the biasing circuits are supplied with a separate 1.2 V.

**Key words:** WiFi, WiGig, IEEE 802.11ac, IEEE 802.11ad, WLAN, Transmitter, Multi-standard, Multi-band, Multi-mode, Configurable, DAC, FIR, DRFC, DDRM, High pass, Low pass, Band pass, Delay line, Filter, Delta-Sigma, Half-Band, DSP, CMOS, FDSOI, 28nm

# Acknowledgments

These past three years and eight months have been a period of personal journey. It was also a period of education and development for me as a researcher. More importantly, though, it has given the opportunity to interact with a number of wonderful people. This PhD work has come to fruition due to the enormous help many individuals have been kind enough to provide it me.

I would like to bestow my heartfelt gratitude to my director of research, Prof. Andreas Kaiser. I have been fortunate enough to learn from him and work with him. His guidance through out my research work has been invaluable, and the standard he sets as a professional is something I have personally admired. I would also like to thank my supervisor, Dr. Antoine Frappé, for his dedication, kindness and keeping his office door always open for every one of my questions.

Since my initial correspondence with the SMART Integrated Circuits Design Group in early 2013, I have benefited immensely from the generosity of the team members. Dr. Bruno Stefanelli has shared with me his valuable experience during my presentations, design reviews, chip assembly and measurement. Dr. Jean-Marc Capron was always there for my presentations, and he is a genuinely nice person. I thank Dr. Axel Flament for his comments and for coming to my presentations. Thank you, Axel, also for the enjoyable afterwork football matches. Florence Alberti welcomed me to this beautiful city on a Sunday morning at Euralille. I would like to thank her for guiding me through the intricate world of French administration.

I would like to thank members of the Silicon Microelectronics Group at IEMN, specifically Prof. Emmanuel Dubois, Dr. Jean-François Robillard, and Matthieu Berthomé. Thank you Dr. Pascale Diener for helping me with the pick and place machine during the chip assembly.

My test chip characterization has been carried out at the IRCICA Telecom Platform during many months. I would like to extend my sincere gratitude to Rédha Kassi and his coworkers for making it convenient for me to work there.

I would like to thank the following past and present members of the SMART-ICD Group: fellow PhD students Dr. Baptiste Grave, Dr. Ilias Sourikopoulos, Cristian Marin, Justine Philippe, Matteo Causo, Dr. Camilo Salazar and Dipal Ghosh; postdocs Dr. Pietro Maris, Dr. Stephane Mebaley Ekome, Dr. Walid Bourennane and Dr. Benoit Larras for their support. I have shared the office with Dipal and Walid for a year now, but it is like they were here for a couple of months. It was great discussing with you all the interesting questions of Science, Technology, History and, of course, 140 GHz oscillator.

I have shared the longest part of my stay with Ilias and Cristian. I thank them for their advices and friendship. It was a pleasure to have shared with you the many fun lunch times. They are some of the highlights of my stay in Lille. Pietro, Stephane and Bruce Ferrer for their friendship during their stay here in Lille. It was great to have you guys around.

I also would like to thank the employees of ISEN Lille which were always glad to help me in the rare cases I had asked for it. Thank you Nathalie Rousseau, Josée Vanbouvelen, and others. Valérie Vandenhende is a pleasant person and a great ambassador to the school.

My work was initially funded through the French ANR WENDY project. It was a collaborative project among IEMN, STMicroelectronics and IMS Bordeaux. I would like to thank the team members of that project: Prof. Yann Deval, Dr. Didier Belot, Dr. Mathieu Vallet, Dr. Olivier-cro Richard, and Dr. Sebastien Dedieu. Yann and Didier are also members of my doctoral jury. I would like thank them and the other members of the jury for accepting the invitations. I am also grateful to Dr. Andreia Cathelin and Dr. Philippe Cathelin for the important comments and suggestions they had given me at different periods of my research.

Finally, I would like to thank my friends and my family members. My brothers, my sisters and my parents have always been supportive, considerate and appreciative of whatever endeavor I have taken. I send them my heartfelt gratitude. The last eight months of my doctoral study have been the most satisfying. I thank Seli for her support and love!

# Contents

| AI | ostrac  | ct                                                        | i   |

|----|---------|-----------------------------------------------------------|-----|

| Ac | know    | vledgments                                                | iii |

| Li | st of l | Figures                                                   | ix  |

| Li | st of [ | Tables                                                    | xv  |

| 1  | Intr    | oduction                                                  | 1   |

| Ĩ  | 1.1     | The Scope of this Study                                   | 1   |

|    |         |                                                           |     |

|    | 1.2     | Original contributions                                    | 2   |

|    | 1.3     | Outline                                                   | 3   |

| 2  | Wir     | reless Communication Systems                              | 5   |

|    | 2.1     | Aggregation of Standards                                  | 5   |

|    | 2.2     | Networks of the future                                    | 6   |

|    |         | 2.2.1 Challenges and Solutions                            | 8   |

|    | 2.3     | The WiFi-WiGig Complementarity                            | 9   |

|    |         | 2.3.1 Tri-band WiFi Radio                                 | 10  |

|    | 2.4     | Summary and conclusions                                   | 11  |

| 3  | Mul     | lti-standard Digital Transmitters                         | 13  |

|    | 3.1     | Brief Theory of Transmitter Operation                     | 13  |

|    |         | 3.1.1 Modulation                                          | 14  |

|    |         | 3.1.2 Cartesian Transmitters Architectures                | 18  |

|    |         | 3.1.3 Polar Transmitter Architecture                      | 20  |

|    |         | 3.1.4 Transmitter Performance Metrics                     | 21  |

|    | 3.2     | Review of Digital Transmitter Architectures               | 23  |

|    |         | 3.2.1 Digital Quadrature Modulators                       | 23  |

|    |         | 3.2.2 The RF DAC Concept                                  | 24  |

|    | 3.3     | Multi-standard Digital Transmitters                       | 27  |

|    |         | 3.3.1 Multi-modal Transmitters in Literature              | 29  |

|    |         | 3.3.2 FIR DAC Based Multi-modal Transmitter Archtiectures | 31  |

|   | 3.4 | Summa    | ary and Conclusions                                   | 34 |

|---|-----|----------|-------------------------------------------------------|----|

| 4 | Con | figurabl | e Finite Impulse Response Digital-to-Analog Converter | 35 |

|   | 4.1 | Operati  | ion of a DAC                                          | 35 |

|   |     | 4.1.1    | Traditional Multi-bit DAC                             | 35 |

|   |     | 4.1.2    | Multi-bit DAC Specification                           | 36 |

|   | 4.2 | Traditio | onal DAC Topologies                                   | 38 |

|   |     | 4.2.1    | R-2R Ladder DAC                                       | 39 |

|   |     | 4.2.2    | Resistor String DAC                                   | 39 |

|   |     | 4.2.3    | Current Steering DAC                                  | 39 |

|   | 4.3 | Finite I | Impulse Response DAC                                  | 40 |

|   |     | 4.3.1    | FIR DAC Implementation Issues                         | 41 |

|   |     | 4.3.2    | L-bit, N-tap FIR DAC Design Challenges                | 42 |

|   |     | 4.3.3    | <i>N</i> -tap, 1-bit FIR DAC Design Challenges        | 43 |

|   |     | 4.3.4    | Frequency Translation of FIR DACs                     | 44 |

|   | 4.4 | FIR DA   | AC Architectures in Literature                        | 48 |

|   |     | 4.4.1    | Multi-bit FIR DACs                                    | 48 |

|   |     | 4.4.2    | 1-bit Semi-digital Reconstruction Filter              | 49 |

|   |     | 4.4.3    | Programmable Filtering DAC                            | 50 |

|   |     | 4.4.4    | Receive-band Noise Filter                             | 51 |

|   |     | 4.4.5    | FIR Power DAC                                         | 51 |

|   | 4.5 | High S   | peed 1-bit, N-tap FIR DAC Design                      | 52 |

|   |     | 4.5.1    | Current Steering Architecture                         | 52 |

|   |     | 4.5.2    | Performance Metrics and Modeling                      | 53 |

|   | 4.6 | Summa    | ary and Conclusions                                   | 64 |

| _ | D   |          |                                                       |    |

| 5 | -   | •        | CEE 802.11ac/ad Transmitter Baseband Architecture     | 65 |

|   | 5.1 | 1        | cation of the standards                               | 65 |

|   |     | 5.1.1    | IEEE 802.11ac                                         | 65 |

|   | _   | 5.1.2    | IEEE 802.11ad                                         | 66 |

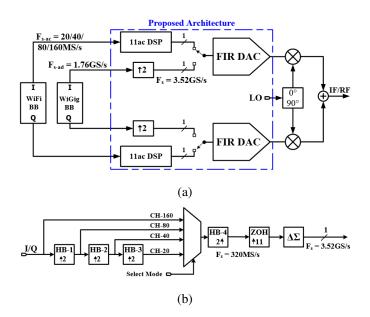

|   | 5.2 | •        | Level Simulation of Proposed Transmitter Architecture | 67 |

|   |     | 5.2.1    | Standard Coexistence                                  | 68 |

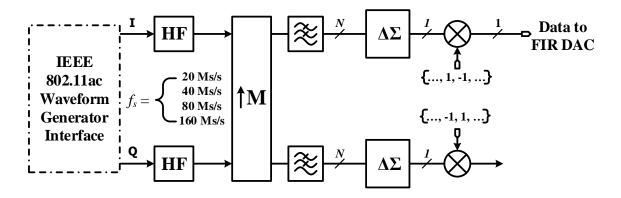

|   |     | 5.2.2    | Transmitter Baseband Architecture                     | 69 |

|   |     | 5.2.3    | DSP Blocks of 802.11ad                                | 70 |

|   |      | 5.2.4  | DSP Blocks of 802.11ac                                                                 | 72 |

|---|------|--------|----------------------------------------------------------------------------------------|----|

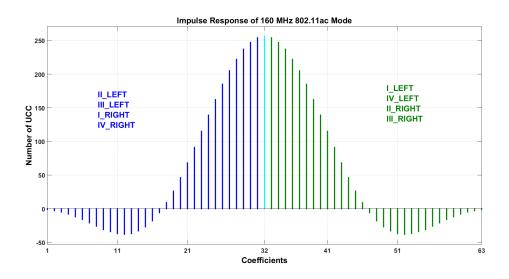

|   |      | 5.2.5  | FIR DAC In Three Modes                                                                 | 76 |

|   | 5.3  | From 7 | Fransfer Function to Circuit Parameters    8                                           | 30 |

|   |      | 5.3.1  | Coefficient Quantization                                                               | 30 |

|   |      | 5.3.2  | Multi-standard FIR DAC Specifications                                                  | 30 |

|   | 5.4  | Summ   | ary and Conclusions                                                                    | 33 |

| 6 | Desi | gn and | Implementation of A Configurable Transmitter Baseband in CMOS 28nm FD-                 |    |

|   | SOI  |        | 8                                                                                      | 85 |

|   | 6.1  | From S | System Level to Floorplan                                                              | 35 |

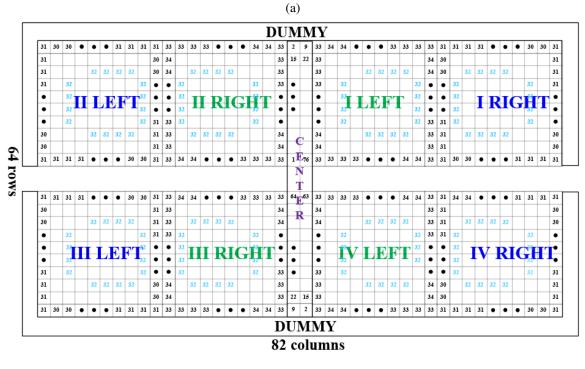

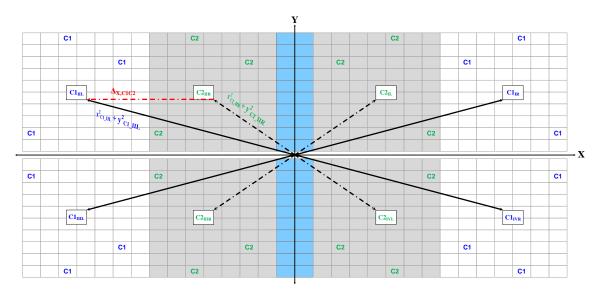

|   | 6.2  | Misma  | tch Errors and Layout Floorplan                                                        | 86 |

|   |      | 6.2.1  | Pseudo-Double Centroid Placement Method                                                | 37 |

|   |      | 6.2.2  | Layout Floorplan                                                                       | 93 |

|   | 6.3  | Desigr | and Layout of Each Block                                                               | 96 |

|   |      | 6.3.1  | Digital Delay Line                                                                     | 96 |

|   |      | 6.3.2  | Mode Selection                                                                         | 98 |

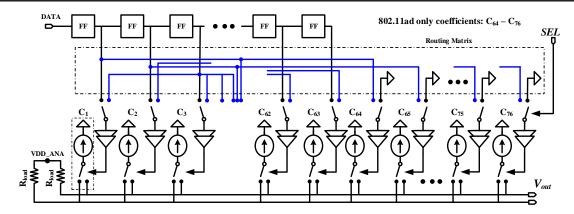

|   |      | 6.3.3  | Routing Matrix                                                                         | 98 |

|   |      | 6.3.4  | Data Drivers                                                                           | )0 |

|   |      | 6.3.5  | Clock Tree and Output Tree                                                             | )4 |

|   |      | 6.3.6  | Unit Current Cell                                                                      | )6 |

|   |      | 6.3.7  | Biasing circuits                                                                       | 10 |

|   | 6.4  | Summ   | ary and Conclusions                                                                    | 14 |

| 7 | Mea  | sureme | nt Results of FIR DAC Prototype                                                        | 15 |

|   | 7.1  | Experi | mental Setup                                                                           | 16 |

|   |      | 7.1.1  | PCB Design                                                                             | 16 |

|   |      | 7.1.2  | Input Data Generation                                                                  | 19 |

|   | 7.2  | Measu  | red Results                                                                            | 20 |

|   |      | 7.2.1  | Biasing Circuits                                                                       | 21 |

|   |      | 7.2.2  | Power Consumption                                                                      | 22 |

|   |      | 7.2.3  | IEEE 802.11ac Mode                                                                     | 24 |

|   |      | 7.2.4  | IEEE 802.11ad Mode                                                                     | 29 |

|   |      | 7.2.5  | Characterization of the FIR DAC for $f_{CLK}$ beyond 600 MHz $\ldots \ldots \ldots 13$ | 32 |

|   |      | 7.2.6  | Comparison with the State of the Art                                                   | 34 |

|     | 7.3     | Conclu   | usions                              | 135 |

|-----|---------|----------|-------------------------------------|-----|

| 8   | Con     | clusion  | s and Future Directions             | 137 |

| Ар  | pend    | ix       |                                     | 139 |

|     | .1      | Transr   | nitter Chain Simulation in Matlab   | 139 |

|     |         | .1.1     | IEEE 802.11ac Transmitter Baseband  | 139 |

|     |         | .1.2     | IEEE 802.11ad Transmitter Baseband  | 143 |

|     | .2      | EVM      | Simulation                          | 144 |

|     |         | .2.1     | Code for EVM Simulation of 802.11ac | 144 |

| Bil | oliogr  | aphy     |                                     | 149 |

| Lis | st of F | Publicat | tions                               | 159 |

| Ab  | strac   | t en Fr  | ançais                              | 161 |

# **List of Figures**

| 2.1  | Evolution of theoretical data rates of wireless technologies from first generation networks               |    |

|------|-----------------------------------------------------------------------------------------------------------|----|

|      | to current giga-bit data rate 4G networks                                                                 | 6  |

| 2.2  | Mobile data traffic by 2020 as predicted by Cisco in [CVM16]. Global mobile data traffic                  |    |

|      | is expected to grow eightfold between 2015 and 2020 with a compound annual growth                         |    |

|      | rate of 53%                                                                                               | 7  |

| 2.3  | Expected IMT-2020 capabilities as compared with those of IMT-Advanced [ITU15]                             | 8  |

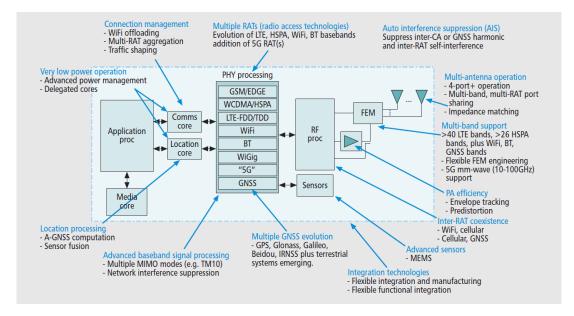

| 2.4  | A 5G device will have to support multiple existing RATs and new ones. The expected                        |    |

|      | capabilities that different parts of the device are shown here[Ban+14b]                                   | 9  |

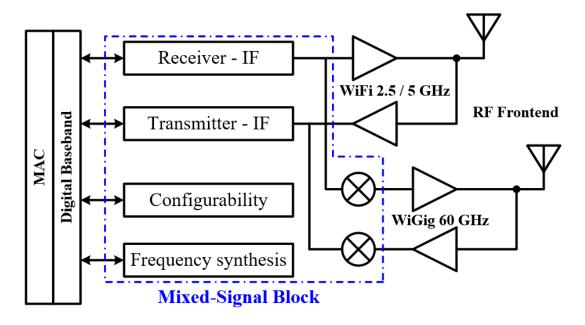

| 2.5  | Block diagram of a configurable transceiver for WiFi and WiGig applications                               | 10 |

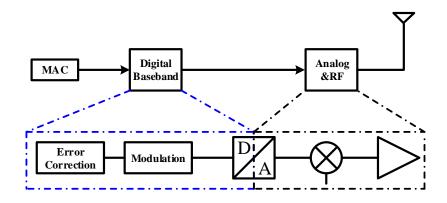

| 3.1  | Essentials blocks of a basic WLAN transmitter. In traditional transmitter, the mixer                      |    |

|      | follows the DAC. However, they can also be implemented in the same circuit.                               | 14 |

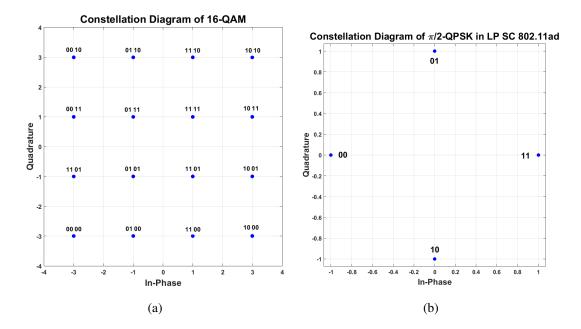

| 3.2  | Constellation diagrams of 16-QAM modulation in 802.11ac and 802.11ad standards, and                       |    |

|      | $\frac{\pi}{2}$ -QPSK modulation of the LP SC mode of the 802.11ad standard $\ldots \ldots \ldots \ldots$ | 16 |

| 3.3  | Basic blocks in the generation of one OFDM symbol                                                         | 16 |

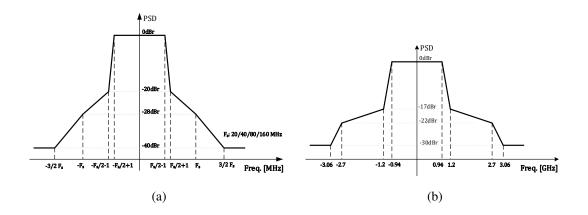

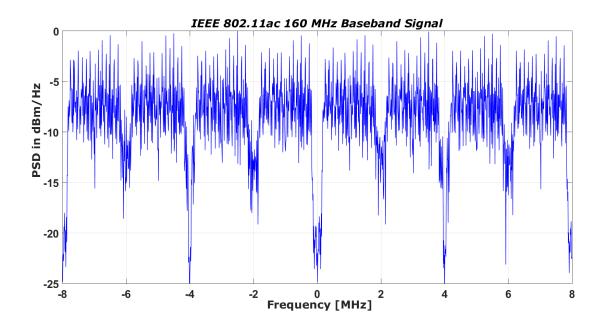

| 3.4  | PSD of a 160 MHz, 802.11ac OFDM symbol using a hann window                                                | 17 |

| 3.5  | Time domain plot of a 160 MHz, 802.11ac OFDM symbol                                                       | 17 |

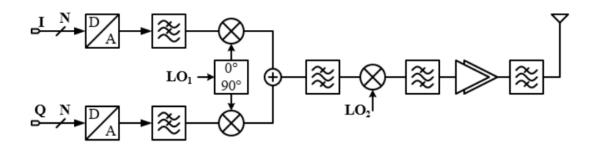

| 3.6  | Direct Conversion transmitter                                                                             | 19 |

| 3.7  | Heterodyne transmitter                                                                                    | 19 |

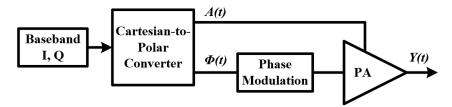

| 3.8  | General block diagram of a polar transmitter                                                              | 20 |

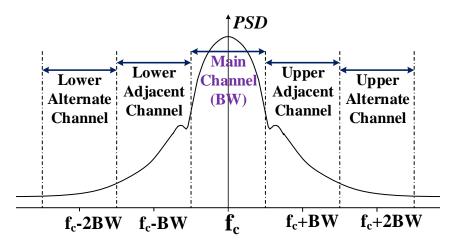

| 3.9  | The ACPR is defined based on the spacing of the main, adjacent and alternate channels                     |    |

|      | in this figure. The ACPR and Alternate CPR measurement results of Chapter 7 are also                      |    |

|      | consistent with this definition.                                                                          | 22 |

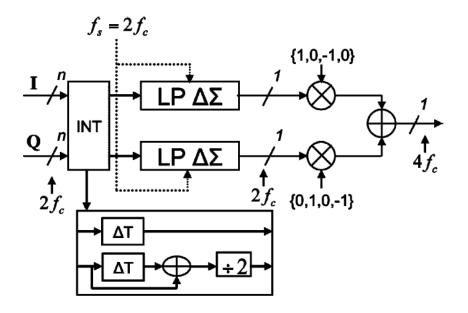

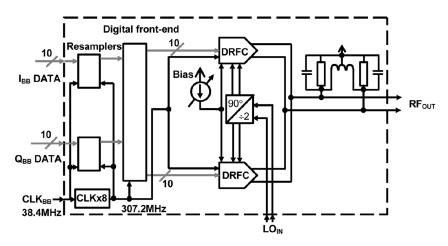

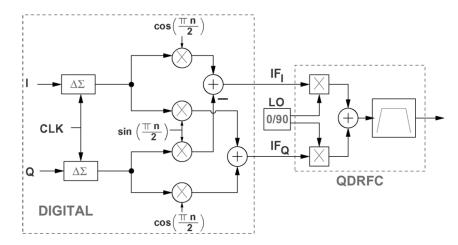

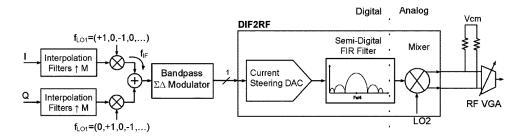

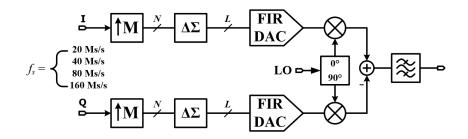

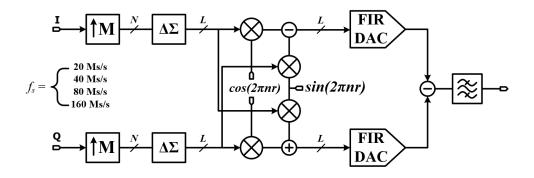

| 3.10 | Block diagram of the digital quadrature mixer based on LPF $\Delta\Sigma$ modulator in [Fra+09] .         | 24 |

| 3.11 | Block diagram of the DDRM in [Elo+07]                                                                     | 25 |

| 3.12 | Block diagram of the digital-IF direct conversion transmitter in [JS07]                                   | 26 |

| 3.13 | Block diagram of the digital-IF transmitter with embedded FIR filtering RF DAC in                         |    |

|      | [Tal+08]                                                                                                  | 27 |

| 3.14 | Block diagram direct conversion transmitter architecture for IEEE 802.11ac based on                       |    |

|      | LPF FIR DAC                                                                                               | 32 |

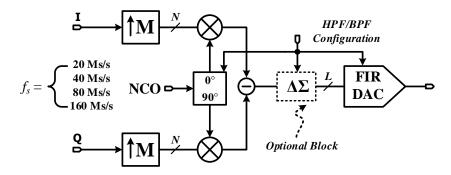

| 3.15 | Block diagram direct conversion transmitter architecture with upconverted $\Delta\Sigma$ input to a    |    |

|------|--------------------------------------------------------------------------------------------------------|----|

|      | BPF FIR DAC. <i>r</i> is ratio of $f_{IF}$ to $f_{CLK}$                                                | 33 |

| 3.16 | Block diagram of digital-IF transmitter architecture based on $\Delta\Sigma$ BPF/HPF FIR DAC $$ .      | 33 |

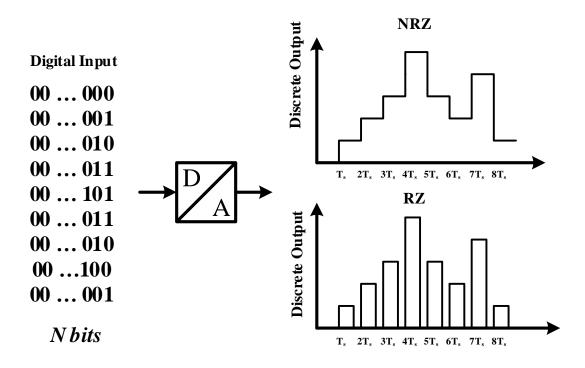

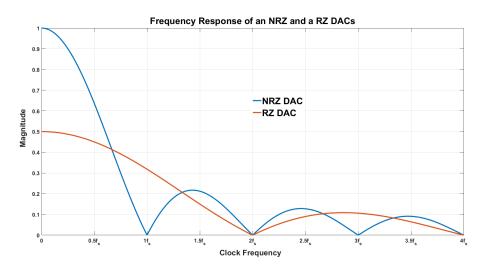

| 4.1  | Time domain operation of a DAC                                                                         | 36 |

| 4.2  | Frequency domain operation of a DAC                                                                    | 36 |

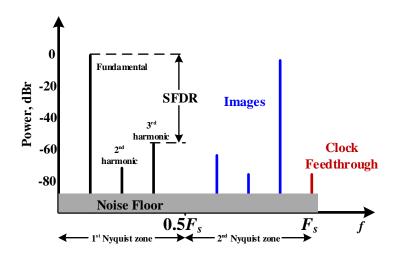

| 4.3  | Metrics of the dynamic performance of a DAC                                                            | 38 |

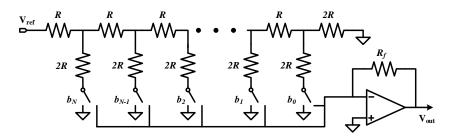

| 4.4  | A $N - bit$ R-2R resistance ladder DAC                                                                 | 39 |

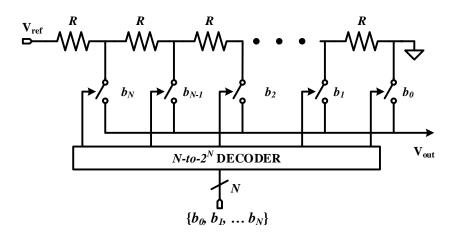

| 4.5  | A $N$ – <i>bit</i> resistor string DAC                                                                 | 40 |

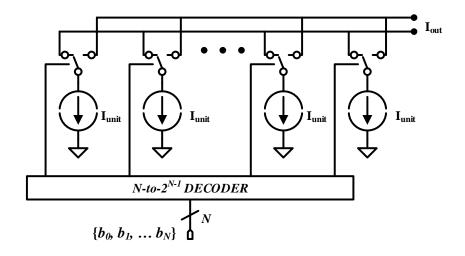

| 4.6  | A thermometric current steering DAC                                                                    | 40 |

| 4.7  | A segmented current steering DAC                                                                       | 41 |

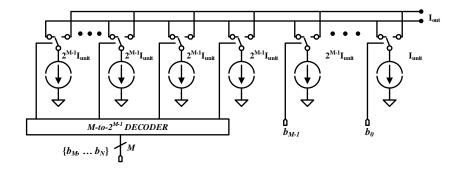

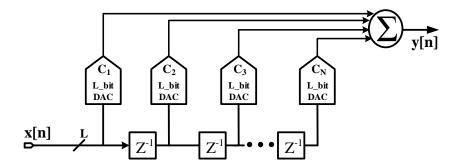

| 4.8  | A general <i>L</i> -bit, <i>N</i> -tap FIR DAC architecture                                            | 43 |

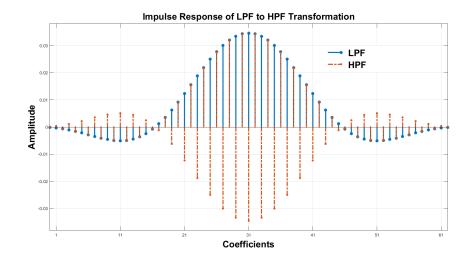

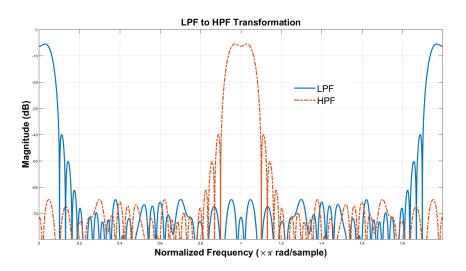

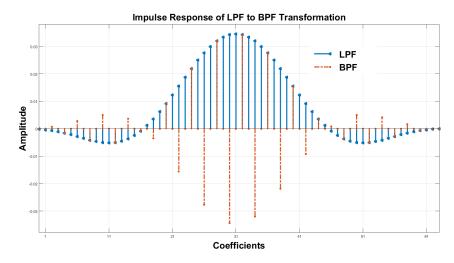

| 4.9  | Impulse response of LPF FIR and its frequency translated HPF version                                   | 45 |

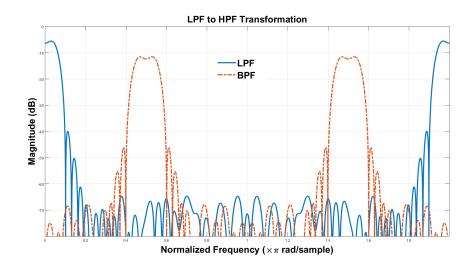

| 4.10 | Magnitude response of LPF FIR and its frequency translated HPF version                                 | 45 |

| 4.11 | Impulse response of LPF FIR and its frequency translated BPF version                                   | 46 |

| 4.12 | Magnitude response of LPF FIR and its frequency translated BPF version                                 | 47 |

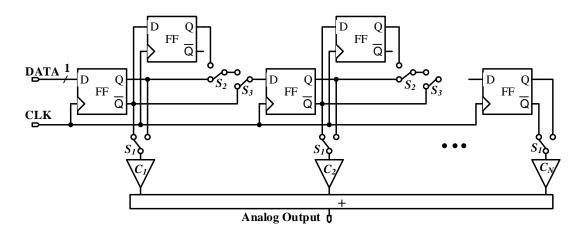

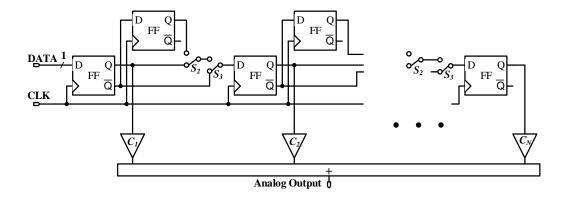

| 4.13 | Transformation of a 1-bit FIR DAC from LPF to BPF and HPF using a configurable                         |    |

|      | delay line                                                                                             | 47 |

| 4.14 | An optimized configurable delay line with only $2(N - 1)$ switches and $2N - 1$ delay cells.           | 48 |

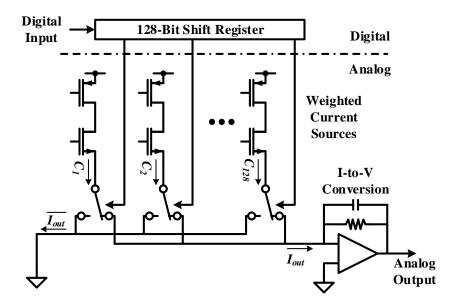

| 4.15 | Current-mode FIR DAC architecture in [SW93]                                                            | 50 |

| 4.16 | Current steering FIR DAC architecture in [AR01]                                                        | 51 |

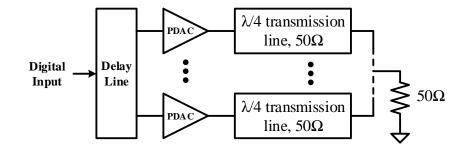

| 4.17 | General structure of the reconfigurable bandpass FIR power DAC architecture in [Fla+08]                | 52 |

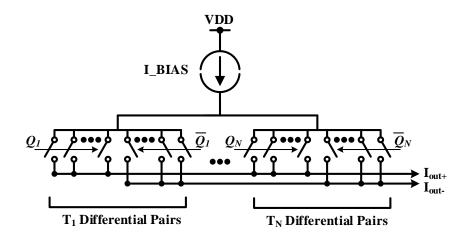

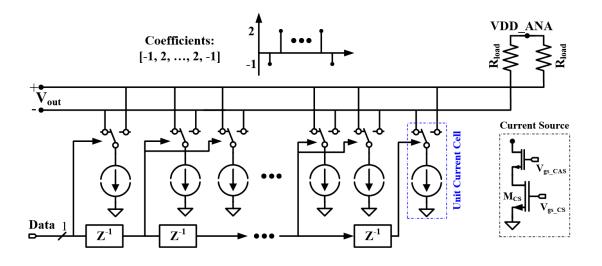

| 4.18 | Current-steering structure for implementing a FIR DAC                                                  | 53 |

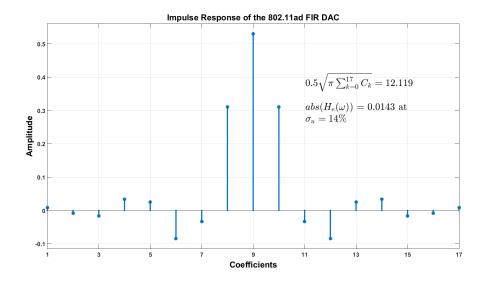

| 4.19 | Impulse response of the 802.11ad FIR DAC. The values from Equation (4.11)                              | 55 |

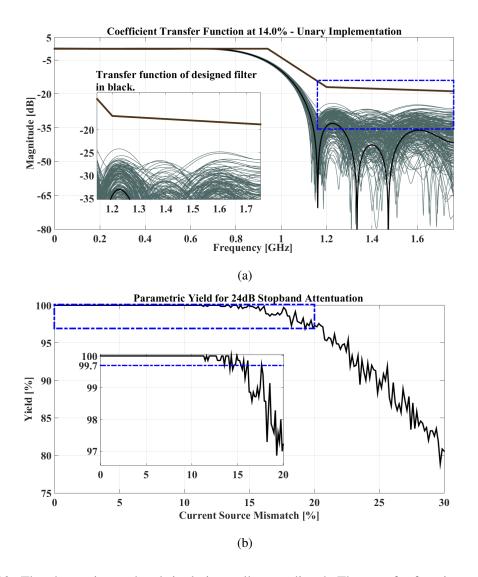

| 4.20 | The change in passband ripple is small as predicted. The transfer function can withstand               |    |

|      | coefficient mismatches up to 14%, and still fulfill the stopband attenuation with at least 5           |    |

|      | dB margin. The percentage yield is plotted against random coefficient mismatch of unary                |    |

|      | current sources with coefficients realized as a sum of independent unary current sources.              | 56 |

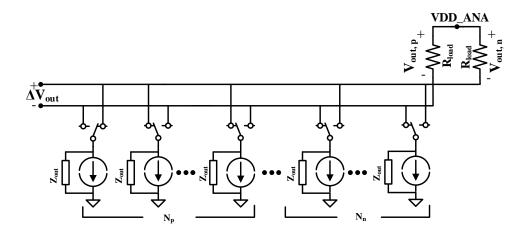

| 4.21 |                                                                                                        | 57 |

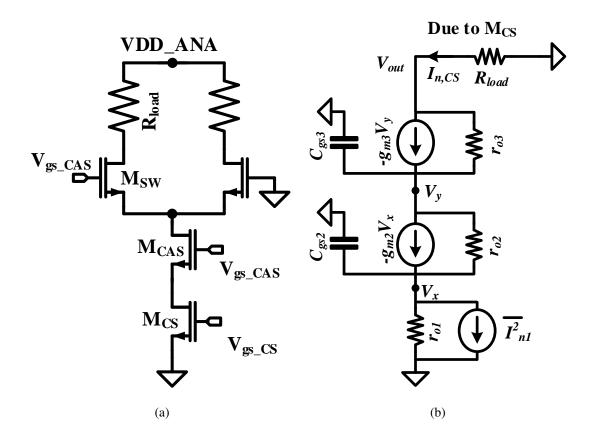

| 4.22 | a) Differentially switched cascode current source, b) Small signal model to find the                   |    |

|      | output-referred noise due to $\overline{I}_{n1}$                                                       | 60 |

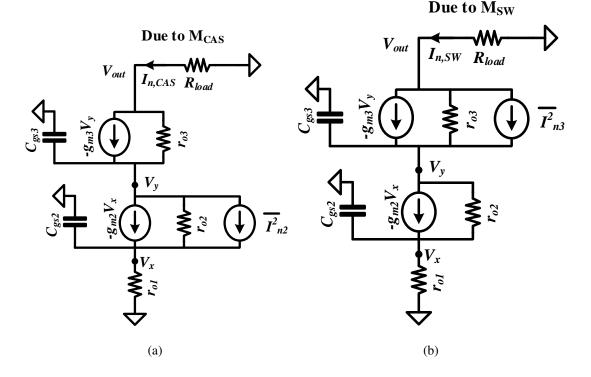

| 4.23 | Small signal model to find the output-referred noise due a) $\overline{I}_{n2}$ b) $\overline{I}_{n3}$ | 61 |

| 5.1  | The transmit masks of the IEEE 802.11ac and IEEE 802.11ad standards                                    | 67 |

| 5.2  | 160 MHz Baseband Signal at 802.11ac Transmitter Input                                                  | 69 |

| 5.3  | Poposed transmitter architecture for IEEE 802.11ac/ad standards and the DSP part of the                 |    |

|------|---------------------------------------------------------------------------------------------------------|----|

|      | 802.11ac                                                                                                | 71 |

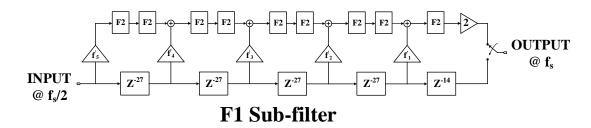

| 5.4  | Schematic of the multiplierless half-band filter with coefficients of sub-filter F1 shown $\ .$         | 73 |

| 5.5  | Schematic of the sub-filter F2 with its 14 long coefficients                                            | 73 |

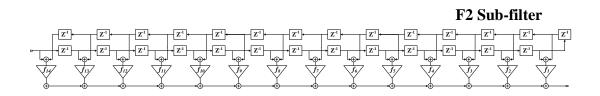

| 5.6  | The frequency responses of the main interpolation by two half-band filter and its sub-filters           | 74 |

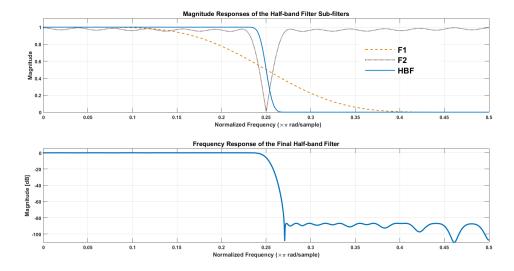

| 5.7  | Signal at the Output of Half-band Filters for 160 MHz Input                                             | 75 |

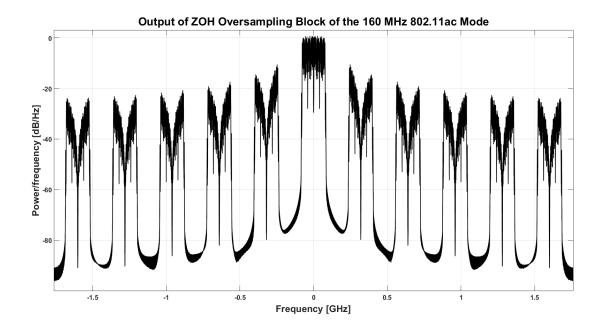

| 5.8  | Output of Zero-Order-Hold for 160 MHz Baseband Input                                                    | 75 |

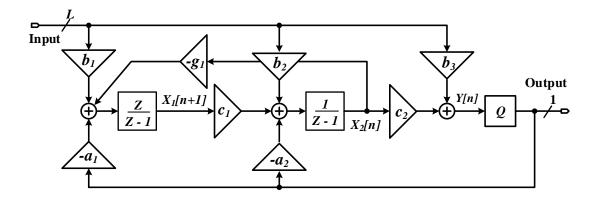

| 5.9  | Schematic of a 3 <sup>rd</sup> -order, 1-bit Delta-Sigma modulator with CRFB topology                   | 76 |

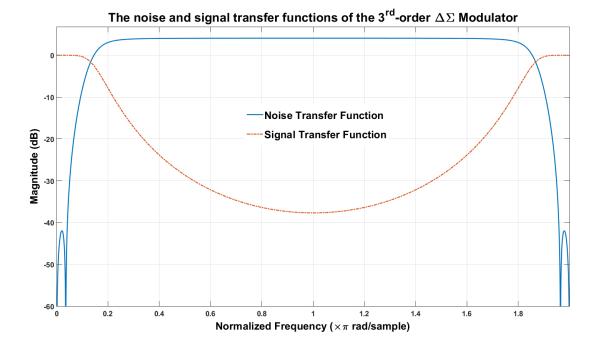

| 5.10 | Noise and signal tranfer functions of the 3 <sup>rd</sup> -order, 1-bit Delta-Sigma modulator with      |    |

|      | CRFB topology                                                                                           | 76 |

| 5.11 | The output of the 802.11ad FIR DAC for 6-bit quantized and 16-bit quantized coeffi-                     |    |

|      | cients. The output fulfills the transmit mask requirements with more than 15dB margin                   | 77 |

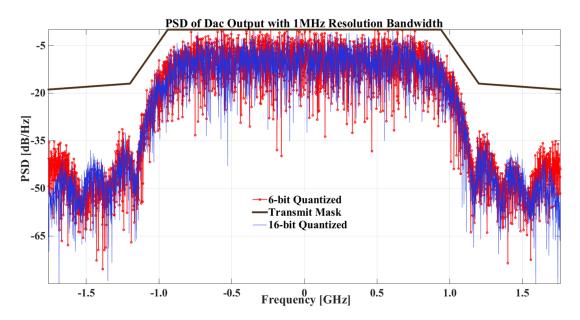

| 5.12 | The FIR DAC filter roll-off cancels the rising quantization noise from the $\Delta\Sigma$ -modulator    |    |

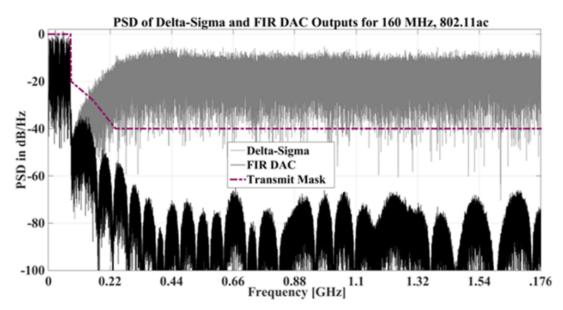

|      | output in the 160MHz mode of the 802.11ac                                                               | 78 |

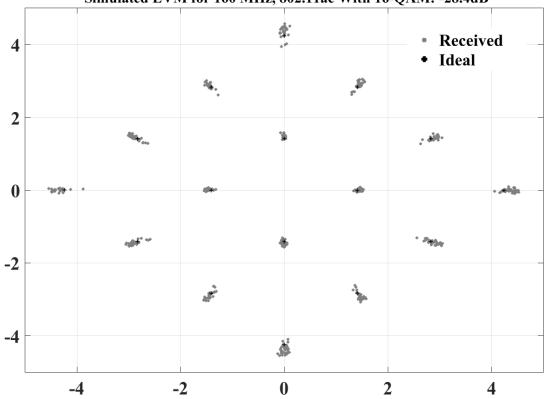

| 5.13 | Simulated EVM with 16-QAM modulation in the 160MHz mode of the 802.11ac                                 | 79 |

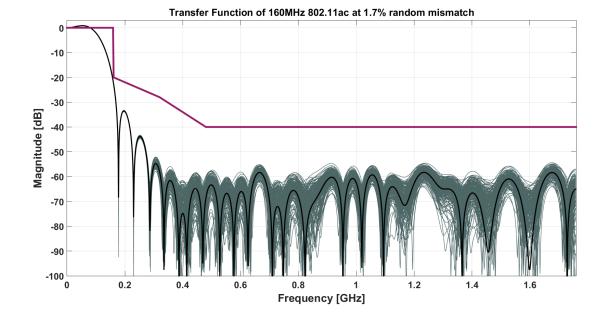

| 5.14 | The transfer function of the 160MHz of the 802.11ac mode with a unit coefficient mis-                   |    |

|      | match of 1.7% standard deviation.                                                                       | 81 |

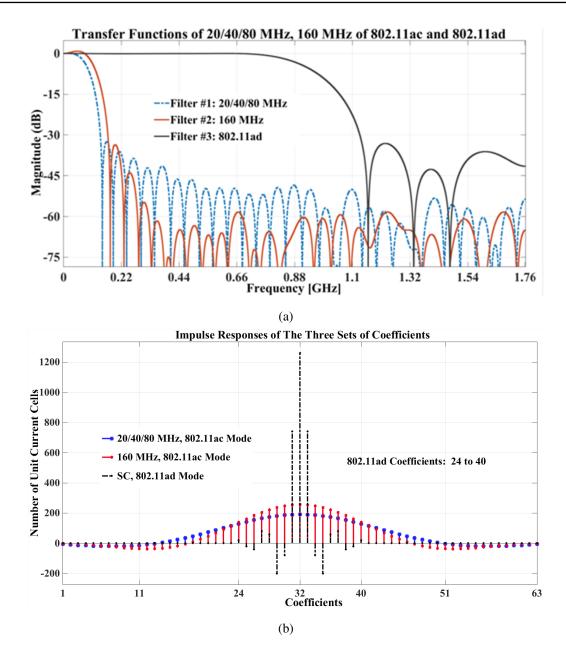

| 5.15 | The transfer functions and impulse responses of the 20/40/80 MHz, 160 MHz of the                        |    |

|      | 802.11ac and the LP SC 802.11ad mode. The samples in the impulse responses are                          |    |

|      | scaled according to the number of unit coefficient elements required to implement each                  |    |

|      | coefficient                                                                                             | 82 |

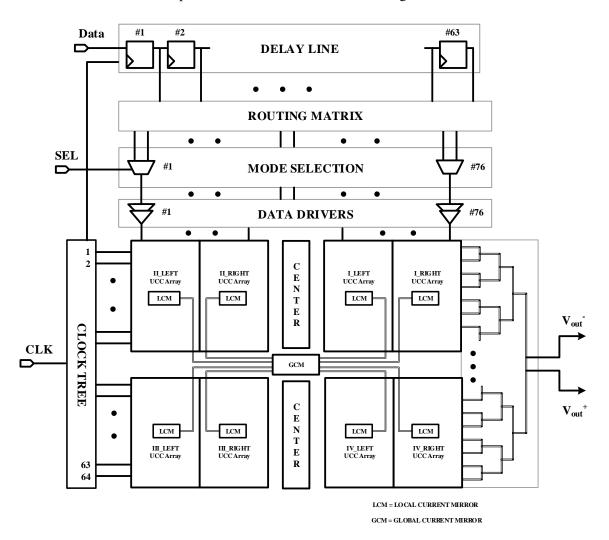

| 6.1  | FIR DAC block diagram                                                                                   | 86 |

| 6.2  | A Pseudo double common-centroid placement for UCC fo FIR DAC coefficients. The                          |    |

|      | blue shaded coefficients in the left of the impulse response are placed in the outer sections           |    |

|      | of each quadrant, and those in green inside. The unmatched center tap is placed in all                  |    |

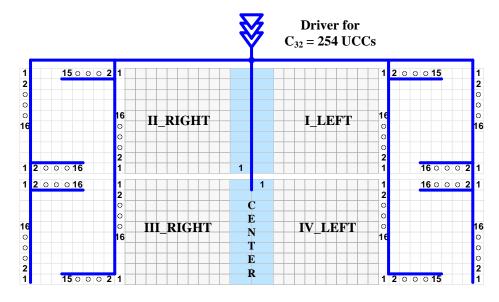

|      | quadrants                                                                                               | 88 |

| 6.3  | The placement of the UCCs in II_LEFT and II_RIGHT of the UCC array. Two co-                             |    |

|      | efficients, $C_{31}$ and $C_{33}$ , equidistant from the center tap, $C_{32}$ , of the 802.11ac impulse |    |

|      | response are highlighted. Two fine-tuning 802.11ad only coefficients, $C_{68}$ and $C_{72}$ , are       |    |

|      | also highlighted. They are also equidistant from the center tap, $C_{70}$ , of the fine-tuning          |    |

|      | coefficient set.                                                                                        | 90 |

| 6.4  | Systematic error differences between even valued coefficients left and right of the center              |    |

|      | tap                                                                                                     | 91 |

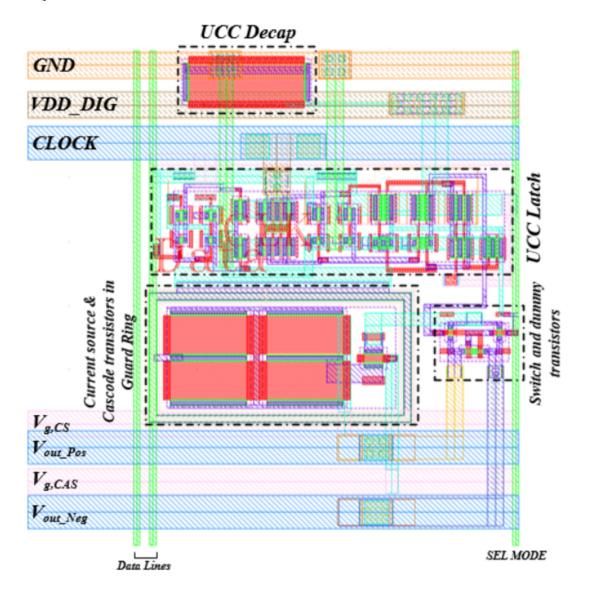

| 6.5  | FIR DAC floorplan. The current mirrors are local and global—LCM and GCM. The data                 |     |

|------|---------------------------------------------------------------------------------------------------|-----|

|      | is propagated from the top starting from 63-flip-flop delay line, to 76-multiplexers mode         |     |

|      | selection, then to 76 drivers. The clock tree has 64-rows and the output is obtained from         |     |

|      | differential outputs of a 64-row tree                                                             | 94  |

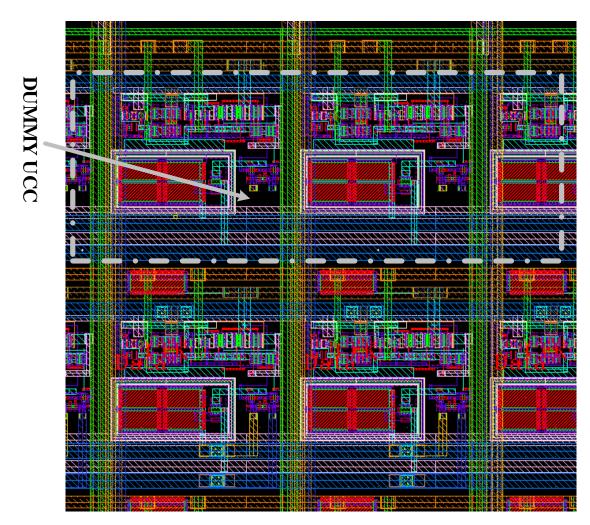

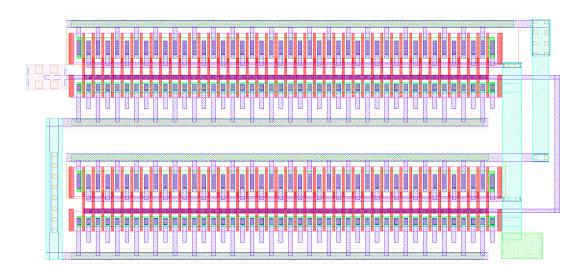

| 6.6  | A section of the UCC array. Dummy UCCs surround the edge of the array as shown.                   |     |

|      | The data, clock, output, bias and select signal lines of the UCC are routed such that the         |     |

|      | array area is exactly the sum of the areas of the UCCs.                                           | 95  |

| 6.7  | FIKRDAC Layout                                                                                    | 97  |

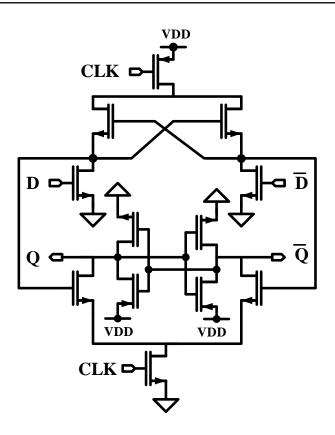

| 6.8  | A semi-static Flip-Flop for the delay line of the FIR DAC                                         | 98  |

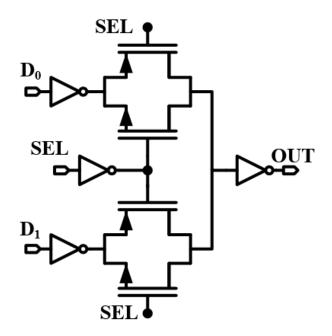

| 6.9  | A 2-by-1 multiplexer for mode selection                                                           | 99  |

| 6.10 | This shows how the coefficients of 802.11ad are created from 802.11ac. The number at              |     |

|      | the top indicate taps of the 802.11ad. Each tap is drives the taps 802.11ac taps listed           |     |

|      | below it and the taps for fine-tuning from 64–76                                                  | 100 |

| 6.11 | The layout of the digital delay line, routing matrix and the mode selection blocks. One           |     |

|      | of the inputs of the Muxs is directly connected to the flip-flops whereas the other is            |     |

|      | connected according to the matrix shown above in the table                                        | 100 |

| 6.12 | The placement of 254 UCCs of coefficient 32 and a depiction of the routing of the data            |     |

|      | line from driver to the UCCs                                                                      | 101 |

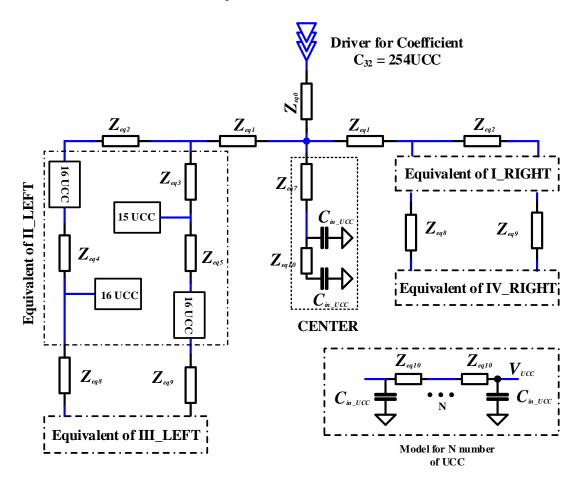

| 6.13 | Model of equivalent impedance of routed data lines for coefficient 32 with 254 UCCs $$ .          | 102 |

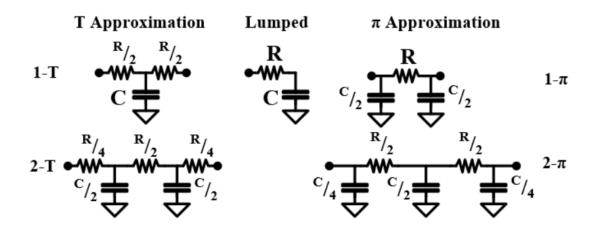

| 6.14 | RC interconnect models that can be used for fast, less accurate estimation of delay $\ldots$ .    | 103 |

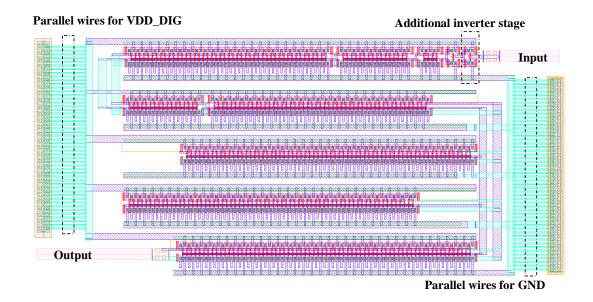

| 6.15 | The layout view of the a five-stage driver used for the biggest coefficients in the center of     |     |

|      | the 802.11ac impulse response. Additional stage inserted not to invert the data. Supply           |     |

|      | connected using parallel thin wires to ensure low current density                                 | 105 |

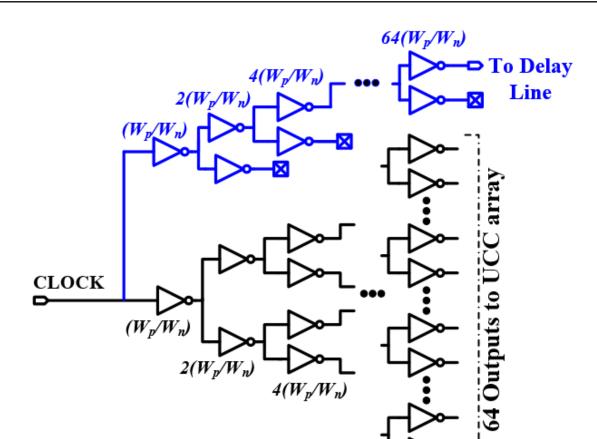

| 6.16 | The clock is distributed with a seven stage clock tree to the UCC array, and a single leaf        |     |

|      | of this tree to the delay line. The inverters in the tree are sized have a fan out of 4. This     |     |

|      | is kept in the inverter chain to the delay line using dummy inverters. $\ldots$                   | 106 |

| 6.17 | The layout view of the final stage buffers of the clock tree. Each PMOS and NMOS are              |     |

|      | sized $2^6$ times the first stage transistors. The fingers are arranged as such so that the clock |     |

|      | tree outputs of each of the 64 rows are routed straight to the UCC array with short wires         |     |

|      | and with minimum distance between the rows of the UCC array. $\ldots$                             | 107 |

| 6.18 | The layout view of the clock tree                                                                 | 107 |

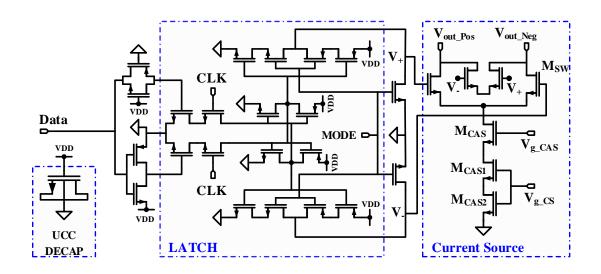

| 6.19 | Transistor level schematic of a Unit Current Cell which works in 802.11ac mode and is             |     |

|      | controlled by <i>SEL</i> signal to turn-off in 802.11ad                                           | 108 |

| 6.20 | The layout view of a unit current cell used in both modes                                         | 109 |

**List of Figures**

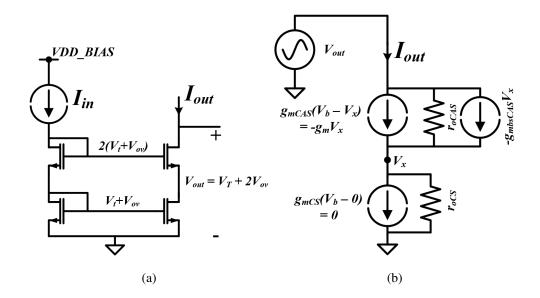

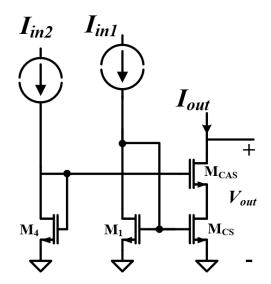

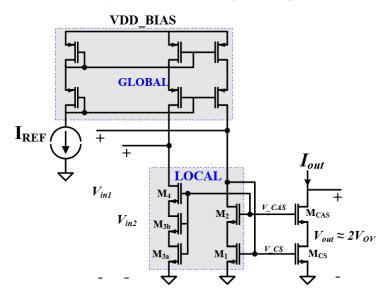

| 6.2 | A simple Cascode current mirror and small signal analysis of its output resistance 111                       | L        |

|-----|--------------------------------------------------------------------------------------------------------------|----------|

| 6.2 | 22 Cascode current mirror biased with two branches                                                           | L        |

| 6.2 | 23 Sooch cascode current mirror for local and global biasing                                                 | <u>)</u> |

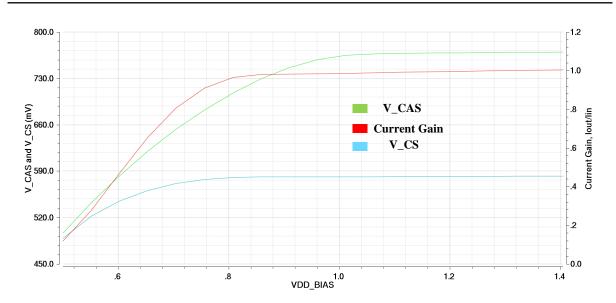

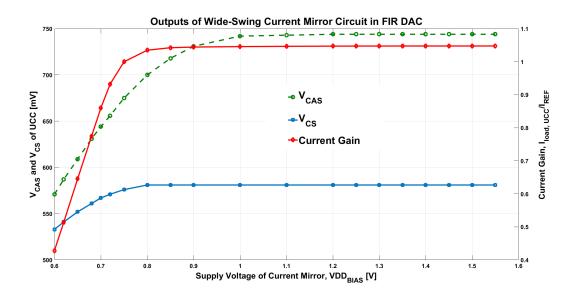

| 6.2 | A simulation of minimum bias VDD that ensures flat current gain                                              | ł        |

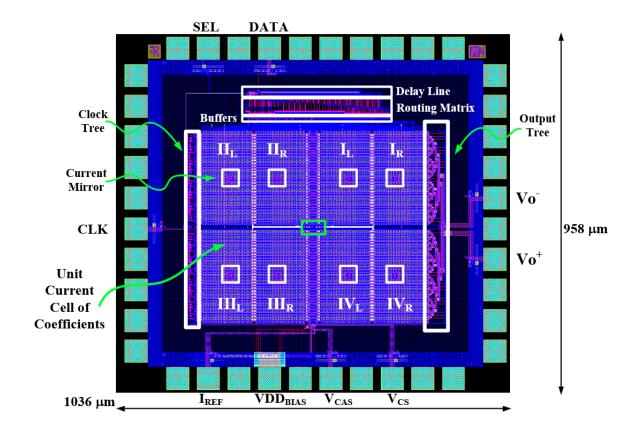

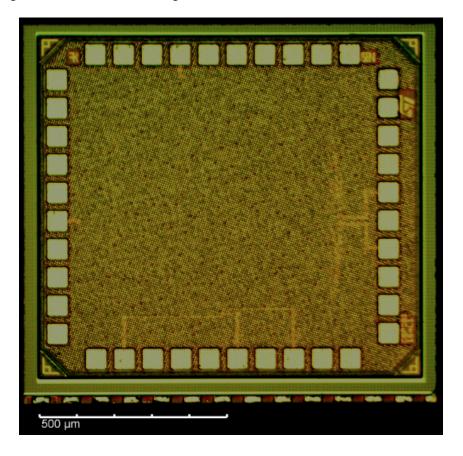

| 7.1 | Configurable FIR DAC prototype die micrograph. It is fabricated in ST 28nm CMOS FDSOI.                       | 5        |

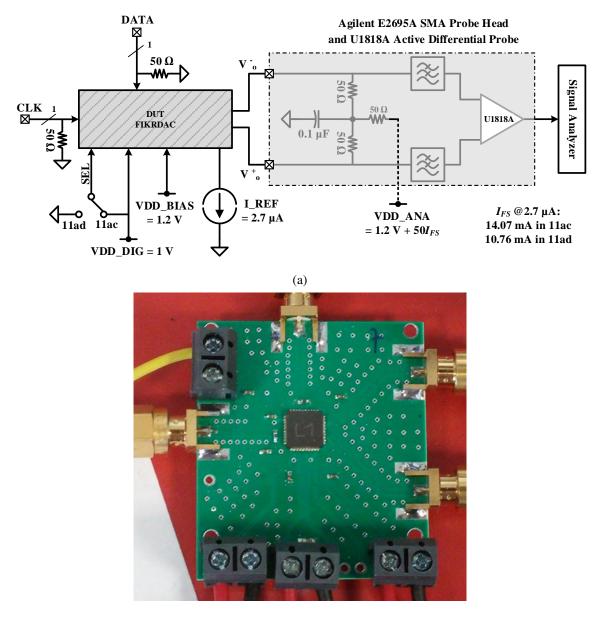

| 7.2 | 2 Schematic of test board and the test board with the packaged die on board. The high                        |          |

|     | speed input and outputs are connected with SMAs, and power connectors were used for                          |          |

|     | the static signals                                                                                           | 7        |

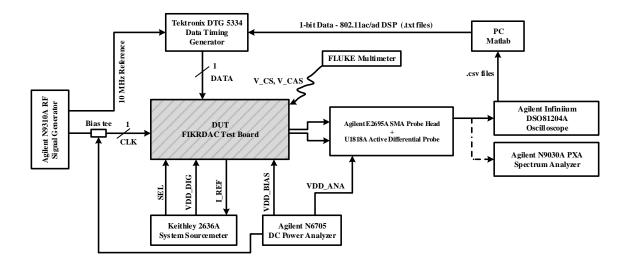

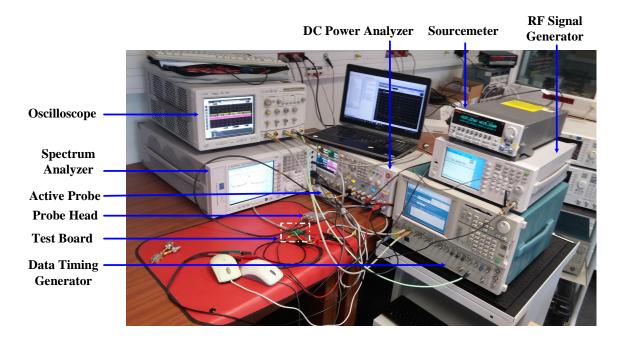

| 7.3 | Instruments used in the measurement Setup                                                                    | 3        |

| 7.4 | The test bench                                                                                               | 3        |

| 7.5 | The transmitter architecture used to generate 802.11ac data for the chip characterization . 119              | )        |

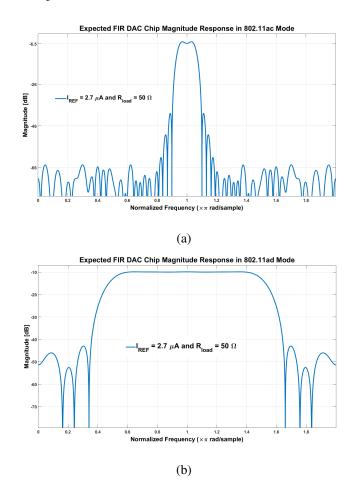

| 7.6 | 5 Transfer functions of the 802.11ac and 802.11ad modes with reference current $2.7\mu A$                    |          |

|     | and load resistance of 50 $\Omega$ . The passband is expected to be attentuated by around 6.5 dB             |          |

|     | and 10 dB in the 802.11ac and 802.11ad modes respectively                                                    | )        |

| 7.7 | The biasing voltages of the current source of the UCC, and the current gain, $\frac{I_{UCC}}{I_{REF}}$ , for |          |

|     | different values of the biasing voltage supply. The current gain plat                                        | L        |

| 7.8 | Power consumption of the digital circuits, supplied by $VDD_{DIG}$ , of the FIR DAC chip at                  |          |

|     | different clock frequencies in the 802.11ac mode and in the 802.11ad modes                                   | )        |

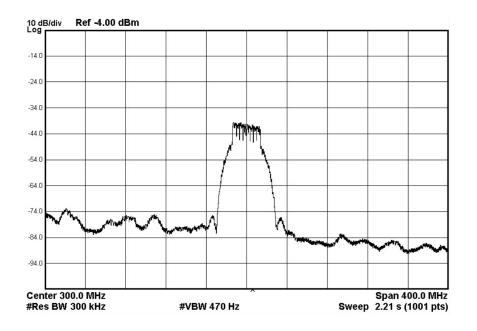

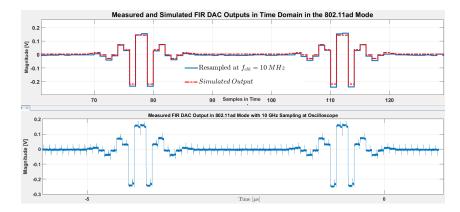

| 7.9 | Output of the FIR DAC for a $\Delta\Sigma$ input in the 802.11ac mode. It is measured at a clock             |          |

|     | frequency of 600 MHz                                                                                         | 5        |

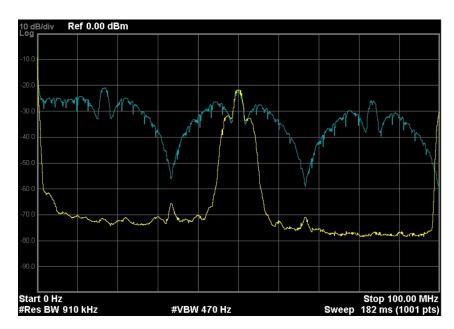

| 7.1 | 0 Output of the FIR DAC for a thrice oversampled $\Delta\Sigma$ input in the 802.11ac mode. It is            |          |

|     | measured at a clock frequency of 100 MHz                                                                     | 5        |

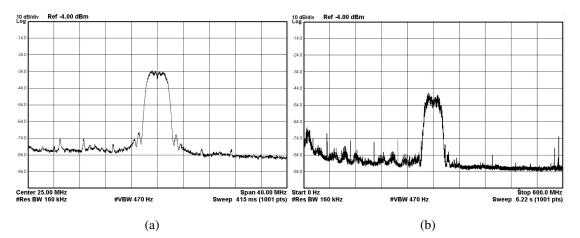

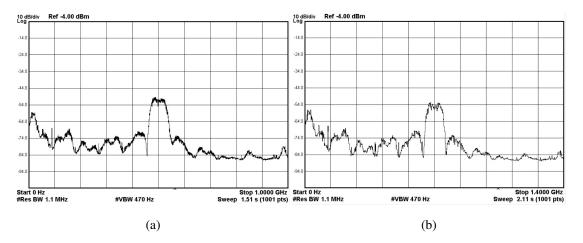

| 7.1 | 1 Filtered output at 50 MHz and 600 MHz clock of a PRBS input generated from the DTG 126                     | 5        |

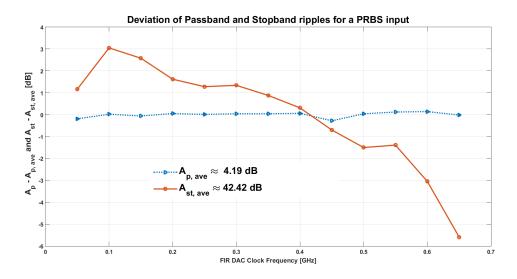

| 7.1 | 2 Passband AND Stopband ripple deviations for a PRBS input in the 802.11ac mode 127                          | 7        |

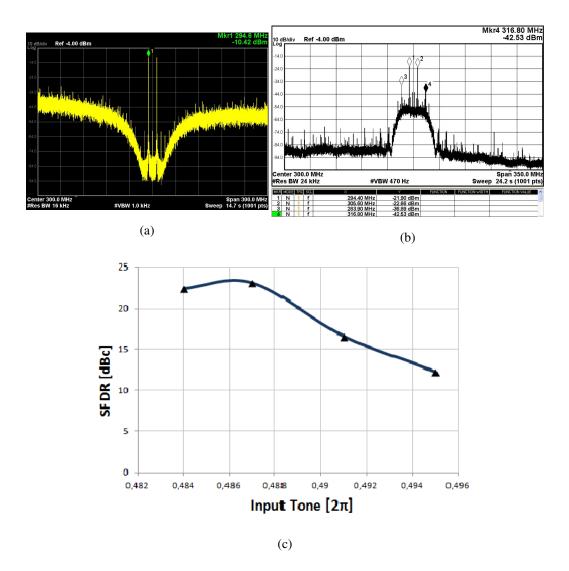

| 7.1 | 3 The signal used as an input for this experiment, b) The measured plot, and c) SFDR in                      |          |

|     | dBc in the bandwidth of the FIR DAC for a clock frequency of 600 MHz                                         | 3        |

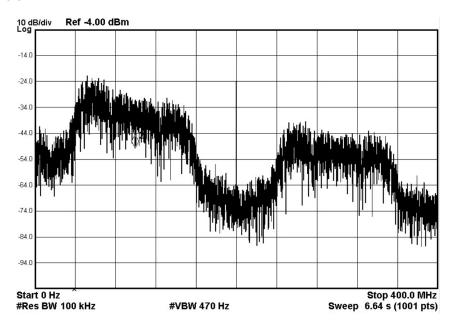

| 7.1 | 4 Filtered output at 200 MHz clock in the 802.11ad mode for a PRBS input generated from                      |          |

|     | the DTG                                                                                                      | )        |

| 7.1 | 5 Filtered output at 200 MHz clock in the 802.11ad mode for a PRBS input generated from                      |          |

|     | the DTG                                                                                                      | )        |

| 7.1 | 6 Time domain measurement for an input sequence at a clock frequency of 10 MHz 130                           | )        |

| 7.17 | Filtered output at 1 GHz and 1.4 GHz clock frequencies of a PRBS input generated from             |     |

|------|---------------------------------------------------------------------------------------------------|-----|

|      | the DTG                                                                                           | 131 |

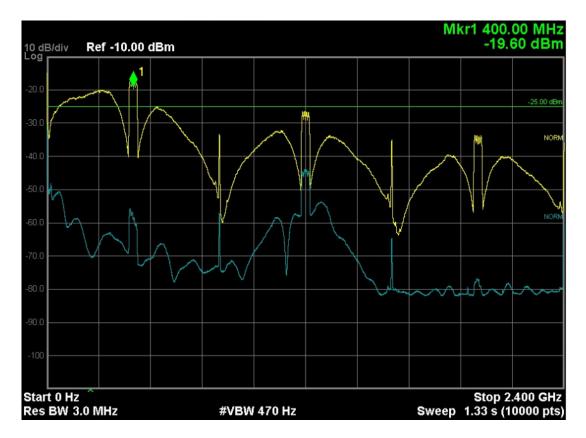

| 7.18 | Output of the FIR DAC for a thrice oversampled $\Delta\Sigma$ input in the 802.11ac mode. It is   |     |

|      | measured at a clock frequency of 2.4 GHz. The input digital pattern DATA from the data            |     |

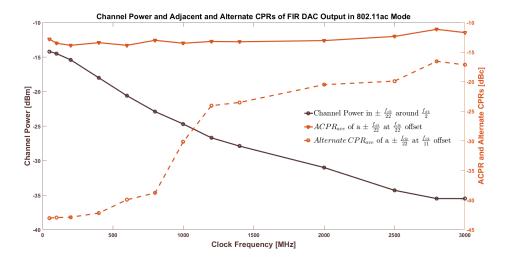

|      | timing generator is shown in yellow, and the measured output in blue                              | 132 |

| 7.19 | Channel power, ACPR, and alternate CPR measurements across different clock frequen-               |     |

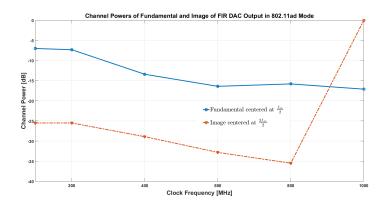

|      | cies for a $\Delta\Sigma$ output pattern as an input to the FIR DAC in the 802.11ac mode          | 133 |

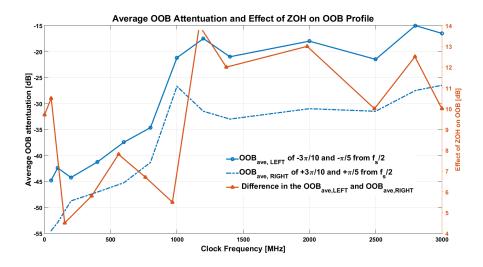

| 7.20 | Out-of-band profile of the fundamental and image stop bands measured at two points for            |     |

|      | a $\Delta\Sigma$ output signal as an input. The effect of ZOH clocking on these two stop bands is |     |

|      | also shown.                                                                                       | 133 |

# **List of Tables**

| 3.1 | Summary of the reviewed digital transmitters                                                 | 28  |

|-----|----------------------------------------------------------------------------------------------|-----|

| 3.2 | A summary of RF DACs for cable TV transmitters                                               | 30  |

| 4.1 | Comparison among the three structures of an FIR DAC                                          | 44  |

| 4.2 | Switch states of delay line for frequency translation of the 1-bit FIR DAC                   | 48  |

| 5.1 | Summary of the Specifications of the 802.11ac and 802.11ad standards                         | 67  |

| 5.2 | Frequency Planning for IEEE 802.11ac/ad Transmitter                                          | 72  |

| 5.3 | Summary of the specifications of the multi-standard FIR DAC                                  | 83  |

| 6.1 | Weights of the 802.11ad mode fine-tuning coefficients                                        | 99  |

| 7.1 | Power Consumption of the FIR DAC chip in two modes                                           | 123 |

| 7.2 | Comparison with the state of the art in digital-to-RF converters of all-digital transmitters | 134 |

| 7.3 | Performance summary of the configurable FIR DAC                                              | 135 |

# Nomenclature

### Symbols

| $\omega \& f$   | Angular frequency & frequency            |

|-----------------|------------------------------------------|

| $\sigma$        | Standard Deviation                       |

| $A_p$           | Passband Ripple                          |

| $A_{st}$        | Stopband Ripple                          |

| fout            | Output Frequency                         |

| $f_s$           | Sampling rate, also clock frequency      |

| $g_m$           | Transconductance                         |

| $g_{ds} \& r_o$ | Drain-to-source conductance & resistance |

| L               | Transistor length                        |

| Pout            | Output Power                             |

| $V_{OV}$        | Overdrive voltage                        |

| W               | Transistor width                         |

### **Abbreviations**

| 1 <b>G</b>   | First Generation Wireless Communication                               |

|--------------|-----------------------------------------------------------------------|

| <b>3</b> G   | Third Generation Wireless Communication                               |

| <b>4</b> G   | Fourth Generation Wireless Communication                              |

| 5G PPP       | 5G Infrastructure Public Private Partnership                          |

| <b>5GNOW</b> | Fifth Generation Non-Orthogonal Waveforms for Asynchronous Signalling |

| 5G           | Fifth Generation Wireless Communication                               |

| ACPR         | Adjacent Channel Power Ratio                                          |

| AM           | Amplitude Modulation                                                  |

| ASK          | Amplitude Shift Keying                                                |

| BPF          | Band Pass Filter                                                      |

| BPSK         | Binary Phase Shift Keying                                             |

| BW           | Signal Bandwidth                                                      |

| CDMA         | Code Division Multiple Access                                         |

| CIFB         | Cascade-of-Integrators, Feedback Form                                 |

| CMOS         | Complementary Metal Oxide Semiconductor                               |

| CRFB   | Cascade-of-Resonators, FeedBack Form                                                |  |

|--------|-------------------------------------------------------------------------------------|--|

| CVSL   | Cascode Voltage Switch Logic                                                        |  |

| DAC    | Digital to Analog Converter                                                         |  |

| DBPSK  | Differential Binary Phase Shift Keying                                              |  |

| DCO    | Digitally Controlled Oscillator                                                     |  |

| DC     | Direct Current                                                                      |  |

| DIDIMO | Direct Digital Modulation                                                           |  |

| DMG    | Directional Multi Gigabit                                                           |  |

| DNL    | Differential Non-Linearity                                                          |  |

| DR     | Dynamic Range                                                                       |  |

| DSP    | Digital Signal Processing                                                           |  |

| EDGE   | Enhanced Data rates for GSM Evolution                                               |  |

| ETSI   | Mobile and wireless communications Enablers for the Twenty-twenty Information Soci- |  |

|        | ety                                                                                 |  |

| EVM    | Error Vector Magnitude                                                              |  |

| FDMA   | Freqeuncy Division Multiple Access                                                  |  |

| FDSOI  | Fully Depleted Silicon On Insulator                                                 |  |

| FEC    | Forward Error Correction                                                            |  |

| FIR    | Finite Impulse Response                                                             |  |

| FM     | Frequency Modulation                                                                |  |

| FSK    | Frequency Shift Keying                                                              |  |

| GCD    | Greatest Common Divisor                                                             |  |

| GPS    | Global Positioning System                                                           |  |

| GSM    | Global System for Communications                                                    |  |

| HDMI   | High Definition Multimedia Interface                                                |  |

| HD     | Harmonic Distortion                                                                 |  |

| HPF    | High Pass Filter                                                                    |  |

| I/Q    | Inphase-Quadrature                                                                  |  |

| IDFT   | Inverse Discrete Fourier Transform                                                  |  |

| IFFT   | Inverse Fast Fourier Transform                                                      |  |

| IF     | Intermediate Frequency                                                              |  |

| IIR    | Infinite Impulse Response                                                           |  |

| IMD3   | Third-Order Intermodulation                                                         |  |

| INL    | Integral Non-Linearity                                                              |  |

| ISI     | Intersymbol Interference                   |

|---------|--------------------------------------------|

| LO      | Local Oscillator                           |

| LP      | Low Power                                  |

| LSB     | Least Significant Bit                      |

| LTE-AG  | Long Term Evolution Advanced               |

| MAC     | Media Access Control                       |

| MCS     | Modulation and Coding Scheme               |

| MIMO    | Multiple Input and Multiple Output         |

| MU-MIMO | Multi-User MIMO                            |

| NRZ     | Non-Return to Zero                         |

| NTF     | Noise Transfer Function                    |

| OFDM    | Orthogonal Frequency Division Multiplexing |

| OSR     | Oversampling Ratio                         |

| PAPR    | Peak to Average Ratio                      |

| PA      | Power Amplifier                            |

| PDAC    | Power DAC                                  |

| PHY     | Physical layer                             |

| PLL     | Phase Locked Loop                          |

| PM      | Phase Modulation                           |

| PRBS    | Pseudo-Random Bit Stream                   |

| PSD     | Power Spectral Density                     |

| PSK     | Phase Shift Keying                         |

| QAM     | Quadrature Amplitude Modulation            |

| QFN     | Quad Flat Non Leaded                       |

| QPSK    | Quadrature Phase Shift Keying              |

| RAT     | Radio Access Technology                    |

| RRC     | Root Raised Cosine                         |

| RZ      | Return to Zero                             |

| SC      | Single Carrier                             |

| SDR     | Signal to Distortion Ratio                 |

| SFDR    | Spurious Free Dynamic Range                |

| SNR     | Signal to Noise Ratio                      |

| STA     | Station                                    |

| TDMA    | Time Division Multiple Access              |

| TPSC  | True Single Phase Clock                         |

|-------|-------------------------------------------------|

| UCC   | Unit Current Cell                               |

| UMTS  | Universal Mobile Telecommunications System      |

| VCO   | Voltage Controlled Oscillator                   |

| VHT   | Very High Throughput                            |

| WCDMA | Wideband Code Division Multiple Access          |

| WENDY | WiGig FlExible TraNsceiver ADvanced SYstem      |

| WiGig | Wireless Gigabit                                |

| WiGig | Wireless Gigabit                                |

| WiHD  | Wireless High Definition                        |

| WiMAX | Worldwide Interoperability for Microwave Access |

| WLAN  | Wireless Local Area Network                     |

| ZOH   | Zero Order hold                                 |

# Introduction

#### **1.1** The Scope of this Study

The aim of this work has been to analyze, design, and demonstrate a digital-to-IF/RF converter circuit that can be configured for processing both high resolution, medium bandwidth and low resolution, wideband baseband signals of recent WiFi standards. Initially, FIR DACs were proposed as ideal blocks to achieve the required design objectives, such as low power consumption and small area, of such a mixed-signal circuit block. Along the course of this PhD work, however, the work has evolved to study and determine how much a performance can be expected from the digital signal processing blocks in a baseband of such transmitters.

The initial goal of this work was to validate at system-level a transmitter baseband architecture for processing IEEE 802.11ac and IEEE 802.11ad signals. Subsequently, given time constraints, it was important to demonstrate a key circuit block, by measuring a CMOS implementation, of the mulit-standard transmitter architecture proposed. A configurable FIR DAC was identified as the bottleneck in the transmitter chain as it determines the maximum achievable carrier frequency and the corresponding signal bandwidth, spectral purity of the analog output, and the lowest power consumption and circuit area that can be targeted.

Even though the solid literature in the area of traditional multi-bit DAC has eased the burden of derivation required in the design of a configurable multi-standard FIR DAC, the scarcity of works in the specific area of high speed configurable FIR DACs required analysis of each design decision and has led to some original contributions.

A top-down research methodology was followed during implementation of the FIR DAC chip. The specifications for the baseband transmitter system were based largely on IEEE 802.11ac and IEEE 802.11ad transmitter standard requirements. Specification for each block in the baseband chain, mainly the FIR DAC block, were then drawn; and those were translated as targets for the parameters of the FIR DAC circuit. Then, simulation at transistor, layout and extracted abstraction levels were carried out until the desired margin was respected.

#### **1.2 Original contributions**

These are the main original contributions of this PhD work:

- Novel digital wireless transmitter architectures based on:

- low pass filter FIR DAC

- high pass filter FIR DAC

- band pass filter FIR DAC

- System-level validation of a configurable low pass filter FIR DAC transmitter as communicated in [GFK16a]

- A semi-digital FIR DAC for LP SC 60 GHz IEEE 802.11ad as communicated in [GFK15]

- Matlab based modeling and simulation alogrithms for EVM of a IEEE 802.11ac/ad transmitter

- A delay-line of a 1-bit FIR DAC configurable for a LPF/BPF/HPF operations

- Thorough small-signal analysis of the noise-limited dynamic range of a differentially-switched cascode current source

- A novel pseudo double common centroid placement method for unary-implementation of a FIR DAC as communicated in [GFK16b]

- Analysis of its bandwidth limitation

- A novel floorplan based on this placement method

- A yield model for thermometric FIR DACs based on stopband rejection of their filtering transfer function

- Design of a prototype FIR DAC that

- is configurable for 160MHz channel bandwidth of the IEEE 802.11ac and IEEE 802.11ad standards

- proves for the first time a low power, multi-GHz operation of a 63-order 1-bit high pass filtering FIR DAC

- The prototype high pass FIR DAC chip is characterized up to a clock frequencies of 3 GHz in the 802.11ac mode, consumes 103.07 mW at 1.4 GHz, and can process passband OFDM signals as wide as 136 MHz. In the 802.11ad case, it can processes SC signals up to a bandwidth of 700 MHz at a clock frequency of 1.4 GHz and consumes 86.89 mW.

#### 1.3 Outline

The work is divided into eight chapters as follows:

- Chapter 1: introduces the problem statement the work has tried to solve. It sets the scope of the study, lists the main original contributions, and gives an outline of the dissertation.

- Chapter 2: examines the historical background of the application area of this work. It recapitulates the predictions related to the capabilities of future 5G standards, and introduces the principal challenges and solutions. The chapter puts the application of this PhD work in perspective with the predicted possible evolution of radio systems.

- Chapter 3: briefly introduces theoretical operation of a modern wireless transmitter. It reviews

digital cartesian transmitter architectures. It further delves into review of multi-modal digital transmitters architectures in recently published works. The chapter closes with a proposal of novel FIR

DAC based multi-modal transmitter architectures.

- Chapter 4: starts with basics of a traditional multi-bit DAC: its operation, specifications, and architectures. Then it follows it with a general discussion of the design challenges of L bit, N tap FIR DACs. It introduces a novel configurable delay-line for a 1-bit FIR DAC. A thorough review of published transmitter-side filtering DACs paves the way for analysis of high speed 1-bit FIR DAC design. Main performance metrics of a 1-bit current-steering FIR DAC architecture and its modeling is derived.

- Chapter 5: presents the system-level validation of the baseband of a digital transmitter based on a low pass filter FIR DAC. High level design and simulation results of each block of the transmitter are included. The chapter ends with further discussion of the high level design of a configurable FIR DAC.

- Chapter 6: details the circuit implementation of a prototype configurable FIR DAC in 28nm CMOS FDSOI. A novel pseudo double common centroid placement method, and the FIR DAC floorplan are discussed. Design of each block of the prototype converter are presented in great detail.

- Chapter 7: is where the results of the measurement of the prototype are explored. The experimental setup, the different ways by which the configurable FIR DAC is characterized are elaborated.

- Chapter 8: stipulates the main conclusions. It also extends the scope of this work by proposing plausible future research directions.

# **Wireless Communication Systems**

The aim of this chapter is to give an overview of wireless communication standards. It covers a bit of history and a bit of the expected future of communication standards. Since the focus of this work is on multi-mode DAC for multi-standard transmitters, some motivations are listed in this chapter. It starts with evolution of standards in section I. In section II, a discussion of challenges and solutions with regard to 5G networks in included. The prototype chip targets the complementarity that exists in the WiFi-WiGig use cases; it is in section 3. The chapter closes with a customary summary and conclusions section.

#### 2.1 Aggregation of Standards

Cellular technology has evolved from the analog, voice only 1G to the current Gb/s data rate LTE-A 4G standard. To accommodate this increase in throughput, the transmission frequencies has also increased from sub-GHz carrier frequency to 2–3 GHz range that is at work today. However, this increase is not totally attributed to increase in available transmission bandwidth. One technology that contributed to this increase is the evolution of access technologies from FDMA to TDMA to CDMA to contemporary access technology based on OFDM.

The same can be said of the evolution of the WLAN standards, namely WiFi. It has evolved from the early 2 Mb/s data rate local area network to the current multi-Gb/s 802.11ac/ad standards. Other standards including short distance, low power Zigbee and Bluetooth, and long distance, low data rate GPS still add their own set of requirements on the design of devices.

Therefore, the proliferation of application specific wireless communication standards have resulted in the multiple standards, multiple devices per user scenario of today. The need for design of multi-standard devices is exacerbated by the crowded spectrum, and the resulting tough out-of-band requirements. Moving to higher carrier frequency, and, thus, broader bandwidths could relax the requirements, and fulfill the increasing demand for faster communication rates. However, the challenges of designing multi-standard devices at higher carrier frequencies or broader bandwidths will be harder to overcome.

Innovation in access technologies, similar to the gains made by using OFDM, will not suffice either. A single innovation in either of transmission frequency, access technologies, channel bandwidth, or type

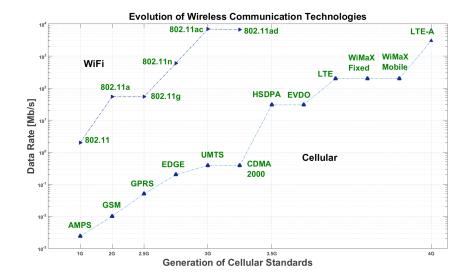

Figure 2.1: Evolution of theoretical data rates of wireless technologies from first generation networks to current giga-bit data rate 4G networks

of antenna may not satisfy the expected needs. A radical change combining all of the above solutions have a better probability of addressing the problem.

The evolution of theoretical data rates of cellular and WiFi standards through the years is plotted in Figure 2.1. The latest standards of WiFi achieve several Gb/s data rates—with the 802.11ac at 160MHz and the IEEE 802.11ad at 2.16GHz maximum channel bandwidths. The uplink and downlink data rates of the latest cellular standard also reaches Gb/s with a maximum of 20MHz channel bandwidth. There is, however, a difference in the achievable distance between these standards. For example, IEEE 802.11ad has an expected reach of less than 10 m. Future networks can be envisioned where the capabilities in both short and long distance standards are combined seamlessly for best user experience. In the next section, a brief summary of the discussion on future 5G networks is presented.

#### 2.2 Networks of the future

Current networks are not expected to support the data demand of the future. This is because of the explosive rise in user data demand coupled with the increasing number of new applications that require low latency, high data rate communications. The 2015 virtual networking index report by Cisco shows that 4G mobile networks account for 47% of mobile data traffic with just 14% of mobile connections while 3G networks contribute for 43% traffic with 34% of connections. In general, a 4G traffic takes the biggest share with 85% more traffic than a non-4G connection. It also reports an increase of more than half a billion in global mobile devices and connections in 2015. Although the growth in mobile data and

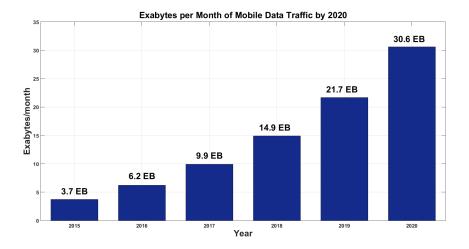

increase in mobile devices does not imply similar proportion of growth in other networks, it does show the exponential demand for faster data. The mobile data traffic growth from 2015 to 2020 is shown in Figure 2.2 [CVM16].

These exponential demands have pushed many governing bodies to plan for the networks of the future. Flagship projects such as METIS 2020 project, 5GNOW, and 5G PPP in Europe, and IMT-2020 under the International Telecommunication Union have led the way for the development and standardization of 5G networks—a generic name for the networks of 2020.

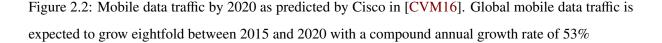

Although a clear set of requirements have not yet been developed for what the 5G networks should look like, there are some targets which show the capacity of the networks of the future. Under the IMT-2020, initiative, the expected capabilities and needed enhancement compared against the current IMT-Advanced are depicted graphically in Figure 2.3.

The METIS project, in its initial project, had also set five requirements that a mobile network in 2020 should support with the same cost and energy dissipation of contemporary networks. These are 1000x increase in mobile data throughput, 10 to 100x increase in number of connected devices and increase in user data, 10x longer battery life for low power massive machine communication, and 5x reduced end-to-end latency [Ola15]. These are achievable objectives with the technologies available today, but require innovation at the network, system and architecture levels.

Some of the techniques that has been mentioned for meeting these requirements include increase in bandwidth by moving to new unlincensed spectrum, denisification of networks with shorter transmission distance, massive MIMO with greater antenna elements, more efficient transmission schemes to improve OFDM, and flexible radio interfaces [Ola15].

Figure 2.3: Expected IMT-2020 capabilities as compared with those of IMT-Advanced [ITU15]

#### 2.2.1 Challenges and Solutions

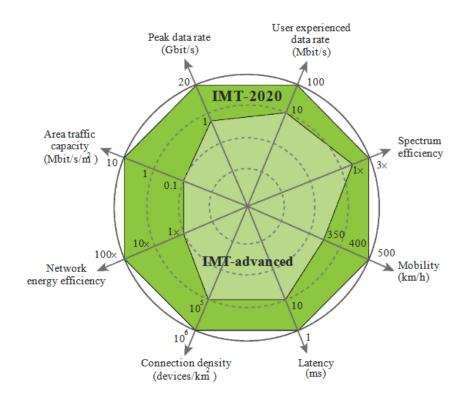

Many of the proposed solutions are an extension of the current technologies. Still, there are many challenges that have to be overcome. A good depiction of the capabilities of a 5G device, with a focus to the communication block, is in Figure 2.4. It shows the challenges and the expected innovations at different parts of the device. For example, of interest to the scope of this work are the number of RATs the transceiver baseband is expected to process, the multi-standard design at the RF parts of the transceiver and the resulting challenges at the front-end module, and the expected challenges of a multi-antenna operation. In this subsection, a brief discussion of the challenges and solutions proposed for future 5G networks are presented.

One of the proposed solutions to free up spectrum and serve more users is decreasing the distance between base stations also called densification. While this allows the incorporation of short-distance communication standards in the 5G network, it faces some challenges, among which the cost of increased infrastructure due to deployement of large number of base stations within small area, and the support of fast and efficient handoff in an environment where there are many RATs [And+14].

A more viable solution for future high data rate networks is increasing bandwidth in an unlicensed spectrum. The challenges to this solution in the PHY layer are design of power efficient and small form factor transceiver architectures that can support MU-MIMO, and antennas that overcome the propagation

Figure 2.4: A 5G device will have to support multiple existing RATs and new ones. The expected capabilities that different parts of the device are shown here[Ban+14b]

loss and atmospheric absorption at mm-waves. These challenges are already being tackled by circuit and antenna designers at this time to some degree. Yet, novel architectures may be needed if massive MIMOs are to be part of mobile terminals [Ban+14b].

Another solution for increasing throughput is novel spectral efficient modulation technique and access technology. While OFDM is a widely used modulation technique, it presents drawbacks. One is the high PAPR that limits the linearity and efficiency of power amplifiers although this may not be a critical problem in a dense network where the transmitted signal does not need to have high power. The other is the need for synchronization and the fact that a big part of an OFDM symbol is taken by the guard interval. It is also a usual practice to fill the edge of an OFDM symbol with null subcarriers. This also results in decreasing the spectral efficiency of OFDM. A technology where the advantages of OFDM are kept with improvements on its drawbacks will be important for 5G networks. Some candidate technologies are already being proposed to supercede OFDM in a 5G network. They are discussed in detail in [Ban+14a].

#### 2.3 The WiFi-WiGig Complementarity

The 802.11ad was developed from the WiGig MAC and PHY. However, WiGig has now merged with WiFi under the WiFi Alliance and standardized in 802.11ad.

Initially released in 1997, WiFi, as standardized by the IEEE 802.11, has hugely impacted the

medium distance local area and personal communications. The latest flavor, 802.11ac, enables WiFi to keep its medium distance capability and reach multi-Gb/s using MIMO. On the other hand, 802.11ad strengthens WiFi in for low power, short distance applications by increasing its capability to multi-Gb/s data rate without the need for MIMO and using simpler modulation schemes. The two standards have made WiFi an indispensable standard, and a candidate for highly dense future networks [VFC13].

Figure 2.5: Block diagram of a configurable transceiver for WiFi and WiGig applications

The 802.11ac and 802.11ad standards have created a good test case for seamless operation of short distance and medium distance communications. Due to its high data rate at low power capabilities, 802.11ad can be used for tasks that require small time duration. For instance, device-to-device data transfer, wireless sync, and wireless display to name a few. Hence, it can be turned on for such tasks. On the contrary, the 802.11ac requires higher power consumption to reach Gb/s data rates. Thus, it is better suited for medium distance, traditional local area network applications.

#### 2.3.1 Tri-band WiFi Radio

The 802.11n, 802.11ac and 802.11ad stretch the reach of WiFi from the crowded 2.4 GHz bands, to 5 GHZ, and mm-wave frequencies respectively. Both 802.11ac and 802.11ad are backward compatible. 802.11ac can be considered as a 5 GHz, wide channel bandwidth version of 802.11n. The idea of triband radio is to employ 2.4 GHz 802.11n for existing networks, 802.11ac for new faster medium distance applications, and 802.11ad for short distance, low power applications [VL11].

There has been some demonstration of this idea in commericial products with the Intel® Tri-band

Wireless-AC 17265 and WiGig Antenna-M10041R. The research in this area is to maximize hardware sharing between the mm-wave 802.11ad and 5 GHz 802.11ac while guaranteeing good performance.

Under the WENDY project of the French National Research Agency, the idea of tri-band radio was targeted. The objective of the project was to research techniques by which a 60 GHz standard could be part of the WiFi ecosystem with respect to how its use cases are entertained and how its circuits are implemented. It targeted the second generation of WiGig based products—the first being standalone WiGig chipsets. Although WiHD was released earlier than WiGig, it specifically targets video streaming application as HDMI cable replacement and was not suited, for instance, with respect to cost, for wireless transfer of general data of other nature.

To implement a highly integrated, configurable and low power tri-band transceiver, the MAC, digital baseband, and the RF front-end circuits should be configurable for operations in all bands. A common frequency synthesizer can deliver a low phase noise signal to all the baseband and mixing blocks at low power constraints. In the RF front-end, the project investigated among other issues how to:

- digitally process baseband signals ranging from 20 MHz to 2 GHz,

- implement digital-to-analog conversion of those baseband signals, and

- upconvert and downconvert IF and RF transmission frequencies of as diverse as 2.5 GHz, 5 GHz, 20 GHz and 60 GHz.

The general block diagram of the transceiver is shown in Figure 2.5. Prototype chips were fabricated for some parts of the tranceiver. In the receiver side, subsampling techniques were employed to solve the problems listed above [GFK13]. In the frequency synthesizer, a wide tuning range mm-wave voltage controlled oscillator was implemented in CMOS 28nm FDSOI [Val+14]. In the transmitter side, it should be understood that the starting objective of this thesis work was to investigate the questions listed above.

#### 2.4 Summary and conclusions

An overview of wireless communication standards commensurate with the scope of this dissertation is presented. Special attention has been given to future networks in line with the initial aim of this PhD work. Recent literature on future 5G networks from both academia and industry is briefly introduced with focus on the challenges and proposed solutions.

Finally, a summary of the ANR project, WENDY, under which this work was started is introduced. The objective of the project was to demonstrate next generation tri-band WiFi transceiver. Design of a configurable mixed-signal block in the transmitter part of such a transceiver was the initial goal for this work.

# **Multi-standard Digital Transmitters**

This chapter investigates the methods that can be implemented for multi-standard transmitter operation. Before that, it will introduce briefly the theoretical operation of a transmitter. Signal processing in cartesian, polar and outphasing transmitter systems is discussed along with modulation schemes. The first section is closed with a highlight of the fundamental transmitter metrics such as transmit mask, EVM, and ACPR.

In the next section, I/Q transmitter architectures are discussed with additional details. It starts with classical architectures such as direct conversion or low-if, heterodyne or two-step transmitter architectures, and ends with a review of modern architectures used in wireless devices. Only the architectures with relevant specs will be discussed.

The last part of this chapter is a theoretical discussion of the possible methods available for implementing a multi-standard transmitter using the traditional architectures. The focus is on the opportunities in the baseband part of the transmitter. Similar to the previous section, this section closes with a mention of recent publications of multi-standard transmitters.

#### **3.1** Brief Theory of Transmitter Operation

From the scope of this dissertation, the name transmitter will refer to the blocks in the lower part of Figure 3.1. However, for completeness, a general block diagram of a WLAN transmitter is shown including the MAC layer. The MAC layer prepares the data units that are exchanged with the PHY according to the transmission format of the standard. It adds the necessary header and defines the payload structure for each user. For example, the 802.11ac standard defines a MU-MIMO capability where an access point transmits data units to multiple receiving stations with one or more antennas. In this case, the MAC layer could define multiple independent data units. The data bits are filled in the PHY layer.

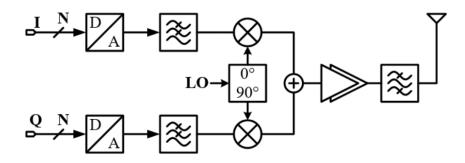

The physical layer mainly performs FEC, and modulation in its digital baseband part and, traditionally, frequency translation, digital-to-analog conversion, filtering and amplification in its analog/RF part. Modulation consists of constellation mapping where bit streams are mapped to complex constellation points, and where the complex symbols are converted to time domain blocks. In a single carrier modulation transmitter, only constellation mapping is done, and the rest of the functions fall under the responsibility of the analog/RF designer. In other words, they are not necessarily implemented in digital baseband. That is the case in 802.11ad where the mapped high speed baseband data can be upconverted and converted to analog without much digital processing (more on this later).

However, advancement in digital signal processors have enabled digital implementation of traditionally analog blocks. The possibility to tune and calibrate digital circuits for best performance have relegated the analog implementation only to the blocks close to the antenna such as the power amplifier or co-existence band pass filter. With this comes the opportunity to implement different standards using one digital hardware. This is the main topic of the final section of this chapter.

Figure 3.1: Essentials blocks of a basic WLAN transmitter. In traditional transmitter, the mixer follows the DAC. However, they can also be implemented in the same circuit.

#### 3.1.1 Modulation

Modulation is the mapping of information carried in one electrical signal, called the modulating signal, into the amplitude, frequency, and/or phase of another signal, called the carrier. Modulation has many advantages in wireless communication which are well covered in many wireless communication text books [Hay09].

#### **Single Carrier**

There are three main modulation types. AM is when the modulating signal controls the amplitude of the carrier, it is FM when it controls the frequency, and PM if the modulation is on the phase of the carrier. Both FM and PM are called angle modulation because, ultimately, both phase and frequency variation can be obtained by varying the angle of the carrier. Each modulation types have different bandwidth efficiency. Probability of error versus energy per bit per spectral noise density  $(\frac{E_b}{N_o})$  graphs are used for

comparing different modulations schemes.

An analog signal modulated by a single carrier of frequency,  $f_c$ , can be generally expressed in polar form as:

$$y(t) = a(t)\cos(2\pi f_c t + \theta(t)).$$

(3.1)

This can be expanded to:

$$y(t) = a(t)\cos(\theta(t))\cos(2\pi f_c t) - a(t)\sin(\theta(t))\sin(2\pi f_c t).$$

(3.2)

The cartesian form of the modulated signal is then:

$$y(t) = x_I(t)cos(2\pi f_c t) - x_Q(t)sin(2\pi f_c t).$$

(3.3)

Where  $x_I(t) = a(t)cos(\theta(t))$  and  $x_Q(t) = a(t)sin(\theta(t))$ . The modulating signal x(t) is generally given by:  $x_I(t) + jx_Q(t) = a(t)e^{j\theta(t)}$ .

The amplitude a(t) follows the modulating signal, x(t), in AM with no modulating signal information on the phase  $\theta(t)$ ; and the angle  $\theta(t)$  varies according to the modulating signal, x(t), in angle modulation with no modulating signal information on the amplitude a(t). In digital modulation, the modulating signal is a sequence symbols. ASK, FSK, and PSK are the digital modulation versions of AM, FM and PM respectively. There are higher order digital modulation schemes such as M-PSK, M-ASK, and M-QAM which are more spectrally efficient. The constellations of 16-QAM and  $\frac{\pi}{2}$ -QPSK are shown as an example in Figure 3.2.

## **OFDM**

Modern wireless communication standards such as IEEE 802.11ac rely on different mechanisms to increase spectral efficiency. Higher order modulation schemes are used to reach Gb/s data rates, for example, 256-QAM in 802.11ac. In addition, OFDM is used to increase throughput in a crowded spectrum.

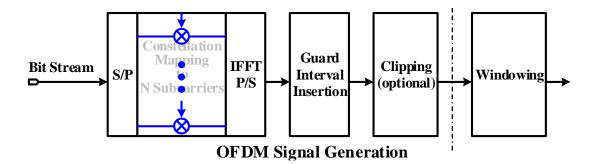

The basic stages in the generation of one OFDM symbol in the baseband of a transmitter is shown in Figure 3.3. The stream of bits are converted to parallel and are mapped to *N* subcarriers according the complex constellation points of the modulation scheme selected. Then the orthogonal subcarriers are summed using an IFFT or IDFT block and converted to time domain. A guard interval is inserted at the end of the summed signal to prevent inter-symbol interference due to multi-path propagation. The IFFT output and the guard interval, can be implemented using cyclic prefix, form an OFDM symbol.

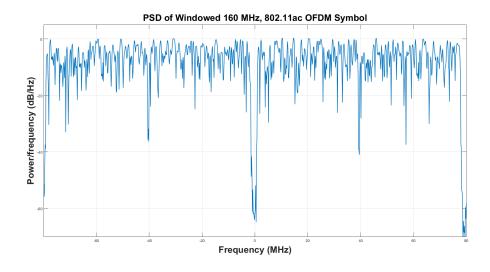

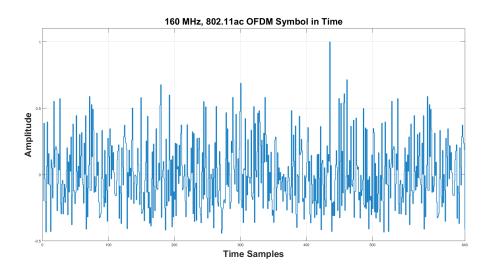

An example based on the 802.11ac standard is given in Figure 3.4 and 3.5. The symbol is generated by mapping a random bit stream to 468 16-QAM data subcarriers, 16 pilot subcarriers and the remaining