N° d'ordre : 42390

## **THESE**

Présentée à l'Université de Lille 1 École Doctorale Sciences Pour l'Ingénieur

Pour obtenir le grade de :

# DOCTEUR DE L'UNIVERSITE

**Spécialité** : SCIENCES ET TECHNOLOGIES DE L'INFORMATION ET DE LA COMMUNICATION

Par

## Yoann LECHAUX

# Étude et fabrication de MOSFET III-V à ionisation par impact pour applications basse consommation

Soutenue le 23 juin 2017 devant la commission d'examen

#### Membres du jury :

| Dr. Xavier WALLART   | Directeur de recherche CNRS, IEMN, Lille | Président du jury  |

|----------------------|------------------------------------------|--------------------|

| Dr. Bassem SALEM     | Chargé de recherche CNRS, LTM, Grenoble  | Rapporteur         |

| Dr. Liviu MILITARU   | Maître de Conférences, INL, Lyon         | Rapporteur         |

| Pr. Nathalie LABAT   | Professeur, IMS, Bordeaux                | Examinatrice       |

| Dr. Nicolas WICHMANN | Maître de Conférences, IEMN, Lille       | Co-encadrant       |

| Pr. Sylvain BOLLAERT | Professeur, IEMN, Lille                  | Directeur de thèse |

« L'inconnu n'existe pas, il n'y a que des choses qui attendent d'être découvertes »

Capt. Kirk, Star Trek

## Remerciements

Ce travail de thèse a été réalisé à l'Institut d'Electronique, de Microélectronique et de Nanotechnologie (IEMN) dirigé par Monsieur Lionel Buchaillot, et plus particulièrement au sein du groupe ANODE (Advanced Nanometric Devices) dirigé par Monsieur Mohamed Zaknoune. Je les remercie de m'avoir accueilli durant ce travail de thèse.

Je tiens à remercier tout d'abord Monsieur Xavier Wallart (IEMN) pour l'honneur qu'il m'a fait d'accepter la présidence du jury ainsi que pour l'intérêt qu'il a porté à mes travaux de thèse.

J'exprime ma reconnaissance ainsi que mes remerciements respectueux à Monsieur Bassem Salem (LTM) ainsi qu'à Monsieur Liviu Militaru (INL) d'avoir jugé ce travail en tant que rapporteurs. Ma reconnaissance et mes remerciements vont aussi à Madame Nathalie Labat (IMS) d'avoir accepté d'être examinatrice de ce travail.

J'adresse tout particulièrement ma gratitude ainsi que mes remerciements à Monsieur Sylvain Bollaert et à Monsieur Nicolas Wichmann d'avoir dirigé et encadré ce travail de thèse. Je les remercie pour leurs conseils, leur rigueur, leur présence et pour tout ce qu'ils m'ont appris durant ces années. Ce fut un réel plaisir de partager et de travailler dans cette ambiance chaleureuse.

Je tiens à remercier aussi tout le personnel de l'IEMN, de la centrale de nanofabrication : J. L. Codron, C. Coinon, M. François, F. Vaurette, Y. Deblock, E. Galopin, M. Dewitte, A. Fattorini, B. Grimbert, C. Boyaval, A. Pageau, I. Roch Jeune, D. Troadec, D. Yarekha, P. Tilmant, L. Morgenroth, S. Ouendi ainsi que le personnel de la centrale de caractérisation : S. Lepilliet, E. Okada, V. Avramovic et S. Eliet.

Je suis reconnaissant aussi envers tous les membres du groupe ANODE et EPIPHY, Yannick Roelens, Mohamed Zaknoune, Ludovic Desplanque, Michèle Carette, François Danneville, Gilles Dambrine et Alain Cappy qui m'ont permis d'accomplir ce travail de thèse.

Un grand merci aussi aux différentes personnes que j'ai côtoyées à l'IEMN et à l'Université de Lille 1 notamment à Patricia Lefebvre qui m'a fait découvrir le plaisir de vulgariser la science aux tout-petits, à Romain Kozlowski, Luc Dubois, Thomas Dargent pour ce qu'ils m'ont appris en termes d'enseignement et Ahmed Addad pour ses images TEM.

Je souhaite aussi remercier tous les doctorant(e)s du laboratoire et notamment mes collègues de bureau et amis à qui je dois énormément et qui m'ont fait découvrir plein de choses : Matej, Vinay, Alexandre, Marina, Aurélien, Maria, Gabriel, Srisaran, Mohammed, Colin, Vincent, Natalia, Kévin, Cibelle, Charlène, Mohamed, Khadim et Sara. Merci aussi à tous les anciens de la « pause café » et à tous les autres que j'ai oubliés de citer mais qui se reconnaîtront.

Merci également à tous mes amis de la fac de Rennes, Chloé, Anthony, Alexis, Minerve, Fanny, Gwen, Maxime...pour tous ces bons moments ensemble.

Enfin, j'adresse ces quelques mots pour exprimer l'immense reconnaissance envers ma famille, mes parents, mon frère et mes sœurs, mais aussi mes grands-parents sans qui cette réussite n'aurait pas été possible. Merci aussi énormément à toi Marine pour ton soutien, ton écoute mais aussi ton aide durant ces années.

# Table des matières

| Table des figures                                                         | XI    |

|---------------------------------------------------------------------------|-------|

| Introduction                                                              | 1     |

| Chapitre 1 – Évolution du MOSFET : du More Moore vers le Beyond CM        | 10S 5 |

| I - Historique et principe de fonctionnement du transistor MOSFET         | 8     |

| 1) Historique                                                             |       |

| Description du MOSFET classique et principe de fonctionnement             |       |

| 3) Fonctionnement et paramètres électriques du MOSFET                     |       |

| II - Évolution de l'architecture du MOSFET classique : More Moore         | 13    |

| 1) Les effets de canal court                                              | 13    |

| 2) Modification de l'empilement métal-oxyde-silicium                      |       |

| 3) Les architectures alternatives 2D et 3D                                |       |

| 4) Vers des transistors MOSFET III-V                                      | 19    |

| III - Les limitations du MOSFET classique                                 | 21    |

| 1) Puissance consommée et tension d'alimentation                          | 21    |

| 2) Pente sous le seuil                                                    |       |

| IV - Transistors innovants à faibles pentes sous le seuil : Beyond CMOS   | 23    |

| 1) Transistors à architectures et matériaux alternatifs                   | 24    |

| 2) Les transistors à injection non thermique des porteurs                 |       |

| 3) Les transistors à fonctionnement non-linéaire                          |       |

| 4) Objectifs et solutions envisagés durant ces travaux                    | 38    |

| Bibliographie du chapitre 1                                               | 41    |

|                                                                           |       |

| Chapitre 2 – Étude, fabrication et caractérisations des diodes <i>pin</i> | 51    |

| I - Comportement électrique des diodes pin : étude analytique             | 54    |

| 1) Evolution du champ électrique dans les diodes <i>pn</i> et <i>pin</i>  | 54    |

| 2) Comportement électrique en polarisation directe                        |       |

| 3) Comportement électrique en polarisation inverse                        |       |

| II - Intérêt des matériaux III-V et hétérostructures                      | 63    |

| 1) Coefficients d'ionisation des matériaux III-V et du silicium           | 63    |

| 2) Facteurs de multiplication des matériaux III-V et du silicium          |       |

| 3) Hétérostructures à base de matériaux III-V                             |       |

| III -  | Fabrication et caractérisations de la diode pin InP/ In <sub>0,53</sub> Ga <sub>0,47</sub> As                                          | s67                                       |

|--------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 1)     | ) Structures épitaxiales et diagramme de bandes d'énergie                                                                              | 67                                        |

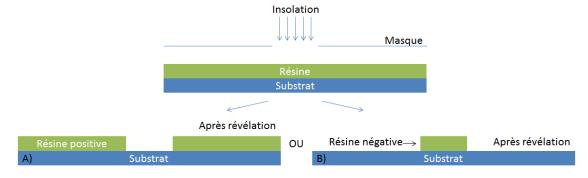

| 2)     |                                                                                                                                        |                                           |

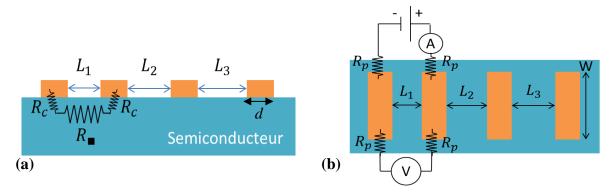

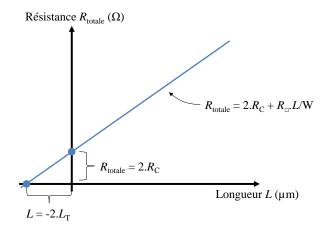

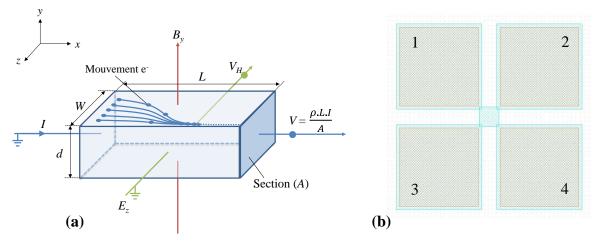

| 3)     | ) Mesure des résistances $R_{\rm C}$ des couches de contact                                                                            | 71                                        |

| 4)     | ) Caractéristiques courant-tension <i>I</i> <sub>D</sub> - <i>V</i> <sub>DS</sub>                                                      | 73                                        |

| 5)     | ) Modélisation des diodes pin InGaAs et InP avec $L_i = 100$ nm                                                                        | 80                                        |

| IV -   | Étude, fabrication et caractérisation de la diode pinin                                                                                | In <sub>0,52</sub> Al <sub>0,48</sub> As/ |

| Iı     | n <sub>0,53</sub> Ga <sub>0,47</sub> As                                                                                                | 82                                        |

| 1)     |                                                                                                                                        |                                           |

| 2)     |                                                                                                                                        |                                           |

| 3)     | , 21                                                                                                                                   |                                           |

| 4)     | <b>,</b>                                                                                                                               |                                           |

| 5)     | ) Caractéristiques $I_D$ - $V_{DS}$ en polarisation inverse des diodes $pinin$                                                         | 89                                        |

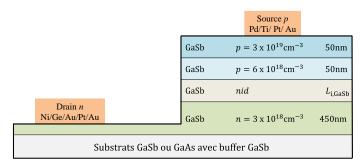

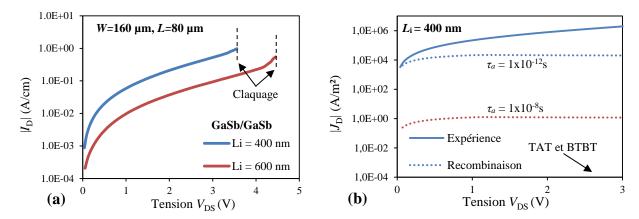

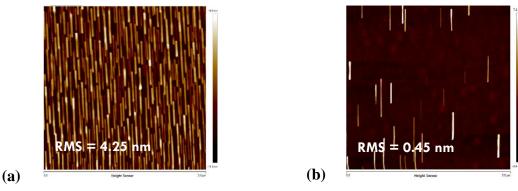

| V - I  | Fabrication et caractérisation de la diode <i>pin</i> GaSbGaSb                                                                         | 91                                        |

| 1)     | ) Structure épitaxiale et réalisation technologique des diodes <i>pin</i> GaSb                                                         | 91                                        |

| 2)     | ) Mesure des résistances $R_{\mathbb{C}}$ et $R_{\square}$ des couches de contact                                                      | 93                                        |

| 3)     | ) Caractéristiques courant-tension <i>I</i> <sub>D</sub> - <i>V</i> <sub>DS</sub>                                                      | 97                                        |

| Conc   | clusion du chapitre 2                                                                                                                  | 102                                       |

|        | iographie du chapitre 2                                                                                                                |                                           |

| Dioii  |                                                                                                                                        | 103                                       |

|        |                                                                                                                                        |                                           |

| Chaj   | pitre 3 — Étude, fabrication et caractérisations de capacités MOS                                                                      | 107                                       |

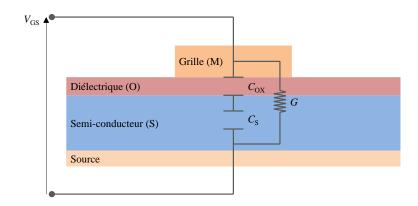

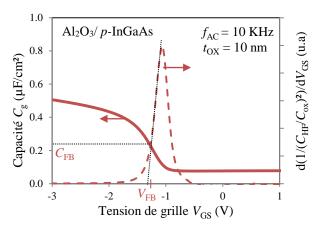

| I - G  | énéralités et caractéristiques électriques                                                                                             | 110                                       |

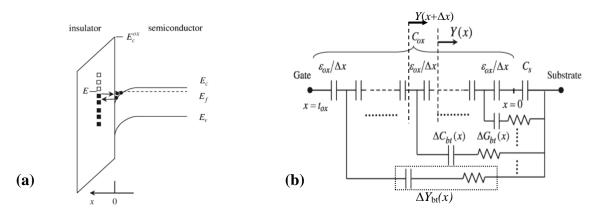

| 1)     | ) Structure MOS réelle                                                                                                                 | 110                                       |

|        | Les différents régimes de fonctionnement et les capacités associées                                                                    |                                           |

|        |                                                                                                                                        | 11.0                                      |

| 11 - 1 | Fabrication et analyses XPS des capacités MOS sur In <sub>0,53</sub> Ga <sub>0,47</sub> As                                             | ······116                                 |

| 1)     | , 1                                                                                                                                    |                                           |

| 2)     |                                                                                                                                        |                                           |

| 3)     |                                                                                                                                        |                                           |

| 4)     | , 1 1                                                                                                                                  |                                           |

| 5)     | , <u> </u>                                                                                                                             |                                           |

| 6)     | ,                                                                                                                                      |                                           |

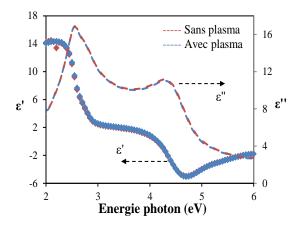

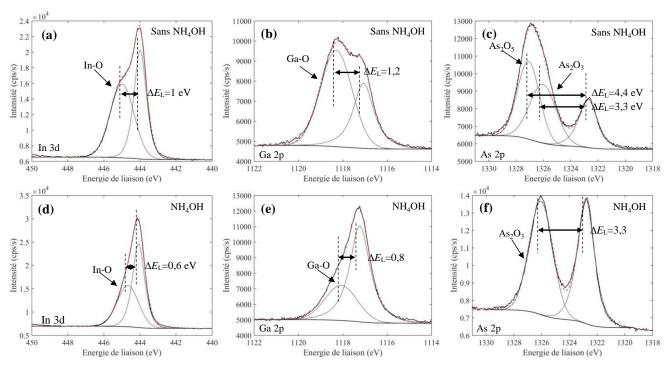

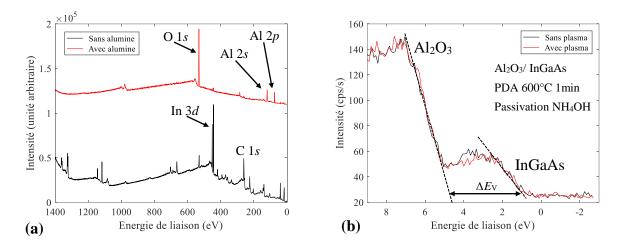

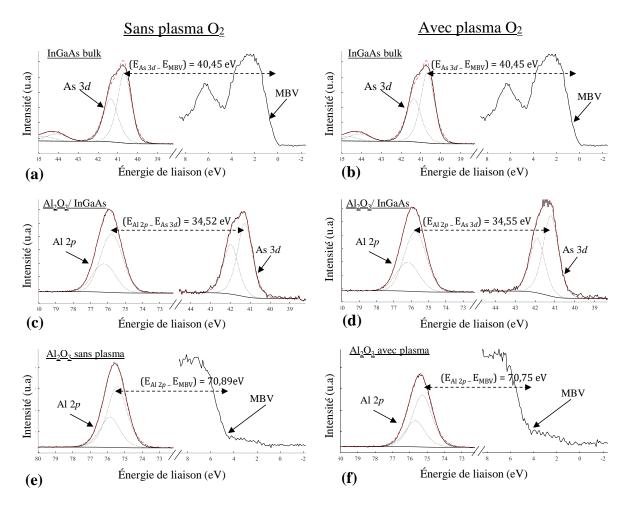

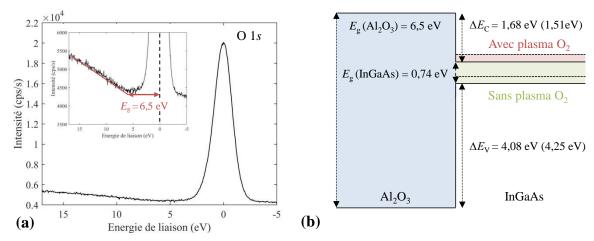

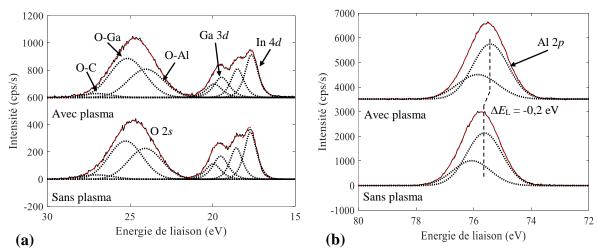

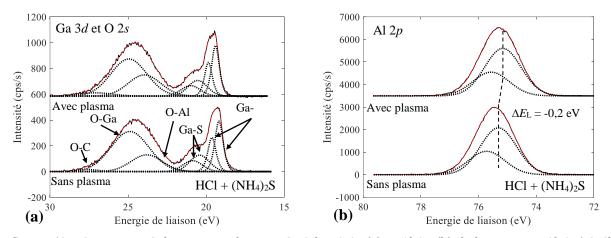

| 7)     | ) Étude XPS de l'interface Al <sub>2</sub> O <sub>3</sub> / In <sub>0,53</sub> Ga <sub>0,47</sub> As et effet du plasma O <sub>2</sub> | 127                                       |

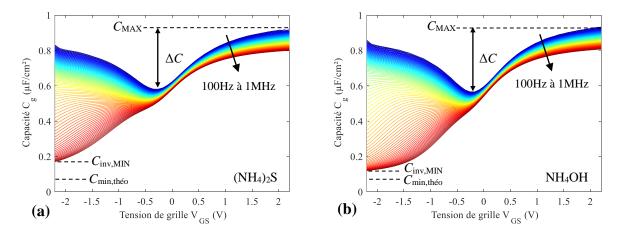

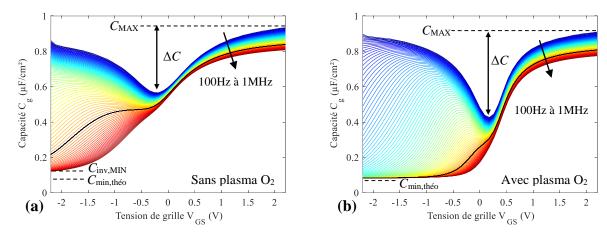

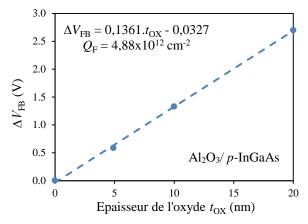

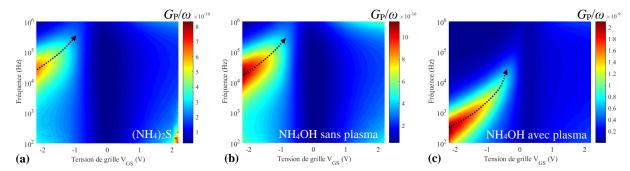

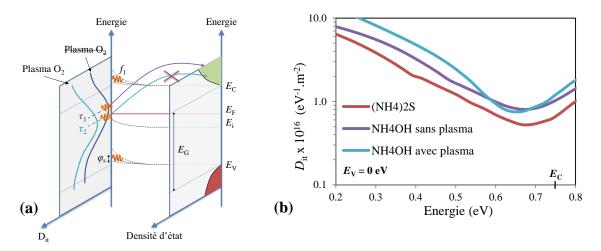

| III -  | Caractérisations électriques des capacités métal/ oxyde/ In <sub>0,53</sub> Ga                                                         | <sub>0,47</sub> As132                     |

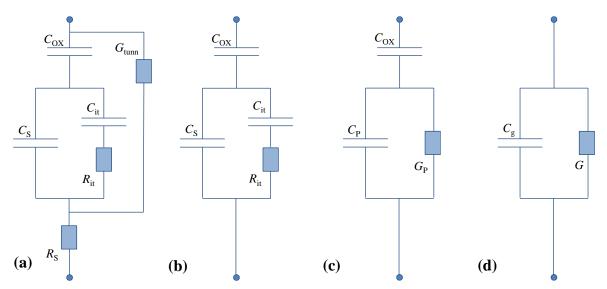

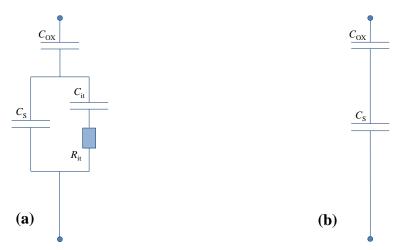

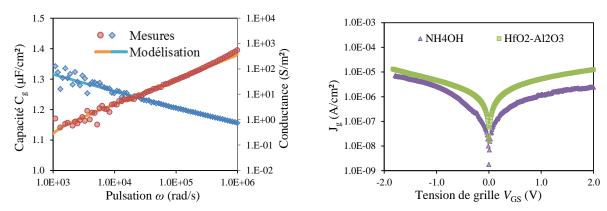

| 1)     | Principe de mesure et schémas équivalents                                                                                              | 132                                       |

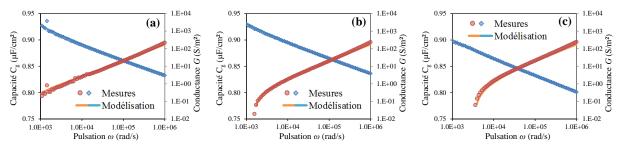

| 2)     |                                                                                                                                        |                                           |

| 3)     |                                                                                                                                        |                                           |

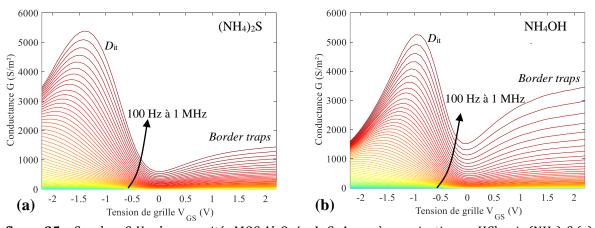

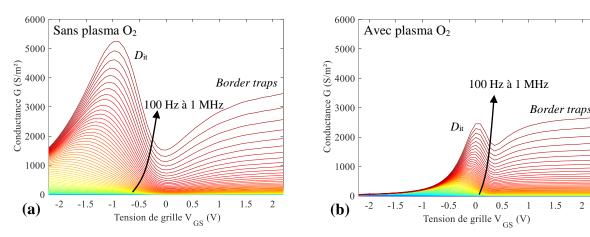

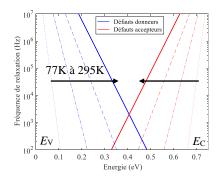

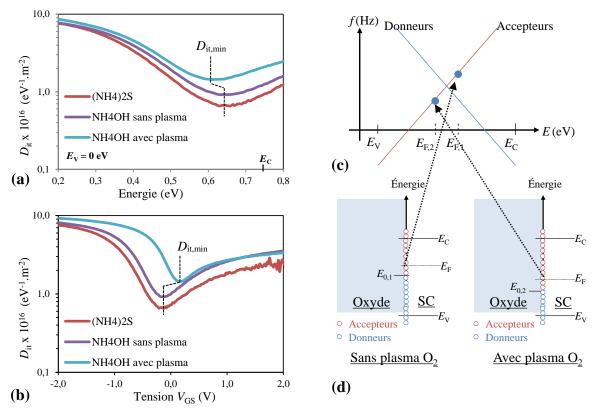

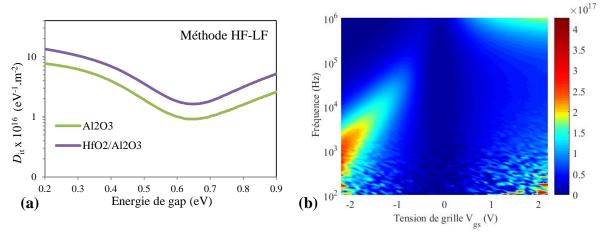

| 4      | Extraction de la densité de défauts d'interface et effet du plasma O2                                                                  |                                           |

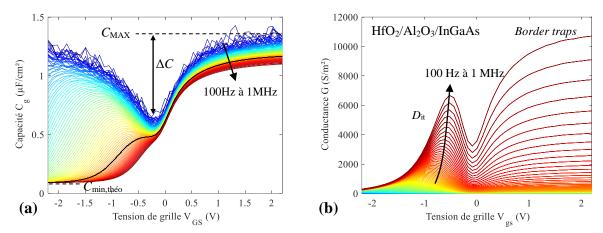

| 5)     | Extraction de la densité de « Border traps » et effet du plasma O <sub>2</sub>                                                             | 148       |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------|

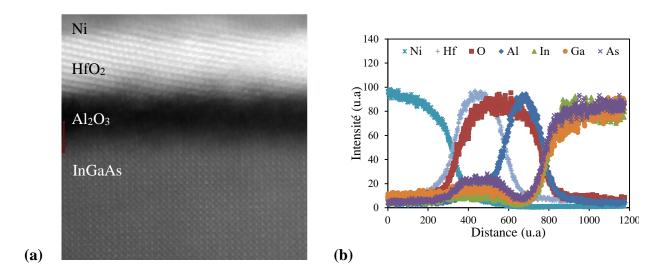

| 6)     | Caractérisations électriques de l'interface HfO <sub>2</sub> / Al <sub>2</sub> O <sub>3</sub> / n-In <sub>0,53</sub> Ga <sub>0,47</sub> As | 151       |

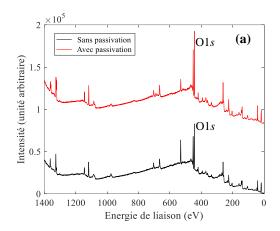

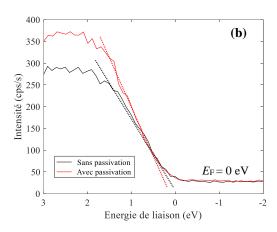

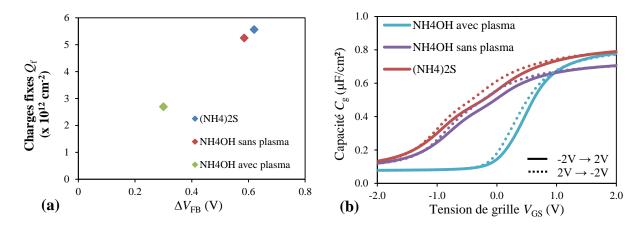

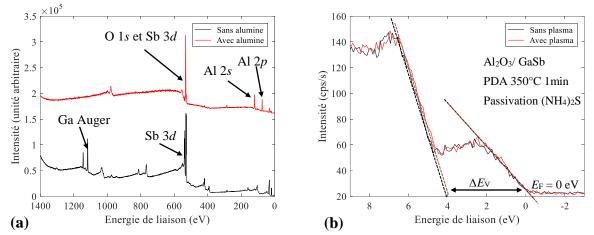

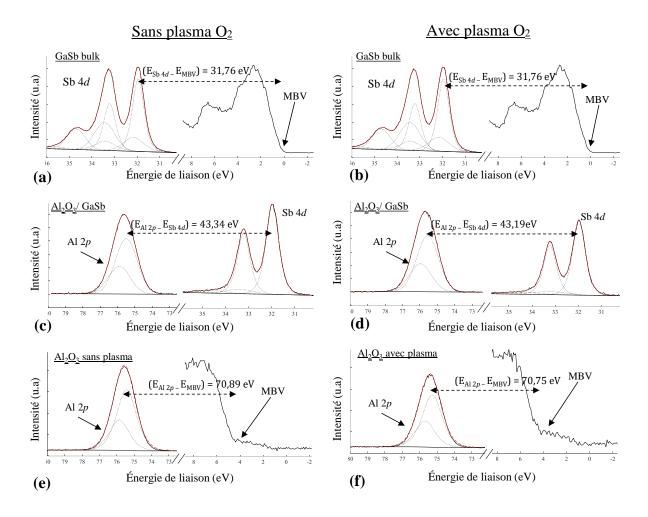

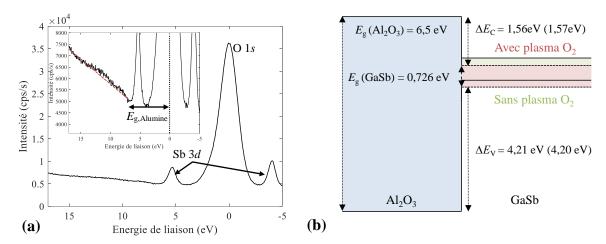

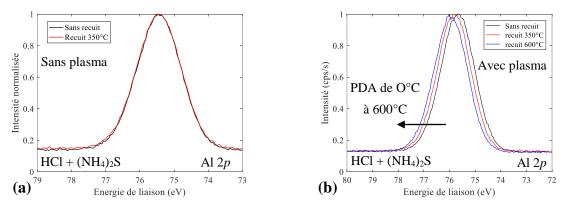

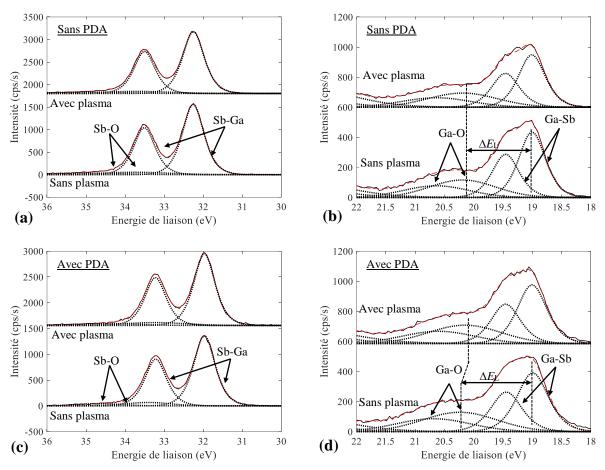

| IV - Í | Étude et analyses XPS de la structure oxyde/ GaSb                                                                                          | 153       |

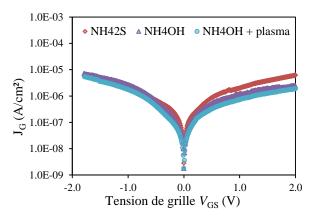

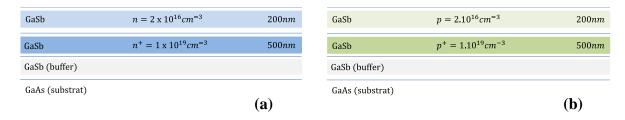

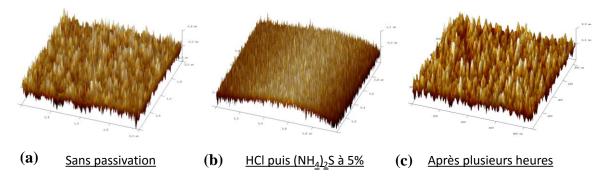

| 1)     | Structures épitaxiales et passivation de la surface du GaSb                                                                                | 153       |

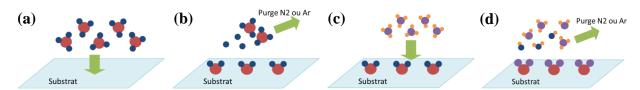

| 2)     | Dépôt d'alumine (Al <sub>2</sub> O <sub>3</sub> ) et traitement par plasma O <sub>2</sub>                                                  | 156       |

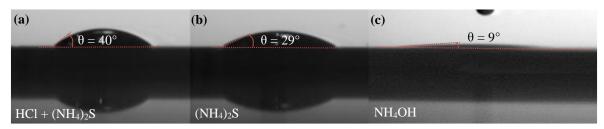

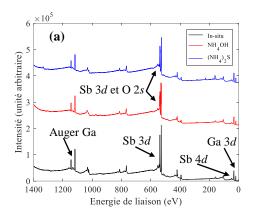

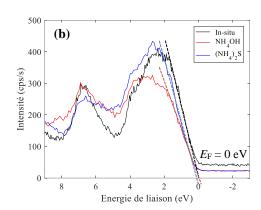

| 3)     | Étude XPS de la surface de GaSb après passivation NH4OH et (NH4)2S                                                                         | 157       |

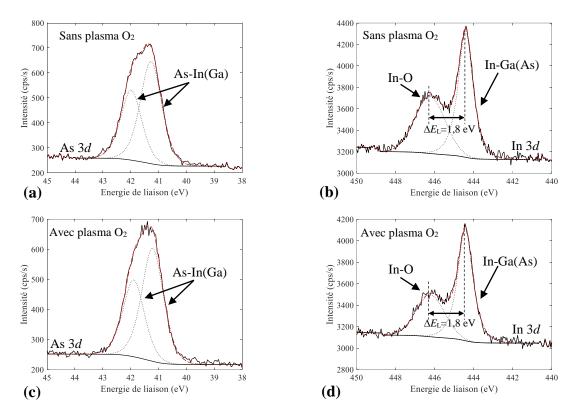

| 4)     | Étude XPS de l'interface Al <sub>2</sub> O <sub>3</sub> / GaSb et effet du plasma O <sub>2</sub>                                           | 159       |

| Conc   | clusion du chapitre 3                                                                                                                      | 166       |

| Bibli  | ographie du chapitre 3                                                                                                                     | 167       |

|        |                                                                                                                                            |           |

| Chap   | itre 4 – Étude et fabrication de transistors à faibles pentes sous le s                                                                    | seuil 175 |

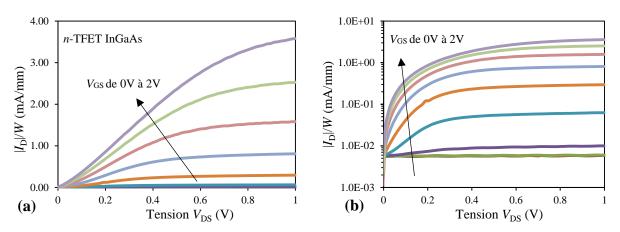

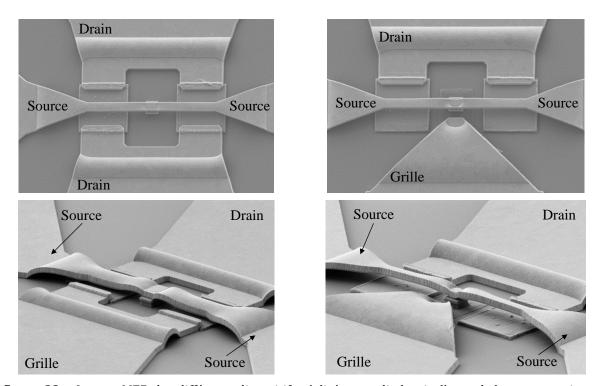

| I - Ét | ude, fabrication et caractérisation de <i>n-</i> TFETs InGaAs                                                                              | 178       |

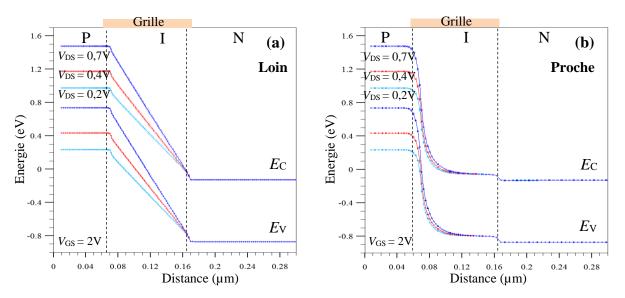

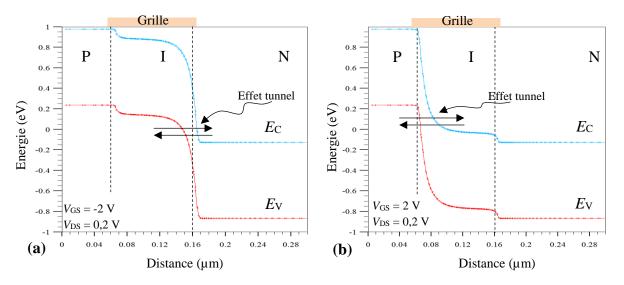

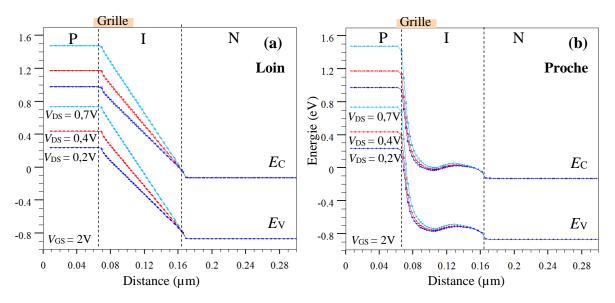

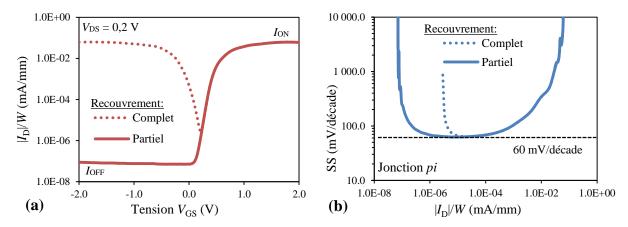

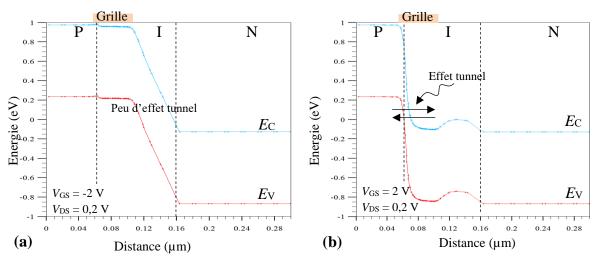

| 1)     | Étude du $n$ -TFET InGaAs ( $L_i = 100 \text{ nm}$ ) par simulation TCAD                                                                   | 178       |

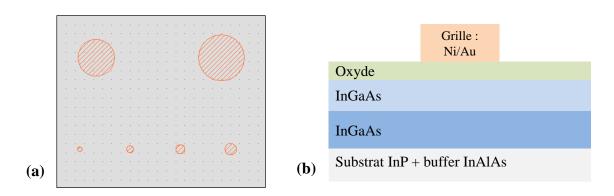

| 2)     | Fabrication du $n$ -TFET InGaAs avec $L_i = 800 \text{ nm}$                                                                                | 183       |

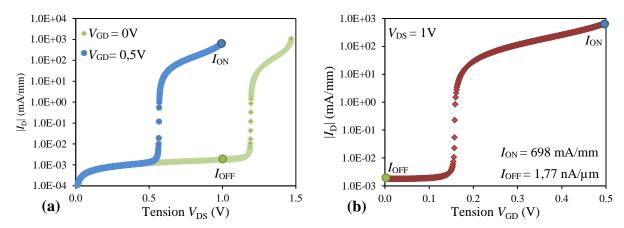

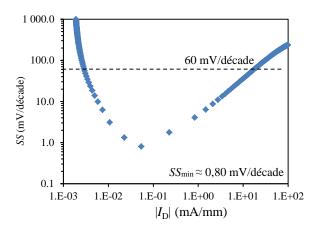

| 3)     | Caractéristiques électriques du $n$ -TFET InGaAs avec $L_i = 800 \text{ nm}$                                                               | 185       |

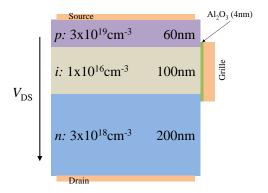

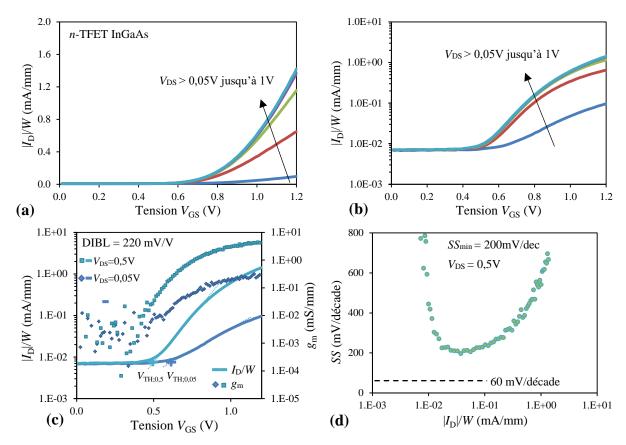

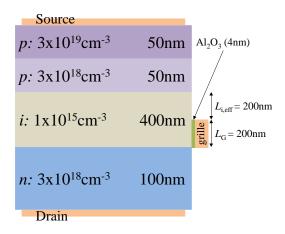

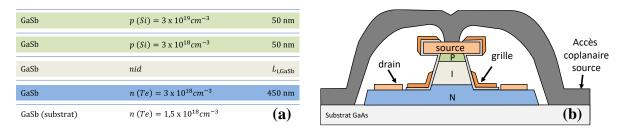

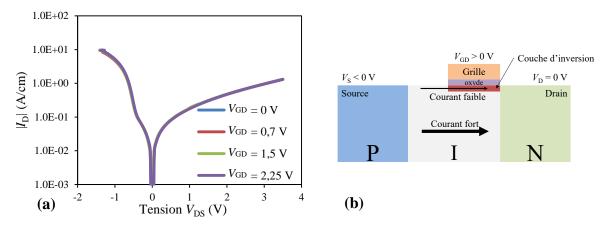

| II - É | tude, fabrication et caractérisation du I-MOSFET GaSb                                                                                      | 187       |

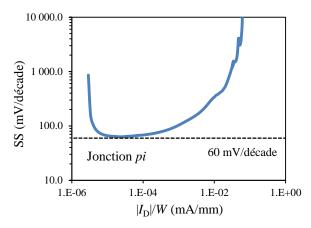

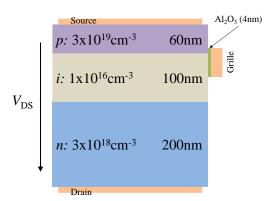

| 1)     | Étude par simulation TCAD du I-MOSFET GaSb                                                                                                 | 187       |

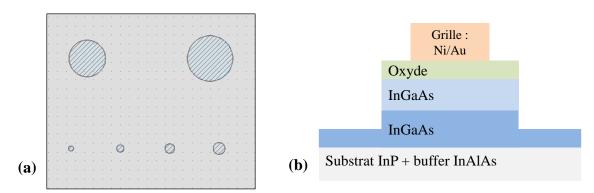

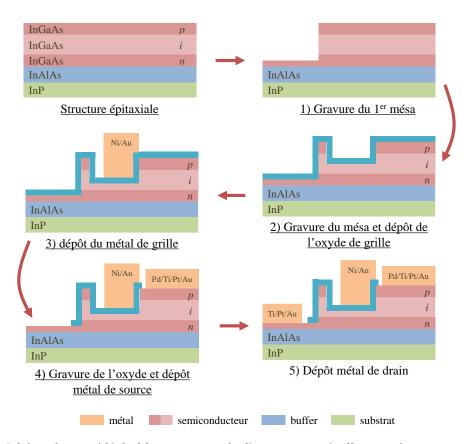

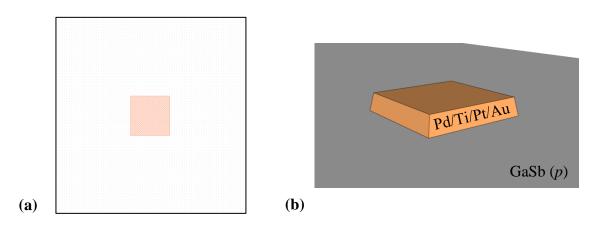

| 2)     | Fabrication des transistors I-MOSFET GaSb                                                                                                  | 190       |

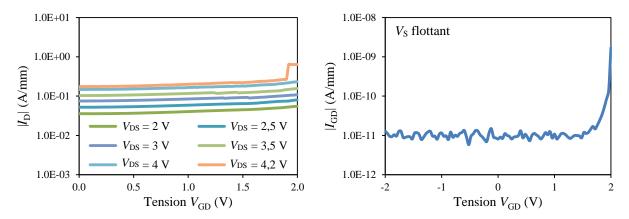

| 3)     | Caractéristiques électriques du I MOSFET GaSb                                                                                              | 199       |

| Conc   | lusion du chapitre 4                                                                                                                       | 201       |

| Biblio | ographie du chapitre 4                                                                                                                     | 202       |

|        |                                                                                                                                            |           |

| Conc   | lusion générale                                                                                                                            | 203       |

| Anne   | xes                                                                                                                                        | 207       |

| Liste  | des publications                                                                                                                           | 231       |

# Table des figures

## Chapitre 1

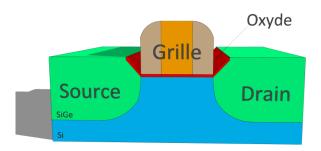

| figure 1 – Schéma 3D d'un transistor MOSFET à base de silicium contraint                                                   |

|----------------------------------------------------------------------------------------------------------------------------|

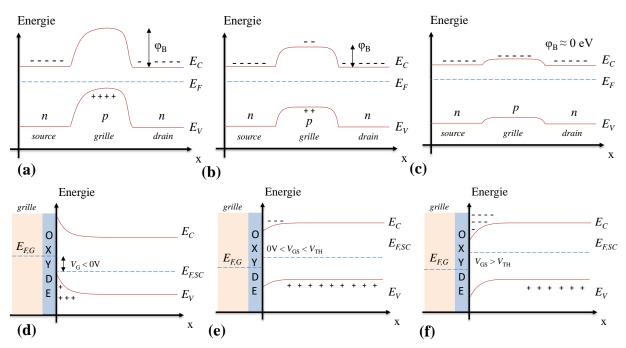

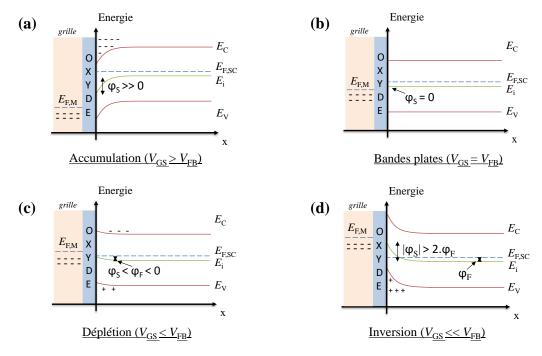

| figure 2 - Diagramme de bandes d'énergies dans les régimes d'accumulation (a)-(d), de                                      |

| désertion (b)-(e) et de forte inversion (c)-(f) pour différentes polarisation $V_{GS}$ . En haut coupe                     |

| le long du canal et en bas coupe transverse au canal (structure MOS)                                                       |

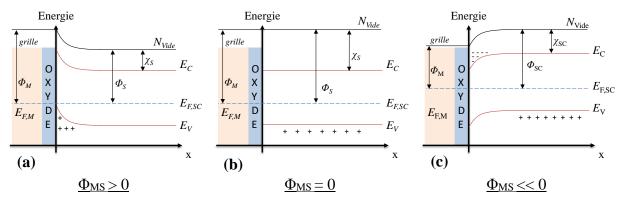

| figure 3 - Diagramme de bande d'énergie dans les régimes d'accumulation (a), de bande                                      |

| plate (b) et d'inversion (c) pour différentes valeurs de $\Phi_{MS}$ de la structure MOS dopé $p$ 11                       |

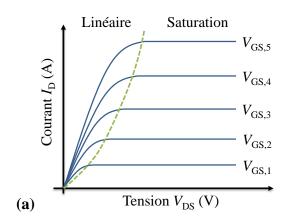

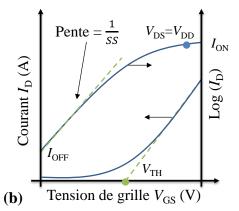

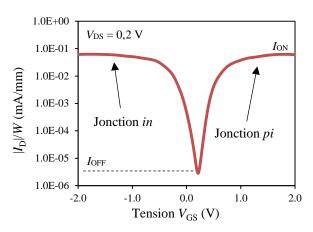

| figure 4 - Courbe de fonctionnement des transistors MOSFETs conventionnels pour                                            |

| différentes valeurs de $V_{\rm GS}$ (a) et courbe de transfert montrant le passage de l'état bloquant                      |

| (OFF) à l'état passant (ON) (b).                                                                                           |

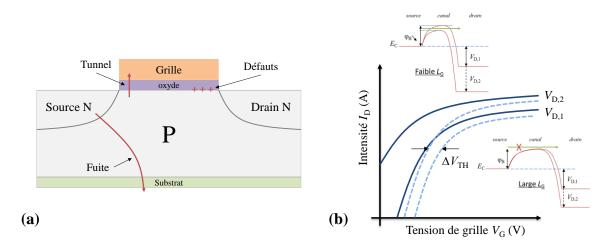

| figure 5 - Schéma simplifié de quelques effets négatifs dus à la réduction d'échelle des                                   |

| MOSFETs menant à une augmentation de la consommation (a) et schéma explicatif de l'effet                                   |

| DIBL et son effet sur une courbe de transfert (b).                                                                         |

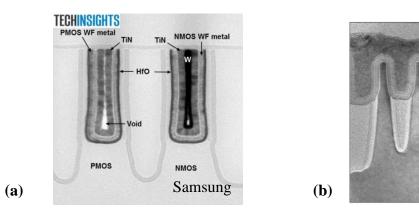

| figure 6 - Transistors 3D FinFETs 14nm de l'architecture Exynos 7420 de Samsung (a) ainsi                                  |

| qu'un transistor 3D FinFET 14 nm de l'architecture Broadwell Y de Intel (b). Source                                        |

| TechInsights et Intel                                                                                                      |

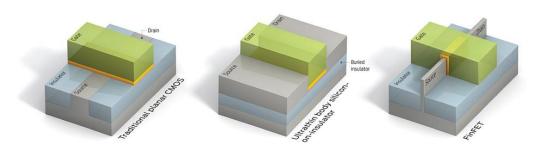

| figure 7 – Représentation simplifiée de l'évolution de l'architecture du MOSFET                                            |

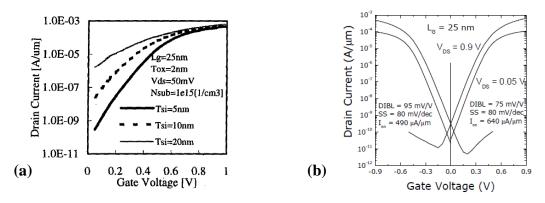

| figure 8 – Caractéristiques de transfert d'un transistor UTB selon l'épaisseur du silicium $t_{\rm Si}$                    |

| réalisé par Y-K. Choi et al. [14] (a) et d'une cellule CMOS UTB [15] (b)                                                   |

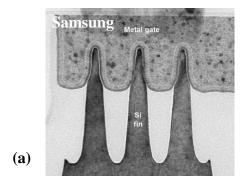

| figure 9 - Image d'un FinFET 14nm de Samsung (Exynos 7420) (a) et d'un FinFET fabriqué                                     |

| par TSMC (b). Nous remarquons que la grille recouvre plusieurs ailettes (multi-grilles) 18                                 |

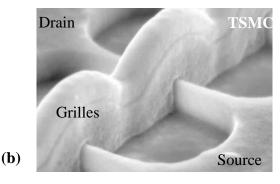

| figure 10 - Image d'empilements verticaux de nanofils de silicium horizontaux réalisés par                                 |

| l'IMEC (a) ainsi que les courbes de transfert pour les transistors de type $n$ et $p$ (b) [26] 19                          |

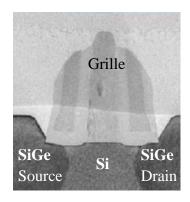

| figure 11 – Image de microscopie électronique à balayage (MEB) d'un MOSFET de longueur                                     |

| de grille 90nm par Intel en 2003.                                                                                          |

| figure 12 - Caractéristique de transfert d'un transistor UTB avec un canal d'InAs de 6nm                                   |

| $L_{\rm G}$ = 40 nm par S. Lee et al. [30] (a) et images MEB de transistors UTB réalisés dans notre                        |

| groupe par M. Pastorek (b) et M. Ridaoui (c).                                                                              |

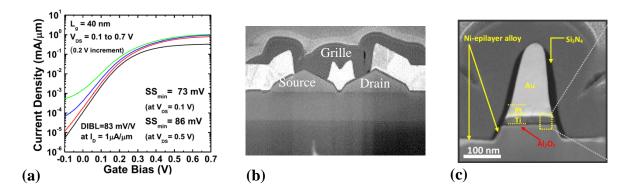

| figure 13 - Allure de la caractéristique de transfert d'un MOSFET. La pente sous le seuil                                  |

| définit l'inverse de la pente entre les états OFF et ON.                                                                   |

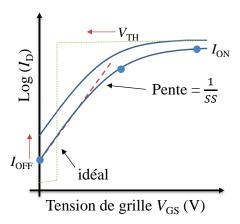

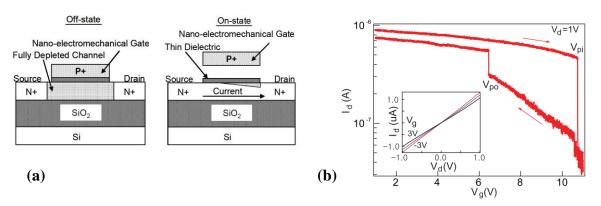

| <b>figure 14</b> – Représentation schématique du transistor à grille suspendue (a) et courbe $I_{\rm D}\text{-}V_{\rm GS}$ |

| expérimentale (b). Nous remarquons la faible pente sous le seuil de l'ordre de 2 mV/décade                                 |

| ainsi qu'une augmentation du courant de fuite $I_{\rm G}$ lors du passage à l'état ON à cause de la                        |

| diminution de la longueur de gap entre l'oxyde et le métal de grille.                                                      |

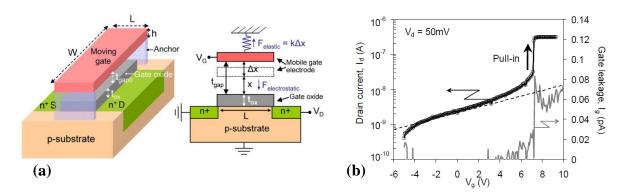

| figure 15 - Représentation schématique d'un NEMFET [54] (a) et une courbe de transfert                                   |

|--------------------------------------------------------------------------------------------------------------------------|

| obtenue par l'équipe de J. H. Kim et al. [55] pour une longueur de grille $L_{\rm G}=1,6~\mu{\rm m}$ (b) 26              |

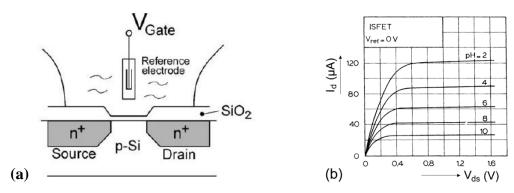

| figure 16 - Représentation schématique d'un ISFET sur silicium (a) et sa courbe de                                       |

| fonctionnement en fonction du pH de la solution (b). La faible taille apporte une sensibilité                            |

| largement supérieure par rapport aux dispositifs classiques                                                              |

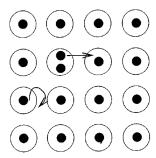

| figure 17 - Illustration du transfert de porteurs dans un matériau à transition de Mott. Les                             |

| atomes sont les cercles blancs ( $\circ$ ), les trous sont les cercles noirs ( $ullet$ ). Sans dopage le transfert       |

| est impossible à cause de la répulsion Coulombienne. Cependant en dopant le matériau, la                                 |

| conservation d'énergie de l'état dégénéré va permettre le transport des trous [70]                                       |

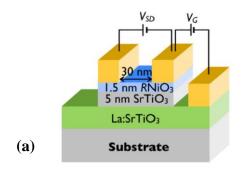

| figure 18 - Représentation schématique d'un MTFET à modulation de dopage à l'aide d'un                                   |

| empilement NdNiO <sub>3</sub> / n-SrTiO <sub>3</sub> [72] (a) et courbe $I_D$ - $V_{DS}$ obtenue par modélisation (b) 29 |

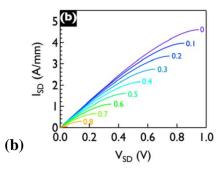

| <b>figure 19</b> – Schéma d'un NCFET (a) et courbe $I_D$ - $V_{GS}$ pour différentes tensions $V_{DS}$ (b) 29            |

| figure 20 - Image de microscopie électronique à balayage d'un FinFET à barrière Schottky                                 |

| de longueur de grille 200 nm [88] (a) et sa courbe $I_{\rm D}\text{-}V_{\rm GS}$ pour différentes valeurs de tension     |

| $V_{\mathrm{SBB}}$ afin de moduler la barrière Schottky (b). De fortes valeurs de $V_{\mathrm{SBB}}$ permettent de très  |

| faibles $SS < 5 \text{ mV/décade.}$ 31                                                                                   |

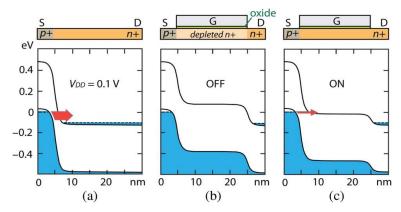

| figure 21 – Schémas des diagrammes de bandes d'une diode présentant l'effet tunnel bande à                               |

| bande (a) et de TFET à l'état OFF (b) et ON (c) [89] pour différentes $V_{\rm GS}$ appliquées 32                         |

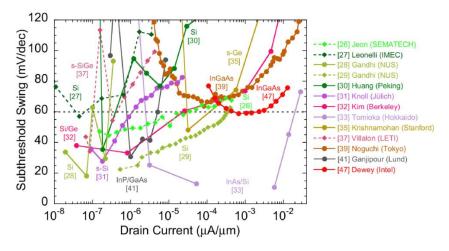

| figure 22 – Graphe représentant la pente sous le seuil $SS$ en fonction du courant de drain $I_{\mathbb{D}}$             |

| pour différentes études sur les TFETs à base de plusieurs matériaux [96]                                                 |

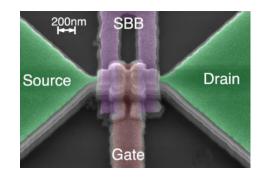

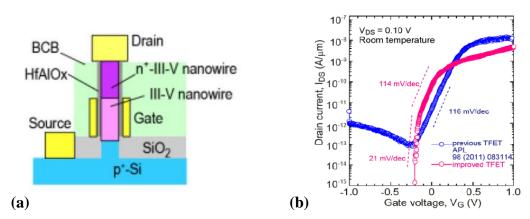

| figure 23 - Transistor à effet tunnel (TFET), il s'agit d'un transistor à base de nanofils III-V                         |

| sur silicium (a) permettant d'achever une pente sous le seuil faible (b) de l'ordre de                                   |

| 21 mV/décade à $V_{DS} = 100$ mV [101]                                                                                   |

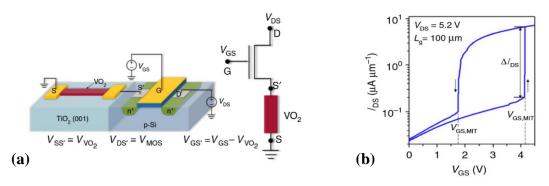

| figure 24 - Transistor nommé hyperFET, il s'agit d'un transistor hybride comprenant un                                   |

| matériau à transition isolant-métal couplé à un transistor MOS à effet de champ classique (a).                           |

| Cela permet d'atteindre des pentes sous-seuil faibles (b) de l'ordre de 10 mV/décade [113]. 34                           |

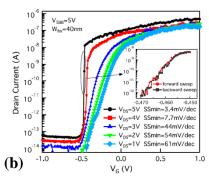

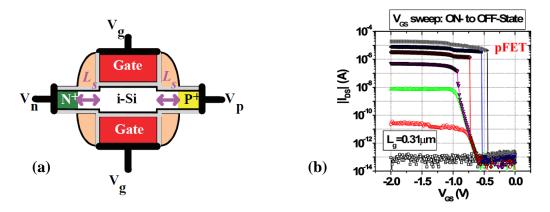

| figure 25 - Représentation schématique d'un feedback FET (a) et la courbe de transfert                                   |

| obtenues sur un feedback FET à canal $p$ en silicium avec $L_{\rm G}=310$ nm et $W=2~\mu{\rm m}$ (b). La                 |

| pente sous le seuil est de l'ordre de 2 mV/décade avec $I_{\rm ON}/I_{\rm OFF} \approx 107$ à $ V_{\rm DS}  = 1,4$ V 35  |

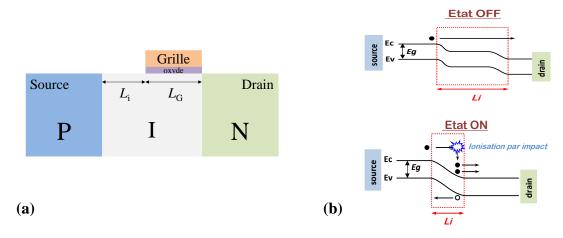

| figure 26 - Représentation schématique du transistor à ionisation par impact consistant en                               |

| une diode pin additionnée d'une grille recouvrant partiellement la zone intrinsèque (a) et ses                           |

| diagrammes de bande associés aux états OFF et ON (b)                                                                     |

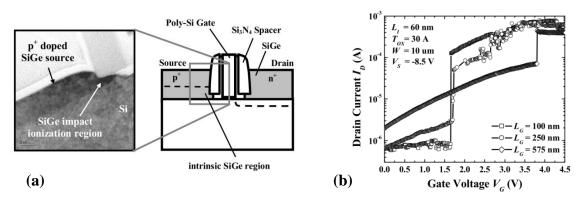

| figure 27 - Représentation schématique et zoom au niveau de la zone intrinsèque d'un                                     |

| I-MOSFET en L par Toh et al. (a). Caractéristique de transfert pour différentes longueurs                                |

| intrinsèques. Pour $L_G = 100$ nm, $SS = 4.8$ mV/décade (b)                                                              |

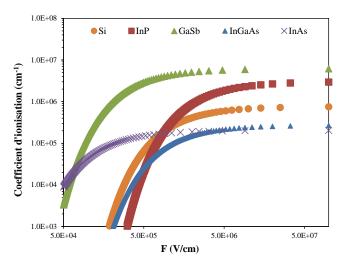

| figure 28 - Courbes des coefficients d'ionisation des électrons permettant de comparer le                                |

| silicium aux matériaux III-V. Nous pouvons noter que l'InGaAs est proche du silicium 39                                  |

## **Chapitre 2**

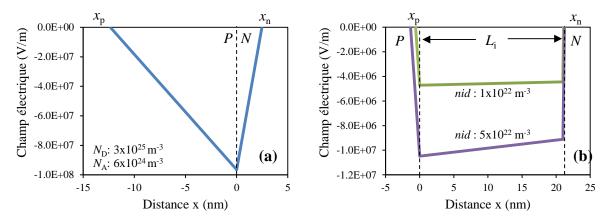

| <b>figure 1</b> – Représentation du champ électrique calculé dans le cas d'une jonction $pn$ (a) et                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| dans le cas d'une jonction $pin$ (b) pour des niveaux de dopages $N_A$ et $N_D$ identiques dans les                                        |

| deux cas. Nous pouvons voir que le champ électrique est plus faible dans la jonction pin que                                               |

| la jonction $pn$ dû à la présence de la zone intrinsèque. L'influence d'un dopage résiduel $nid$                                           |

| (dans notre cas légèrement $n$ ) dans la zone intrinsèque d'une jonction $pin$ est également                                               |

| représentée                                                                                                                                |

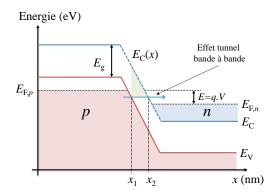

| figure 2 – Diagramme de bandes d'énergies simplifié d'une diode en polarisation inverse                                                    |

| avec les zones $p$ et i dégénérées. Il est possible de définir une barrière de potentielle                                                 |

| triangulaire et obtenir $x_2=x_1+E_g.qF$                                                                                                   |

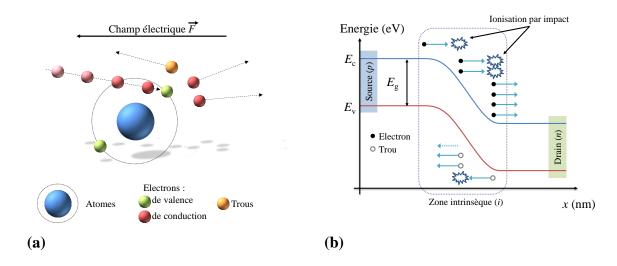

| figure 3 - Principe de création d'une paire électron-trou dans un semiconducteur (a) et                                                    |

| diagramme de bande montrant l'ionisation par impact (avalanche) dans une diode pin (b) 59                                                  |

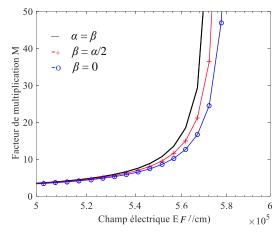

| figure 4 – Facteurs de multiplication des électrons obtenus par calcul dans différents cas de                                              |

| coefficients d'ionisation $\alpha$ et $\beta$ , lorsque $\alpha = \beta$ (en noir), $\alpha = i/2$ (-+ rouge) et $\beta = 0$ (-0 bleu). 63 |

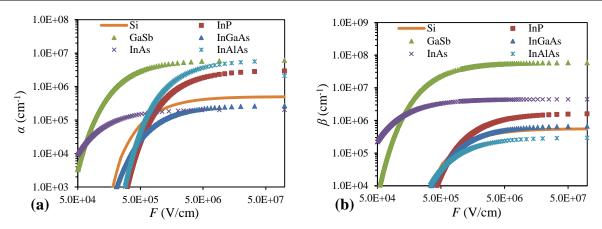

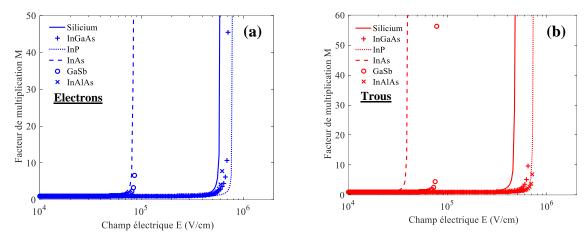

| figure 5 – Coefficients d'ionisation pour les électrons (a) et pour les trous (b) pour différents                                          |

| matériaux. Le silicium présente des caractéristiques similaires à l'InGaAs64                                                               |

| figure 6 - Facteur de multiplication des électrons (a) et des trous (b) pour différents                                                    |

| matériaux tels que le GaSb (o), l'InAs (), l'InP (), l'InAlAs (x), l'InGaAs (++) et le                                                     |

| silicium () avec $L_i = 300 \text{ nm}$ 65                                                                                                 |

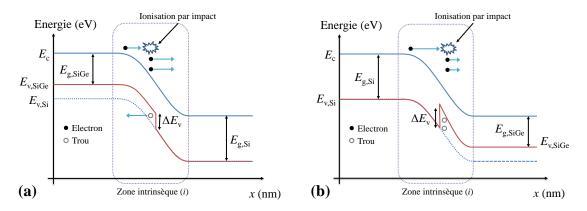

| figure 7 - Représentation schématique des diagrammes de bandes d'énergie de transistors                                                    |

| I-MOSFET basés sur l'hétérostructure SiGe/Si dans le cas de E.H. Toh et al. (a) et dans le cas                                             |

| de D. Sarkar et al. (b)                                                                                                                    |

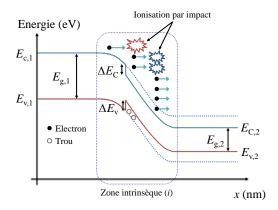

| figure 8 - Représentation schématique des diagrammes de bandes d'énergie d'un transistor                                                   |

| I-MOSFET à matériaux III-V basé sur une hétérostructure de type 1. Cette hétérostructure                                                   |

| permet un gain d'énergie cinétique grâce à la discontinuité $\Delta E_{ m C}$ et d'amplifier le champ                                      |

| électrique grâce à la discontinuité $\Delta E_{ m V}$                                                                                      |

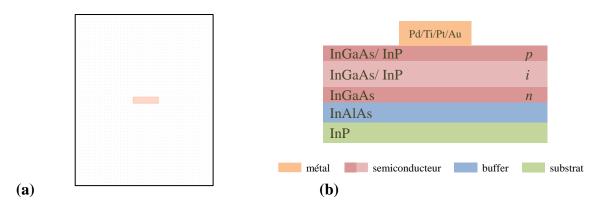

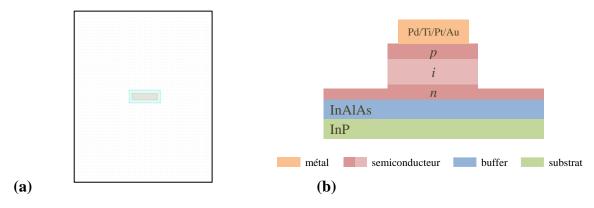

| figure 9 – Schémas des hétérostructures InP/ InGaAs pour différentes longueurs intrinsèques :                                              |

| 30 nm, 50 nm, 100 nm (a) et des homostructures d'InP ou d'InGaAs de longueurs                                                              |

| intrinsèques 100nm (b)                                                                                                                     |

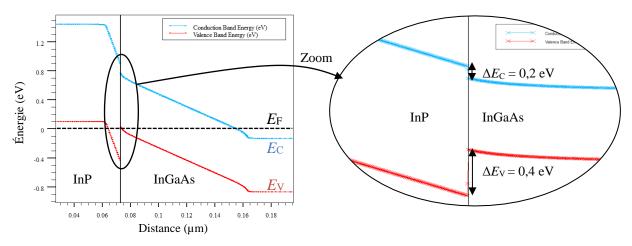

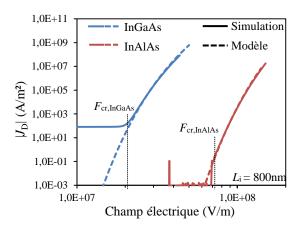

| figure 10 - Simulation TCAD montrant l'alignement des bandes de conduction et de valence                                                   |

| de la diode $pin$ InP/ InGaAs ( $L_i = 100$ nm) sans polarisation et son zoom à droite                                                     |

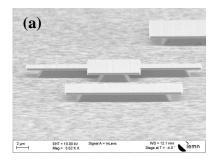

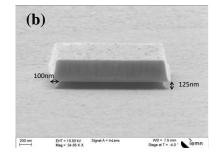

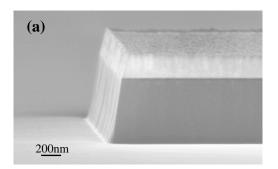

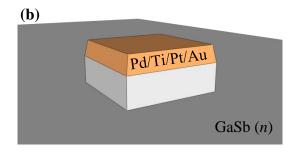

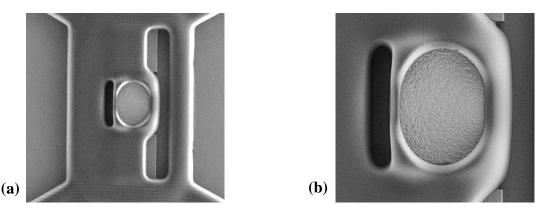

| figure 11 - Masque permettant la réalisation du contact ohmique supérieur (a). Dans un                                                     |

| premier temps le substrat est nettoyé et le contact Pd/Ti/Pt/Au est déposé par évaporation par                                             |

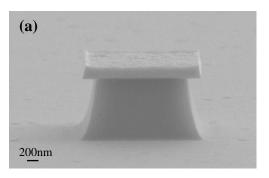

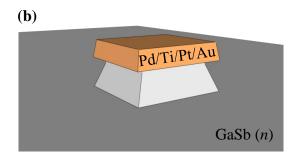

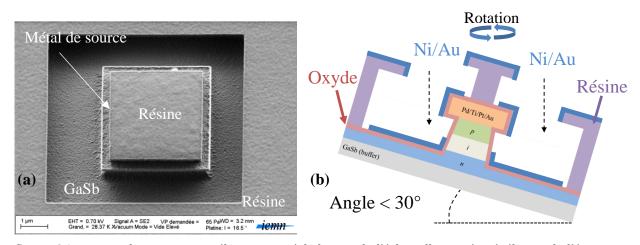

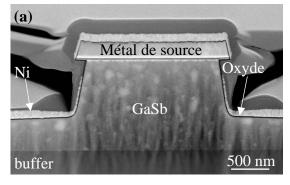

| faisceau d'électrons (b)                                                                                                                   |

| figure 12 – Masque permettant la réalisation du mésa « peu profond » (a). La gravure du                                                    |

| mésa est effectuée à l'aide d'une solution diluée d'acide orthophosphorique (b)                                                            |

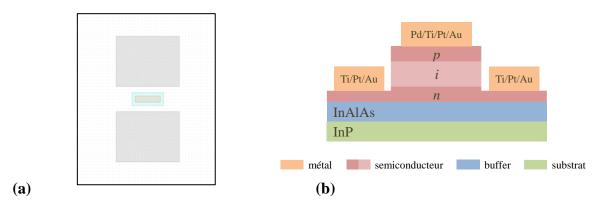

| <b>figure 13</b> – Masque permettant la réalisation du 2nd contact ohmique de type $n$ (a). Les                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| contacts ohmiques Ti/Pt/Au sont déposés par évaporation par faisceau d'électrons (b) 70                                                                                                                   |

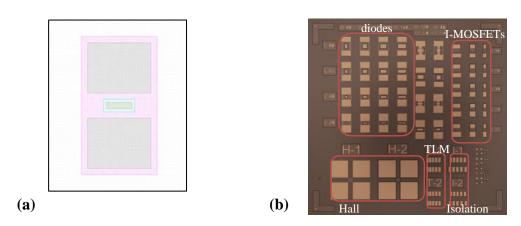

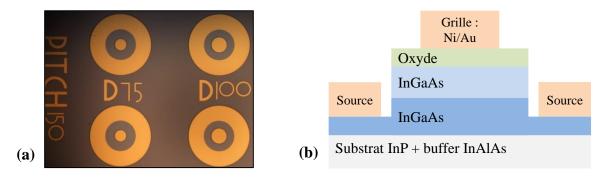

| figure 14 - Masque permettant la réalisation du mésa d'isolation (a). Image au microscope                                                                                                                 |

| optique d'un champ du masque avec différents composants fabriqués (b). Ce masque a été                                                                                                                    |

| réalisé par N. Wichmann                                                                                                                                                                                   |

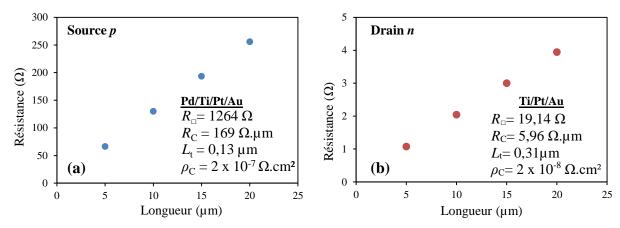

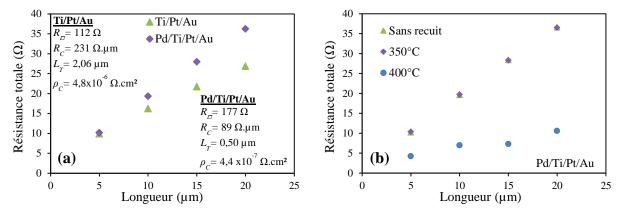

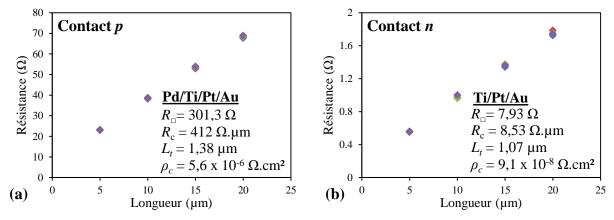

| figure 15 - Mesures de la résistance totale par la méthode TLM en fonction de la distance                                                                                                                 |

| séparant deux contacts de même type pour le contact de source $p$ (a) et de drain $n$ (b) 73                                                                                                              |

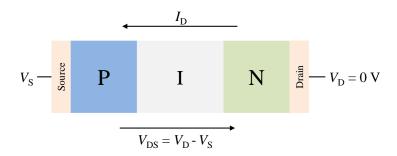

| figure 16 - Schéma d'une diode pin présentant la configuration de mesure avec la source du                                                                                                                |

| côté $p$ et le drain du côté $n$ . Ainsi la polarisation inverse est obtenue lorsque $V_{\rm DS} > 0$ V 74                                                                                                |

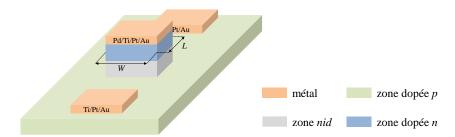

| figure 17 - Schéma d'une diode pin présentant les différentes dimensions de développement                                                                                                                 |

| W et de longueur $L$ . La section efficace $S=W$ x $L$ et le périmètre de la structure                                                                                                                    |

| $P = 2 \times (W + L)$                                                                                                                                                                                    |

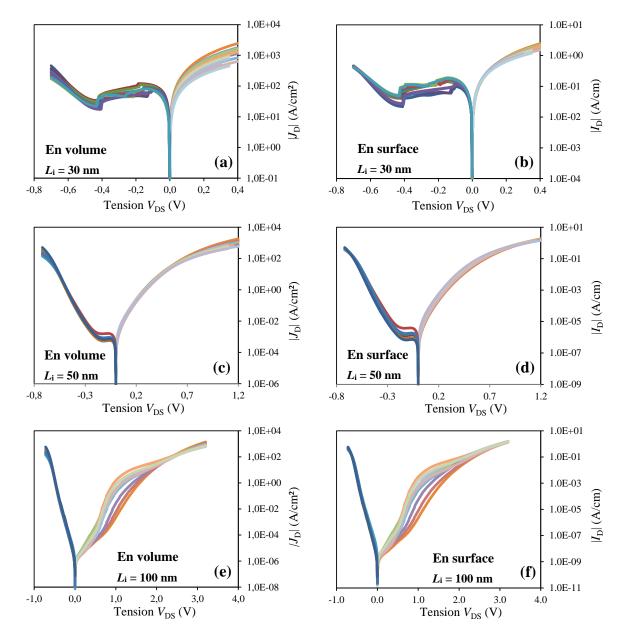

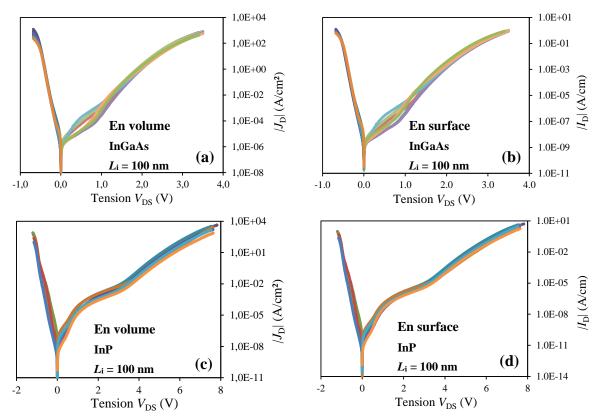

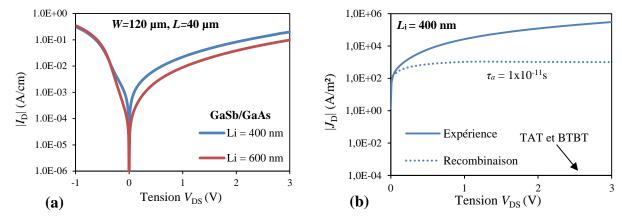

| <b>figure 18</b> – Caractéristiques $J_{\rm D}(I_{\rm D})$ - $V_{\rm DS}$ à température ambiante pour les différentes diodes $pin$                                                                        |

| InP/ InGaAs de longueurs intrinsèques 30 (a, b), 50 (c, d) et 100 nm (e, f) pour chaque valeur                                                                                                            |

| de développement $W$ et de longueur $L$ avec des normalisations volumique (à gauche) et                                                                                                                   |

| linéique (à droite).                                                                                                                                                                                      |

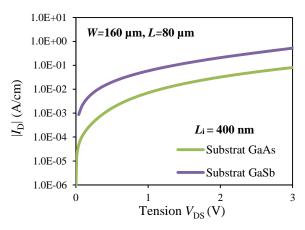

| $\mathbf{figure} \ 19$ – Caractéristiques $J_{\mathrm{D}}(I_{\mathrm{D}})$ - $V_{\mathrm{DS}}$ à température ambiante pour les différentes diodes $pin$                                                   |

| InGaAs (a, b) et InP (c, d) de longueurs intrinsèques 100 nm pour chaque valeur de                                                                                                                        |

| développement $W$ et de longueur $L$ avec des normalisations volumique (à gauche) et linéique                                                                                                             |

| (à droite)                                                                                                                                                                                                |

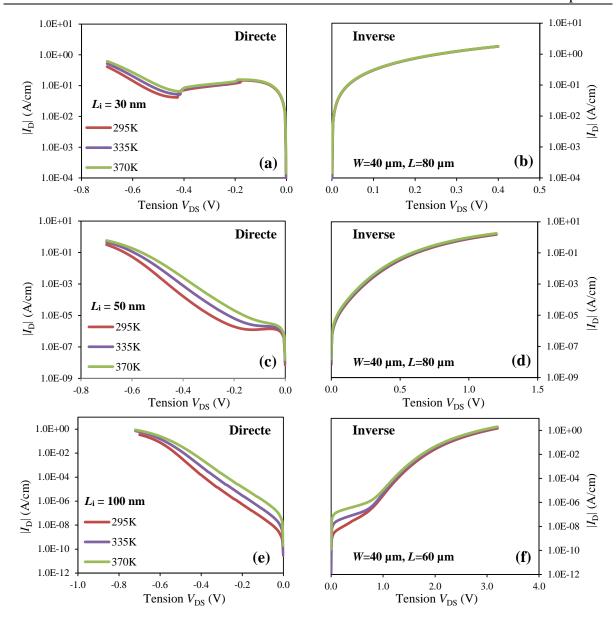

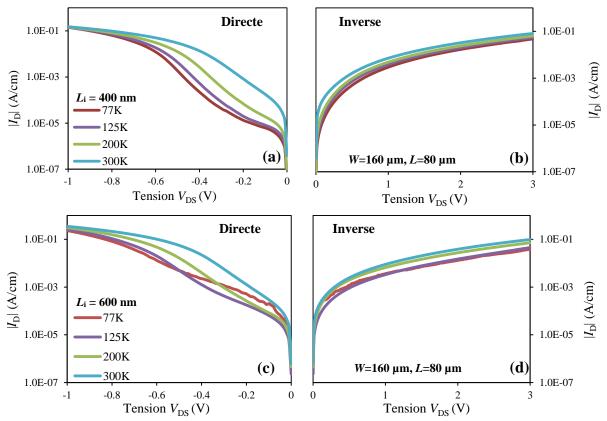

| <b>figure 20</b> – Caractéristiques $I_{\rm D}$ - $V_{\rm DS}$ en polarisation directe (à gauche) et inverse (à droite) en                                                                                |

| fonction de la température pour les diodes pin InP/ InGaAs de longueurs intrinsèques 30                                                                                                                   |

| (a, b), 50 (c, d) et 100 nm (e, f)                                                                                                                                                                        |

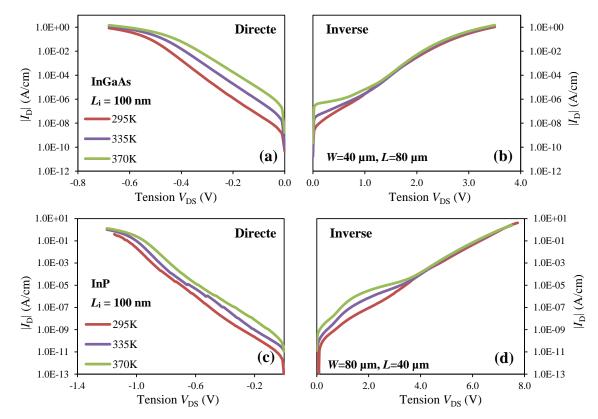

| figure 21 – Caractéristiques $I_{\rm D}$ - $V_{\rm DS}$ en polarisation inverse (à gauche) et directe (à droite) en                                                                                       |

| fonction de la température pour les deux diodes pin : InGaAs (a, b) et InP (c, d) de longueur                                                                                                             |

| intrinsèque 100 nm                                                                                                                                                                                        |

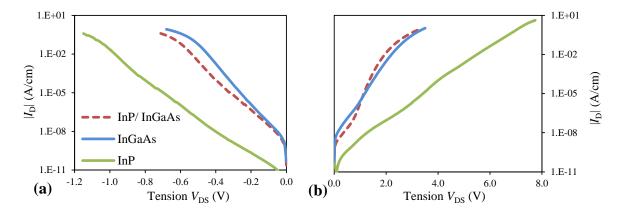

| $\textbf{figure 22} - \text{Caract\'eristiques} \ \textit{I}_{\text{D}}\text{-}\text{V}_{\text{DS}} \ \text{pour les diodes} \ \textit{pin} \ \text{InP, InGaAs} \ \text{et InP/ InGaAs} \ \text{detail}$ |

| longueur intrinsèque 100 nm en polarisation directe (a) et en polarisation inverse (b) 80                                                                                                                 |

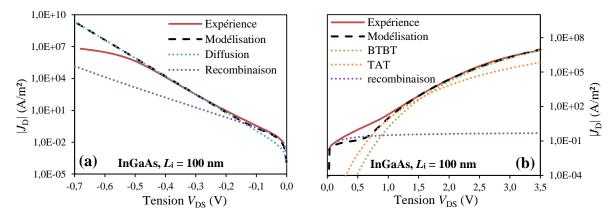

| figure 23 - Courbes des résultats expérimentaux et de modélisation analytique des diodes pin                                                                                                              |

| InGaAs de longueur intrinsèque 100 nm en polarisation directe (a) et inverse (b)                                                                                                                          |

| figure 24 – Courbes des résultats expérimentaux et de modélisation analytique des diodes pin                                                                                                              |

| InP de longueur intrinsèque 100 nm en polarisation directe (a) et inverse (b)                                                                                                                             |

| figure 25 - Représentation schématique de la structure épitaxiale des diodes pinin                                                                                                                        |

| InAlAs/ InGaAs                                                                                                                                                                                            |

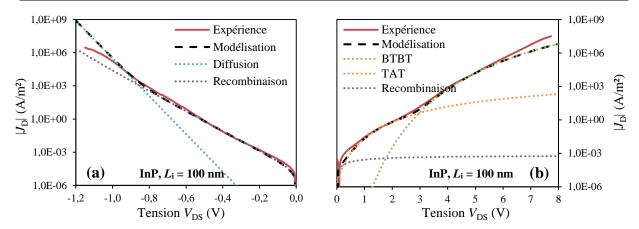

| figure 26 - Simulation TCAD montrant l'alignement des bandes de conduction et de valence                                                                                                                  |

| de la diode ninin InAlAs/ InGaAs (structure II) sans polarisation V <sub>Ds</sub> et son zoom à droite 84                                                                                                 |

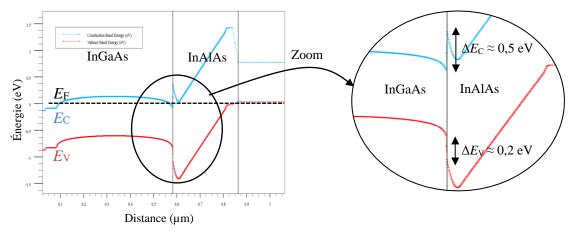

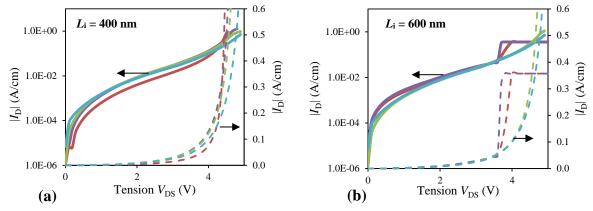

| <b>figure 27</b> – Courbes $I_D$ - $V_{DS}$ des diodes $pin$ InGaAs et InAlAs de longueur intrinsèque 800 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| obtenue par modélisation (tiret) et simulation TCAD (trait plein)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

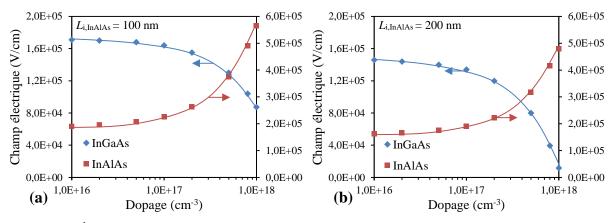

| figure 28 - Évolution du champ électrique dans les diodes pinin, obtenue par simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TCAD à $V_{\rm DS}=10~{\rm V}$ , en fonction du dopage $n$ de la zone médiane pour $L_{\rm i,InAlAs}=100~{\rm nm}$ (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| et $L_{i,InAlAs} = 200 \text{ nm (b)}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

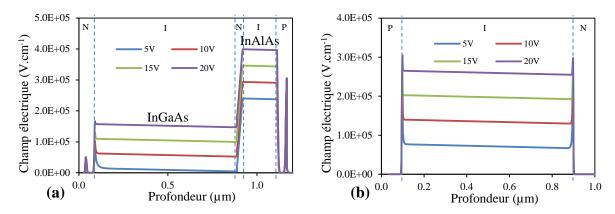

| figure 29 – Profil du champ électrique pour différentes tensions $V_{\mathrm{DS}}$ obtenue par simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TCAD dans la diode $pinin$ InAlAs/ InGaAs avec des longueurs intrinsèques $L_{i,InGaAs} = 800$ nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| et $L_{i,InAlAs} = 200$ nm (a), comparée à la structure $pin$ à base d' InGaAs de longueur intrinsèque                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $L_{i,InGaAs} = 800 \text{ nm (b)}.$ 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

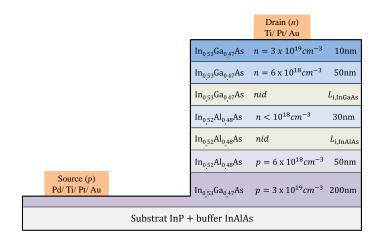

| $\mathbf{figure} \ 30$ – Structure des diodes $pinin \ \mathrm{InAlAs}/ \ \mathrm{InGaAs}$ . Le dopage de la zone $n \ \mathrm{m\'ediane}$ est                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $\label{eq:continuous} \mbox{de 5 x } 10^{17} \mbox{ cm$^{-3}$ lorsque } \mbox{$L_{i,InAlAs}$} = 100 \mbox{ nm et de 8 x } 10^{17} \mbox{ cm$^{-3}$ lorsque } \mbox{$L_{i,InAlAs}$} = 200 \mbox{ nm. } \mbox{ 88 cm.} \mbox{$M_{i,InAlAs}$} = 200 \mbox{ nm. } \mbox{$M_{i,InAlAs}$}$ |

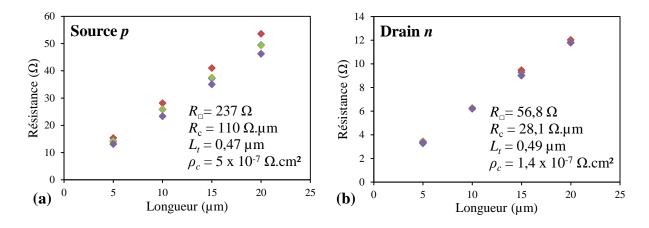

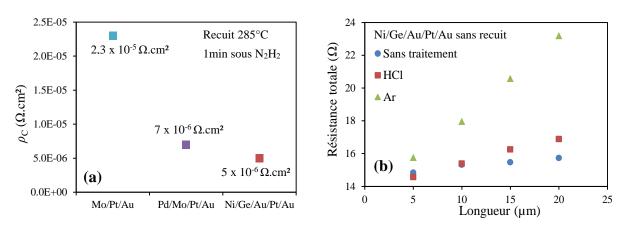

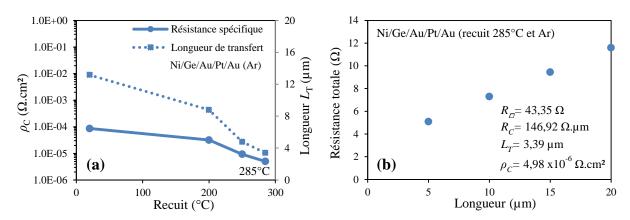

| figure 31 - Mesures des résistances d'accès par la méthode TLM pour le contact de source p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (a) et de drain $n$ (b). Nous avons obtenu de faibles valeurs de résistances spécifiques de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| l'ordre de $10^{-7}~\Omega.cm^2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

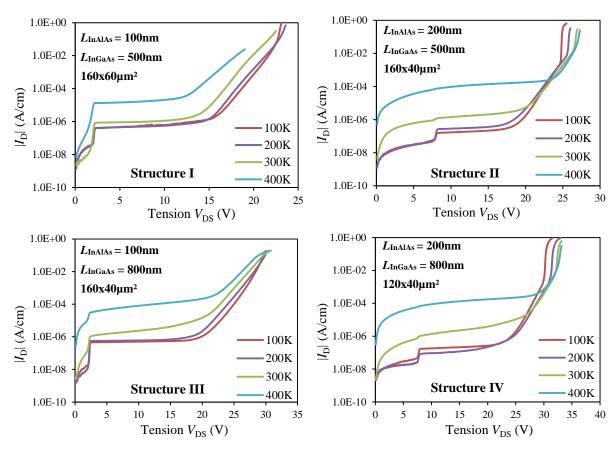

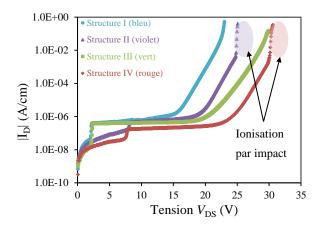

| figure $32$ – Caractéristiques $I_D$ - $V_{DS}$ des diodes $pinin$ en fonction de la polarisation inverse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| pour différentes températures allant de 100K à 400K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

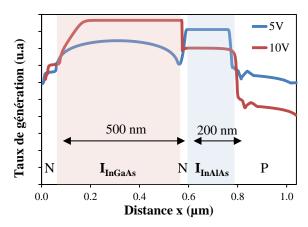

| figure 33 - Représentation du taux de génération thermique pour la structure II obtenue par                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

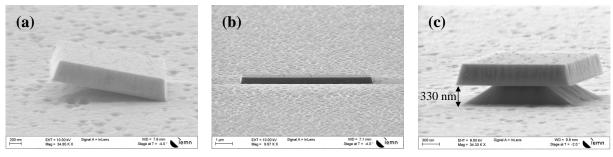

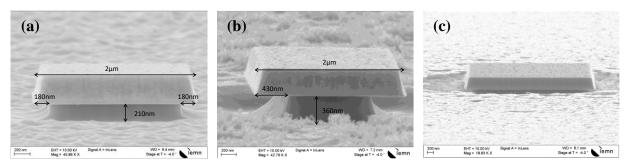

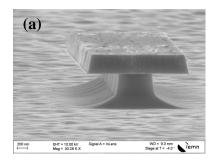

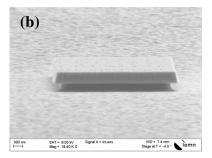

| simulation TCAD à $V_{DS} = 5V$ et $V_{DS} = 10V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |