### UNIVERSITE DE LILLE SCIENCES ET TECHNOLOGIES

### École doctorale : Sciences pour l'Ingénieur Institut d'Electronique, de Microélectronique et de Nanotechnologie

**THÈSE**

Présentée par

Tianqi ZHU

Pour obtenir le grade de Docteur de l'Université

Spécialité Micro et Nano Technologies, Acoustique et Télécommunications

# Convertisseurs thermoïoniques à gap micrométrique : matériaux, conception et fabrication d'un démonstrateur

Soutenue le 17 décembre 2019 devant le jury composé de:

- M. Katir ZIOUCHE, Professeur des Universités, Université de Lille Sciences et Technologies

- M. Karl JOULAIN, Professeur des Universités, Institut P' / TNR

Mme Xiaohui TANG, Chargée de Recherche, ICTEAM, EPL, Université Catholique de Louvain

- M. Stéphane MONFRAY, Ingénieur R&D, STMicroelectronics, Crolles

- M. Aomar HALIMAOUI, Ingénieur R&D, STMicroelectronics, Crolles

- M. Jean-François ROBILLARD, Professeur Associé, IEMN/ISEN/Yncréa Hauts-de-France

- M. Emmanuel DUBOIS, Directeur de Recherche CNRS, IEMN

### Acknowledgments

This PhD research project has been conducted in the Silicon Microelectronics Group at the *Institut d'Electronique*, de Microélectronique et de Nanotechnologies (IEMN) and financially supported by the European Research Council (ERC).

Apart from the financial support to accomplish this work and to provide me a chance to receive scientific training with theoretical, technical, administrative and linguistic aspects. I would like to give my acknowledgments to everybody accepted to preside and join the jury of my thesis, as well as M. Karl JOULAIN and M. Aomar HALIMAOUI to have been kind rapporteur of this research work. Especially Jean-François ROBILLARD who accepted to fill the role of examiner and his help in recent months in providing suggestions and improvement opinions. I would like to thank Dr. Emmanuel Dubois, who was my thesis director during the last 4 years, and guiding me through difficulties in front of me during research works. His valuable experience in the field of micro-electronics guided this work and inspired me to make it better.

Special acknowledgments I want to address to Jean-François Robillard, thanks to his experience, knowledge, advice. Especially his time and energy on this UPTEG ERC Starting Grant project. Without his tutorship and supervision, the work may not be carried out smoothly. His involvement and his motivation were of great help in the realization of this thesis work. Great thanks.

Thanks for the informatics support by Jean-Michel Droulez, all the laptop, server and software license in the working period are in good condition. All the problems I meet can be solved quickly with his help. To be honest, it is a great honor to be one group member of Silicon Microelectronic Group. For a long time the help of group members are so helpful in every aspect. For nano-fabrication technical problems Maciej Haras was a good guide at beginning of the project. By working with Valentina Gorgis I got familiar with basics of cleanroom and got a sound idea of the ultra-high vacuum setup. Here, I want to pass my acknowledgments to her, her help made my life as a new doctor student much easier. Matthieu Berthomé, thank you for helping me in laser cutting my samples and giving me a trainning for the laser equipment. In the same way, I gratefully thank all other group members: Valeria Lacatena, Justine Philippe, Stanislav Didenko, Thierno Moussa Bah, Jean Marc Boucaud, Arun Bhaskar, Quentin Hivin.

The technological work was realized in the laboratory thanks to the support of IEMN staff, particularly: Marc Derwitte, Christiane Legrand, Marc François, Pascal Tilmant, François Vaurette, Dmitri Yareka, Christophe Boyaval, Sylvie Lepilliet, Annie Fattorini, David Delcroix etc. Also, I want to thanks the help of Nora Benbahlouli and Florence Alberti for all the administrative work in all aspects from a simple entering card to working contract and sejour card in France. Without your help, life would not be that easy. Without your help, the trip to summer school and conferences would not be possible. I am deeply grateful to Xu Tao, who introduced me to my thesis director and let me known the chance of appling for this PhD position.

Finally yet importantly, I want to thank my father my mother and all my family members for supporting my studies and your mental support is indispensable which encouraged me to finish my thesis. Same as all my friends in the laboratory, in University of Lille, and who lives at Lille metropole and at Paris including but not only: Zhang Tianchen, Lin Tianjun, Cheng Shiqi, Gu Sijia, Jiang Wei, Hao Jianpin, Lin Quyang, Zhou Di, Wei Wei, Li Shuo, Din Xiaokun, Liu Yuxin, Zhou Xin, etc.

### **Table of Contents**

| Acknowled       | gments                                                                                        | 3  |

|-----------------|-----------------------------------------------------------------------------------------------|----|

| General Int     | roduction                                                                                     | 8  |

| Introductio     | n Générale                                                                                    | 11 |

| Chapter 1 T     | hermionic Energy Conversion                                                                   | 13 |

| 1.1             | Energy conversion and generation                                                              | 15 |

| 1.1.1           | Energy consumption and electric energy in the world                                           | 15 |

| 1.1.2           | Conventional Thermal energy generator based on Seebeck effect                                 | 17 |

| 1.1.3           | Unconventional Micro Thermionic energy Convertor and its structure                            | 18 |

| 1.1.4           | Comparison of two thermal electric convertors                                                 | 20 |

| 1.1.5           | Thermionic energy convertor challenges                                                        | 21 |

| 1.2             | TEC history from 20 <sup>th</sup> century to 21 <sup>th</sup> century, the history and future | 22 |

| 1.2.1           | Early research during 20 <sup>th</sup> century                                                | 22 |

| 1.2.2<br>Quo Va | Thermionic development During cold war and thermionic crisis in 1990s (Thermadis report)      |    |

| 1.2.3           | Renewed interest with nanotech and low work function materials on TECs                        | 25 |

| 1.3             | State of the art                                                                              | 26 |

| 1.3.1           | Limitations of work function and recent solutions                                             | 26 |

| 1.3.2           | Researches and recent solutions for space charge reduction                                    | 30 |

| 1.4             | Approaches in the frame of the UPTEG project                                                  | 35 |

| 1.4.1           | Low-work function material candidates                                                         | 35 |

| 1.4.2           | inspiring structure designs lead to our conception                                            | 36 |

| 1.4.3           | Proof of concept under vacuum                                                                 | 39 |

| 1.4.4           | Encapsulation of Micro Thermionic electric convertor                                          | 39 |

| 1.5             | Chapter summary                                                                               | 40 |

| Chapter 2 L     | ow Work function Material Coating and Characterization                                        | 47 |

| 2.1             | Introduction                                                                                  | 49 |

| 2.1.1           | The term of "work function"                                                                   | 49 |

| 2.1.2           | Work function and Properties                                                                  | 50 |

| 2.1.3           | Conclusion                                                                                    | 54 |

| 2.2             | Experimental Setup                                                                            | 54 |

| 2.2.1           | Chemical Vapor Deposition/measurement setup                                                   | 54 |

| 2.2.3           | In chamber characterization methodology                                                       | 57 |

| 2.2.4           | Ex-situ characterization methodology                                                          | 63 |

| 2.3         | Potassium oxide with CVD process                                          | 65  |

|-------------|---------------------------------------------------------------------------|-----|

| 2.3.1       | Contact potential difference with Kelvin probe                            | 65  |

| 2.3.2       | Photoemission characterization                                            | 66  |

| 2.3.3       | Thermionic emission characterization                                      | 67  |

| 2.3.4       | XPS spectrum characterization                                             | 68  |

| 2.4         | Cesium oxide with CVD process                                             | 70  |

| 2.4.1       | Contact potential difference with Kelvin probe                            | 70  |

| 2.4.2       | Photoemission characterization                                            | 70  |

| 2.4.3       | Thermionic emission characterization                                      | 71  |

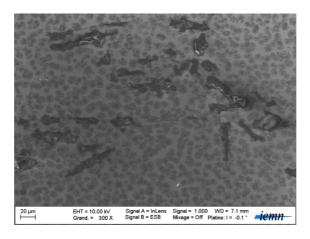

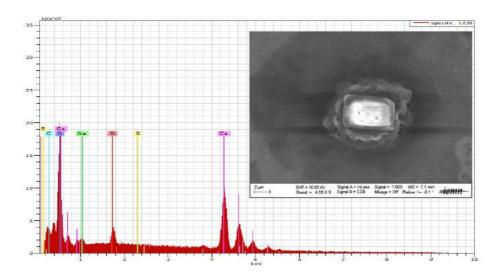

| 2.4.4       | SEM-EDX characterization                                                  | 72  |

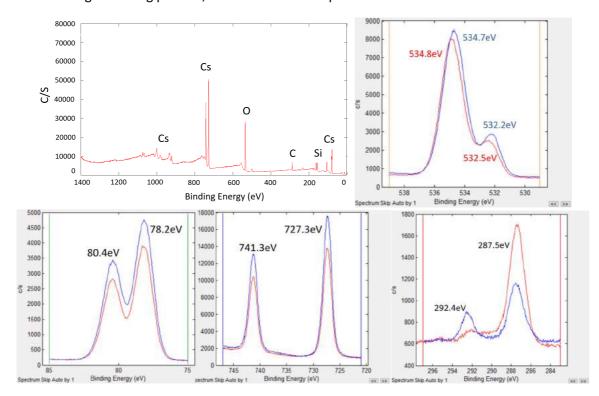

| 2.4.5       | XPS spectrum characterization                                             | 73  |

| 2.5         | Cesium oxide with ALD process                                             | 74  |

| 2.5.1       | Contact potential difference with Kelvin probe                            | 74  |

| 2.5.2       | Thermionic emission characterization                                      | 75  |

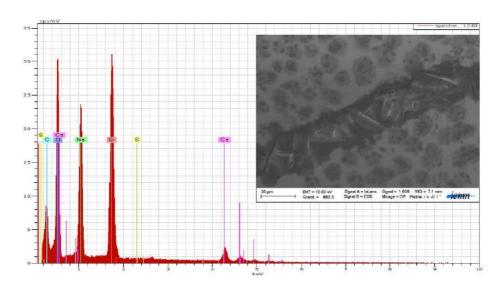

| 2.5.3       | SEM-EDX analyses                                                          | 76  |

| 2.5.4       | XPS analyses                                                              | 78  |

| 2.6         | Chapter summary                                                           | 78  |

| Chapter 3 S | tructure, Technical indicators and the Finite Element Method MTC modeling | 83  |

| 3.1         | Introduction                                                              | 84  |

| 3.2         | Theoretical Calculation of Maximizing Efficiency                          | 84  |

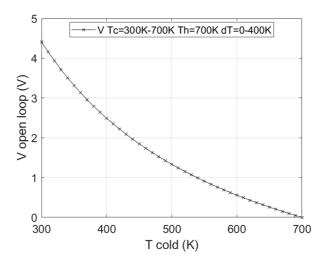

| 3.2.1       | Forward/backward emission and open loop voltage                           | 84  |

| 3.2.2       | Ideal power density and efficiency under no space charge condition        | 91  |

| 3.2.3       | Space charge effect                                                       | 93  |

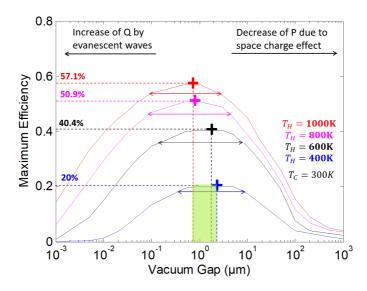

| 3.2.4       | Ideal gap dimension                                                       | 96  |

| 3.3         | Thermal Insulation                                                        | 97  |

| 3.3.1       | Introduction                                                              | 97  |

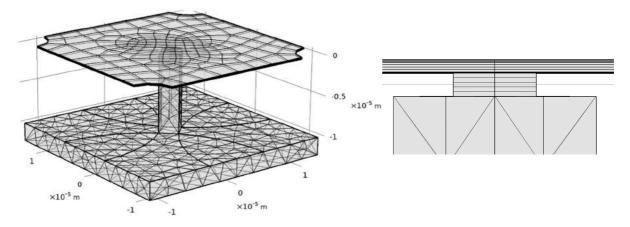

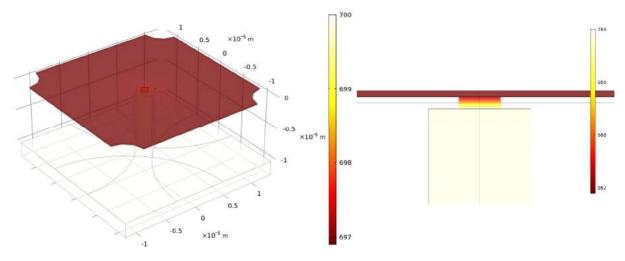

| 3.3.2       | FEM modeling for thermal conductivity of kelvin probe by thermal emission | 99  |

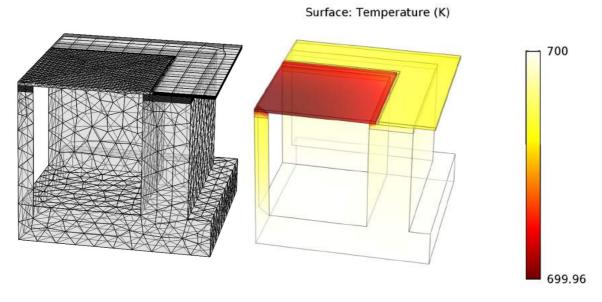

| 3.3.3       | COMSOL modeling for heat flux through contacts by conduction              | 103 |

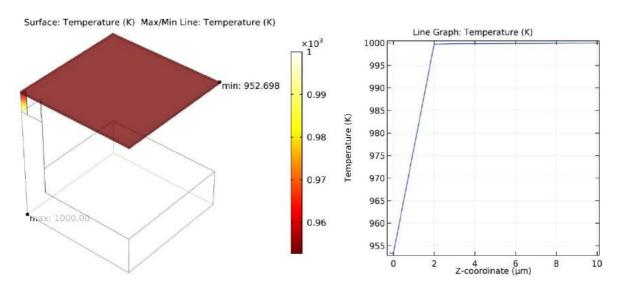

| 3.3.4       | Modeling for capacity of diffuse heat by membrane                         | 107 |

| 3.4         | Conclusion                                                                | 111 |

| Chapter 4 F | abrication of micrometer-gap parallel electrodes                          | 116 |

| 4.1         | Introduction                                                              | 117 |

| 4.2         | Designing the device                                                      | 117 |

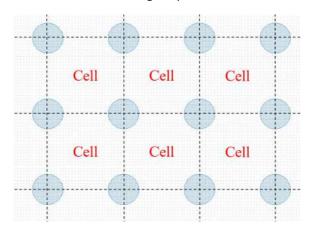

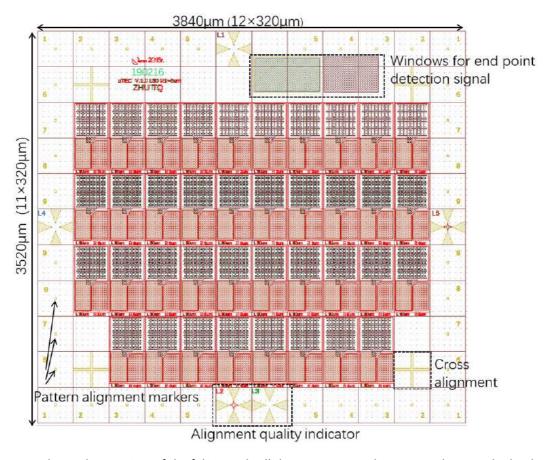

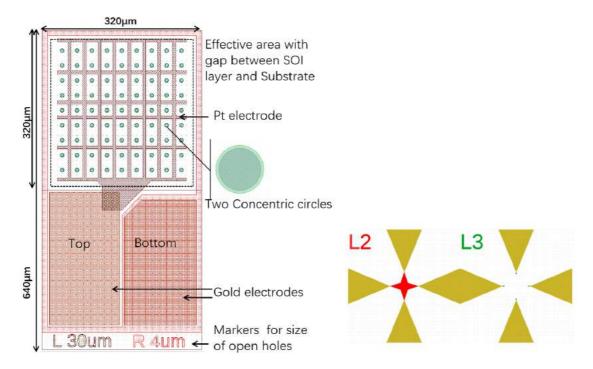

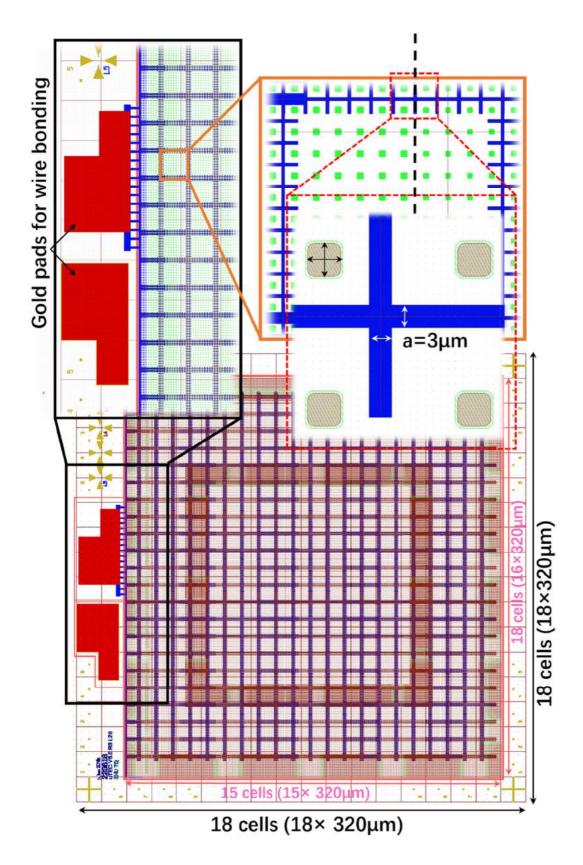

| 4.2.1       | Layout                                                                    | 117 |

| 4.2.2       | Improvements and later version                                            | 121 |

|             |                                                                           |     |

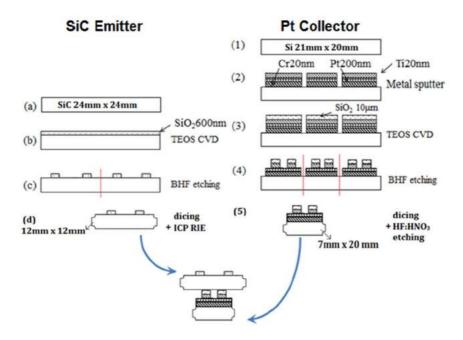

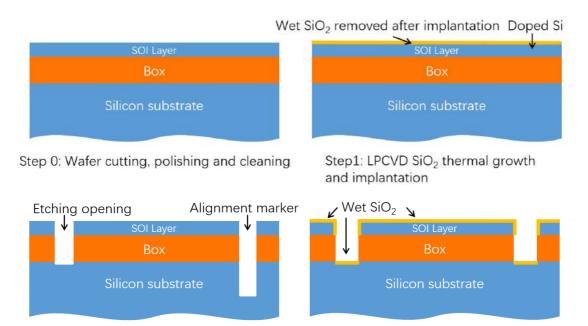

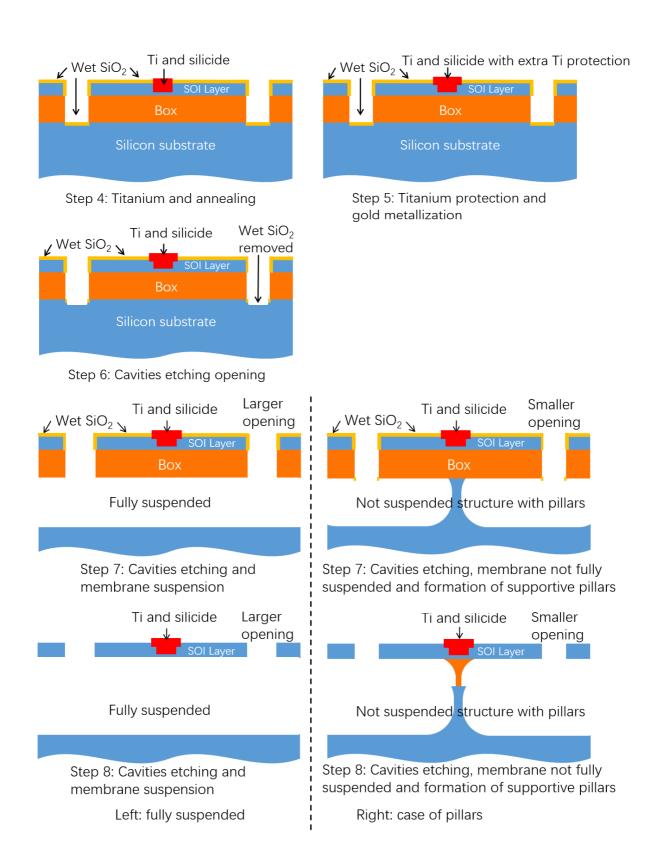

|    | 4.3.1       | Process Overview                                                              | 124 |  |  |

|----|-------------|-------------------------------------------------------------------------------|-----|--|--|

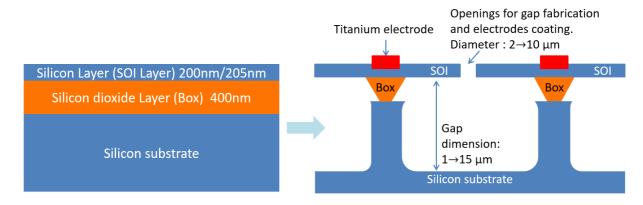

|    | 4.3.2       | Step 0 - SOI wafer                                                            | 126 |  |  |

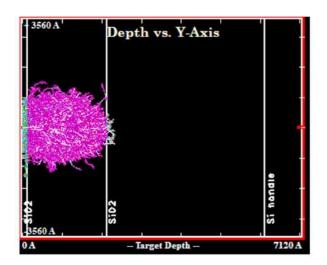

|    | 4.3.3       | Step 1 - SiO <sub>2</sub> thermal growth and implantation                     | 127 |  |  |

|    | 4.3.4       | Step 2 –Alignment marker and etching apertures                                | 129 |  |  |

|    | 4.3.5       | Step 3 - Sidewall protection                                                  | 134 |  |  |

|    | 4.3.6       | Step 4 – Titanium metallization and annealing                                 | 134 |  |  |

|    | 4.3.7       | Step 5 – Titanium protection and gold metallization                           | 139 |  |  |

|    | 4.3.8       | Step 6 – Cavities etching apertures                                           | 141 |  |  |

|    | 4.3.9       | Step 7 – Membrane suspension                                                  | 143 |  |  |

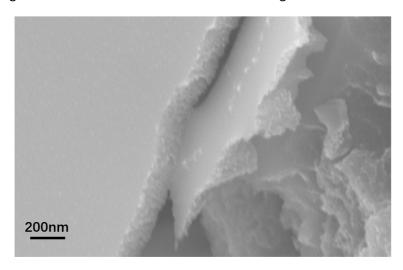

|    | 4.3.10      | Step 8 –SiO <sub>2</sub> etching to minimize pillars cross-section            | 145 |  |  |

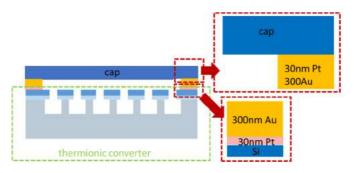

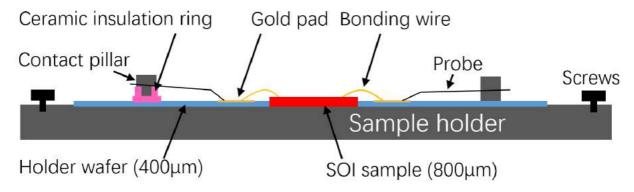

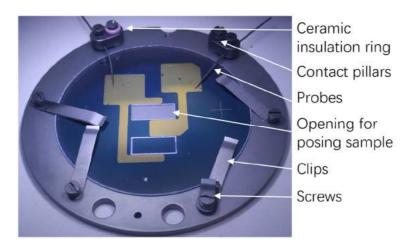

|    | 4.4         | Device mounting for characterization                                          |     |  |  |

|    | 4.4.1       | Mounting design for mechanical fixation, electrical insulation and connection | 148 |  |  |

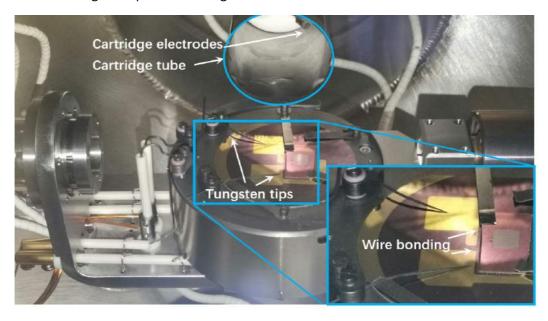

|    | 4.4.2       | Tungsten tips and bonding                                                     | 151 |  |  |

| ,  | 4.5         | Characterization for micro thermionic convertor, analyses and perspectives    |     |  |  |

| ,  | 4.6         | Chapter summary                                                               | 153 |  |  |

| Со | nclusions   | and Perspectives                                                              | 157 |  |  |

|    | Conclusions |                                                                               |     |  |  |

|    | Perspectiv  | es                                                                            | 158 |  |  |

### **General Introduction**

The efficiency of energy generation is one of the main indicators of the development level of human society. While the technology of massive production of high-quality energy, especially electrical energy, have not been revolutionarily innovated for many decades, the importance of harvesting low-quality energy and converting to high-quality energy are keeping increasing [Petroleum 18]. The Unconventional principles of thermoelectric generation project (UPTEG) funded by the European Research Council focuses on the performance of thermoelectrics, including phononic engineering, thermoelectric generator (TEG) based on Seebeck effect and micro thermionic converters based on thermionic emission. This thesis is one part of the UPTEG project and is focused on Micro-Thermionic Convertor (MTC).

Generally speaking, the performance of thermoelectric energy generators (TEG) has been limited by the difficulty of conciliation between electron-crystal electrical conductivity and phonon-glass thermal properties [Rowe 95]. These are two ambivalent factors ruling the conduction of both electrical and thermal currents. The figure of merit (zT) is a value that represents the trade-off between these ambivalent properties [Kittel 96]. In recent decades, with the microelectronics processes, micro/nanoscale structuration is intensively researched and proved to yield better zT by means of electron and/or phonon confinement.

However, the Micro Thermionic Converter, which is an unconventional thermoelectricity converter based on thermionic effect, has theoretically near zero heat conduction, and an equivalent zT about 10 which is higher than solid-state conversion. At the same time, MTCs have all the great advantages of solid-state convertors. It converts heat in to electric current in direct, silent way, without mechanical movement and in a reliable way. MTCs have a remarkably different compared to TEGs. MTCs consist in a pair of parallel electrodes with high temperature difference separated by a micron scale vacuum gap. Both electrodes are coated with low work function materials, which helps hot electrons evaporate and emit from the hot electrodes' surfaces efficiently.

MTC is one type of Thermoelectric Converter (TC). Despite potentially very high current densities, TC is a technical route abandoned in the 90s' due to several reasons. The complexity in the fabrication of large surface parallel electrodes with micrometer gaps in between was more than difficult at that time. Secondly, it is hard to overcome the problems of thermal losses. Last, the space charge effect in large dimension gaps that originally were supposed to be solved with plasma technology leads to more engineering challenges. However, MTC has become a promising solution, due to the fact that the microfabrication technology has been greatly improved. In recent years, scientific research on Thermionic Energy Converters (TEC) revives.

The field of Thermionic Energy Converters is a huge topic that relates solid-state physics, solid-state chemistry, materials science and thermal engineering. The diversity of academic subjects and complexity of the topic makes it hard, if not impossible, to fully demonstrate in one single thesis. So what is presented here focuses on synthesis and characterization low work function alkali metal oxide material films, thermal-gradient finite element modelling simulation, fabrication of prototype MTCs with careful thermal engineering design and characterization.

The targets in this project that we propose include: explore the renewed approach based on electronic micro fabrication technology; test working state at an easier regime with non-ignited and low space charge; build a reasonable temperature difference between electrode at about 100K; propose an

alternative revolutionary solution to power applications in lower power devices from microwatt to watt range.

This manuscript is organized in four chapters. The first chapter presents the general view of thermionic energy conversion including MTC basics, history, the state-of-the-art and our approach in the frame of the UPTEG project. The second chapter focuses on low work function material coating by two different technologies and film work function characterization with different methods and with different equipment. The third chapter reviews existing models and designs of MTCs compared to the prototype of this project with numerical simulation of thermo-isolation and temperature gradient management. The fourth chapter presents the technological part of this thesis including the device layout design, step-by-step fabrication, setup integration and finally prototype characterization. At last, is the overall conclusion to the unconventional thermoelectricity convertor based on thermo-electronic emission.

### Chapter 1

This chapter provides a general view of thermal energy generator/harvester with general review about the motivation for the thermal energy field as a constantly researched topic. At the beginning of this chapter, recent data about global energy consumption is presented. Each year the total consumption is rising, however with limited renewable energy production, the energy crisis needs to be considered seriously. On the other side, thermal energy has a massive potential to be utilized. It is an abundant source and easy accessible, which promises thermal energy generators to a bright future. Then, illustration of the thermionic energy convertor basics, which include its working principles, its structure and its first discovery. Then a history of almost 100 years of conception and innovation of thermionic convertors is studied. Later, the state-of-the-art is reviewed with all recent models and approaches to build efficient MTCs with efforts of different aspects. At last is our approaches in the frame of the UPTEG project with two different material candidates and two coating processes with corresponding device structures.

#### Chapter 2

With this knowledge, the properties of how MTCs work, a highly efficient emitting material must be integrated at the surface of electrodes. The first section will be a simple introduction to work function. Since the work function is not a characteristic of a bulk material, rather as a property of the surface [Halas 10], what the MTCs really require is a film from several atoms thickness or at most several nanometers. This chapter will then present the development of a system with sound workflow to achieve low work function film deposition and characterization. One of the highlights is to match the work function results of different measurement principles on one single sample. This matching process increases the reliability and repeatability of measurement and can help to avoid the influence of Kelvin Probe surface pollution due to chemical vapor deposition in the chamber.

Particularly, we analyze and compare the performances of two alkali metal oxides: Potassium oxides  $(K_xO_y)$  and Cesium oxides  $(Cs_xO_y)$ . These compounds feature a very low work function lower than 1 eV which are even better than alkali like potassium metal and cesium metal. These elements are also abundant and not particularly dangerous in experimental conditions. In our workflow these alkali material were firstly deposited on highly-doped clean silicon surface to form a thin film. The oxide thin films were characterized by Kelvin Probe, photoemission and thermionic emission measurements. Then X-ray photoelectron spectroscopy and energy-dispersive X-ray spectroscopy were also tested. All the results on the synthesis of these thin films were obtained under high vacuum and controlled temperature.

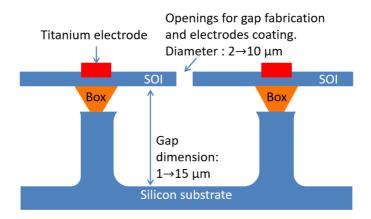

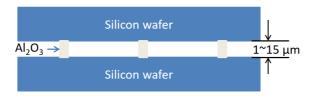

### Chapter 3

Although, in theory, the MTCs has little to no thermal leakages and not like other thermoelectric generator that need to balance between electron-crystal electrical conductivity and phonon-glass thermal properties, thermal leakages also need to be carefully considered in real devices. Furthermore, unlike TEGs, the heat gradient direction of MTCs are perpendicular to the wafer surface. A considerable temperature difference, ideally over 100 degrees, needs build up in less than one-millimeter distance. This is the biggest challenge for the real MTC devices. To meet this demand a layer of both electrical and thermal isolation material is needed in between the electrodes, which at the same time provides structure stability.

This chapter focused on designing possible structures and corresponding parameters for the design of a prototype with maximum efficiency in real experimental conditions. Different finite element analysis were performed to explore the technical indicators for an efficient MTC with acceptable thermal losses and best temperature difference between the two electrodes.

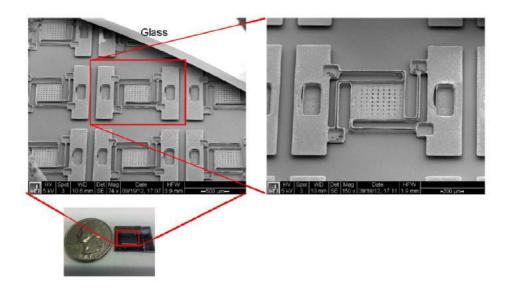

### Chapter 4

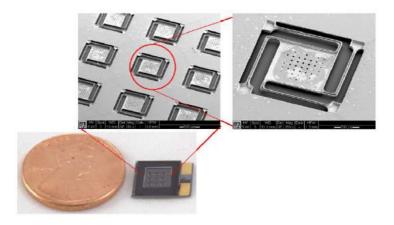

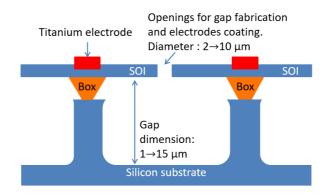

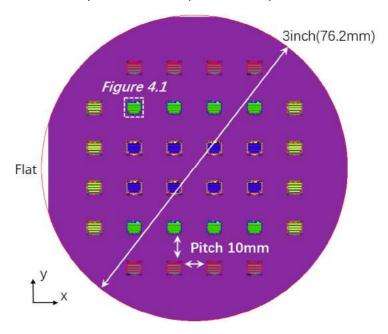

This chapter presents engineering and technological aspects of this work including design and fabrication of the prototype. As a prototype, the design needs to be harmless, cheap, industrially compatible and reliable based on existing nano/micro-fabrication processes and technology. One of the best solution is to fabricate upon silicon on insulator (SOI) wafer with silicon (Si) layer thickness of 200nm.

After fabricating the electrodes with gaps, we integrate it to our characterization platform before low work function film deposition on electrode surface in-between the vacuum gap. Then the MTC was ready to be tested. The prototype MTC proves that thermo-convertors based on thermo-emissions effect are one environmentally friendly, cheap and industrially compatible generator with much higher potential than other energy harvest devices.

| [Petroleum 18] | British Petroleum, "BP Statistical Review of World Energy 2018" British Petroleum, 67th annual statistical report on world energy, June 2018 |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| [Rowe 95]      | D. M. Rowe, CRC Handbook of Thermoelectrics (CRC, Boca Raton, 1995).                                                                         |

| [Kittel 96]    | Charles Kittel, "Introduction to Solid State Physics".                                                                                       |

| [Halas 10]     | Stanislaw Halas, Tomasz Durakiewicz, "Is work function a surface or a bulk property?", Vacuum, 85, 486-488 (2010)                            |

### Introduction Générale

L'efficacité de la production d'énergie est l'un des principaux marqueurs du niveau de développement d'une société humaine. Bien que la technologie de production massive d'énergie de haute qualité, en particulier l'énergie électrique, n'ait pas été révolutionnée depuis de nombreuses décennies, l'importance de la récolte d'énergie de faible qualité et la conversion en énergie de haute qualité est de plus en plus forte [Petroleum 18]. Les principes non conventionnels du projet de production thermoélectrique (UPTEG) financé par le Conseil Européen de la Recherche se concentrent sur les performances thermoélectriques, y compris l'ingénierie phononique, le générateur thermoélectrique (TEG) basé sur l'effet Seebeck et les micro convertisseurs thermiques à base d'émission thermoïnique. Cette thèse est une partie du projet UPTEG et se concentre sur le Convertisseur Micro-Thermoïnique (Micro-Thermionic Converter MTC).

D'une manière générale, la performance du générateur d'énergie thermoélectrique (TEG) est limitée par la difficulté à concilier une conductivité électrique forte, comme celle d'un cristal, et une conductivité thermique faible, comme celle d'un verre [Rowe 95]. Il s'agit de deux facteurs ambivalents qui gouvernent la conduction du courant électrique et thermique. Le Facteur de mérite (zT) est une valeur qui représente le compromis entre ces propriétés ambivalentes [Kittel 96]. Au cours de la dernière décennie, avec les procédés de la microélectronique, la micro/nano structuration est vue comme une voie pour obtenir une amélioration de zT grâce au confinement des électrons et/ou phonons.

Cependant, dans le cas des Convertisseurs Micro Thermoélectroniques, qui sont des convertisseurs non-conventionnels basés sur l'effet thermoïnique, la conduction de chaleur est théoriquement proche de zéro. Cela permet un zT équivalent à environ 10 qui est plus élevé que la conversion à l'état solide. Alors que, dans le même temps, les MTCs ont tous les avantages liés à l'état solide. Ils convertissent la chaleur en courant électrique en directement, silencieusement, sans parties mobiles et de manière fiable. Les MTCs ont un principe remarquablement différent des TEGs. Les MTCs consistent en une paire d'électrodes parallèles avec une différence de température élevée, séparées par un vide à l'échelle du micron. Les deux électrodes sont revêtues de matériaux à faible travail de sortie, ce qui permet aux électrons de s'évaporer de la surface de l'électrode chaude.

Comme les TEGs, le MTC est un type de convertisseur thermoélectrique (TC). En dépit de densités de courant potentiellement très élevées, TC est une voie technique abandonnée dans les années 90 pour plusieurs raisons. La complexité de la fabrication de grandes électrodes parallèles avec des écarts micrométriques était plus que difficile à l'époque. Deuxièmement, il est difficile de surmonter les problèmes de pertes thermiques. Enfin, l'effet de charge spatiale est prépondérant pour les gaps de grande dimension. Ce phénomène était censé être résolu par la technologie de plasma qui conduit à encore plus de défis d'ingénierie. Cependant, le MTC est une solution prometteuse, en raison du fait que la technologie de microfabrication a été grandement améliorée. Ces dernières années, la recherche scientifique sur les convertisseurs énergétiques thermoïniques (TEC) est ravivée.

Le champ des Convertisseur Micro-Thermoïnique est un sujet énorme qui allie physique à l'état solide, chimie à l'état solide, science des matériaux et de l'ingénierie thermique. La diversité du sujet académique et la complexité du sujet rendent difficile, voire impossible, de le traiter pleinement en une seule thèse. Donc, ce qui est présenté ici se concentre sur la synthèse et la caractérisation de faible travail de sortie des films d'oxyde de métal alcalin, simulation de modélisation d'éléments finis à

gradient thermique, prototype de fabrication de MTCs avec une conception d'ingénierie thermique minutieuse et caractérisation des prototypes du MTC.

Les objectifs de ce projet sont notamment: explorer l'approche renouvelée basée sur la technologie de micro-fabrication; tester l'état de fonctionnement à un régime plus facile avec une charge d'espace faible; établir une différence de température raisonnable entre les électrodes d'environ 100K; proposer une solution alternative aux applications de puissance dans les appareils de faible puissance de la gamme microwatt au watt.

Ce manuscrit est organisé en quatre chapitres. Le premier chapitre présente la vision générale de la conversion de l'énergie thermoïnique, y compris les bases de MTC, l'histoire, l'état de l'art et notre approche dans le cadre du projet UPTEG. Le deuxième chapitre se concentre sur le revêtement de matériaux à faible travail de sortie par deux techniques différentes et la caractérisation du travail de sortie de film avec différentes méthodes et avec différents équipements. Le troisième chapitre présente les modèles existants et la conception des MTCs comparés au prototype de ce projet avec une simulation numérique du transfert et de l'isolation thermique et de maintien du gradient de température. Le quatrième chapitre présente la partie technologique de cette thèse, y compris la conception et l'agencement des dispositifs, la fabrication étape par étape, l'intégration et enfin la caractérisation des prototypes.

[Halas 10] Stanislaw Halas, Tomasz Durakiewicz, "Is work function a surface or a bulk

property?", Vacuum, 85, 486-488 (2010)

[Kittel 96] Charles Kittel, "Introduction to Solid State Physics". 1996

[Petroleum 18] British Petroleum, "BP Statistical Review of World Energy 2018" British

Petroleum, 67th annual statistical report on world energy, June 2018

[Rowe 95] D. M. Rowe, CRC Handbook of Thermoelectrics (CRC, Boca Raton, 1995).

### Chapter 1 Thermionic Energy Conversion

This chapter provides a general view of thermal energy generators/harvesters and the motivation for the thermal energy field as a constantly researched topic.

At the beginning of this chapter, recent data about global energy consumption is presented. The total consumption is rising each year, however with limited renewable energy production, the energy crisis need to be considered seriously. On the other side, thermal energy has a huge potential to be utilized with its abundant sources and accessibility, which promise all thermal energy generators to a bright future. Compared to other energy harvesting devices TEC has many advantages, while several challenges remain to be solved.

Later in this chapter, the thermionic energy convertor basics are illustrated, which include its working principles, its structure and its first discovery. The history of almost 100 years of conception and innovation of thermionic convertors is presented. Later, the state-of-the-art is reviewed with all recent models and approaches to build an efficient MTC with efforts of different aspects. At last, our approaches in the frame of the UPTEG project with two different material candidates and two coating processes with corresponded device designs.

### 1.1 Energy conversion and generation

- 1.1.1 Energy consumption and electric energy in the world

- 1.1.2 Conventional Thermal energy generator based on Seebeck effect

- 1.1.3 Unconventional Micro Thermionic energy Convertor and its structure

- 1.1.4 Comparison of two thermal electric convertors

- 1.1.5 Thermionic energy convertor challenges

### 1.2 TEC history from 20<sup>th</sup> century to 21<sup>th</sup> century, the history and future

- 1.2.1 Early research during 20th century

- 1.2.1.1 Richardson Equation

- 1.2.1.2 Beginning from 1915, the first proposition by Schlichter

- 1.2.2 Thermionic development during cold war and thermionic crisis in 1990s (Thermionic Quo Vadis report)

- 1.2.3 Renewed interest with nanotech and low work function materials on TECs

### 1.3 State-of-the-art

- 1.3.1 Limitations of work function and recent solutions

- 1.3.1.1 Low work function materials

- 1.3.1.2 Nano structure method to lower work function

- 1.3.1.3 Intercalation

- 1.3.1.4 Photo-enhanced TEC and PETE

- 1.3.2 Researches and recent solutions for space charge reduction

- 1.3.2.1 Negative electron affinity (NEA)

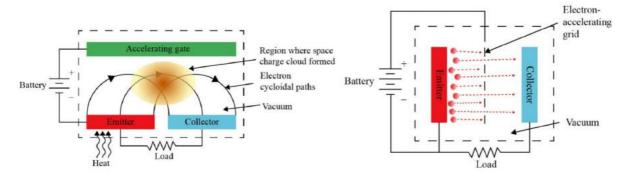

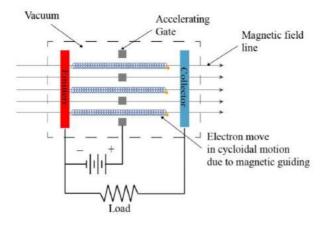

- 1.3.2.2 Micro Thermionic electric convertor structure

- 1.3.2.3 Integration of electric and magnetic fields

### 1.4 Approaches in the frame of the UPTEG project

- 1.4.1 Low work function material candidates

- 1.4.2 Inspiring structure designs lead to our design

- 1.4.2.1 U-shape membrane design by Berkeley University

- 1.4.2.2 Emitter and collector stack structure by Tohoku University

- 1.4.2.3 Expectation and technical indicators for our design

- 1.4.3 Proof of concept under vacuum (parallel electrodes)

- 1.4.4 Encapsulation of Micro Thermionic electric convertor

### 1.5 Chapter summary

### 1.1 Energy conversion and generation

### 1.1.1 Energy consumption and electric energy in the world

Energy is not only a basic scalar physical quantity but also the cornerstone of development of human civilization. With the process of understanding and taking advantage of different types of energies, from potential energy, kinetic energy to chemical energy, from thermal energy to electric energy, the human productivity improves together with human society. The modern society, nowadays, is maintained by the enormous energy supply and is in constantly rising demand of all types of energies. The energy consumption rate is a barometer of the human society. According to [Petroleum 2018] a constant growth of consumed primary energy can be observed during last decades. In 2010, a serious financial crisis began causing a significant recession in both industrial branches and the tertiary industry, which is revealed as a global drop in primary energy consumption.

Years after the start of second industrial revolution in the late 19<sup>th</sup> century, the electrification of industry took place [Nye 90], followed by household electrification at 1920s in cities. With the massive utilization of electricity and electrification the inexpensive production of aluminum, chlorine, sodium hydroxide and magnesium became possible [McNeil 90]. However, around 100 years after electrification, in 2014 the fossil energy production still takes a ratio of 81%. The latest data show, in year 2017, global electricity production reaches 25551.3TWh [REN21 2018], among which 73.5% is generated by fossil fuel and nuclear energy which is known as not renewable sources. On the other side, 26.5% of global electric energy was provided by the renewable sources with an annual increase of 2% compared to 2016. Thanks to the development of photovoltaic power generation and massive construction of wind power farms, year 2017 has the greatest renewable electricity ratio increase during the past decade.

|                                       |      | 2013    | 2014    | 2015    | 2016    | 2017    |

|---------------------------------------|------|---------|---------|---------|---------|---------|

| Global electricity production         | TW∙h | 23457.6 | 23918.8 | 24289.5 | 24930.2 | 25551.3 |

| Fossil fuel energy and nuclear energy | %    | 77.9    | 77.2    | 76.3    | 75.5    | 73.5    |

| Renewable energy                      | %    | 22.1    | 22.8    | 23.7    | 24.5    | 26.5    |

| Hydropower                            | %    | 16.4    | 16.6    | 16.6    | 16.6    | 16.4    |

| Wind                                  | %    | 2.9     | 3.1     | 3.6     | 4.0     | 5.6     |

| Biomass                               | %    | 1.8     | 1.8     | 2.0     | 2.0     | 2.2     |

| Solar                                 | %    | 0.7     | 0.9     | 1.2     | 1.5     | 1.9     |

| Geothermal, CSP and Ocean             | %    | 0.4     | 0.4     | 0.4     | 0.4     | 0.4     |

Table 1.1 Ratios of electricity generation from BP Statistical Review of World Energy 2018

Table 1.1 presents the trend of global energy production by different resource. In between 1980 to 2013, in average, world electricity generation by renewable sources has an increase rate of about 3.6%. This annual increase rate in the closest five recent years is almost 8.2%, which is more than twice the previous rate. Due to the high efficiency of electricity use, compared to other energy consumption methods, electrical energy is surely a better choice. So all the efforts to increase the production of electricity from renewable energy are worthwhile.

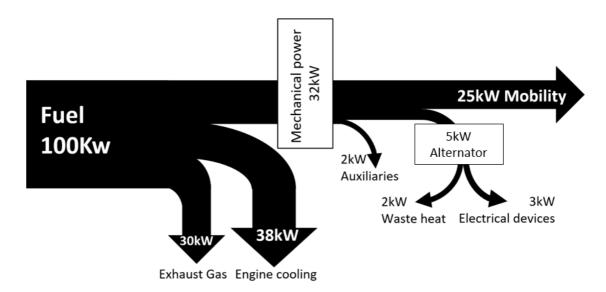

On the other side, the typical non-renewable energy, the fossil fuel energy has a much lower efficacy compared to electricity. For instance, most of all modern vehicles operate with internal combustion engines that consume fossil fuel. However, despite the pollution of the internal combustion engine, only one quarter of all input energy is transformed into movement. Figure 1.1 present the energy lost at each stage and resulting in a final efficiency of about 25%. If counting from on wheel power, the efficiency may be even lower. One thing worthy to mention is that even through the absolute efficiency

seems to be a low value, it is not that bad when compared to Carnot efficiency due to the intrinsic limitation of all heat engines.

Figure 1.1: Sankey diagram for diesel light duty vehicles.

In European Union, 12% of the total  $CO_2$  emission are generated by internal combustion engine [EU 2015]. Furthermore, more pollution like sulfide, nitrogen oxides NOx (NO and  $NO_2$ ) and solid micro particles are also not negligible. These widely distributed engines lead to a bigger problem dealing with the pollution. For thermal power electrical stations operated by fossil fuel, the pollution is concentrated and can be well treated by various specific devices and processes, which is not possible for vehicles. The example above tells that electrical energy is a clean and better solution for the human energy demand.

With the conclusion that electricity is among the best energy form for human industry and living, facing a great accelerating of energy consumption, the necessity of efficient power conversion is needed more than ever before. Unfortunately, all known conversion types for electricity power has some defects either products great amount of pollution or dangerous by-products. For some renewable electrical energy production methods, the defects are either high cost or negative impact on natural environment. The idea of energy production from waste energy is thus receiving more and more attention recently [Harb 11], [Harne 13], [Matiko 14] and [Radousky 12].

So from where the energy can be generated? Nowadays, one of the most popular answer is solar energy, which is the ultimate source of fossil fuel energy, hydropower, wind energy etc. Beginning from year 2005, the photovoltaic devices and total power generation by photovoltaic increased rapidly. Thanks to the technology development and the governmental actions, the price of this renewable energy production device has dropped over 95% in a few years, which accounts for the explosive development of this clean energy. In recent years, the industrially produced solar cells have reached a highest efficiency of 21.5%, while the highest efficiency of multi-junction solar cells in laboratory is reported to be 46.0% [Dimroth 14]. However, the character of photovoltaic energy means it is highly dependent on fatal conditions like weather and sunshine direction.

On the other side, when the question is that from where the energy can be harvested? Harvesting from thermal energy is the most promising answer. During the electricity production and transportation about two third of total input primary energy was lost and converted into thermal energy

[International energy agency 2008] and only around 31.5% of the input energy was delivered to consumers as electric energy in 2007. For some more instance, 19.5%-50% of overall primary energy consumption turns into heat losses of dwelling, 6.5%-16.7% of energy consumption in industrial scenario is lost in form of heat. All over the world, a surprisingly high rate of energy is lost in the form of heat. In other words, more energy is lost than it is consumed. So to preserve the economic growth and develop an alternative energy sources is a critical task for all humans before the fossil fuels heading to depleted.

In this report, an unconventional method of energy harvesting and generation will be presented with details. The very first idea of energy harvesting comes from harvesting electrical energy from heat. Thermal energy is what most types of energy ends into. What's more, thermal energy is the most abundant and easily accessible energy form. Therefore, it is one of the best source for energy harvesting. Fortunately, with the development of semi-conductor micro fabrication technology, this unconventional energy harvesting method can be miniaturized and has a promising future.

### 1.1.2 Conventional Thermal energy generator based on Seebeck effect

Talking about harvesting electrical energy from heat, the first and most popular solution is thermoelectric generator (TEG), which is also named Seebeck generator. As it is named, the TEG has a working principle based on Seebeck effect. A TEG works like any heat engines, with the given thermal input and temperatures at both sides forming a temperature gradient, has an output as electrical potential. The fact that a heat flow passing through material leads to a drift of charge carriers, which consequently result in a voltage difference. Thomas Johann Seebeck firstly discovered this phenomenon [Seebeck 25] [Seebeck 26] in year 1821.

It seems to be a great way to convert energy from heat to electricity and it has been produced for military and aerospace applications for decades. However, it has a low typical efficacy of 5-8%. Note that these devices are reversible and most popular usage is heat pumps. The biggest problem is limited by the development of material science. The performance of thermoelectric generation has been limited by the difficulty of conciliation between electron-crystal electrical conductivity and phonon glass thermal properties [Rowe 95]. In other words, to design thermoelectric generators with good performance, a material with high conductivity and at the same time a low thermal conductivity property is needed.

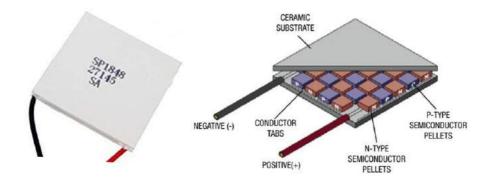

Figure 1.2 (a) Photo of commercial TEG product; (b) Inner structure of TEG module.

Figure 1.2 presents a typical commercial TEG module and its inner structure, which is an array of P-type and N-type semiconductor in series. With the ceramic substrate of different temperature at two

side, a temperature gradient is established along each semiconductor. Charge carriers of different types will drift from hot to cold. With the movement of these carriers, a thermal current and voltage potential are created.

Still, in real case scenarios, the TEG has some engineering defaults that need to be solved: High generator output resistance which is not friendly for low impedance loads as a power supplier; low thermal conductivity which is not a good harvester for heat source as a digital microprocessor; and limited capacity for release cold-side heat to air which add an additional parasitic loss to total output.

Despite the challenges facing TEG, with the advantages of thermoelectric generator, it is still the most popular and wide production device for thermal energy harvester/generator.

### 1.1.3 Unconventional Micro Thermionic energy Convertor and its structure

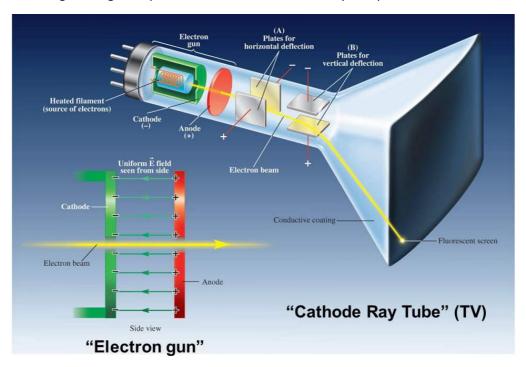

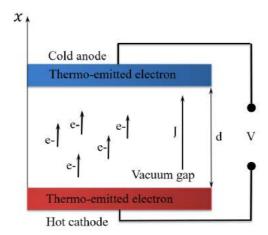

In this section is focused on the basic principal of Micro Thermionic energy Convertor. The basic principles are simple, and phenomenas are around us in daily life. As we know when metal is heated to a high enough temperature, the electrons will have higher energy. When electrons have enough energy to overcome the work function barrier, electrons can be emitted from a metal surface. Just like Figure 1.3 presented, in old cathode tube TV, screen shines when electrons hit the fluorescent screen, and these electrons ejected from electron gun are firstly emitted from heated filament. The heated filament has a high enough temperature and electrons can easily escape from filament surface.

Figure 1.3: Principle of Cathode Ray Tube TV.

The Micro Thermionic energy Converter or MTC works in the same principle as presented in Figure 1.3. MTC converts thermal energy into electrical energy directly. The basic structure of convertor consists of a high temperature electrode and a low temperature electrode parallel positioned with a vacuum gap separating the two electrodes. This direct energy conversion is based on thermoelectric emission or thermionic emission. Being in contact with heat source, the hot cathode reaches a high temperature, and electrons from this surface get enough energy for extraction and evaporation from the surface of the conductive material. Some electrons will transport through the vacuum gap and arrive at the cold

anode. This phenomenon was firstly demonstrated in 1880 by Thomas Edison. During the experiment to determine the origin of filament breaks inside lamps and the blackening of incandescent lamp bulbs, the thermionic electron emission was observed [Waits 03] [Fleming 96]. Then in 1915, this energy conversion principle was proposed by W. Schlichter [Schlichter 15].

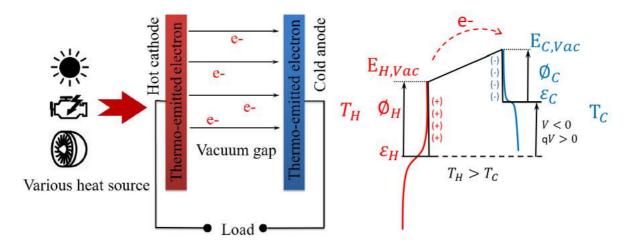

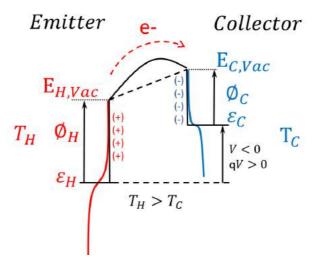

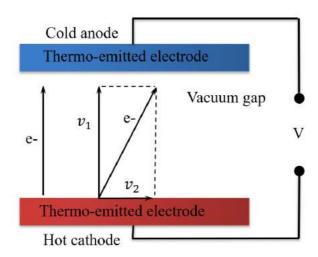

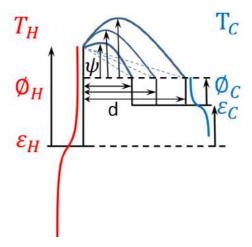

Figure 1.4 (a) Generic architecture of a MTC; (b) Energy diagram of MTC.

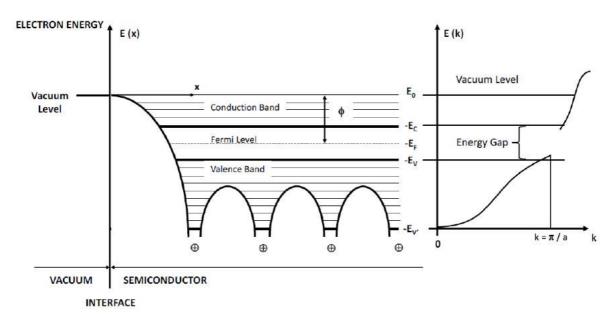

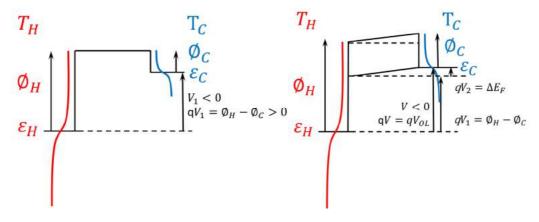

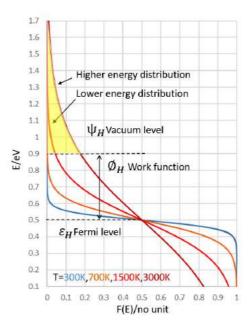

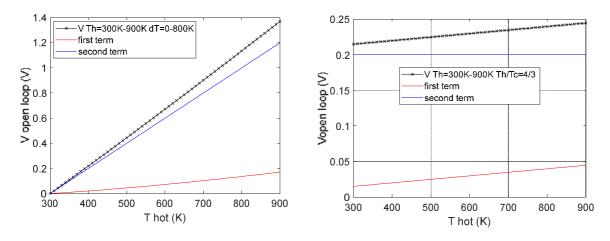

Presented in Figure 1.4(a), the simplest structure of Thermionic energy Converter is constituted by two parallel electrodes facing each other, with thermionic electrons evaporated and emitted from hot electrode to the cold electrode. The thermionic current can then pass through a load connected to the load circuit of the converter. For Micro Thermionic Converter, the "micro" term applies to the vacuum gap distance. MTC with several micrometer large vacuum gap will get best performance. The Figure 1.4(b) is an energy diagram representing the energy band of hot cathode and cold anode. Firstly, like the architecture diagram these two electrodes are separated by a vacuum gap. Both side of electrodes has its electrical potential and corresponding Fermi level  $\varepsilon$ . The work function  $\emptyset$  is the property of each electrode surface material. Then the hot cathode is heated by absorbing the heat from any kind of energy source. With the increasing temperature, the electrons have enough energy jump to vacuum level  $E_{Vac}$  and some may evaporate from its surface. Some electrons arrive at cold anode and if the circuit is open, potential will consequently build up at the anode. The cathode losing electrons will be positively charged. With negative charge on anode, Fermi level (and thus vacuum level) shifts up, repelling backward electrons. Finally, an equilibrium is reached when the forward and backward currents equalize. The energy band in the gap can be present with a striate line connecting vacuum level of cathode and anode. Detailed research about the size of vacuum gap, corresponding heat loss crossing the gap and final efficiency as a function of gap parameters will be discussed in chapter 3.

With great advantage for MTC energy conversion conception is its simple physical phenomenon. Moreover, without any moving element, MTC is particularly suitable for miniaturization and compatible with all existing MEMS technology. It is not hard to imagine that one day in the close future with sensor and its power supplier all integrated on the same silicon chips, sensors can be easily distributed at more position without the limitation of power supply. Finally yet importantly, theoretically speaking the MTC will reach a high efficiency, which can be as much as 21% at low temperature working condition ( $T_H$ =400K  $T_C$ =300K). The efficiency of MTC is calculated by the total output divided by total input power. To well understand the efficiency of a heat engine, the efficiency is compared to Carnot limit. Carnot efficiency is the theoretical maximum efficiency for all reversible heat engine at given working condition. 21% total efficiency is 85% of Carnot's limit, which is an efficiency far forward comparing to conventional technologies.

### 1.1.4 Comparison of two thermal electric convertors

After presenting two thermal energy generators based on different physical phenomena, a simple comparison will be illustrated in this sector. Begin from what these two thermal convertors have in common. First of all, due to the fact that thermal energy is abundant and easily accessible energy, both types of thermal electric convertors have a stupendous potential and a bright future. Secondly, the research and development of a better TEG or MTC are highly depending on material science. For TEGs the need to find a material with low thermal conductivity and high electrical conductivity is essential. This property of materials, in thermoelectric research field, is evaluated by zT, the figure of merit.

$$zT = \frac{S^2}{\rho \kappa} T = \frac{S^2 \sigma}{\kappa_e + \kappa_l} T$$

Eq 1. 1

The figure zT is a property of material and calculated by Eq 1.1, where S is Seebeck coefficient,  $\rho$  is electrical resistivity,  $\sigma$  is electrical conductivity,  $\kappa$  is the thermal conductivity,  $\kappa_e$  is electronic thermal conductivity and  $\kappa_l$  is lattice thermal conductivity and T is cold temperature. The zT value for thermal energy generators can be calculate by the properties of used material. For MTCs, the corresponded zT values is obtained by fitting it efficiency by the same working condition, the T<sub>c</sub>. Unlike efficiency, which is a variable value at different working Temperature for a same device, figure of merit zT present the ability of a given material or heat engine to efficiently produce thermoelectric power in all working temperature range.

So why the MTC has a higher zT than TEG? One main difference is the thermal conductivity through the device. For the TEG, heat passes through thermoelectric materials by conductivity. In other words, the thermoelectric material physically connects the heat source and cold heat sink. While the MTC works differently in the case of thermal flow. By eliminating the material between hot energy source and cold electrode, the only heat exchange through the vacuum gap is by radiation. This results in much lower thermal loss and greater efficiency. With zT values, the maximum efficiency at different temperature can be calculated by the following equation.

$$\eta = \left(1 - \frac{T_C}{T_H}\right) \cdot \frac{\sqrt{1 + zT} - 1}{\sqrt{1 + zT} + \frac{T_C}{T_H}}$$

Eq 1. 2

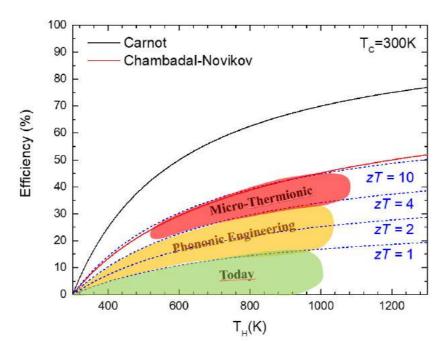

Figure 1.5 presents, at given cold temperature equal to 300K, thermal engine efficiency for different values of the figure of merit working at different input hot temperature. Generally speaking, the thermal engines nowadays have an equivalent zT value of about 0.7. The refinement of the technology has a possible limit of up to 2. Some of the best efficient geothermal power plants have an equivalent zT of about 4. Furthermore for some nuclear power plant and solar power plant, an equivalent zT of 10 can be possible [Vining 09]. For a MTC with electrode work function at 0.5eV the equivalent figure of merit is about 10. This means that MTC can reach a total thermal efficiency of 50% if it is working at nuclear powered heat source, which is about 1300K.

$$\eta_{Carnot} = 1 - \frac{T_{C}}{T_{H}}$$

Eq 1. 3

$$\eta_{\mathit{CN}} = 1 - \sqrt{\frac{T_{\mathsf{C}}}{T_{\mathsf{H}}}}$$

Eq 1. 4

In Figure 1.5, two reference solid lines are presented. The back line is Carnot efficiency at given condition, and the red solid line is Chambadal-Novikov efficiency. In the case of vacuum thermionic energy conversion  $T_{\rm C}$  and  $T_{\rm H}$  are temperature corresponding to cold anode and hot cathode. The Carnot efficiency  $\eta_{Carnot}$  is the maximum efficiency possible for reversible engines. The red line

represents the efficiency at maximum power output for all endo-reversible thermal engines. Corresponding equations for Carnot and Chambadal-Novikov efficiency are presented above.

Figure 1.5 At different figure of merit, temperature-efficiency plots.

During the design process of a reliable thermal generator, in order to achieve high efficiency in the system requires extensive engineer design in order to balance between the heat flow through the device and maximizing the temperature gradient across them. For our project, the discussion of efficiency and maximization of temperature gradient will be present in Chapter 3.

What is the difference between these two thermal electrical generators? First, due to different generation principles the 3D structure of TEG is more complicated and need either new material or doping technology with dedicated structure for each cell of semiconductor. The complicated structure means it will meet more challenges when facing thermal stress in operation environment. On the other hands, for MTCs, structure is much simple. The only concern of MTCs' structure is building the temperature gradient and limit heat flow. The second difference in between two types of thermal generators is the geometric direction of studied materials process and the direction of temperature gradient direction. In the case of TEG, the temperature gradient has same direction as material geometric length direction. For MTCs, the low work function coating material on the electrodes' surface are perpendicular to thermal gradient. Due to the fact that the power output of thermal electrical device is proportional to its surface. The fabrication of a massive scale TEG device are much more complicated. On the other side, the surface coating process can usually applied on a bigger surface. Last is the potential of two principles. The Seebeck effect is easy to tackle and consequently lots of TEGs have been commercialized and products for civilian use can be found on the market. The MTCs are much more difficult and far from the process of commercialization, due to the current limitation by space charge effect and the limitation of old mechanical fabrication methods. However with newly developed Micro/Nano-fabrication process in 21 century, MTC has much larger potential to be researched and discovered.

### 1.1.5 Thermionic energy convertor challenges

Similarly to TEG, the research and development of TEC are limited by material science. In order to make electrons easier to escape from the hot cathode's surface, a lower work function material is necessary. With a material of 0.5eV work function, the equivalent zT can be as high as 10, while with a work function of 1.0eV, the zT value drop to below 1 at less than 1000K working range. Moreover, the corresponding coating process of this low work function material is critical, in order to have a stable and uniform coating on cathode substrate. A stable coating process is critical. The surface will be facing a tough mechanical and thermal condition during working circumstances. In this case, when a high temperature will be applied on one electrode, a thermal stress will be applied on the structure. So a stable coating material and process will contribute greatly in fabrication and increase device stability.

The mechanical structure in between electrode and in micro vacuum gap should be rigid and resist the atmosphere pressure with vacuum inside. In addition, it should be as small as possible with material of minimum thermal conductivity. Other than thermal stress, mechanical fatigue caused by large number of thermal cycles should be taken in to consideration.

### 1.2 History from 20th century to 21th century, the history and future

Other than challenge of finding a better material with lower work function and improving some engineer stabilization properties, there are many methods to approach a better performance for Thermionic Convertors (TC), including:

- **High particle velocity/grid** [Child 1911] [Langmuir 1913]

- Arc-mode (ignited mode)/hybrid [Langmuir 1923] [Schlichter 1915]

- Plasmatron principle [Hatsopoulos 1963]

- Resonance ionization [Hernqvist 1958] [Lee 2012]

- Reduce inter-electrode gap [Kiejna 1979] [Durakiewicz 2001] [Ibragimov 2001]

In this section, history of TCs with different scientific approach at different decades will be presented.

### 1.2.1 Early research during 20th century

After the first scientific report about the electron emission by Elster and Geitel in 82[Elster 82], and the discovery of Edison effect from Edison' lamps in 1884, the cathode rays were identified by Thomson as negatively charged particles of fundamental importance [Thomson 97] [Thomson 99]. Then, after Stoney had suggested the term electron [Stoney 94] in 1894, Richardson presented an approach that quantified the electron emission current. In 1901, Richardson published the results of his experiments: the current from a heated wire seemed to depend exponentially on the temperature of the wire with a mathematical form similar to the Arrhenius equation. The equation was firstly put forward by Arrhenius in order to describe chemical reaction rate, which is dependent on the absolute temperature.

### 1.2.1.1 Richardson Equation

Later, the thermal emission law had a mathematical form [Richardson 01][Richardson 03]:

$$J = AA^*T^2 exp\left(-\frac{q\phi_s}{\nu_T}\right)$$

Eq 1. 5

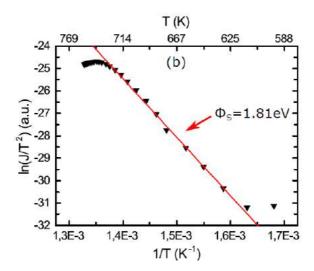

In Eq 1.5, J is the emission current density, T is the temperature of the sample,  $\emptyset_S$  is the work function of the metal, k is the Boltzmann constant, and  $AA^*$  is the thermal emission constant. Here A a universal constant. The mathematical form of  $A^*$  is presented in Eq 1.6. The  $\exp\left(-\frac{q\emptyset_S}{kT}\right)$  represents the Maxwell-Boltzmann distribution. The Arrhenius linear plot with  $\frac{1}{T}$  as X axis and  $\ln\left(\frac{J}{T^2}\right)$  as Y axis will present the relationship between absolute temperature and thermionic current presented in Figure 1.6.

Figure 1.6 Arrhenius linear plot

$$A^* = \frac{4\pi mk^2 e}{h^3} = 1.20173 \times 10^6 Am^{-2}K^{-2}$$

Eq 1. 6

or  $A^* = 120 Acm^{-2}K^{-2}$  Eq 1. 7

In these equations, m and e are the mass and charge of an electron, and h is Planck's constant. Eq 1.6 is an approximate theoretical value of Richardson's constant. With the mathematical relation presented by the equation above, the thermoelectric emission was connected to the work function of the emitter cathode. After analyzing experimental data, it was observed that the work function for metals has a linear relationship with temperature.

$$\emptyset = \emptyset_0 + \alpha T$$

Eq 1. 8

In Eq 1.5 the values of constant  $\alpha$  has an order of  $10^{-4} eV$ .  $K^{-1}$  according to experimental data, and is an order of magnitude smaller with theoretical calculations. [Durakiewica 01][Ibragimow 01]

### 1.2.1.2 Beginning from 1915, the first proposition by Schlichter

In 1915, with interest in phenomena surrounding glow effect around electrical heated solids, Schlichter studied a process that would "in principle present a possibility to directly convert heat energy to electrical energy as the economical method of such a procedure would be of great technical importance" [Schlichter 15]. In his report, Schlichter described the efficiency of the thermoelectric converter in an equation similar to Carnot efficiency.

$$N_0 = \frac{T_2 - T_1}{T_2}$$

Eq 1. 9

In Eq 1.6,  $T_2$  is the temperature of the glow-electrode (emitter) and  $T_1$  is the temperature of the counter-electrode (collector). One noticeable thing is that, although the calculated efficiency of thermionic convertor, which is close to Carnot limit, is highly overestimated. In Schlichter first experiment, thermionic energy convertor with platinum electrodes at 1000°C with a reported efficiency of  $1.5 \times 10^{-11}$ . According to the conclusion in his report, the low efficiency magnitude was mainly attributed to radiation losses without addressing the space charge phenomenon. Although the first experimental result is not auspicious, thermionic energy convertor remains to be one of the generator offers maximum efficiency amount all types of energy convertor.

## 1.2.2 Thermionic development During cold war and thermionic crisis in 1990s (Thermionic Quo Vadis report)

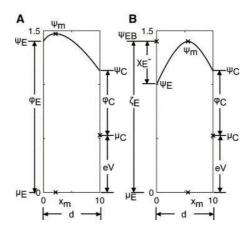

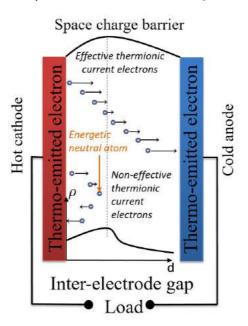

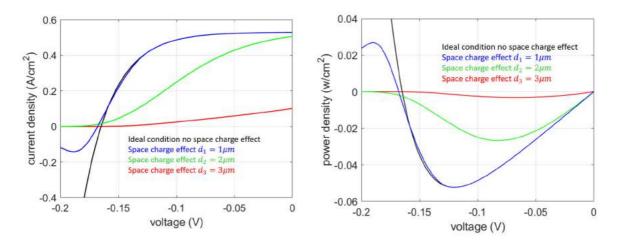

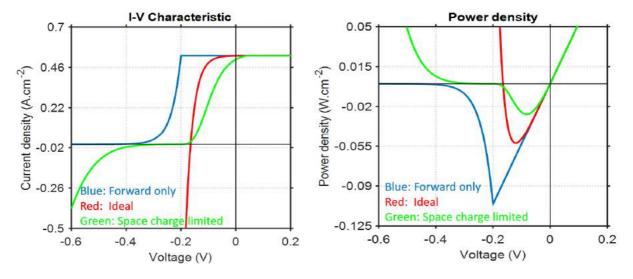

Child and Langmuir firstly described the space charge effect in 1910s. Describing that the saturated thermionic electron emission current building a sufficient electrical field that prevents an electronic charge accumulation adjacent to the emitter boundary [Child 11] [Langmuir 13] [Langmuir 23]. However, in 1955, 40 years after the first proposition by Schlichter, the space charge effect was officially recognized as one of two most limiting factors for Thermionic convertors. In 1958, Hernqvist postulated two key efficiency limitations, including electrode work function difference and interelectrodes space charge effects presented in Figure 1.7 [Hernqvist 58]. A more detailed discussion of space charge effect can be found in Chapter 3.

Figure 1.7. Energy diagram of MTC with space charge barrier located in the gap of inter-electrodes.

In order to limit space charge effect, Hernqvist, in his experiment, introduced positive ions, which can be generated through impact ionization for lower cathode temperature of 1200-1500°C in an ignited or arc-mode converter [Hernqvist 63]. In the same year, an ignited cesium converter operating in plasma mode is reported by Hatsopoulos, which lowers the space charge barrier [Hatsopoulos 63]. During the process of investigation of thermionic emission, Hatsopoulos introduced two types of TECs, namely, vacuum TECs(VTECs) and vapor TECs [Hatsopoulos 65].

For vapor TECs, the inter-electrodes space is filled with cesium vapor and space charge effect is neutralized by the positive ions, because cesium is easily ionized. In this case, vapor TECs has a better performance in aspects of implementation and thermal isolation structure design, compared to VTECs.

So early researches were usually focused on the vapor TECs. However, vapor TECs in real case scenarios are facing problems like insufficient positive ions and unfavorable effects of elastic collision in the interelectrodes space. In one word, due to the limitation of fabrication techniques, most research and development on TECs were focused on vapor TECs in mid to late 20<sup>th</sup> century.

As we know, electrode work functions are the other main limitations for efficiency of thermionic converters. Efforts to find an alternative method to lower work function were also made in early 20<sup>th</sup> century. In 1925, Langmuir and Kingdon published a report illustrating the ionization of cesium vapor when a filament is heated to 1200K with a negatively charged cylinder surrounded. The work function of tungsten filament during this process was lowered to 2.69eV, instead of 4.53eV. [Langmuir 25] Further study were also carried out by Wilson in 1966. Thermionic converter with polycrystalline electrode surface and different cesium vapor filling the gap [Wilson 66].

Back to year 1960s, thermionic converters were studied not only for academic research, but also by government and industry. In the early 1960s, U.S. government conducted a program of large-scale thermionic converter focused primarily on solar and nuclear powered systems. While the program failed to produce convincing results and eventually terminated, research on thermionic energy converters were carried on, for example application of laser excitation of cesium atoms for continuous ion generation was also suggested in 1976 by Hansen from NASA [Hanson 76]. Years later, in Soviet Union, two large nuclear reactors equipped with a 5kW power Thermionic energy converter were successfully orbited and operated in space within the TOPAZ program in 1987. This program was abandoned due to budget restriction and political reasons in 1988.

Figure 1.8 Thermionic reactor of TOPAZ II at Kirtland Air Force Base

Then at 1990s, with little advancement of thermionic scientific research and lack of advanced technology and fabrication techniques, the research and development of thermionic converter met a great crisis, which lasted for more than a decade. It became obvious that large scale TEC was a deadend.

### 1.2.3 Renewed interest with nanotech and low work function materials on TECs

At the beginning of 21<sup>st</sup> century, with the great improvement of micro/nanofabrication and material science, the enthusiasm of researching thermionic energy converter is revived. In one way, the study of low work function material has been improved due to massive renovation of micro/nanofabrication technology, for example Chemical Vapor Deposition (CVD) and nanowire growth. In another way, the second challenge of TECs, to minimize the space charge effect has some break through. Many new methods like using negative electron affinity (NEA) property or incorporate external electric and magnetic fields were proposed recently. Together with the MEMS technology,

which make a closed-spaced micro gap TECs possible to fabricate, TECs as an energy harvester and generator meet its shirley valentine (second wind).

### 1.3 State of the art

In this section, recent solutions for TECs will be presented in two parts. The first part is focused on work function of electrodes, and the second part is research about minimizing the space charge effect for TECs. These two challenging factors have been the biggest obstacles before the commercialization of TECs.

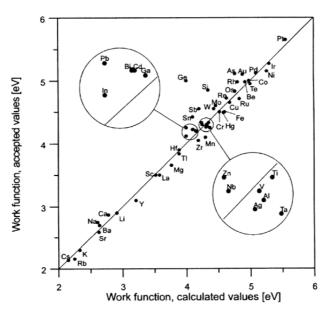

#### 1.3.1 Limitations of work function and recent solutions

According to thermal emission law by Richardson the work function of the electrodes is one the the most significant factor that affect the efficiency of a TEC. Work function is a parameter of material surface. It defines the amount of energy required for an electron to transit from Fermi level to vacuum level. In other words, it is the minimum amount of energy for an electron to be evaporated from material surface. In the case of a TEC, it is the first barrier for electrons before emitted out of the surface and arrive at inter-electrodes space.

In order to maximize the efficiency of a TEC, both emitter and collector must have a low enough work function. The output voltage and work function of two electrodes will be further discussed in chapter 3.

### 1.3.1.1 Low work function Materials

Alkali metals, in the field of TECs, are one of the most widely studied materials. They are well known for the low work function characteristics. In early research of 20<sup>th</sup> century, the alkali metals, especially ionized cesium, were key components for an effective vapor TECs. However, recent research with modern coating technology, alkali metals are regarded as good emitter surface material candidates.

In 2001, work function reduction of platinum was reported by using cesium adsorption method. The work function of platinum dropped from 5.6eV to 1.4eV after the process [Hishinuma 01]. Later, similar cesium adsorption was carried out on semiconductor. And the reduction of work function on silicon was observed [Sinsarp 03].

With the development of advanced coating process, alkaline earth metal can also be deposited on silicon or metal substrate. For example, in one research of thermally isolated low work-function emitter, both barium and barium oxide (BaO) were deposited onto a polycrystalline-silicon carbide substrates, with thin adhesive tungsten layer by Lee's group [Lee 14]. The work function of electrode with barium oxide reached as low as 1.7eV. Similar work function drop was observed on barium coated sample. According to the report, the system with barium oxide was running stable for hours with a temperature of 900-1400K. Other than barium oxide, LaB<sub>6</sub> is a popular material for many types of thermal emission application, which has a work function equals to 2.5eV. The high melting point and low evaporation rate at high temperature makes LaB<sub>6</sub> the best for cathodes in applications like SEM, microwave tubes, electron lithography, electron beam welding, X-ray tubes and so on.

With chemical vapor deposition method, our group has tested different alkali metal film coating techniques, including potassium and cesium. A significant drop was observed on hydrogen-passivated (100) p-type silicon substrate. For silicon substrate with potassium oxide film, the work function dropped from 4.7eV to 1.35eV. For cesium oxide film, the final work function dropped to 1.66eV [Morini 14] [Giorgis 16]. Details about the coating technique, operation and measurement will be presented in Chapter 2.

Not only alkali metal and alkaline earth metal are good candidates for a low work function emitter, diamond film and graphene-based TEC were able to reach a high efficiency. An extremely low work function of 0.9eV was acquired with phosphorus-doped polycrystalline diamond films on metallic substrate. The film was reported stable at sustained temperature of 765°C [Koeck 09]. Moreover, for nitrogen-incorporated, ridged nano diamond films on silicon substrates can achieve a work function of 1.39eV and can sustain a temperature of up to at least 900°C [Paxton 10].

### 1.3.1.2 Nano structure methods to lower work function

Surface nanostructure is one new method to lower the work function. The newly named field electron emission is an example. In this case, electrons emission is enhanced by a field-effect named electrostatic field. It is normally referred as cold emission, as it occurs at lower temperature compared to planar emitter TECs. A study carried out by Pan and his group producing aligned SiC nanowires (SiCNWs) on stainless steel substrates [Pan 00]. The structure proved to feature a superior field enhancement factor for thermionic emission for given materials and conditions.

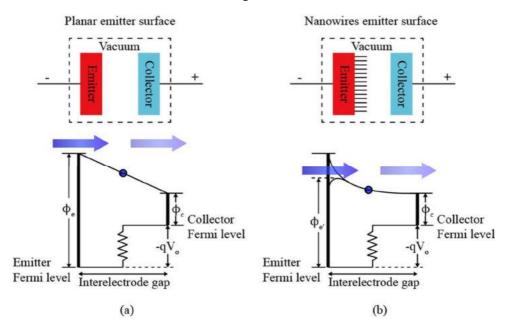

Figure 1.9 Schematic energy diagram of two types of electron emission TEC from (a) planar emitter surface and (b) nanowires emitter surface. [Smith 06] [Kamarul 16]

Figure 1.9 presents two energy diagrams, comparing electron emission from different surfaces. Experimental results prove that the nano-tips make electrons arrive at vacuum level at lower energy cost. This is due to Schottky barrier lowering [Smith 06]. Multiple publications have announced that SiCNWs are compatible with microfabrication techniques, feature good thermal and chemical stability and are thus excellent candidates for high-temperature MEMS devices. The field-enhanced TEC with SiCNWs seems to be another promising solution.

In 2007, Xi and his group reported an experiment, which combines both field emission and BaO/SrO coating for a TEC device. In the experiment, a thin barium strontium oxide uniform coating was successfully deposited on the surfaces of vertically aligned CNTs grown on tungsten ribbons. Although the field enhancement factor was not optimal due to the diameters of nano-tips, the work function of emitter was reduced to 1.9eV with a field enhancement factor of 467 [Jin 07].

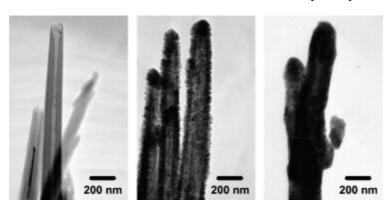

Figure 1.10 (a) TEM image of CNTs before coating. (b) 50 nm coated CNTs. (c) 100 nm barium strontium oxide coated CNTs.

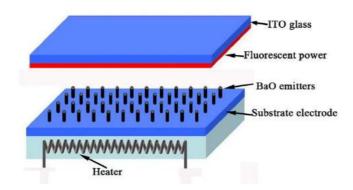

Later, a thermal-assisted electric field was demonstrated and field emission device was fabricated by Cui and his group with barium oxide coating on CNTs [Cui 17]. The calculated results of BaO emitter work function dropped from 1.44eV at room temperature to 0.96eV at 593K.

Figure 1.11 Scheme of thermally-assisted field emitter [Cui 17].

Recent research confirms that the thermionic emission current acquired from individual hot CNTs is not following the Richardson-Dushman law [Wei 14] [Wei 10]. Wei and his group claimed that during *in situ* multi-probe measurement, the measured electron emission density is more than one order of magnitude higher than prediction by Richardson's law. In the same time, the Arrhenius plot were found to exhibit an upward bending feature instead of straight lines.

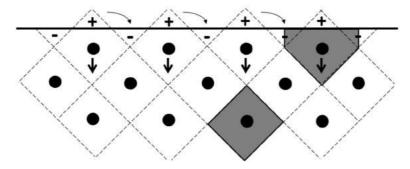

### 1.3.1.3 Intercalation

Intercalation is a chemistry process where guest molecules or ions are inserted or included into materials with layered structures. The host materials usually has a layered structure like carbon or graphite. Intercalation expands the Van der Walls gap between layers, which needs energy. This energy is supplied by charge transfer in between the host and the guest.

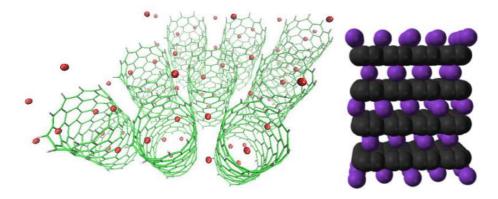

Figure 1.12 (a) Model of intercalation of potassium into single-wall CNTs (b) Model of intercalation of potassium into graphite

Figure 1.12 present two intercalation models with famous intercalation host, the carbon nanotube and graphite. Carbon nanotube (CNT) is another promising nanomaterial. Due to its excellent electrical conductivity and thermal stability. A research by Westover and his group showed that the intercalation of potassium into single-wall and multiwall CNTs resulted in the work function of 2eV for both application [Westover 10]. The work function of pristine CNTs, which has similar value as graphite, is usually about 4-5eV [Ago 99] [Sun 02]. The reduction of work function by intercalation with potassium metal atoms is significant.

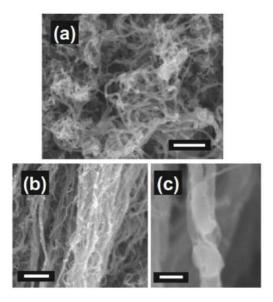

Figure 1.13 FESEM images of K/MWCNTs, showing metal, presumable potassium, inside individual MWCNTs. Scale bars are 500 nm, 1  $\mu$ m and 100 nm, in (a) (b) and (c), respectively. [Westover 10]

Similar experiment has been tested on different types of graphitic carbon nanofibers (GCNFs). The direct reaction of GCNFs with molten potassium gives potassium/graphitic carbon nanofiber (K/GCNF) intercalates a stoichiometry-controlled potassium loading. Thermionic emission is observed on stage-1 ( $C_8K$ ; 29 wt% K) K/narrow tubular GCNF intercalate at 300°C. The stage-1 K/herringbone GCNF displayed a work function of 2.2eV and remained thermally stable at the temperatures of up to 1000°C. Compared to the work function of carbon nanotubes, which is about 4.6eV minimum that depends on parameters optimization, a reduction of 2.4eV is achieved. [Michel 08].

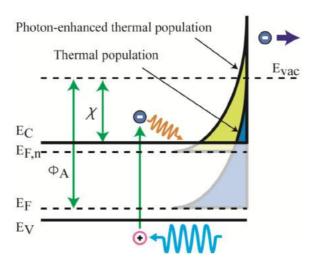

#### 1.3.1.4 Photo-enhanced TEC and PETE

Another alternative method to enhance the evaporation of hot electrons is known as Photon-Enhanced Thermionic Emission (PETE). An additional conduction band carrier population created by photoexcitation can enable this new type of electron emission process. PETE, in case of p-type materials, combines photovoltaic and thermionic effects into a single physical process, which takes advantage of both the high per-quanta energy of photons and the available thermal energy due to thermalization and absorption losses [Schwede 10].

Figure 1.14 Energy diagram of PETE process. Photon-generated electrons increase the conduction-band population, leading to effective work-function decrement and enabling the device to harvest both photon and heat energy. [Lee 14]

The scheme of the PETE process presented in Figure 1.14 consists in three stages. First, electrons in valence band  $E_V$  are excited by photons into the conduction band  $E_C$ . Second, they rapidly thermalize within the conduction band and diffuse throughout the emitter. Finally, electrons that reach the surface with energies greater than the electron affinity can emit into the vacuum. The PETE process is advantageous especially for p-type emitters compared to thermionic emission from n-type materials due to the larger output voltage. It results that in p-type semiconductors Fermi level is near to valence band and away from conduction band. With the theoretical model of PETE above, a conversion module was fabricated for serving Concentrated Solar Power (CSP) applications and patented in 2012 [Trucchi 15]. This module named  $ST^2G$  is a solar thermionic-thermoelectric generator. By involving both thermionic and thermoelectric conversion stages and connected thermally in series, the calculated overall conversion efficiency was claimed to be up to 30% or greater. Although PETE is firstly discovered in a study of concentrated solar power applications [Schwede 10] and is still intensively studied in solar cell utilization to allow electrons carry both the photon energy and the thermal energy. It is considered as an essential improvement in TEC research.

### 1.3.2 Research and recent solutions for space charge reduction

Space charge effect is a important phenomenon for thermionic emission. The evaporated electrons filling a vacuum space and resulting in a negatively charged cloud and an electric current passing through the vacuum. The first assumption is that the distribution of electrons is even. Then according to Poisson equation, we have:

$$\nabla^2 \Psi = -\frac{\rho}{\epsilon_0}$$

Eq 1. 10

$\epsilon_0$  is dielectric constant of vacuum,  $\Psi$  is the energy barrier of space charge effect. If  $\rho$  is constant (even distribution),  $\Psi$  is a parabola. However, due to the fact that thermionic current  $\vec{J}=ne\vec{V}$  does not depend on position, while the kinetic energy of electrons change according to the position due to the existence of electoral barrier. So the even distribution assumption is wrong. So, the Poisson equation can be written as:

$$\frac{\partial^2 \Psi}{\partial x^2} = -\frac{\rho(x)}{\epsilon_0}$$

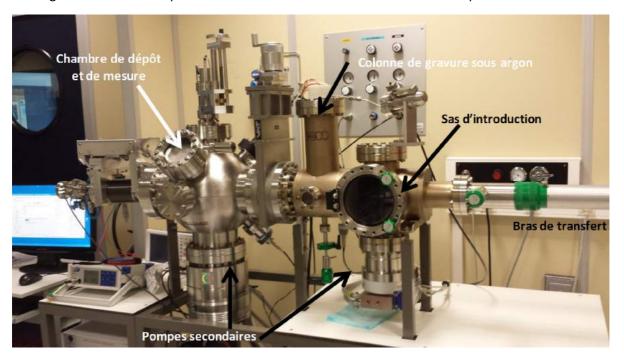

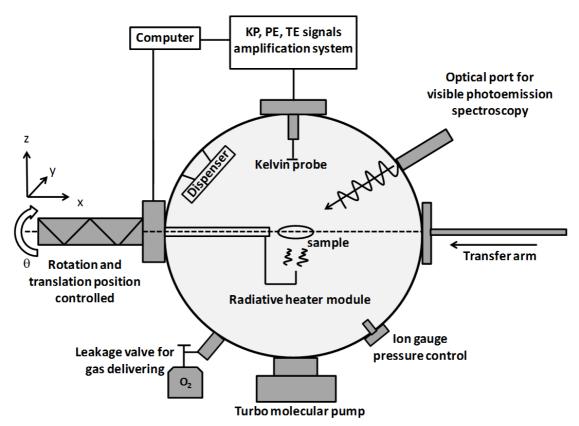

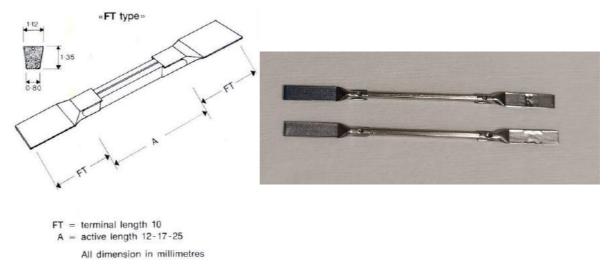

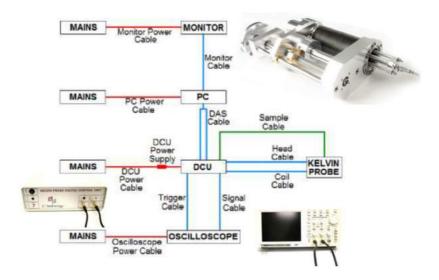

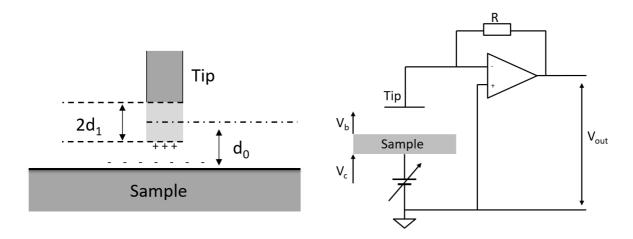

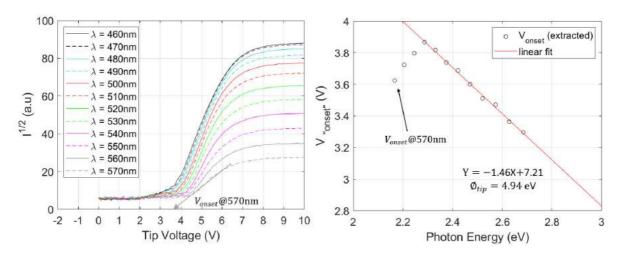

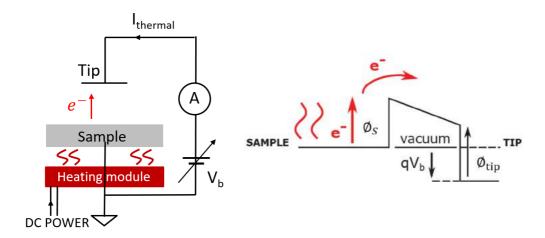

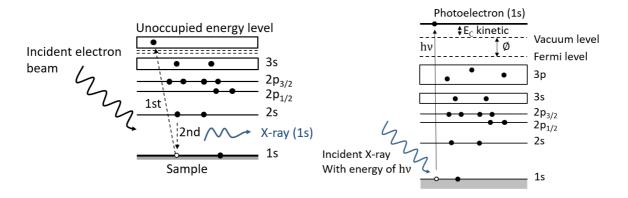

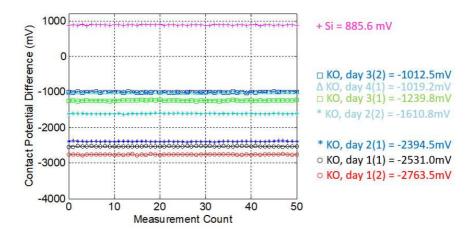

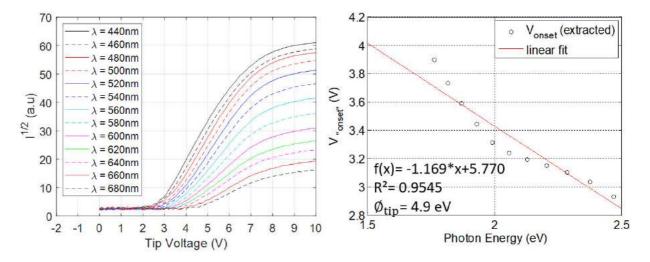

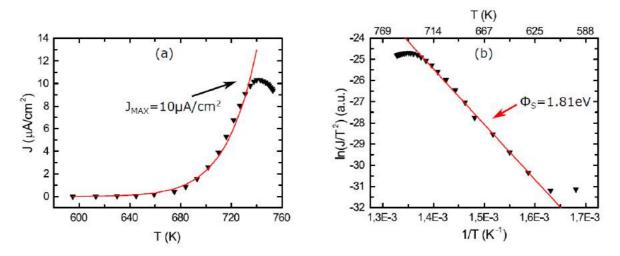

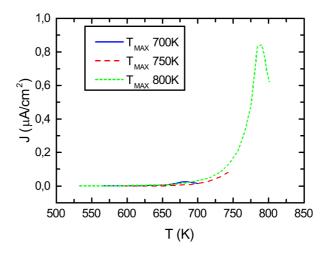

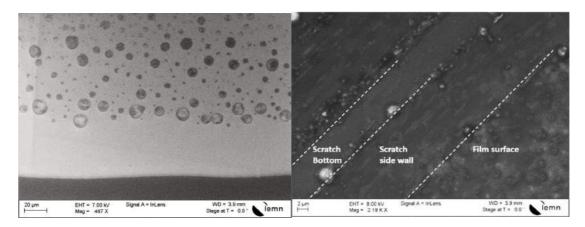

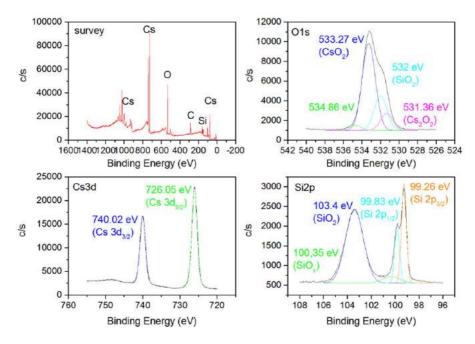

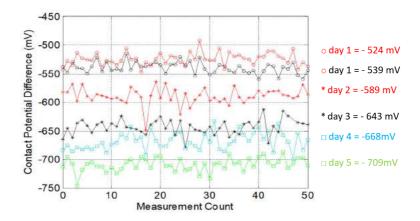

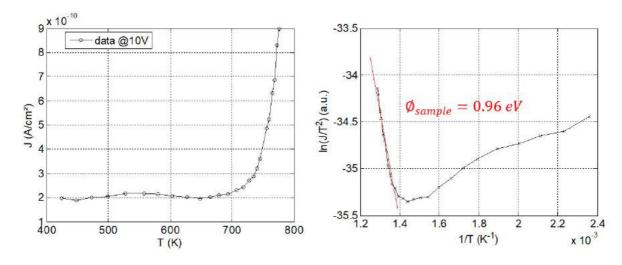

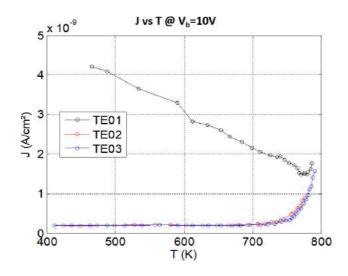

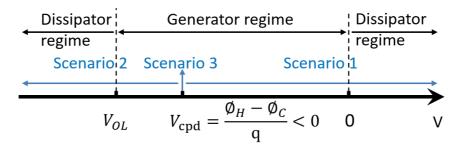

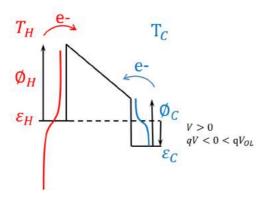

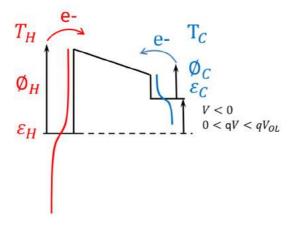

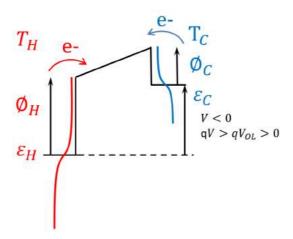

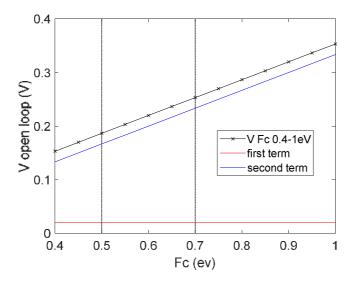

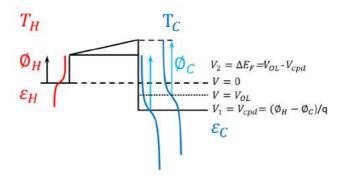

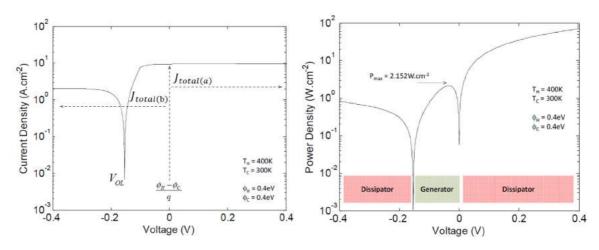

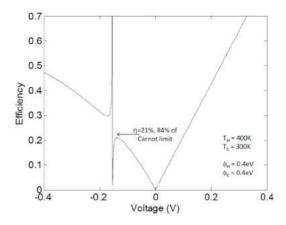

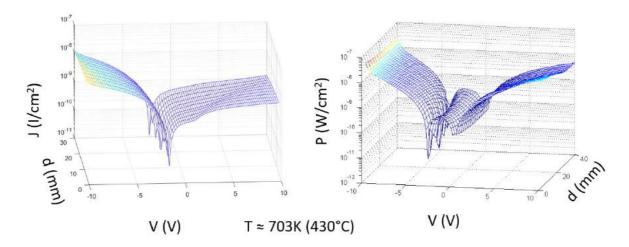

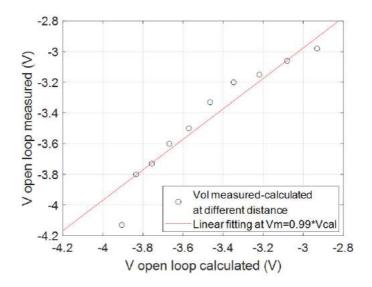

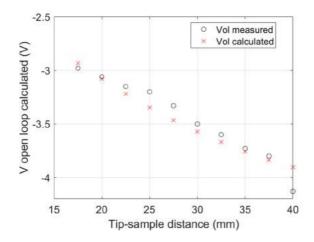

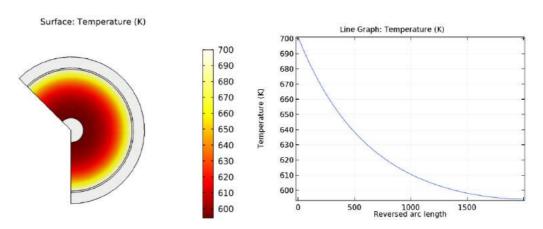

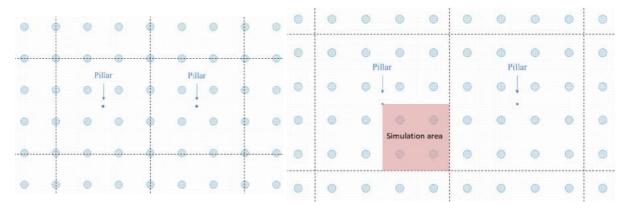

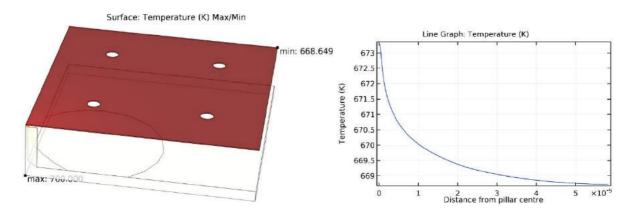

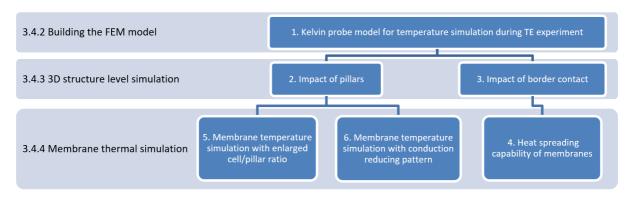

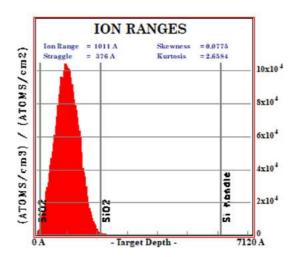

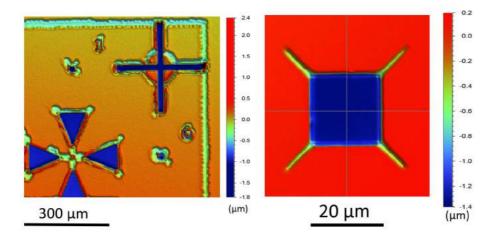

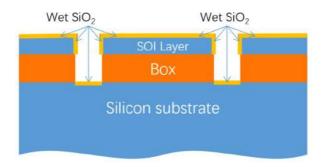

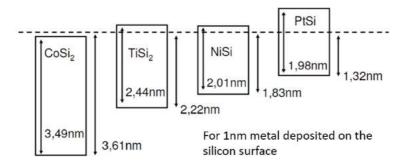

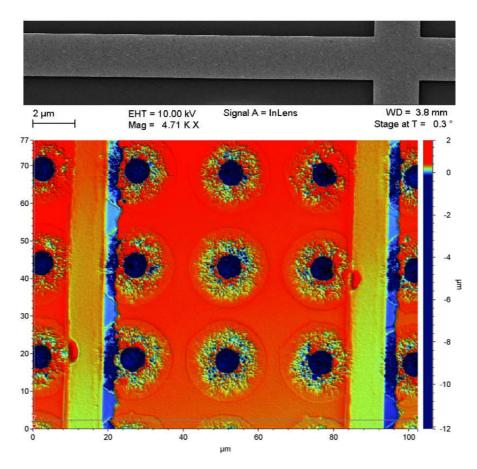

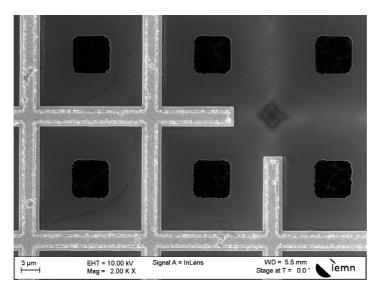

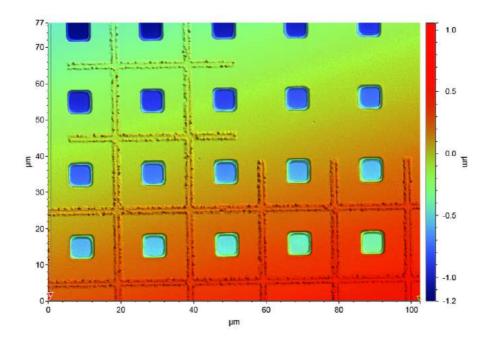

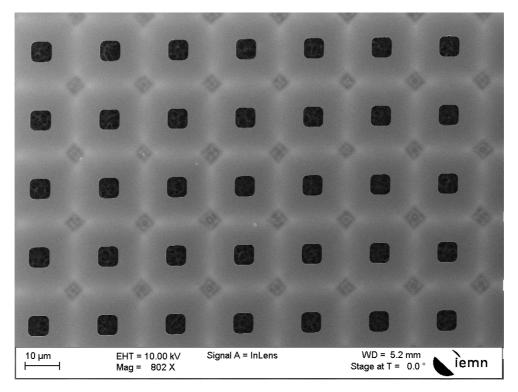

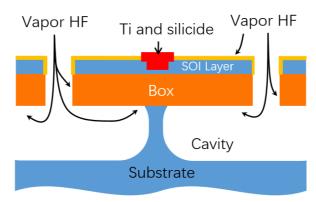

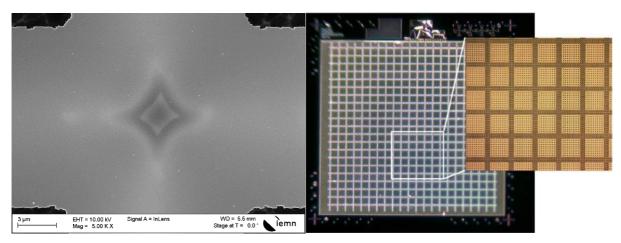

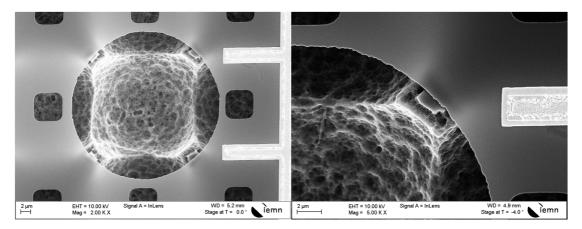

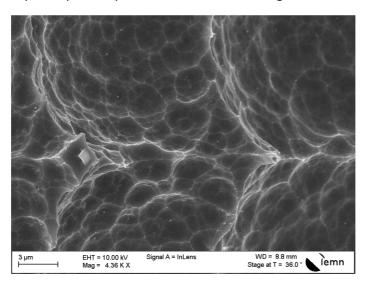

Eq 1. 11