# THESE

# Présentée à l'Université de Lille Ecole Doctorale Sciences Pour l'Ingénieur

Pour obtenir le grade de :

# **DOCTEUR de l'UNIVERSITE**

Spécialité : Électronique, microélectronique, nanoélectronique et micro-ondes

Par Issa ALAJI

# Design and characterization of power detectors in 55-nm BiCMOS technology for 5G and THz applications

Conception et caractérisation de détecteurs de puissance en technologie BiCMOS 55 nm pour les applications 5G et THz

Soutenue le 5 Novembre 2020 devant la commission d'examen

Membres du jury :

Pr. Christophe Lethien Pr. Dominique Schreus Pr. Eric Kerhervé Dr. Djamel Allal Mr. Daniel Gloria Dr. Jean François Villemazet Pr. Guillaume Ducournau Pr. Christophe Gaquiere

IEMN Lille KU Leuven IMS Bordeaux LNE Paris ST Crolles Thales Toulouse IEMN Lille IEMN Lille Président Rapporteur Rapporteur Examinateur Invité Invité Co-Directeur de thèse Directeur de thèse

## Acknowledgments

I have been pursuing my PhD degree for almost three years in the IEMN laboratory at Villeneuve d'Ascq, thanks to the European project «EURAMET - ADVANT» which finances this work.

First of all, I would like to thank all the jury members. I would thank *Pr. Christophe Lethien* for his interest in this work, and for accepting to chair the review commission. I would thank *Pr. Dominique Schreus*, and *Pr. Eric Kerhervé* for accepting to review this work. I also thank *Mr. Daniel Gloria*, *Dr. Allal Djamel* and *Dr. Jean Francois Villemazet* for accepting to examine this work.

I would like to express my sincere gratitude to my supervisors *Pr. Christophe Gaquière* and *Pr. Guillaume Ducournau* for their presence, time and advices which helped me to go on when I have problems in the research.

I would like to thank the characterization team in the IEMN, *Sophie, Vanessa, Etienne* and *Sylvie,* it would be much harder without their technical supports in the measurements. I would like to especially thank *Sylvie* for her technical advices and her time helping me to finish the measurement of all the devices designed in this thesis.

I would like to thank all the IEMN staff, and especially *Mrs. Nora Benbahlouli* and *Mr. Andy Ledent* for helping me with administrative matters.

I would thank *Pr. Jean Claude de Jaeger, Dr. Nicolas Defrance and Dr. Marie Lesecq* for their scientific supports. Additional thanks go to my colleagues in the «group puissance». I would like to especially thank my colleague *Neila* who helped me a lot. Thanks *Neila*, you were always there to help me solve different problems. I would also thank my office colleague *Caroline* for her good and positive mood, for her encouragement and her help. To my colleague *Haitham*, we worked together, we helped each other, I really appreciate the time spent with you. Thanks to my colleague *Walid* who helped me to learn the basics of the microelectronic designs. Thanks to my colleagues *Mahmoud, Quentin* and *Martin* for their good mood, nice discussions and good time we spent together.

Finally, many thanks to my uncle *Jean*, my ante *Aline* and my cousin *Jihad* for their help, faith and encouragement. The great thank to my family, *my father's soul* my sister *Roula*, my brother in law *Milad* and my *great mother*, without you I would be nothing. I hope that we will meet soon.

# **Table of Contents**

| List of Tab  | bles                                                | 1  |

|--------------|-----------------------------------------------------|----|

| List of Figu | ures                                                | 2  |

| General in   | troduction                                          | 8  |

| Chapter 1    | Power Measurement Applications & Power Sensors      | 13 |

| 1.1 At       | brief history of RF and microwave power measurement | 14 |

| 1.2 Wh       | ny measuring power?                                 | 14 |

| 1.3 Pov      | wer measurements applications                       | 15 |

| 1.3.1        | Proof of design                                     | 16 |

| 1.3.2        | Component protection                                | 16 |

| 1.3.3        | Power regulation                                    | 16 |

| 1.3.4        | Measuring or improving of system efficiency         | 17 |

| 1.3.4        | 4.1 Envelope tracking technique (ET)                | 18 |

| 1.3.5        | THz power detection                                 | 22 |

| 1.4 Pov      | wer sensors                                         | 23 |

| 1.4.1        | Power definition                                    | 24 |

| 1.4.2        | Types of power measurement                          | 25 |

| 1.4.3        | Some backgrounds of power detectors                 | 27 |

| 1.4.4        | Heat based power detectors                          | 27 |

| 1.4.4        | 4.1 Bolometers                                      |    |

| 1.4.4        | 4.2 Thermocouple sensors                            |    |

| 1.4.5        | Diode based detectors                               | 32 |

| 1.5 Co       | nclusion                                            | 33 |

| Chapter 2    | Diode Based Detectors : Theory & Parameters         |    |

| 2.1 Int      | roduction                                           |    |

| 2.2 D     | iode detector principles                             |    |

|-----------|------------------------------------------------------|----|

| 2.3 D     | iode detector parameters                             | 40 |

| 2.3.1     | Bandwidth of interest ( $\Delta f$ )                 | 41 |

| 2.3.2     | Power consumption $(P_D)$                            | 41 |

| 2.3.3     | Voltage or current sensitivity $(\gamma)$            | 43 |

| 2.3.4     | The detector noise floor                             | 45 |

| 2.3       | 3.4.1 Thermal (Johnson) noise                        | 45 |

| 2.3       | 3.4.2 Flicker (1/f) noise                            | 46 |

| 2.3       | 3.4.3 Avalanche noise                                | 47 |

| 2.3       | 3.4.4 Shot noise                                     | 47 |

| 2.3       | 8.4.5 Estimation of noise equivalent power (NEP)     | 48 |

| 2.3.5     | Video resistance $(R_V)$                             | 50 |

| 2.3.6     | Video bandwidth ( <i>BW</i> )                        | 51 |

| 2.3.7     | Dynamic range ( <i>Dy</i> )                          | 52 |

| 2.3.8     | Figure of merit (FOM)                                | 54 |

| 2.4 C     | onclusion                                            | 54 |

| Chapter 3 | 8 PN Diode Detectors : Design & Characterization     | 57 |

| 3.1 In    | troduction                                           | 58 |

| 3.2 TI    | he technology SiGe 55-nm BiCMOS                      | 58 |

| 3.3 Ez    | xtraction of the diode parameters                    | 59 |

| 3.4 D     | esign of adjustable power detector based on PN diode | 66 |

| 3.4.1     | N-load circuit                                       | 67 |

| 3.4.2     | PN diode                                             | 68 |

| 3.4.3     | Matching network                                     | 69 |

| 3.4.4     | Detection simulation in ADS                          | 69 |

| 3.4    | 4.5   | Measurement results                                      | .71  |

|--------|-------|----------------------------------------------------------|------|

| 3.4    | 4.6   | Theoretical analysis                                     | .78  |

| 3.5    | The   | e thermal behavior of the PN diode                       | .79  |

| 3.:    | 5.1   | The deviation of the PN model with temperature           | .80  |

| 3.:    | 5.2   | The deviation of the sensitivity with temperature        | .85  |

| 3.:    | 5.3   | Simulation / measurement of sensitivity with temperature | .86  |

| 3.6    | Sta   | te of the art                                            | . 88 |

| 3.7    | Co    | nclusion                                                 | . 88 |

| Chapte | er 4  | Zero Bias Detectors : Design & Characterization          | .91  |

| 4.1    | Intr  | oduction                                                 | .92  |

| 4.2    | Zer   | o bias detectors for 5G applications                     | .92  |

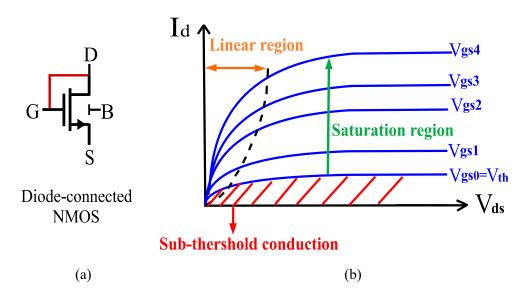

| 4.2    | 2.1   | Overview of MOSFET operation regions                     | .93  |

| 4.2    | 2.2   | Zero bias detector based on single NMOS                  | .95  |

|        | 4.2.2 | 2.1 Detector design                                      | .95  |

|        | 4.2.2 | 2.2 Measurement results                                  | .98  |

| 4.2    | 2.3   | Zero bias detector using stack of 6 NMOS                 | 104  |

|        | 4.2.3 | 3.1 Theoretical background                               | 105  |

|        | 4.2.3 | 3.2 Detector design                                      | 107  |

|        | 4.2.3 | 3.3 Measurement results                                  | 108  |

| 4.2    | 2.4   | Linearizing the detector response                        | 111  |

| 4.2    | 2.5   | Temperature compensated zero bias detector               | 112  |

|        | 4.2.5 | 5.1 Theoretical background                               | 113  |

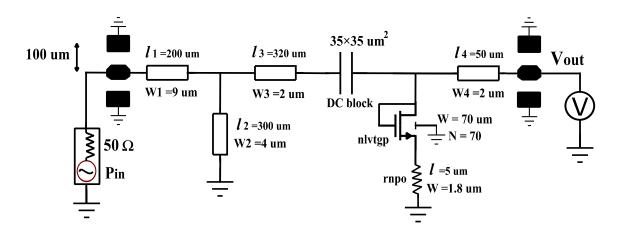

|        | 4.2.5 | 5.2 Detector design                                      | 114  |

|        | 4.2.5 | 5.3 Measurement results                                  | 115  |

| 4.2    | 2.6   | State of the art                                         | 120  |

| 4.3 F                                 | requency compensated power detector in G-band |     |

|---------------------------------------|-----------------------------------------------|-----|

| 4.3.1                                 | Theoretical background                        |     |

| 4.3.2                                 | Detector design                               |     |

| 4.3.3                                 | Measurement results                           |     |

| 4.3.4                                 | State of the art                              |     |

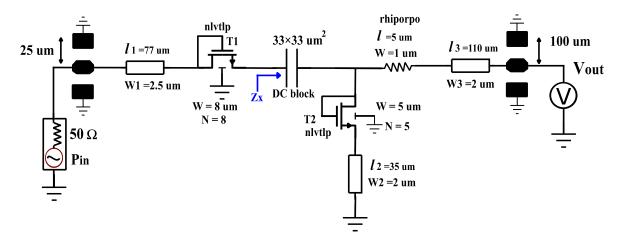

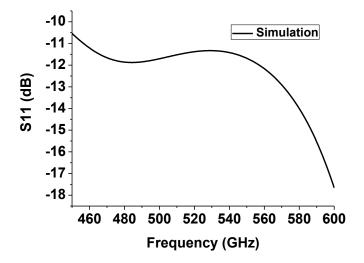

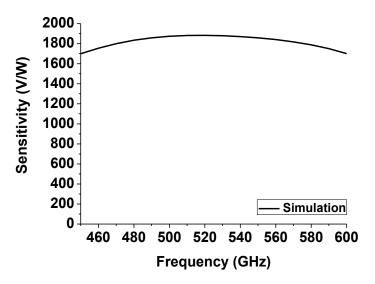

| 4.4 T                                 | Hz power detector                             | 129 |

| 4.5 C                                 | onclusion                                     | 131 |

| General conclusions and future works1 |                                               | 134 |

| Reference                             | es                                            |     |

| List of Publications                  |                                               | 145 |

| Annex 1                               |                                               | 146 |

| Annex 2                               |                                               | 148 |

# **List of Tables**

| Table 1.1 Comparison between heat and diode based power detectors                        |

|------------------------------------------------------------------------------------------|

| Table 3.1 The extracted model elements values for L1N1.                                  |

| Table 3.2 The extracted model elements values for L2N5.                                  |

| Table 3.3 Extracted ideality factor and saturation current values for L1N1 and L2N5.66   |

| Table 3.4 The stubs dimensions in the matching networks for the detectors L1N1 and       |

| L2N5                                                                                     |

| Table 3.5 The extracted parameters of the detectors L1N1 for three values of biasing     |

| current                                                                                  |

| Table 3.6 The extracted parameters of the detectors L2N5 for three values of biasing     |

| current                                                                                  |

| Table 3.7 The extracted saturation current and built-in potential for several            |

| temperatures                                                                             |

| Table 3.8 Comparison with other published power detectors for frequency < 110 GHz88      |

| Table 4.1 The extracted parameters of the zero bias detectors based on single transistor |

| at 44 GHz104                                                                             |

| Table 4.2 The extracted parameters of the Stack zero bias detector @ 44 GHz110           |

| Table 4.3 The extracted parameters of the GP detector at 44 GHz, using the equation      |

| 4.10                                                                                     |

| Table 4.4 The extracted parameters of the temperature compensated detector at 45         |

| GHz for two temperature                                                                  |

| Table 4.5 The state of the art of ZBDs for the frequency < 110 GHz.120                   |

| Table 4.6 The extracted parameters of the frequency compensated detector in G-band       |

| at 180 GHz and 220 GHz128                                                                |

| Table 4.7 The state of the art of power detectors for the frequency band $(140 - 320)$   |

| GHz129                                                                                   |

# **List of Figures**

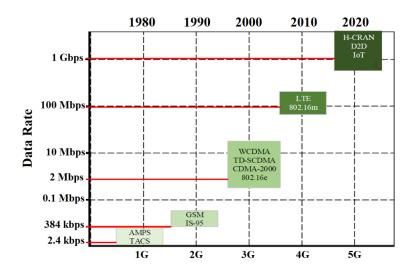

| Figure 1 Journey of cellular networks [15]9                                                 |

|---------------------------------------------------------------------------------------------|

| Figure 1.1 (a) Power measurement at dc and low frequencies, (b) variation of the            |

| voltage along transmission line at RF & microwave frequencies15                             |

| Figure 1.2 Power amplifier control loop for radar system17                                  |

| Figure 1.3 (a) The power added efficiency (PAE) versus input power for an amplifier         |

| using fixed power supply, (b) the output power versus input power for an amplifier          |

| [29]                                                                                        |

| Figure 1.4 Load lines of class-B biased GaAs HBT PA for modulated power supply              |

| [32]19                                                                                      |

| Figure 1.5 The PAE curves for different supply levels (when ET is used)                     |

| Figure 1.6 Envelope tracking block diagram [33]20                                           |

| Figure 1.7 Some of THz applications [37]22                                                  |

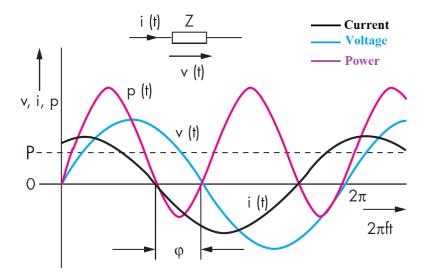

| Figure 1.8 The voltage, current and power absorbed in load Z                                |

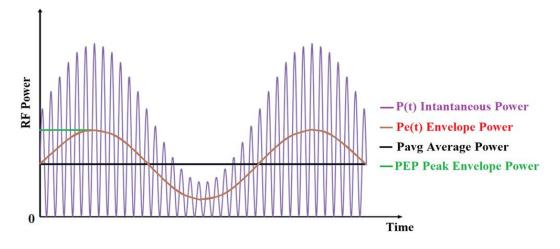

| Figure 1.9 Modulated signal with the illustration of several power types                    |

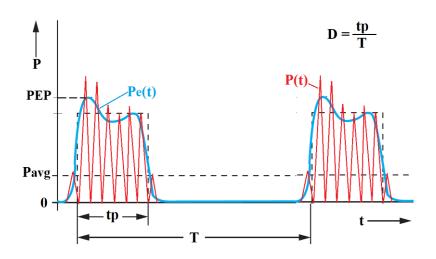

| Figure 1.10 Pulsed signal with the illustration of several power types                      |

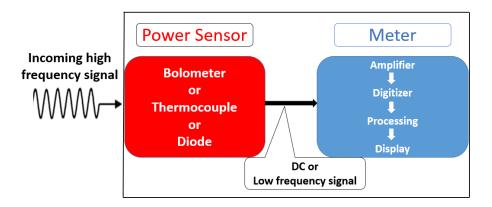

| Figure 1.11 Basic block diagram of power detectors27                                        |

| Figure 1.12 Thermistor characteristic with temperature [45]                                 |

| Figure 1.13 Thermistor as RF power detector in Wheatstone bridge configuration [47].        |

|                                                                                             |

| Figure 1.14 Simple thermocouple structure                                                   |

| Figure 1.15 Thermocouples are connected in series (thermopile)                              |

| Figure 1.16 Block diagram of thermocouple detector                                          |

| Figure 1.17 Basic diode functions: (a) diode rectifier, (b) diode detector, (c) mixer [52]. |

|                                                                                             |

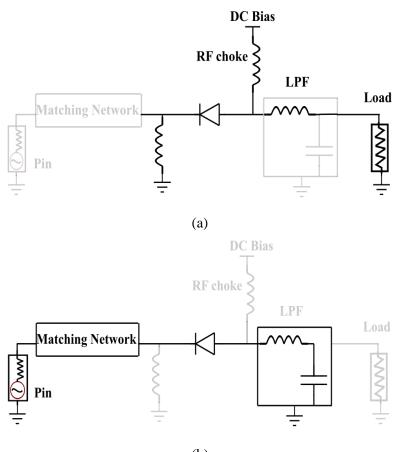

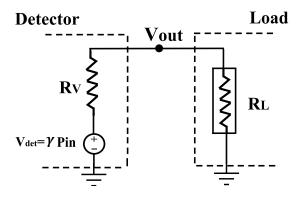

| Figure 2.1 Basic diode detector configuration [55]                                          |

| Figure 2.2 The intrinsic small signal model of diode                                        |

| Figure 2.3 The circuit path of: (a) DC and low frequency signals, (b) RF signal40           |

| Figure 2.4 I-V characteristic of a diode in different operating regions                     |

| Figure 2.5 I-V curves for three states of input RF power, with a constant biasing           |

| current <i>Ib</i>                                                                           |

| Figure 2.6 The equivalent circuit of noisy resistor (R) at temperature T in voltage and     |

| current modes [58]                                                                          |

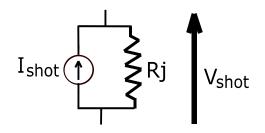

| Figure 2.7 The equivalent circuit of shot noise generated in diode junction [58]47        |

|-------------------------------------------------------------------------------------------|

| Figure 2.8 The video equivalent circuit of diode detector loaded by resistance RL with    |

| smoothing capacitor <i>CL</i> 51                                                          |

| Figure 2.9 The RF and DC power paths in rectenna51                                        |

| Figure 2.10 (a) The output voltage behavior of diode versus input RF power, (b) the       |

| sensitivity curve versus input RF power53                                                 |

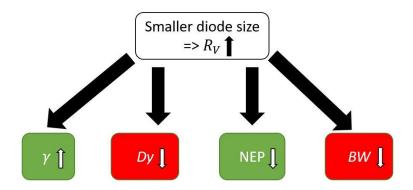

| Figure 2.11 The effects of diode size over the intrinsic parameters considering zero bias |

| diode55                                                                                   |

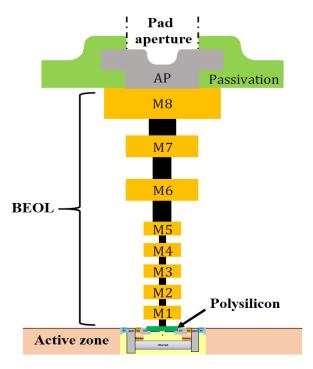

| Figure 3.1 The back-end diagram of the 55-nm BiCMOS technology from                       |

| STMicroelectronics                                                                        |

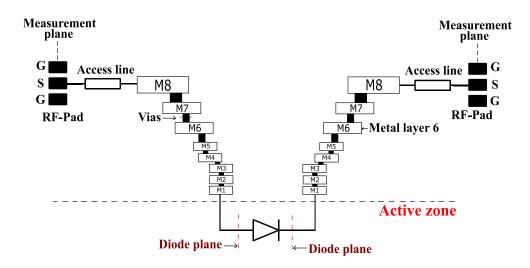

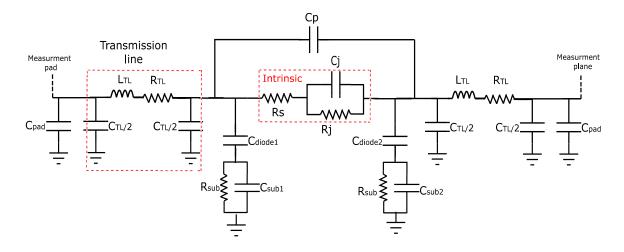

| Figure 3.2 The test structure diagram of the diode stand alone60                          |

| Figure 3.3 The test structure model including the intrinsic and extrinsic elements60      |

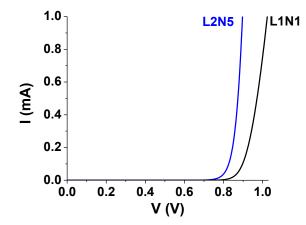

| Figure 3.4 The I-V measured curves for L1N1 and L2N5                                      |

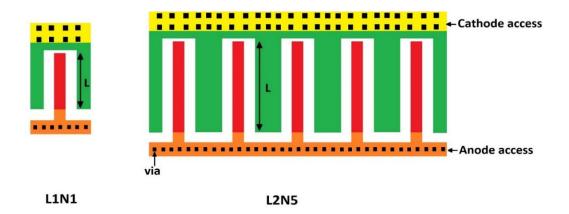

| Figure 3.5 The layout illustration of the diodes L1N1 and L2N561                          |

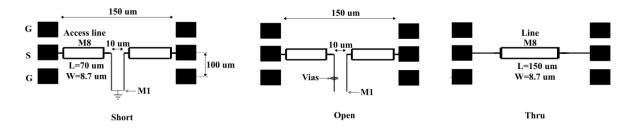

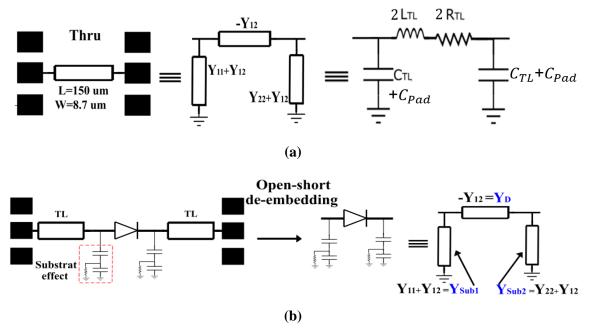

| Figure 3.6 The dummy structures diagrams                                                  |

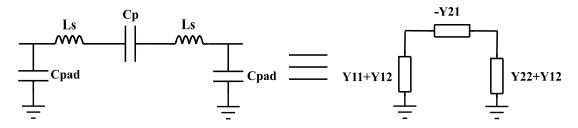

| Figure 3.7 The Equivalent Pi network of open structure                                    |

| Figure 3.8 The equivalent Pi network of : (a) thru structure, (b) de-embedded test        |

| structure63                                                                               |

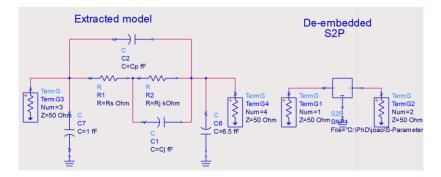

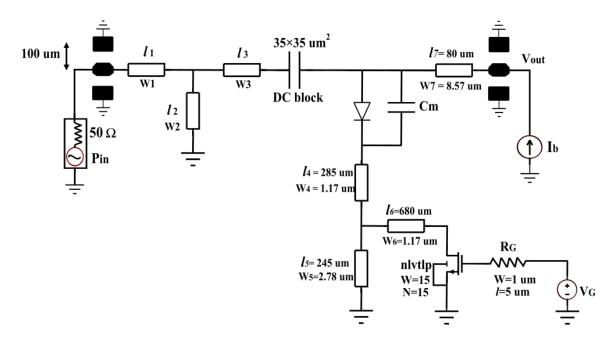

| Figure 3.9 (a) The schematics of ADS simulation of the extracted model and                |

| measurements, (b) comparison of measured and extracted S11 and S21 of the PN              |

| diode for two sizes (L1N1 @ 0.1 µA, and L2N5 @ 1uA)66                                     |

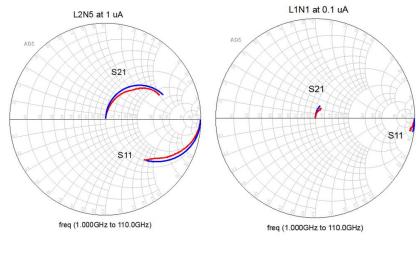

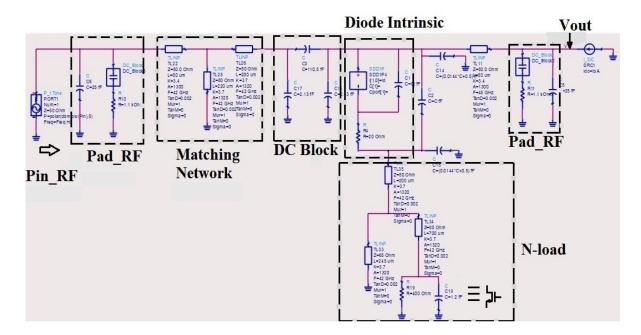

| Figure 3.10 The adjustable detector circuit based on PN diode67                           |

| Figure 3.11 The large signal intrinsic model of diode, Vj is the voltage across the       |

| junction70                                                                                |

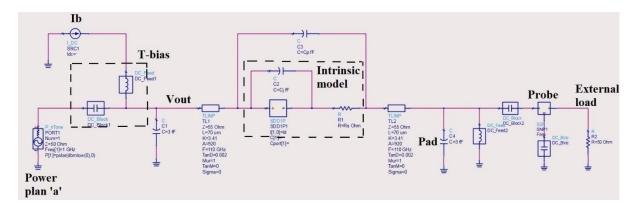

| Figure 3.12 The detector schematic simulated in ADS70                                     |

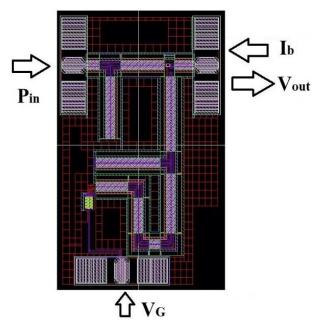

| Figure 3.13 The layout of the detectors L1N1 and L2N571                                   |

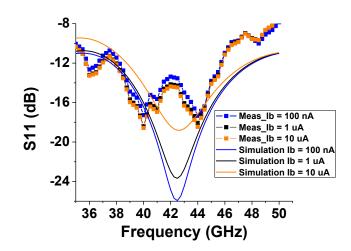

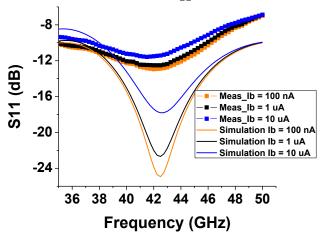

| Figure 3.14 The measured and simulated S11 for L1N1 detector at Pin=-12 dBm72             |

| Figure 3.15 The measured and simulated S11 for L2N5 detector at <i>Pin</i> =-12 dBm72     |

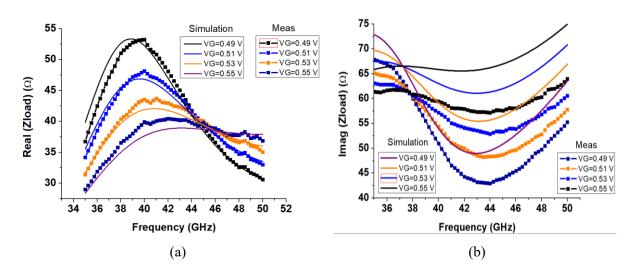

| Figure 3.16 The measured / simulated real and imaginary parts of N-load impedance         |

| Zload for several VG values                                                               |

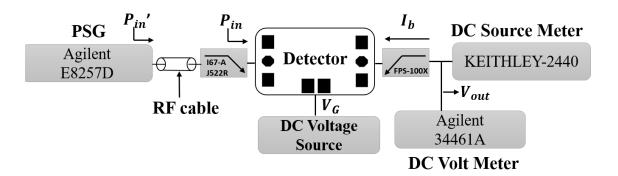

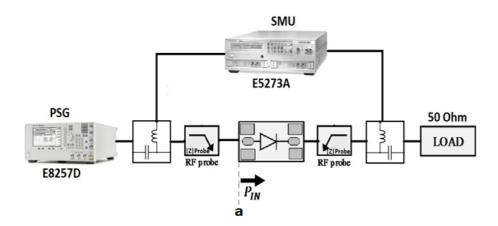

| Figure 3.17 Test bench block diagram to extract the voltage sensitivity74                 |

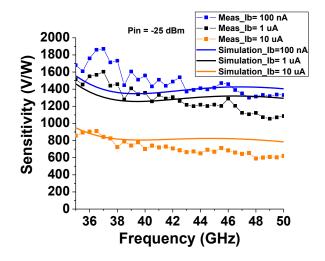

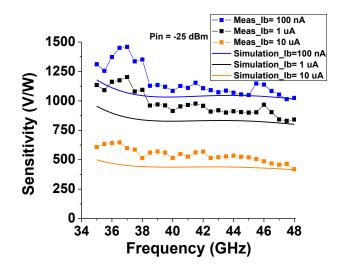

| Figure 3.18 The measured and simulated voltage sensitivity curves vs frequency for        |

| L1N1 detector at <i>Pin</i> = -25 dBm                                                     |

| Figure 3.19 The measured and simulated voltage sensitivity curves vs frequency for               |

|--------------------------------------------------------------------------------------------------|

| L2N5 detector at <i>Pin</i> = -25 dBm75                                                          |

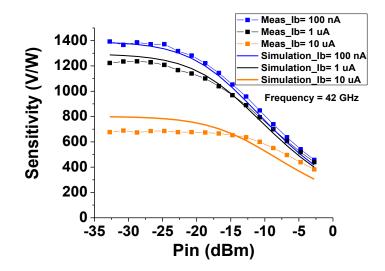

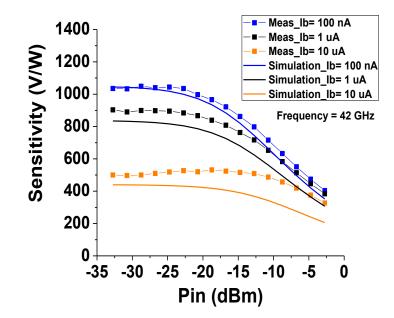

| Figure 3.20 The measured and simulated voltage sensitivity curves vs input power for             |

| L1N1 detector at 42 GHz76                                                                        |

| Figure 3.21 The measured and simulated voltage sensitivity curves vs input power for             |

| L2N5 detector at 42 GHz77                                                                        |

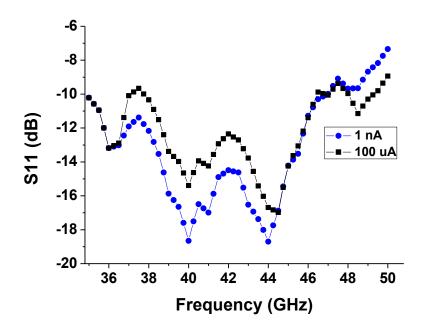

| Figure 3.22 The S11 measurements for L1N1 detector at 1 nA and 100 $\mu$ A biasing               |

| currents                                                                                         |

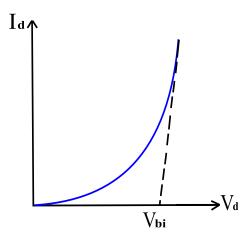

| Figure 3.23 The extraction of <i>Vbi</i> 80                                                      |

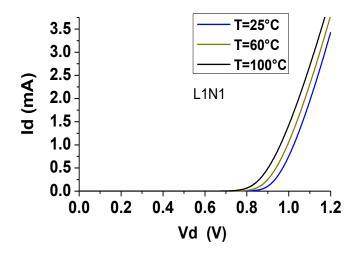

| Figure 3.24 The measured I-V curves corresponding to three temperatures for the                  |

| diode L1N1                                                                                       |

| . 81                                                                                             |

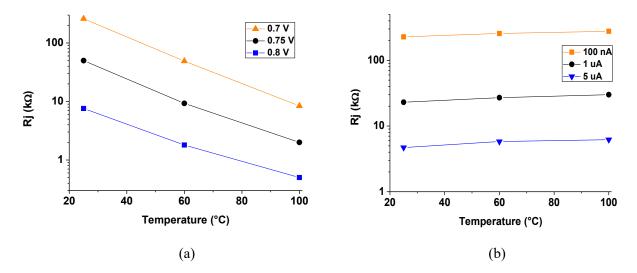

| Figure 3.25 The variation of $Rj$ value with temperature for: (a) different biasing              |

| voltage values, (b) different biasing current values                                             |

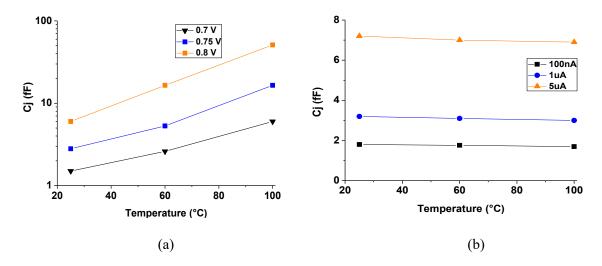

| Figure 3.26 The variation of <i>Cj</i> with temperature for: (a) different biasing voltage       |

| values (b) different biasing current values83                                                    |

| Figure 3.27 The variation of $\Delta V$ for two temperatures in: (a) voltage biasing (b) current |

| biasing                                                                                          |

| Figure 3.28 The variation of intrinsic cutoff frequency with temperature for different           |

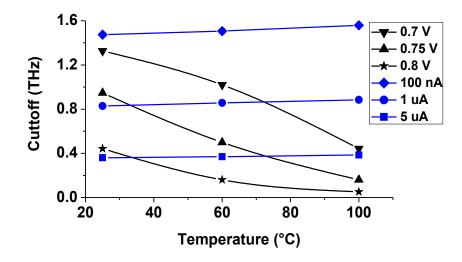

| voltage and current biasing values84                                                             |

| Figure 3.29 Test bench block diagram to extract the voltage sensitivity of the diode             |

| L1N1                                                                                             |

| Figure 3.30 The extracted voltage sensitivity in function of temperature for several             |

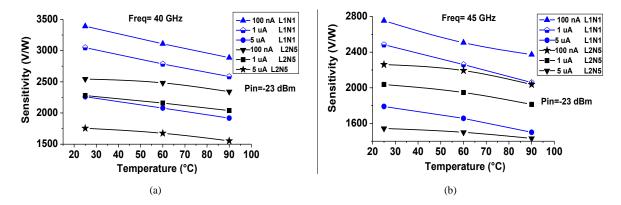

| biasing current values, two diode sizes, at -23 dBm: (a) 40 GHz, (b) 45 GHz86                    |

| Figure 3.31 The test structure schematic simulated in ADS                                        |

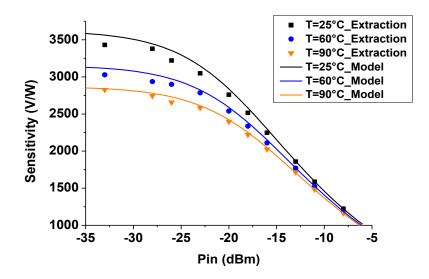

| Figure 3.32 The extracted and simulated voltage sensitivity in function of input power           |

| for several temperatures at 40 GHz, $1\mu A$ biasing current using the diode L1N187              |

| Figure 4.1 (a) Diode connected NMOS transistor, (b) the output characteristic of NMOS            |

| transistor showing different operation regions94                                                 |

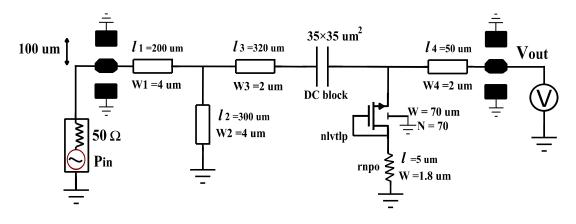

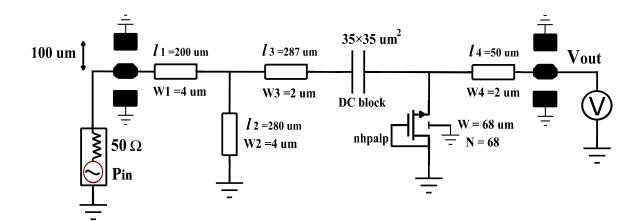

| Figure 4.2 The schematic of the detector GP96                                                    |

| Figure 4.3 The schematic of the detector LP96                                                    |

| Figure 4.4 The schematic of the detector HPA97                                                   |

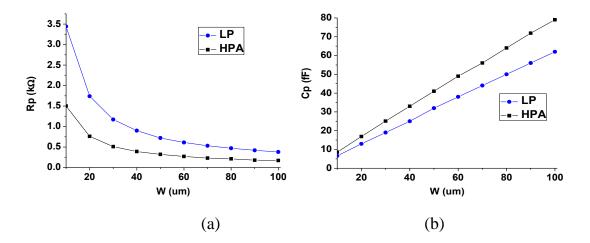

| Figure 4.5 The extracted <i>RP</i> and <i>CP</i> values (from Cadence) for diode connected NMOS |

|-------------------------------------------------------------------------------------------------|

| at 42 GHz, for <i>N</i> = <i>W</i> 97                                                           |

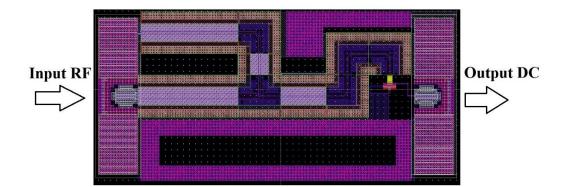

| Figure 4.6 The layout of the zero bias detector based on single NMOS                            |

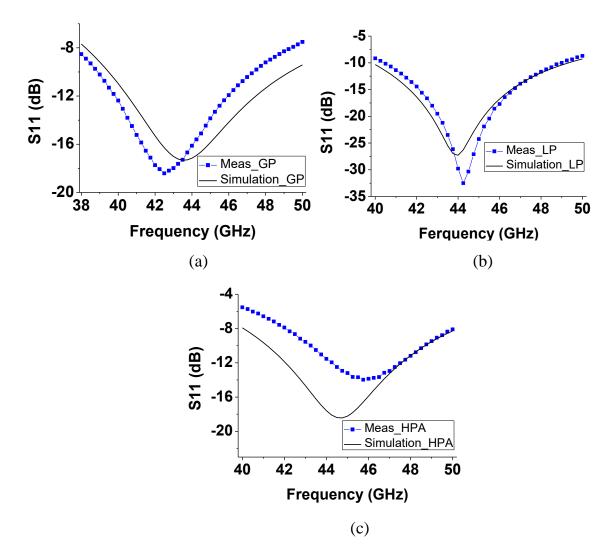

| Figure 4.7 Measured and simulated S11 for: (a) GP, (b) LP, (c) HPA detectors at                 |

| <i>Pin</i> =-12 dBm                                                                             |

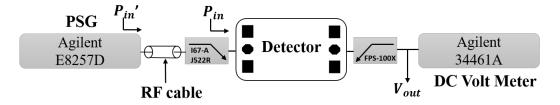

| Figure 4.8 Test bench block diagram to extract the voltage sensitivity of zero bias             |

| detectors                                                                                       |

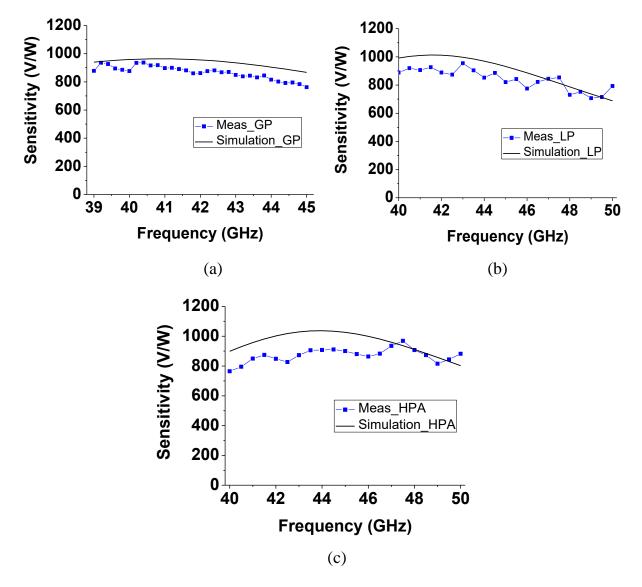

| Figure 4.9 The measured and simulated voltage sensitivity curves vs frequency @ Pin=            |

| -25 dBm for: (a) GP, (b) LP, (c) HPA detectors                                                  |

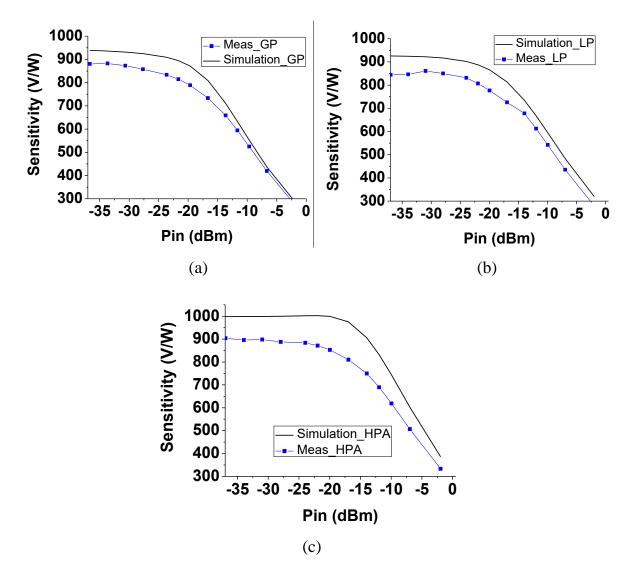

| Figures 4.10 The measured and simulated voltage sensitivity curves vs input power at            |

| 44 GHz for: (a) GP, (b) LP, (c) HPA detectors101                                                |

| Figure 4.11 The DC equivalent circuit of detector loaded by resistance RL102                    |

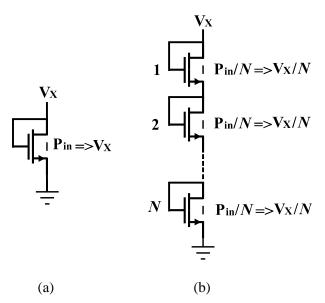

| Figure 4.12 The DC voltage generated using (a) single transistor, (b) stack of $N$              |

| transistors                                                                                     |

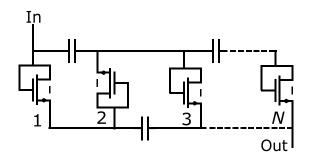

| Figure 4.13 Parallel stack of N transistors107                                                  |

| Figure 4.14 Zero bias detector schematic based on stack of 6 transistors107                     |

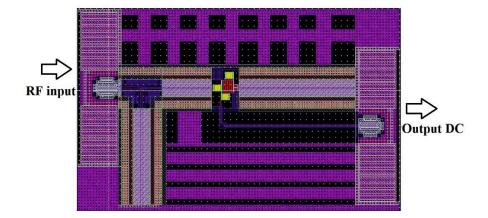

| Figure 4.15 The layout of zero bias detector based on stack of 6 transistors108                 |

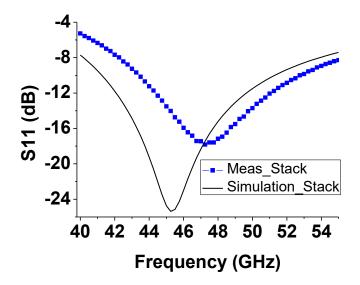

| Figure 4.16 The measured and simulated S11 of the stack zero bias detector @ Pin= -             |

| 12 dBm                                                                                          |

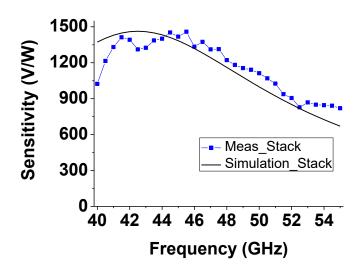

| Figures 4.17 The measured and simulated voltage sensitivity curves vs frequency of the          |

| Stack detector @ Pin= -25 dBm109                                                                |

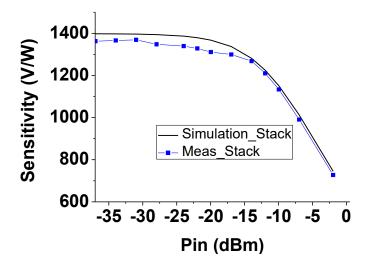

| Figures 4.18 The measured and simulated voltage sensitivity curves vs input power of            |

| Stack detector at 44 GHz detectors110                                                           |

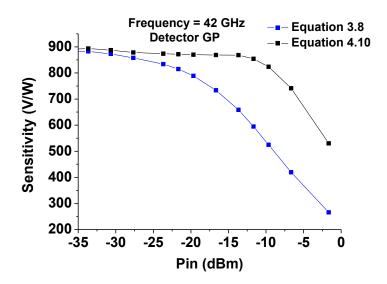

| Figure 4.19 The extracted voltage sensitivity curves of GP detector using the equations         |

| 3.8 and 4.10                                                                                    |

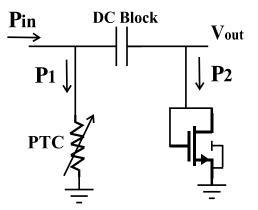

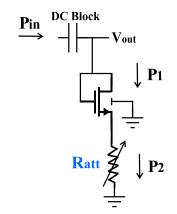

| Figure 4.20 Temperature compensation technique by adding a PTC in parallel with the             |

| transistor                                                                                      |

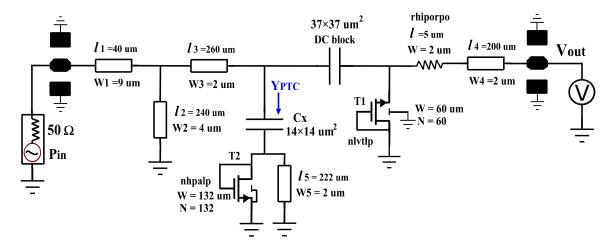

| Figure 4.21 The schematic of temperature compensated detector114                                |

| Figure 4.22 The layout of the temperature compensated detector115                               |

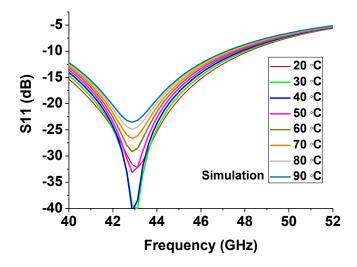

| Figure 4.23 The simulated S11 of the temperature compensated detector for several               |

| temperatures116                                                                                 |

| Figure 4.24 The measured S11 of the temperature compensated detector for several                |

| temperatures                                                                                    |

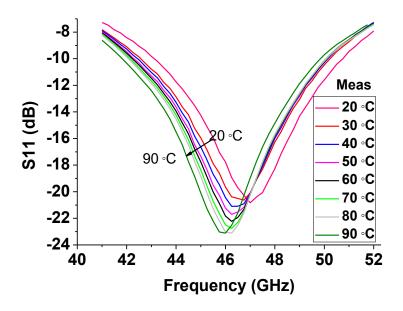

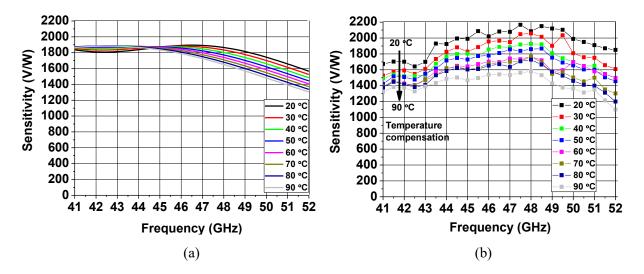

| Figure 4.25 The equivalent parallel resistor of the PTC circuit for several                |            |

|--------------------------------------------------------------------------------------------|------------|

| temperatures: (a) simulation, (b) measurement11                                            | l <b>7</b> |

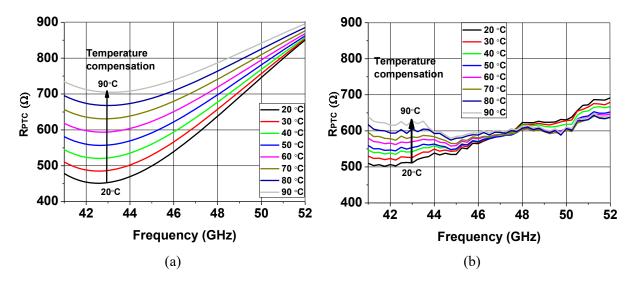

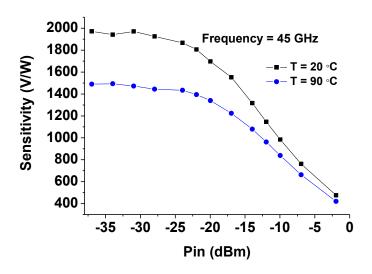

| Figure 4.26 The voltage sensitivity curves vs frequency of the temperature compensate      | d          |

| detector @ Pin= -25 dBm: (a) simulation, (b) measurements11                                | 8          |

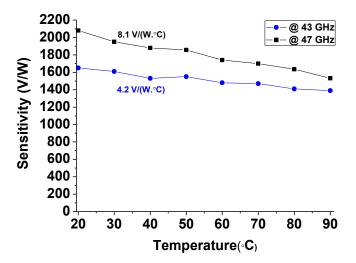

| Figure 4.27 The measured sensitivity curves vs temperature of the temperature              |            |

| compensated detector at two frequencies, <i>Pin</i> = -25 dBm11                            | 8          |

| Figure 4.28 The measured voltage sensitivity curve vs input power of the temperature       |            |

| compensated detector at 45 GHz11                                                           | 9          |

| Figure 4.29 Frequency compensation technique by adding a self-varied resistance with       |            |

| frequency12                                                                                | 21         |

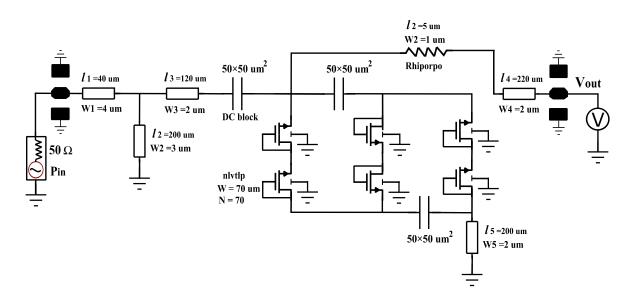

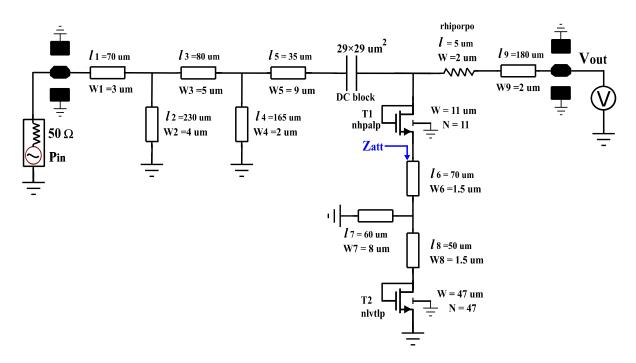

| Figure 4.30 The schematic of the frequency compensated detector in G-band12                | 22         |

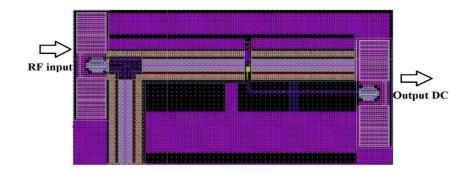

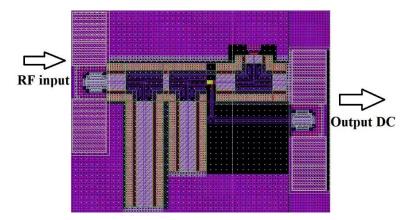

| Figure 4.31 The layout of the frequency compensated detector in the G-band12               | 23         |

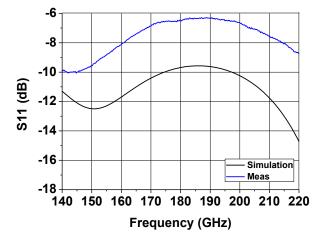

| Figure 4.32 The measured and simulated <i>S</i> 11 of the frequency compensated detector   |            |

| in G-band12                                                                                | 24         |

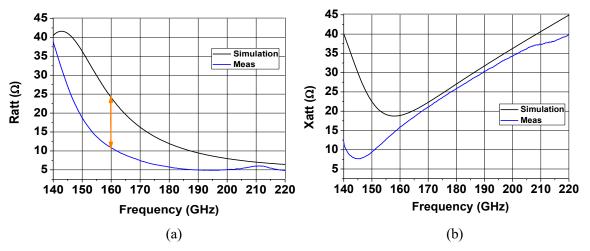

| Figure 4.33 The simulated and measured: (a) <i>Ratt</i> , (b) <i>Xatt</i> 12               | 24         |

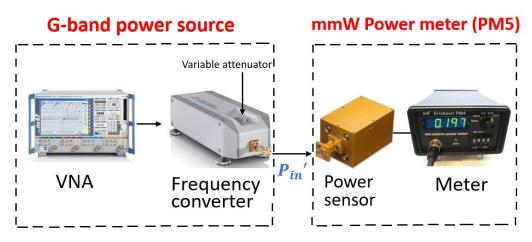

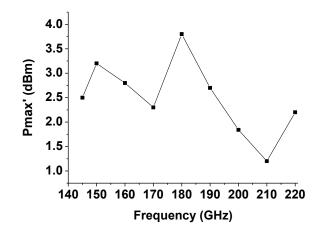

| Figure 4.34 The test bench used to characterize the G-band power source12                  | 25         |

| Figure 4.35 The measurements of the maximum output power of the G-band source.             |            |

|                                                                                            | 25         |

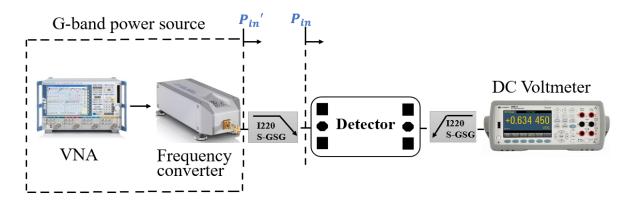

| Figure 4.36 The test bench used to extract the voltage sensitivity values of the frequence | 2y         |

| compensated detector in G- band12                                                          | 26         |

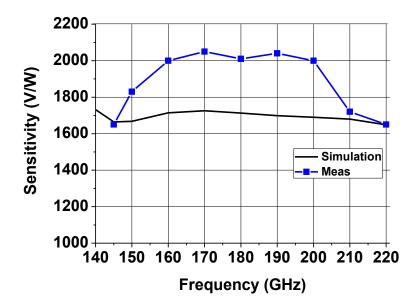

| Figure 4.37 The measured and simulated voltage sensitivity curves vs frequency of the      |            |

| frequency compensated detector in G-band, at <i>Pin</i> = -25 dBm12                        | 27         |

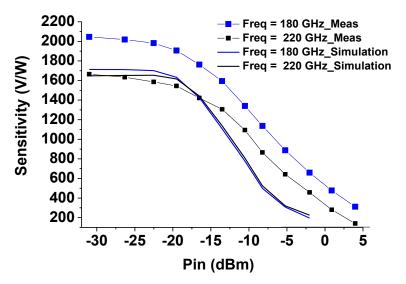

| Figure 4.38 The measured voltage sensitivity curve vs input power of the frequency         |            |

| compensated detector in G-band at 180 GHz and 220 GHz12                                    | 27         |

| Figure 4.39 The schematic of the THz detector                                              | 30         |

| Figure 4.40 The simulated S11 parameters of the THz detector                               | 30         |

| Figure 4.41 The simulated voltage sensitivity curve versus frequency of the THz            |            |

| detector13                                                                                 | 31         |

## **General introduction**

The mobile communication system brings real-time communicating to people in a mobile state without physical transmission line. It has been continuously developing since the cellular communication concept was proposed by Bell Labs in 1970s [1]-[3]. The first generation of mobile communication system (1G) was commercially launched in 1980s. This system adopted analog electronics technology and can only provide low quality voice service, very small system capacity and limited services [4].

In early 1990's, the second generation mobile systems (2G) were rolled out commercially as digital communication systems. The system capacity and quality were significantly improved as compared to (1G) because of its digital nature. Low data rate services (384 Kb/s) were also added in (2G) systems along with voice services [5].

In the 21st century, the third generation mobile systems (3G) were standardized under the coordination of International Telecommunication Union (ITU) [6]. Based on the Code Division Multiplexing Access (CDMA) technology, (3G) systems provided higher data rates, larger bandwidth, and higher system capacity.

Long Term Evolution (LTE) proposed by Third Generation Partnership Project (3GPP) was the initial taste of (4G) networks around 2004 [7]. With the introduction of the orthogonal frequency division multiple access OFDMA and MIMO (multiple-input and multiple-output), (4G) networks provide much higher data rates than (3G) [8], [9].

(5G) is the actual generation of mobile communication technologies. Its initial launch was in 2012 [10], and commercially introduced in 2020. The main (5G) aims are to provide higher data rates, lower latency, seamless coverage, lower power consumption and higher reliable communications [11]. So many researches have been also done to enhance the machine-to-machine (M2M) and Internet of Things (IoT) technologies. These technologies are operated using the (5G) systems. Several ranges of Millimeterwave (mmW) frequencies are utilized in (5G) systems for back-haul (up to 100 GHz), this allows to provide higher data rate (of at least 1 Gb/s) and lower latency as compared to (4G) [12], however, higher power consumption is required. In addition, the huge number of IoT sensors that will be installed makes it difficult to sustain all batteries [13],[14].

Figure 1 Journey of cellular networks [15].

Moreover working at high frequencies makes the thermal effect an issue requiring more power consumption. For those reasons, the battery life is crucial and considered as one of the biggest hurdles in the development of IoT devices [16]. In this context, several methods are proposed for reducing power consumption [17]. Using envelope tracking technique (ET) could be a promising solution to increase the efficiency of (5G) and IoT devices [18]. As a part of envelope tracking circuit, several power detector topologies (zero bias detectors) are proposed and studied in this thesis. Another detector topology (tunable detector) is also proposed in this thesis, this can be utilized in different 5G applications. These detectors are designed using the SiGe 55-nm BiCMOS technology from STMicroelectronics, in the frequency band (35 - 55) GHz allowing to cover several 5G bands [19].

(6G) is the next generation of mobile communication system which will be commercially launched in 2030. This generation will be able to use higher frequencies than (5G) systems (THz frequencies), providing higher capacity and much lower latency (1  $\mu$ s latency of communications) [20].

Nowadays, the use of THz waves became more popular. This is because of their interesting properties, and also, the new sophisticated technologies which allow to deal with such high frequencies. THz waves are mainly utilized in high resolution imagining for medical and security applications [21], and also in spectroscopy providing information that other waves cannot [22].

In this thesis, power detectors (using the same technology) dedicated for higher frequency applications (in sub-THz and THz) are also studied. The design and characterization of those detectors have been done for two frequency ranges. The first range is (140-220) GHz in G-band. This detector can be used in integrated power detection for power measurement instrumentations. The second range is (0.45-0.6) THz, where radar and THz imaging systems are forecasted as the main applications.

Very high performances can be obtained when the III-V technologies are utilized to design THz detectors [23]. However, they have high cost and cannot be integrated with the digital (processing) parts on the same silicon chip. The detectors presented in the thesis (based on silicon technology) exhibit very good performances and allow the integration with the digital parts. Therefore, these detectors can be interesting for several reasons:

- Because of the integration capability, these detectors help increasing the compactness and the overall efficiency of power measurement systems at such high frequencies.

- $\succ$  They have low cost.

- > They are not available in the market.

The thesis is organized as the following:

The first chapter presents the need of power measurements by explaining the most common applications with some examples at different frequency ranges. The principles of the heat and diode based sensors are also presented, showing the pros and cons for each type.

The second chapter studies the basic diagram of diode based detectors by explaining the function of each block. The detector parameters are discussed in detail, showing their importance depending on the applications, and their effects on each other.

The third chapter presents the extraction of the small signal model of the PN diode (which is under development). Then, the design of tunable detectors (using the extracted model) is presented. The model of the diode is also extracted for several temperatures in order to help to design temperature compensated detector (based on this diode).

The fourth chapter focuses on the design and characterization of zero bias detector, based on MOSFET (NMOS) transistors. Several detector topologies are designed and characterized, dedicated for 5G, IoT and THz applications.

It is worth to mention that, part of this thesis (detectors for 5G applications) has been done in the frame of European project (EURAMET - 16ENG06 ADVENT), which is supported by the European Metrology Program for Innovation and Research (EMPIR). The aim is to calibrate our detectors (at 42 GHz) using a heat based detector (as a reference), which is designed by Laboratoire national de métrologie et d'essais (LNE).

# Chapter 1 Power Measurement Applications & Power Sensors

#### 1.1 A brief history of RF and microwave power measurement

From the beginning of the RF and microwave systems, it was necessary to determine the power level in different systems plans (input power, output power, power level inbetween the stages, etc.). The power measurement principles were quite primitive compared to nowadays technologies. In the late 1930s, the klystron microwave power tube was used in the early experimental stages of klystron cavity to give a gross indication of power level [24]. Whereas the diode-based detection of the day was not capable to work at such microwave frequencies as the klystron tube.

For the high power systems, set of terminals were being arranged to absorb the power, then, the built-up heat versus time was being measured. With the launch of the crystal technology in the period of the world war II, new types of detectors were initiated based on this technology. Consequently, the detectors became faster, more rugged and performed at higher frequencies. One of the earliest sensing element built in crystal technology had a positive temperature coefficient (PTC); this type of element uses the power substitution methods to produce the readout voltage. The thermistors which have negative temperature coefficient (NTC) were much more rugged, for this reason, they became more dominant compared to PTC elements. The calorimeters were also being used with the thermistors in the early measurements. In the 1960's, the 434A power meter was an oil-flow calorimeter, where the maximum measurable power using this meter was about 10 watt [25]. On the other hand, water flow calorimeters were being used for medium and high power levels.

Finally, it is worth to mention that some of the early power sensors are still used nowadays (such as thermistors, calorimeters, diodes ...). However, more decent technologies and complex instruments are employed to improve the detection performances.

## 1.2 Why measuring power ?

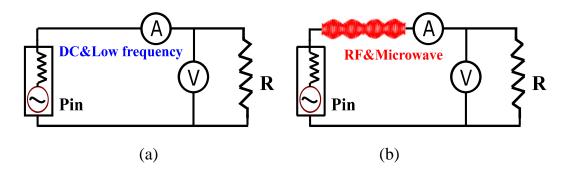

Measuring the voltage and current in DC and low frequency systems can be very accurate and simple as in figure 1.1 (a). For a resistive load, the power can be calculated

using the effective current and voltage drop across the load, as in equation 1.1:

$$P = V_{ms} \cdot I_{rms} = \frac{V_{ms}^{2}}{R} = I_{rms}^{2} \cdot R$$

(1.1)

Figure 1.1 (a) Power measurement at dc and low frequencies, (b) variation of the voltage along transmission line at RF & microwave frequencies.

However, for higher frequencies such as RF and microwave, the propagation wavelength becomes smaller, and so comparable to the dimensions of transmission lines. Because of that, the voltage (and current) varies along transmission lines as in figure 1.1 (b). In addition, signal reflections, standing waves, and impedance mismatch become very significant error sources.

In the following, we can mention two main reasons for which the power measurement is performed (instead of voltage or current) at high frequencies:

- The power delivered to the load (*R*) is constant along the lossless transmission line.

Therefore, the measured power does not depend on the meter position.

- 2) Performing voltage or current measurement in waveguide is more complicated.

## **1.3** Power measurements applications

Measuring the power in most of RF and microwave systems is necessary and sometimes even crucial. There are thousands of unique applications where power measurement is required and helpful. RF power detector is considered as the key element to establish the power measurement. Some of the common applications are mentioned and explained in the following paragraphs.

#### **1.3.1 Proof of design**

The designers often need to determine power levels in different system plans, and so verify the validity of their circuits. Amplifiers and couplers circuits are common examples where the input and output power have to be measured. These measurements are useful to determine the power gain of amplifiers, coupling factor and losses in couplers.

## **1.3.2** Component protection

Two possible effects can be produced when high instantaneous (peak) or steady stat power is applied on a device:

- Overstressing the device, which causes temporal or permanent modification in their physical characteristics.

- 2) Causing dielectric breakdown, over-heating and damaging the device.

Even at power levels well below the damage threshold, excessive power can change the performance of the system. This usually happens when the input power level excess the compression point producing a distortion in the output signal. Therefore, power levels are usually measured and controlled in order to keep the systems in proper operating zone and safe conditions.

## **1.3.3 Power regulation**

Power regulation is considered as one of the most important issues to be fulfilled in the RF and microwave systems. For example, in the communication and wireless industries, there are usually a number of regulatory specifications that must be met by any transmitting device. The most common regulatory requirement is to specify the maximum power which may be radiated by the antenna.

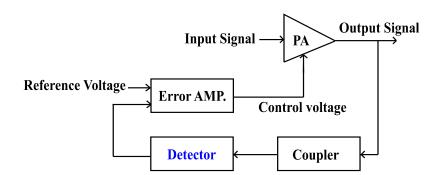

Regulated amplifier for radars is another example [26], where accurate power control is required to meet system specifications under operating conditions (temperature and supply voltage variation). The power control loop works as the following:

Figure 1.2 Power amplifier control loop for radar system.

The detector read the output power of the PA through the coupler as shown in figure 1.2. The reference voltage (which is set by the controller) is compared to the detector output. Then, the error amplifier reduces the error value in the output signal by changing the control voltage, and so the power gain. In this application, measurement accuracy is the most important parameter that the detector has to fulfill. It is worth to mention that the control loop technique does not depend on frequency, hence it can be used at higher frequencies (at millimeter waves for 5G transmitters).

## 1.3.4 Measuring or improving of system efficiency

Efficiency is a measure of how well a device (or system) converts one energy source to another. In microwave engineering, we are interested in converting DC to RF power or the opposite.

With the rapid development of wireless communication systems, the demand of higher data rate and larger frequency bandwidth is more and more increased. This can only be achieved by consuming more energy [27]. Therefore, increasing the efficiency of the devices is necessary.

In mobile radio networks, the amplifiers in both cell phones and base stations consume the highest amount of energy comparing to other system parts. (50-80) % of the consumed power in the base station is drained in power amplifier [28]. Moreover, these amplifiers suffer from low efficiencies. Hence, increasing their efficiencies will significantly increase the overall system efficiency and the battery life. In this thesis, the envelope tracking technique (ET) is forecasted as the application of power detector, where the aim is to improve the efficiency of amplifiers in 5G and IoT systems.

## **1.3.4.1** Envelope tracking technique (ET)

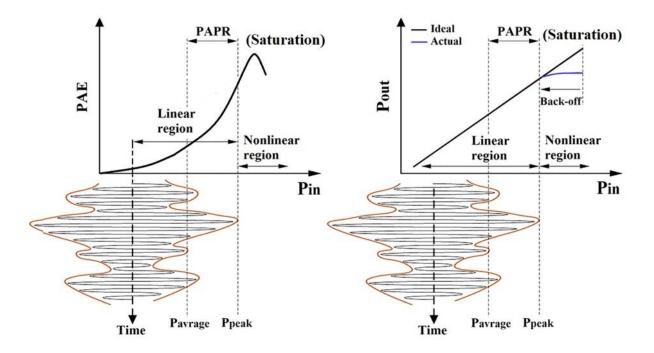

Traditionally, power amplifiers (PAs) are biased so that there is sufficient DC power at the transistor to supply for peak output RF power. However, when the output level is smaller than the peak value, the extra DC power must be dissipated in the transistor as a heat, since it is not transferred to the RF load. The higher the value of peak to average power ratio (PAPR), the higher is power dissipated in the transistors, thus, lower efficiency is obtained. Figure 1.3 (a) shows the variation of power added efficiency (PAE) with the input power for an amplifier biased by a fixed power supply.

Figure 1.3 (a) The power added efficiency (PAE) versus input power for an amplifier using fixed power supply, (b) the output power versus input power for an amplifier [29].

As it can be seen, the maximum efficiency is only obtained near the saturation region. Biasing the amplifier by a fixed power supply is usually inefficient, this is because most of the modern modulated signals (such as OFDM modulation) have high PAPR values [30].

Modulating the power supply level can be a solution to improve the efficiency of an amplifier. This is done by decreasing the supply level when the output level is smaller than the peak value, thus decreasing the dissipated power in the transistors. Figure 1.4 shows the load lines corresponding to two signal input levels when modulated power supply is used. Instead of maintaining the same biasing point for small output level, ET technique decreases the supply voltage ( $V_{CE High}$  to  $V_{CE Low}$ ). Hence, the biasing point is changed allowing for enough load line swing, while decreasing the DC power. It is worth to mention that the gain does not change with the supply voltage, and the last is adjusted to ensure that no extra power is dissipated in the transistor. This technique is used to increase the power efficiency in mmW power amplifier [31].

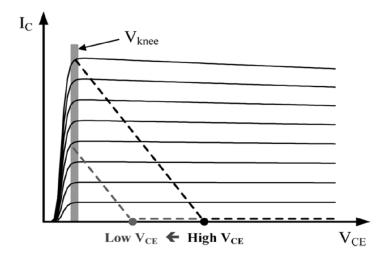

Figure 1.4 Load lines of class-B biased GaAs HBT PA for modulated power supply [32].

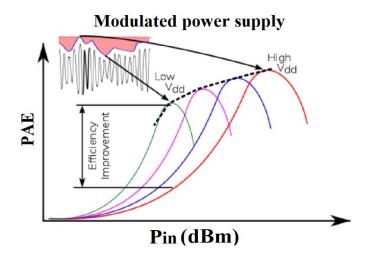

Figure 1.5 shows the PAE curves for different supply levels (which follow the variation of the input signal), where the peak efficiency values are obtained for all signal levels (even at low power). In other words, envelope tracking technique makes the efficiency follow its peak values of the swept supply voltage, thus, significant improvement is obtained.

Improving the linearity of amplifiers is another important benefit of using ET technique,

Figure 1.5 The PAE curves for different supply levels (when ET is used).

since it allows following the input signal levels to keep the operating point in the linear region.

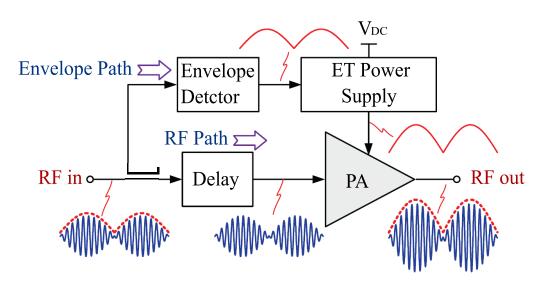

Figure 1.6 shows the simple version of envelop tracking diagram. It consists of several stages which are briefly explained in the following:

• **RF coupler**: This coupler is located at the input RF signal. Its main function is to divide the input RF power in two parts in order to feed the envelop detector and the amplifier. The losses and coupling factor of the coupler have to be designed in order to keep the input power - of the detector and amplifier - higher than their noise floors and lower than their compression points. The coupler also has to be matched at the input in order to absorb the maximum of the input RF power.

Figure 1.6 Envelope tracking block diagram [33].

• Envelope detector: Its function is to extract the envelope (bass band) signal. This signal drives the ET power supply (modulated power supply). The detector has to fulfill two critical parameters: (1) Fast response is required in order to track the envelope variation. For this reason, the heat based detectors are not useful in this application. (2) The power consumption has to be minimum possible in order to take the full benefit of the ET technology.

The diode based detector dedicated to ET technique is explained in detail in this thesis.

- **ET power supply:** It is a modulated power supply. The output supply level depends on the input control signal (coming from the envelope detector). Hence, it has the same shape as the envelope of RF signal. Some requirements have to be met in the design of ET power supply [34]:

- The output bandwidth has to be sufficiently large (typically around two to three times of the envelope signal bandwidth), so it can accurately follow the envelope signal.

- The ET power supply must be highly efficient in order to take the full benefit of the ET technology.

- 3) Using switch mode power supply (SMPS) offers high efficiency level, however it generates high frequency noise which causes severe issues related to power integrity (PI) and radio frequency interference (RFI) [35]. The larger envelope signal bandwidth, the higher noise level is produced. Therefore, innovative SMPS design is required to ensure low noise level.

- 4) Usually, decoupling capacitor is added at the output of power supply in order to eliminate the ripples and noise level. In the case of ET power supply, decoupling capacitor cannot be added since the supply power is not DC (has the shape of RF envelope). This means that ET supply must have very low output impedance to absorb any noise that might appear.

- **Delay:** This stage makes a delay in the RF input signal which is fed to the power amplifier. This compensates the response time of the detector and the ET power supply.

## 1.3.5 THz power detection

The THz frequencies spectrum is defined in the range 0.1 to 10 THz [36], these waves are located in the area between electronics and photonics fields in the electromagnetic spectrum. THz radiation is characterized by the following unique features:

- It can penetrate through a wide variety of dielectric materials such as fabric, paper, plastic, leather and wood.

- It is non-ionizing and has minimal effects on the human body.

- It is significantly absorbed by water at specific frequencies.

- It is highly reflected by metals.

In the context of THz power detection, terahertz imaging is utilized in many applications, some of them are mentioned in the following.

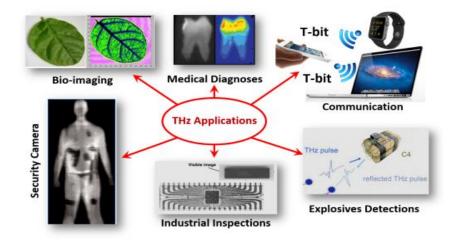

Figure 1.7 Some of THz applications [37].

As previously described, terahertz radiation is sensitive to water and has very low photon energy, those properties make THz imaging suitable for many biomedical applications [21]. The non-ionizing character of THz radiation makes it less harmful to living tissue than X-ray. This is especially interesting for medical applications such as cancer diagnosis [38]. It has been proved that terahertz imaging can replace other diagnostic technologies for imaging the structure of teeth [39]. High water absorption of THz radiation makes it a very useful tool for plant scientists for the inspection of the water in vegetative tissues [40].

In the field of defense and security, it has been shown that THz spectroscopy can be used for the detection of explosive materials, and concealed weapons [22]. THz imaging can also be an alternative to X-ray and non-imaging millimeter-wave systems [41].

In this thesis, integrated THz power detectors are designed using the SiGe 55-nm BiCMOS technology from STMicroelectronics in the frequency ranges (140 - 220) GHz, and (450 - 600) GHz.

Concerning the RF front ends devices, III-V technologies allow better performance comparing to silicon technologies. However, using the low cost BiCMOS technology to build our detectors allows the integration with the digital parts on the same chip. This helps reducing the losses and improving the overall efficiency.

Power detections at such high frequencies require high sensitivity value because of two main issues:

- The losses (in the probes, wave transitions and transmission lines) are relatively high. For example, the insertion loss of 50  $\Omega$  microstrip lines in BiCMOS technology from STMicroelectronics is about (3.5 dB/mm) at 500GHz (simulated performance).

- The electromagnetic waves are significantly attenuated by the medium (9 dB/km at 300 GHz for the air, depending of the relative humidity (RH)), thus the received power levels (to be detected) are relatively low.

#### **1.4 Power sensors**

There are several technologies available for RF power measurement. One of those technologies uses direct sensing elements, this includes:

- Thermal sensing elements (such as thermistors) to measure the heat effect of RF power.

- Nonlinear devices (such as diodes and transistors) which rectify the RF signal.

Another technology uses indirect methods to quantify the RF power, this includes:

- Tuner receiver which receives the RF signal, then its amplitude component is measured.

RF sampling, where the RF signal is treated as a baseband signal and directly digitized.

The power sensor has to be chosen following the applications. In the following paragraphs, different types of power measurement are briefly presented, then, different types of direct sensing elements are explained.

## **1.4.1 Power definition**

When voltage signal v(t) is applied on a load Z, current signal i(t) will pass through, and vice versa. The power dissipated (absorbed) in the load is defined in the following equation:

(1.2)

$$P = V_{rms} \cdot I_{rms} \cdot \cos(\phi)$$

Figure 1.8 The voltage, current and power absorbed in load Z.

Where  $V_{rms}$  and  $I_{rms}$  are the RMS values of the voltage and current signals over the load,  $\varphi$  represents the phase shift between the voltage and current signals. It is worth to mention that  $\varphi$  is equal to zero for pure resistive load.

The power P represented in equation 1.2 is commonly used in the RF and Microwave engineering, it is referred as the true or active power. This power quantity is what would be indicated by a thermal power meter.

#### 1.4.2 Types of power measurement

Figure 1.8 shows the power curve when a simple sinusoidal signal is applied. However, the waveforms are more complex in real applications (depending on the modulation type).

When modulated signals are considered, several definitions of power quantities are more appropriate [42]. In the following, each power quantity is briefly explained:

- The instantaneous power P(t): It represents the actual power of the signal (carrier) at any given time. The detection of this power type is considered as a reproduction of the waveform. A detector with very fast response is required in order to capture the fast variation of the signal carrier.

- The envelope power P<sub>e</sub>(t): It represents the actual power of the envelope signal at any given time. The detection of this power type is considered as a reproduction of the envelope signal (baseband signal). A detector with fast response is required in order to capture the variation of the envelope signal.

- The average power P<sub>avg</sub>: It represents the average value of the envelope power signal P<sub>e</sub>(t) over a specified period of time (usually the modulation period). The P<sub>avg</sub> value is what would be indicated by thermal power meters, therefore, this type of detection is usually referred as true-RMS detector. In this case, the detector does not need to have fast response, since it averages out the power of a waveform for a certain time period.

- The peak envelope power PEP: It represents the highest value of the envelope power signal P<sub>e</sub>(t). PEP is an important parameter for specifying transmitters (as explained in 1.3.3). A detector with a fast response is required in order to follow the peaks of the envelope signal.

Figure 1.9 Modulated signal with the illustration of several power types.

The pulse power P<sub>pulse</sub>: Measuring a signal with high power levels can damage the power sensor. One possible solution is to apply several bursts of the signal (pulsed signal) instead of continuous mode, this can avoid burning out the sensor. Radar system is another application where pulsed signal measurement is required. Such type of measurement can be done by dividing the average power P<sub>avg</sub> over the duty cycle of the pulses (D). The pulse power averages out all aberrations that can occur due to the pulse modulation, such as overshooting and ringing (as shown in figure 1.10). For this reason, it is called pulse power and not peak or peak pulse power.

Figure 1.10 Pulsed signal with the illustration of several power types.

As a conclusion, the heat based sensors can only measure the average power  $P_{avg}$  since no fast response is required.

#### **1.4.3 Some backgrounds of power detectors**

The RF signal power can be directly measured using power sensors and meters as shown in figure 1.11, where the power sensors are considered as the key elements. The function of the sensors is to convert the incoming high frequency power (i.e. RF, microwave, millimeter-wave or even higher) to a DC or low frequency signal. The meters measure (read) the output signal of the sensor, and then, display the result.

Figure 1.11 Basic block diagram of power detectors.

Two main types available of power sensors:

- 1) Heat based sensors (bolometers and thermocouples).

- 2) Diodes (or transistors).

In the following paragraphs, we present the principles of the bolometer, thermocouple, and diode detectors. Since the diode detector is the core of the thesis, it will be explained in detail in the next chapter.

#### 1.4.4 Heat based power detectors

As the name suggests, this type of detectors dissipates the incoming RF power into heat, the resulting temperature rise is somehow measured in order to calculate the RF power.

The heat based RF power sensors are able to measure the true average power as a heat over a period of time, thus, they measure the RF energy which is independent of the waveform. In many cases, this is considered as an advantage comparing to other detection techniques, where the PAPR can affect the results [43]. These detectors are mainly used as reference power standards, since they are considered to have very low uncertainty in their measurements [24].

Considering the response time, the heat based sensors are not suitable for measuring fast variation or instantaneous signal values due to their slow responses. Those types of measurement are usually done using diode based detectors. The heat based detectors mainly include two types of technologies: bolometers and thermocouples.

#### 1.4.4.1 **Bolometers**

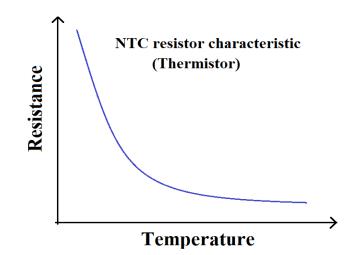

Bolometers are RF power sensors based on thermistors. These elements have negative temperature coefficient of resistance (NTC), i.e. their resistance values decrease with temperatures [44] (figure 1.12). The thermistor heats up as a result of dissipating RF power, as well as the effect of ambient temperature.

Figure 1.12 Thermistor characteristic with temperature [45].

This type of sensors was one of the first utilized to measure the RF power. In most of modern applications, bolometers are replaced by thermocouple and diode detectors due to their larger dynamic ranges and higher sensitivities.

Nowadays, thermistors are still used as reference power standards in most of national standards, this is because of two main reasons:

- They are the only present-day sensors which allow DC power substitution measurement techniques. This type of measurement can be done with very low uncertainty [46].

- 2) There are no weighting errors when RF power is converted into heat.

Thermistor elements can be mounted in coaxial cables or waveguide structures, thus, they can be fed by microwave signals (or even higher frequencies) using the common transmission lines. The sensor circuit has to be designed so that it absorbs the maximum possible of incident power. This can be done by fulfilling the following conditions:

- The impedance of the sensor circuit has to match the impedance of mounting structure.

- The losses in sensor circuits have to be minimum possible. Therefore, low resistivity and dielectric losses within the mounting structure are required. This is important because only the power dissipated in the thermistor is indicated in the power meter.

- The sensor has to be thermally isolated from the environment, hence, it is far less affected by the ambient temperature.

# **Operating principles:**

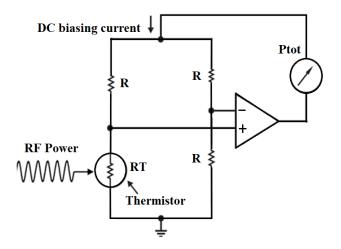

The most common implementation place of the thermistor is in auto-balancing Wheatstone bridge (as in figure 1.13) using the DC substitution technique [47].

In this case, the thermistor is considered as a temperature measurement device and RF load at the same time. The output of the amplifier is used as a power source to bias the bridge. Because the deferential input voltage of the amplifier is about zero, certain amount of power will be drawn bringing the bridge to the balance stat (i.e. producing RT is equal to the other resistors R).

We call the power  $P_{OFF}$  is the total power drawn by the balanced bridge  $(P_{tot})$  before applying the RF signal. When the input RF power is injected, the thermistor absorbs this power producing additional heat. Hence, the (RT) value tends to be lower, and the bridge is no more balanced. Because of the feedback power source configuration, the power drawn  $(P_{tot})$  is decreased bringing back the bridge to the balance state. We call the later power  $P_{ON}$ .

Figure 1.13 Thermistor as RF power detector in Wheatstone bridge configuration [47].

The total power dissipated in the thermistor is due to the incoming RF power and the DC bias. As a result, the incoming RF power can be extracted using the difference  $(P_{OFF} - P_{ON})$ . This computation is only valid in the ideal case, i.e. all the incoming RF power is absorbed in the thermistor. In practice, there are some existing losses in the input transmission line, the mount structure, and others; correction factor is added to take those facts into account.

It worth to mention that the three resistors (R) are designed to have a negligible temperature coefficient of resistance; otherwise, error of measurement can be produced. To avoid having this error, the bridge is configured with two identical thermistors; where only one thermistor is exposed to the RF power; the second thermistor is used to compensate the variation in ambient temperature.

#### 1.4.4.2 **Thermocouple sensors**

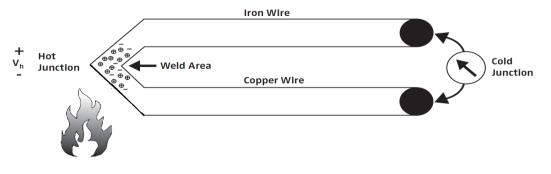

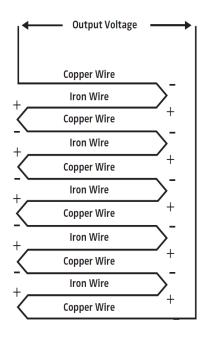

The working principle of thermocouple sensors is based on Peltier effect. It tells that, dissimilar metals generate a potential due to temperature differences at a hot and a cold sides of the metals as in figure 1.14. The thermocouples have been used as RF power sensors since their introduction in 1974 [48]. In practice, number of thermocouples are electrically connected in series to build the thermopile as shown in the figure 1.15.

Figure 1.14 Simple thermocouple structure.

This connection can boost up the output voltage, hence, it can be easily amplified and measured by voltmeter. The thermocouples provide three main advantages over the thermistors [49]:

- > They exhibit higher sensitivity levels and larger dynamic ranges.

- $\succ$  They are more rugged.

- They exhibit higher performance at high frequency bands. This is because the power sensor is electrically isolated from the RF input circuit, thus, it does not suffer from the problem of the high frequency leakage through the DC bias circuit.

Figure 1.15 Thermocouples are connected in series (thermopile).

# **Operating principles:**

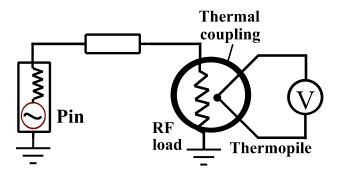

Modern thermocouple sensors are typically designed to be integrated in silicon circuit chip [50]. The incoming RF power is injected and absorbed by an integrated RF load. This load is thermally coupled with the hot junctions of the thermopile (as illustrated in figure 1.16), hence, the heat generated in the load rises up the temperature of the hot junctions. This increase of temperature is quantified by measuring the DC output voltage of the thermopile. This voltage is very linear with input power and has a relatively long time constant due to heat flow delays.

Figure 1.16 Block diagram of thermocouple detector.

# 1.4.5 Diode based detectors

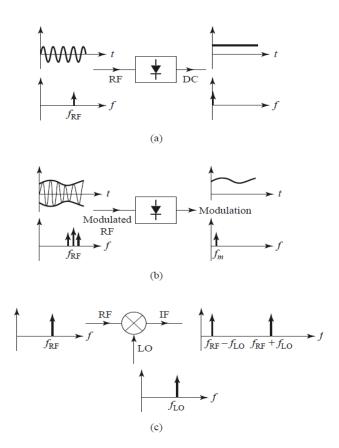

Since 1900s, diodes have been used as passive devices in most of electronic systems [51]. Their fundamentals and applications have not changed since 1980s. However, their technologies have been continuously developed in order to improve their performances, and allow to operate at higher frequencies. In microwave engineering, the diodes are used in three main applications [52]:

Rectification: Converting high frequency signal to DC.

> Detection: Demodulating of amplitude-modulated signal.

Mixing: Shifting (up or down) the frequency of an input RF signal.

The diodes convert high frequency energy to DC (or low frequencies) using their rectification properties; these properties arise due to their nonlinear current-voltage (I-V) characteristic. When diode is used as a power detector, the high frequency signal is directly applied on the diode, and then, the output low frequency signal is measured.

PN, Schottky (SBD) and backward tunnel (BTD) diodes are the main diode types used in the power detection [53]. Usually, the fabrication of BTD is more difficult than SBD, however the BTDs exhibit higher sensitivity values at zero bias with lower value of video resistance, and lower temperature dependence [54].

Figure 1.17 Basic diode functions: (a) diode rectifier, (b) diode detector, (c) mixer [52].

Diode based power detectors have two major advantages:

1) They are able to measure very low levels of power (down to -90 dBm).

2) They exhibit fast response, hence, they can track the fast variation of the RF signal. On the other hand, the diodes sensors are very sensitive to ambient temperature, in addition, they have poor linearity. Therefore, the heat based detectors are still adopted as the transfer standard detectors.

### **1.5** Conclusion

In this chapter, we showed the importance of the power measurements in several microwave and THz applications. We also showed that the power levels are relatively

low at such high frequencies, this is due to the high losses in the mediums and systems circuitries, therefore, detectors with high sensitivity values are required.

Different types of power measurements were briefly explained, where the required measurement type is determined following the applications.

The heat and diode based detectors were briefly introduced. The heat based detectors are very accurate for true RMS power measurement. However, their response time is slow. Therefore, they are suitable for steady state or continuous wave (CW) signals. In addition, they are often used as reference power standards. The diode based detector can track the fast variations of input signals. However, they suffer from poor linearity and high sensibility to ambient temperature. The table 1.1 shows a direct comparison between those detectors, indicating the better one to be used concerning each parameter.

|                                      | Heat based detectors                 | Diode based detectors              |

|--------------------------------------|--------------------------------------|------------------------------------|

| Cost                                 |                                      | Lower cost                         |

| Simplicity                           |                                      | Simpler structure                  |

| Accuracy                             | Most accurate                        |                                    |

| Linearity                            | Best linearity                       |                                    |

| Integrity                            |                                      | Easier to be integrated            |

| Response time                        |                                      | Faster response                    |

| Sensibility to waveform              | Not sensible to signal waveforms     |                                    |

| Sensibility to temperature           | Less affected by ambient temperature |                                    |

| Working bandwidth                    | Can work at larger frequency band    |                                    |

| Minimum detectable<br>power          |                                      | Can detect lower level of RF power |

| Voltage (or Current )<br>Sensitivity |                                      | Have higher values of sensitivity  |

#### Table 1.1 Comparison between heat and diode based power detectors.

In a nutshell, each type of power sensor has its own strengths and weaknesses following its application.

# Chapter 2 Diode Based Detectors Theory & Parameters

## 2.1 Introduction

In this chapter, the theory of the diode based power detector will be discussed in detail, since it is the core of this thesis. Following the application, certain detector parameters are more critical than others. The correlations between these parameters will be explained in detail. This will help to develop detectors with optimal specifications, dedicated to certain applications.

# 2.2 Diode detector principles

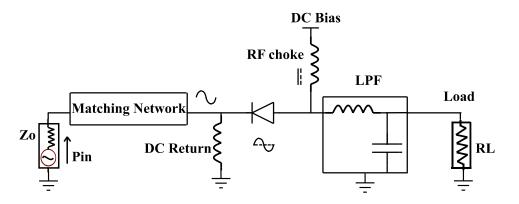

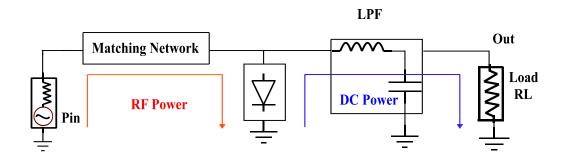

RF and microwave signals can be detected using a nonlinear semiconductor device such as diodes or transistors. Figure 2.1 shows the basic configuration of diode based detectors (video receiver), where the diode is utilized to rectify the high frequency signal. This configuration can be more complicated (depending on the topology); for example, several diodes might be utilized (instead of single diode) in order to improve some detection parameters.

Figure 2.1 Basic diode detector configuration [55].

The function of each block is explained in the following:

- > The RF signal source: The source can be an antenna, amplifier, or any stage which feeds an available power  $P_{in}$ , with an internal impedance Zo.  $P_{in}$  is the power to be measured.

- Matching network: Usually, the input impedance of detector is not matched with the source impedance Zo. Therefore, matching network is necessary to ensure that

maximum RF power is absorbed in the detector, meanwhile avoiding standing waves which can cause an error of measurement [24].

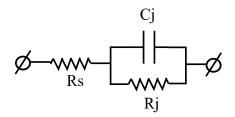

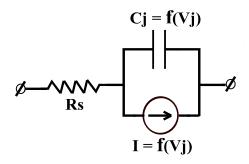

> **Diode:** (PN or Schottky) diodes or any equivalent device such as diode connected transistors can be employed to rectify the RF signal. The diode is biased using DC power (voltage or current) source to allow operating at a certain DC point. However, some types of diodes (usually Schottky diodes) have low threshold voltages, thus no DC biasing source is required; this type of diodes is called zero bias. The intrinsic equivalent circuit of diode (small signal model) consists of an active part  $R_j$  (the junction nonlinear resistor which rectifies the signal), in parallel with parasitic junction capacitance  $C_j$  (which is considered as a parasitic capacitance). As well as a series resistance  $R_s$  representing the resistance of the active layer [56].

Figure 2.2 The intrinsic small signal model of diode.

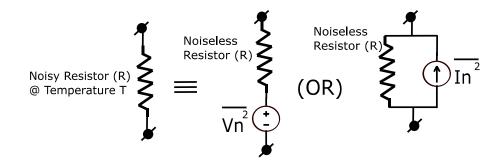

- Choke inductors: They exhibit high impedance to RF signal and short circuit to DC and low frequency signals. The function of these inductors is to avoid RF short circuit through the DC biasing source (or the ground directly). The DC return choke inductor pulls the cathode potential to the DC ground, providing a closed DC biasing circuit. Figure 2.3 shows the circuit paths for RF and baseband signals.

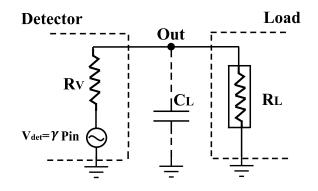

- Low pass filter (LPF): This filter is considered as the key element to correctly follow the variation of the envelope (baseband) signal. The main function of this filter is to determine the bandwidth of the output signals (rectified signals); this bandwidth is called video bandwidth. Depending on the application, there are several LPF topologies which can be used such as RLC (as in figure 2.1) or simple RC filter. The video bandwidth has to be carefully chosen to avoid increasing the noise floor of the detector (more details are explained in paragraph 2.3.6).

(b)

Figure 2.3 The circuit path of: (a) DC and low frequency signals, (b) RF signal.

▶ Load  $(R_L)$ : The detector drives the load  $R_L$  which is connected at its output. Depending on the application, the load can be (1) a simple voltmeter, (2) an amplifier to extract the envelope signal, (3) ADC (analog to digital converter) to allow digital processing of the RF power value, (4) modulated power supply to control the biasing of an amplifier, etc. To avoid loading the detector, the internal impedance value of the diode has to be much smaller (or even negligible) comparing to the load impedance  $(R_L)$ , hence, the DC biasing current only flows through the diode (more details are explained in 2.3.5).

# 2.3 Diode detector parameters

To establish the RF power measurement, the detector parameters have to be carefully chosen (or designed). In practice, we cannot obtain an ideal power detector with the best performances in all parameters. Therefore, some detector parameters are usually sacrificed (or degraded) in order to improve (or make the trade-off with) others. In the following, we explain the theory of those parameters, and the relations between each other.

# **2.3.1 Bandwidth of interest** ( $\Delta f$ )

The bandwidth of interest represents the desired frequency band (of RF signal) which can be measured by the detector. The bandwidth is probably the first parameter to be considered when choosing (or designing) a power detector. To maximize the absorbed power at the input, a matching network (corresponding to the bandwidth of interest) can be added (or integrated) to the detector. This network also rejects the undesired frequencies which can be injected in the detector. A bulky matching network can cause significant losses in the input power (especially at high frequencies), thus, small networks sizes are recommended.

# 2.3.2 Power consumption $(P_D)$

And

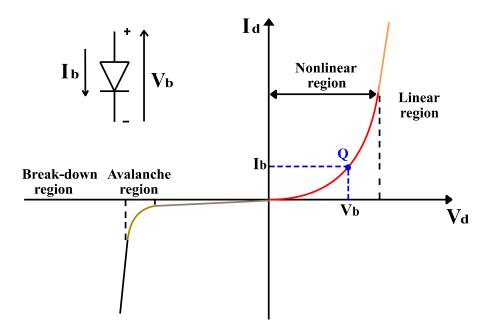

As discussed in the paragraph 2.2, some diodes need to be biased in order to operate at a certain DC point (Q). This helps to decrease their high impedances (since high impedance can block the input signal), and enhance their non-linearity of I-V curve (which is poor around 0). Figure 2.4 shows the different regions of I-V diode characteristic, and the static operating point Q. For the detection purpose, the diode has to be biased so the Q point is kept in the nonlinear region. The following equation provides the I-V relation of a diode [57]:

$$I = I_{s} (\exp(V/nV_{T}) - 1)$$

(2.1)

$$I_{S} = A^{*}.A.T^{2} \exp\left(\frac{-q.\phi_{B}}{K.T}\right)$$

(2.2)

Where I, and V are the current and voltage across the junction, n is the ideality factor,  $I_s$  is the saturation current,  $V_T$  is the thermal voltage ( $V_T = 26$  mV at room temperature), A is the

effective junction area,  $A^*$  is the effective Richardson constant, K is the Boltzmann constant, T is the absolute temperature in kelvin, and  $Ø_B$  is the barrier height with no bias.

Figure 2.4 I-V characteristic of a diode in different operating regions.

The DC power consumed for biasing the diode is given in the equation 2.3.

$$P_D = V_b \times I_b \qquad (W) \tag{2.3}$$

Where  $V_b$  and  $I_b$  are the DC voltage and current biasing values. From the equation 2.3, the higher current (or voltage) biasing value, the higher is the power consumption. In some applications, the power consumption is a critical parameter. As an example, the diode detector which is employed to improve an amplifier efficiency (and decrease the overall power consumption as in ET technique in figure 1.6). In this case, using a zero bias diode (where no DC biasing required) can be the optimal solution.

Varying the value of biasing current (or voltage) affects all the detector parameters. This includes power consumption, matching condition, sensitivity value, noise floor, dynamic range and video resistance. All those effects are explained in the next paragraphs.

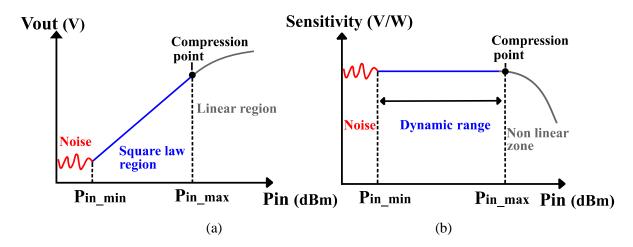

# **2.3.3** Voltage or current sensitivity ( $\gamma$ )

The sensitivity is the ability of a detector to convert the input RF signal into DC or low frequency signal. The last corresponds to extract the envelope signal of high frequency signal. In this thesis, we are interested in the voltage sensitivity values, thus, DC current source is required for biasing the diode.

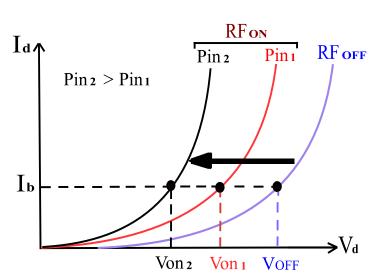

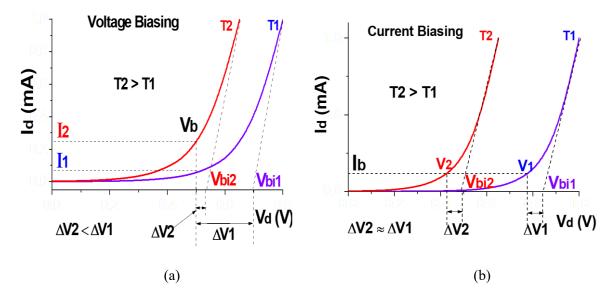

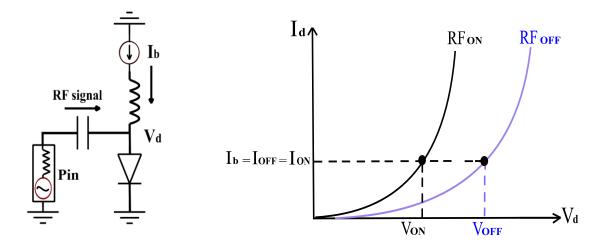

We define  $(V_{OFF})$  as the DC voltage across the diode corresponding to the DC biasing current  $(I_b)$ ; while the voltage  $(V_{ON})$  is the DC voltage across the biased diode (using the same  $I_b$ ) when the RF power is applied (as illustrated in figure 2.5).

For low level of RF power, the difference voltage  $(V_{OFF} - V_{ON})$  is proportional to the applied RF power. The voltage sensitivity (response coefficient in V/W) of a diode can be defined by the equation 2.4.

$\gamma = \frac{V_{OFF} - V_{ON}}{P_{in}} \qquad (V/W) \tag{2.4}$

Figure 2.5 I-V curves for three states of input RF power, with a constant biasing current  $I_b$ .

In the equation 2.4,  $P_{in}$  is the available input power. Higher sensitivity value means that the detector is able to generate higher output DC voltage for lower RF input power. This is considered one of the most important parameters for selecting a power detector. For example, in millimeter and submillimeter waves applications, the level of losses in the overall systems is relatively high and signal levels usually of limited power. Thus, week levels of RF input power is usually to be measured. In this case, having power detector with high sensitivity value is mandatory.

The sensitivity value depends on several parameters mentioned in the following:

- Physical characteristics of the device: We can mention several characteristics such as doping level of the active layer, and series (access) resistances of the diode. The efficiency of the device increases (and so the sensitivity value) by decreasing the parasitic effects, such as parasitic capacitance with substrate.