### SCUOLA SUPERIORE SANT'ANNA UNIVERSITÉ DE LILLE École doctorale des sciences pour l'ingénieur

Thèse de doctorat en informatique et applications préparée au sein des laboratoires ReTiS et CRIStAL

Enabling Predictable Hardware Acceleration in Heterogeneous SoC-FPGA Computing Platforms

Techniques pour l'amélioration de la prévisibilité de l'accélération matérielle pour les plateformes informatiques hétérogènes SoC-FPGA

Marco Pagani

Supervisors - Directeurs de thèse Giorgio Buttazzo, Giuseppe Lipari

> *Tutor* Mauro Marinoni

Soutenue le 20 juillet 2020 devant le jury composé de:

| Smail Niar            | Université Polytechnique Hauts-de-France | Examinateur  |

|-----------------------|------------------------------------------|--------------|

| Jörg Henkel           | Karlsruher Institut für Technologie      | Examinateur  |

| Luca Abeni            | Scuola Superiore Sant'Anna               | Examinateur  |

| Francesca Palumbo     | Università degli Studi di Sassari        | Examinatrice |

| Sanjoy Baruah         | Washington University in St. Louis       | Rapporteur   |

| Liliana Cucu-Grosjean | INRIA de Paris                           | Rapportrice  |

| Giusppe Lipari        | Université de Lille                      | Directeur    |

| Giorgio Buttazzo      | Scuola Superiore Sant'Anna               | Directeur    |

Ph.D. course in emerging digital technologies Academic year 2018/2019

## Abstract

Modern computing platforms for embedded systems are evolving towards heterogeneous architectures comprising different types of processing elements and accelerators. Such an evolution is driven by the steady increasing computational demand required by modern cyber-physical systems. These systems need to acquire large amounts of data from multiple sensors and process them for performing the required control and monitoring tasks. These requirements translate into the need to execute complex computing workloads such as machine learning, encryption, and advanced signal processing algorithms, within the timing constraints imposed by the physical world. Heterogeneous systems can meet this computational demand with a high level of energy efficiency by distributing the computational workload among the different processing elements.

This thesis contributes to the development of system support for real-time systems on heterogeneous platforms by presenting novel methodologies and techniques for enabling predictable hardware acceleration on SoC-FPGA platforms. The first part of this thesis presents a framework designed for supporting the development of real-time applications on SoC-FPGAs, leveraging hardware acceleration and logic resource "virtualization" through dynamic partial reconfiguration. The proposed framework is based on a device model that matches the capabilities of modern SoC-FPGA devices, and it is centered around a custom scheduling infrastructure designed to guarantee bounded response times. This characteristic is crucial for making dynamic hardware acceleration viable for safety-critical applications. The second part of this thesis presents a full implementation of the proposed framework on Linux. Such implementation allows developing predictable applications leveraging the large number of software systems available on GNU/Linux while relying on dynamic FPGA-based hardware acceleration for performing heavy computations. Finally, the last part of this thesis introduces a reservation mechanism for the AMBA AXI bus aimed at improving the predictability of hardware accelerators by regulating BUS contention through a bandwidth reservation mechanism.

## Riassunto

Le moderne architetture di calcolo per sistemi integrati sono in via di evoluzione verso piattaforme sempre più eterogenee, comprendenti diverse tipologie di processori e acceleratori. Tale evoluzione è guidata dalla necessità di soddisfare la crescente richiesta di capacità di calcolo da parte dai moderni sistemi cyber-fisici. Questi sistemi hanno la necessità di acquisire e processare grandi quantità di dati, provenienti da differenti sensori, in modo da poter eseguire le necessarie operazioni di controllo e supervisione. Tali requisiti si traducono nella necessità di eseguire carichi computazionali complessi quali algoritmi per l'apprendimento automatico, l'elaborazione numerica dei segnali e la crittografia, nel rispetto dei vincoli temporali imposti dall'interazione con il mondo fisico. Le piattaforme eterogenee consentono di soddisfare questa domanda di calcolo distribuendo il carico di lavoro di calcolo tra i diversi processori e acceleratori, mantenendo quindi un elevato livello di efficienza energetica.

Questa tesi contribuisce allo sviluppo del supporto per i sistemi in tempo reale su le piattaforme eterogenee, presentando un insieme di tecniche e metodologie per rendere predicibile l'accelerazione hardware su piattaforme SoC-FPGA. La prima parte di questa tesi presenta un framework progettato per supportare lo sviluppo di applicazioni in tempo reale su piattaforme SoC-FPGA, sfruttando l'accelerazione hardware e la riconfigurazione dinamica parziale per «virtualizzare» le risorse logiche. Il framework è basato su un device model che esprime le caratteristiche delle moderne piattaforme SoC-FPGA, ed è strutturato intorno a un'infrastruttura di schedulazione progettata per garantire tempi di risposta limitati. Questa caratteristica è fondamentale per rendere l'accelerazione hardware dinamica utilizzabile nel contesto dei sistemi critici. La seconda parte della tesi presenta un implementazione completa del *framework* proposto su Linux. Grazie a questa implementazione, è possibile sviluppare applicazioni predicibili in ambiente GNU/Linux, sfruttando l'accelerazione dinamica basata su FPGA per eseguire le operazioni computazionalmente più pesanti, utilizzando al contempo la grande quantità di software e librerie offerte dall'ambiente. Successivamente, l'ultima parte di questa tesi presenta un meccanismo di regolazione della banda per il bus AMBA AXI concepito per migliorare la predicibilità dell'accelerazione hardware sulle piattaforme eterogenee.

## Résumé

Les architectures informatiques modernes pour les systèmes intégrés évoluent vers des plateformes de plus en plus hétérogènes, comprenant différents types de processeurs et d'accélérateurs. Cette évolution est entraînée par la nécessité de répondre à la demande croissante de capacité de calcul par les systèmes cyber-physiques modernes. Ces systèmes doivent acquérir et traiter de grandes quantités de données, provenant de différents capteurs, afin d'exécuter les tâches de contrôle et de surveillance nécessaires. Ces exigences se traduisent par la nécessité d'exécuter des charges de calcul complexes telles que des algorithmes d'apprentissage automatique, de traitement numérique des signaux et de cryptographie, en respectant les contraintes de temps imposées par l'interaction avec le monde physique. Les plateformes hétérogènes permettent de répondre à cette demande de calcul, en distribuant le travail entre les différents processeurs et accélérateurs, ce qui permet de maintenir un niveau élevé d'efficacité énergétique.

Cette thèse contribue au développement du support pour les systèmes temps réels sur des plateformes hétérogènes, en présentant un ensemble de techniques et de méthodologies pour rendre prévisible l'accélération matérielle sur les plateformes SoC-FPGA. La première partie de cette thèse présente un framework pour soutenir le développement d'applications en temps réel sur les plateformes SoC-FPGA, en utilisant l'accélération matérielle et la reconfiguration dynamique partielle pour « virtualiser » les ressources logiques. Le framework est basé sur un *device model* qui exprime les caractéristiques des plateformes SoC-FPGA modernes, et il est structuré autour d'une infrastructure d'ordonnancement conçue pour garantir des temps de réponse limités. Cette caractéristique est fondamentale pour rendre l'accélération matérielle dynamique viable dans le contexte des systèmes critiques. La deuxième partie de la thèse présente une implémentation complète du framework proposé sur Linux. Grâce à cette implémentation, il est possible de développer des applications prévisibles dans l'environnement GNU/Linux, en profitant de l'accélération dynamique basée sur FPGA pour exécuter les opérations de calcul les plus intensifs, tout en utilisant la grande quantité de logiciels et de

bibliothèques offerts par l'environnement. Ensuite, la dernière partie de cette thèse présente un mécanisme de régulation de la bande pour le bus AMBA AXI conçu pour améliorer la prévisibilité de l'accélération matérielle sur les plateformes hétérogènes.

# Contents

| 1        | Intr | oduction                                              | 9         |

|----------|------|-------------------------------------------------------|-----------|

|          | 1.1  | FPGA as computing devices                             | 10        |

|          |      | 1.1.1 Software programmable devices                   | 10        |

|          |      | 1.1.2 SIMD processing and GPUs                        | 11        |

|          |      | 1.1.3 Instruction set architecture                    | 11        |

|          |      | 1.1.4 FPGA as programmable computing devices          | 11        |

|          |      | 1.1.5 High-level systemes is                          | 13        |

|          |      | 1.1.6 FPGA-based hardware accelerators                | 13        |

|          |      | 1.1.7 Overheads and limitations of HW-programmability | 16        |

|          | 1.2  | Predictability of hardware accelerators               | 16        |

|          | 1.3  | Heterogenous SoC-FPGAs                                | 17        |

|          | 1.4  | Reconfigurable hardware                               | 18        |

| <b>2</b> | Ess  | ential background                                     | <b>21</b> |

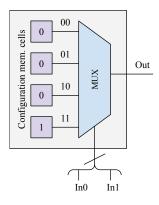

|          | 2.1  | Overview of FPGAs architecture                        | 22        |

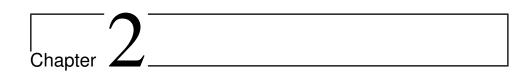

|          |      | 2.1.1 Internal architecture                           | 22        |

|          | 2.2  | Design flow                                           | 25        |

|          | 2.3  | FPGA configuration                                    | 25        |

|          |      | 2.3.1 Dynamic partial reconfiguration                 | 26        |

|          | 2.4  | On-chip interconnections                              | 26        |

| 3        | The  | e FRED framework                                      | 28        |

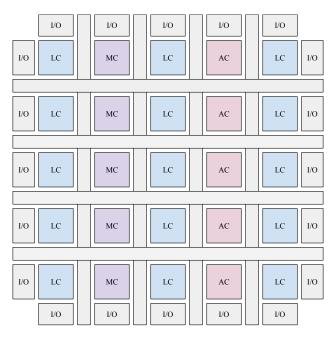

|          | 3.1  | Platform model                                        | 29        |

|          | 3.2  | Application model                                     | 29        |

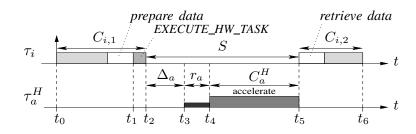

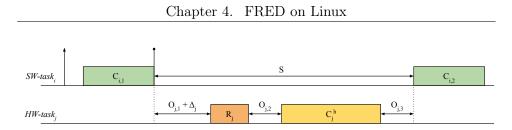

|          |      | 3.2.1 Hardware task model                             | 29        |

|          |      | 3.2.2 Reconfiguration interface model                 | 30        |

|          |      | 3.2.3 Software task model                             | 30        |

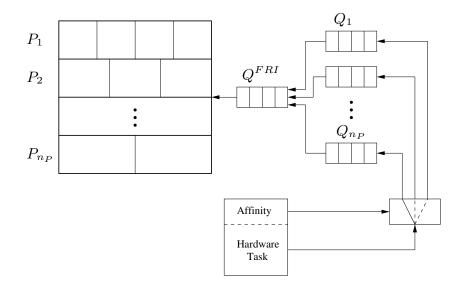

|          | 3.3  | Scheduling infrastructure                             | 32        |

|          |      | 3.3.1 Slot scheduling                                 | 33        |

|          |      | 3.3.2 FRI scheduling                                  | 33        |

| Contents |

|----------|

|----------|

|          |                |          | Ficket-based scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   |   |   |   |   |   |   | 34        |

|----------|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|---|-----------|

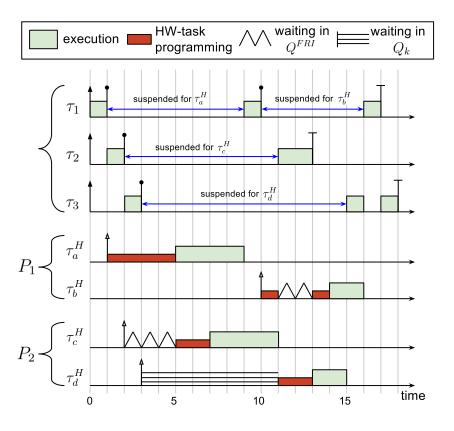

|          | <b>a</b> 4     |          | Scheduling example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |   |   |   |   |   |   |   | 35        |

|          | 3.4            |          | nication between SW and HW-tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |   |   |   |   |   |   |   | 36        |

|          | 3.5            | -        | e-time bounds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |   |   |   |   |   |   |   | 38        |

|          | 3.6            |          | I validation and profiling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |   |   |   |   |   |   | 39        |

|          |                |          | System architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |   |   |   |   |   |   |   | 40        |

|          |                |          | Experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |   |   |   |   |   |   |   | 40        |

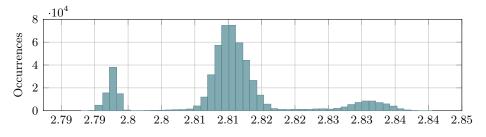

|          |                | 3.6.3 I  | Experimental results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | · | • | • | • | • | • | • | • | 41        |

| 4        | FRI            | ED on L  | inux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |   |   |   |   |   |   |   | <b>43</b> |

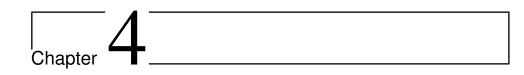

|          | 4.1            | Platform | n support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |   |   |   |   |   |   |   | 44        |

|          |                |          | System support design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |   |   |   |   |   |   |   | 44        |

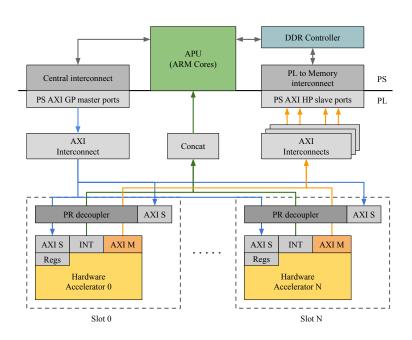

|          | 4.2            |          | $_{\rm 1}$ pport                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |   |   |   |   |   |   |   | 48        |

|          |                |          | Kernel-space components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   |   |   |   |   |   |   | 49        |

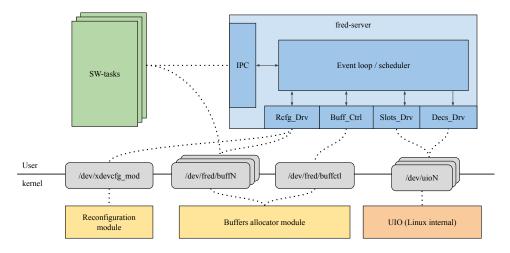

|          |                |          | Jser-space components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |   |   |   |   |   |   |   | 51        |

|          | 4.3            |          | upport library API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |   |   |   |   |   |   |   | 55        |

|          | 4.4            |          | $dy application \dots \dots \dots \dots \dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |   |   |   |   |   |   | 59        |

|          |                |          | Case study architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   |   |   |   |   |   |   | 59        |

|          |                |          | Application internals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |   |   |   |   |   |   |   | 61        |

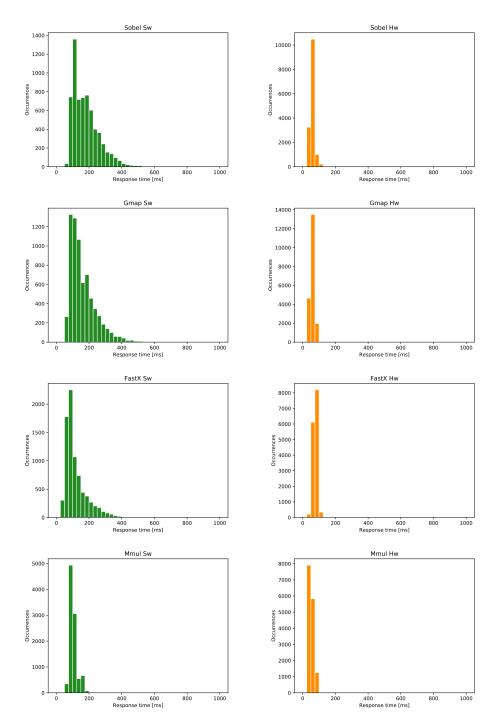

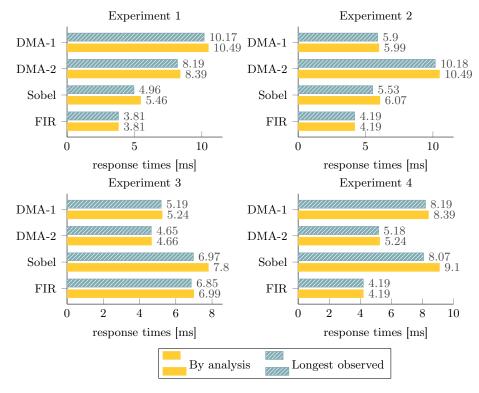

|          | 4.5            |          | ance evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |   | 63        |

|          | 1.0            |          | Speed up evaluation experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |   | 63        |

|          |                |          | System acceleration experiment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |   |   |   |   |   |   |   | 64        |

|          |                |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • | • | • | • | • |   |   | · | 01        |

| <b>5</b> | $\mathbf{Enh}$ | ancing   | BUS predictability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |   |   |   |   |   |   |   | 68        |

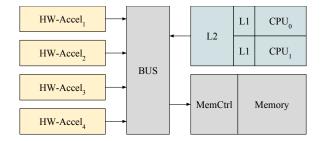

|          | 5.1            | The pro  | blem of BUS contention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |   |   |   |   |   |   |   | 69        |

|          | 5.2            | System   | model and Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |   |   |   |   |   |   |   | 70        |

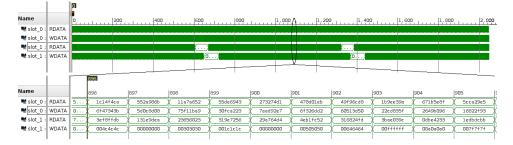

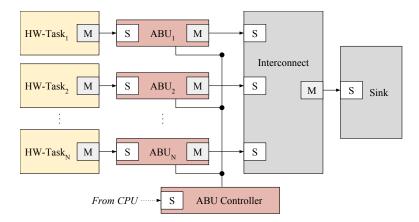

|          |                | 5.2.1    | AXI interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |   |   |   |   |   |   |   | 70        |

|          |                | 5.2.2 I  | HW-tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |   |   |   |   |   |   |   | 72        |

|          |                | 5.2.3    | Sink module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |   |   |   |   |   |   | 73        |

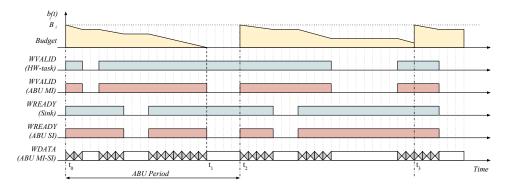

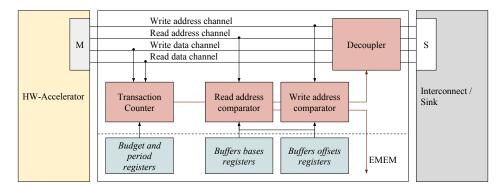

|          | 5.3            | AXI Bu   | dgeting Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |   |   |   |   |   |   |   | 74        |

|          |                | 5.3.1    | ABU working principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |   |   |   |   |   |   |   | 75        |

|          | 5.4            |          | dth-driven response-time analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |   |   |   |   |   |   |   | 77        |

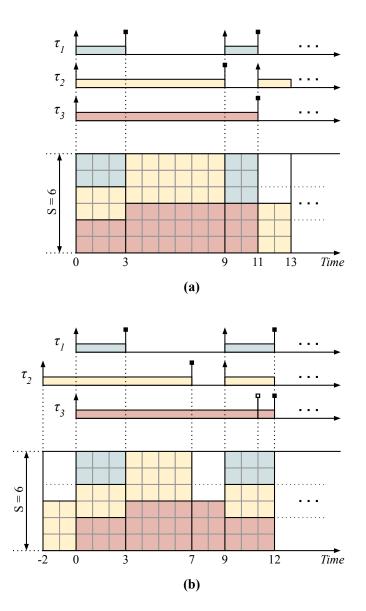

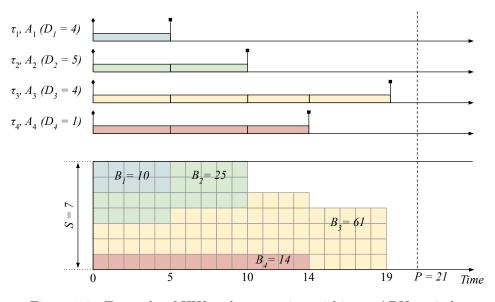

|          |                |          | Ilustrative example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |   |   |   |   |   |   |   | 78        |

|          |                |          | Analysis issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |   |   |   |   |   |   |   | 80        |

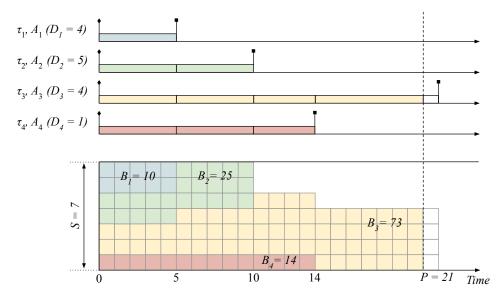

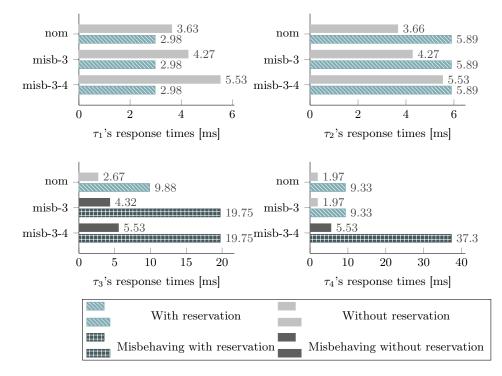

|          | 5.5            |          | e-time analysis with ABUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |   |   |   |   |   |   |   | 81        |

|          |                | -        | Analyzing ABUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |   |   |   |   |   |   |   | 81        |

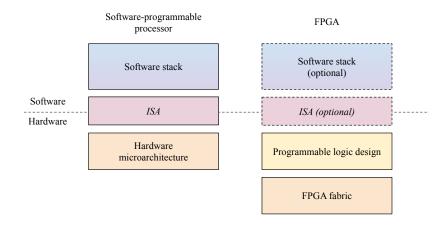

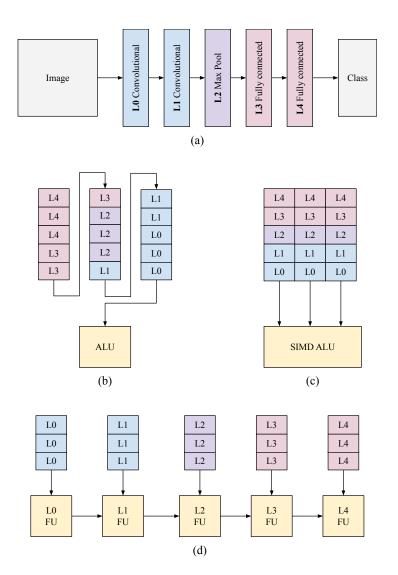

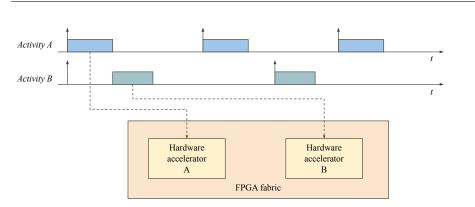

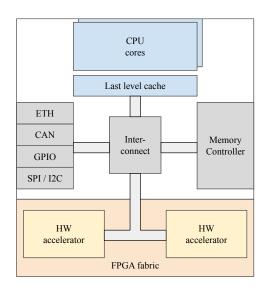

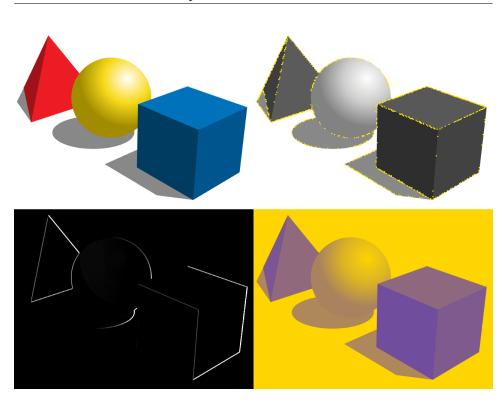

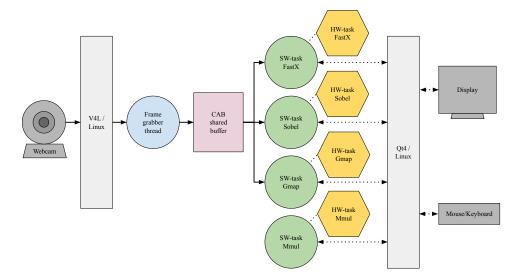

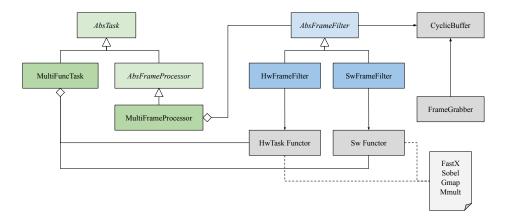

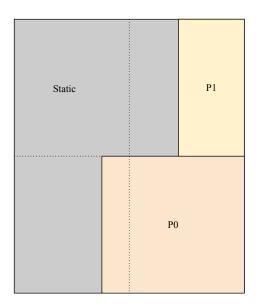

|          |                |          | Analysis example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |   |   |   |   |   |   |   | 85        |