# THÈSES

50.376 1968 28

PRÉSENTÉES

# A LA FACULTÉ DES SCIENCES DE L'UNIVERSITÉ DE LILLE

POUR OBTENIR

# LE GRADE DE DOCTEUR ÈS-SCIENCES PHYSIQUES

PAR

Vincent Cordonnier ingénieur ISEN licencié ès-sciences physiques diplomé d'études supérieures

# PREMIÈRE THÈSE

# ETUDE DE LA SIMULTANEITE EN MEMOIRE CENTRALE D' UN ORDINATEUR MODELE DE MEMOIRE PARTAGEE

DEUXIÈME THÈSE

Propositions données par la Faculté

Soutenues en mai 1968 devant la Commission d'examen

MM. P. BACCHUS

Président

P. POUZET

P. VIDAL

Examinateurs

J. ARSAC

Membre invité

# UNIVERSITE DE LILLE FACULTE DES SCIENCES

### DOYENS HONORAIRES

MM. H. LEFEBVRE, M. PARREAU

#### PROFESSEURS HONORAIRES

MM. ARNOULT, BEGHIN, BROCHARD, CAU, CHAPPELON, CHAUDRON, CORDONNIER, DEHEUVELS, DEHORNE, DOLLE, FLEURY, P. GERMAIN, KAMPE DE FERIET, KOURGANOFF, LAMOTTE, LELONG, Mme LELONG, MM. MAZET, MICHEL, NORMANT, PARISELLE, PASCAL, PAUTHENIER, ROIG, ROSEAU, ROUBINE, ROUELLE, WIEMAN, ZAMANSKY.

#### DOYEN

Monsieur DEFRETIN, Professeur de biologie et physiologie animales.

#### ASSESSEURS

MM. HEUBEL, Professeur de chimie. LEBRUN, Professeur d'électronique.

#### PROFESSEURS

MM. BACCHUS Mathématiques Appliquées

BEAUFILS Chimie

BONNEMAN Chimie

BECART Physique

BLOCH Biologie et Physiologie Animales

BOUGHON Sciences de la Terre

BOUGHON Mathématiques Pures

BOUISSET Biologie et Physiologie Animales

BOURIQUET Biologie Végétale

CELET Sciences de la Terre

CONSTANT Electronique, Electrotechnique et Automatique

CORSIN Sciences de la Terre

DECUYPER Mathématiques Pures

DEDECKER Mathématiques Pures

DEHORS Electronique, Electrotechnique et Automatique

DELATTRE Sciences de la Terre

MM. DELEAU Sciences de la Terre

DELHAYE Chimie

DESCOMBES Mathématiques Pures

DURCHON Biologie et Physiologie Animales

FOURET Physique

GABILLARD Electronique, Electrotechnique et Automatic

GLACET Chimie

GONTIER Mathématiques Appliquées

HEIM DE BALSAC Biologie et Physiologie Animales

HOCQUETTE Biologie Végétale

LEBEGUE Botanique (Amiens)

Mme LEBEGUE Physique (Amiens)

Melle LENOBLE Physique

LIEBAERT Electronique, Electrotechnique et Automatique

LINDER Biologie Végétale

LUCQUIN Chimie

MARION Chimie (Amiens)

MARTINOT-LAGARDE Mathématiques Appliquées

Melle MARQUET Mathématiques Pures

MENNESSIER Géologie (Amiens)

MONTARIOL Chimie

MONTREUIL Chimie

MORIAMEZ Physique (Valenciennes)

MOUVIER Chimie (Saint-Quentin)

PARREAU Mathématiques Pures

PEREZ Physique

PHAM MAU QUAN Mathématiques Pures

POUZET Mathématiques Appliquées

PROUVOST Sciences de la Terre

SAVARD Chimie SCHILTZ Physique

SCHALLER Biologie et Physiologie Animales

Mme SCHWARTZ Mathématiques Pures

TILLIEU Physique

TRIDOT Chimie

VAZART Botanique (Amiens)

VIVIER Biologie et Physiologie Animales (Amiens)

MM. WATERLOT

Sciences de la Terre

WERTHEIMER

Physique

MAITRES DE CONFERENCES

MM. BELLET Physique

BENABOU Mathématiques Pures

BILLARD Physique

BOILLET Physique

BUI TRONG LIEU Mathématiques Pures

CHERRUAULT Mathématiques Pures

CHEVALIER Mathématiques (Amiens)

DERCOURT Sciences de la Terre

DEVRAINNE Chimie (Calais)

Mme DIXMIER Mathématiques (Amiens)

Mme DRAN Chimie

DUQUESNOY Chimie (Amiens)

GOUDMAND Chimie

GUILBAULT Biologie et Physiologie Animales

GUILLAUME Biologie Végétale

HENRY Physique (Amiens)

HERZ Mathématiques Appliquées

HEYMAN Physique (Amiens)

HUARD DE LA MARRE Mathématiques Appliquées

JOLY Biologie et Physiologie Animales (Amiens)

LABLACHE-COMBIER Chimie

LACOSTE Biologie Végétale

LAMBERT Physique (Saint-Quentin)

LANDAIS Chimie

LEHMANN Mathématiques Pures

Mme LEHMANN Mathématiques Pures

LOUCHEUX Chimie

MAES Physique

METTETAL Zoologie (Amiens)

MONTEL Physique

NGUYEN PHONG CHAU Mathématiques (Saint-Quentin)

PANET Electronique, Electrotechnique et Automatique

PARSY

Mathématiques Pures

RACZY

Physique (Valenciennes)

SAADA

Physique

SEGARD

Chimie

TUDO

Chimie Minérale Appliquée (Amiens)

VAILLANT

Mathématiques Pures

VIDAL

Electronique, Electrotechnique et Automatique

Mme ZINN-JUSTIN

Mathématiques Pures

#### TABLE DES MATIERES

#### INTRODUCTION

# CHAPITRE I - LES ELEMENTS DE DEFINITION DE LA MEMOIRE CENTRALE

- A Capacité de la mémoire centrale et format technologique.

- B Format logique de l'information.

- Les informations à représenter.

- Longueur optimum de l'unité d'information.

# CHAPITRE II - ACCROISSEMENT DE LA VITESSE DE LA MEMOIRE : MEMOIRE PARTAGEE.

- A L'allongement des mots dans la mémoire.

- B Partage de la mémoire.

- C Evaluation du débit d'une mémoire partagée.

- D Organisation pratique d'une mémoire partagée.

- Commutation spaciale

- Commutation spacio-temporelle.

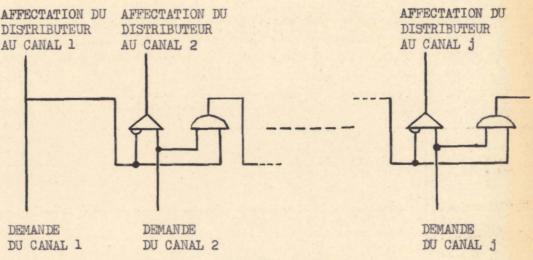

- E La mise en oeuvre des priorités.

# CHAPITRE III - COMPORTEMENT DE LA MEMOIRE EN PRESENCE DES CIRCUITS QUI L'EXPLOITENT.

Référence à des matériels existant ou en projet.

- A Occupation de la mémoire pour un taux donné de demandes.

- B Solution particulière dans le cas du régime stationnaire.

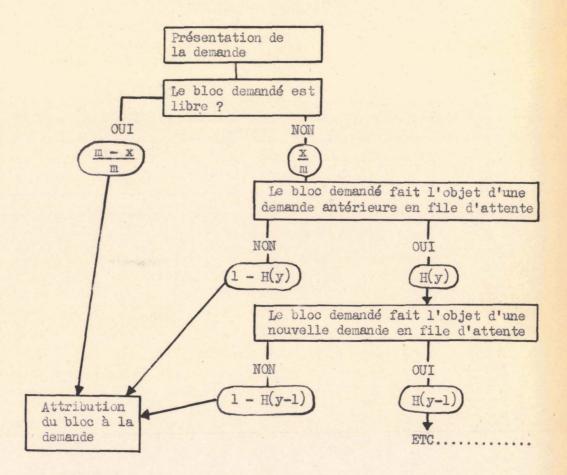

- C Emploi d'une file d'attente.

- D Occupation de la mémoire associée à une file d'attente.

- E Temps de service.

# CHAPITRE IV - COMPORTEMENT DE LA MEMOIRE EN REGIME TRANSITOIRE.

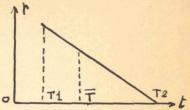

- A Calcul du comportement de la mémoire en régime transitoire.

- B Solution par l'emploi de variables discontinues.

- C Rôle de la file d'attente en régime transitoire.

- Cas de l'interruption de programme.

- Cas du branchement conditionnel

- D Temps perdu par le traitement.

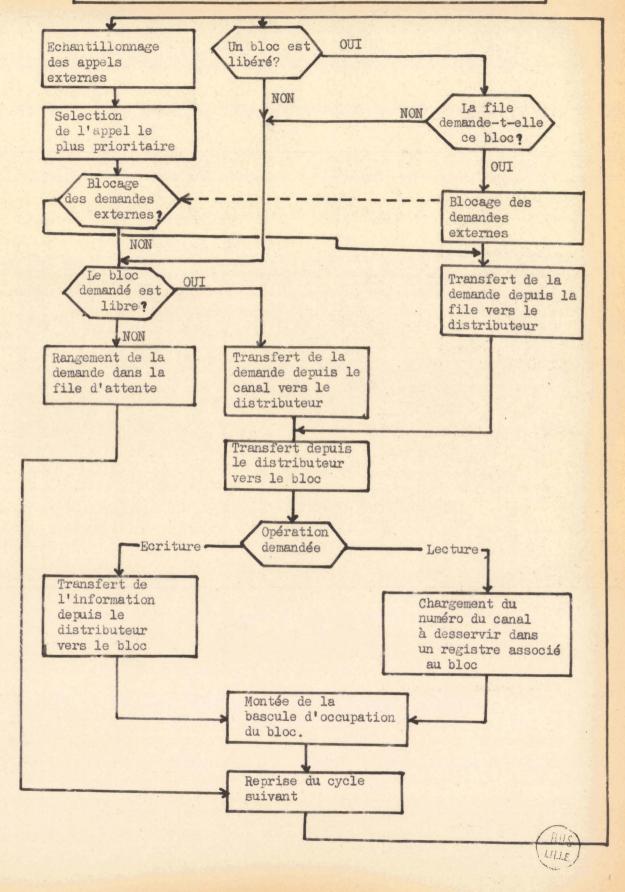

### CHAPITRE V - MODELE DE GESTION D'UNE MEMOIRE PARTAGEE.

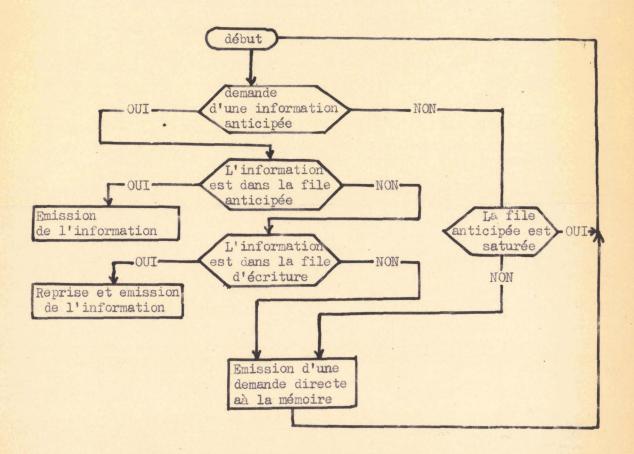

- A Principes d'une organisation de recherche anticipée.

- La file d'attente de données.

- La file d'attente d'instructions.

- La file d'attente d'écriture.

- B Optimisation de la recherche anticipée.

- Caractèristiques communes aux files d'attente.

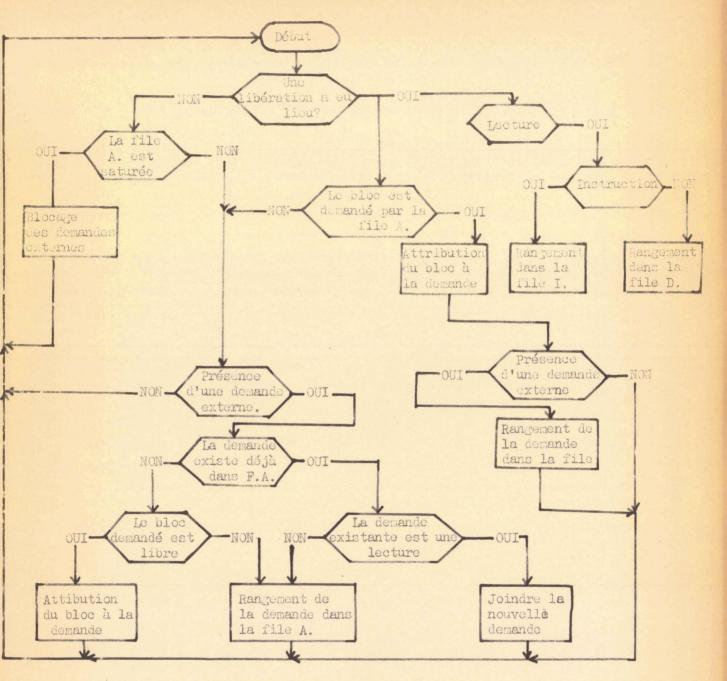

- Principe de l'organisation proposée.

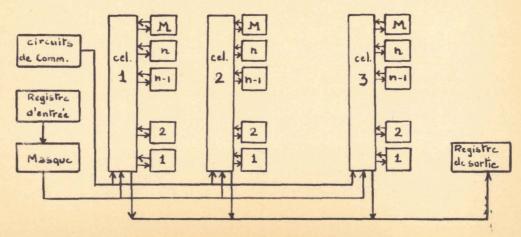

- La mémoire à logique distribuée.

- Chaine des cellules disponibles.

- Chaine des priorités.

- C Format des données traitées.

- D Séquences de traitement des demandes.

CONCLUBION.

BIBLIOGRAPHIE.

L'évolution technologique des systèmes de traitement de l'information se poursuit depuis quelques années dans deux directions complémentaires. Toutes deux visent à accroître la vitesse à laquelle les traitements peuvent être poursuivis. L'accroîssement de vitesse ne concerne pas seulement les unités centrales mais aussi et parallélement les moyens d'accés à la machine.

La première de ces deux directions est une tentative au niveau des composants élémentaires d'une machine que sont les circuits logiques et de stockage. On peut admettre facilement que le gain de vitesse d'un ensemble est proportionnel au gain réalisé sur les vitesses des composants, à condition, toutefois, que l'accroissement des performances élémentaires reste homogéne pour l'ensemble des circuits. Il semble que cette première direction soit, dans l'état actuel de la technologie, d'un intérêt limité en raison du coût lié à l'accroissement des performances et qui croit exponentiellement en fonction de la vitesse. Pour les circuits logiques, on situe autour d'une dizaine de nano-secondes, le temps de commutation qui permette de réaliser le meilleur compromis de prix à performances. On admet, de plus, que cet optimum ne variera guère dans les prochaines années, les efforts de recherche s'orientant plus vers l'intégration à grande échelle des circuits de traitement et de stockage que vers un gain de performances intrinséques de chacun d'eux.

La seconde direction permettant d'obtenir un gain en performances est la simultanéité des traitements. Il y a longtemps que les machines disposent du moyen de poursuivre simultanément le traitement interne et les échanges avec les organes périphériques. Il y a quelques années, la notion de simultanéité a été introduite dans l'unité centrale elle-même sous des formes diverses et plus ou moins efficaces. Ce qu'on appelle le multitraitement ne peut être l'apanage que d'ensembles importants ou trés spécialisés. L'évolution technologique citée plus haut va vraisemblablement permettre de doter des ensembles moyens, voire même modestes, de ces possibilités de traitements internes simultanés.

Les éléments de stockage et particulièrement la mémoire centrale qui se trouvent sollicités au début et à la fin de toute opération, doivent suivre une évolution comparable. Or un examen de l'évolution des circuits logiques d'une part, des circuits de stockage d'autre part, fait apparaître une différence de plus en plus marquée entre leurs vitesses relatives.

Cet état de fait se trouve aggravé par l'accroissement des tâches qui sont confiées à la mémoire. L'apparition des simultanéités, leur gestion, le multi-traitement et le volume croissant des programmes de contrôle et d'ordonancement interne exigent des capacités croissantes et des débits de mémoire de plus en plus élevés.

Le but de ce travail est d'étudier dans quelles conditions il est possible d'améliorer les performances globales d'un organe de stockage en faisant fonctionner en simultanéité plusieurs éléments indépendants. L'étude concerne surtout la mémoire centrale d'un ordinateur qui est la plus sollicitée et des manières les plus diverses. Il est certain, néammoins, à condition de changer l'échelle des temps, que presque tous les résultats pourraient s'appliquer à un groupe de mémoires externes pour définir, par exemple, les conditions d'exploitation d'un fichier de trés grandes dimensions.

Ce qui, cependant, particularise l'application à la mémoire centrale, c'est que les choix, les décisions et les réglements de conflits, inhérents à toute gestion simultannée, ne peuvent être pris en charge par le programme. La logique associée à un groupe de mémoires centrales fonctionnant en simultanéité doit être totalement cablée ce qui conduit cenduit à examiner en détail les diverses éventualités qui peuvent se présenter. Un modèle de gestion est proposé qui présente l'avantage d'une structure logique totalement unifiée. Ceci est rendu possible par l'emploi d'une mémoire supplémentaire de type associatif. Ses performances doivent être nettement supérieures à celles des unités qu'elle contrôle mais elle ne réclame, en contre-partie, qu'une capacité très limitée.

#### CHAPITRE I

#### LES ELEMENTS DE DEFINITION DE LA MEMOIRE CENTRALE.

#### INTRODUCTION

Pour deux raisons, la définition des caractèristiques d'un système de traitement de l'information doit commencer par celles de sa mémoire.

La première résulte de la position privilégiée de la mémoire au centre de tous les échanges et de tous les traitements entrepris par la machine. Le choix des caractèristiques de la mémoire fixe, de manière presque difinitive, une grande partie des caractèristiques globales de l'ensemble : Le format des données et des instructions, les possibilités d'adressage, les modes d'accès des organes périphériques.

La seconde raison est d'ordre technologique. Actuellement la fonction de stockage est, relativement à la fréquence de son emploi, la plus lente des fonctions internes d'une machine. De plus, depuis quelques années, l'éccart des vitesses relatives se creuse: En 1959, par exemple, la machine I.B.M. 704 disposait d'une mémoire à tores de ll micro-secondes de temps de cycle alors qu'il lui fallait 72 micro-secondes pour effectuer une addition; dans une machine récente du pême constructeur disposant d'une mémoire de 750 nano-secondes de temps de cycle, l'addition ne réclame plus que 120 nano-secondes. L'équilibre ne peut se rétablir que par une étude logique de la structure de la machine dans laquelle la mémoire sera, en premier lieu, favorisée.

Les éléments sur lesquels portent les choix à faire sont liés les uns aux autres; tous doivent être susceptibles d'une évaluation du rapport: performances à prix.

# A - CAPACITE DE LA MEMOIRE ET FORMAT TECHNOLOGIQUE.

La presque totalité des mémoires centrales qui équipent les ordinateurs actuels est représentée par des mémoires à tores magnétiques. L'évolution la plus prévisible se fera dans le sens d'un accroissement de la vitesse et de possibilités de lecture non destructive. La technologie qui, dans quelques années, a les plus grandes chances de supplanter les tores magnétiques est la mémoire à circuits actifs intégrés. L'organisation logique en sera identique.

Une mémoire est, en premier lieu, définie par sa capacité. Il est habituel de le faire en indiquant successivement le nombre de positions adressables et la longueur de chacune de ces positions. Si l'on suppose que la mémoire est utilisée au mieux, on exprimera plus simplement cette capacité par le nombre total de positions binaires dont elle dispose. Cette capacité C est le produit du nombre M de positions adressables par le nombre L de positions binaires des mots technologiques.

A priori, on cherchera à obtenir la capacité désirée avec un choix sur les valeurs de M et L tel que le prix unitaire de la cellule de mémoire soit le plus faible possible. Il faut ajouter comme élément du choix, la vitesse que l'on peut évaluer par le temps de cycle de la mémoire ou mieux, par le produit de ce temps de cycle par la longueur du mot traité.

L'obtention de la formule PRIX = F ( M, L, T ) permettrait de comparer avec précision les différentes solutions possibles.

Une telle tentative peut s'appuyer soit sur des considérations de prix de revient, soit sur les catalogues de prix fournis par les constructeurs. Ces deux approches sont complémentaires, la première pouvant fournir l'allure de la courbe représentative, la seconde fournissant la valeur réelle des coéfficients dans la détermination desquels entrent trop d'éléments partiels : prix des composants, temps d'assemblage, ammortissement du matériel de fabrication, présence des services commercianx et nécessité d'uniformiser et de rationaliser les prix.

# Estimation à partir des composants;

Toutes les mémoires à tores magnétiques comportent:

- L'empilage des plans de mémoire.

- Les circuits de sélection d'adresses.

- Les gémerateurs de courants pour la lecture, l'écriture et qui commandent les fils de sélection.

- Les circuits de lecture et d'inhibition.

- Les alimentations et les circuits annexes.

- Les circuits de rythme et les liaisons avec l'extérieur.

La loi la plus simple à déterminer est celle qui relie le prix à la longueur du mot, la vitesse et le nombre de mots restant constant. Le nombre de plans et de circuit de lecture et d'inhibition est égal à la longueur du mot. Les autres circuits sont pratiquement indépendants de cette longueur.

# Estimation directe à partir des prix de vente;

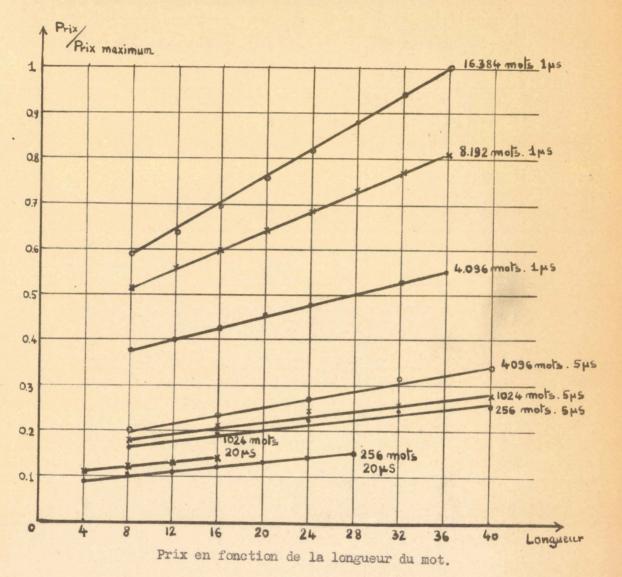

On doit donc trouver une loi de la forme : P = P + k.L

Les courbes ci-dessous montrent que cette loi correspond bien à la réalité.

La loi qui permet d'évaluer le prix en fonction du nombre de mots adressables de la mémoire est plus complexe car, selon la technologie employée et

la rapidité désirée, les solutions sont très diverses. Lorsque le nombre de

mots passe de n à 4 n, le nombre de lignes de commande est doublé. En pratique,

l'emploi de transformateurs de courants commandés par plusieurs primaires, de

circuits d'aiguillage ou de regroupement à diodes, la division d'un plan de

mémoire en deux ou quatre sous-groupes afin de conserver un bon rapport signal

à bruit, font que cette estimation n'est qu'approximative.

Il faut, de plus remarquer que la variation ne peut être continue comme pour la longueur des mots. Il s'agit ordinairement d'une loi géométrique de raison 2 et dans un intervalle relativement restreint (1.024 à 32.768 mots).

Si on pose cependant que le prix doit être de la forme :

$$P = P_0^i + k^i \sqrt{M}$$

On obtient un résultat qui ne concorde que d'assez loin avec les valeurs réellement proposées.

} L = 64 bits L= 32 bits 3.4 3.0 L = 16 bits 2,6 L = 16 bits 9.2 1.8 145 1.4 245 1.0 2.048 4.096 8.192 16.384 32.568

Mémoires rapides de capacité moyenne

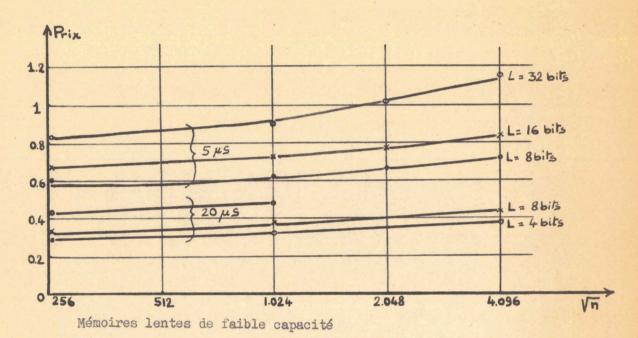

Il est possible d'extraire de ces deux courbes déterminant le prix en fonction de la longueur et du prix en fonction du nombre des mots, un résultat plus concret en prenant comme paramètres la vitesse et la capacité exprimée par la quantité de positions binaires contenues dans la mémoire.

Pour une capacité donnée, la variable sera par exemple, la longueur du mot et la fonction le prix de la position binaire.

Pour des mémoires ne comportant qu'un petit nombre de mots, la nécessité de disposer d'alimentations, de circuits de dythmes dont le coût est à peu près indépendant de la capacité de la mémoire, doit faire apparaître l'intérêt d'allonger les mots.

Pour des mémoires de capacité plus importante, le coût de ces éléments devient proportionnellement plus faible. Comme le prix croit linéairement avec la longueur des mots mais simplement comme la racine carrée de leur nombre, il doit exister une capacité pour laquelle il y a exactement compensation.

Au delà de cette capacité, l'accroissement de la capacité sera plus avantageusement obtenu par une augmentation du nombre des mots.

La courbe ci-dessous fait effectivement apparaître ce fait. Elle ne peut cependant constituer seule, un premier stade indépendant des choix à opérer car elle ne représente que les éléments statiques du stockage. Les caractéristiques dynamiques de ce stockage sont directement liées à la longueur du mot.

# B - FORMAT LOGIQUE DE L'INFORMATION.

Le support physique de l'information est presqu'universellement binaire. Cette propriété, imposée par la technologie, se prète, du reste, parfaitement au traitement automatique car elle ne laisse, à chaque instant et pour chaque information élémentaire, que l'alternative entre deux solutions. Une technologie capable de présenter plus de deux états serait certainement plus riche mais il n'est pas certain que les moyens théoriques actuellement disponibles permettent d'exploiter au mieux cette richesse.

Il existe une autre raison de choisir le binaire: Etant donné qu'en un endroit d'une machine doit prendre place une information pouvant présenter N valeurs différentes, le code binaire conduit à une redondance moyenne minimale et donc à la structure la plus économique.

Pour comparer deux sytèmes, il faut le faire sur la même valeur maximum de N: Pour comparer les systèmes à base 2 et 10, on a pris 1.024 et 1.000. Pour comparer les systèmes à base 2 et 3 on a pris 2.048 et 2.187.

Lorsque N varie de manière continue de 0 à la valeur maximum on trouve pour les trois systèmes, les redondances moyennes suivantes:

- Système à base 2 : 1,35

- Système à base 3 : 1,50

- Système à base 10: 1,82

En pratique, cet avantage du binaire est un peu illusoire de ce point de vue car la distribution des valeurs de N est loin d'être régulière et continue; d'autre part il n'est pas toujours possible d'exploiter pratiquement l'avantage théorique invoqué: La longueur des mots ne sera pas la longueur exactement utile mais un multiple entier d'une longueur de base ce qui accroit la redondance; la longueur de certains mots peut varier au cours du traitement et la longueur retenue en sera la valeur maximum.

On doit enfin remarquer que dans les algorithmes soumis au machines, le raisonnement s'appuie sur des choix entre deux solutions à partir de la présence ou de l'absence d'une condition unique. Il est rare que le nombre des issues soit supérieur à deux et il s'agit alors de cas particuliers provenant plus de la nature propre du problème que de principes généraux. Le binaire facilite ainsi la conception et surtout l'emploi des machines. On retrouve aussi un critère économique puisque tout aiguillage complexes peut se décrire comme un enchaînement de dichotomies successives.

# a) Les informations à représenter.

Une analyse faite par les logiciens d'IBM à propos de la machine STRETCH conduisait à distinguer cinq familles de données en fonction de leur taille, leur codage et leur emploi (1):

- Les quantités numériques exprimées en virgule fixe.

- Les adresses qui représentent un cas particulier de nombre en virgule fixe mais avec un format réduit.

- Les quantités numériques exprimées en virgule flottante.

- Les mots logiques tels que les codes d'opération, les masques et les mots chargés de décrire l'état de la machine et l'évolution du traitement en cours.

- Les informations dites d'édition qui se présentent comme des suites de caractères de longueur quelconque. Ces informations représentent les données qui apparaissent dans les échanges entre l'unité centrale et les organes d'accès.

Une information peut faire l'objet de traductions qui, en lui conservant son sens, la font passer d'une famille à une autre. C'est ainsi qu'un nombre est présenté au début du traitement comme une suite de caractères puis se trouve transformé en une expression binaire en virgule flottante ou en virgule fixe pour être enfin reconvertie en une suite de caractères avant d'être éditée.

On pourrait imaginer d'accroître encore la variété des informations que peut gérer la machine en faisant figurer les nombres en précision multiple, les nombres complexes et, par exemple, les listes et les tableaux.

Pour que ces différents modes d'expression soient acceptés par la mémoire, donc dans le format fixe et unique imposé par la technologie et d'autre part par les circuits spécialisés, le logicien ne peut que découper un mot de mémoire ou, au contraire, en grouper plusieurs selon ses besoins. La tendance actuelle qui favorise le traitement en parallèle pour des question de rapidité, provoque un alongement des mots technologiques afin de permettre à la mémoire de fournir, en un seul cycle, les informations les plus volumineuses qu'elle puisse contenir.

L'accroissement du débit de la mémoire obtenu par des mots technologiques longs conduit à un diminution du rendement de l'élément de stockage, les informations les plus courtes n'occupant qu'une fraction de la place qui est mise à leur disposition. Le taux d'occupation utile de la mémoire sera donc plus faible.

Pour concilier la bonne occupation de la mémoire avec son débit, il faut employer des formats variables, obtenus par regroupement mais surtout par découpage du mot technologique en essayant d'organiser le stockage pour que les informations extraites de la mémoire soient toutes utiles.

Le metilleur emploi d'une zone de mémoire exigerait que chaque mot se voit attribuer le nombre exact de bits dont il a besoin. Si L représente la longueur maximum, les longueurs des différents formats seront des sous-multiples de L. Une information sera adressée par l'indication du mot technologique qui la contient, sa position dans ce mot et sa longueur. Le bénéfice obtenu ainsi dans la zone de stockage des données exige, en contre-partie, une augmentation de capacité dans la zone de définition, zone qui contient les adresses. Ainsi, par exemple, dans une mémoire de 1024 mots technologiques, chaque mot étant formé de 64 bits, il existe 65.536 positions binaires. Une adresse capable de désigner une position comporterait 16 bits. Si la longueur peut étre comprise en 1 et 64 bits, il faut ajouter à l'adresse de la position initiale, une partie "longueur" qui réclamera 6 bits. Au total, la définition d'un mot exigera 22bits alors que la définition des mots technologiques de la mémoire n'en réclame que 10. Il faut donc trouver une solution de compromis pour laquelle on cherchera une optimisation simultannée de la zone des données et de la zone des adresses.

# b) Recherche de la longueur optimum de l'unité d'information.

L'adressage se faisant en binaire, la découpe des mots technologiques doit, elle aussi, se faire selon cette numération de manière à établir une continuité entre les positions successives, condition indispensable à l'emploi du calcul d'adresses et de l'indexation. C'est aussi la seule méthode pour exprimer, sans redondance, la longueur du mot.

La place occupée par une information se compose de la zone qui lui est allouée pour le stockage arondie à un multiple entier de la longueur de base et de la zone qui sert à la définition de son emplacement; cette seconde zone se trouve le plus souvent dans la partie réservée au programme.

On appelle  $L_1$  le nombre de bits utilisés pour le stockage,  $L_2$  le nombre de bits nécessaires à l'adressage et  $L_0$  la longueur de l'information de base. Tout mot enregistré dans la mémoire sera astreint à occuper un nombre de positions binaires qui soit un multiple de  $L_0$ .

On suppose que la distribution des longueurs est uniforme ce qui permet d'évaluer facilement la perte de place correspondant à un choix donné de Lo.

Si on prend la mémoire de 1.024 mots de 64 bits déjà citée plus haut en exemple, on suppose que la plus grande information qu'il soit possible de définir comporte effectivement 64 bits. Pour les longueurs L<sub>0</sub> comprises entre 1 et 64, on peut chiffrer la place totale nécessaire en mémoire pour stocker une information :

| Valeur<br>de Lo | Définition de<br>l'adresse initiale | Définition de<br>la longueur | Perte moyenne<br>de place par mot |           |

|-----------------|-------------------------------------|------------------------------|-----------------------------------|-----------|

| l bit           | 16 bits                             | 6 bits                       | 0 bit                             | 22 bits   |

| 2 bits          | 15 bits                             | 5 bits                       | 0,5 bit                           | 20,5 bits |

| 4 bits          | 14 bits                             | 4 bits                       | 1,5 bits                          | 19,5 bits |

| 8 bits          | 13 bits                             | 3 bits                       | 3,5 bits                          | 19,5 bits |

| 16 bits         | 12 bits                             | 2 bits                       | 7,5 bits                          | 21,5 bits |

| 32 bits         | ll bits                             | l bit                        | 15,6 bits                         | 27,5 bits |

| 64 bits         | 10 bits                             | 0 bit                        | 31,5 bits                         | 41,5 bits |

Le minimum se situe donc entre les valeurs de L<sub>O</sub> de 4 et 8 bits. Si on prend comme unité indivisible d'information, un groupe de 4 ou 8 bits, tout mot pris en charge par la mémoire sera un multiple entier de l'une de ces deux quantités. On choisira de préférence la longueur de 8 bits pour deux raisons: La logique sera sensiblement plus simple dans ce cas puisque le découpage est moins poussé. Par ailleurs, la bonne exploitation de ces possibilités suppose que le programmeur ou le système de programmation soient capables de déterminer la longueur nécessaire pour chaque information; le travail de l'un et la complexité de l'autre seront réduits dans la mesure où l'analyse du format nécessaire à cette information ne requiert qu'une précision moindre.

On retrouve, par ce raisonnement l'octet, introduit il y a quelques années bien que les principales raisons invoquées, à cette époque, en sa faveur aient été d'un autre ordre.

Le raisonnement ne tient pas compte de la répartition des longueurs qui ont été implicitement supposées étre toutes équiprobables. En pratique, la probabilité d'apparition des différentes longueurs est très variable. Il faut alors tenir compte de la place réclamée par chaque information en pondérant le résultat par la probabilité de rencontrer cette information.

On a repris le calcul précédent en considérant deux lois de distribution empruntées à une enquête faite par la revue CONTROL ENGINEERING, l'une pour les application scientifiques, l'autre pour la gestion.

Applications de gestion - Répartition des longueurs.

Mot ..... soupiramm serétasas : atid 4 eb eteM -

- Mots de longueur comprise entre 4 et 8 bits... 30%

- Mots de longueur comprise entre 8 et 16 bits.. 20%

- Mots de longueur comprise entre 16 et 32 bits. 15%

- Mots de longueur comprise entre 32 et 64 bits., 5%

Sur un total de 1.000 mots, en supposant que la répartition dans chaque tranche est uniforme, on trouve les occupations suivantes pour le stockage:

| _     |       |       | the same of the sa | and the second | -     | -     |                                    |

|-------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------|-------|------------------------------------|

| 84487 | 89277 | 33175 | 30144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 09T0£          | 37468 | 33755 | JATOT                              |

| T0000 | 72000 | 74000 | 0009T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0008T          | 50000 | SS000 | Sone correspondante<br>d'adressage |

| 70    | 75    | . ÞI  | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38             | SO    | 55    | Longueur de la<br>partie adresse   |

| 8402  | 8402  | 1792  | 7991                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 009T           | 89ST  | 7225  | 32-64 bits                         |

| TOSTO | SESO  | SISO  | 0877                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0917           | 0007  | 3920  | 16-32 bits                         |

| 72800 | 0019  | 3200  | 2500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2800           | 5600  | 5200  | 8-16 bits                          |

| 19200 | 0096  | 0087  | 2400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2400           | STOO  | 096T  | stid 8-4                           |

| 19200 | 0096  | 0087  | 2400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1200           | 7500  | 1200  | stida                              |

| 19    | 35    | 91    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>*</b>       | 2     | t     | Tranche<br>Tranche<br>de longueur  |

Dans la mesure où les hypothèses faites sur la distribution des longueure sont assez proches de la réalité, on retrouve les conclusions précédentes : La longueur de l'information unitaire doit étre de 2, 4 ou 8 bits.

Application acientifique - Répartition des longueurs. - Mots de 4 bits : caractères numériques - Mots de 4 bits : caractères numériques

cours des calculs.

- Mots de longueur comprise entre 4 et 8 bits.... 5%

- Mots de longueur comprise entre 8 et 16 bits... 15%

- Mots de longueur comprise entre 16 et 32 bits... 45%

- Mots de longueur comprise entre 32 et 64 bits

Il semblerait utile d'introduire une tranche supplémentaire entre 32 et 48 bits, la longueur correspondante se prêtant bien à la représentation des nombres en virgule flottante en simple précision c'est à dire avec de 7 à 9 chiffres de mantisse. Il semble que les auteurs aient reporté cette catégorie d'informations dans la tranche comprise entre 16 et 32 bits ce qui est un minimum compte tenu des arreurs d'arondi qui se propagent au qui est un minimum compte tenu des arreurs d'arondi qui se propagent au

| En prenant les mêmes bases de calcul, on peut | établir | blir le | tableau | suivant: |

|-----------------------------------------------|---------|---------|---------|----------|

|-----------------------------------------------|---------|---------|---------|----------|

| Valeur de Lo                       | 1     | 2     | 4     | 8     | 16    | 32    | 64    |

|------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Tranche de<br>longueur             |       |       |       |       |       |       |       |

| 4 bits                             | 400   | 400   | 400   | 800   | 1600  | 3200  | 6400  |

| 4 - 8 bits                         | 325   | 350   | 400   | 400   | 800   | 1600  | 3200  |

| 8 -16 bits                         | 1875  | 1950  | 2100  | 2400  | 2400  | 4800  | 9600  |

| 16-32 bits                         | 11025 | 11250 | 11700 | 12600 | 14400 | 14400 | 28800 |

| 32-64 bits                         | 12125 | 12250 | 12500 | 13000 | 14000 | 16000 | 16000 |

| Longueur de la partie adresse      | 22    | 20    | 18    | 16    | 14    | 12    | 10    |

| Zone correspondante<br>d'adressage | 22000 | 20000 | 18000 | 16000 | 14000 | 12000 | 10000 |

| TOTAL                              | 47750 | 46200 | 45100 | 45200 | 47200 | 52000 | 74000 |

On trouve encore un optimum pour L<sub>0</sub> égal à 4 ou 8. On remarque cependant que la variation relative du nombre de bits nécessaires lorsque l'on s'éloigne de ces valeurs, est plus faible que dans le cas précédent. Il est possible, en particulier, de prendre une valeur de 16 bits ce qui n'apporte pas de pertes importantes de capacité tout en apportant une simplification aux circuits de décodage d'adresses.

Deux facteurs qu'il est difficile de chiffrer peuvent modifier les résultats obtenus. Ils agissent tous deux dans le même sens de telle sorte que la longueur la plus économique peut s'en trouver modifiée.

Le premier provient de la nécessité de conserver à une information, un format suffisant au cours de toutes les opérations qu'elle subira au cours du traitement; Les réajustements de longueur sont très difficles à entreprendre en cours de calcul et faisant perdre du temps. Si le programmeur ou le système de programmation affectent à une donnée, au début du traitement, la longueur qui lui convient exactement, elle risque, par la suite de provoquer un dépassement de capacité. Ce dépassement est d'autant plus génant que la zons qui fait suite à la zone allouée à l'information peut être occupée. Chaque dépassement provoque un appel du programme superviseur qui devra décaler une partie importante des informations stockées ou allouer une nouvelle zone à l'information. Dans les deux cas, ce dépassement de capacité va provoquer une perte de temps telle qu'il est préférable de l'éviter en affectant systèmatiquement à une information, une place supérieure à celle qu'elle réclame effectivement.

Le vocate autour provient du fait que toutes les positions contenant des informations ne cont par necessairement définies par une adresse individuelle dans la zone de désignation. L'adressage indirect, l'emploi de registres d'index qui permettent à l'aide d'une seule adresse explicite, d'accéder à un grand nombre d'informations disposées régulièrement dans la mémoire, permettent une réduction de la dimension de la zone de mémoire affectée à la désignation des informations.

Le premier point conduit à accroître les dimensions de la zone de stockage tandis que le second permet la réduction de la zone de désignation. Il s'en suit un déplacement de la longueur optimale vers des valeurs plus élevées.

En conclusion, une longueur de 8 bits, pour l'information la plus élémentaire, répond le mieux au critère d'occupation posé. Si cemendant on admet qu'il est nécessaire d'ajouter de 10 à 20% de bits supplémentaires à chaque information et que 20 à 30% des adresses effectives ne sont pas explicitées dans la zone de désignation, il est alors plus normal de prendre une longueur de 16 bits. On a considéré comme obligatoire de subdiviser le mot technologique en termes élémentaires dont le nombre soit une puissance de deux afin que , l'adressage étant fait en binaire, le calcul d'adresses conduise toujours à un nombre formé de deux parties indépendantes : le code de désignation du mot technologique d'une part et le code de désignation de la position et de la longueur d'autre part. Il n'est cependant pas nécessaire que la longueur de l'information de base soit une puissance de deux. La discussion entreprise n'a considéré que ces puissances de deux mais elle a permis de constater que la variation de la place occupée en mémoire pour Lo variant de 1 à 16 ne dépasse pas 10% dans le cas le plus défavorable. Si pour des raisons particulières, le choix d'une longueur de base qui ne soit pas une puissance de deux s'imposait, on serait assuré. dans la limite des bornes indiquées, de ne pas s'éloigner beaucoup de l'optimum.

#### CHAPITRE I I

ACCROISSEMENT DE LA VITESSE DE LA MEMOIRE : MEMOIRE PARTAGEE .

#### INTRODUCTION

Dans presque toutes les machines actuelles, les performances de l'unité de traitement sont étroitement liées à celles de la mémoire. Cette situation résulte du fait que les vitesses des éléments logiques ont progressé plus rapidement que celles des éléments de stockage. La différence est accentuée per le fait que la charge des organes de stockage s'accroit en raison:

- De la généralisation des interruptions de programme.

- De l'emploi systèmatique des langages symboliques qui conduisent à des programmes en langage machine plus lourds et imposent pour un même travail, un nombre plus élevé de consultations de la mémoire.

- Des systèmes de programmation Moniteurs et superviseurs qui peuvent occuper près de 30% du temps de la machine et plus de la moitié de la capacité de la mémoire.

La gestion des interruptions comme celle des canaux d'entrées-sorties de même que les compilateurs et les divers programmes du système se caractèrisent par le fait qu'ils n'emploient que des instructions très élémentaires mais font un grand emploi de la mémoire.

Devant cet état de choses, deux tendances se manifestent; leurs buts sont identiques bien qu'elles ne concernent pas les mêmes classes de matériels: Il s'agit toujours d'aligner les possibilités de la mémoire centrale sur celles de la logique de traitement.

- a) A partir du temps de cycle de la mémoire, considéré comme donnée initiale, on réalise une machine avec une technologie lente ce qui en réduit le prix. On trouve, par exemple, des machines dans lesquelles le stockage se fait en parallèle et le traitement en série. Une telle option ne concerne que des machines de performances faibles ou moyennes.

- b) En conservant au temps de cycle technologique des valeurs usuelles, il est possible d'accroitre le débit de l'information soit en allongeant les mots stockés soit en faisant travailler en simultanéité plusieurs blocs de mémoire c'est à dire en partageant la mémoire centrale.

En pratique, les performances et les circuits cablés correspondant à ces solutions ne se situent pas au même niveau. L'allongement des mots de la mémoire n'est pas un phènomème récent mais plutôt une évolution progressive suivant les progrès technologiques et la demande du marché pour des systèmes de plus en plus puissants. Le partage de la mémoire, au contraire, représente une modification brutale par rapport aux solutions précédentes et ne peut être envisagé que pour des systèmes de grosse puissance, actuellement du moins.

# A - L'ALLONGEMENT DES MOTS DANS LA MEMOIRE.

On peut évaluer le débit d'une mémoire par le nombre d'informations binaires qui peuvent être pris en charge par une opération de lecture eu d'écriture pendant l'unité de temps. Selon cette définition, le débit est inversement

proportionnel au temps de cycle de la mémoire mais il est aussi proportionnel

à la longueur du mot technologique. Lorsque l'information traitée est de longueur variable, une distinction est nécessaire entre le débit utile de la

mémoire correspondant aux seules informations traitées et le débit réel défini

plus haut.

Dans les machines à mots de performances moyennes, le mot de mémoire correspond au mot des registres de traitement. A toute opération de lecture ou d'écriture correspond l'échange d'une information totalement utile. D'ordinaire, cette information constitue un tout pour laquel un seul cycle de mémoire est nécessaire.

Dans les machines à caractères, il faut plusieurs cycles de mémoire pour permettre l'échange d'une information complète. Pour cette raison, la mémoire à caractères est réservée aux petits systèmes. L'évolution entre les machines 1400 et les machines de la série 360 de I.B.M., par exemple, est marquée, entre autres choses, par le fait que la correspondance entre les adresses et les positions physiques de la mémoire ne s'établit pas du tout de la même manière. Dans les machines de la série 1400, les circuits de sélection, commandés par les poids faibles de l'adresse, sélectionnaient un mot de la mémoire. Ce mot pouvait comporter 8, 16 ou 32 bits. Le dernier chiffre de poids fort de l'adresse permettait alors la sélection d'un groupe unique de 8 bits dans le registre de sortie de la mémoire. Une telle solution, par le fait que deux caractères successifs étaient placés dans deux mots nécessairement différents ne permettait pas d'augmenter le débit. Dans les machines de la série 360, ce sont les poids forts qui désignent le mot technologique et les poids faibles qui désignent la position dans le mot. De la sorte, deux caractères d'adresses successives peuvent apparaitre dans le même cycle de lecture et le débit de la mémoire, à performances identiques, s'en trouve augmenté.

Suivant la même évolution que les machines à caractères, les machines à mots voient la longueur des formats technologiques augmenter en même temps que leur puissance de traitement.

Bien qu'il soit un peu prématuré de préjuger de l'accroissement de performances qu'apporte l'allongement du format des mots stockés, les formats étant très diversifiés selon la nature de l'information enregistrée, on peut essayer de chiffrer le bénéfice qui résulte du groupement d'informations indépendantes à l'intérieur d'un même mot technologique.

Il est utile d'extraire de la mémoire, en un même cycle, deux ou plusieurs informations indépendantes lorsque ces informations doivent faire l'objet d'un traitement séquentiel.

Parmi les informations séquentielles issues de la mémoire, on trouve en premier lieu, les programmes. Il peut s'agir aussi bien de programmes exprimés en langage source que de programmes en langage machine. La seule différence porte sur la longueur des groupes binaires correspondants. Une statistique faite sur un groupe de programmes écrits en langage machine pour l'ordinateur de l'ISEN fait apparaître la proportion suivante de ruptures de séquences:

- Pour les programmes traduits par le compilateur, une instruction de saut pour 12 instructions.

- Pour le compilateur, une instruction de saut pour 8 instructions.

Dans une proportion approximative de 90 à 95% les programmes écrits en langage machine sont séquentiels. Les langages symboliques, sont, quant à eux, lus de manière presque exclusivement séquentielle. Leur traitement ne l'est pas pour autant puisque l'analyse de chaque caractère peut conduire à de nombreuses opérations de recherche, de rangement, de branchements et d'identification imbriquées les unes dans les autres par des instructions de sauts. L'analyse des programmes symboliques ne trouve son intèret dans l'allongement des mots de mémoire que si les instructions d'analyse de ces programmes sont très évoluées. C'est le cas de la machine B 5500 de BURROUGHS qui permet l'analyse de huit caractères contenus dans une position de mémoire en les appelant en séquence à la suite d'une seule opération de lecture. Il s'agit cependant d'un cas relativement exceptionnel. (2)

Une seconde catégorie d'informations traitées dans l'ordre où elles figurent dans la mémoire sont celles qui font l'objet d'opérations d'entréessorties.

Il arrive, enfin, surtout dans les travaux de gestion qu'une partie des données traitées soient disposées dans la mémoire dans l'ordre où elles ont à apparaître.

Pour la recherche du programme, le nombre d'instructions que l'on peut faire figurer dans un mot de mémoire est compris entre l et 8. Le format d'une instruction peut varier entre 8 et 32 bits. Le premier cas représente une instruction sans adresse; le second autorise une forme très complète d'instruction avec une partie adresse importante et de nombreuses information complémentaires telles que l'indication d'un accumulateur, d'un registre d'index et d'un adressage indirect. Par ailleurs, la longueur du mot technologique ne peut guère dépasser une centaine de bits. Comme on a intérêt à diviser ce mot en groupes distincts, par une puissance de 2, il sera pratiquement possible de loger 1, 2, 4 ou, au plus 8 instructions par mot.

En admettant que la proportion des consultations de la mémoire réservées à la recherche du programme se situe aux environs de 25 à 30%, on peut chiffrer le gain de temps résultant du groupement d'instructions. Si on prend comme longueur moyenne d'une séquence sans branchement, la valeur de 10 instructions, on trouve:

- -Pour deux instructions par mot, un gain de 4,5 cycles pour 30 cycles soit: 15%.

- -Pour quatre instructions par mot, un gain de 6,75 cycles pour 30 cycles soit: 22;5%.

- -Pour huit instructions par mot, un gain de 7,25 cycles pour 30 cycles soit: 24%.

Ce gain de temps est obtenu au prix d'un effort technologique acceptable: Il suffit, dans le premier cas, par exemple de dédoubler le registre d'ordres et de valider l'une ou l'autre des deux parties par un sélecteur à bascule.

Une solution de ce genre, adoptée sur la machine B 5500 permet le chargement simultané de quatre instructions; le format réduit des instructions de cette machine favorise une telle option.

Il est plus difficile d'évaluer au niveau des données, l'avantage que l'on peut retirer du groupement de plusieurs informations indépendantes à l'intérieur d'un seul mot de mémoire. Si ces informations font effectivement l'objet d'un traitement séquentiel, le bénéfice est du même ordre de grandeur que pour le programme. C'est le cas des listes, de tableaux, des piles et des suites de caractères, groupement que l'on rencontre assez souvent pour que se justifie certaines options technologiques basées sur le principe invoqué.

Le caractère séquentiel des informations traitées a semblé suffisament fréquent pour que, dans la machine de l'ISEN, il apparaisse un indicateur d'adressage séquentiel qui permet de supprimer la partie adresse de l'instruction soit, en moyenne quatre caractères.

#### B - PARTAGE DE LA MEMOIRE.

Une autre solution qui commence à se faire jour dans les ensembles importants, consiste à multiplier les blocs de mémoire en leur conférant la possibilité de fonctionner en simultanéité. Si, pour une technologie donnée, une mémoire unique peut atteindre un débit donné, plusieurs mémoires fonctionnant simultanément auront un débit incontestablement supérieur. Le gain réalisé est lié au nombre de blocs indépendants et à la gestion de leur simultanéité.

L'Adressage dans les blocs. En supposant que la mémoire, constituée de blocs indépendants, est entièrement adressable, une partie de l'adresse servira à définir le numéro du bloc tandis que l'autre partie définira la position dans le bloc. L'emploi obligatoire des méthodes de calcul d'adresses impose que ces deux parties soient exprimées dans un système de numération unique de telle sorte que toute indexation des adresses permette le chevauchement sur plusieurs blocs sans solution de continuité.

On peut alors se demander s'il faut affecter les poids forts ou les poids faibles de l'adresse à la définition des blocs. En d'autres termes, il s'agit de savoir si le balayage en séquence des adresses explorera la totalité d'un bloc avant de passer au suivant ou si, au contraire, il prendra une position successivement dans chacun des blocs.

Dans le cas où le bloc est défini par les poids forts de l'adresse, en supposant que chacun des utilisateurs travaille dans une zone de positions voisines les unes des autres, on spécialise, pour des séquences longues, chaque bloc en l'attribuant à un ou plusieurs demandeurs. Dans le cas, par exemple, de quatre blocs pouvant être mis à la disposition de quatre canaux demandeurs, on peut imaginer que chaque bloc travaille, pour un travail donné, avec l'un des canaux. Les blocs sont de capacité identique mais les besoins des canaux sont très différents de telle sorte que:

- Ou bien on assigne rigidement un bloc à un canal, tous les blocs ayant une capacité suffisante pour absorber le volume d'informations le plus élevé. On exploite alors très mal la capacité de la mémoire. Une structure de ce type existe dans la machine SABRAC (3) où deux blocs indépendants fonctionnent en simultanéité, l'un connecté à l'unité de traitement, l'autre connecté à une mémoire externe à tambour. Les connexions sont assurées par une bascule. Il ne semble pas que cette organisation ait eu un grand succès en raison de son manque de souplesse et des difficultés de programmation qu'elle entraine.

- Ou bien on autorise le chevauchement sur plusieurs blocs mais il arrive alors que pendant de longues périodes, deux canaux exploitent le même bloc tandis que d'autres blocs seront au repos. Les performances diminuent donc. Par ailleurs, le jeu des priorités entre les demandes issues des divers canaux risque de couper complètement l'accès à la mémoire au canal qui ne dispose que de la priorité la plus faible.

Si ce sont les poids faibles de l'adresse qui définissent le bloc sélectionné, l'attribution des blocs à un demandeur travaillant sur des adresses voisines se fera de manière totalement aléatoire et les conflits de priorité n'auront qu'un caractère très fugitif. Il se peut même que, sous certaines conditions, les circuits de priorité soient totalement supprimés et remplacés par un simple chainage des demandes et un verrouillage des blocs au travail. Cette seconde solution semble donc préférable. C'est celle qui a été adoptée dans la machine CDC 6600 de CONTROL DATA, sans que de leur propre aveu, les logiciens aient été capables de chiffrer exactement le bénefice obtenu.

# C - EVALUATION DU DEBIT D'UNE MEMOIRE PARTAGEE.

Puisque l'attribution des blocs aux canaux demandeurs est aléatoire, l'évaluation du débit ne peut être que statistique. Cependant on préfère évaluer maintemant les performances d'une machine sur un long traitement que sur les temps d'exécution d'opérations élémentaires de telle sorte que la définition statistique du débit est aussi significative que celle du temps de cycle d'une mémoire centrale classique.

Soit une mémoire partagée en m blocs simultannés ayant même capacité et même temps de cycle T. Ces mémoires desservent n canaux demandeurs. On suppose que:

- Chaque canal dispose d'une voie de lecture et d'une voie d'écriture qui peuvent être satisfaites ensemble ou séparément sur un cycle complet du bloc concerné.

- Chaque canal dispose de plus, d'une voie adresse qui précise la position concernée.

- Les probabilités d'appel de tous les canaux sont du même ordre. Si certains canaux pouvaient se contenter de débits très inférieurs à ceux des autres, ils peuvent être groupés sur une seule voie d'accès à la mémoire.

On peut supposer, pour faciliter le calcul, que toutes les mémoires sont exactement synchrones et que l'ensemble des demandes qui apparaissent pendant un temps de cycle sont regroupées au début du cycle. Il est impossible, dans cette hypothèse, de déterminer le temps d'accès à la mémoire mais l'évaluation du débit n'est pas modifiée. Le nombre de demandes qui se présentent pendant le temps T n'est pas nécessairement égal au nombre de canaux. Il se peut qu'un canal présente plusieurs demandes tandis qu'un autre n'en présente, en moyenne, qu'une fraction.

Lorsqu'un cycle vient de se terminer, tous les blocs sont libres. Les demandes sont alors examinées dans l'ordre des priorités décroissantes. Soient Dl, D2, D3, ..... Dp, ces demandes.

- Dl a une probabilité 1 d'étre satisfaite.

- La demande D2 dispose de m 1 blocs et la probabilité de voir D2 satisfaite est:

$$P_2 = \frac{m-1}{m}$$

- La demande D3 aura la probabilité  $P'_3 = \frac{m-2}{m}$  d'étre satisfaite si D2 a été satisfaite. Dans le cas contraire, D3 aura la probabilité de satisfaction  $P'_3' = \frac{m-1}{m}$

$$P_{3} = P'_{3} \cdot P_{2} + P'_{3} \cdot (1 - P_{2})$$

$$P_{3} = \frac{m:-2}{m} \cdot \frac{m-1}{m} + \frac{1}{m} \cdot \frac{m-1}{m}$$

$$P_{3} = (\frac{m-1}{m})^{2}$$

- On trouve que la probabilité de satisfaction de la demande D4 est de la forme:

$P4 = \left(\frac{m-1}{m}\right)^3$

La loi de formation des probabilités successives est récurrente et la probabilité de satisfaction de la demande i s'obtient à partir de la probabilité de satisfaction de la demande d'ordre (i-1):

$$P_{i-1} = (\frac{m-1}{m})^{i-2}$$

- La probabilité P<sub>i</sub> est la somme de deux termes représentant le succès ou l'échec de la demande de priorité immédiatement supérieure. Si cette dernière demande s'est soldée par un échec, la demande de rang i conserve la même probabilité puisque le nombre de blocs reste identique. Si cette demande a été un succès, le nombre des blocs disponibles a diminué de 1. On constate qu'il existe une probabilité non nulle de satisfaction pour une demande dont le rang serait supérieur au nombre de blocs.

$$P_{i} = P_{i-1}(1 - P_{i-1}) + P_{i-1}(P_{i-1} - 1/m)$$

$$P_{i} = P_{i-1}^{2} - P_{i-1}^{2} + P_{i-1} \cdot \frac{m-1}{m}$$

$$P_{i} = P_{i-1} \cdot \frac{m-1}{m} = (\frac{m-1}{m})^{i-1}$$

Si, à l'instant initial, p demandes se sont présentées, la probabilité globale sur l'ensemble des réponses effectivement fournies sera la somme des probabilités affectées à chacune des demandes. Cette somme représente le débit de la mémoire:

$$D_{p} = \sum_{i=0}^{i=p-1} \left( \frac{m-1}{m} \right)^{i}$$

Expression que l'on peut encore mettre sous la forme:

$$D_{p} = \frac{1 - \left(\frac{m-1}{m}\right)^{p+1}}{1 - \frac{m-1}{m}}$$

Lorsque p tend vers l'infini, le débit tend vers m, valeur maximum obtenue si tous les blocs sont mis au travail. Il est possible de présenter plus de demandes qu'il n'existe de blocs dans la mémoire; toute demande, quel que soit le nombre des demandes prioritaires desservies avant elle, conserve une chance d'être servie. Cette remarque concerne tout particulièrement les machines fonctionnant en temps partagé et capables de se mettre à la disposition d'un grand nombre de périphériques très lents. Pour ceux-ci, une attente pouvant se prolonger sur plusieurs centaines de cycles de la mémoire n'a guère d'importance. Ils peuvent donc se contenter d'une probabilité de satisfaction très faible.

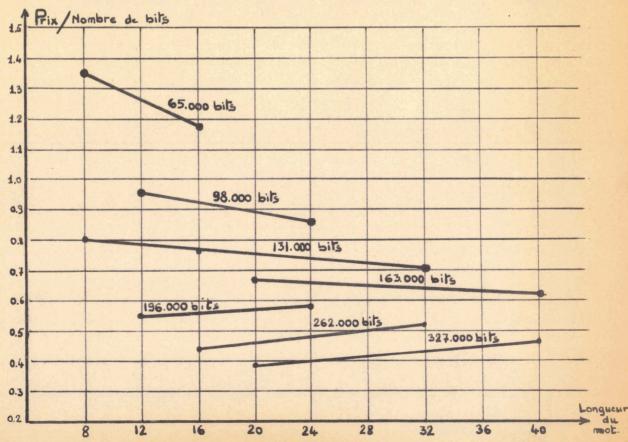

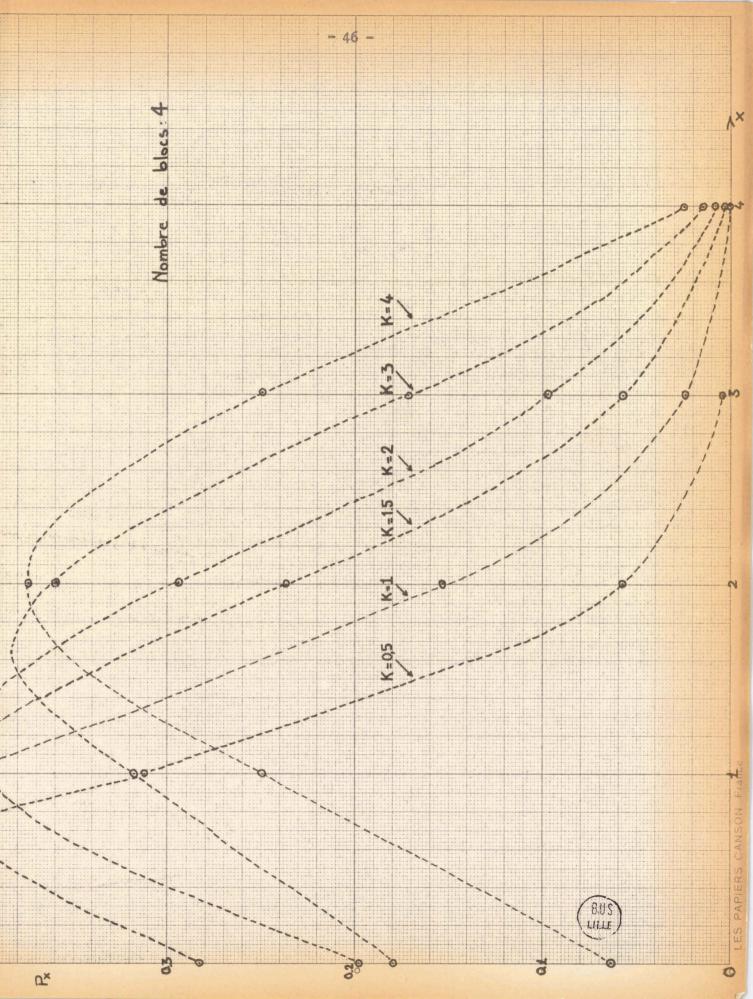

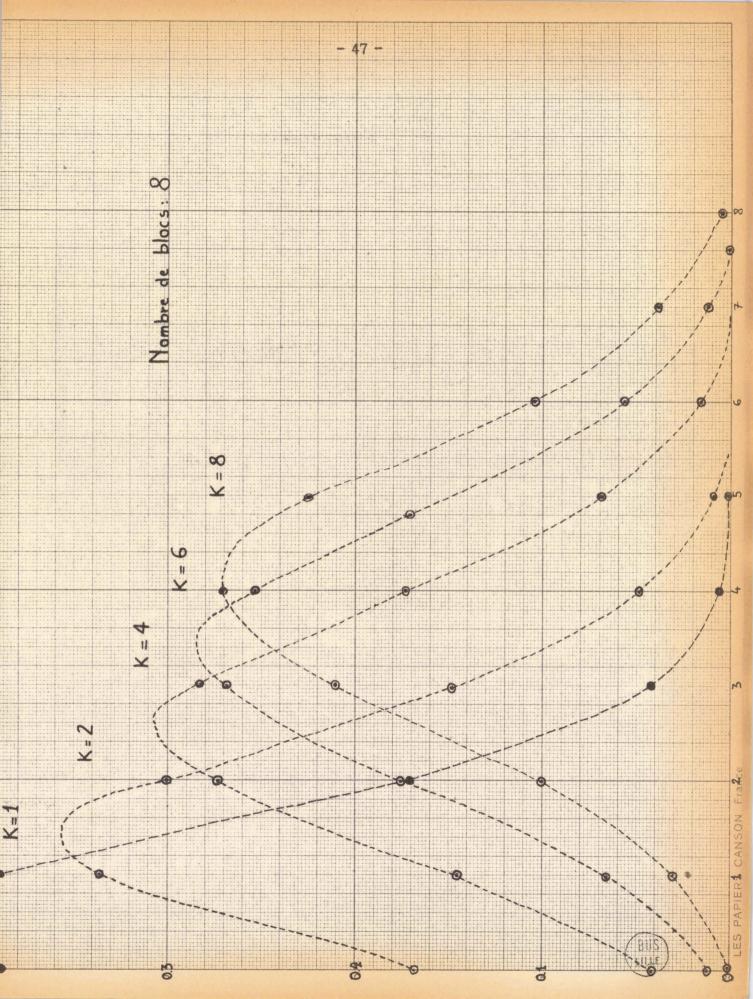

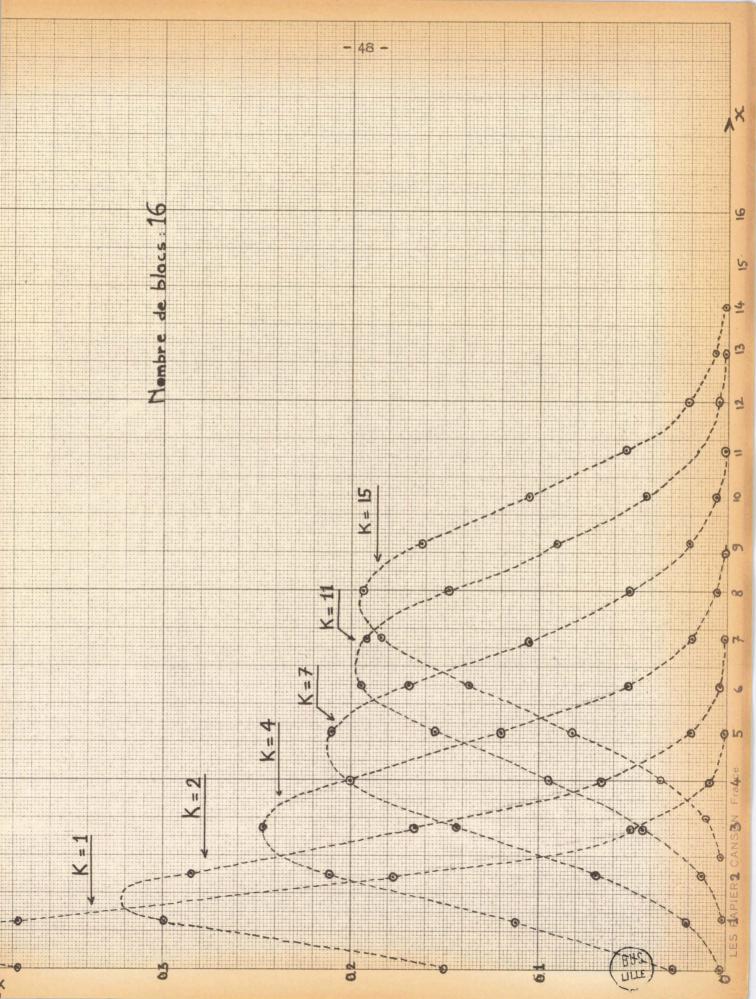

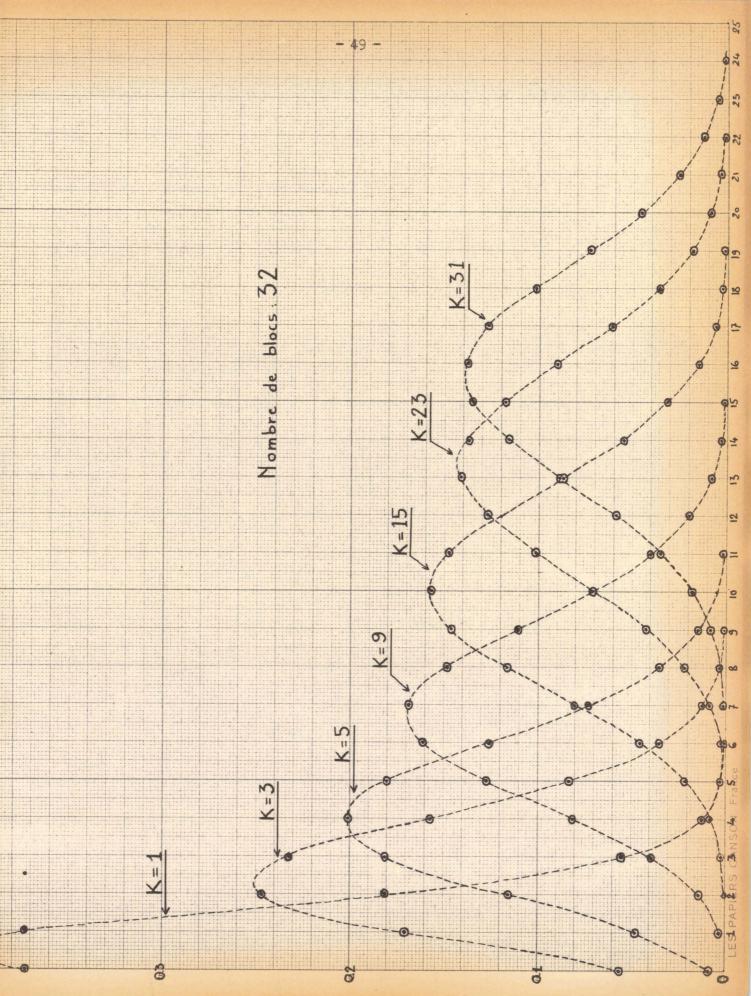

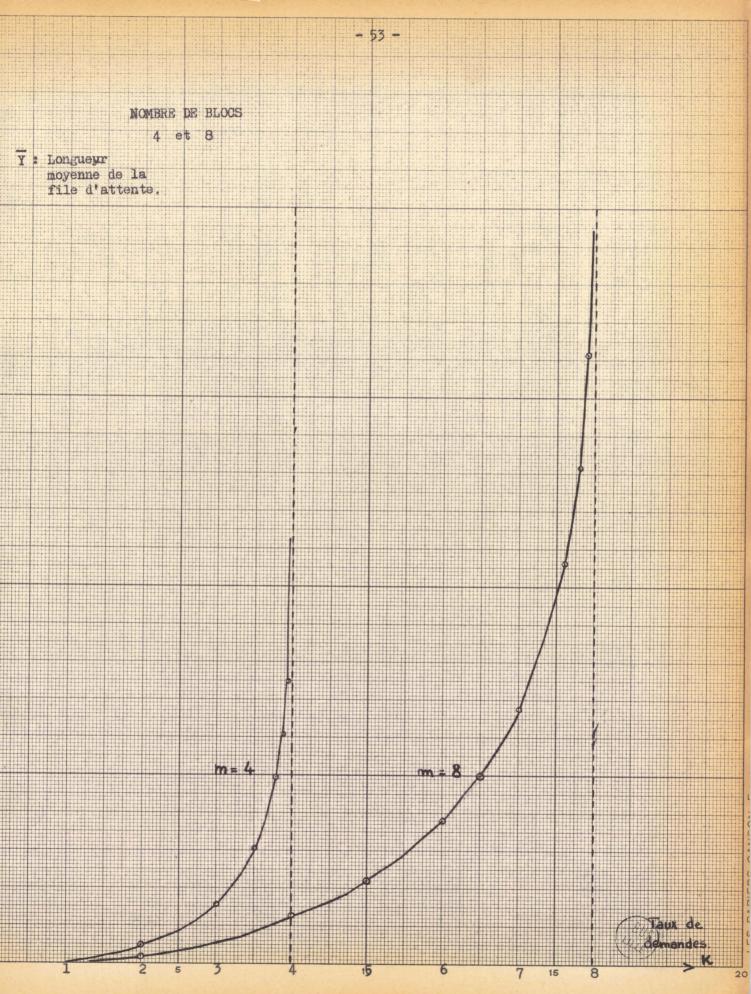

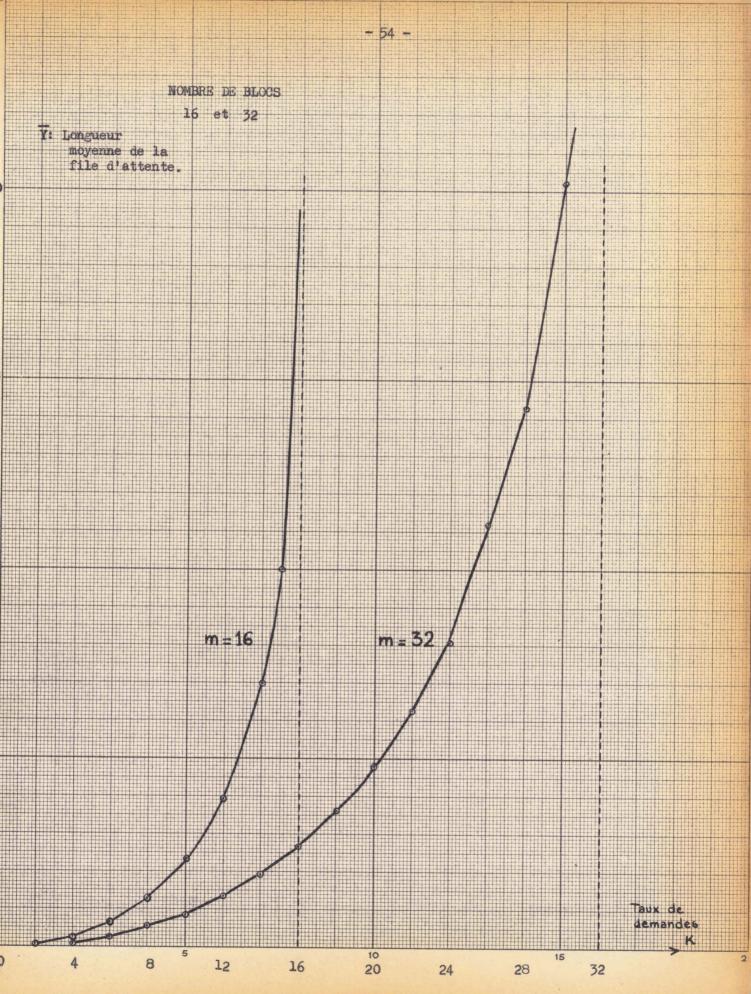

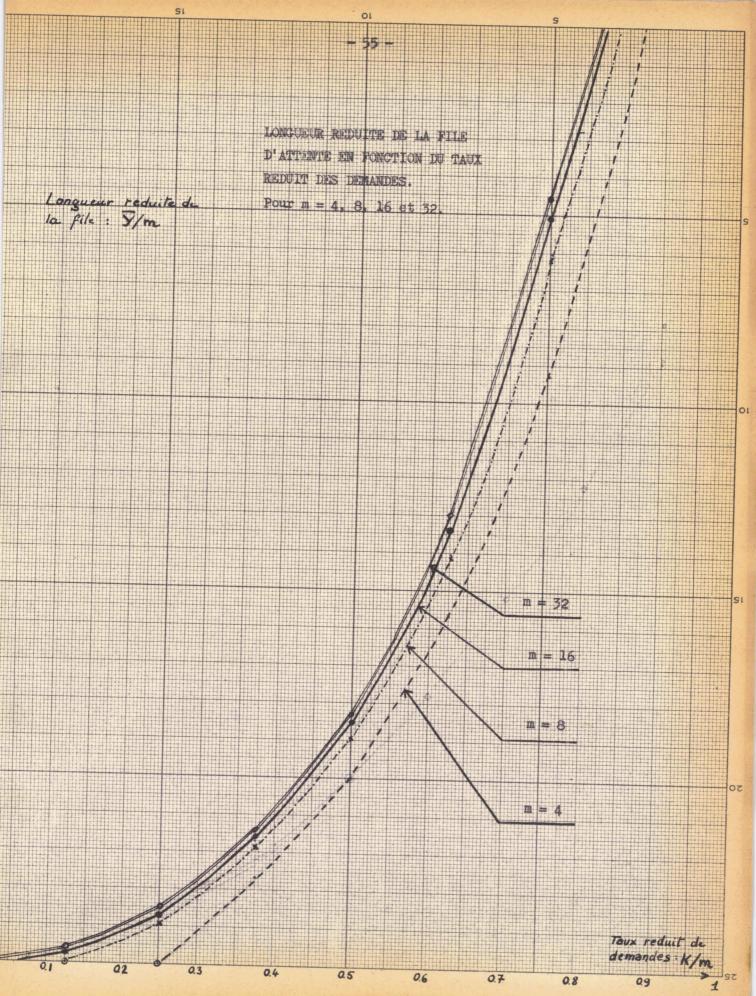

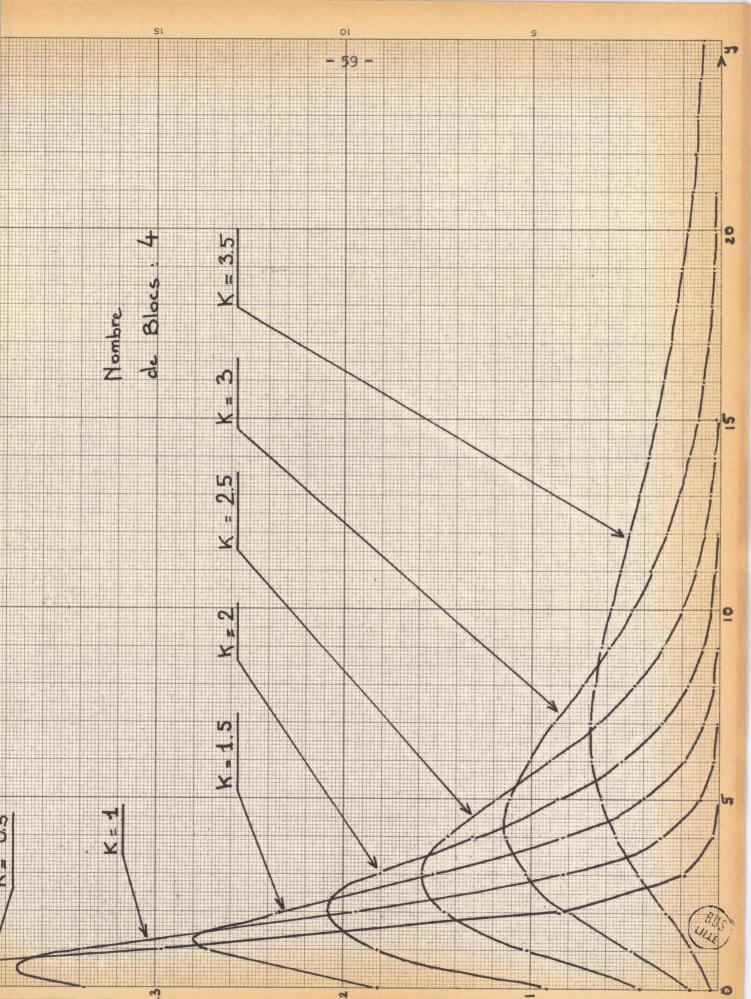

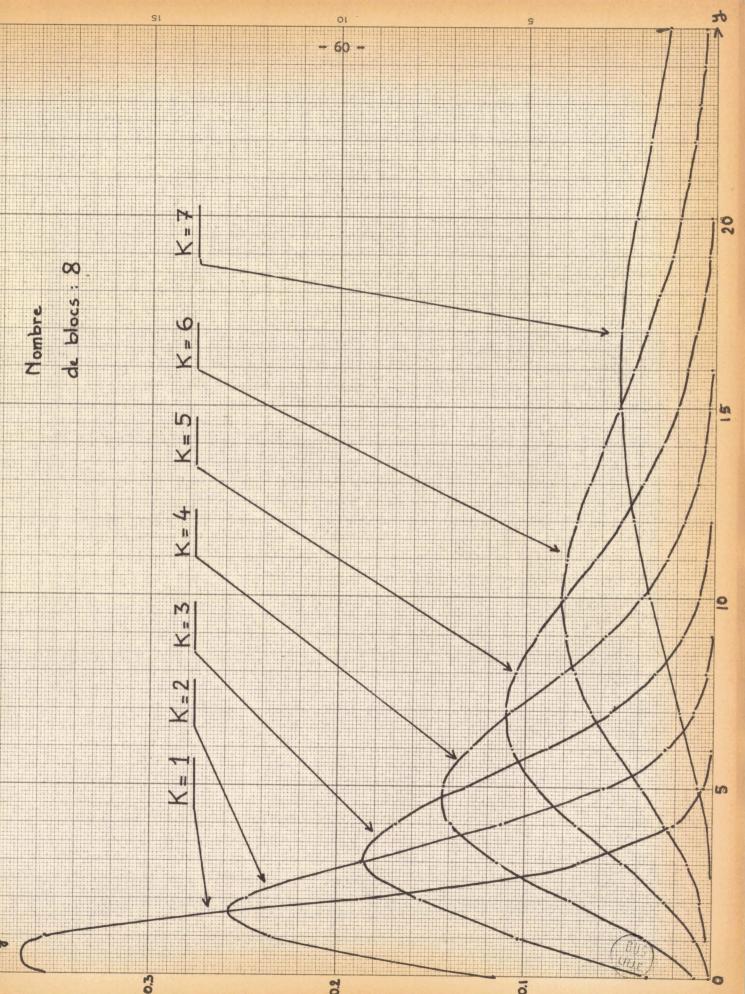

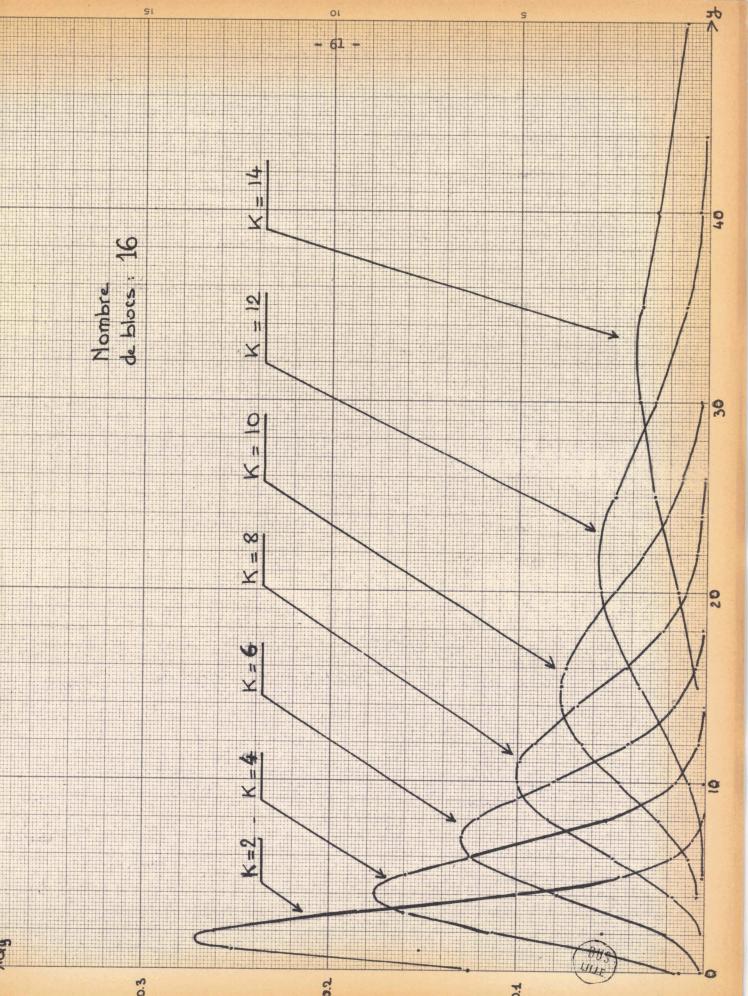

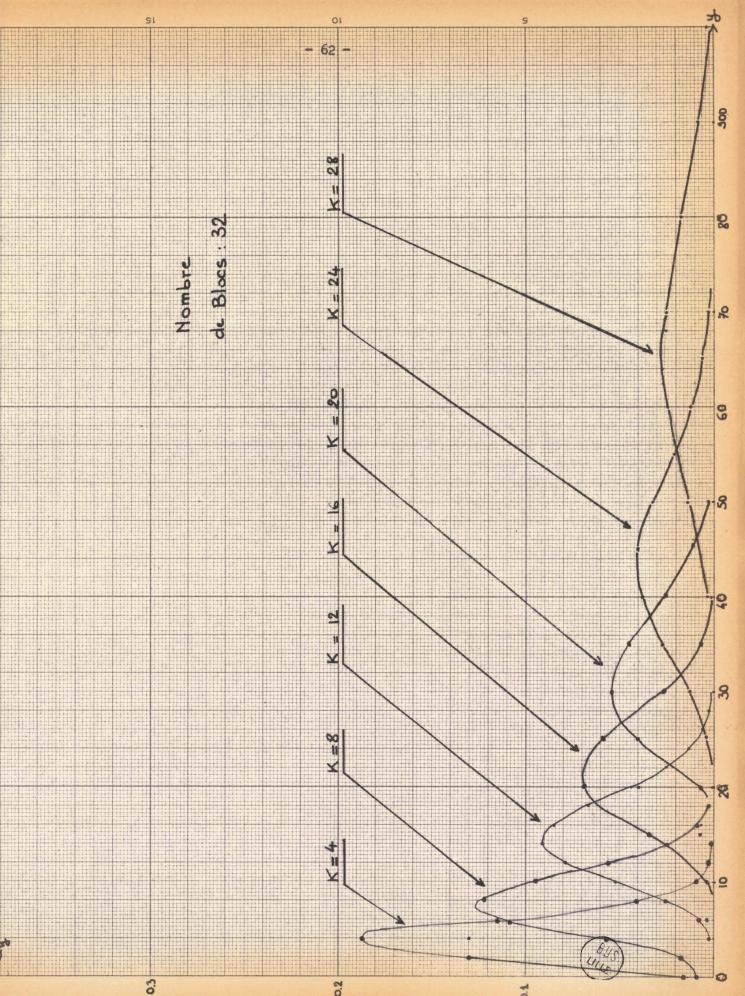

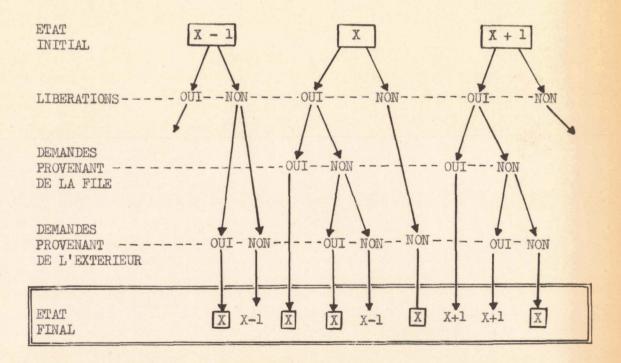

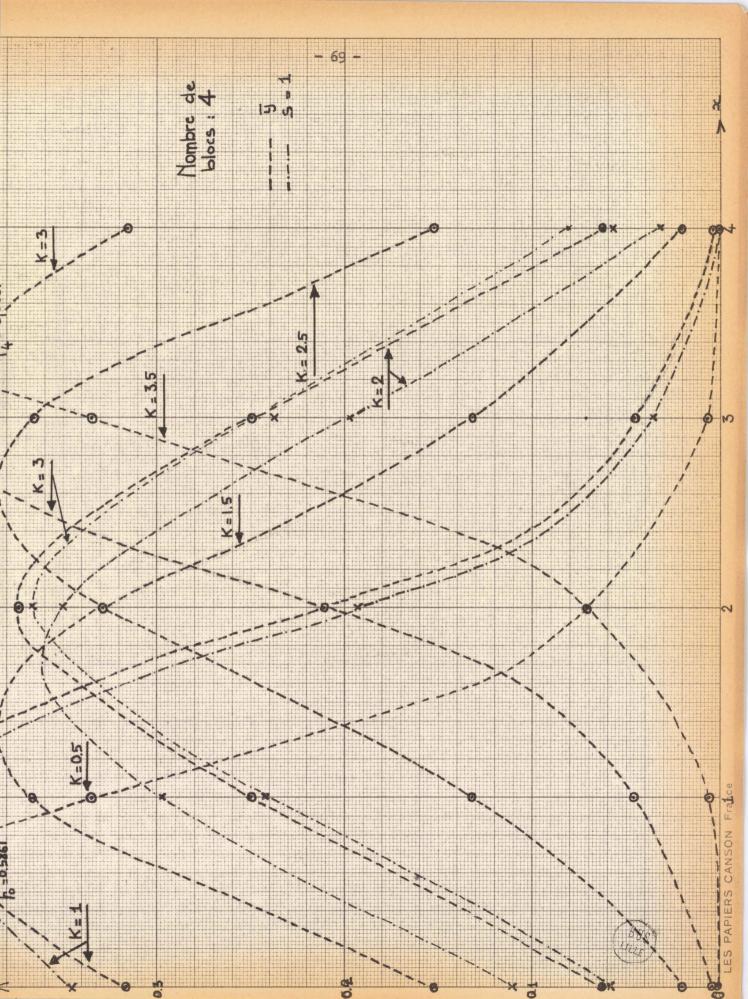

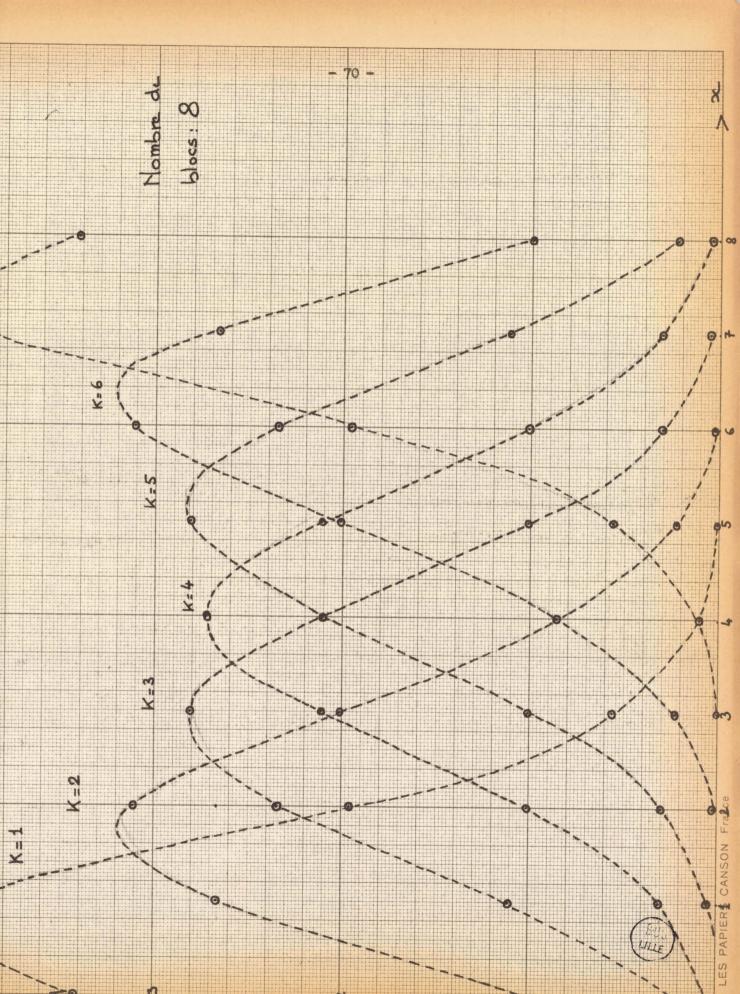

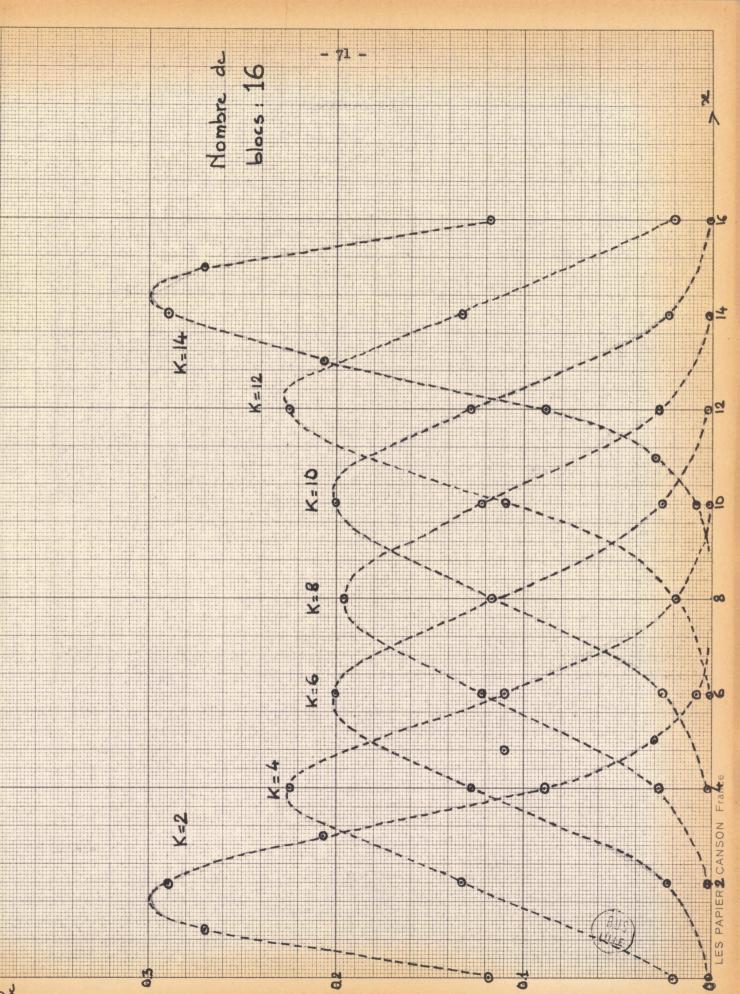

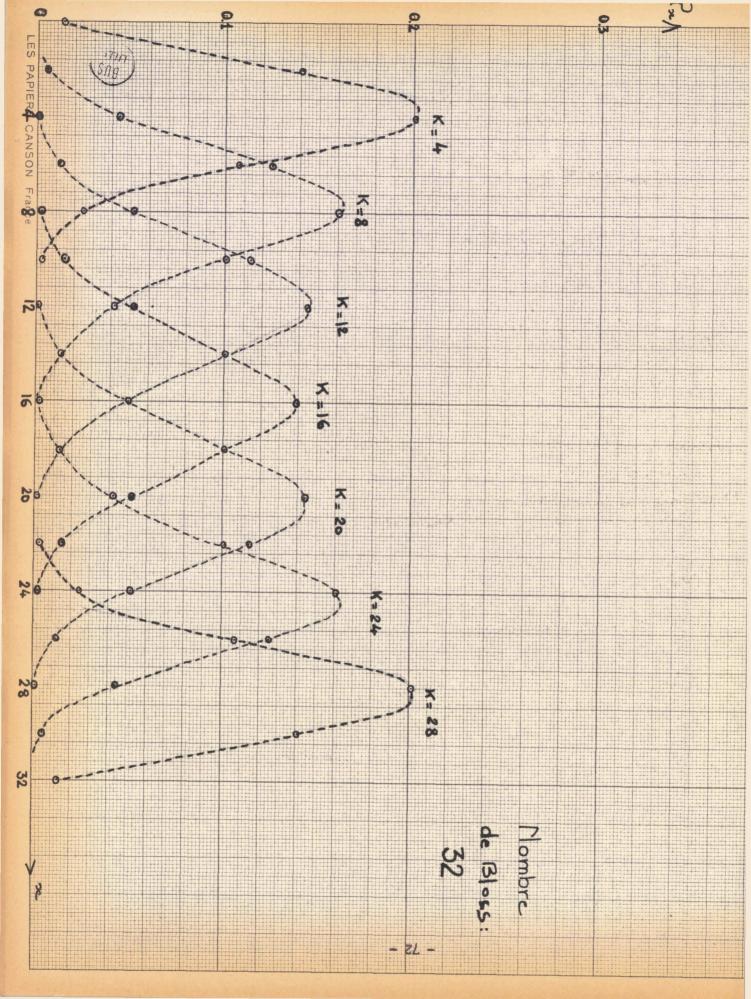

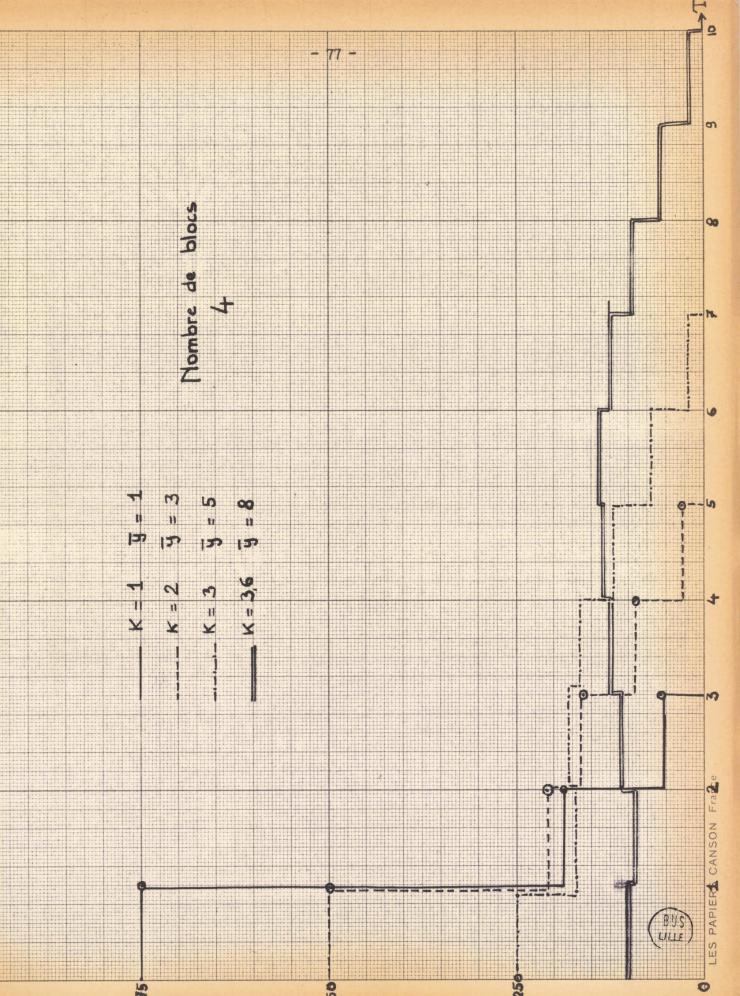

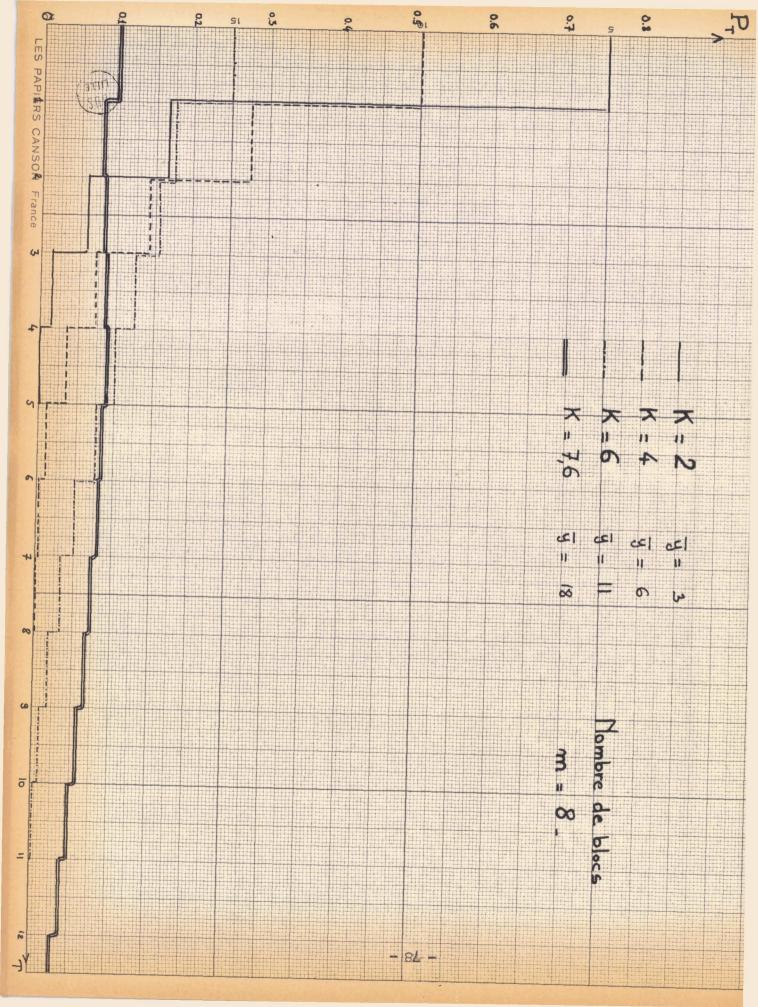

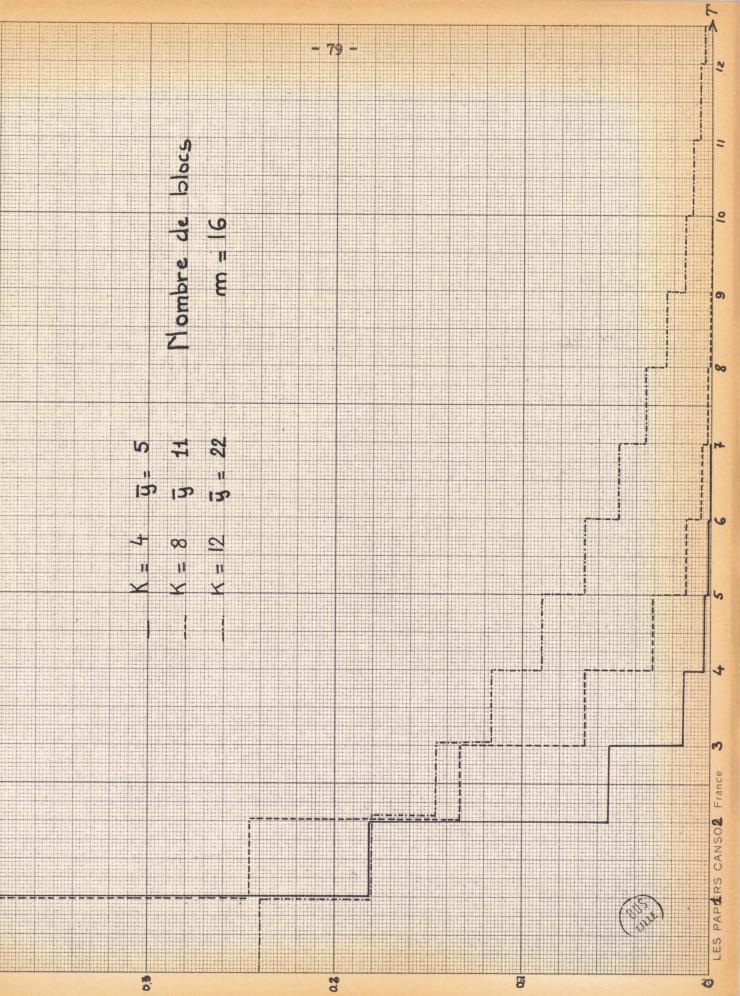

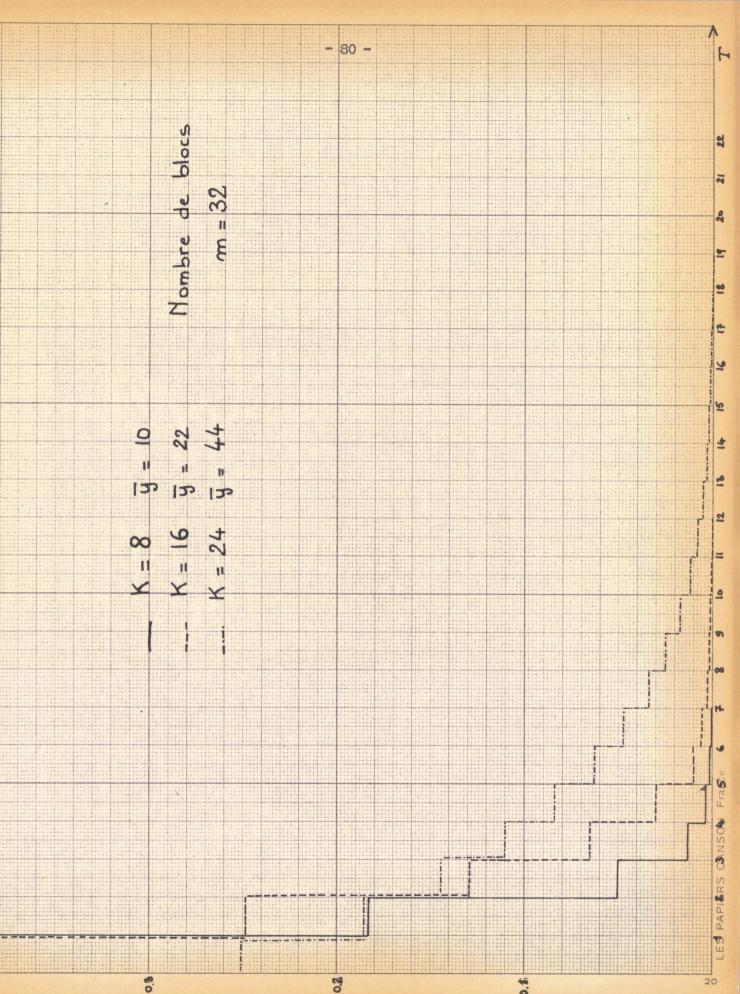

Application. Si on admet que les poids faibles de l'adresse définissent le bloc, l'adressage étant binaire, le nombre de blocs indépendants doit étre une puissance de deux. Le calcul du débit en fonction du nombre de blocs a été fait pour 2, 4, 8, 16, 32 et 64 blocs.

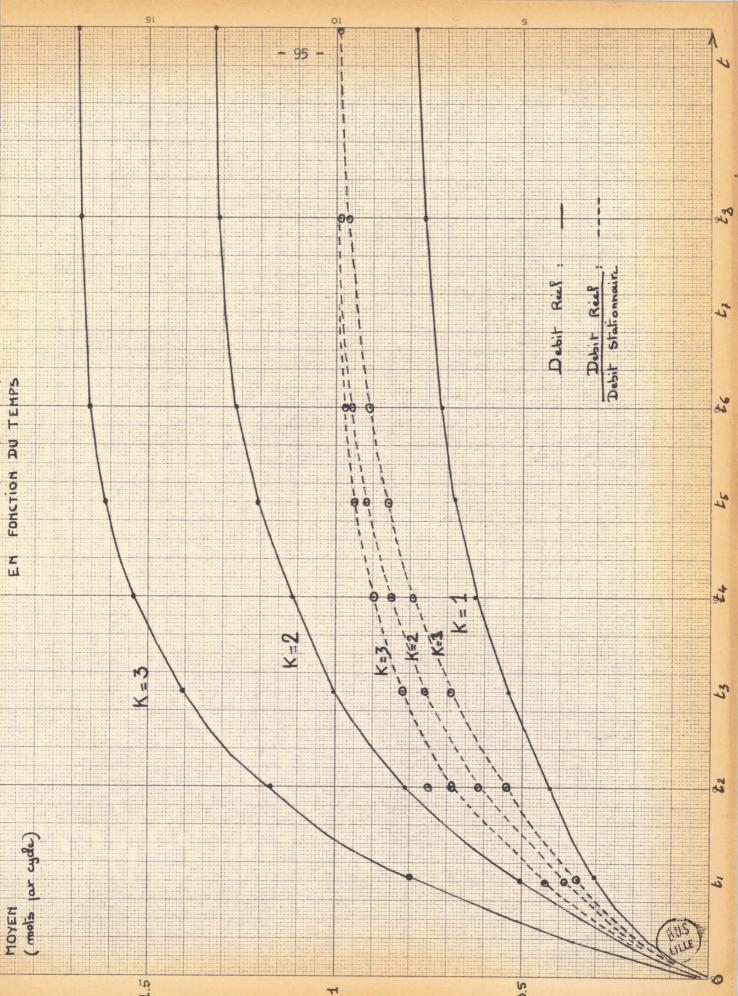

Le nombre de demandes, qui représente la variable varie de 1 jusqu'à une valeur telle que la probabilité de satisfaction soit inférieure à 0,01. Les courbes de la page suivante résument ces résultats.

## D - ORGANISATION PRATIQUE D'UNE MEMOIRE PARTAGEE

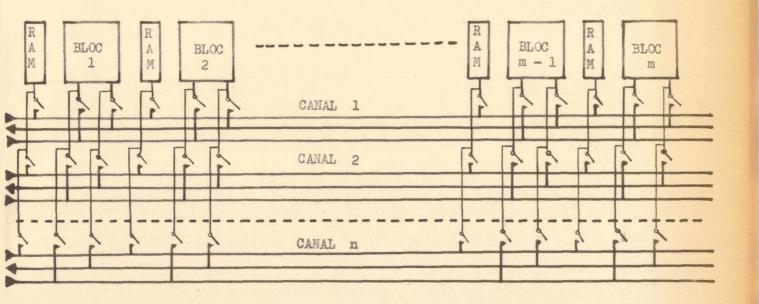

S'il existe n canaux indépendants et m blocs de mémoire, il faut assurer à chaque canal la possibilité d'accéder à chacun des blocs ce qui réclame théoriquement n.p aiguillages. Chacun de ces aiguillages est triple puiqu'il doit commuter d'une part la partie adresse désignant la position dans le bloc et d'autre part les voies de lecture et d'écriture.

# 1) Commutation purement spaciale.

Un réseau d'interrupteurs permet, à tout instant de relier n'importe quel canal à n'importe quel bloc. La logique de priorité commande les portes placées du coté du canal tandis que la partie adresse qui désigne le bloc dans la demande commande les portes placées du coté des mémoires.

Cette solution devient rapidement très lourde: Par exemple, pour 8 blocs de 8.000 mots soit une capacité totale de 64.000 mots de 32 bits chacun, il faut, pour desservir 4 canaux:

- Pour les adresses ( 13 bits ):13 x 8 x 4 soit 416 portes.

- Pour la voie d'écriture: 32 x 8 x 4 soit 1024 portes.

- Pour la voie de lecture: 32 x 8 x 4 soit 1024 portes.

Au total, cette solution réclame 2.464 portes ce qui est très lourd. Elle présente cependant l'avantage de permettre un fonctionnement totalement asynchrone.

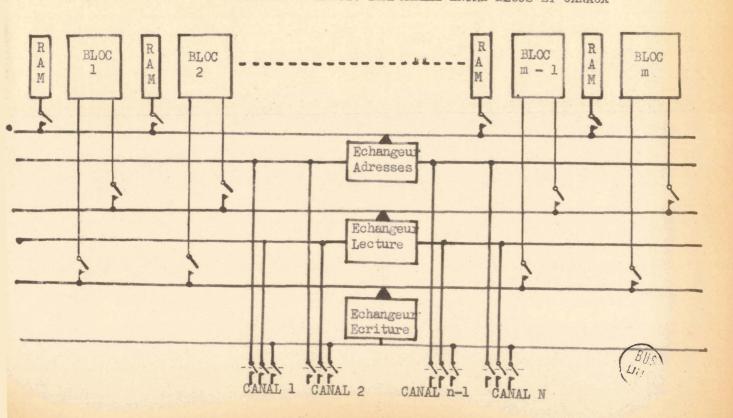

# 2) Commutation spacio-temporelle.

On peut obtenir une économie significative de circuits par la mise en oeuvre d'une solution en apparence moins souple: La répartition non seulement spaciale mais aussi temporelle des connexions entre canaux et blocs. Chaque canal débouche par un premier réseau de portes sur trois unités d'échange, l'une pour les adresses, les deux autres pour la lecture et l'écriture. Ces unités d'échange sont, à leur tour reliées par un second réseau de portes aux blocs de la mémoire. Il suffit de n + p aiguillages triples. Dans le cas de la mémoire prise en exemple plus haut, il faut:

- Pour les portes du coté des canaux: (13 + 32 + 32).4 soit 308 portes.

- Du coté des blocs: (13 + 32 + 32).8 soit 616 portes.

Au total, cette solution ne réclame que 924 portes.

Cette économie sur les circuits d'aiguillage ôte, en contre-partie, la possibilité d'une simultanéité totale des blocs. A un instant donné, il ne peut s'établir qu'une seule connexion entre un canal et un bloc.

Pour que le débit ne soit pas diminué, l'unité d'échange doit étre extrêmement rapide. Si on désire qu'elle ne puisse, en aucun cas, réduire ce débit, il faut qu'elle soit capable, pendant le temps T de cycle d'un bloc, de satisfaire chacun des autres. Si la mémoire comporte m blocs, le temps total d'intervention de l'unité d'échange sera au maximum égal à T/m. En fait, il faut faire la différence entre les opérations de lecture et les opérations d'écriture. En supposant que chaque bloc de la mémoire dispose de son propre registre d'entrée-sortie, une opération de lecture va se traduire par une demande suivie, après un certain délai, de l'acquisition de l'information demandée dans le registre d'entrée-sortie. Il est impossible de figer les portes de commutation pendant ce délai. Les ordres de commutation doivent donc étre dédoublés, les demandes d'écriture provenant du canal en même temps que l'information à écrire et les demandes de lecture étant émises par les blocs lorsqu'ils ont obtenus l'information.

Le temps de cycle de l'unité d'échange, qui sera pris comme référence dans toute la suite, représente donc le temps de base de la mémoire partagée. Pendant un cycle on doit pouvoir faire les opérations suivantes:

- Choisir une demande provenant de l'un des canaux, déterminer s'il s'agit d'une lecture ou d'une écriture.

- Dans le cas d'une demande d'écriture, décoder l'adresse du bloc, examiner s'il est libre et dans l'affirmative transférer l'adresse et l'information vers le bloc.

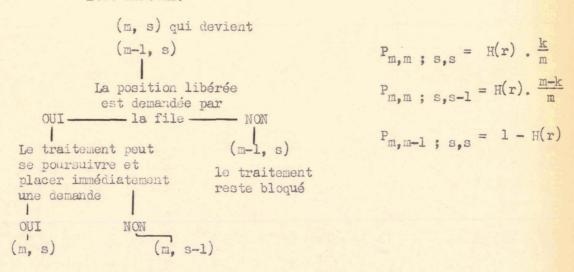

- Dans le cas d'une demande de lecture, procéder aux mêmes opérations, sans transfert d'information.