THÈSE

présentée à

# L'UNIVERSITE DES SCIENCES ET TECHNIQUES DE LILLE FLANDRES ARTOIS

pour obtenir

Le titre de DOCTEUR ES SCIENCES

par

Przemyslaw BAKOWSKI

## CONTRIBUTION A LA CONCEPTION DE L'ARCHITECTURE MATERIELLE DES ORDINATEURS

Projet LIDO

Préprocesseur pour la compilation en silicium

Exemplaire corrigé après avis du jury

Thèse soutenue le 11 Juillet 1986 devant la Commission d'Examen

Membres du Jury

Président

Rapporteur

Examinateurs

C. CARREZ

V. CORDONNIER

G. JOURNEL

D. ETIEMBLE

R. MARCZINSKI

UNIVERSITE DES SCIENCES ET TECHNIQUES DE LILLE FLANDRES ARTOIS U.F.R. d'I.E.E.A. 841, M3 - 59655 VILLENEUVE D'ASCO CEDEX Tél. 2043 44 83 M. CONSTANT Eugène I.E.E.A.

M. FOURET René Physique

M. GABILLARD Robert I.F.E.A.

M. MONTREUIL Jean Biologie

M. PARREAU Michel Mathématiques

M. TRIDOT Gabriel Chimie

M. WERTHEIMER Raymond

M. VIVIER Emile

## P R O F E S S E U R S lère classe

Biologie

Physique

| M. | BACCHUS Pierre              | Mathématiques        |

|----|-----------------------------|----------------------|

| M. | BEAUFILS Jean-Pierre (dét.) | Chimie               |

| M. | BIAYS Pierre                | G.A.S.               |

| M. | BILLARD Jean (dét.)         | Physique             |

| M. | BOILLY Bénoni               | Biologie             |

| M. | BOIS Pierre                 | Mathématiques        |

| M. | BONNELLE Jean-Pierre        | Chimie               |

| M. | BOUGHON Pierre              | Mathématiques        |

| M. | BOURIQUET Robert            | Biologie             |

| M. | BREZINSKI Claude            | I.E.E.A.             |

| M. | CELET Paul                  | Sciences de la Terre |

| M. | CHAMLEY Hervé               | Biologie             |

| M. | COEURE Gérard               | Mathématiques        |

| M. | CORDONNIER Vincent          | I.E.E.A.             |

| M. | DEBOURSE Jean-Pierre        | S.E.S.               |

| M. | DYMENT Arthur               | Mathématiques        |

|    | - 1 -                       |                      |

## PROFESSEURS lère classe (suite)

M. ZEYTOUNIAN Radyadour

Physique M. ESCAIG Bertrand Mathématiques M. FAURE Robert Chimie M. FOCT Jacques S.E.S. M. GRANELLE Jean-Jacques Mathématiques GRUSON Laurent M. Biologie GUILLAUME Jean Μ. Mathématiques M. HECTOR Joseph Chimie M. LABLACHE COMBIER Alain M. LACOSTE Louis Biologie Sciences de la Terre M. LAVEINE Jean Pierre Mathématiques M. LEHMANN Daniel Physique Mme LENOBLE Jacqueline Chimie M. LHOMME Jean S.E.S. M. LOMBARD Jacques Chimie M. LOUCHEUX Claude Chimie M. LUCQUIN Michel E.U.D.I.L. M. MIGEON Michel Recteur à Grenoble Mathématiques M. MIGNOT Fulbert (dét.) Sciences de la Terre M. PAQUET Jacques Sciences de la Terre M. PROUVOST Jean Biologie M. ROUSSEAU Jean-Paul I.E.E.A. M. SALMER Georges I.E.E.A. M. SEGUIER Guy S.E.S. M. SIMON Michel S.E.S. M. STANKIEWICZ François Physique M. TILLIEU Jacques I.E.E.A. M. VIDAL Pierre

Mathématiques

##

| M. ANTOINE Philippe           | Mathématiques (Calais) |

|-------------------------------|------------------------|

| M. BART André                 | Biologie               |

| Mme BATTIAU Yvonne            | Géographie             |

| M. BEGUIN Paul                | Mathématiques          |

| M. BELLET Jean                | Physique               |

| M. BERZIN Robert              | Mathématiques          |

| M. BKOUCHE Rudolphe           | Mathématiques          |

| M. BODARD Marcel              | Biologie               |

| M. BOSQ Denis                 | Mathématiques          |

| M. BRASSELET Jean-Paul        | Mathématiques          |

| M. BRUYELLE Pierre            | Géographie             |

| M. CAPURON Alfred             | Biologie               |

| M. CARREZ Christian           | I.E.E.A.               |

| M. CAYATTE Jean-Louis         | S.E.S.                 |

| M. CHAPOTON Alain             | C.U.E.E.P.             |

| M. COQUERY Jean-Marie         | Biologie               |

| Mme CORSIN Paule              | Sciences de la Terre   |

| M. CORTOIS Jean               | Physique               |

| M. COUTURIER Daniel           | Chimie                 |

| M. CROSNIER Yves              | I.E.E.A.               |

| M. CURGY Jean-Jacques         | Biologie               |

| Mle DACHARRY Monique          | Géographie             |

| M. DAUCHET Max                | I.E.E.A.               |

| M. DEBRABANT Pierre           | E.U.D.I.L.             |

| M. DEGAUQUE Pierre            | I.E.E.A.               |

| M. DELORME Pierre             | Biologie               |

| M. DELORME Robert             | S.E.S.                 |

| M. DE MASSON D'AUTUME Antoine | S.E.S.                 |

|                               |                        |

M. DEMUNTER Paul

C.U.E.E.P.

## PROFESSEURS 2ème classe (Suite 1)

M. JOFFRE Patrick

| M.  | DENEL Jacques           | I.E.E.A.               |

|-----|-------------------------|------------------------|

| M.  | DE PARIS Jean-Claude    | Mathématiques (Calais) |

| Mle | DESSAUX Odile           | Chimie                 |

| M.  | DEVRAINNE Pierre        | Chimie                 |

| M.  | DHAINAUT André          | Biologie               |

| Mme | DHAINAUT Nicole         | Biologie               |

| M.  | DORMARD Serge           | S.E.S.                 |

| M.  | DOUKHAN Jean-Claude     | E.U.D.I.L.             |

| M.  | DUBOIS Henri            | Physique               |

| M.  | DUBRULLE Alain          | Physique (Calais)      |

| M.  | DUBUS Jean-Paul         | I.E.E.A.               |

| M.  | FAKIR Sabah             | Mathématiques          |

| M.  | FONTAINE Hubert         | Physique               |

| M.  | FOUQUART Yves           | Physique               |

| M.  | FRONTIER Serge          | Biologie               |

| M.  | GAMBLIN André           | G.A.S.                 |

| M.  | GLORIEUX Pierre         | Physique               |

| M.  | GOBLOT Rémi             | Mathématiques          |

| M.  | GOSSELIN Gabriel (dét.) | S.E.S.                 |

| M.  | GOUDMAND Pierre         | Chimie                 |

| M.  | GREGORY Pierre          | I.P.A.                 |

| M.  | GREMY Jean-Paul         | S.E.S.                 |

| M.  | GREVET Patrice          | S.E.S.                 |

| M.  | GUILBAULT Pierre        | Biologie               |

| M.  | HENRY Jean-Pierre       | E.U.D.I.L.             |

| M.  | HERMAN Maurice          | Physique               |

| M.  | JACOB Gérard            | I.E.E.A.               |

| M.  | JACOB Pierre            | Mathématiques          |

| M.  | JEAN Raymond            | Biologie               |

I.P.A.

### PROFESSEURS 2ème classe (suite 2)

M. RACZY Ladislas

RICHARD Alain

RAOULT Jean François

M.

M.

E.U.D.I.L. JOURNEL Gérard M. Biologie M. KREMBEL Jean Mathématiques M. LANGRAND Claude I.E.E.A. LATTEUX Michel M. Chimie Mme LECLERCQ Ginette Sciences de la Terre LEFEVRE Christian M. Mathématiques Mle LEGRAND Denise Mathématiques (Calais) Mle LEGRAND Solange Mathématiques Mme LEHMANN Josiane Physique LEMAIRE Jean Géographie LHENAFF René M. Physique M. LOCQUENEUX Robert C.U.E.E.P. M. LOSFELD Joseph E.U.D.I.L. M. LOUAGE Francis (dét.) Physique M. MACKE Bruno I.E.E.A. M. MAIZIERES Christian Physique M. MESSELYN Jean S.E.S. M. MESSERLIN Patrick Physique M. MONTEL Marc Biologie Mme MOUNIER Yvonne Mathématiques M. PARSY Fernand Biologie Mle PAUPARDIN Colette Chimie M. PERROT Pierre Biologie PERTUZON Emile M. Chimie PONSOLLE Louis M. Biologie PORCHET Maurice M. E.U.D.I.L. POVY Lucien M.

Biologie

I.E.E.A.

Sciences de la Terre

#### PROFESSEURS 2ème Classe (suite 3)

M. WATERLOT Michel

Mme ZINN JUSTIN Nicole

M. RIETSCH François E.U.D.I.L. M. ROBINET Jean-Claude E.U.D.I.L. M. ROGALSKI Marc Mathématiques M. ROY Jean-Claude Biologie M. SCHAMPS Joël Physique Mme SCHWARZBACH Yvette Mathématiques M. SLIWA Henri Chimie M. SOMME Jean G.A.S. Mle SPIK Geneviève Biologie M. STAROSWIECKI Marcel E.U.D.I.L. M. STERBOUL François E.U.D.I.L. M. TAILLIEZ Roger Institut Agricole Mme TJOTTA Jacqueline (dét.) Mathématiques M. TOULOTTE Jean-Marc I.E.E.A. M. TURRELL Georges Chimie M. VANDORPE Bernard E.U.D.I.L. M. VAST Pierre Chimie M. VERBERT André Biologie M. VERNET Philippe Biologie M. WALLART Francis Chimie M. WARTEL Michel Chimie

Sciences de la Terre

### CHARGES DE COURS

#### M. ADAM Michel

S.E.S.

## CHARGES DE CONFERENCES

| M. | BAFCOP Joël                    | I.P.A. |

|----|--------------------------------|--------|

| M. | DUVEAU Jacques                 | S.E.S. |

| M. | HOFLACK Jean                   | I.P.A. |

| M. | LATOUCHE Serge                 | S.E.S. |

| M. | MALAUSSENA DE PERNO Jean-Louis | S.E.S. |

| M. | NAVARRE Christian              | I.P.A. |

| М. | OPIGEZ Philippe                | S.E.S. |

A ma femme

#### Przemyslaw BAKOWSKI

# CONTRIBUTION A LA CONCEPTION DE L'ARCHITECTURE MATERIELLE DES ORDINATEURS

Projet LIDO Préprocesseur pour la compilation en silicium

\* \* \*

A CONTRIBUTION TO THE DESIGN OF COMPLEX COMPUTER ARCHITECTURE

LIDO Project A Silicon Compiler Preprocessor

#### REMERCIEMENTS

Je tiens à exprimer toute ma reconnaissance à Monsieur V. Cordonnier, Professeur à l'Université Lille I, qui m'a accueilli dans son Laboratoire de Recherche et qui m'a accordé une confiance exigeante.

#### Je tiens à remercier:

Monsieur C. Carrez, Professeur à l'Université Lille I, de m'avoir fait l'honneur de présider le jury de cette thèse.

Monsieur D. Etiemble, Professeur à l'Université Paris VI, d'avoir accepté d'être rapporteur de cette thèse et d'avoir bien voulu me faire profiter de ses remarques constructives.

Monsieur G. Journel, Professeur à l'Université Lille I, d'avoir accepté, malgré des responsabilités multiples, de faire partie du jury de cette thèse.

Monsieur R. Marczynski, Professeur à l'Académie des Sciences de Pologne, d'avoir accepté d'être rapporteur de cette thèse et d'avoir franchi les frontières afin d'assister à la soutenance.

Je tiens également à remercier:

Tous mes collègues du Laboratoire d'Informatique Fondamentale qui, par leur soutien et leur aide ont contribué à ce travail.

#### TABLE DES MATIERES GENERALE

#### I. INTRODUCTION

- 1. Modèlisation globale de l'architecture du matériel

- 2. Description de l'architecture du matériel

- 3. Analyse et synthèse de l'architecture du matériel

## II. LA "FORMATIQUE" DU MATERIEL INFORMATIQUE - Une approche systémique

- et morphologique de la complexité du matériel informatique

- 1. Introduction

- 2. Formes (systèmes) élémentaires

- 3. Formes (systèmes) de deuxième ordre

- 4. Formes (systèmes) de troisième ordre

- 5. Formes (systèmes) de quatrième ordre

- 6. Remarque finale

#### III. LE LANGAGE LIDO - Langage Interprétable pour la Description des Ordinateurs

- 1. Introduction

- 2. Présentation du langage LIDO

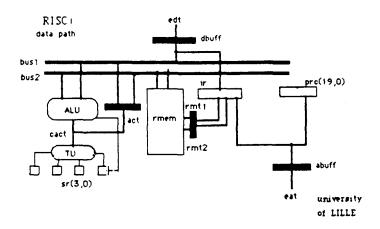

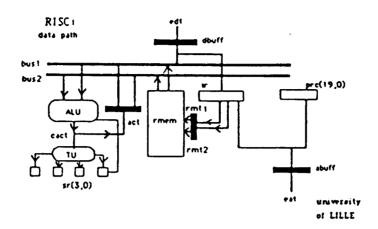

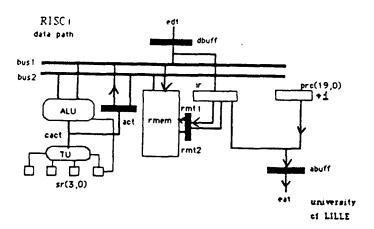

- 3. Description comparative des processeurs de type RISC

- 4. Remarques finales

#### IV. LE SYSTEME LIDO - Préprocesseur pour la compilation en silicium

- 1. Introduction

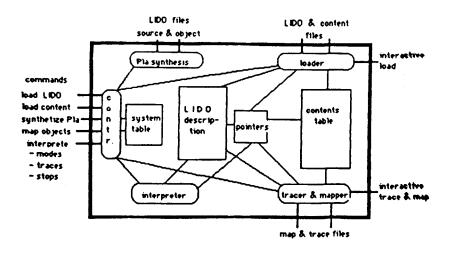

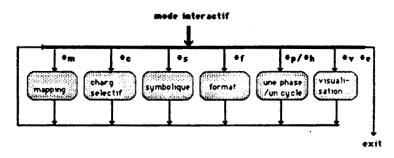

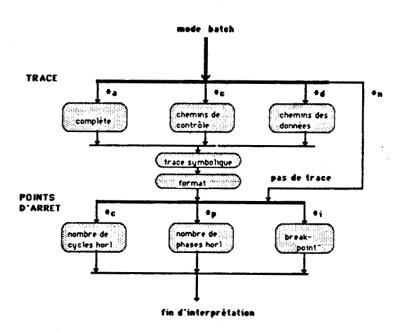

- 2. Les fonctions du système LIDO

- 3. Construction du système LIDO

- 4. Les modes de travail et les commandes du système LIDO

#### V. EN CONCLUSION

#### VI. BIBLIOGRAPHIE

VII. APPENDICES - La syntaxe du langage LIDO et deux exemples de travail sur système LIDO

#### I. INTRODUCTION

L'arrivée des systèmes VLSI a bouleversé profondément les méthodes traditionnelles de conception du matériel informatique et a apporté des moyens permettant de réaliser des structures et des fonctions d'un nouvel ordre de complexité. Toute méthodologie et tout outil informatique permettant de maîtriser et de concevoir des systèmes de plus en plus complexes ou évolués (évolué ne doit pas forcément signifier plus complexe) contribuent ainsi au développement du matériel informatique.

Dans ce mémoire nous présentons une approche et une méthodologie de conception dites "systémiques" qui permettent de concevoir l'architecture du matériel orientée VLSI. L'approche systémique consiste à comprendre et à modéliser les structures matérielles de façon globale en tenant compte du caractère hiérarchique de ces structures. Cette approche implique un certain raisonnement particulier propre à la dualité information » structure matérielle, étalée sur plusieurs niveaux "systémiques".

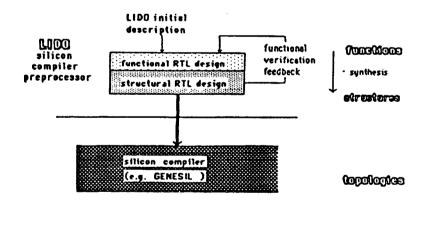

L'approche systémique est à la base de la méthodologie mise en oeuvre pour concevoir l'architecture du matériel selon le langage et le système LIDO (Langage Interprétable pour la Description des Ordinateurs). L'ensemble langage-système permet de décrire, d'analyser et de synthétiser les architectures complexes (a fortiori les plus simples) des ordinateurs afin de pouvoir les utiliser à l'entrée d'un compilateur en silicium de type GENESIL.

Ce mémoire est composé de trois parties correspondant aux trois étapes suivantes:

- modélisation globale

- description (langage LIDO)

- analyse et synthèse (système LIDO)

Ces trois étapes étant basées sur les mêmes concepts nous présentons ci-dessous une introduction générale et commune.

\* systémique - (angl.systemic) Adj. Qui se rapporte ou affecte un système dans son ensemble. N.f. La systémique, technique des systèmes complexes. LE PETIT ROBERT 1983.

Projet LIDO Page 5

#### 1. Modélisation de l'architecture du matériel

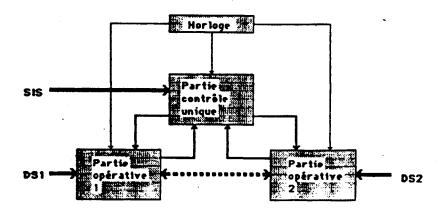

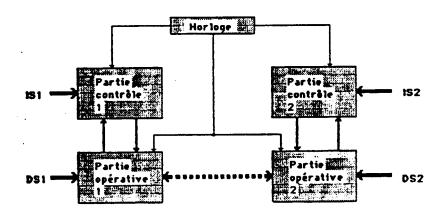

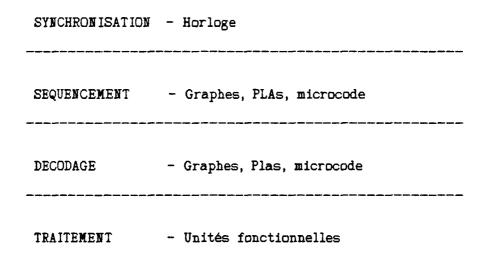

Il est évident qu'une conception dite raisonnée de l'architecture du matériel doit être établie à partir de certaines "images" ou "formes" générales représentant les traits essentiels de l'aspect structurel et de l'aspect fonctionnel de cette architecture. Ces traits devraient être dépourvus de tous les détails techniques et technologiques intervenant exclusivement de façon quantitative (p.e. nombre de bits traités par UAL ou nombre de mots de mémoire centrale). Ce type de modélisation, bien qu'il nous semble irremplaçable pour la compréhension des phénomènes et des structures du matériel, est relativement rare, ou limité, malgré les efforts considérables faits dans cette direction [Gil83]. Parmi les exemples les plus connus nous trouvons le découpage traditionnel d'un système matériel complexe en partie contrôle et en partie opérative. Cette décomposition enrichie par le facteur quantitatif donne la fameuse classification de Flynn [Fly68]: SISD, SIMD, MIMD et (MISD). Une autre approche relative à la modélisation de la partie contrôle (automate) permet de découper la fonctionnalité de cette partie en fonctions de transition et en fonctions de sortie (automate de Mealy). Prises ensemble les fonctions de transition (séquencement), les fonctions de sortie (décodage) et les fonctions de la partie opérative donnent trois niveaux de complexité fonctionnelle pour un système matériel relativement simple. Dans la même optique on peut facilement ajouter de nouvelles couches fonctionnelles telles que les fonctions de synchronisation (horloge) ou les fonctions de contrôle dans un système multiprocesseur.

Il reste quand même à expliquer la nature des liens et des interactions entre les différents niveaux structurels et fonctionnels d'un système complexe. On peut se demander si les signaux de synchronisation, ou encore "signaux" d'alimentation peuvent être considérés comme de l'information. Par ailleurs nous voudrions par exemple savoir si l'introduction de la microprogrammation augmente ou non le nombre de niveaux de complexité d'un système donné.

De telles questions se posent immédiatement si on veut introduire un certain ordre ou établir une classification. Depuis quelques années l'attention d'un certain nombre de chercheurs est attirée par la recherche de concepts relatifs

Fage 6 Projet LIDO

aux fonctions d'ordre supérieur capables de refléter la complexité opérationnelle du matériel informatique. Ces traveaux portent sur l'aspect global (architecture) [Bou83] et sur l'aspect détaillé (logique) [Han85],[Gor83] de ce matériel. Parallèlement l'efficacité, malgré ses limites, de la classification de Flynn et la validité des concepts proposés par Giloi [Gil83] ("computer architecture is defined by ordred pair (operational principle,hardware structure)") semblent tracer de nouvelles voies vers la compréhension plus cohérente et plus profonde de la nature du matériel informatique.

Notre méthode de modélisation [Bak83], restant entièrement dans le cadre des concepts proposés par Flynn et Giloi, emprunte de plus quelques concepts reconus et largement employés en systémique [Dur81],[Moi78]. Parmi ces derniers celui de systèmes énergétiquement et structurellement ouverts (voir von Bertalanffy, "General System Theory") nous a été très utile.

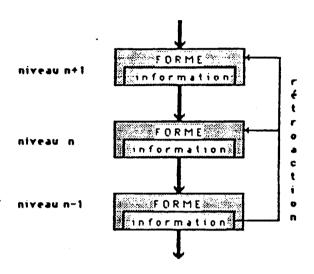

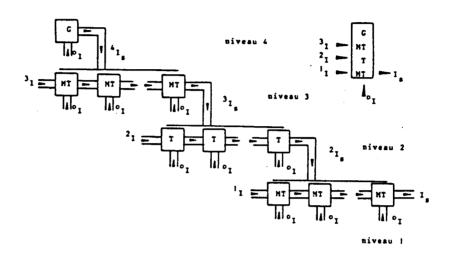

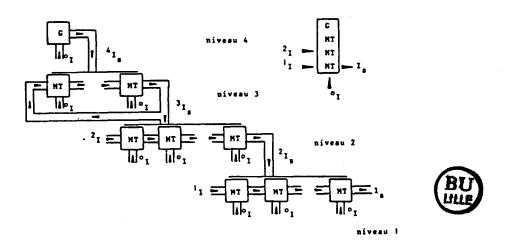

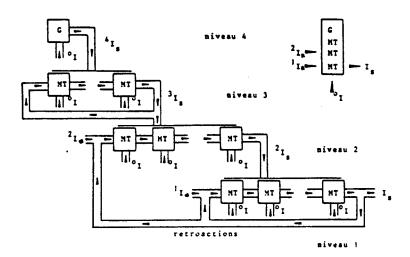

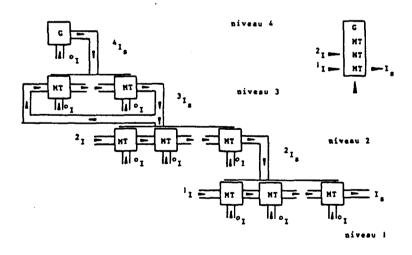

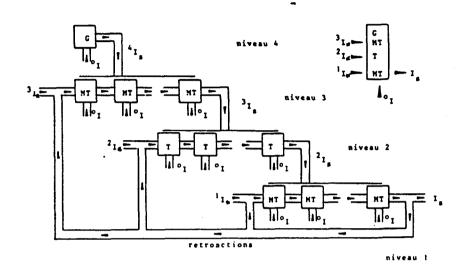

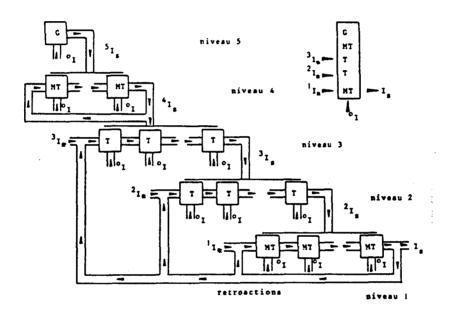

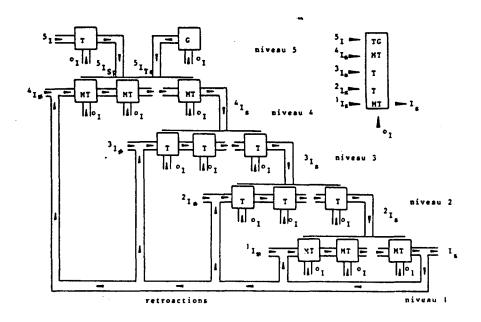

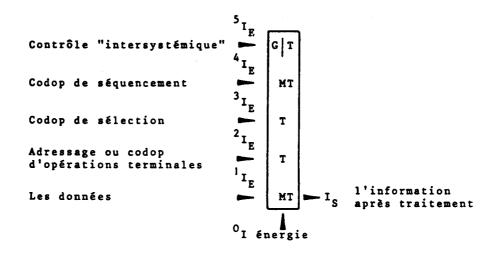

La méthode proposée dans la première partie du mémoire consiste "en gros" à voir l'architecture des ordinateurs comme superposition de couches structurelles (formes) animées par des flux d'informations. A chaque niveau systémique correspond son niveau d'information. L'influx d'énergie (alimentation) est considéré comme l'information de base indispensable pour l'animation de chaque autre niveau d'information.

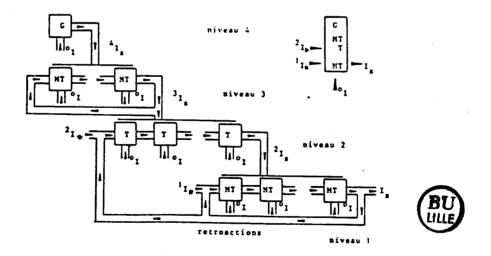

La dualité information e structure (forme) matérielle est un couplage qui permet de résoudre le problème d'interfaçage dynamique entre différents niveaux systémiques. Le passage d'un état d'information d'un niveau superieur à celui du niveau inférieur provoque des modifications structurelles du niveau subordonné. De cette façon à chaque flux d'informations peut être associé un ou plusieurs "flux de structures" subordonnées qui par la suite impliquent à nouveau des flux d'informations, qui eux mêmes provoquent de nouveaux "flux de structures" etc... En réalité, il est difficile de trouver des systèmes complexes dont l'agencement est exclusivement descendant. Dans la plupart des cas on rencontre des systèmes qui disposent de structures impliquant des rétroactions ascendantes qui sont par ailleurs indispensables pour l'enchaînement de plusieurs instructions (éxécution de programmes ou microprogrammes) ou pour des modifications dynamiques concernant l'éxécution d'instructions singulières.

Projet LIDO Page 7

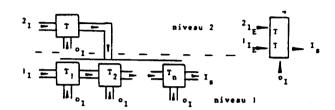

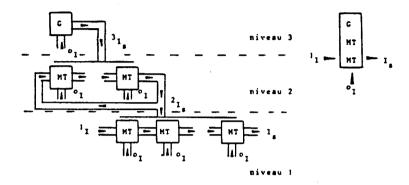

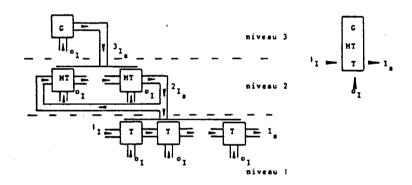

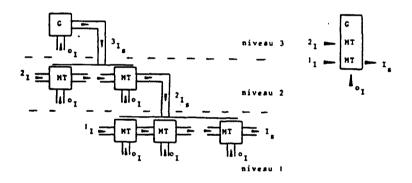

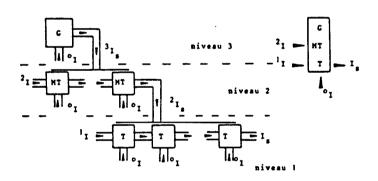

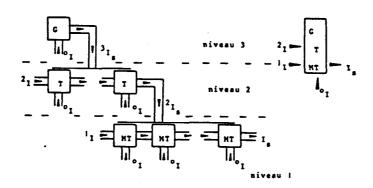

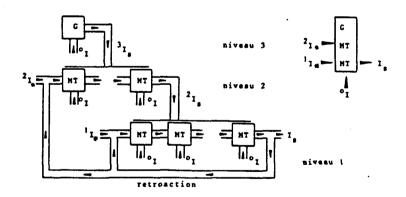

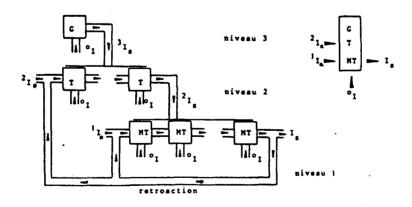

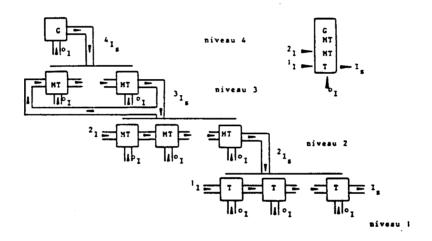

## NIVEAUX SYSTEMIQUES

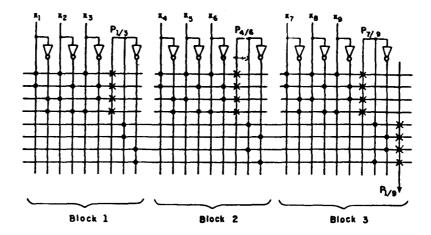

Fig.1.1. La superposition et l'agencement des niveaux systémiques

L'approche systémique offre des moyens de compréhension et de classification pour les différentes architectures matérielles par rapport à leur ordre de complexité interne. Cet ordre correspond au nombre de niveaux d'informations traitées par une architecture donnée.

#### Remarque terminologique

Afin de rendre les modèles systémiques plus cohérents dans le domaine terminologique nous employons le terme "forme" dans le sens d'une structure matérielle interne acheminant les flux d'informations.

L'opposition classique forme « matière peut ainsi être remplacée par une autre, mieux adaptée à nos besoins: forme » information.

#### 2. Description de l'architecture du matériel

Les langages pour la description du matériel (angl. Computer Hardware Description Languages - CHDLs) sont aussi vieux que le matériel informatique [Mar79], et plus vieux même que le mot informatique\*. La deuxième génération des CHDLs commence par l'introduction des langages CDL [Chu65], DDL [Du168] et AHDL [Hill71], et par la nouvelle possibilité liée à ces notations: la simulation. Parmi les successeurs européens les plus proches nous trouvons RTS I [Pi173], CASSANDRE [Mer71], OSM [Mar75]. Une liste plus détaillée et complètée par des remarques relatives à l'implémentation est donnée par Shiva [Shi79] (voir la page suivante Tab.1.1.).

Une évolution rapide des CHDLs et l'afflux des nouvelles notations ("Hardware description languages: voices from the Tower of Babel" [Lip77]) ont conduit à l'organisation d'un symposium international biennal appelé "Computer Hardware Description Languages and Their Applications" (1971), suivi d'un premier effort important de standardisation des CHDLs, réalisé par le groupe CONLAN [Pi183]. Indépendamment du projet CONLAN nous assistons à la création de nouveaux outils descriptifs de plus en plus variés et spécifiques [Mar79], [Paw81], [Bak83].

L'arrivée de la technologie VLSI, évènement capital pour l'évolution des CHDLs (surtout dans le domaine de la compilation en silicium) a provoqué de nouveaux efforts dont les résultats peuvent influencer sérieusement la conception du matériel informatique [Lieb83],[Dew83]. Dans ce cadre le langage VHDL (VHSIC Hardware Description Language) sa méthodologie et son environment représentent une entreprise sans précédent. Le tableau Tab.1.2. donne les informations caractèrisant les ambitions du projet VHDL par rapport aux quelques langages CHDL les plus connus aux Etats Unis. Dans ce tableau nous apercevons plusieurs paramètres d'un langage CHDL. Nous essaierons d'expliquer les plus signicatifs.

\* néologisme introduit en 1962 par Philippe Dreyfus et construit à partir des mots "information" et "automatique" [angl, data processing]

Projet LIDO Page 9

IMPLEMENTATION DETAILS OF HDL'S

| Language     | Reference  | Adapted from | Implemented<br>Machine | Implementation<br>Language |

|--------------|------------|--------------|------------------------|----------------------------|

| ACDL         | 9          | _            | ••                     |                            |

| AHPL         | 10-12      | APL          | CDC-6400               | SNOBOL                     |

|              |            |              | DEC-10                 | Fortran                    |

| ALERT        | 13-14      | APL          | 1BM 7094               |                            |

| APDL         | 15-16      | ALGOL        | CDC-G20                | ALGOL-60                   |

| APL          | 7          | _            | many                   | Assembly                   |

| APL+DS       | 17         | APL          |                        | -                          |

| CASD         | 18         | PL/1         | IBM 360                | PL/I                       |

| CASSANDRE    | 19         | ALGOL        | IBM 360,370            | Assembly                   |

| CDL          | 20-29      | ALGOL        | IBM 370                | Fortran Assembly           |

| CSL          | 30         | ALGOL        | IBM 370/155            | BCPL                       |

| DDL          | 31-39      | -            | Harris 6024/3          | -<br>-                     |

| DIGITEST II  | 40         | P1/1;        | 114(11) 0024/3         | _                          |

| DIGITED I II | 70         | petry Nets   | _                      | **                         |

| DIDL         | 41         | peny neis    |                        |                            |

| DSDL         | 42         | DDL          | 1BM 360                | -<br>XPL                   |

|              | 43         |              |                        | <del>-</del>               |

| FLOWWARE     | 43         | flowcharts   | IBM 360/50             | PL/1                       |

|              | 4.4        | CDL          | NOVA-800               | Nova Assembly              |

| FST          | 44         | -            | IBM 360                | Fortran IV                 |

| GLIDE        | 45         | -            | _                      | -                          |

| HARGOL       | 46         | ALGOL        | -                      | _                          |

| HILO         | 47         |              | ICL 1900               | -                          |

| ISP          |            |              |                        |                            |

| ISPL         | 48-54      | ALGOL        | PDP-10                 | BLISS                      |

| ISPS         |            |              |                        |                            |

| LALSD        | 55-57      | _            | IBM 360/91             | PL/1                       |

|              |            |              | CDC 6400               | SNOBOL                     |

| LASCAR       | 58         | CASSANDRE    | ***                    | _                          |

| LCD          | 59         | PL/1         | -                      | _                          |

| LDT          | 60         | RTL          | Burroughs              | ALGOL-58                   |

| LOGAL        | 61         | RTL          | UNIVAC 1108            | Fortran IV                 |

| LOTIS        | 62         | ALGOL        | -                      | -                          |

| MDL          | 63         | APL          | _                      | <u>-</u>                   |

| MODEL/LINDA  | 64         |              |                        | Ξ                          |

| OSM)         | 65         | _            | ODRA-1305              | PLAN                       |

| PMS          | 49         | ALGOL        | PDP-10                 | SNOBOL                     |

| -            | 6          | ALGOL        |                        | ALGOL                      |

| RTL          |            | -            | CDC1604                |                            |

| RTS I        | 66         | ALGOL        | Siemens 4004/151       | Fortran                    |

| RTS II       | 67-68      | RTS-I        | -                      | -                          |

| RTS III      | 69<br>30   | CDL,RTS II   | <b>-</b>               | -                          |

| SDL          | <b>7</b> 0 | RTL          |                        | -                          |

| SDL II       | 71         | ALGOL        | -                      | •                          |

| SDL          | 72         | -            |                        | -                          |

| SMITE        | 73         | -            | CYBER 174              | _                          |

| SSM          | 74         | -            | <del>-</del>           | -                          |

| VDL          | 75         | <del>-</del> | -                      | -                          |

| V-PMS        | 76         | PMS          | <del>-</del>           | -                          |

Notes: 1) "-" Indicates that the detail is either not available or not known.

2) No accuracy is claimed for the contents of this table.

Tab.1.1. Les langages "classiques" CHDLs et leurs implémentations

Page 10

| Features supported                                          | 101        | TI-HDL      | COL | AHPL | ZEUS     | CON-<br>LAN | TEGAS    | ISPS     | WHOL        |

|-------------------------------------------------------------|------------|-------------|-----|------|----------|-------------|----------|----------|-------------|

| Scope—range of hardware:                                    |            |             |     |      |          |             |          |          |             |

| Digital-systems design                                      | ×          | ×           |     | ×    | ×        | x           | X        | ×        | X           |

| Gate-level-design                                           | <b>X</b> . | X           | X   | ×    | ×        | ×           | x-       | X        | ×           |

| Digital-circuit design                                      |            |             |     |      |          |             |          |          |             |

| Combinational design<br>Synchronous design                  | ×          | x           | _   | x    |          | X           | ×        | x        | X           |

| Asynchronous design                                         | *          |             | ×   |      |          |             | X<br>X   |          | 1           |

| Mixed-mode design                                           |            | â           |     | •    |          | •           | ī        | •        | ž           |

| Management of design:                                       |            |             |     |      |          |             |          |          | <del></del> |

| Hierarchy                                                   | x          | x           |     | x    | x .      | -           | ×        | 1        |             |

| Modularity                                                  | ×          | ×           |     | x    | ×        | X           | ×        | ×        | ×           |

| Incremental compile                                         |            | x           |     |      | x        | ?           |          | •        | X           |

| Arbitrary decompose                                         | X          | ĸ           |     | X    | ×        | X           | X        | X        | X           |

| Libraries                                                   | X          | K           |     | X    | ×        | X           | X        | x        | X           |

| Data abstraction                                            |            |             |     |      | X        | ×           |          |          | ×           |

| User type conv                                              |            |             |     |      |          |             |          |          | X           |

| Alternate description<br>Reusable designs                   | x          | X           |     | x    | ×        | ×           | x        | x        | X-X         |

| Timing description:                                         |            | <u> </u>    |     |      |          |             |          | <u> </u> | <u> </u>    |

| Timing at all levels                                        | ×          | ×           | 63  | ×    | x        | ×           | <u> </u> | ×        |             |

| Specify timing data                                         | -          | ×           |     | ×    | _        | x           | x        | X        | X           |

| User-defined data                                           |            | ×           |     | x    |          | X           | I        |          | X           |

| Timing constraints                                          |            | ×           |     |      |          |             | x        |          | x           |

| Propagation delay                                           | X          | x           |     | ×    |          | x           | x        | X        | X           |

| Inertial and transport                                      |            |             |     |      |          |             |          |          | X           |

| Architectural description:                                  |            |             |     |      |          |             |          |          |             |

| Algorithmic description                                     | x          | x           |     | ×    | X        | X           | X        | X        | X           |

| Architectural description                                   | ×          |             | X   | ×    | ×        | x           | X        | X        | X           |

| Parallelism                                                 | ×          |             | X   | X    | X        | x           | 1        | X        | ×           |

| Control and data separate<br>Descriptive continuum          | x          |             | x   |      | ×        | ×           |          |          | x           |

| User assertions                                             |            |             |     |      | •        | ž           |          | x        | Ŷ           |

| Explicit structure                                          |            | ×           |     | ×    | ×        | ī           |          | -        | -           |

| Implicit structure                                          | x          | x           | z   | ×    | x        | X           | x        | ×        | X           |

| Generic components                                          |            | x           |     |      | ×        | x           | x        |          | X           |

| Regular structures                                          | X          | x           | X   | X    | ×        | X           | x        | ×        | X           |

| Recursive structures                                        |            |             |     | X    | <u>x</u> | ×           |          |          |             |

| Interlace description:                                      |            | <del></del> |     |      |          |             |          |          |             |

| Explicit interface                                          |            | ×           |     | X    | ×        | ×           | ×        | x        | ×           |

| Defined at all levels                                       | 62         | x           | N2  | X    | ×        | X           | ×        | x        | X           |

| Supports functional equiversity<br>Strongly typed interface | na         |             |     |      | x        | x           |          |          | X<br>X      |

|                                                             |            |             |     |      |          |             |          |          | <u> </u>    |

| Design environment:  Environment into                       |            |             |     |      |          |             |          | 3        |             |

| Language extensibility:                                     |            |             |     |      |          |             |          |          | <u> </u>    |

|                                                             |            | ·           |     |      |          |             |          |          | <u> </u>    |

| User-defined data types                                     |            |             |     |      | X        | ×           |          |          | X           |

| Design tool support<br>Multiple technologies                | ×          | x           |     | ×    | ×        | Z<br>Z      |          | x        | X           |

| Multiple methodologies                                      | ×          | ×           | -   | ž    | -        | ×           | -        | x        | î           |

|                                                             | <u> </u>   |             |     |      |          |             |          |          |             |

na--Not applicable: This feature is based upon another feature which the language does not support.

7. —We could not determine the language support for this feature.

Tab.1.2. Les paramètres du langage VHDL

#### Niveaux de description (scope - range of hardware)

Etant donné que les ordinateurs peuvent être conçus sur différents niveaux d'abstraction les langages CHDL peuvent être classés par rapport au niveau principal visé par leur utilisation:

- niveau des instructions

- niveau du transfert de registres

- niveau logique

Tout de suite il faut souligner qu'il n'existe pas de notation limitée exclusivement au niveau des instructions ou du transfert de registres. Un tel langage serait peu utile pour la description complète des fonctions et/ou des structures du matériel reél.

#### Types de description

Traditionnellement on distingue deux types de description [Bar75]:

- description procédurale

- description non-procédurale

Une description procédurale définit le fonctionnement d'une architecture du matériel de façon algorithmique. L'enchaînement des opérations y est indiqué par l'ordre typographique de la description. Les langages dits procéduraux sont dans la plupart des cas derivés de langages de programmation (p.e. AHDL), ou prévus pour la description du matériel au niveau des instructions (p.e. ISPS, LASCAR). Les langages non-procéduraux permettent de décrire un système matériel de façon typographiquement libre. Les liens entre les objets décrits sont établis à partir d'étiquettes d'activation (reste à résoudre le problème des opérations asynchronnes dont le déroulement réél est impliqué par l'ordre topologique). Ce type de description est préféré pour la spécification proche de la structure

Page 12

matérielle des ordinateurs (p.e. CDL, RTS I, CASSANDRE, OSM ...), ou pour la spécification des circuits au niveau logique (p.e. LALSD).

#### Aspects de description

Indépendamment du niveau de description ou du type de description un langage CHDL peut être adapté à un ou aux deux aspects de description:

- aspect fonctionnel

- aspect structurel

L'aspect fonctionnel est lié aux fonctions et aux opérations du matériel vues à partir des différents niveaux de conception. L'aspect structurel concerne la description des structures qui supportent différentes fonctions d'un système (p.e. registres, connecteurs, bus, portes logiques). Les structures décrites en langage de haut niveau de conception peuvent être dépourvues de fonctionnalités précises et interprétables, tel est le cas de la notation P-M-S (Processor-Memory-Switch) [Bell71], qui représente exclusivement des liens structurels entre les unités globales d'une organisation matérielle. L'aspect structurel est plus souvent lié aux spécifications de type non-procédural concernant le niveau transfert de registres et le niveau logique.

#### VLSI et CHDLs

L'arrivée des systèmes VLSI, intégrant dans un seul composant des dizaines ou des centaines de milliers d'éléments actifs, ouvre une nouvelle époque pour les CHDLs.

La nécessité d'une vérification fonctionnelle détaillée d'un système integré avant sa fabrication fait appel a des moyens symboliques tels que les langages CHDLs. Au même titre les langages pour la description deviennent des langages pour la conception du matériel intégré. Leur utilisation est obligatoire dans le

Frojet LIDO Fage 13

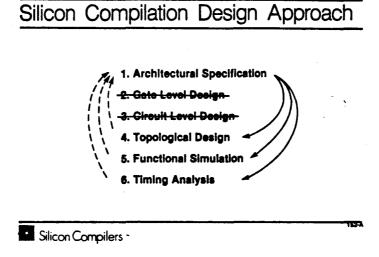

processus de synthèse automatique liée aux problèmes de compilation en silicium. Il existe deux manières d'attaquer ces nouveaux problèmes. La première consiste à adapter les anciennes notations en ajoutant de nouveaux niveaux de conception (p.e. niveau topologique). La deuxième solution c'est le développement d'une notation originale exploitant l'expérience accumulée par les concepteurs des systèmes VLSI. La première méthode à été utilisée par un certain nombre de chercheurs disposant d'une base logicielle (langages, simulateurs) datant des années soixantes et soixante-dix. Un des développements de cette méthode est l'extension du langage LALSD II vers un système multiniveaux permettant la simulation au niveau transfert de registres et au niveau logique [Su85]. Une autre extension multiniveaux beaucoup plus vaste est représentée par le système CASCADE [Bor85] dont les origines peuvent être facilement retrouvées dans les langages CASSANDRE et LASCAR (voir le tableau 1.1.). Parmi les développements plus récents, au premier plan se trouve le langage VHDL, au deuxième le langage ZEUS. Il faut toutefois souligner que l'arrivée de compilateurs en silicium, tels que GENESIL [Sil85], réalisés par les spécialistes de circuits integrés impose une nouvelle approche de la conception du matériel integré qui consiste à générer les descriptions topologiques directement à partir du niveau transfert de registres sans passer par le niveau logique et le niveau circuit.

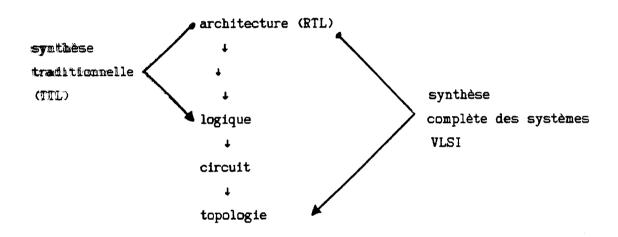

Fig.1.2. L'approche "directe" de la compilation en silicium utilisée dans le compilateur GENESIL.

Page 14 Projet LIDO

Argument principal utilisé en faveur de cette approche est le suivant:

A Typical Function Built from Gates or Unstructured Transistors Takes 2 to 10 Times More Transistors and Area than a Structured Design

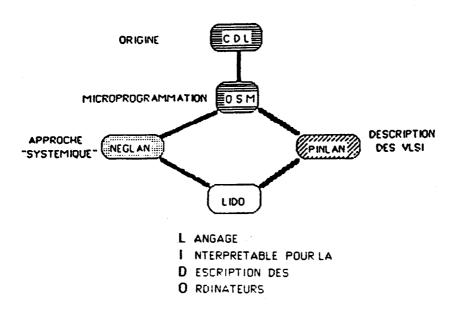

Notre proposition s'aligne sur cette dernière tendance et par ailleurs trouve ses origines dans la suite des langages CHDLs issue de la notation CDL. Cette suite de développements est illustrée ci-dessous.

#### ORIGINES DU LANGAGE LIDO

Fig.1.3. Les origines du langage LIDO (Langage Interprétable pour la Description des Ordinateurs).

Le langage CDL est reconu comme prototype des langages RTL non-procéduraux [Chu65]. L'un de ses descendants, le langage OSM [Mar75] à été développé à l'Académie Polonaise des Sciences afin de modéliser de gros ordinateurs au contrôle microprogrammé (p.e. IBM 370/158). Les descriptions en langage OSM sont simulées par les systèmes de simulation 3SM [Mar75] et 3SM-K [Bak78]. Par rapport au CDL, le langage OSM a une structure modulaire et se caractèrise par l'utilisation intensive de graphes de contrôle. Le développement du langage NEGLAN [Bak83] marque la première étape vers la description systémique du matériel informatique. Son but principal est de décrire le fonctionnement du matériel de façon "libre" et naturellement active. Cette possibilité est liée à l'introduction du contrôle négatif qui permet d'inhiber les "normalement actives". Le langage NEGLAN est simulé par le système MAMAYA étudiants Polytechnique implémenté par les de 1'Ecole (implémentation en PASCAL). Une autre forme de développement a été exprimée par le langage PINLAN [Mar79] destiné à la description comportementale (entrées + sorties, PINS ) des systèmes LSI.

La richesse des résultats et des expériences acquises pendant le développement et l'implémentation des langages cités a permis de concevoir et de réaliser le langage et le système LIDO, qui font respectivement l'objet de la deuxième et de la troisième partie de ce mémoire. Ici nous nous limiterons à quelques remarques essentielles concernant le langage LIDO qui permet:

- la description systémique du matériel

- la description orientée VLSI

- la description des architectures évoluées

#### Description systémique

Le langage LIDO permet de décrire le matériel informatique de façon largement non-procédurale et basée sur le concept de systèmes ouverts emprunté à la systémique. Dans ce cadre conceptuel le matériel à décrire est considéré comme l'ensemble des objets "normalement actifs" ou "normalement inactifs". De plus on impose une hiérarchie fonctionnelle et structurelle découpant des systèmes

Page 16 Projet LIDO

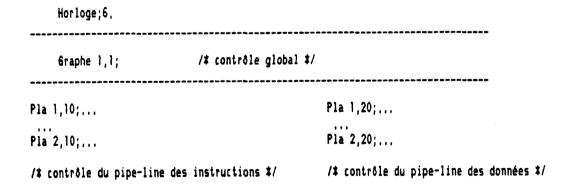

complexes en plusieurs couches, chacune correspondant à un niveau d'informations traitées par le système. Les couches (strata) de caractère global sont exprimées par différentes constructions telles que:

A l'exclusion de l'horloge, qui est un mécanisme unique pour chaque description, les autres mécanismes sont multiples et étalés sur plusieurs niveaux locaux. De cette façon on dispose d'arrays de graphes, d'arrays de matrices logiques de différentes sortes, et d'arrays d'unités fonctionnelles.

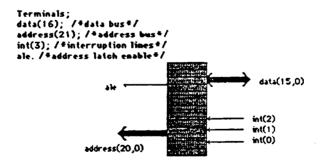

La communication entre différents niveaux systémiques et à l'interieur d'un même niveau peut se faire à l'aide de différents types de porteurs d'informations tels que:

- les connecteurs

- les terminaux

- les registres

Les connecteurs permettent de définir la communication asynchronne (endochronne), les registres la communication synchronne et/ou contrôlée, les terminaux peuvent participer dans les deux types de communication.

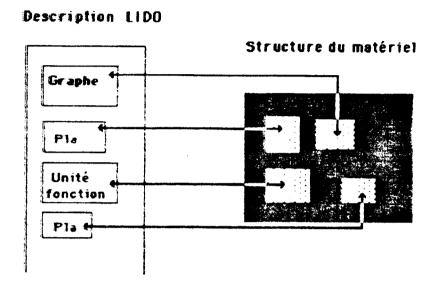

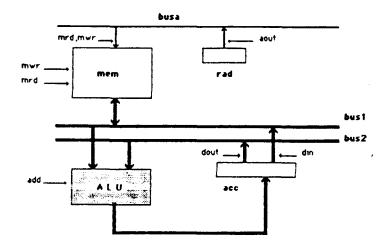

Tous ces moyens pris ensemble donnent au concepteur de matériel la possibilité de "bijection" entre la description d'un système et le système lui même de telle manière qu'à chaque unité décrite en langage LIDO correspond une unité topologique d'un système réél. De plus, chaque description peut être modifiée

Projet LIDO Fage 17

(recablée) ou étendue d'une manière totalement libre, correspondant à la manière dont on recompose ou augmente une structure matérielle réelle.

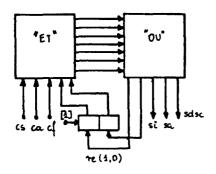

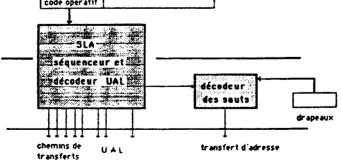

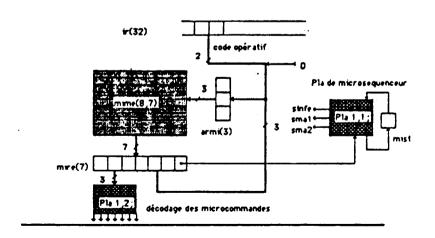

Fig.1.4. La "bijection" entre une description en langage LIDO et la structure materielle réelle.

#### Description orientee WASI

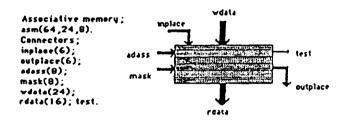

L'utilisation du langage pour la conception de l'architecture moderne dans le cadre de la compilation en silicium oblige à introduire des mécanismes correspondant aux sous-systèmes topologiques des systèmes VLSI. Parmi ces mécanismes on trouve toutes les structures géométriquement régulières, telles que les métaires ROM, RAM, les matrices PLA, SLA et NGA. Le langage LIDO offre ces structures comme constructions de base.

Page 18 Frojet LIDO

#### Description des architectures évoluées

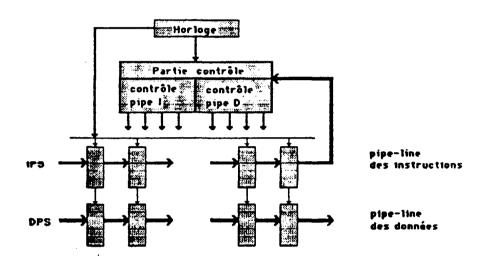

La comlexité des systèmes VLSI et bientôt des systèmes ULSI dépassa largement la complexité d'une UAL (l'exemple usé d'echantillonage de langages CHDLs) ou d'un processeur simple de type von Neumann. Les systèmes à plusieurs unités de traitement, multiprocesseurs, architecture pipe-line et data-flow, deviennent accessibles aux concepteurs de circuits intégrés.

Un langage qui suit, ou mieux, anticipe de nouvelles architectures, doit permettre leur description. L'utilisation de mécanismes multiples ("arrays" de mécanismes - graphes, matrices logiques, unités fonctionnelles) en langage LIDO assure cette possibilité. De plus, l'introduction de mémoires associatives comme porteurs primitifs d'informations facilite les spécifications des machines disposant de mémoires virtuelles et des machines data-flow dont l'unité "matching unit" nécessite une recherche associative des arguments prêts à éxécuter.

#### 3. L'analyse et la synthèse de l'architecture du matériel

Les modèles et ensuite les langages pour la description de l'architecture des ordinateurs constituent les points de départ pour l'analyse et la synthèse du matériel informatique. L'analyse fonctionnelle du matériel décrit en CHDLs représente l'un des principaux objectifs pour la conception de nouvelles architectures. Malgré le nombre important de langages CHDL le nombre d'implémentations (compilateurs, simulateurs, interpréteurs) est relativement limité. Parmi les implémentations les plus connues on trouve celles des langages CDL [Bara75], DDL [Diet75], AHPL [Swa77], ISPS [Bar81], CASSANDRE [Mer73], OSM [Mar75], RTS I [Pi174], et plus récamment LALSD II [Su85], LASCAR [Bor78], HSL-FX [Hos85].

La grande majorité des simulateurs est basée sur la compilation du langage source, ou sur l'interprétation d'une forme intermédiaire, précompilée, de description. Presque tous ont été conçus avant l'époque des systèmes VLSI.

Projet LIDO Page 19

L'arrivée de nouvelles possibilités techniques liées à l'intégration à très haute échelle, a imposé aux concepteurs des CHDLs de nouveaux objectifs et de nouvelles contraintes. Un de ces objectifs est la synthèse automatisée ou automatique des circuits VLSI à partir d'une description architecturale. Cette synthèse, qui implique une nouvelle dimension à savoir la topologie, est radicalement différente de celle ancienne limitée à la transformation architecture -> portes logiques. Malgré ce changement d'objectif la plupart des systèmes visés pour le développement du matériel intégré restent dans le cadre traditionnel et sont complétés par deux niveaux de conception : circuit et topologie.

Fig.15. La synthèse traditionnelle et moderne du matériel informatique.

Les systèmes CASCADE, VLSI-DE, HSL-FH peuvent servir d'exemples. Une stratégie alternative a été adoptée et réalisée par les concepteurs du système GENESIL. Flle consiste à générer la topologie d'un système VLSI directement à partir d'une description détaillée au niveau transfert de registres. La "compilation directe" des descriptions détaillées RTL a permis de simplifier le processus de synthèse en évitant une grande partie des problèmes liés à l'interfaçage entre différents miveaux de conception. Il est quand même nécessaire de souligner que

Page 20 Projet LIDO

la description initiale d'un circuit à compiler doit être très précise et détaillée.

description structurelle, détaillée au niveau transfert de registres

+

#### COMPILATION en SILICIUM

1

sous-systèmes topologiques d'un système VLSI

Fig.1.6. La compilation "directe" d'une description RTL en silicium.

Ci-dessous nous présentons une liste d'objets (fonctions) utilisés à l'entrée du GENESIL (Genesil Function Set).

| The Designer's     | Vocabulary                            |

|--------------------|---------------------------------------|

| • Memory:          | RAM, ROM, FIFO, Stack                 |

| • Complex Logic:   | PLA, Decode, Encode                   |

| Datapath:          | ALU, Counter, Comparator, Shifter     |

| • PADS:            | Input, Output, Clock,<br>Synchronizer |

| • Random Logic:    | Gates, Flip Flops                     |

| • Test Structures: | Scan Path, LSSD                       |

| Skon Compilers     | 47                                    |

Fig.1.7. La liste d'objets (fonctions) disponibles à l'entrée du GENESIL

Projet LIDO Fage 21

la description initiale d'un circuit à compiler doit être très précise et détaillée.

description structurelle, détaillée au niveau transfert de registres

.

COMPILATION en SILICIUM

,

sous-systèmes topologiques d'un système VLSI

Fig.1.6. La compilation "directe" d'une description RTL en silicium.

Ci-dessous nous présentons une liste d'objets (fonctions) utilisés à l'entrée du GENESIL (Genesil Function Set).

Fig.1.7. La liste d'objets (fonctions) disponibles à l'entrée du GENESIL

Projet LIDO Page 21

La nécessité, pour un compilateur en silicium de type GENESIL, de fournir une description structurelle et détaillée au niveau transfert de registres, restreinte aux primitifs fortement typés, limite de façon significative l'espace et la flexibilité de conception offerts à l'utilisateur. D'où la nécessité, soulignée même par les réalisateurs de compilateur GENESIL, d'un préprocesseur travaillant à partir d'une spécification textuelle et assurant un grand espace de conception.

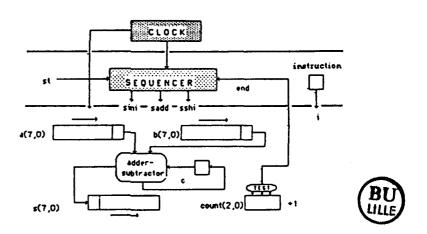

Le système LIDO a été conçu afin de remplir cette tâche. Il permet de concevoir une vaste gamme d'architectures incluant des machines SISD, SIMD, MIMD, pipeline et data-flow, orientées vers les systèmes VLSI.

Les trois rôles principaux du système LIDO sont les suivants:

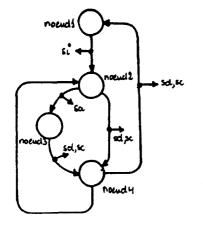

- interprétation symbolique (analyse symbolique)

- interprétation "profonde" (analyse détaillée)

- synthèse automatique des chemins de contrôle

L'interprétation symbolique, dans le contexte systémique, consiste à générer des traces d'activation des chemins de données ("flux des structures") sans la visualisation des contenus des porteurs d'informations.

Ce style d'interprétation libère le concepteur de l'analyse détaillée des résultats du traitement des données [Mil85]. L'interprétation "profonde", seule possibilité de travail envisagée dans les simulateurs traditionnels (CDL, CASSANDRE, OSN,...), implique l'éxécution détaillée des opérations activées pendant les processus d'interprétation (simulation), ce qui permet, mais en même temps rend obligatoire, la génération de traces d'interprétation pour différents jeux de données. Il nous semble important de souligner, que seul le choix de l'interprétation directe", mode de travail du système LIDO, permet de résoudre de façon simple le problème d'accès à la description source, qui est indispensable dans le processus de l'interprétation symbolique.

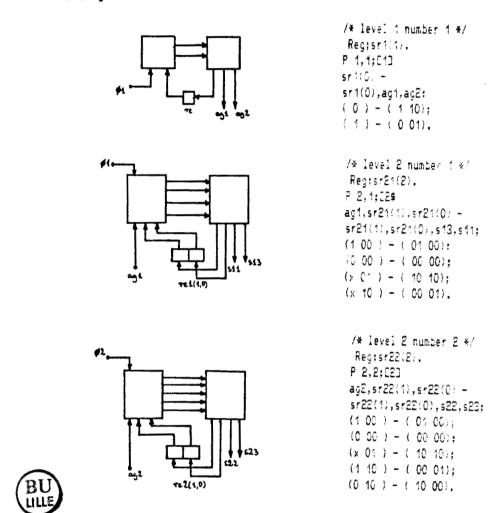

La synthèse automatique des chemins de contrôle consiste à transformer leur description fonctionnelle exprimée par les graphes de contrôle en description structurelle exprimée par les matrices logiques. Etant donné que les graphes et les matrices logiques appartiennent aux constructions de base du langage LIDO,

Fage 22 Projet LIDO

les transformations graphes  $\rightarrow$  matrices logiques préservent l'intégrité des descriptions, ce qui assure la possibilité d'interprétation des descriptions structurelles et des descriptions fonctionnelles. La synthèse automatique des descriptions structurelles optimisées est l'objectif principal visé dans le développement des futurs versions du système LIDO.

L'un de nos soucis principaux, lors de l'élaboration du système LIDO, a été d'offrir à l'utilisateur un outil simple et intégré, dont l'apprentissage soit une question de quelques heures. D'un autre côté nous voulions utiliser de la façon la plus large possible l'approche systémique, qui à notre avis, peut faciliter la tâche de compréhension et de création d'architectures matérielles de plus en plus complexes.

#### Une réflexion sur l'approche systémique

Il nous semble nécessaire de remarquer que l'approche systémique ne doit pas être considerée comme une "science", une "thèorie" ou une "discipline", mais comme une méthodologie permettant d'englober la totalité des éléments du système étudié, ainsi que leurs interactions et leurs interdépendances. L'approche systémique n'a rien avoir avec une approche systématique, qui consiste à aborder un problème ou à effectuer une série d'actions de manière séquentielle et détaillée.

Il faut également souligner que l'approche systémique et le terme systémique utilisés dans notre mémoire n'impliquent ni de nouveaux éléments ni de nouvelles architectures, ni même de nouveaux domaines de recherche. Ils permettent exclusivement d'organiser notre connaissance et d'exprimer notre point de vue de façon plus efficace et mieux adaptée à notre but principal, qui est la maîtrise de la complexité fonctionnelle et structurelle du matériel informatique.

Projet LIDO Fage 23

# LA FORMATIQUE DU MATERIEL INFORMATIQUE

Une approche systémique et morphologique de l'architecture des systémes matériels

Cette partie du mémoire a été présentée pendant la conference: IFIF WG10.1 Vorking Conference on Methodologies for Computer System Design, Lille, 15-17 Septembre 1983

#### TABLE DES MATIERES

- 1. Introduction

- 2. Formes élémentaires composants de premier ordre

- 2.1. Composants transitifs 1FT

- 2.2. Composants mémorisants 'Fm

- 2.3. Composants générateurs 1FG

- 2.4. Composants mémorisants-transitifs 'F(MT)

- 3. Formes de deuxième ordre

- 3.1. Formes transitives 2F2T

- 3.2. Formes transitives-mémorisantes 2FTM

- 3.3. Formes transitives/mémorisantes-transitives 2FT(MT)

- 3.4. Formes génératrices

- 3.5. Formes transitives-génératrices/mémorisantes-transitives 2F(TG)(MT)

- 4. Formes de troisième ordre

- 4.1. Formes \*F2gcmT>

- 4.2. Formes \*F2GT

- 4.3. Formes \*Ferents

- 4.4. Formes \*Facmtot

- 4.5. Formes \*Ferents

- 4.6. Formes à rétroaction 3Fg2(MT) et 3FgT(MT)

- 5. Formes de quatrième ordre

- 5.1. Formes 4F2G(MT)T

- 5.2. Formes 4F2GT(MT)

- 5.3. Formes 4F2G2(MT)

- 5.4. Formes 4Fechtotemto

- 6. Formes de cinquième ordre

- 6.1. Formes Fraggetemts

- 6.2. Formes \*F(GT)(MT)2T(MT)

- 7. Remarque finale

II. APPROCHE SYSTEMIQUE ET "MORPHOLOGIQUE" DE LA COMPLEXITE DE L'ARCHITECTURE MATERIELLE DES ORDINATEURS

#### 1. Introduction

Le chapitre présent est consacré à la modélisation globale et systémique de l'architecture matérielle. Cette approche orientée vers le problème de la complexité fonctionnelle et structurelle du matériel nous donne la base conceptuelle utilisée par la suite pour la description, l'analyse et la synthèse des architectures detaillées. A côté de termes tels que : fonction, structure, système, et hiérarchie, nous utilisons très fréquemment les termes "forme" et "sélection". La forme signifie pour nous la structure matérielle qui conduit, mémorise ou "trans-forme" l'"in-form-ation" présente à son entrée. Ces trois fonctions se réalisent, dans notre approche, à l'aide d'une seule opération : la sélection.

La "super-position" des formes simples est étroitement liée à la superposition ou à la hiérarchisation des différentes sortes d'information (l'alimentation, les données, les adresses, les signaux de contrôle, les signaux de synchronisation). D'où les notions de "complexité hiérarchisée", de "formes d'ordre supérieur" et de "niveaux systémiques".

Dans ce chapitre, à partir de formes simples nous établirons plusieurs modèles complexes de l'architecture du matériel. Toutefois, ces modèles réprésentent les structures et les fonctionnements des systèmes digitaux de façon largement globale sans donner leur interprétation détaillée. La spécification détaillée des mêmes modèles globaux fera l'objet du chapitre suivant dans lequel nous présenterons le langage LIDO et ses applications. Ici nous allons d'abord présenter les formes ou composants élémentaires du matériel informatique. Ces formes de base transforment, mémorisent et génèrent des informations de nature différente: données, adresses, codes opératifs, phases, etc...

Chaque sous-chapitre est successivement consacré à la présentation de systèmes à deux, trois, quatre puis cinq niveaux de complexité systémique. Les systèmes à

Projet LIDO Page 27

plusieurs niveaux de complexité peuvent exécuter un grand nombre de processus (instructions) basés sur un même ensemble de formes de traitement. Les systèmes (formes d'ordre supérieur à un) choisis comme exemples sont représentatifs des principaux schémas fonctionnels et structurels du matériel informatique.

Page 28 Frojet LIDO

### NOTATIONS

Sélection positive globale (contrôle positif) :

$$\mathbf{I} \Leftarrow \mathbf{I}^{1-\mathbf{i}} \Leftarrow \mathbf{I}^{1-\mathbf{i}} \mathsf{K} = \mathbf{I}^{\mathbf{i}}$$

Sélection négative globale (contrôle négatif) :

$$i_{I} \approx |i-1|_{I} \Rightarrow |i-1|_{F} \Rightarrow I$$

Sélection positive/négative globale (contrôle positif/négatif) :

$$i_{I} \approx |i^{-1}_{I}| \Rightarrow |i^{-1}_{F}| \Rightarrow I$$

Rétroaction du niveau i-l vers le niveau i :

O<sub>I</sub> - Information globale d'ordre zéro (l'influx d'énergie)

i I - Information globale d'ordre i

OF - Forme globale d'ordre zéro (connecteurs)

i<sub>F</sub> - Forme globale d'ordre i

j/i - Information d'ordre global i et d'ordre local j

j/iF - Forme d'ordre global i et d'ordre local j

$i_{I \rightarrow j}$   $i^{-1}_{I \rightarrow j}$   $i^{-1}_{F \rightarrow j}$   $F \rightarrow I$ Emergence de forme

d'ordre de complexité

supérieur

### 2. Formes élémentaires - composants de premier ordre

Les processus et les systèmes que nous allons étudier sont composés de différents types de composants ou formes élémentaires. Tous ces composants sont considérés comme des éléments de premier ordre fonctionnel et structurel, même si dans leur réalisation il est possible d'utiliser des fonctions et des circuits logiques d'ordre supérieur à un. Cela signifie que l'on distingue deux ordres d'informations : l'information d'ordre zéro - OI (influx d'énergie), et l'information d'ordre un - II, traitée par les composants. Le caractère global de ces composants signifie d'autre part que nous allons considérer l'information qui entre et qui sort des composants comme une information codée le plus souvent sur plusieurs bits.

- Il y a trois types de composants :

- formes élémentaires transitives composants transitifs,

- formes élémentaires mémorisantes composants mémorisants,

- formes élémentaires génératrices composants générateurs.

## 2.1. Composants transitifs - 1FT

Les composants transitifs sont des formes de premier ordre qui transforment l'information à l'entrée -  $^1$ I par l'intermédiaire de l'information d'ordre zéro -  $^0$ I en information à la sortie -  $^{\rm I}$ S

Représentation textuelle :

$${}^{1}F_{T}[{}^{1}I, {}^{0}I] = {}^{1}I \Rightarrow {}^{1}I \Rightarrow {}^{0}I \Rightarrow {}^{0}F \Rightarrow I_{S}$$

après émergence :

$${}^{1}F_{T}[{}^{1}I] = {}^{1}I \Rightarrow F_{T} \Rightarrow I_{S} \text{ avec } {}^{1}I \neq I_{S}$$

Représentation graphique :

Interprétation :

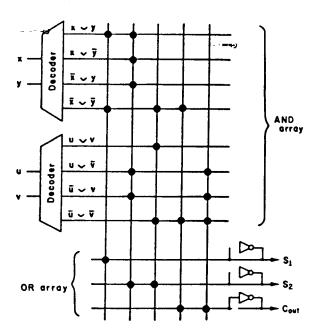

Les composants transitifs représentent une grande classe de

fonctions et de circuits combinatoires utilisés pour la transformation de l'information numérique et non-numérique. Parmi eux nous pouvons distinguer des struct@res spécialisées comme les additionneurs et les comparateurs, et des structures universelles comme les "mémoires" ROM et les matrices logiques PLA. Les structures de l'additionneur et du comparateur exécutent une seule fonction. Ce sont les formes irrégulières et non redontantes qui "performent" les fonctions régulières. Par contre les structures ROM et PLA sont destinées à exécuter une fonction parmi plusieurs possibles. Le choix des fonctions est limité par les dimensions des formes régulières, mais la fonction choisie peut être totalement irrégulière.

## 2.2. Composants mémorisants - 1FM

Les composants mémorisants sont des formes de premier ordre qui mémorisent l'information introduite à l'entrée - l par l'intermédiaire de l'influx d'énergie qu'est l'information d'ordre zéro - l. Les composants mémorisants ne transforment pas l'information, ils se contentent de la conserver. Cette conservation est due aux boucles rétroactives positives alimentées par l'influx d'énergie.

après émergence :

$${}^{1}F_{M}[^{1}I] = {}^{1}I \Rightarrow F_{M} \Rightarrow I_{S}$$

avec  ${}^{1}I = I_{S}$

Représentation graphique :

### Interprétation :

Les composants mémorisants constituent une grande classe d'éléments-mémoire dans lesquels on enregistre une information soit à un bit, soit à plusieurs bits. Comme composants mémorisants existent les bascules et les registres, les deux étant des formes de premier ordre. Les contenus des registres et des bascules représentent les états de l'information, c'est-à-dire les états de fonctionnement du système informatique.

### 2.3. Composants générateurs - 1FG

Les composants générateurs sont des formes de premier ordre qui génèrent l'information exclusivement à partir de l'influx d'énergie (ou information d'ordre zéro –  $^{0}$ I). La génération de l'information est due aux boucles rétroactives négatives. Le délai de la rétroaction implique la fréquence des oscillations caractéristique d'un générateur donné.

Représentation textuelle :

après émergence :

Représentation graphique :

### Interprétation :

Tous les circuits générateurs de signaux de synchronisation, autrement dit tous les circuits générateurs d'impulsions de cadencement, sont des composants générateurs. Ils contiennent des boucles de rétroaction négatives alimentées par un influx d'énergie. La fréquence des oscillations

Page 32 Projet LIDO

dépend soit des capacités et des résistances internes des circuits, soit d'éléments spéciaux comme le quartz.

## 2.4. Composants mémorisants-transitifs - 1 FMT

Les connections des composants mémorisants-transitifs forment la base des transformations de l'information mémorisée. Ce type de transformation est largement utilisé dans les systèmes informatiques car il permet d'enchaîner en séquences plusieurs fonctions, ce qui donne les processus. Les connections des composants mémorisants et transitifs se retrouvent sur tous les niveaux de complexité qui possèdent leurs propres états de fonctionnement.

Représentation textuelle :

$${}^{1}F_{MT}[{}^{1}I, {}^{0}I] = {}^{1}I \Rightarrow {}^{0}I \Rightarrow {}^{0}F \Rightarrow {}^{1}I \Rightarrow {}^{0}F \Rightarrow {}^{I}I \Rightarrow {$$

$${}^{1}F_{MT}[^{1}I] - {}^{1}I \Rightarrow F_{T} \Rightarrow {}^{1}I \Rightarrow F_{M} \Rightarrow \dots \Rightarrow I_{S}$$

$${}^{1}F_{MT}[{}^{1}I] - {}^{1}I \Rightarrow F_{MT} \Rightarrow I_{S}$$

Représentation graphique :

Interprétation :

Les connections des formes mémorisantes-transitives constituent des ensembles opérateurs qui transforment et mémorisent l'information. Au niveau d'une horloge multiphase les composants sont utilisés pour l'enchaînement et la mémorisation de plusieurs phases dans un cycle d'horloge. Au niveau d'un séquenceur les composants mémorisants et transitifs sont connectés afin de produire différentes séquences de signaux. Enfin, au niveau terminal de traitement les composants mémorisants-transitifs enchaînent les flux de données traitées de façon séquentielle.

### 3. Les formes de deuxième ordre

Les formes de deuxième ordre de complexité possèdent deux niveaux systémiques : le contenu, état fonctionnel de niveau supérieur qui par les opérateurs-sélecteurs définit la structure de niveau inférieur. Ces deux niveaus systémiques sont construits à partir de différents types de composants, ce qui donne différents systèmes de deuxième ordre qui "performent" différents types de prosessus.

## 3.1. Formes transitives de deuxième ordre - <sup>2</sup>F<sub>TT</sub>

Dans les formes transitives de deuxième ordre les composants transitifs sont superposés. On obtient ainsi deux niveaux systémiques de complexité et de multiplexité. Le niveau supérieur est géré par l'information d'ordre global deux –  $^2$ I, le niveau inférieur par l'information d'ordre global un –  $^1$ I.

a) Représentation textuelle après émergence (suppression de l'information-énergie  $^{0}$  I) :

$${}^{2}F_{TT}[{}^{2}I, {}^{1}I] = {}^{1/2}I \Rightarrow {}^{1/2}F_{T} \Rightarrow {}^{2}I \Rightarrow {}^{1}I \Rightarrow {}^{1}F_{T} \Rightarrow I_{S}$$

b)Représentation textuelle avec macro-sélection (contrôle) négative et positive (⇒) :

$$^{2}F_{TT}[^{2}I,^{1}I] \Rightarrow ^{1/2}I \Rightarrow ^{1/2}F_{T} \Rightarrow ^{2}I \Rightarrow ^{1}I \Rightarrow ^{1}F_{T} \Rightarrow I_{S}$$

La formule a ne concerne que la sélection "positive", c'est-à-dire celle dont les valeurs d'information de deuxième ordre spécifient les formes de premier ordre à sélectionner. Losqu'on veut utiliser la sélection "négative" il est néces-saire d'introduire la formule b qui comporte des sélecteurs négatifs.

### Représentation graphique :

où  $\Rightarrow$  - ensemble des opérateurs de sélection positifs et/ou négatifs.

### Interprétation :

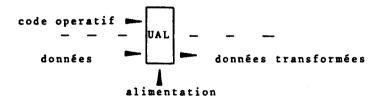

Les formes transitives de deuxième ordre constituent une classe de circuits combinatoires complexes qui éxécutent différentes fonctions choisies par le niveau supérieur de complexité. Simultanément peuvent être exécutées plusieurs fonctions parallèles ou enchaînées. Le parallèlisme, ou consécutivité des fonctions exécutées, dépend de la disposition spatiale des structures sélectionnées.

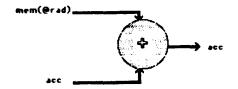

Parmi les formes transitives de deuxième ordre les plus connues nous trouvons les unités arithmétiques et logiques dans lesquelles le même ensemble de composants transitifs est utilisé pour exécuter plusieurs fonctions différentes. Chaque unité fonctionnelle qui ne contient pas de composant mémorisant et qui "donne" plusieurs fonctions, constitue une structure transitive de deuxième ordre.

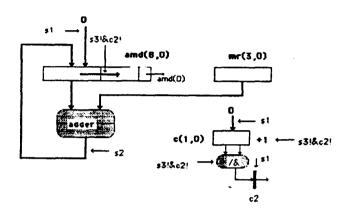

Unité arithmétique et logique :

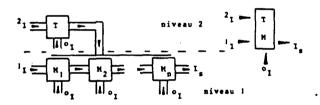

## 3.2. Formes transitives/mémorisantes de deuxième ordre - 2FTM

Les formes <sup>2</sup>F<sub>TM</sub> de deuxième ordre constituent de "vraies" mémoires dans lesquelles on peut stocker et extraire de l'information de premier ordre - <sup>1</sup>I. Les composants mémorisants forment le niveau inférieur de complexité, les composants transitifs le niveau supérieur. L'information de niveau supérieur - <sup>2</sup>I - sélectionne les composants mémorisants de niveau inférieur.

Représentation textuelle :

$${}^{2}F_{TM}[{}^{2}I, {}^{1}I] = {}^{1/2}I \Rightarrow {}^{1/2}F_{T} \Rightarrow {}^{2}I \Rightarrow {}^{1}I \Rightarrow {}^{1}F_{M} \Rightarrow I_{S}$$

Représentation graphique :

où \_\_\_\_ - ensemble des opérateurs-sélecteurs qui sélectionnent les structures subordonnées.

### Interprétation :

Les formes transitives/mémorisantes de deuxième ordre constituent des ensembles de composants qui mémorisent plusieurs valeurs de variables considérées comme l'information de premier ordre. L'information de deuxième ordre peut être conçue comme des adresses de composants mémorisants formant le niveau inférieur de complexité. Dans le cas de la mémoire à écriture et à lecture les composants mémorisants (M<sub>1</sub>..M<sub>n</sub>) sont intégrés et on ne peut accéder qu'à un seul de ces composants à la fois, en conséquence qu'à une seule information. Dans le cas des registres ou des bascules les composants mémorisants sont distribués

et il est possible de sélectionner, par une seule valeur d'information de deuxième ordre, plusieurs registres et/ou bascules simultanément.

Dans ces deux cas nous utilisons la sélection spatiale des composants mémorisants.

où RWM - Read Write Memory.

# 3.3. Formes transitives/mémorisantes-transitives de deuxième ordre - 2F T(MT)

Les formes  $^2F_{T(MT)}$  de deuxième ordre forment deux niveaux de complexité. Au niveau inférieur nous trouvons les composants mémorisants-transitifs, au niveau supérieur les composants transitifs. L'information de deuxième ordre sélectionne aussi bien les composants mémorisants que les composants transitifs. Ce qui permet d'enregistrer l'information transformée par le système.

Représentation textuelle :

$${}^{2}F_{T(MT)}[^{2}I,^{1}I] = {}^{1/2}I \Rightarrow {}^{1/2}F_{T} \Rightarrow {}^{2}I \Rightarrow {}^{1}I \Rightarrow {}^{1}F_{MT} \Rightarrow I_{S}$$

avec la sélection (contrôle) positive et négative :

$${}^{2}F_{T(MT)}[^{2}I,^{1}I] = {}^{1/2}I \Rightarrow {}^{1/2}F_{T} \Rightarrow {}^{2}I \Rightarrow {}^{1}I \Rightarrow {}^{1}F_{MT} \Rightarrow I_{S}$$

Fage 37

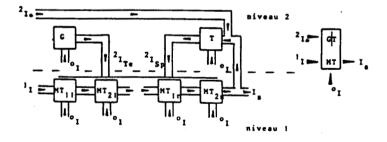

### Représentation graphique :

## 3.4. Formes génératrices de deuxième ordre - <sup>2</sup>F<sub>2G</sub>

Les formes génératrices de deuxième ordre forment deux niveaux de complexité. Le niveau inférieur comporte les composants mémorisants-transitifs, et le niveau supérieur un composant générateur. L'information générée par ces systèmes de deuxième ordre n'est influencée par aucune information entrante, sa-f par l'influx d'énergie, c'est-à-dire l'information d'ordre zéro.

Il faut souligner que la sélection des formes mémorisantes-transitives a un caractère temporel du fait qu'elle est utilisée pour la production des séquences de fonctions.

Représentation textuelle :

Page 38 Projet LIDO

#### Représentation graphique :

où <sup>2</sup>I<sub>S</sub> - l'information générée par le composant générateur au niveau 2,

I<sub>S</sub> - l'information sortante recyclée au niveau 1.

### Interprétation :

Les formes génératrices de deuxième ordre sont des systèmes multiphases utilisés comme horloges dans le matériel informatique. En principe ces systèmes ne sont pas contrôlés par des signaux externes, la seule entrée étant l'alimentation.

## 3.5. Formes transitives-génératrices/mémorisantes-transitives $\frac{2}{F}$ (TG) (MT)

Les formes  $^2F_{(TG)(MT)}$  de deuxième ordre alors même qu'elles sont identiques aux formes génératrices  $^2F_G$  par leur type de composants, sont complètement différentes par la nature de l'information qu'elles traitent. On peut les considérer comme les systèmes les plus simples de traitement de l'information du fait qu'elles emploient à la fois la sélection temporelle et la sélection spatiale des formes qui constituent le niveau inférieur du système.

a) Représentation textuelle sans rétroaction :

$${}^{2}_{F_{(TG)(MT)}[^{2}I,^{1}I]} = {}^{1/2}I \Rightarrow {}^{1/2}_{F_{T}} \Rightarrow {}^{2}I_{Sp} \Rightarrow {}^{1}_{I} \Rightarrow {}^{1}_{F_{MT}} \Rightarrow I_{S}$$

$${}^{1/2}_{F_{G}} \Rightarrow {}^{2}I_{Te} \Rightarrow {}^{1}_{I} \Rightarrow {}^{1}_{F_{MT}} \Rightarrow I_{S}$$

où  $^2I_{Sp}$  - information de la sélection spatiale,  $^2I_{Te}$  - information de la sélection temporelle.

b) Représentation textuelle avec rétroaction (du niveau l vers le niveau 2) :

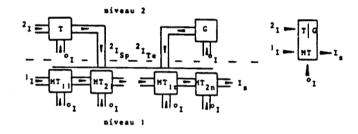

a) Représentation graphique de  ${}^2F_{(TG)(MT)}$  sans rétroaction :

- où 2 I Sp | | | | | 2 I Te la sélection combinée par l'information entrante pour la sélection spatiale, et par l'information générée pour la sélection temporelle.

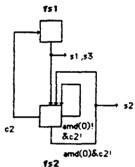

- b) Représentation graphique de  ${}^2F_{(TG)(MT)}$  avec rétroaction :

où la boucle de rétroaction introduit l'"autosélection" par le contenu des composants subordonnés MT11..MT2n.

#### Interprétation:

Les formes transitives-génératrices/mémorisantes-transitives sont capables d'exécuter plusieurs processus différents. Les rudiments de séquencement (deux états) sont assurés par le composant générateur et la sélection temporelle. La base de la variété fonctionnelle est donnée par la sélection spatiale, précédée éventuellement par la transformation des signaux de la sélection spatiale  $^2\mathrm{I}_{\mathrm{Sn}}$ .

La forme transitive-génératrice/mémorisante de type a permet d'exécuter plusieurs processus différents, chacun étant une composition de plusieurs fonctions. Chaque séquencement interne est réduit à deux phases. Le choix des fonctions, et par là même des processus, est effectué par l'information extérieure de deuxième ordre. Ce type de forme n'est pas capable de "mémoriser" les séquences de fonctions. Il n'est pas "auto-commandé".

La forme  $^2F_{(TG)(MT)}$  de type b comporte une boucle de rétroaction. Cette boucle transporte l'information de niveau inférieur afin de sélectionner, à la phase suivante du fonctionnement, un ou plusieurs composants mémorisants-transitifs du même niveau. Cette forme est "auto-commandée", ce qui permet de construire des processus à plusieurs phases à l'intérieur du système. Ces processus peuvent être "modifiés" ou "choisis" par l'information extérieure de deuxième ordre.

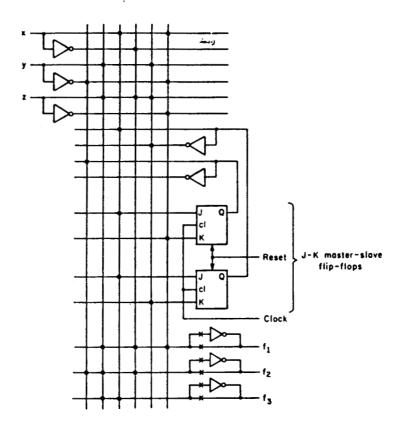

La nature des processus peut être différente. Nous ici en évoquer deux types :

- 1) les processus de séquencement caractéristiques de la partie contrôle des processeurs informatiques,

- 2) Les processus de traitement caractéristiques de la totalité des processeurs informatiques.

Dans le premier cas l'information sortante constitue les signaux de séquencement qui ensuite peuvent activer les différentes opérations de traitement (opérations terminales). Les systèmes d'un tel type forment le séquenceur. Le séquenceur de la représentation structurelle a produit plusieurs séquences différentes de contrôle, toutes définies entièrement par l'information externe (les instructions). La forme b avec rétroaction permet de modifier dynamiquement, c'est-à-dire pendant

le déroulement du processus, la suite de ce processus initialement défini par l'information externe.

Une forme transitive-génératrice/mémorisante-transitive de deuxième ordre peut également exécuter directement le traitement des données. Dans ce cas les formes subordonnées mémorisantes-transitives mémorisent et transforment les données. Elles "performent" les fonctions de traitement (fonctions terminales). Il faut souligner que ce type de traitement exige un séquencement des fonctions défini extérieurement au système ou prévu au niveau des données (niveau inférieur) et transmis par une boucle rétroactive au niveau supérieur.

### 4. Formes de troisième ordre - 3F

Les formes de troisième ordre possèdent trois niveaux de complexité: niveaux supérieur, médian et inférieur. Le niveau supérieur est constitué du composant générateur, les niveaux médian et inférieur des composants transitifs et/ou mémorisants. Les formes étudiées dans ce sous-chapitre se distinguent essentiellement par la nature des deux niveaux subordonnés au niveau supérieur générateur.

Par rapport aux formes de deuxième ordre de complexité, les formes de troisième ordre contiennent un niveau de multiplexité de plus qui donne soit la nouvelle dimension de la sélection temporelle, soit celle de la sélection spatiale.

## 4.1. Formes. de troisième ordre <sup>3</sup>F<sub>2</sub>G(MT)

Les niveaux de complexité donnent trois niveaux d'états superposés. Le niveau supérieur comporte un composant générateur,

les deux autres niveaux des composants mémorisants-transitifs.

La structure génératrice de deuxième ordre est formée de deux

niveaux : le supérieur et le médian. Le niveau inférieur est

construit à partir des composants mémorisants-transitifs ; il

transforme et mémorise l'information entrante.

Page 42 Projet LIDO

Représentation textuelle :

$$^{3}F_{2G(MT)}[^{1}I] = ^{1/3}F_{G} \Rightarrow ^{3}I_{s} \Rightarrow ^{1/2}F_{G} \Rightarrow ^{2}I_{s} \Rightarrow ^{1}I \Rightarrow ^{1}F_{MT} \Rightarrow I_{S}$$

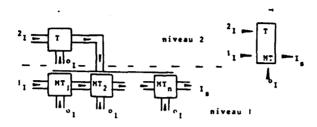

Représentation graphique :

l 2 T S - les sélecteurs des composants mémorisants-transitifs du niveau inférieur (terminal).

Interprétation :

La forme  $^{3}$ F $_{2G(MT)}$  est utilisée soit comme séquenceur, soit comme processeur. Les niveaux supérieur. et médian forment l'horloge multiphase qui effectue :

- soit la sélection temporelle des composants mémorisants-transitifs du séquenceur, celui-ci produisant des séquences à plusieurs pas, chacun de plusieurs phases; cette possibilité donne des séquenceurs produisant une grande variété de processus de séquencement.

- soit le cadencement multiphase des opérations exécutées sur les données stockées dans les composants mémorisants et transformées par les composants transitifs ; possibilité qui ne permet d'exécuter qu'un seul processus multiphase.

## 4.2. Formes de troisième ordre <sup>3</sup>F<sub>2GT</sub>

Par rapport aux formes précédentes les formes  $^3F_{2GT}$  ne possèdent au niveau inférieur que des composants transitifs. Ces forment donnent deux niveaux d'états : les états générés par le niveau supérieur, et ceux générés par le niveau médian.

Représentation textuelle :

$${}^{3}F_{2GT}[^{1}I] = {}^{1/3}F_{G} \Rightarrow {}^{3}I_{s} \Rightarrow {}^{1/2}F_{G} \Rightarrow {}^{2}I_{s} \Rightarrow {}^{1}I \Rightarrow {}^{1}F_{MT} \Rightarrow {}^{1}S_{G}$$

ou de façon contractée pour les formes génératrices :  ${}^{3}F_{2GT}[^{1}I] = {}^{2/3}F_{G} \Rightarrow {}^{2}I_{s} \Rightarrow {}^{1}I \Rightarrow {}^{1}F_{MT} \Rightarrow {}^{1}S_{G}$

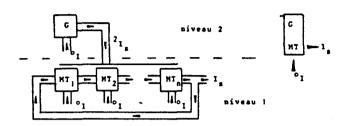

Représentation graphique :

Interprétation :

La forme <sup>3</sup>F<sub>2GT</sub> peut servir comme partie de commande du système informatique. Les niveaux supérieur et médian génèrent les signaux de synchronisation et de séquencement, le niveau inférieur donne des ramifications des états de séquencement (ici phases d'horloge multiphase). Ce type de forme est largement utilisé pour le contrôle microprogrammé.

Page 44 Projet LIDO

# 4.3. Formes de troisième ordre 3FG2(MT)