N° d'ordre : 212

50376

1988

179

50376

1988

179

présentée à

L'UNIVERSITE DES SCIENCES ET TECHNIQUES DE LILLE FLANDRES ARTOIS

pour obtenir le titre de

**DOCTEUR EN ELECTRONIQUE**

par

Sylvie BARANOWSKI - MAGNIEZ

**UTILISATION D'UN MICROCONTROLEUR DANS

UNE APPLICATION DE SECURITE

TEST ET EVALUATION DU TAUX DE COUVERTURE

DE PANNES ET DE LA SECURITE**

Soutenue le 29 Mars 1988 devant la Commission d'Examen

|                   |      |    |            |             |

|-------------------|------|----|------------|-------------|

| Membres du Jury : | MM.  | R. | GABILLARD  | Président   |

|                   | F.   |    | LOUAGE     | Rapporteur  |

|                   | Y.   |    | DAVID      | Rapporteur  |

|                   | V.   |    | CORDONNIER | Examinateur |

|                   | J.F. |    | DHALLUIN   | Invité      |

|                   | B.   |    | LE TRUNG   | Invité      |

|                   | R.   |    | LARDENNOIS | Invité      |

## AVANT PROPOS

Ce travail a été réalisé au Laboratoire de RadioPropagation et Electronique de l'Université des Sciences et Techniques de Lille Flandres Artois dirigé par Monsieur le Professeur Gabillard.

Je tiens à le remercier de m'avoir offert de travailler dans son laboratoire sur un sujet aussi passionnant que la sécurité des systèmes et de l'honneur qu'il me fait en présidant ce jury.

Je remercie également Monsieur le Professeur Louage, directeur de l'ENSA et Monsieur le Professeur Cordonnier d'accepter de juger ce travail.

Je tiens aussi à remercier Monsieur David, directeur de l'INRETS-CRESTA, de l'intérêt qu'il témoigne envers ce travail et de l'honneur qu'il me fait en le jugeant.

J'exprime ma profonde reconnaissance à Monsieur Dhalluin, ingénieur à MATRA TRANSPORT. Les nombreuses discussions que nous avons eues m'ont permis de progresser dans ce travail. Je le remercie de l'aide qu'il m'a apportée et de sa participation à ce jury.

Monsieur Le Trung, directeur de recherches à l'INRETS-CRESTA, et Monsieur Lardennois, directeur de recherches à MATRA TRANSPORT, ont accepté de juger ce travail et je les en remercie.

Je tiens aussi à remercier tout le personnel du CRESTA pour sa gentillesse.

Et enfin je remercie le personnel du laboratoire , celui de l'UFR et toutes les personnes qui, de près ou de loin, ont contribué à l'aboutissement de ce travail.

## SOMMAIRE

## PREMIERE PARTIE

### LA MISE EN SECURITE DES SYSTEMES DE COMMANDE A MICROPROCESSEUR

#### I) LA SECURITE DES AUTOMATISMES DANS LES TRANSPORTS TERRESTRES

|                                                                     |      |

|---------------------------------------------------------------------|------|

| I.1) Définitions et ordres de grandeur                              | p 10 |

| Sûreté de fonctionnement                                            |      |

| - la fiabilité                                                      |      |

| - la sécurité                                                       |      |

| - la disponibilité                                                  |      |

| - la réparabilité                                                   |      |

| I.2) La mise en sécurité des systèmes de commande à microprocesseur | p 14 |

| I.3) La méthode choisie                                             | p 19 |

#### II) LE PROCEDE DE SECURITE ETUDIE

|                               |      |

|-------------------------------|------|

| II.1) Présentation générale   | p 21 |

| II.1.1) le processus commandé |      |

| II.1.2) la commande           |      |

| II.2) Les tests fonctionnels  | p 26 |

#### III) LES TESTS FONCTIONNELS

|                                                           |      |

|-----------------------------------------------------------|------|

| III.1) Les hypothèses de pannes sur la partie opérative   | p 28 |

| III.2) Modélisation du fonctionnement du microprocesseur  | p 30 |

| III.3) Le test des instructions arithmétiques et logiques | p 33 |

| III.4) Les autres instructions                            | p 37 |

| III.5) Le test de la RAM                                  | p 38 |

| III.6) Le test de la ROM                                  | p 43 |

| III.7) Organisation du programme de test                  | p 44 |

| III.8) Conclusion                                         | p 47 |

## DEUXIEME PARTIE

### EVALUATION DU TAUX DE COUVERTURE DE PANNES D'UN MICROPROCESSEUR

#### I) METHODES DE DETERMINATION DU TAUX DE COUVERTURE DE PANNES

- |                                                  |      |

|--------------------------------------------------|------|

| I.1) Le schéma bloc du microprocesseur est connu | p 52 |

| I.2) La structure interne est inconnue           | p 53 |

#### II) APPLICATION AU SYSTEME ETUDIE

- |                                                                 |      |

|-----------------------------------------------------------------|------|

| II.1) Connaissance de la structure interne du 8031              | p 56 |

| II.2) Proportion de surface occupée par chaque bloc fonctionnel | p 57 |

| II.3) Détermination des taux partiels de couverture de pannes   | p 58 |

| II.4) Le bloc ROM                                               | p 58 |

| II.5) Les blocs Port 0 et Port 2                                | p 59 |

| II.6) Le bloc ALU                                               | p 61 |

| II.7) Le bloc RAM                                               | p 62 |

| II.8) Le bloc PC/DPTR                                           | p 64 |

| II.9) Les blocs PLA - Control Logic - Timing                    | p 66 |

| II.10) Le bloc CLOCK                                            | p 68 |

| II.11) Les blocs Port Control et RAM Control                    | p 68 |

| II.12) Les blocs Timer, Interrupt and Serial Port               | p 69 |

| II.13) Détermination du taux de couverture de pannes            | p 71 |

#### III) LA SIMULATION DES FAUTES

- |                                      |      |

|--------------------------------------|------|

| III.1) Utilisation de l'appareil     | p 75 |

| III.2) Simulation de fautes internes | p 75 |

| III.3) Résultats                     | p 78 |

#### IV) CONCLUSION

## TROISIEME PARTIE

### CALCUL DES PARAMETRES DE LA SURETE DE FONCTIONNEMENT DE STRUCTURES MONOPROCESSEUR ET BIPROCESSEUR

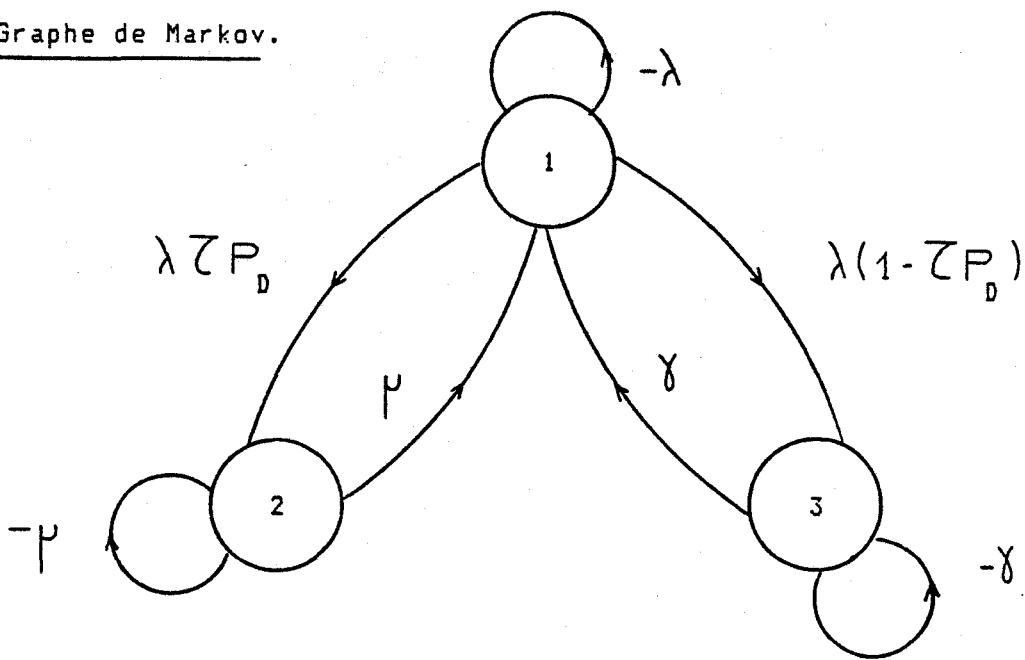

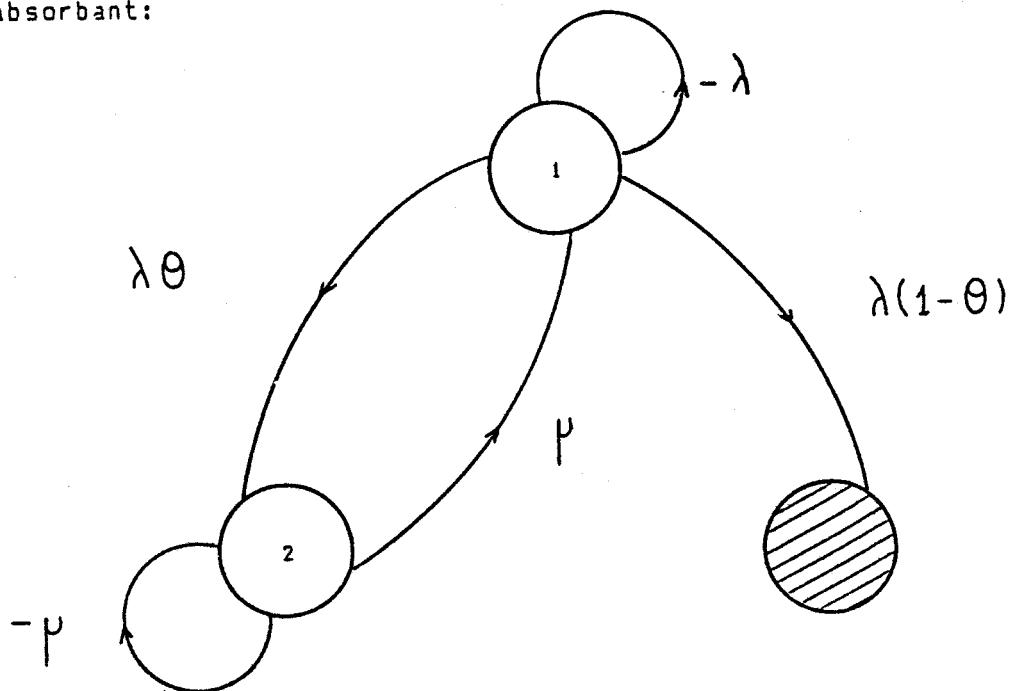

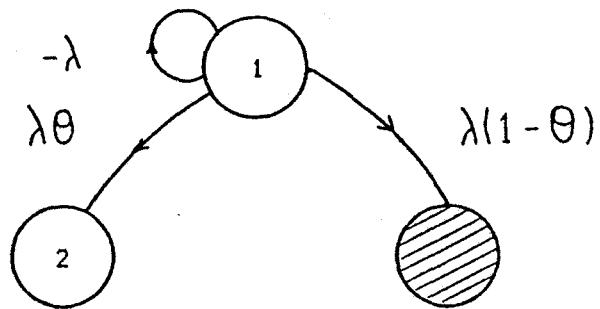

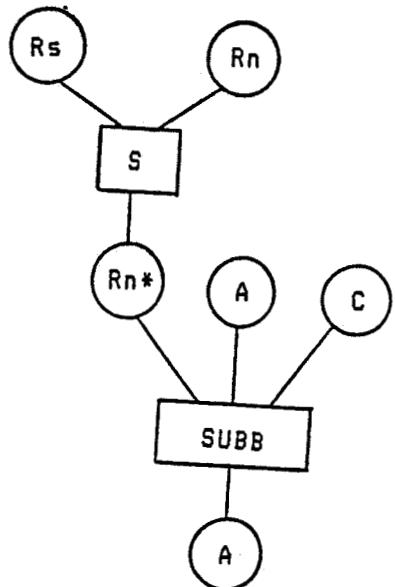

I) L'UTILISATION DES GRAPHES D'ETATS p 82

#### II) STRUCTURE MONOPROCESSEUR

|                                                       |      |

|-------------------------------------------------------|------|

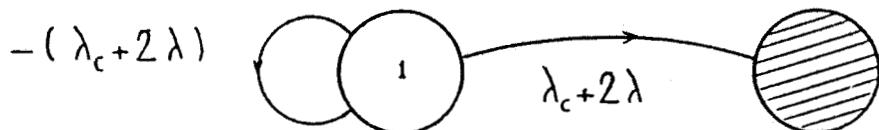

| II.1) Principe général                                | p 87 |

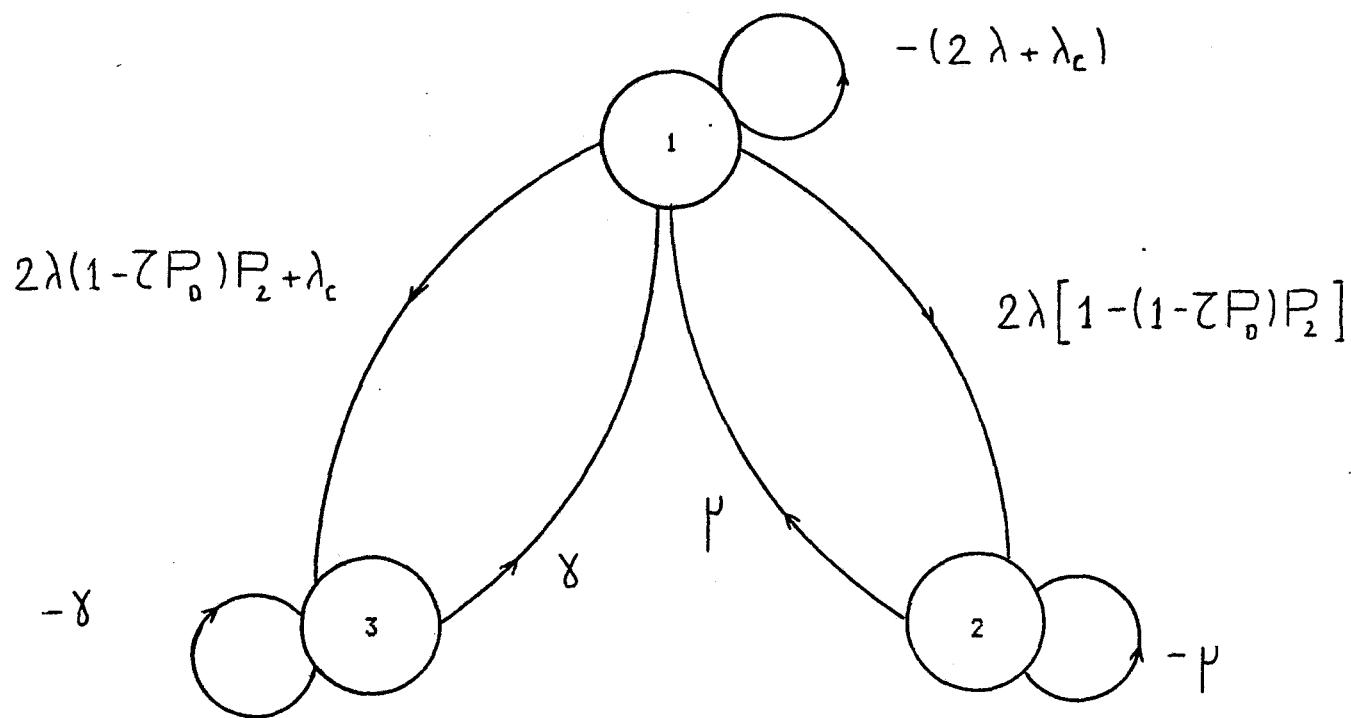

| II.2) Graphe de Markov                                | p 88 |

| II.3) Calcul de la fiabilité                          | p 90 |

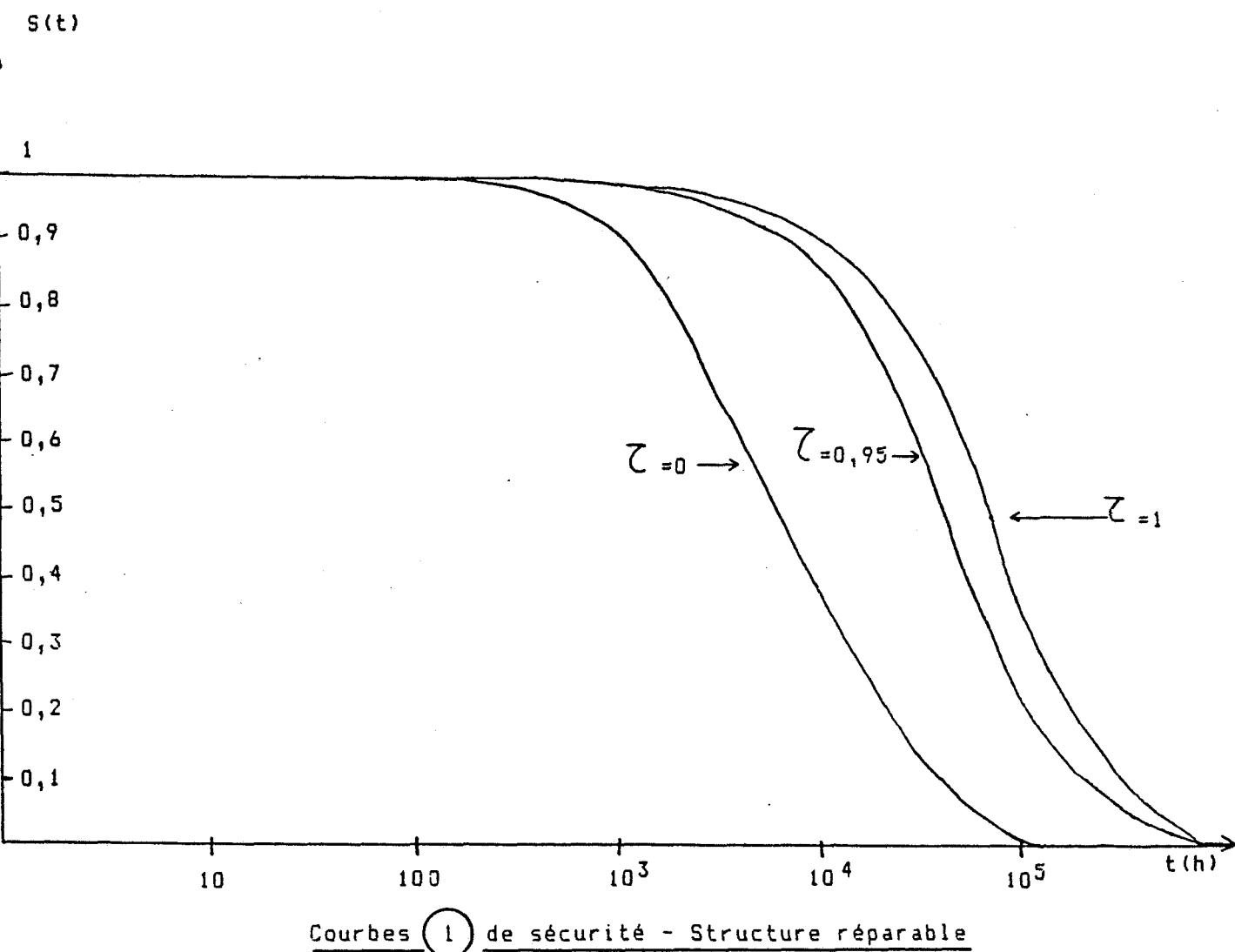

| II.4) Calcul de la sécurité (structure réparable)     | p 91 |

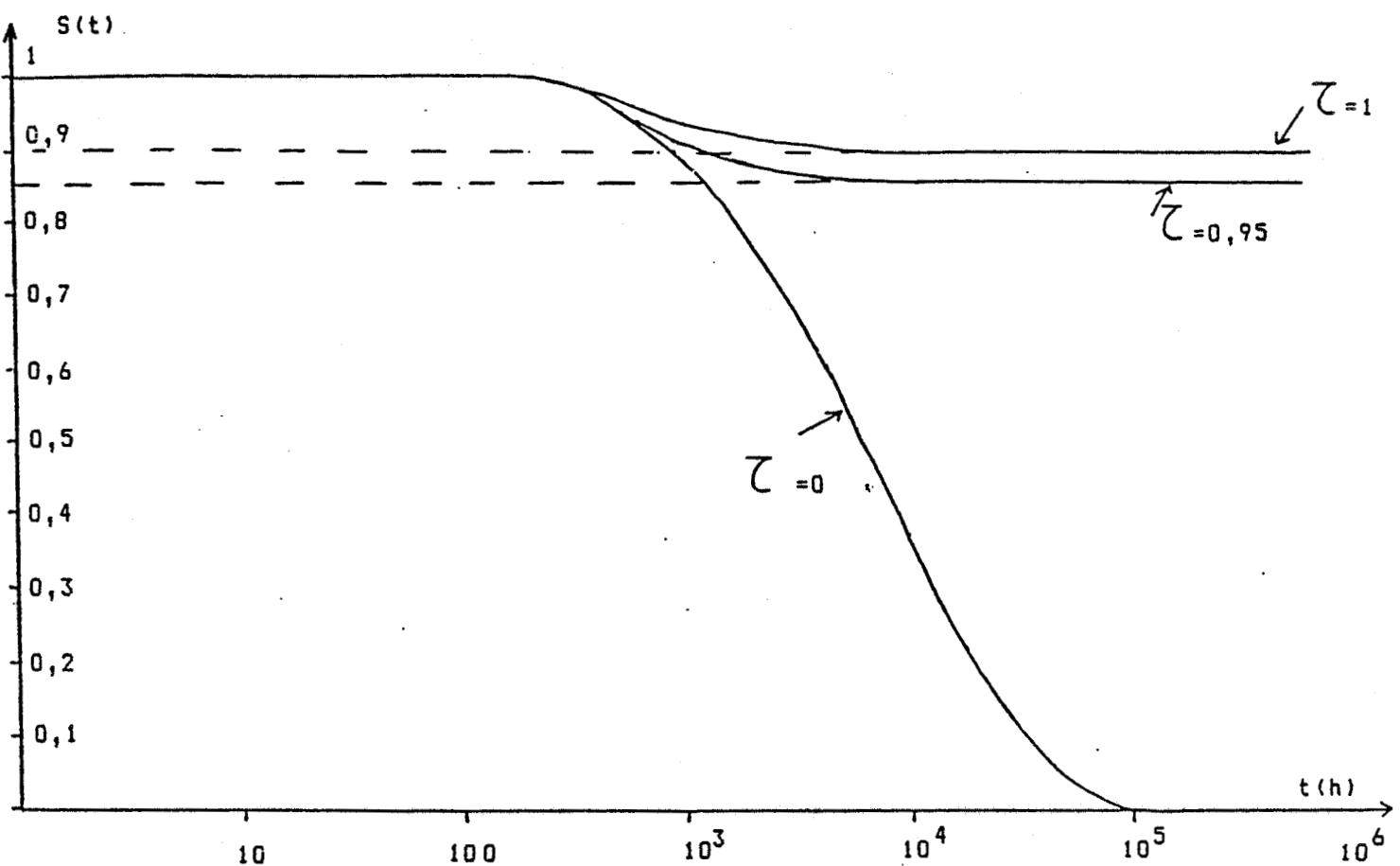

| II.5) Calcul de la sécurité (structure non réparable) | p 93 |

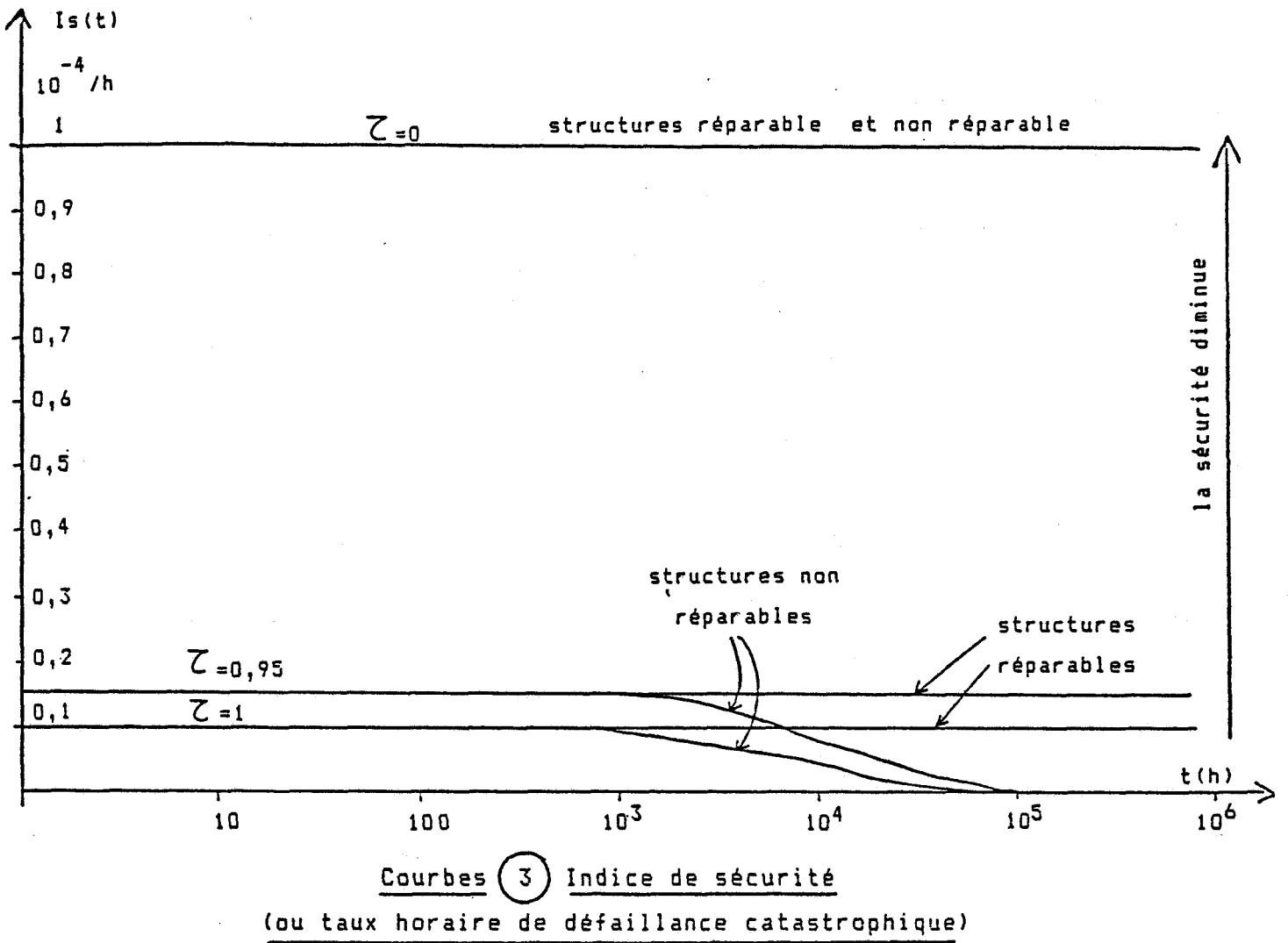

| II.6) Calcul de l'indice de sécurité                  | p 93 |

| II.7) Résultats numériques obtenus                    | p 94 |

| II.8) Conclusion                                      | p 97 |

#### III) STRUCTURE BIPROCESSEUR

|                                                            |       |

|------------------------------------------------------------|-------|

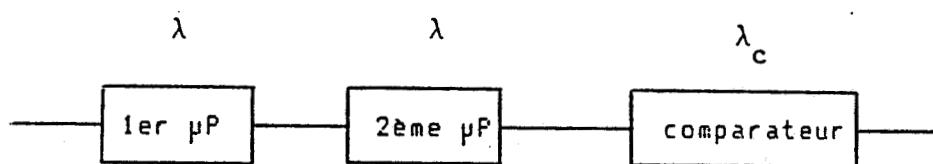

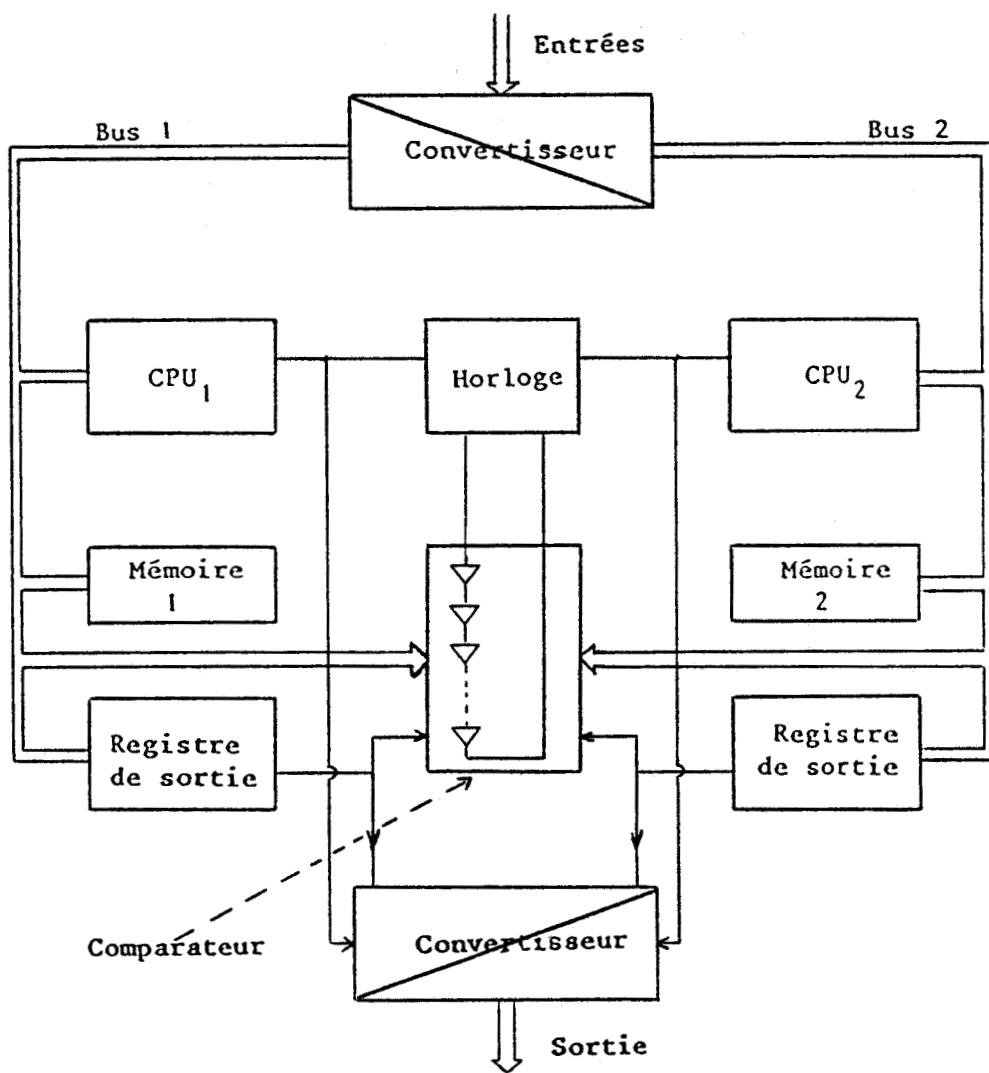

| III.1) Principe général                                    | p 98  |

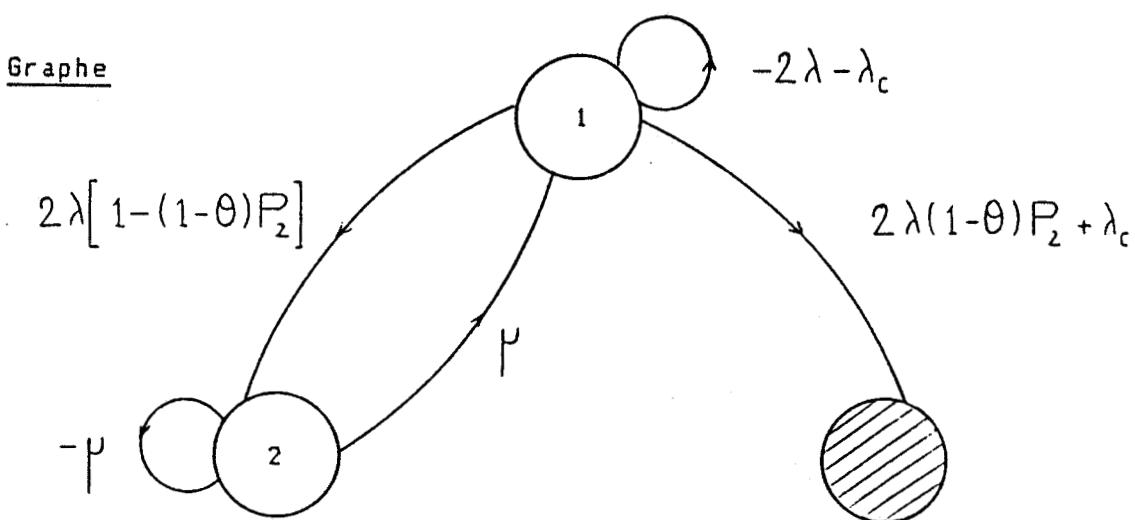

| III.2) Graphe de Markov                                    | p 99  |

| III.3) Calcul de la fiabilité                              | p 102 |

| III.4) Calcul de la sécurité (structure réparable)         | p 102 |

| III.5) Calcul de la sécurité (structure non réparable)     | p 105 |

| III.6) Calcul de l'indice de sécurité                      | p 105 |

| III.7) Résultats obtenus                                   | p 105 |

| III.7.1) Influence du comparateur                          | p 105 |

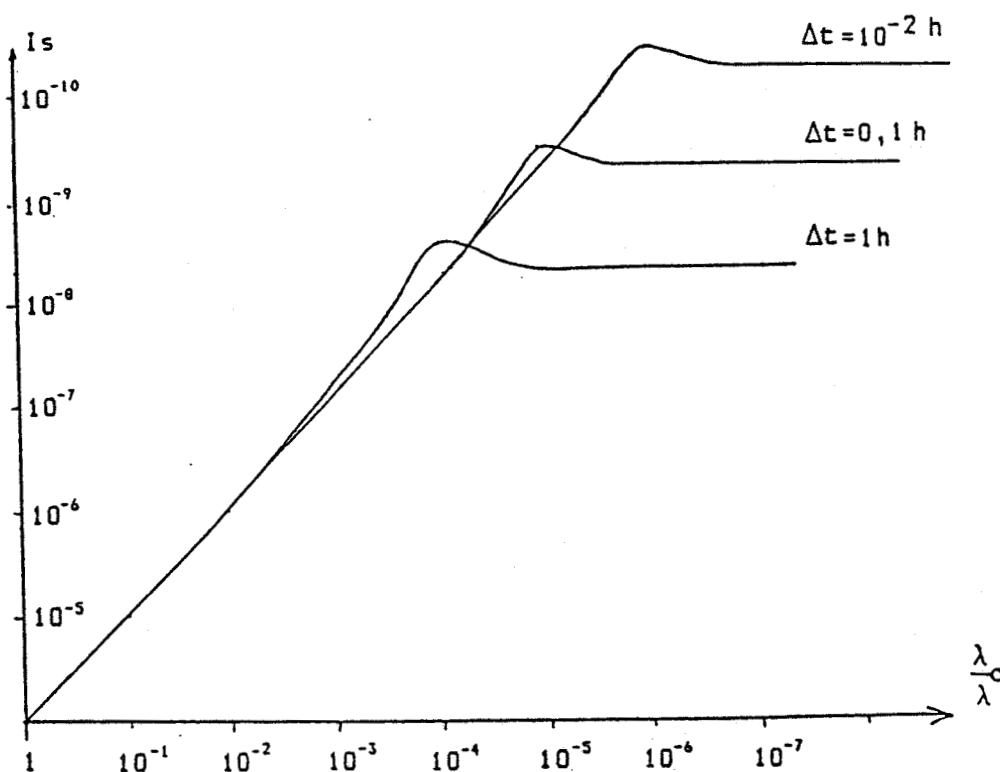

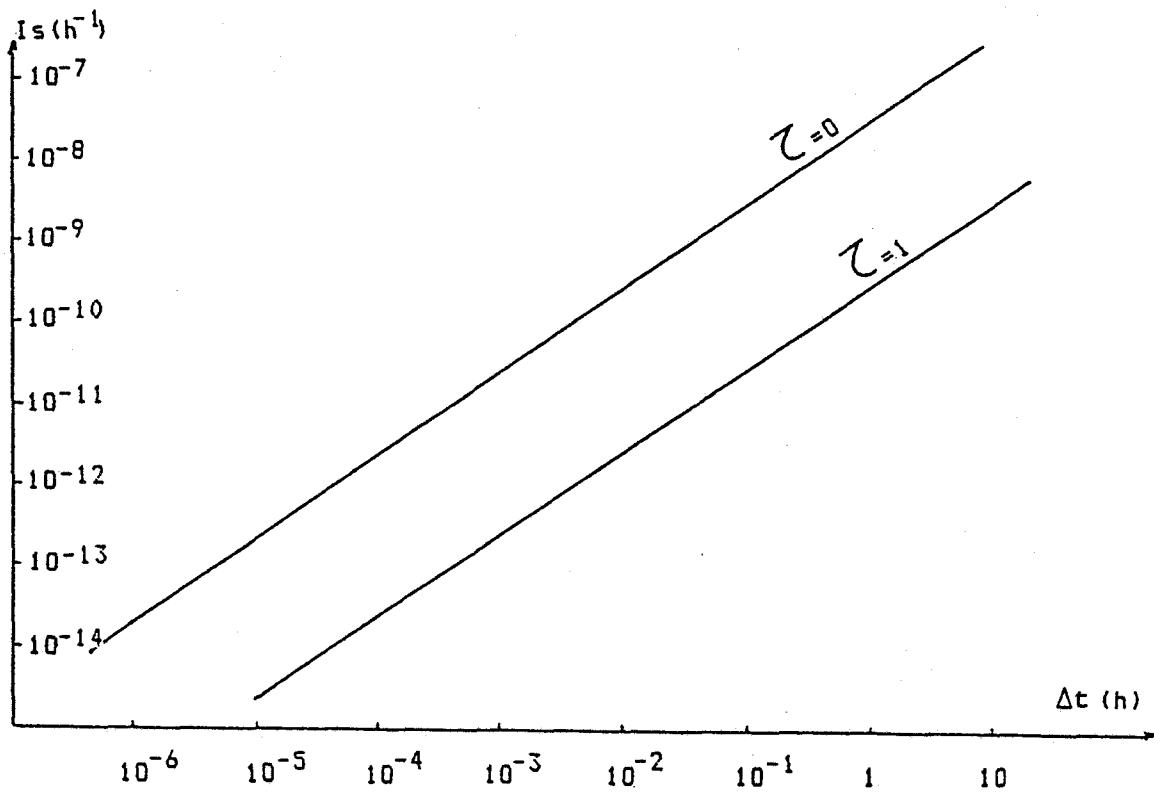

| III.7.2) Influence de la latence de propagation $\Delta t$ | p 109 |

| III.7.3) Influence des tests fonctionnels                  | p 111 |

| III.8) Conclusion                                          | p 112 |

IV) COMPARAISON AVEC UN SYSTEME EXISTANT p 113

REFERENCES BIBLIOGRAPHIQUES

p 120

ANNEXES

Annexes 1 Liste des instructions du 8031 p 127

Annexes 2 Les graphes d'exécution abstraite p 128

## **INTRODUCTION GENERALE**

## INTRODUCTION

Les progrès technologiques récents ont permis la mise au point de circuits intégrés très performants permettant de remplacer plusieurs cartes électroniques par un seul circuit.

Le monde des transports, et de la sécurité en général, n'est pas resté insensible à ces progrès permettant la réduction du nombre des cartes de commande, mais surtout une amélioration importante des performances et des possibilités de reconfiguration rapide des systèmes. Les microprocesseurs ont donc fait leur entrée dans les automatismes de commande de processus en sécurité.

Auparavant, les cartes de commande étaient composées de circuits électroniques discrets (transistors, résistances,...) dont les pannes étaient connues; l'étude de sécurité était relativement simple et la conception en sécurité intrinsèque possible. Dorénavant, les cartes sont composées de circuits intégrés dont la complexité est telle qu'il est impossible d'en connaître toutes les pannes et, par là même, de faire de la conception en sécurité intrinsèque.

Les méthodes de mise en sécurité de ces systèmes à microprocesseurs ont toutes, sous diverses formes, le même but: activer la panne si elle existe, la détecter et inhiber les commandes avant qu'elles ne deviennent dangereuses.

Dans la première partie, nous présentons la méthode que nous avons choisie et qui est basée essentiellement sur l'émission périodique d'un signal déterministe et sur l'exécution de tests fonctionnels cycliques permettant l'activation de toutes les fonctions du microprocesseur.

Après une description détaillée des routines de test réalisées, nous présentons, dans la deuxième partie, une méthode d'évaluation du taux de couverture de pannes d'un microprocesseur (proportion de pannes détectées), méthode que nous appliquons au système étudié.

Dans la troisième partie, notre souci principal est de chiffrer la sécurité obtenue avec notre système. Nous développons ensuite l'apport de la redondance et l'influence des tests fonctionnels cycliques sur l'indice de sécurité et nous concluons cette partie par une comparaison avec un système existant.

1<sup>ère</sup> PARTIE

LA MISE EN SECURITE DES SYSTEMES DE COMMANDE

A MICROPROCESSEUR

## I) LA SECURITE DES AUTOMATISMES DANS LES TRANSPORTS TERRESTRES.

### I.1) Définitions et ordres de grandeur .

La mise en service d'un système de transport nécessite d'avoir déterminé, au préalable, les valeurs numériques caractérisant sa sûreté de fonctionnement (fiabilité, sécurité, disponibilité, réparabilité...) et, bien entendu, vérifié qu'elles se situaient dans les limites souhaitées.

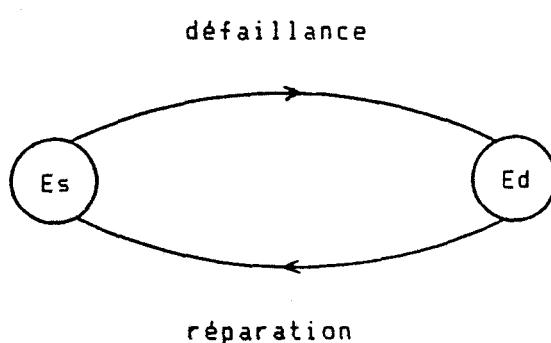

#### a) Sûreté de fonctionnement (REF.LAP).

La sûreté de fonctionnement est l'aptitude d'un système à accomplir les tâches qui lui sont confiées dans des conditions données.

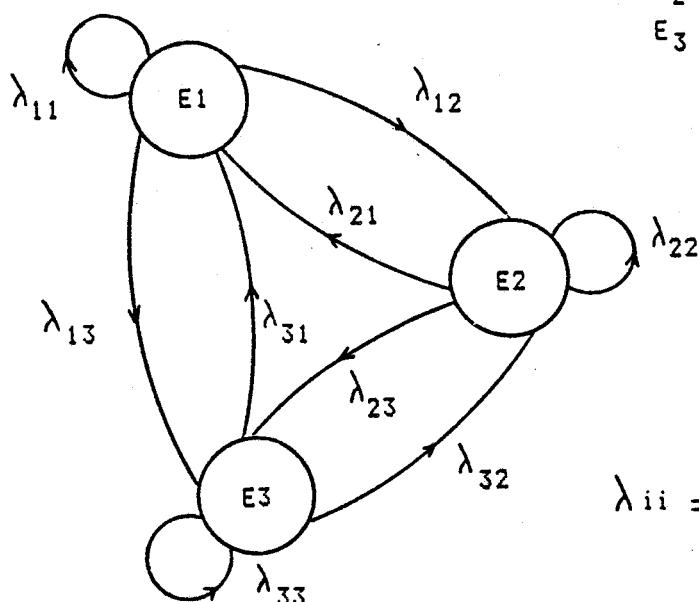

Soit  $e(t)$ , l'état du système à l'instant  $t$ .

$$e(t) \in \{E_1, E_2, E_3\}$$

avec

$E_1$  : état "en bon fonctionnement"

$E_2$  : état "en panne non dangereuse"

$E_3$  : état "en panne dangereuse".

Les principales grandeurs qui caractérisent la sûreté de fonctionnement sont définies ci-dessous:

- la fiabilité  $R(t)$ .

La fiabilité est la probabilité que le système fonctionne correctement durant l'intervalle de temps  $[t_0, t]$ ,  $t_0$  étant l'instant de première mise en service; c'est donc la probabilité qu'aucune panne ne se produise entre  $t_0$  et  $t$ .

$$R(t) = \mathcal{P} \left\{ e(Z) = E_1, \forall Z \in [t_0, t] \right\}$$

- la sécurité  $S(t)$ .

La sécurité est la probabilité que le système ne soit pas dans un état dangereux durant l'intervalle  $[t_0, t]$ ; c'est donc la probabilité qu'aucune panne dangereuse ne se produise entre  $t_0$  et  $t$ .

$$S(t) = \mathcal{P} \left\{ e(Z) \in \{E_1, E_2\}, \forall Z \in [t_0, t] \right\}$$

- la disponibilité  $A(t)$ .

La disponibilité est la probabilité que le système fonctionne correctement à l'instant  $t$ , indépendamment de sa vie antérieure.

$$A(t) = \mathcal{P} \left\{ e(t) = E_1 \right\}$$

- la réparabilité  $RF(t)$ .

La réparabilité est la probabilité que le système soit réparé à l'instant  $t$  sachant qu'il était en panne durant l'intervalle de temps  $[t_0, t]$ .

$$RF(t) = \mathcal{P} \left\{ e(t) = E_1 / e(Z) \in \{E_2, E_3\}, \forall Z \in [t_0, t] \right\}.$$

b) Ordres de grandeur.

- la fiabilité

Soit  $f(t)$  la densité de probabilité de panne d'un système; on définit le taux instantané de défaillance  $\lambda(t)$  comme étant égal à:

$$\lambda(t) = \frac{f(t)}{R(t)}.$$

$\lambda(t)$  a pour dimension l'inverse d'un temps.

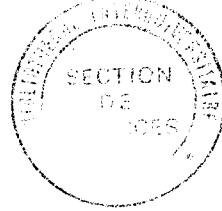

Les équipements considérés ont une courbe de taux instantané de défaillance en fonction du temps de la forme :

Si les équipements utilisés sont déverminés (la période de jeunesse est révolue) et remplacés dès qu'ils atteignent leur période de vieillesse, le taux instantané de défaillance peut être considéré comme constant et égal à  $\lambda_0$ . La fiabilité s'exprime alors par une fonction exponentielle.

$$R(t) = e^{-\lambda_0 t}.$$

Le taux de défaillance horaire du microprocesseur utilisé dans l'application que nous présentons dans les chapitres suivants a été évalué dans REF.DHA1.

$$10^{-5}/h < \lambda_0 < 10^{-4}/h$$

- la sécurité

Le niveau de sécurité s'exprime généralement par l'indice de sécurité  $I_s$ , ou taux horaire de défaillance catastrophique (contraire à la sécurité). Sa définition est la suivante:

$$I_s = - \frac{1}{S(t)} \cdot \frac{dS(t)}{dt}.$$

Pour information, dans le cas du métro VAL, l'ordre de grandeur de la valeur du taux horaire de défaillance catastrophique est:

$I_s < 10^{-6}/h$  pour les systèmes de commande de portes de véhicule

$I_s < 10^{-10}/h$  pour le système de contrôle sécuritaire du véhicule (tiroir sécurité).

- la disponibilité

Si la mise en sécurité d'un système consiste à l'arrêter dès que l'on constate le moindre écart entre son évolution présente et son évolution désirée, la disponibilité et la sécurité sont des grandeurs qui dépendent inversement l'une de l'autre:

Un système qui ne fait rien (la disponibilité est nulle) est parfaitement sûr (la sécurité est maximale).

On peut aussi mettre un système en sécurité en utilisant la redondance (§ I.2.2) et dans ce cas, la sécurité et la disponibilité évoluent dans le même sens (si on tolère le fonctionnement en mode dégradé).

L'étude présentée vise essentiellement l'amélioration de la sécurité.

- la réparabilité

Le système étudié est composé d'une ou plusieurs cartes de commande à microprocesseur; la réparation est ici très simple: la carte défectueuse est remplacée par une carte en bon état. Cette manière de procéder améliore aussi la disponibilité (temps de réparation plus courts). La réparabilité est une caractéristique dépendant de la structure modulaire du système et donc relativement facile à obtenir.

## I.2) La mise en sécurité des systèmes de commande à microprocesseur

Lorsqu'un dispositif est réalisé en sécurité intrinsèque, il prend, en cas de défaillance de l'un de ses constituants, un état de sécurité (état non dangereux) préalablement défini. La conception en sécurité intrinsèque est remise en cause par l'utilisation des microprocesseurs pour la commande de processus en sécurité. En effet, la complexité du circuit est telle qu'il est impossible d'être sûr que le processus prendra l'état de sécurité en cas de défaillances internes; on a donc recours à la conception en sécurité probabiliste (calcul de la probabilité d'apparition des pannes résiduelles dangereuses).

Différentes méthodes de mise en sécurité de systèmes à microprocesseur existent: les tests, la redondance, les codages,...etc.

On distingue ainsi:

### I.2.1) Les méthodes "hors ligne".

Les méthodes de mise en sécurité "hors ligne" consistent à prendre des précautions lors de la conception du système et/ou à effectuer des tests de ses composants, le système n'étant pas en service.

Citons quelques exemples:

- l'utilisation de composants de fiabilité élevée

- le retrait systématique des composants ayant atteint la limite de leur vie utile

- le test de fonctionnement

Ce test consiste à vérifier le fonctionnement d'un microprocesseur en observant son comportement dans un environnement donné; deux méthodes principales existent: le test déterministe et le test aléatoire.

- le test déterministe.

Il consiste à envoyer au microprocesseur un ensemble de vecteurs de test prédéterminés et à comparer le comportement du circuit testé à celui d'un circuit de référence ou à un ensemble de vecteurs de sortie issus de simulations (REF.VEL) (REF.BEL1) (REF.BEL2).

- le test aléatoire.

Il consiste à envoyer à deux circuits (celui de référence et celui sous test) une séquence de vecteurs pseudo-aléatoires de longueur déterminée et à comparer les deux sorties. (REF.THE)

Ces tests permettent de vérifier le fonctionnement d'un circuit avant de le mettre en service mais peuvent aussi servir à effectuer des tests hors-ligne périodiques si cela s'avère nécessaire.

### I.2.2) Les méthodes "en ligne".

La surveillance en ligne est un moyen efficace de limiter les conséquences de l'apparition de pannes dangereuses: les pannes sont détectées (avec une certaine probabilité de détection) et les commandes émises par le microprocesseur sont inhibées avant que leurs conséquences ne deviennent dangereuses.

Plusieurs méthodes existent, citons en quelques unes:

- la conception de circuits de sécurité.

Une méthode consiste à concevoir un microprocesseur de sécurité disposant d'un maximum de protections internes: codage des informations internes (ex: parité), redondance des blocs internes sensibles (ex: la RAM) avec utilisation d'un code double-rail,...etc. (REF.BIE)

Une seconde méthode est basée sur la conception de circuits facilement testables (microprocesseurs ouverts): le nombre d'instructions et de blocs fonctionnels est limité au strict nécessaire, toutes les informations utiles au test (externe) sont accessibles à l'utilisateur,...etc. (REF.HSURF)

La nécessité de la conception et de la réalisation de circuits intégrés très spécialisés donc de petite série constituent le gros inconvénient de ces deux méthodes. En effet, ceci n'est pas accessible à beaucoup de concepteur de systèmes de sécurité qui préfèrent utiliser des composants du commerce, moins chers et dont la grande diffusion offre une garantie de bonne conformité fonctionnelle (les défauts de conception sont éliminés au fur et à mesure de leur apparition).

- les logiciels de test.

Il s'agit d'implanter en mémoire un programme, exécuté périodiquement, qui permet de tester les différentes unités du microprocesseur (l'unité arithmétique et logique, les mémoires, les bus,...etc).

La vérification du bon fonctionnement du circuit peut être faite, par exemple, en contrôlant un signal de chien de garde émis lors du déroulement du programme ou un message codé reflétant, sous forme compacte, la valeur des vecteurs de sortie (signature). (REF.SAU)(REF.JOU)

Cette méthode requiert l'utilisation d'un contrôleur, souvent spécialisé, sachant décoder l'information de sortie ( détecteur de variation temporelle de signal de chien de garde, analyseur de signature) et sur lequel une étude de sécurité doit aussi être faite (ces circuits peuvent être conçus en sécurité intrinsèque).

- la redondance.

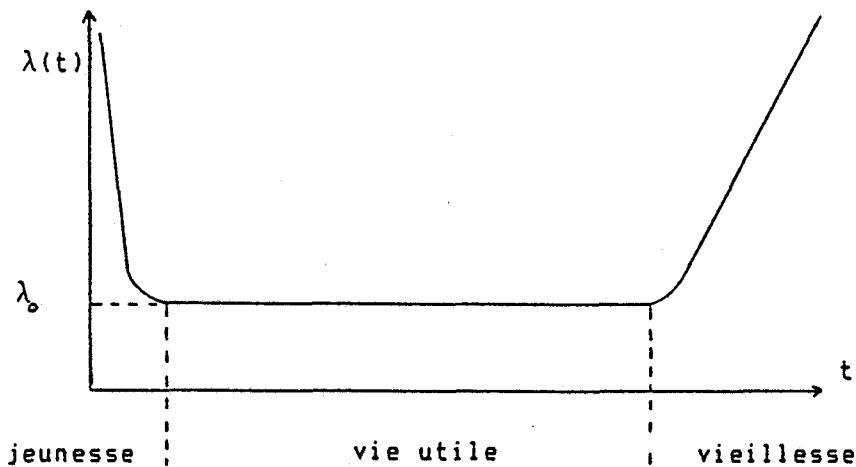

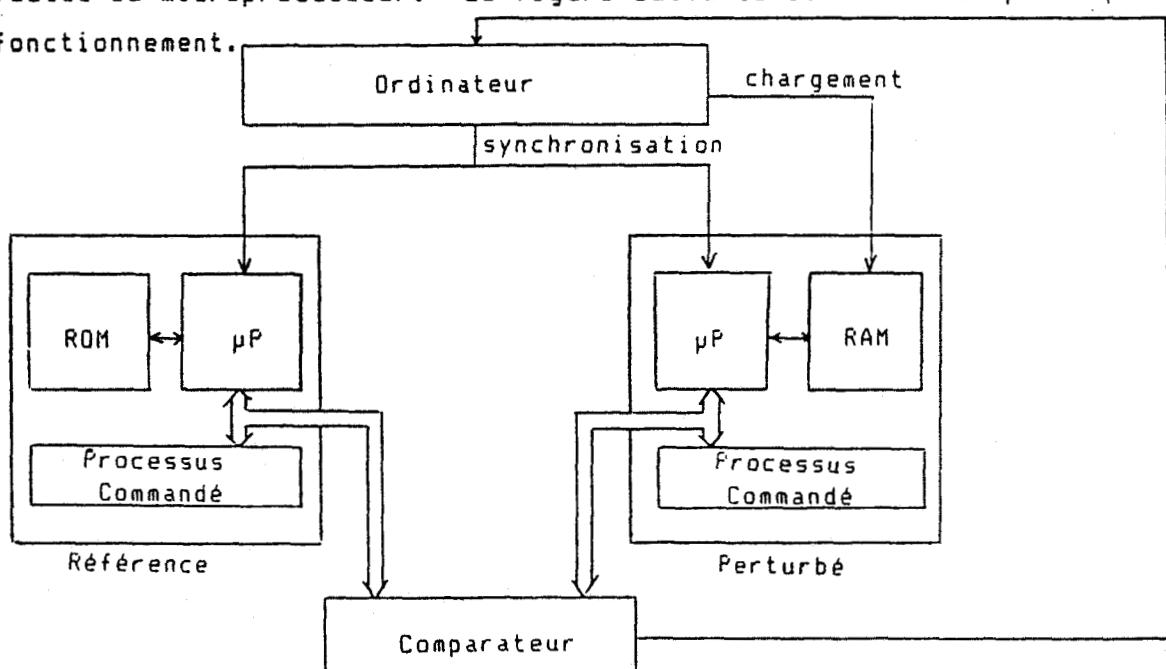

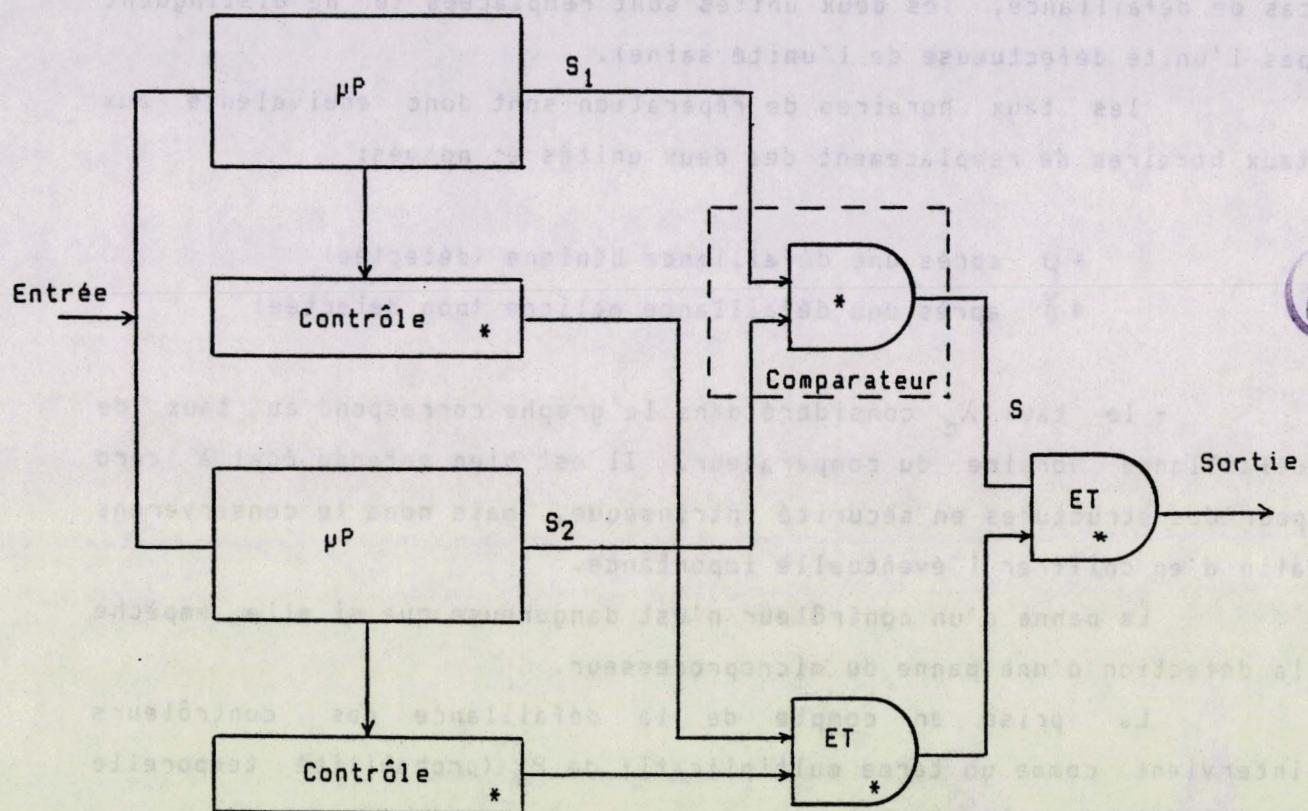

La redondance est un terme général signifiant que l'on confie le même traitement à plusieurs unités dont on compare les résultats pour détecter leurs anomalies de fonctionnement.

Le schéma général est le suivant:

Il existe deux types de redondance:

\* la redondance homogène:

les unités et les programmes sont identiques (REF.PIL) (REF.CAS).

\* la redondance hétérogène:

les unités sont différentes et/ou les programmes sont différents (mais le traitement reste le même) (REF.SEV).

Le comparateur permet de vérifier la concordance des résultats issus des différentes unités (aspect sécurité) et, quand c'est un voteur  $k$  parmi  $n$  (avec  $k > \frac{n}{2}$  et  $n > 2$ ), il déconnecte la ou les unités défaillantes et le fonctionnement du système peut continuer en mode dégradé (aspect disponibilité).

Pour les redondances, la sécurité repose essentiellement sur:

- le comparateur, il doit être étudié avec soin

- l'impossibilité d'apparition de pannes de mode commun, ceci doit être démontré.

De plus, la synchronisation des différentes unités peut poser des problèmes, surtout pour les redondances hétérogènes.

- le codage.

Les informations à traiter sont codées. Toute anomalie de fonctionnement lors du traitement (pannes de microprocesseurs, parasites,...) transforme (avec une probabilité donnée) le mot de sortie codé correctement en un mot de sortie hors-code.

Cette méthode nécessite un encodeur en entrée et un décodeur-détecteur d'erreurs en sortie.

La sécurité repose principalement sur le décodeur qui valide la sortie et sur le choix du code. En effet, plus le code est sensible aux perturbations, meilleure est la détection (probabilité de non détection plus faible).

Un exemple de cette méthode est donné dans REF.SAC.

- les solutions mixtes.

Toutes les méthodes présentées ont des limites et il est parfois nécessaire d'associer plusieurs procédés afin d'obtenir l'indice de sécurité souhaité; parfois même, l'indice de sécurité étant suffisant, une redondance supplémentaire permet d'augmenter la disponibilité du dispositif.

Un exemple de solution mixte est donné dans REF.DAV où le système PUSH utilisé pour le métro de Hambourg associe la redondance et les logiciels de test.

- conclusion.

Nous nous sommes limités à présenter quelques exemples de solutions au problème de la mise en sécurité de systèmes de commande à microprocesseur; cette liste n'est bien entendu pas exhaustive.

Selon les objectifs à atteindre:

- sécurité élevée au détriment de la disponibilité

- amélioration de la disponibilité

- encombrement réduit: un système redondant augmente considérablement la taille de la carte de commande

- vitesse du processus à commander: des logiciels de test exécutés cycliquement ralentissent considérablement le déroulement du programme d'application,

une méthode, ou une association de méthodes, est choisie plutôt qu'une autre; mais la mise en sécurité reste du domaine de l'imagination des concepteurs et il n'existe pas de solution unique à un problème donné.

### I.3) La méthode choisie.

Le chapitre suivant présente la méthode choisie; elle est basée sur un dispositif de chien de garde amélioré et sur des logiciels de test exécutés de façon cyclique. Dans la dernière partie, nous évaluerons l'apport de la redondance sur un tel dispositif.

PRESENTATION GENERALE DU SYSTEME ETUDE

## II) LE PROCEDE DE SECURITE ETUDIE.

### III.1) Présentation générale (REF.DHA2).

#### III.1.1) Le processus commandé.

Le processus commandé est un processus de sécurité. Sa vitesse d'évolution est très lente: le temps de changement entre deux états consécutifs n'excède pas 10 ms.

#### III.1.2) La commande.

Le caractère discontinu du processus à commander permet de représenter l'évolution de la commande par un graphe de PETRI. Une méthode d'implantation de ces graphes sur microprocesseurs a été mise au point au laboratoire.(REF.ELK)

L'intérêt de cette méthode est d'organiser l'écriture et le traitement du programme de commande du processus de façon très modulaire.

Chaque action (étape transition-commande) se présente sous forme d'un module de programme élémentaire.

En cours de traitement un moniteur enchaîne l'exécution des différents modules correspondant au marquage du réseau de Pétri.

Cette modularité confère au logiciel de commande une grande sûreté de fonctionnement. La description de la commande par un réseau de Pétri tient compte des aspects sécurité:

- détection de pannes sur les capteurs

- détection de pannes sur les effecteurs

- traitement "anti-rebond",....

De plus, la sécurité des transmissions est prise en compte par le codage des informations (REF.QUA).(REF.GAB).

Les aspects sécurité "processus - processeur" étant pris en compte, il ne reste plus alors que les aspects "processeur - processus".

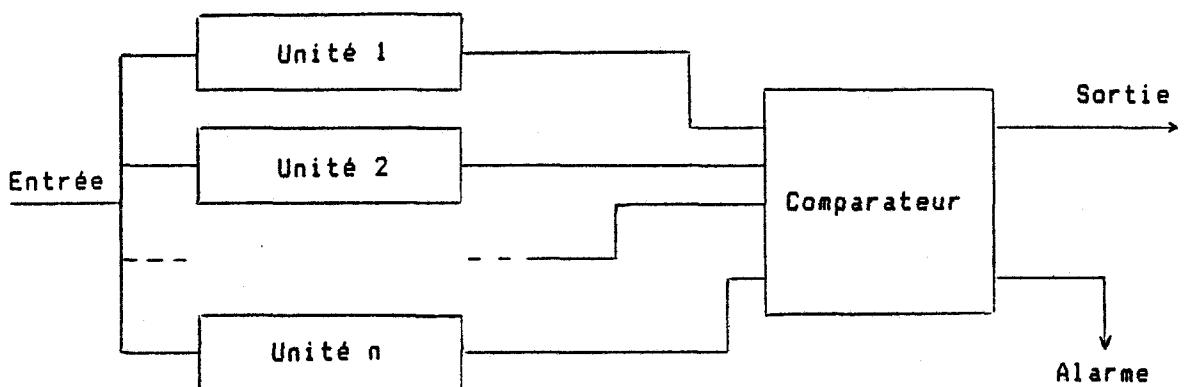

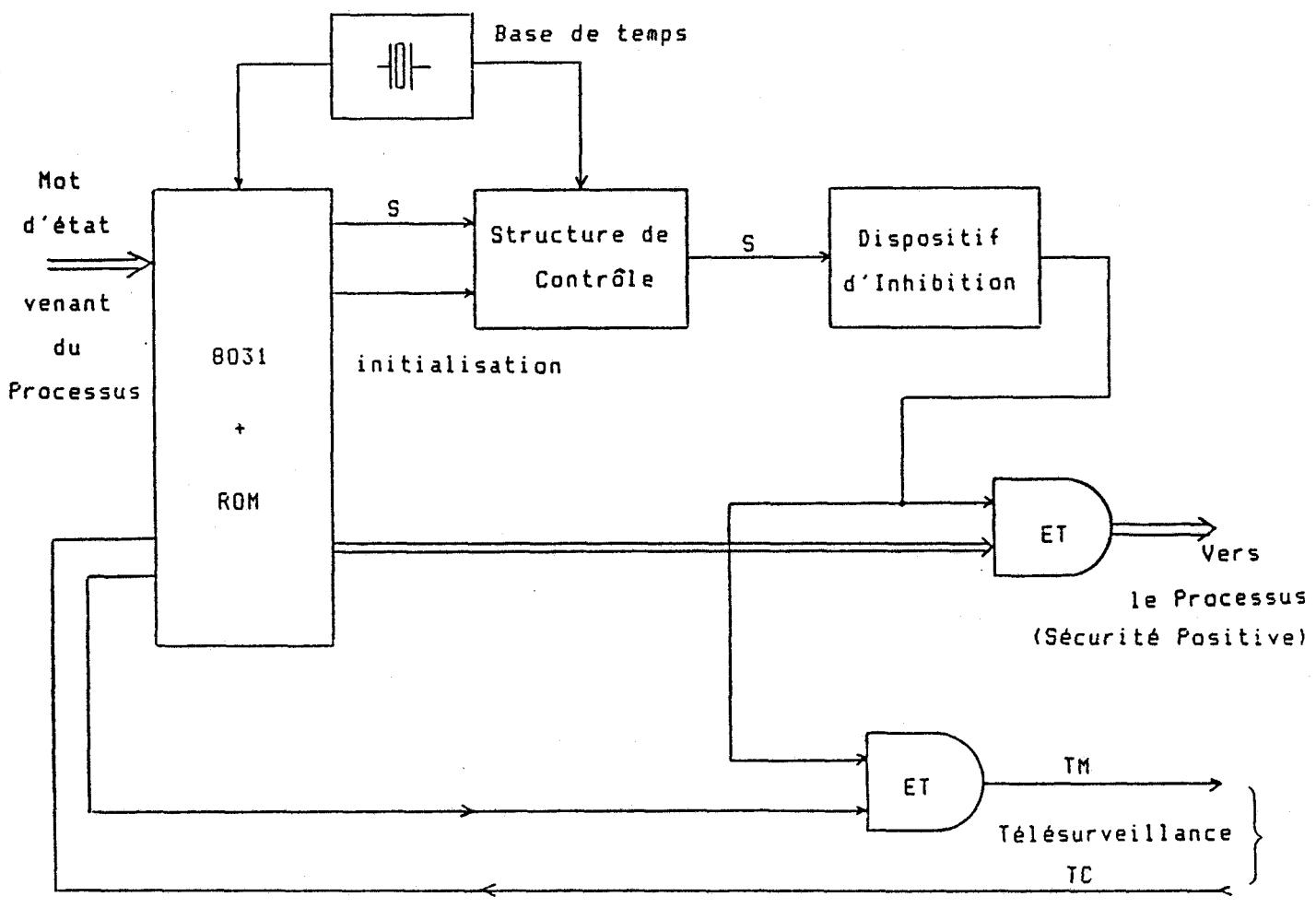

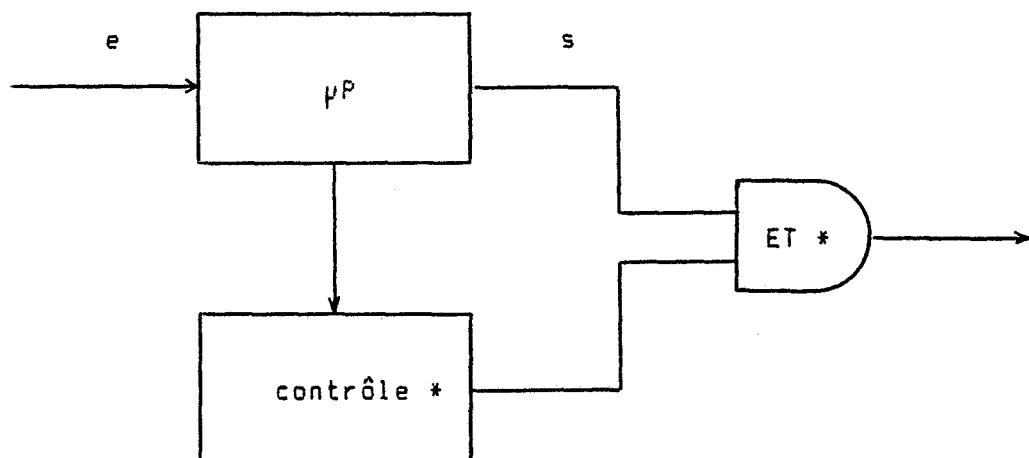

La modularité du programme d'application a permis l'implantation d'un procédé de test temporel. Celui-ci consiste à normer temporellement les différents modules de manière à faire émettre périodiquement par le microprocesseur, un signal nommé signal équitemps.

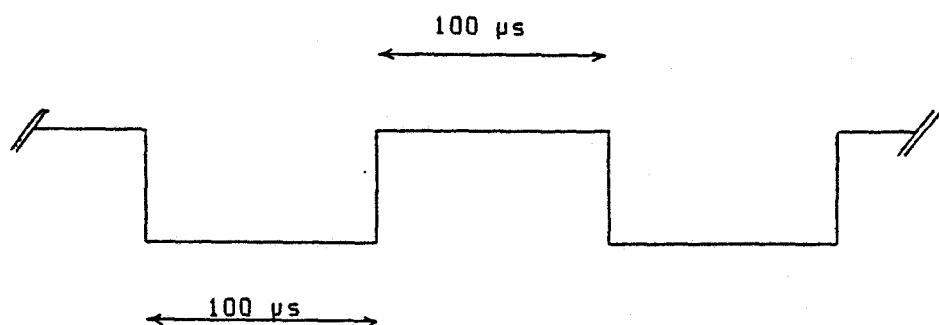

Ce dernier est un créneau de fréquence fixe 5 kHz et de rapport cyclique fixe 1/2.

Ce signal est émis en permanence durant l'exécution du programme et toute variation de fréquence et/ou de rapport cyclique traduit un mauvais fonctionnement du microprocesseur.

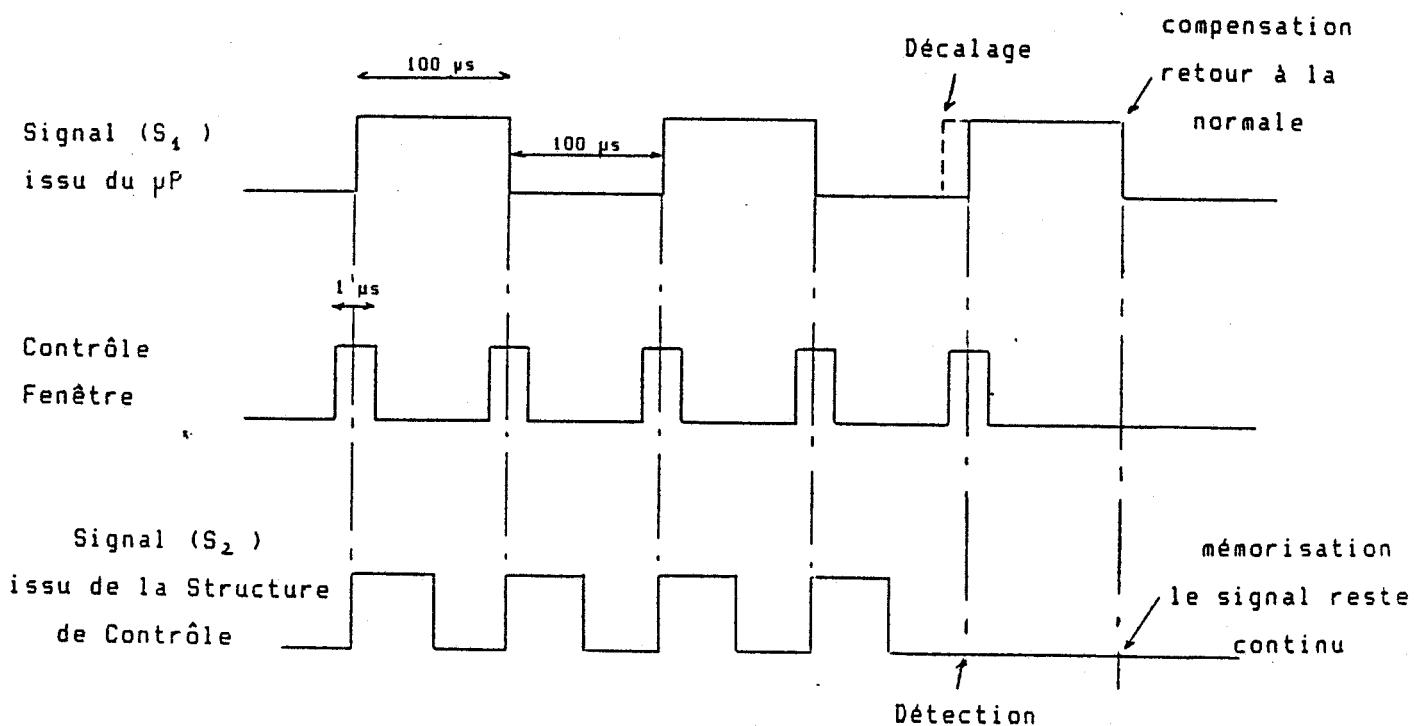

Le signal équitemps est surveillé par une structure de contrôle externe (REF.BAR) qui décide de la conformité ou non de ce signal. Un écart de 1μs (ou plus) est détecté; 1μs correspondant à la durée minimale d'une instruction du microprocesseur choisi (le 8031 de Intel) et fonctionnant avec une horloge de 12MHz.

## FONCTIONNEMENT DE LA STRUCTURE DE CONTROLE

Dès qu'un front du signal équitemps ne se présente pas dans la fenêtre de  $1\mu s$ , il y a détection de l'erreur.

De plus, elle est mémorisée puisque la structure de contrôle ne peut plus retourner dans l'état lui permettant de délivrer à nouveau un signal de bon fonctionnement même si par ailleurs le front suivant se présente dans la fenêtre; ceci permet de s'affranchir des possibilités de compensation d'erreurs.

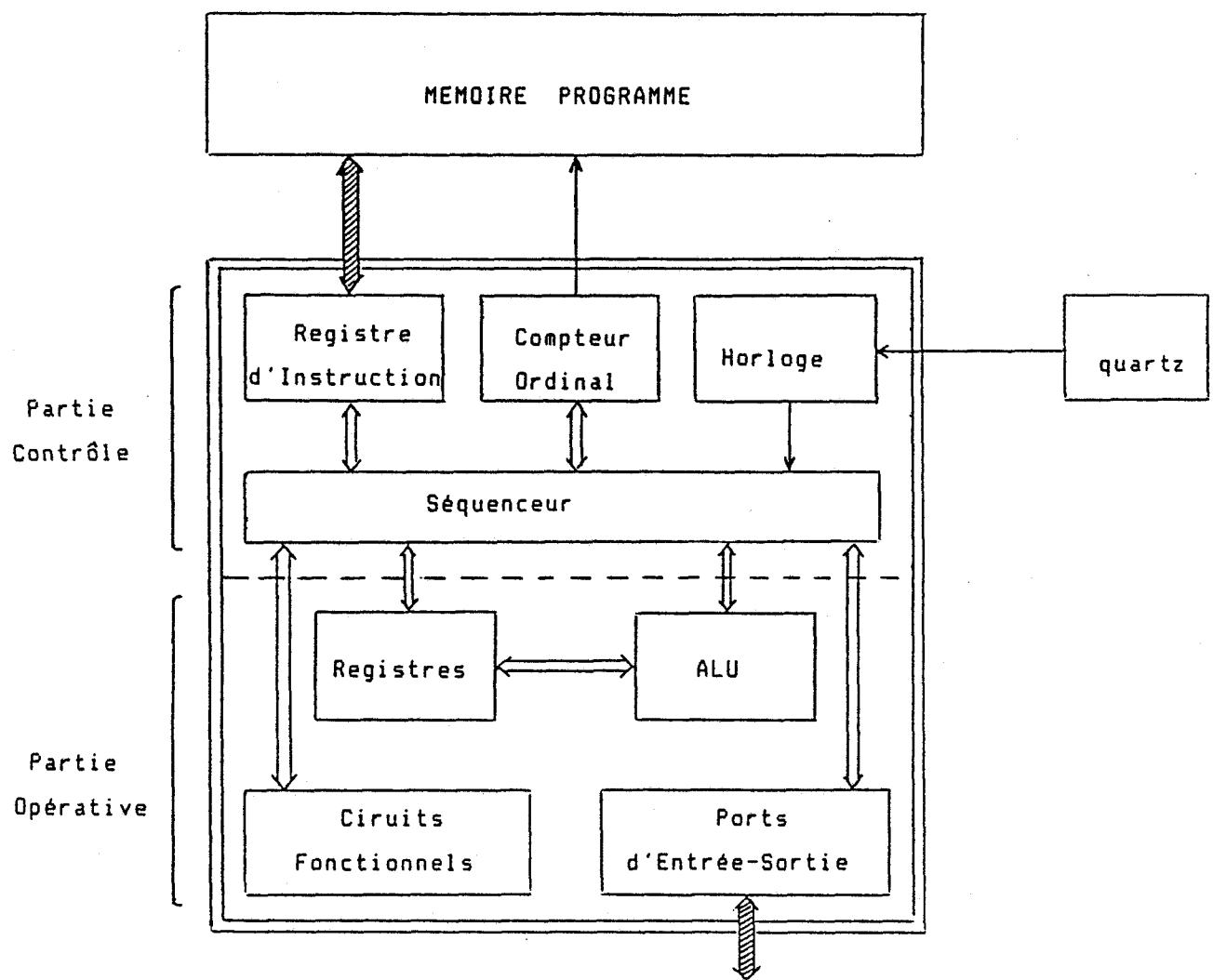

### SYNOPTIQUE DE L'UNITE DE TRAITEMENT

TM : Télémesure      TC : Télécommande

L'observation temporelle ou contrôle du signal équitemps permet de détecter les défaillances du microprocesseur si celles-ci modifient naturellement la durée d'exécution du programme.

Toutefois, il est nécessaire d'introduire des procédures de test de la partie opérative du microprocesseur, partie essentiellement logique dont les défauts n'altèrent pas forcément le signal équitemps.

En effet:

- le temps d'exécution d'une opération arithmétique ou logique défectueuse n'est pas nécessairement altéré bien que le résultat de l'opération soit faux

- le rangement d'une donnée au mauvais endroit peut durer le même temps que son rangement au bon endroit.

La contrainte majeure est d'éviter que le microprocesseur puisse, en cas de défaillance, envoyer des commandes qui rendent le processus dangereux. De ce fait, les programmes de test doivent permettre de savoir si le microprocesseur est défaillant ou non. La localisation du défaut n'est pas utile, seul l'aspect sécurité est étudié, la réparation se limitant au remplacement de la carte défectueuse.

Les routines de test sont donc organisées de manière à altérer le signal équitemps en cas de défaillance du microprocesseur.

De ce fait :

le schéma général de l'unité de traitement présenté précédemment suffit, seule la taille de la ROM est augmentée.

la structure de contrôle, en validant ou non le signal équitemps, sert donc aussi de contrôleur de logiciel de test.

Les programmes de test doivent, de plus, s'imbriquer parfaitement dans le programme principal, ne pas en gêner le déroulement normal ni altérer le signal équitemps lors du passage d'un programme à l'autre.

Les programmes de test sont donc découpés en modules et un module est exécuté entre deux traitements de place de réseau de Pétri (que les transitions soient ou non franchies).

L'évolution du processus à commander étant lente vis à vis de la durée de traitement d'une place, le microprocesseur peut, par rapport au processus, rester oisif 90% du temps; ce temps disponible est mis à profit pour exécuter les routines de test.

## II.2) Les tests fonctionnels.

Les tests fonctionnels comme le nom l'indique servent à tester les fonctions réalisées par le microprocesseur. Ils portent essentiellement sur la partie opérative du microprocesseur :

éléments de mémorisation: registres, ROM, RAM

opérateurs: UAL, circuits de décalage,...

bus de données et d'adresses, circuit d'adressage...

La partie opérative est décomposée en blocs testés individuellement.

La partie contrôle du microprocesseur ( séquenceur, décodeur d'instructions et d'adresses,...) n'est pas directement accessible à l'utilisateur, elle ne peut donc être testée que par ses actions à travers la partie opérative. De plus, c'est elle qui coordonne le fonctionnement du microprocesseur (séquencement) et une défaillance à ce niveau a de forte chance de se traduire par des décalages temporels.

Les hypothèses de pannes portent donc essentiellement sur la partie opérative qui est la seule directement accessible à l'utilisateur donc au test.

Le chapitre 3 présente la démarche suivie lors de l'élaboration de ces programmes de test.

### III) LES TESTS FONCTIONNELS (REF MAG-S).

#### III.1) Les hypothèses de pannes sur la partie opérative.

La partie opérative est constituée :

- des éléments de mémorisation

- des opérateurs (UAL,...)

- des bus de données et d'adresses et circuits d'adressage

##### III.1.1) Les éléments de mémorisation.

Pour chaque registre et pour un registre et son voisin (test de diaphonie), on considère:

- les collages simples ou multiples de n bits quelconques

- les courts-circuits (couplage) de type ET ou OU entre un nombre quelconque de bits.

##### III.1.2) Les opérateurs.

On distingue deux types de pannes dans les opérateurs:

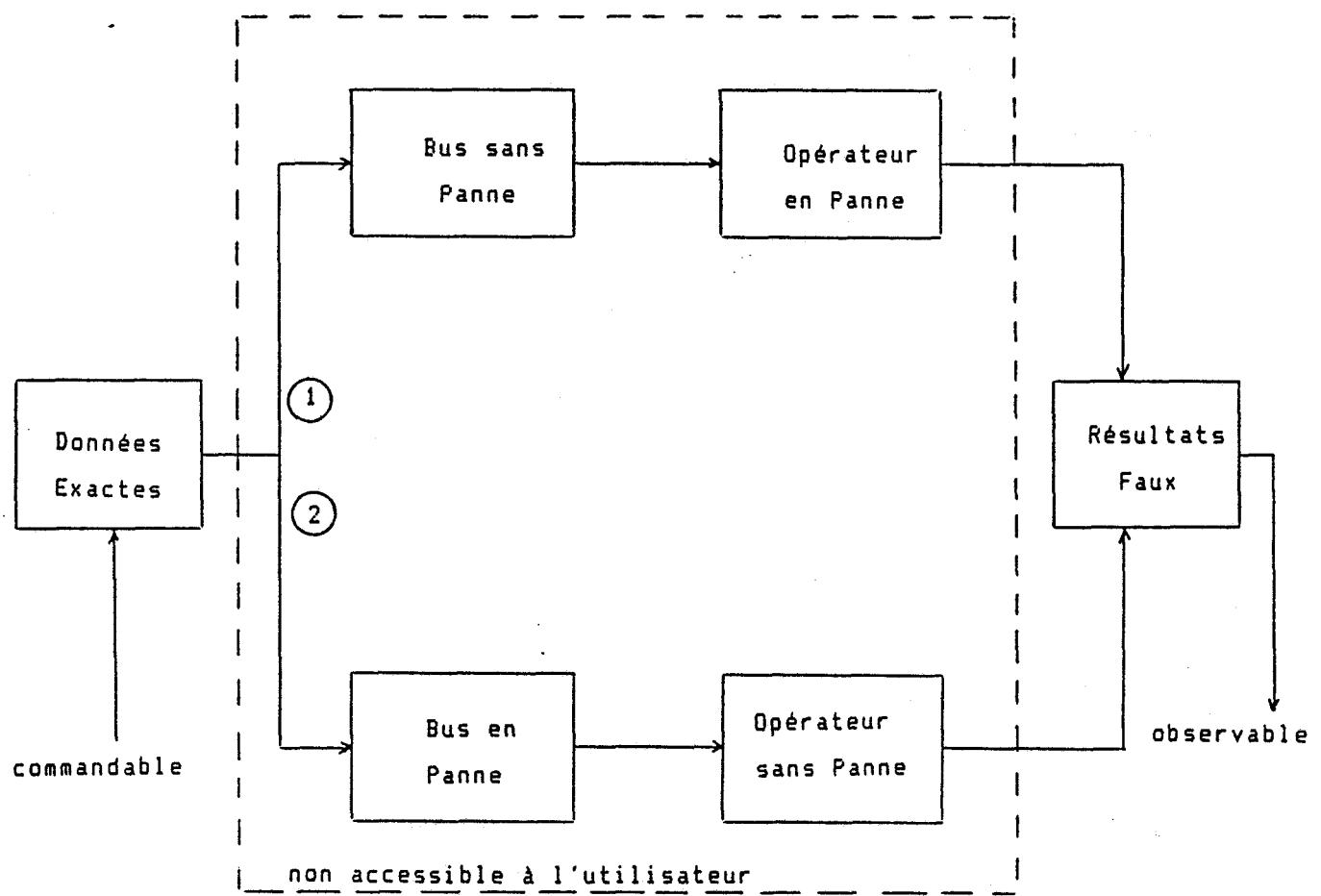

###### III.1.2.a) les pannes externes

Elles agissent sur les bus situés entre l'opérateur et ses registres opérandes ou résultats. Les pannes externes sont du type collage ou couplage, simples ou multiples, sur chacun de ces bus.

Il suffit donc, pour tester le bus entre l'opérateur et le registre résultat, de vérifier qu'il n'y a pas de collage ou de couplage des bits du résultat.

Un fonctionnement défectueux du bus reliant un registre opérande à l'opérateur amène des données fausses à l'entrée de celui-ci. Ceci est équivalent, vis à vis du test, à la présence de données exactes à l'entrée d'un opérateur défectueux.

Le test sera complet à condition d'obtenir un résultat faux que les données transittent par le chemin 1 ou le chemin 2 .

Le but du test est de détecter les défaillances du microprocesseur et non pas de les localiser; les pannes affectant le bus d'entrée sont donc détectées lors des tests détectant les pannes internes à l'opérateur.

### III.1.2.b) les pannes internes.

Ce sont des pannes qui influent sur l'interdépendance des bits du résultat de l'opération. Par exemple, pour un additionneur, il faut vérifier qu'il n'y a pas de collage ou de couplage affectant les retenues.

Il faut, de plus, vérifier la fonction réalisée par l'opérateur.

### III.1.3) Les bus.

Comme pour les pannes externes des opérateurs, les pannes sur les bus peuvent être ramenées à des pannes sur les registres ou les opérateurs.

Les bus ne sont donc pas testés directement puisqu'un couplage ou collage, simple ou multiple est détecté lors des tests des registres ou des opérateurs.

Rappelons que le but est de détecter les pannes et non pas de les localiser; il n'y a donc pas de tests spécifiques des bus puisque ces pannes sont détectées par ailleurs.

## III.2) Modélisation du fonctionnement du microprocesseur.

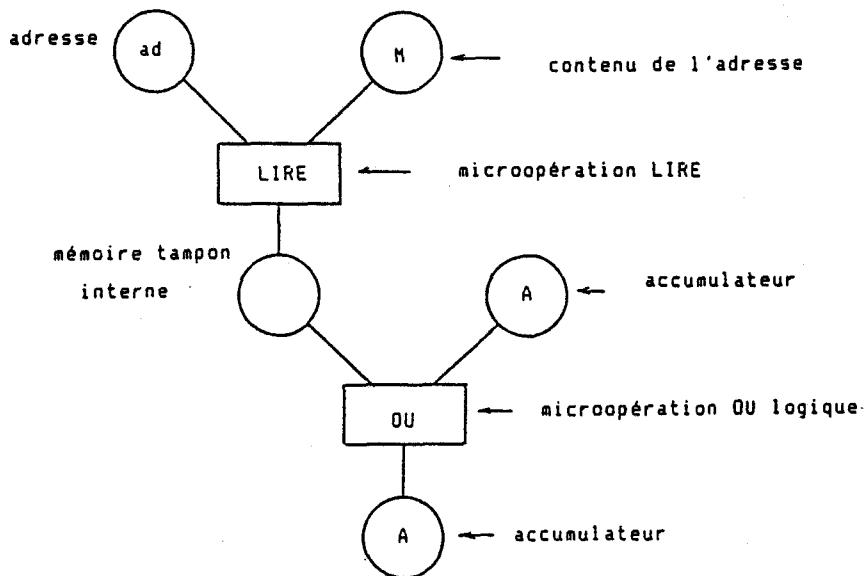

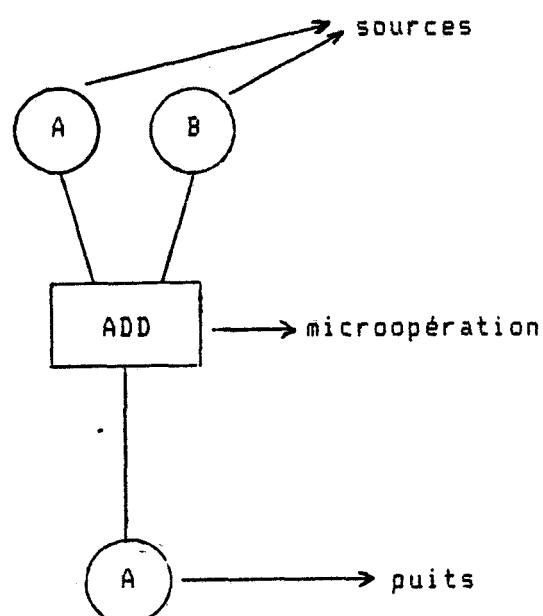

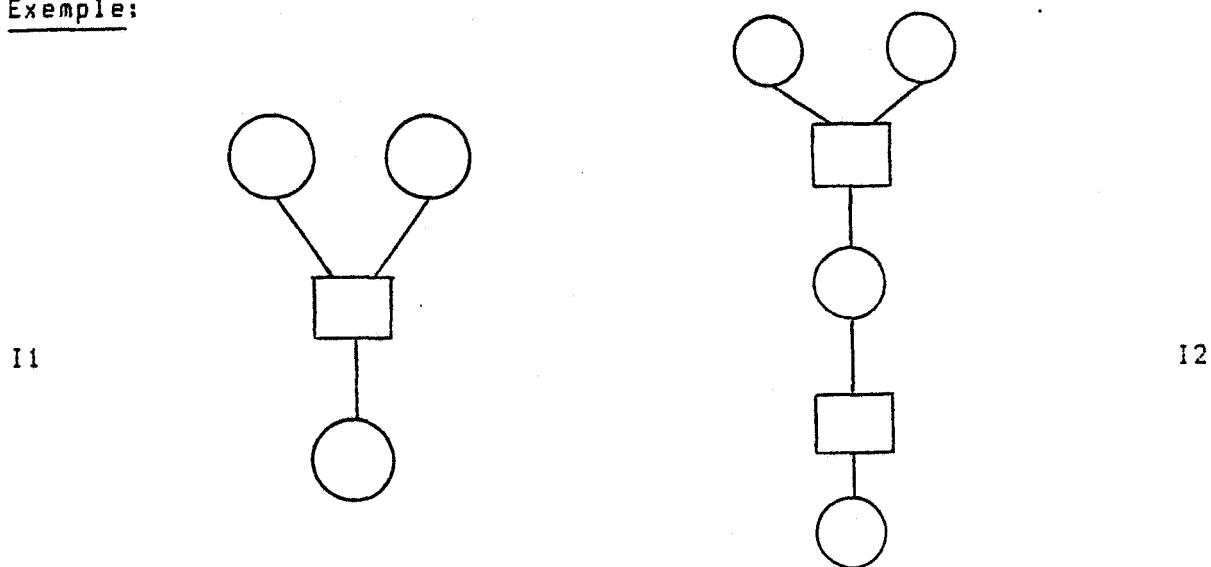

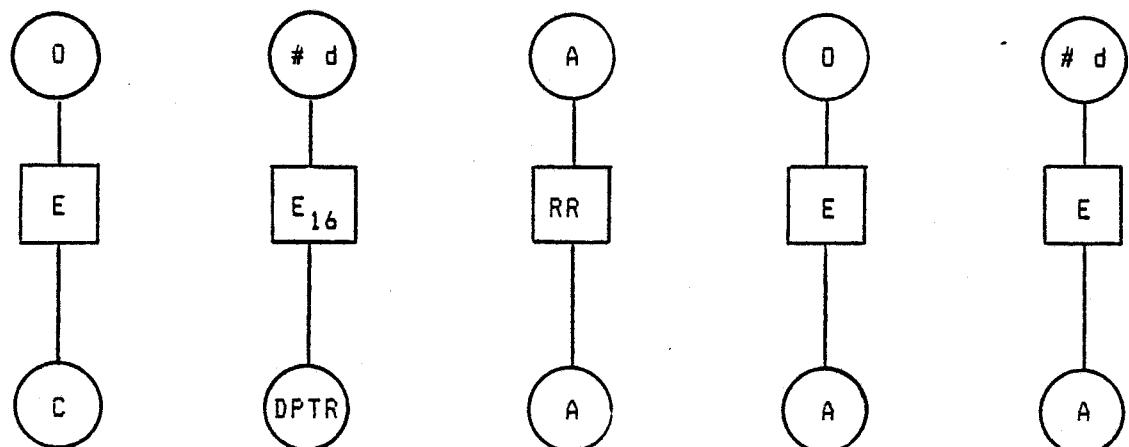

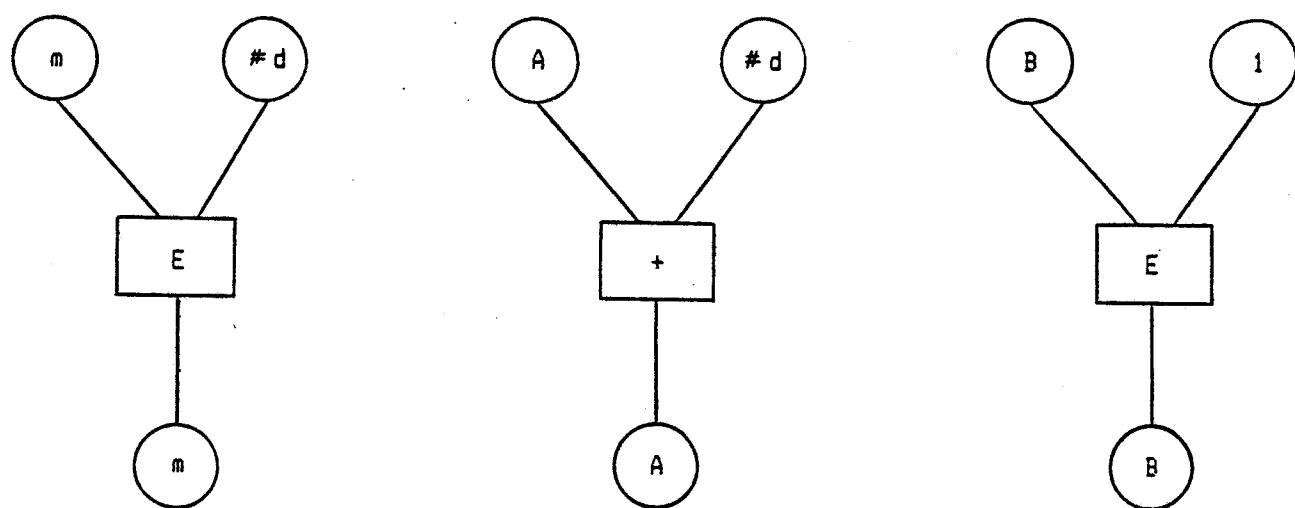

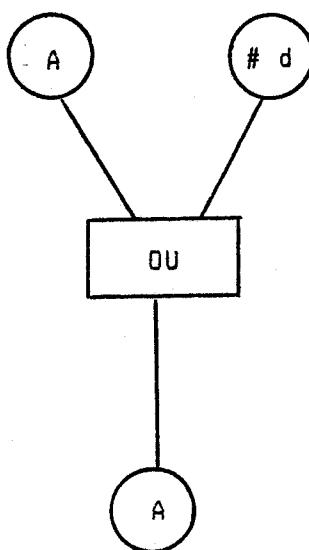

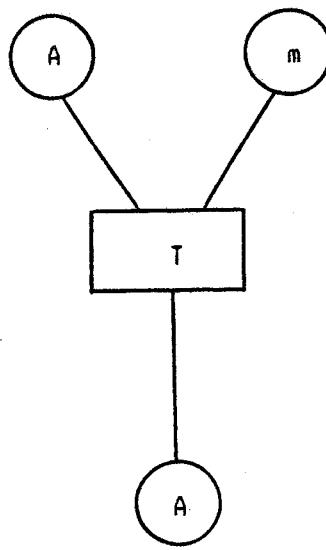

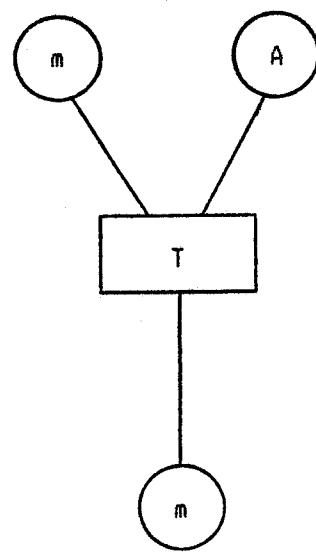

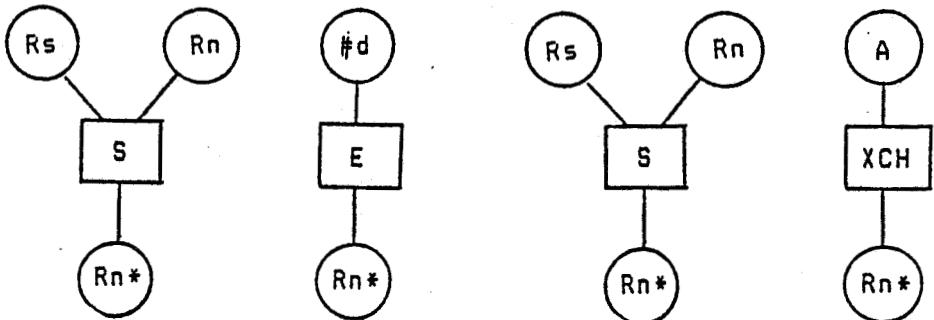

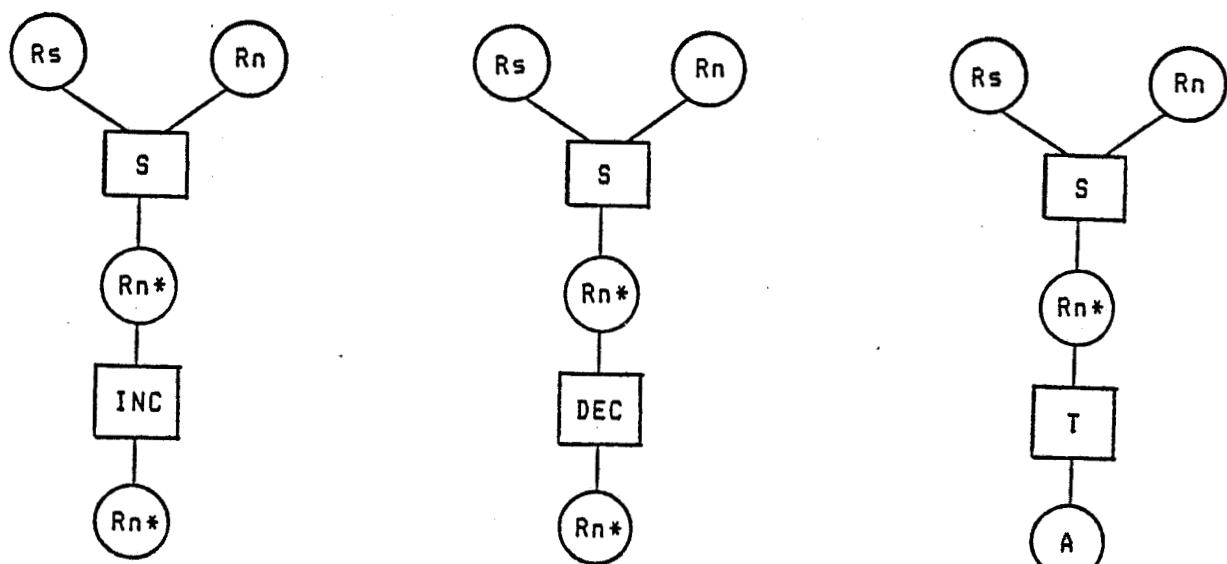

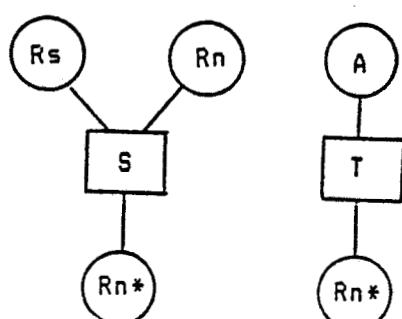

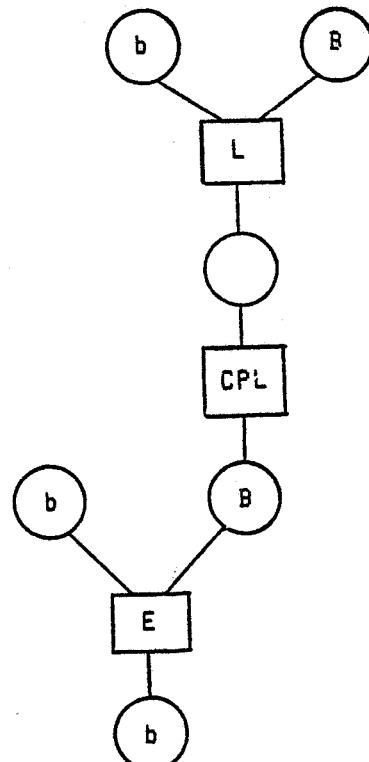

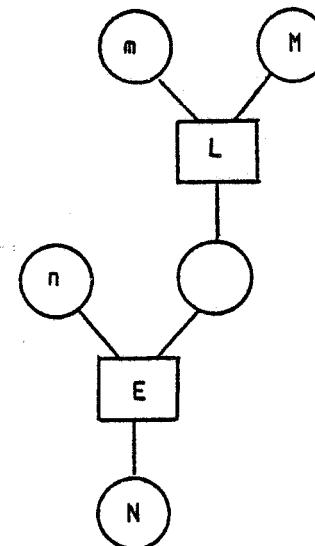

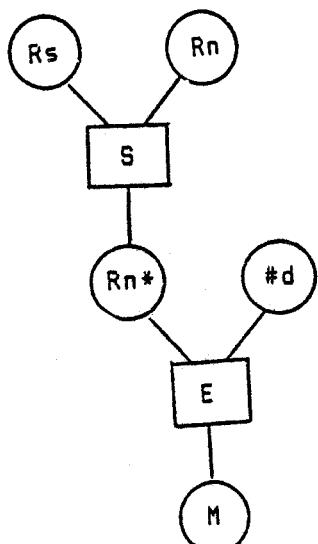

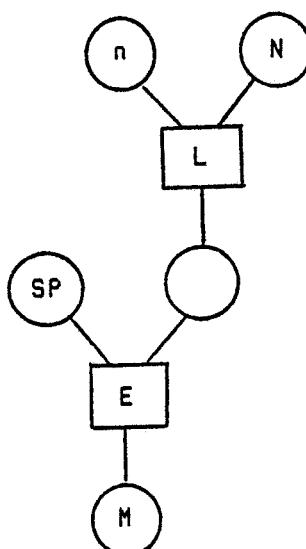

### III.2.1) Les graphes d'exécution abstraite (REF.ROB).

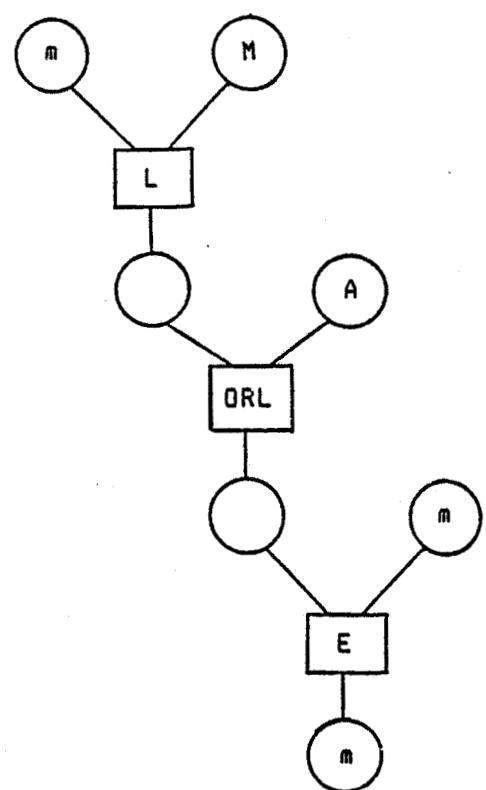

Les fonctions et les unités fonctionnelles activées par chaque instruction peuvent être représentées par des graphes d'exécution abstraite.

Le lecteur trouvera en annexe II la description des méthodes d'obtention et d'analyse de ces graphes ainsi que la représentation graphique des instructions utilisées dans les programmes d'application.

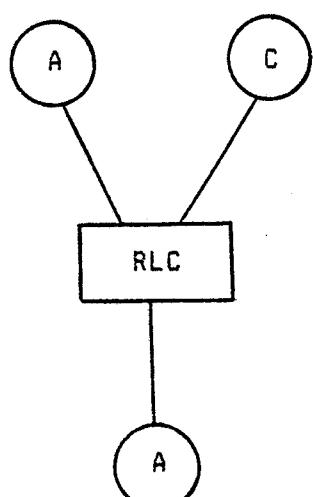

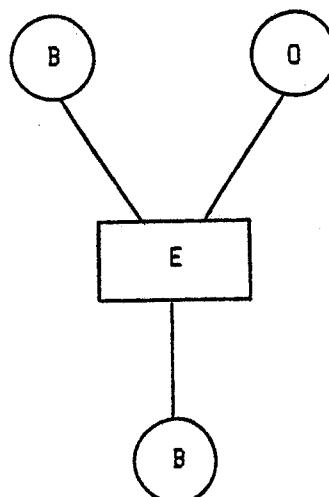

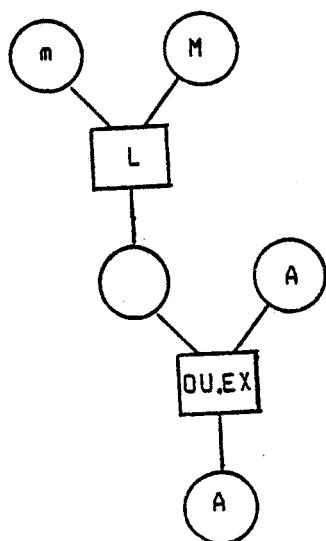

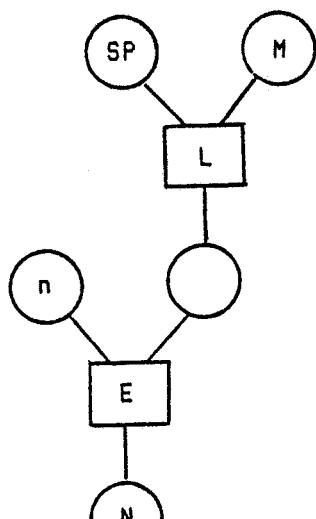

Le graphe suivant décrit l'instruction "ORL A, adresse" qui réalise un OU logique entre l'accumulateur et le contenu d'une adresse, le résultat étant disponible dans l'accumulateur

### III.2.2) Analyse des graphes.

La liste des instructions du microprocesseur utilisé dans l'application (le 8031 de Intel) est donnée en annexe I.

Une étude effectuée sur ce microprocesseur a donné les résultats suivants:

L'ensemble  $D$  des instructions structurellement dominantes est constitué de :

A cet ensemble, il faut ajouter un certain nombre d'instructions, constituant l'ensemble I, afin d'exciter chacune des micro-opérations

- \* CPL complémentation

- \* RR rotation à droite

- \* RL rotation à gauche

- \* RRC rotation à droite à travers la retenue

- \* RLC rotation à gauche à travers la retenue

- \* MUL multiplication

- \* DIV division

- \* ANL ET logique

- \* ORL OU logique

- \* DA ajustement décimal

- \* XRL OU exclusif

- \* XCH échange des contenus de deux registres

- \* CLR remise à zéro d'un registre

- \* SWAP échange des demi octets d'un registre.

### III.2.3) Restrictions nécessitées par l'application.

Le but principal de l'introduction de programmes de test dans le programme d'application est d'éliminer les mauvais fonctionnements possibles dûs à une défaillance du microprocesseur.

Nous n'envisageons pas un test exhaustif du microprocesseur mais uniquement un test des parties du circuit utiles au programme d'application (et au programme de test). Il n'y a donc que les instructions utilisées qui sont testées.

Un test complet du microprocesseur nécessite le test des instructions de l'ensemble D u I (définis précédemment). Compte tenu de la remarque qui vient d'être faite, les instructions non utilisées sont éliminées de cet ensemble.

Pour traiter les graphes de Pétri avec un 8031 selon la méthode développée dans REF.ELK il ne nous faut tester que:

- les cinq instructions structurellement dominantes

- les instructions CPL, RR, RLC, ANL, ORL, XRL, XCH ET CLR de l'ensemble I.

A ceci, il faut ajouter le test des unités fonctionnelles propres au 8031: la RAM, l'EPROM, le contrôleur d'interruptions et les timers.

- les tests de la RAM et de l'EPROM sont envisagés

- le contrôleur d'interruptions n'est pas utilisé; si, lors d'un mauvais fonctionnement, une interruption est autorisée, le signal équitemps est altéré, il n'est donc pas nécessaire de tester ce contrôleur.

- un des timers est inutilisé, l'autre sert de générateur de bauds pour l'UART pour la télésurveillance du fonctionnement du processus. Le contrôle du bon fonctionnement de ces unités est effectué par ailleurs (mise en sécurité des transmissions REF.QUA, REF MAG-C).

Dans les paragraphes suivants, nous présentons les tests des différentes unités du microprocesseur ainsi que leur mise en œuvre dans l'application étudiée.

### III.3) Le test des instructions arithmétiques et logiques.

Un test exhaustif des instructions arithmétiques et logiques requiert le test de chaque fonction pour toutes les combinaisons des 256 valeurs possibles de chaque opérande (soient 65536 combinaisons de deux opérandes de 8 bits).

Un test exhaustif n'est donc pas envisageable, il faut alors trouver un algorithme de recherche des vecteurs de test qui permette l'investigation la plus complète possible de chaque fonction par un nombre raisonnable de vecteurs.

### III.3.1) Décomposition des fonctions arithmétiques et logiques.

Soit  $f$  une fonction arithmétique ou logique de deux opérandes  $X$  et  $Y$  qui donne un résultat  $Z$ :

$$Z = f(X, Y)$$

Par une décomposition booléenne des opérandes et du résultat, on obtient:

$$(z_0, z_1, z_2, \dots, z_n) = f(x_0, x_1, x_2, \dots, x_n, y_0, y_1, y_2, \dots, y_n)$$

avec  $n \geq 1$

Toute fonction générale peut être décomposée en un système de plusieurs fonctions simples:

$$z_0 = f_0(x_0, \dots, x_n, y_0, \dots, y_n)$$

$$z_1 = f_1(x_0, \dots, x_n, y_0, \dots, y_n)$$

*8*      *9*      *10*      *11*      *12*

• • • • •

• • • • •

10. The following table shows the number of hours worked by 1000 employees in a company.

$$z = f_-(x_1 - \dots - x_n, y - \dots)$$

On cherche à écrire les fonctions  $f_i$  de manière à mettre en évidence la dépendance entre la  $i$ ème composante du résultat et les  $i$ èmes composantes des opérandes.

$$z_i = f_i(X, Y) = \bar{x}_i \bar{y}_i C_i^0 + \bar{x}_i y_i C_i^1 + x_i \bar{y}_i C_i^2 + x_i y_i C_i^3$$

Les fonctions  $C_i^j$  sont appelées fonctions contextes, ce sont des fonctions booléennes des variables  $x_k$  et  $y_k$  avec  $k \neq i$ .

Pour les fonctions logiques, les fonctions contextes sont des fonctions constantes.

ex: Pour la fonction OU exclusif :

$$z_i = f_i(X, Y) = \bar{x}_i \bar{y}_i 0 + \bar{x}_i y_i 1 + x_i \bar{y}_i 1 + x_i y_i 0$$

Pour les fonctions arithmétiques, les fonctions contextes correspondent à la fonction "génération de retenues".

ex: Pour l'addition :

$$z_i = f_i(X, Y) = \bar{x}_i \bar{y}_i C_i^0 + \bar{x}_i y_i C_i^1 + x_i \bar{y}_i C_i^2 + x_i y_i C_i^3$$

avec  $C_i^0 = C_i^3 = C_i = (x_{i-1}) \cdot (y_{i-1}) + C_{i-1} (x_{i-1} + y_{i-1}) ; C_i^1 = C_i^2 = C_i$

Le choix des opérandes de test des fonctions arithmétiques et logiques se fait donc de cette manière:

- Toutes les combinaisons des  $i$ èmes bits des opérandes

- Si les fonctions contextes ne sont pas constantes, elles prennent successivement la valeur 1 et la valeur 0.

Le test consiste alors à regarder la valeur du  $i$ ème bit du résultat (et du  $(i+1)$ ème bit si on fait une opération arithmétique) pour chacune des combinaisons des  $i$ èmes bits des opérandes (les  $(i-1)$ èmes bits des opérandes servent à affecter une valeur à la fonction contexte pour les opérations arithmétiques), la valeur des autres bits du résultat et des opérandes étant indifférente.

### III.3.2) Le test des couplages.

Les vecteurs de test déterminés précédemment permettent de vérifier le fonctionnement de l'instruction au niveau de la fonction réalisée mais, ne testent pas l'absence de collage ou de couplage des bits du résultat.

Les couplages sont de quatre types:

- a) le couplage  $C_1$  : le passage à 1 d'un bit du résultat entraîne le passage à 1 d'un autre bit

- b) le couplage  $C_2$  : le passage à 0 d'un bit du résultat entraîne le passage à 0 d'un autre bit

- c) le couplage  $C_3$  : le passage à 1 d'un bit du résultat entraîne le passage à 0 d'un autre bit

- d) le couplage  $C_4$  : le passage à 0 d'un bit du résultat entraîne le passage à 1 d'un autre bit.

Pour détecter ces couplages, il suffit d'avoir un résultat du type:

- a) 00000100; Seul le ième bit du résultat est à 1, tous les autres sont à 0. On vérifie ainsi que le passage à 1 du ième bit n'entraîne pas le passage à 1 d'un autre bit (couplage  $C_1$ ). Ce type de résultat doit être obtenu au moins une fois pour chaque i, i variant de 0 à 7.

- b) 11110111; Seul le ième bit du résultat est à 0, tous les autres sont à 1. Un raisonnement analogue au précédent est tenu mais dans le cas du couplage  $C_2$ .

- c) 11111111; Tous les bits sont à 1. Ceci permet de détecter les couplages du type C<sub>3</sub> entre un ou plusieurs bits du résultat.

- d) 00000000; Tous les bits sont à 0. Ceci permet de détecter les couplages du type C<sub>4</sub> entre un ou plusieurs bits du résultat.

Pour révéler tous ces couplages sans augmenter le nombre de vecteurs de test, il suffit de donner une valeur précise aux bits dont la valeur était indifférente au paragraphe III.3.1 de manière à obtenir les résultats des quatre types qui viennent d'être présentés.

Les vecteurs de test ainsi déterminés permettent aussi de détecter les collages de un ou plusieurs bits du résultat.

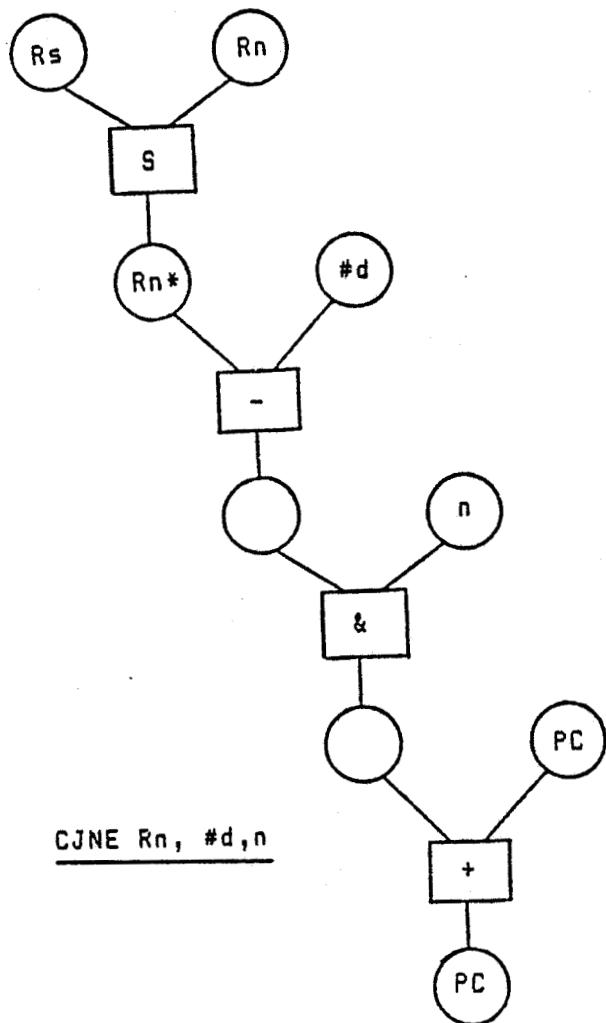

#### III.4) Les autres instructions.

Le raisonnement qui vient d'être tenu est étendu aux instructions "non arithmétiques ou logiques" ( CJNE, RR,...).

Ces instructions ne peuvent pas être décomposées mathématiquement de façon rigoureuse comme les instructions arithmétiques et logiques; néanmoins une méthode analogue est utilisée pour déterminer les vecteurs de test:

- ils doivent permettre de vérifier le fonctionnement de l'instruction pour toutes les combinaisons de valeurs des bits de rang i des opérandes et ce pour  $0 \leq i \leq 7$ .

- de plus, les valeurs des bits de rang j ( $j \neq i$ ) sont choisies de manière à tester tous les couplages des bits du résultat.

### III.5) Le test de la RAM.

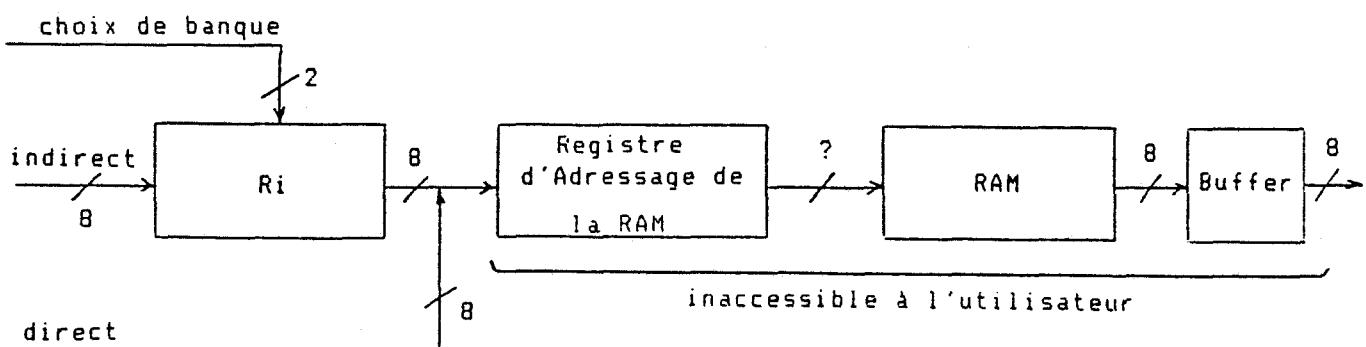

#### III.5.1) Le test des modes d'adressage.

Les défaillances survenant lors de l'adressage d'un registre Ri peuvent avoir les conséquences suivantes:

- aucun registre n'est adressé

- un ou plusieurs registres Rj sont adressés à la place du registre Ri

- un ou plusieurs registres Rj sont adressés en plus du registre Ri.

Ces défauts ne peuvent être détectés que s'ils sont la conséquence d'une défaillance d'un mécanisme d'adressage (par comparaison de l'adressage d'un même registre par deux méthodes différentes: directe et indirecte). Par contre si c'est le registre d'adressage de la RAM qui est défaillant, l'erreur ne peut être détectée par comparaison des deux modes d'adressages (pannes de mode commun).

La vérification des mécanismes d'adressage (direct et indirect) peut se décomposer en trois parties:

- vérification de l'écriture de toutes les données

- vérification de la lecture de toutes les données

- vérification de l'adressage de tous les registres

Le test de l'adressage bit à bit d'un registre n'est pas envisagé puisque ce mode d'adressage n'est pas utilisé.

### III.5.1.a) Vérification de lecture et écriture.

Pour un registre déterminé, il faut vérifier que toutes les données possibles (256 valeurs pour des registres de 8 bits) écrites de façon directe (resp. indirecte) peuvent être lues de façon indirecte (resp. directe).

L'utilisation des deux modes d'adressage permet de s'affranchir des pannes d'un mécanisme d'adressage si l'autre est sans défaut (ou s'il a un défaut dont les conséquences n'entraînent pas la compensation des erreurs).

### III.5.1.b) Vérification de l'adressage des registres.

Il faut vérifier que tous les registres de la RAM peuvent être adressés. C'est essentiellement l'adressage indirect qui est testé puisque c'est le mode d'adressage qui met en oeuvre le plus grand nombre d'éléments du microprocesseur.

Le registre adressé indirectement est comparé au registre adressé directement (en l'absence de panne, c'est le même). Le test exhaustif de l'adressage de tous les registres de la RAM n'est pas utile. En effet, lors de la comparaison des deux mécanismes d'adressage, il apparaît qu'il suffit de vérifier l'absence de collage ou de couplage sur les 8 bits d'adresse, le reste étant commun aux divers modes d'adressage (c'est la panne de mode commun évoquée précédemment).

### MECANISME D'ADRESSAGE

La vérification de l'adressage par la comparaison des deux modes d'adressage direct et indirect se limite donc aux cas suivants:

adresses

testées

00 H ————— couplage 0 ---> 1 (couplage C<sub>1</sub>)

01 H

02 H

04 H

08 H ————— couplage 1 ---> 1 (couplage C<sub>2</sub>)

10 H

20 H

40 H

7F H ————— couplage 1 ---> 0 (couplage C<sub>3</sub>)

7E H

7D H

7B H

77 H ————— couplage 0 ---> 0 (couplage C<sub>4</sub>)

6F H

5F H

3F H

La définition des différents couplages ainsi que la détermination des octets correspondants sont présentées au paragraphe III (test des instructions arithmétiques et logiques).

La méthode est identique mais ici le bit de rang 7 n'est pas pris en compte car il est inaccessible en adressage indirect (seule la zone RAM d'adresse 00 H à 7F H est accessible par adressage indirect sur le 8031).

### III.5.1.c) Adressage indirect par d'autres registres.

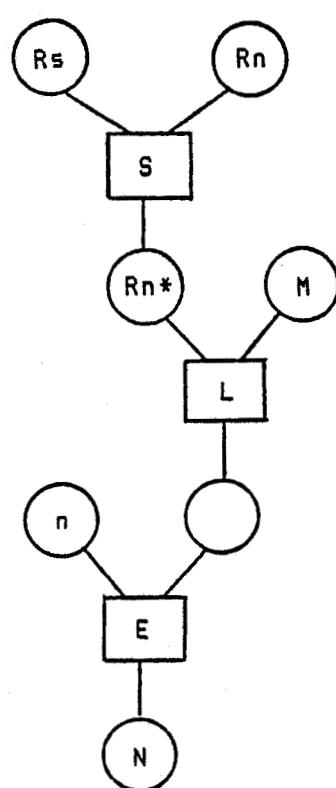

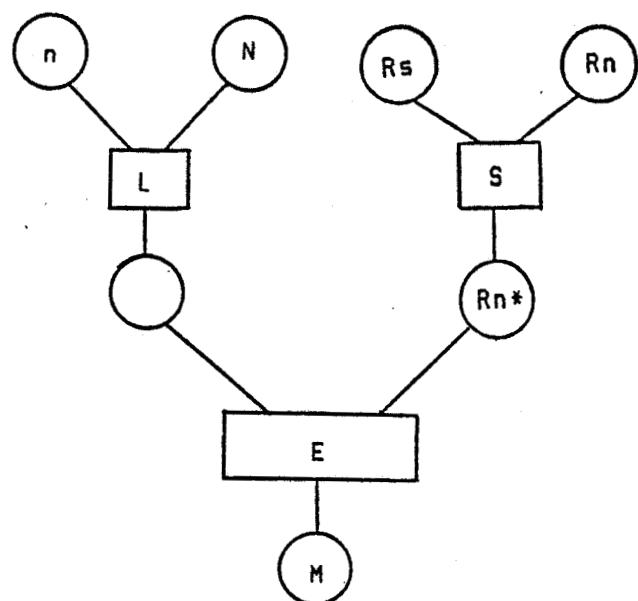

Il faut nécessairement tester l'adressage indirect par tous les registres possibles. Dans le cas du 8031, il n'y a que deux registres ( $R_0$  et  $R_1$ ) qui permettent l'adressage indirect.

Le test se limite aux zones RAM effectivement adressées par ces registres dans le programme d'application. Il s'effectue par comparaison des registres indirectement adressés par les deux registres  $R_0$  et  $R_1$ , autorisés (en l'absence d'erreur, ce sont les mêmes).

### III.5.2) Test du contenu de la RAM.

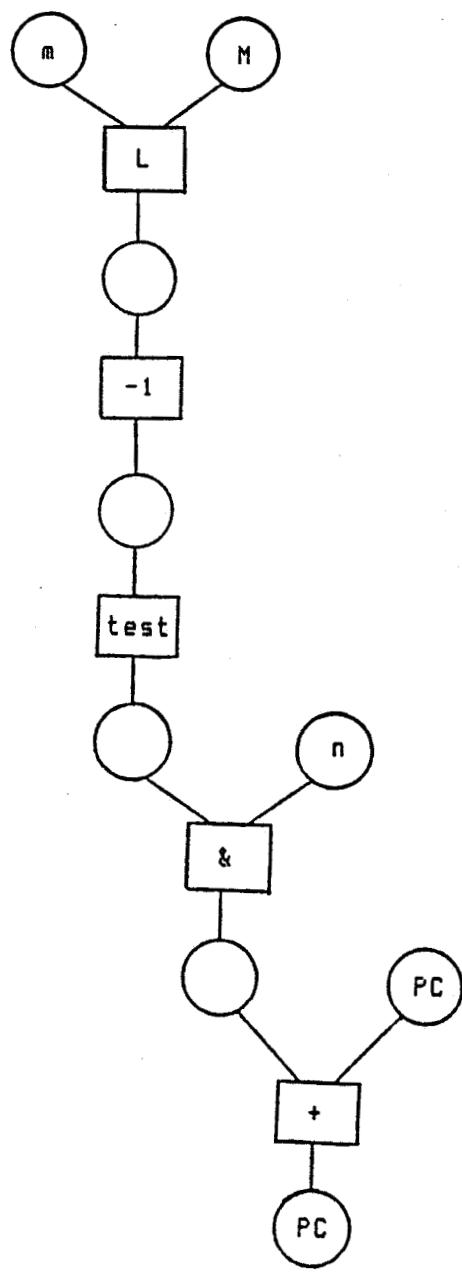

Le test du contenu de la RAM est effectué de façon exhaustive. Il est constitué de la vérification suivante: toutes les données (256 valeurs pour des registres de 8 bits) peuvent être écrites ou lues et ce, pour chaque registre de la RAM.

Il est évident que dans le cas présent, il était possible de limiter le nombre de vecteurs de test au nombre nécessaire à la détection des collages et des couplages des zones élémentaires de 1 bit constituant chaque registre. Compte tenu de l'algorithme de test utilisé (décrémentation et comparaison avec émission du signal équitemps), le test exhaustif est beaucoup moins couteux en octets et à peine plus couteux en temps que le test avec un nombre restreint de vecteur; le test exhaustif a donc été retenu.

### III.5.3) Le test de la diaphonie.

Ce test permet de vérifier l'absence de couplage entre deux bits de deux registres voisins. Le problème consiste à connaître l'implantation des cases mémoires dans la RAM afin de déterminer quel est le registre voisin d'un autre registre donné.

La RAM du 8031 est divisée en deux zones de 128 octets:

une première zone, dont les adresses sont comprises entre 00 H et 7F H, entièrement accessible à l'utilisateur et ,

une deuxième zone nommée RAM-SFR (Random Access Memory for Special Function Registers) dont une partie seulement est accessible à l'utilisateur: c'est dans cette zone que se situent les registres spéciaux (accumulateur, registre B, le pointeur de données, le pointeur de pile,...); ceux-ci sont testés individuellement.

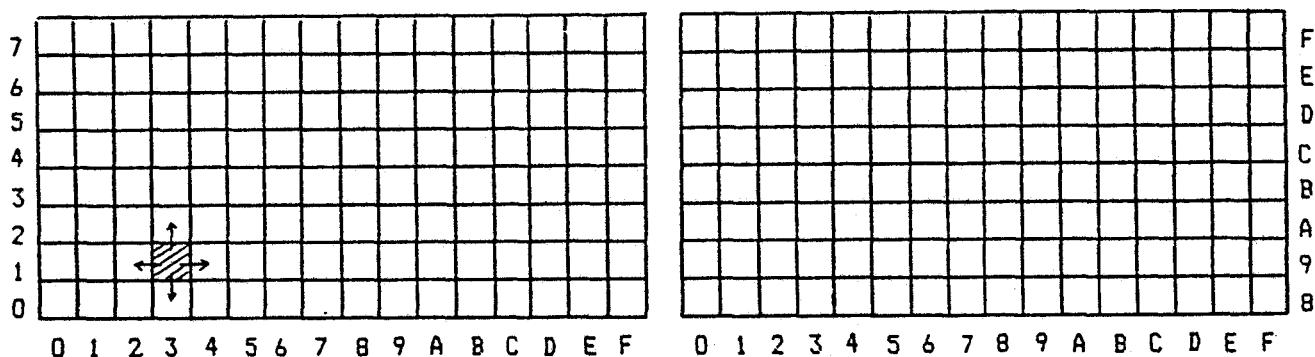

L'implantation des cases mémoires de la RAM peut être déduite des informations contenues dans REF.INT, elle pourrait donc être représentée par le schéma ci-dessous:

Sur cette figure, les flèches indiquent les différents couplages à tester pour la case d'adresse 13 H :

13 H <----> 23 H

13 H <----> 03 H

13 H <----> 12 H

13 H <----> 14 H

Il faut alors tester les couplages entre les registres:

- d'adresse X et X±10 H

- d'adresse X et X±01 H.

En fait, seule la moitié de ces couplages est testée puisque le couplage entre les registres d'adresses X et X+10 H est le même que celui entre les registres d'adresses (X+10 H) et (X+10 H)-10 H.

### III.5.4) Difficultés rencontrées.

- Le mécanisme d'adressage indirect utilise la pile du microprocesseur lors de son fonctionnement et le pointeur de pile, utile au programme d'application, peut contenir une adresse quelconque de la RAM. Il a donc fallu résoudre le problème de la sauvegarde de ce pointeur.

- Le test de la RAM s'effectue "en ligne", les registres contiennent donc des données nécessaires au bon fonctionnement du programme. Il est, de ce fait, indispensable de sauvegarder ces données avant de tester les registres qui les contiennent et de les réécrire correctement dans le registre d'origine avant leur utilisation par le programme principal.

### III.6) Le test de la ROM.

La ROM testée est une 27128 (16 k Octets).

Le test consiste en 16 "checksums". Chaque checksum est la somme arithmétique de tous les octets contenus dans 1 k Octets de mémoire, les valeurs justes des résultats sont mises sous la forme de 48 octets (3 octets par résultat) contenus dans un même k Octets de mémoire.

Ces tests permettent de détecter les changements d'un octet de la ROM, les problèmes de lecture, d'adressage,...et toutes les erreurs multiples qui ne se recombinent pas, et ceci par k Octets de programme.

Le test étant divisé en 16 checksums distinctes, la probabilité de compensation d'erreurs est plus faible que s'il était constitué d'une seule checksum sur 16 k Octets.

Ces checksums sont exécutées périodiquement à la même fréquence que les autres tests fonctionnels.

### III.7) Organisation du programme de test.

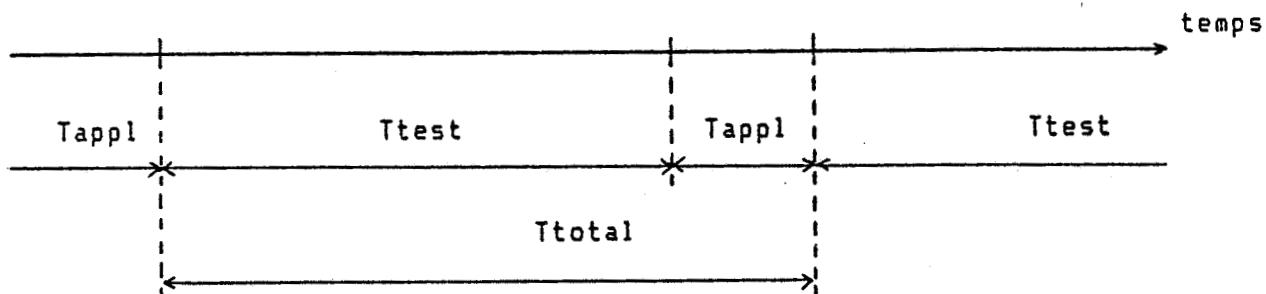

#### III.7.1) Durée des modules de test.

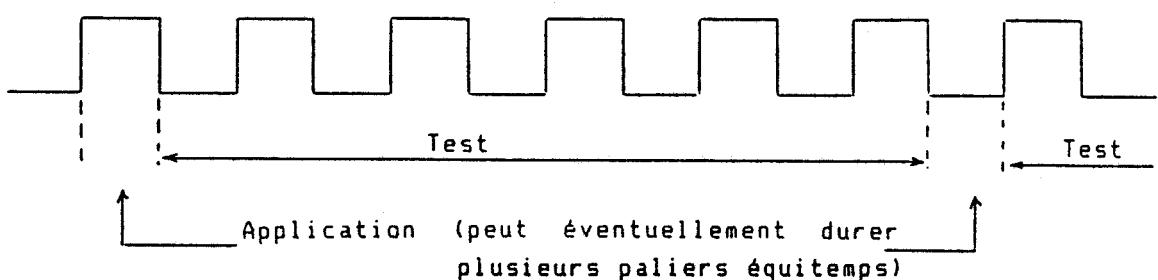

Le programme de test est découpé en modules de 1ms maximum pour ne pas gêner le fonctionnement du programme principal.

Le test d'une instruction ou d'une zone mémoire est effectué en un module et éventuellement en plusieurs modules partiels si la durée de ce test excède 1 ms.

#### III.7.2) Le contrôle des résultats.

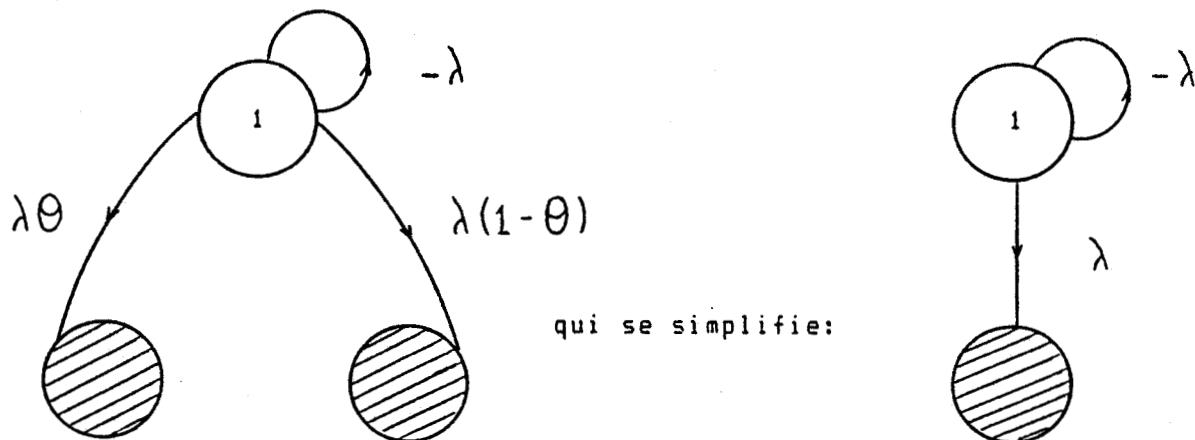

Il ne faut en aucun cas que ce soit le microprocesseur qui se déclare exempt de défaillance.

C'est le signal équitemps qui doit refléter le fonctionnement du microprocesseur.

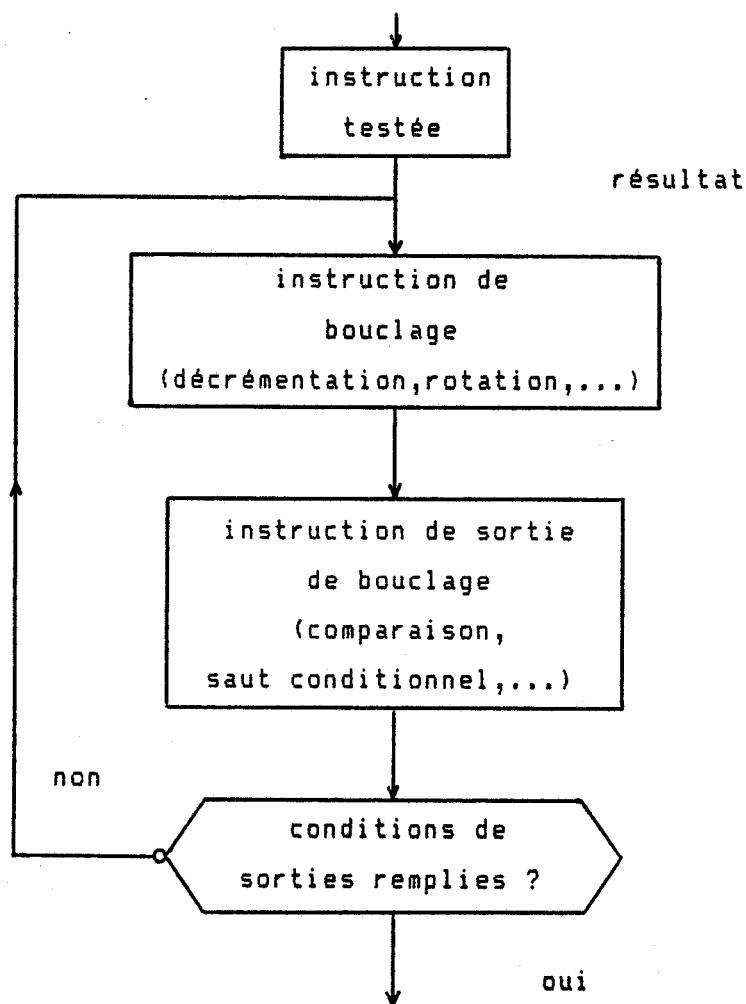

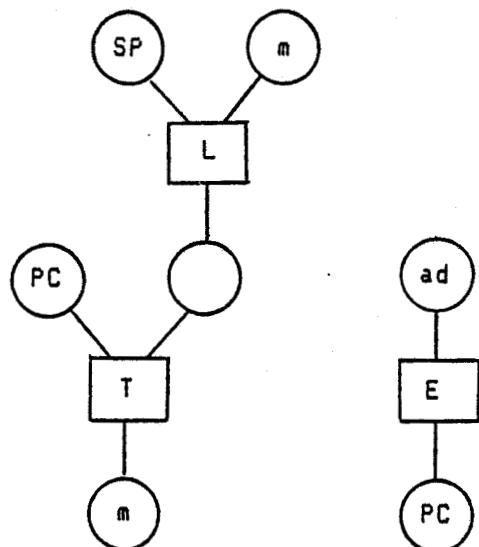

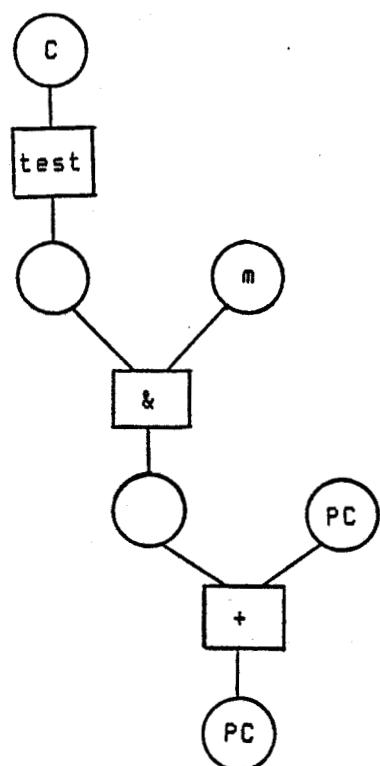

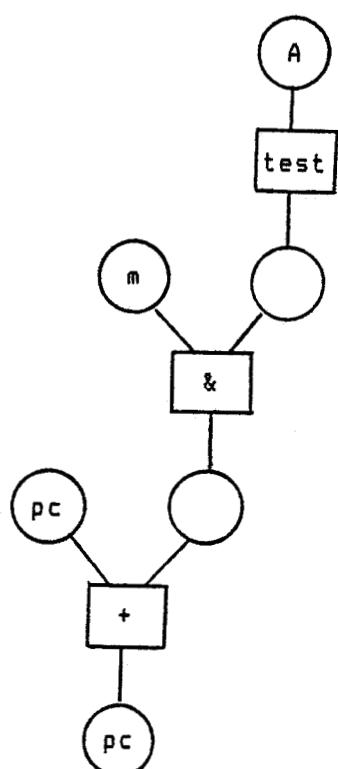

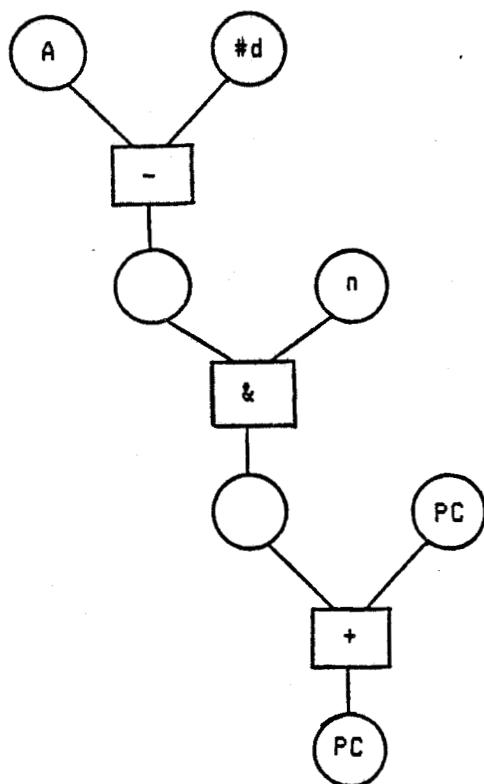

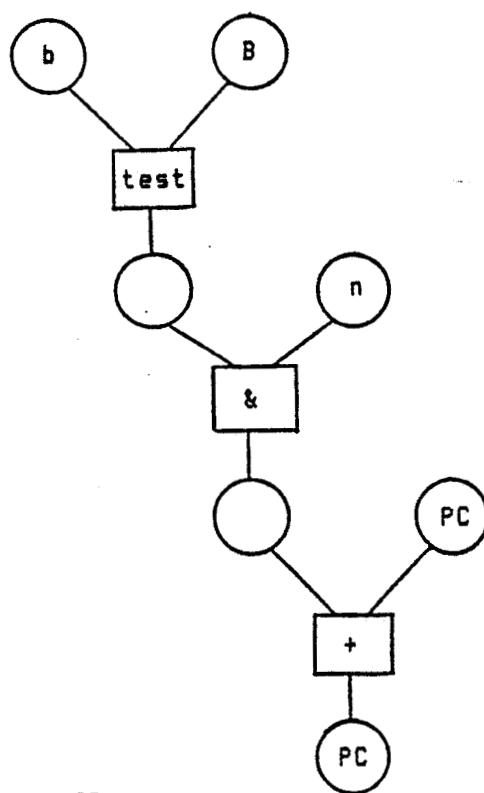

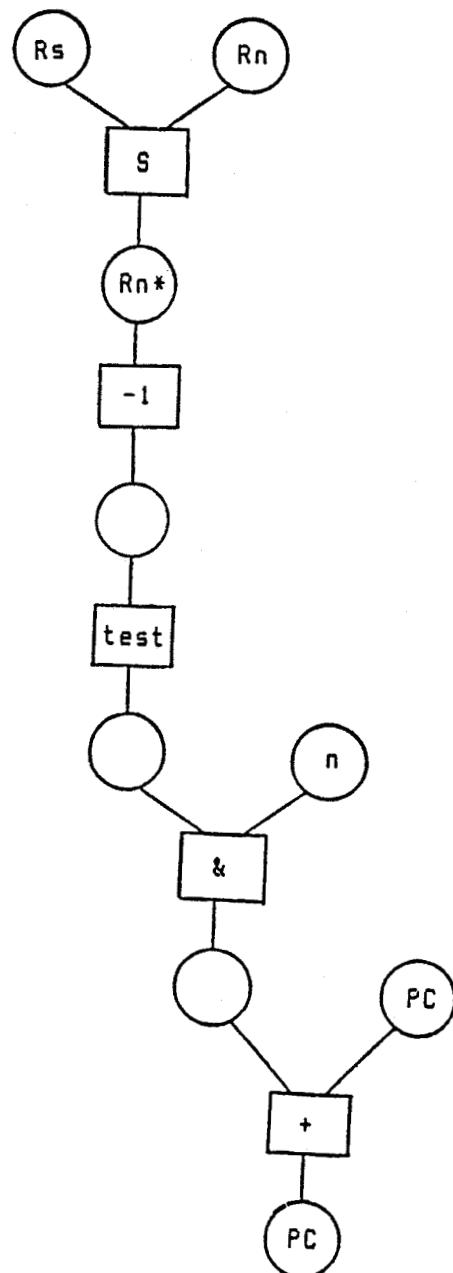

Le programme de test est donc organisé de manière telle que les résultats conditionnent les temps d'exécution des différentes routines; ceci est obtenu au moyen d'instructions de bouclage :

le nombre de boucles exécutées reflète la validité du résultat qui, de ce fait, n'est pas basée sur une seule instruction pouvant elle-même, s'avérer défaillante et donc déclarer juste un résultat faux.

Ce principe est illustré par le schéma suivant:

Le nombre de boucles conditionne l'instant d'apparition du front du signal équitemps émis, s'il ne concorde pas au signal de fenêtre de la structure de contrôle, l'écart temporel est détecté et elle inhibe les commandes envoyées par le microprocesseur (Cf chap.II).

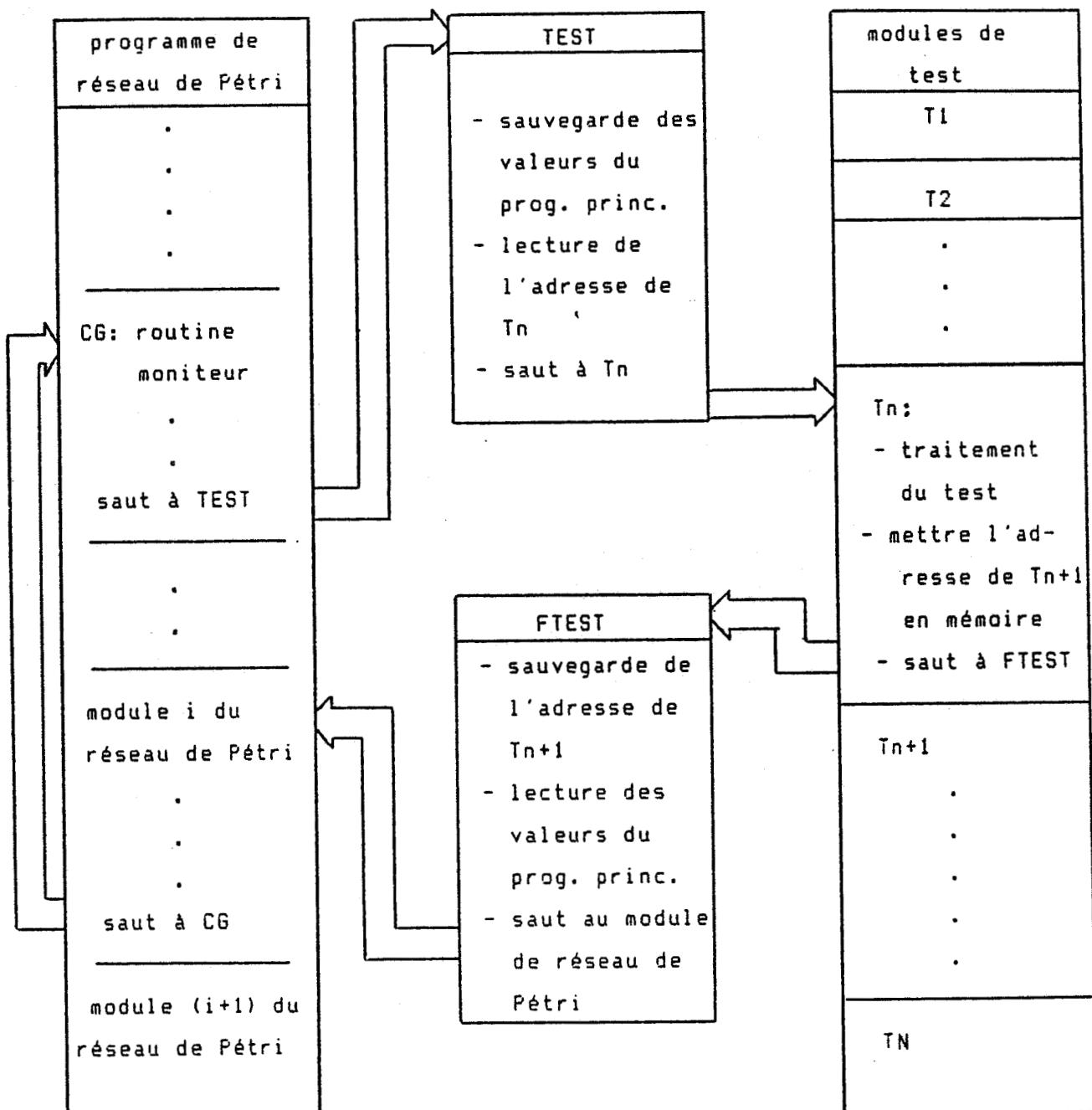

### III.7.3) Le programme.

Le programme de test dont la conception vient d'être décrite occupe un espace mémoire de 6 k Octets et le test complet du microprocesseur est exécuté en 650 ms.

Le programme est cyclique: lorsque le test est terminé, le nouveau module exécuté est le premier.

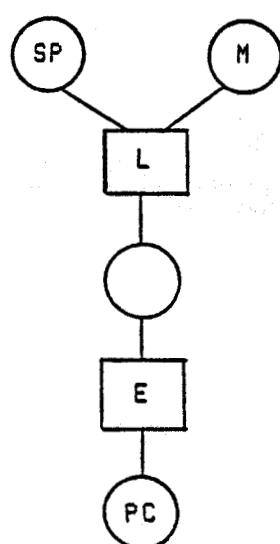

## ORGANISATION GENERALE DES PROGRAMMES D'APPLICATION ET DE TEST

prog.princ correspond au programme principal de réseau de Pétri

T<sub>i</sub> : ième module de test

N : nombre total de modules de test.

### III.8) Conclusion.

Un test complet et exhaustif d'un microprocesseur nécessite l'application d'un nombre considérable de vecteurs de test. La méthode que nous venons d'exposer permet de réduire très fortement ce nombre tout en offrant la possibilité de faire un test complet.

Elle possède en outre l'avantage d'être applicable à d'autres microprocesseurs (moyennant une étude de ceux-ci) et notamment aux circuits 16 bits, 32 bits,... et ceci sans que le nombre de vecteurs de test ne devienne prohibitif.

Prenons un exemple:

Le test complet d'une opération à deux opérandes de  $n$  bits nécessite  $2^n$  vecteurs pour un test exhaustif et  $10n+2$  vecteurs par la méthode exposée; de même pour le test d'un mécanisme d'adressage sur  $n$  bits :  $2n+2$  vecteurs au lieu de  $2^n$  pour un test exhaustif, etc....

Cette méthode permet donc de faire le test de circuits travaillant sur des champs de données de  $n$  bits de plus en plus grands (microprocesseurs 16, 32 bits,...) sans se heurter au problème de "l'explosion combinatoire" du nombre de vecteurs de test.

2<sup>ème</sup> PARTIE

EVALUATION DU TAUX DE COUVERTURE DE PANNE

D'UN MICROPROCESSEUR

## INTRODUCTION

La grande difficulté de la mise en sécurité des microprocesseurs est l'évaluation de cette sécurité.

En effet, les structures internes de ces composants sont généralement inconnues de l'utilisateur et les méthodes classiques d'évaluation de la sécurité ne sont plus applicables.

Nous avons essayé de donner un ordre de grandeur du taux de couverture de pannes du système de sécurité étudié. La démarche a été la suivante :

- 1) Evaluation grossière et pessimiste de la sécurité par analyse du schéma topographique du circuit.

- 2) Evaluation par la mesure.

## I) METHODES DE DETERMINATION DU TAUX DE COUVERTURE DE PANNEES.

La définition du taux de couverture de pannes ( $\bar{C}$ ) que nous adoptons dans ce mémoire est la suivante:

Le taux de couverture de pannes est égal à la probabilité de détecter une panne lorsque celle-ci a eu lieu.

Si l'hypothèse d'équiprobabilité des pannes peut être émise, le taux de couverture de pannes se détermine simplement par le rapport du nombre de pannes détectées sur le nombre de pannes possibles.

$$\bar{C} = \frac{\text{nombre de pannes détectées}}{\text{nombre de pannes possibles}}$$

Selon le niveau de connaissance que l'on a de la structure interne du microprocesseur, la détermination du taux de couverture de pannes est plus ou moins précise.

La connaissance fine de la structure interne du microprocesseur au niveau des transistors ou même des portes logiques est souvent inaccessible à l'utilisateur qui ne dispose en général que de manuels d'utilisation, et de plus elle est difficilement exploitable.

En effet, de part la combinatoire (nombre de pannes possibles par élément et nombre d'éléments), on conçoit mal de faire le bilan de toutes les pannes possibles à ce niveau puis d'en déduire les influences sur les phénomènes observables de l'extérieur du microprocesseur afin de vérifier que toutes ces pannes sont détectables.

La couverture absolue de toutes les pannes est impossible; une approche microscopique n'est envisageable que lors de la conception du microprocesseur si l'on implante des contrôleurs dans le silicium (REF.BIE).

Notre approche sera donc relative, notre objectif étant de chiffrer une valeur minimale de la proportion de défaillances détectées. Les défaillances sont observées d'un point de vue logique ou fonctionnel.

Une solution qui est proche de la structure réelle du microprocesseur tout en restant exploitable est basée sur la connaissance du "schéma-bloc" de celui-ci c'est à dire, un schéma représentant tous les blocs fonctionnels ainsi que les liaisons entre eux (bus).

Ce schéma doit être suffisamment précis: chaque bloc fonctionnel doit pouvoir être considéré comme élémentaire. Ceci suppose une collaboration étroite avec le constructeur qui fournit malheureusement rarement ce genre de document néanmoins, quelques explications, notamment sur le fonctionnement de la partie contrôle permettraient d'améliorer considérablement la connaissance du circuit.

En l'absence de ces informations, il faut, pour résoudre le problème admettre l'hypothèse d'équiprobabilité des pannes en regard de la proportion de surface occupée.

Cette hypothèse découle des remarques suivantes:

- les transistors constituant un circuit intégré peuvent être considérés comme uniformément répartis sur la surface de celui-ci; un phénomène extérieur tel qu'une perturbation électromagnétique peut produire un défaut n'importe où sur la puce.

- lors de la réalisation des circuits, des malfaçons peuvent se produire, certains transistors peuvent avoir des faiblesses qui se révèleront de façon aléatoire durant la vie utile du composant. Ceci peut se produire n'importe où sur le wafer (sauf sur les circuits périphériques éliminés) et donc n'importe où sur un microprocesseur de ce wafer.

Un schéma topographique détaillé du circuit intégré s'avère utile pour évaluer, de façon relative, la surface occupée par chaque partie constituant le microprocesseur.

Et enfin, si aucune de ces informations n'est disponible, une solution consiste à faire un bilan des pannes détectées de façon sûre mais le taux de couverture total ne pourra pas en être déduit.

I.1) Le schéma bloc du microprocesseur est connu.

Hypothèses:

- Le constructeur a fourni un schéma bloc fonctionnel détaillé du microprocesseur.

- Le schéma bloc fonctionnel est suffisamment précis pour que chaque unité puisse être considérée comme élémentaire; le microprocesseur se présente sous la forme d'un assemblage d'unités fonctionnelles indépendantes et reliées entre-elles par des bus.

- Le modèle de pannes est localisé au bloc:

- \* collage ou couplage des entrées d'un bloc

- \* collage ou couplage des sorties d'un bloc

- \* la table de vérité du bloc est modifiée (mauvais fonctionnement)

- \* collage ou couplage sur un bus de liaison entre blocs.

Le bilan des pannes possibles devient simple à faire et de cardinalité maîtrisable. Il faut alors analyser chacune de ces pannes de manière à déterminer si elles sont détectées ou non (analyse de la propagation des erreurs dues aux défauts des blocs jusqu'à une sortie observable et vérification de la détection de chacune de ces erreurs lors des tests).

La liste des pannes possibles et des pannes détectées étant dressée, le taux de couverture de pannes est alors le rapport suivant:

$$\zeta = \frac{\text{nombre de pannes détectées}}{\text{nombre de pannes possibles}}$$

si on admet que toutes les pannes sont équiprobables.

Dans le cas contraire, il faut attribuer un coefficient à chaque panne, celui-ci correspond à sa probabilité d'apparition.

Cette méthode nécessite toutefois de connaître précisément le schéma bloc du microprocesseur: il doit refléter la réalité interne du circuit et ne pas comporter d'omission (dans un but de protection du secret industriel par exemple).

Lorsque ces informations ne sont pas disponibles, une deuxième méthode peut être appliquée: elle est moins précise mais plus accessible à l'utilisateur.

#### I.2) La structure interne est inconnue.

Dans ce cas, il faut exploiter les informations contenues dans les manuels d'utilisation éventuellement complétées par des explications de fonctionnement ou des indications de topographie du circuit fournies par le constructeur.

Si cette information est complétée par des précisions sur le fonctionnement de la partie contrôle (les renseignements fournis par les manuels d'utilisation sont très succincts dans ce domaine), cela permet de faire des hypothèses de pannes de cette partie basées sur un fonctionnement réel du circuit et non sur un fonctionnement possible.

Dans ce cas, la définition des pannes et le calcul du taux de couverture de pannes présentés au paragraphe précédent ne sont plus applicables.

Une solution possible consiste alors en une décomposition du microprocesseur en blocs généraux et non plus élémentaires (ex: les registres, l'unité arithmétique et logique, la RAM, la ROM,...etc), chaque bloc étant considéré séparément pour définir les hypothèses de pannes. La connaissance du circuit est ici trop faible pour adopter des hypothèses de pannes générales et applicables à l'ensemble des blocs.

Des hypothèses de pannes sont donc faites pour chaque bloc afin de vérifier si les tests fonctionnels couvrent bien l'ensemble des pannes du bloc considéré et en déterminer un taux partiel de couverture de pannes.

Lorsque la topographie du circuit est connue, la proportion de la surface totale occupée par chaque bloc peut alors être déterminée et si les hypothèses suivantes sont vérifiables :

- les événements du type: pannes du bloc  $i$  sont indépendants.

L'apparition d'une panne dans un bloc  $i$  ( $i; 0 < i <$  nombre total de blocs) est un événement parfaitement aléatoire,

- deux blocs occupant la même surface ont la même probabilité de tomber en panne: équiprobabilité des pannes par rapport à la surface occupée,

le taux de couverture de pannes se définit par:

$$\bar{C} = 1 - P_{NDT}$$

$P_{NDT}$  étant la probabilité de non détection d'une panne du microprocesseur soit:

$$P_{NDT} = \frac{\sum_{i=1}^N \lambda_i P_{NDi}}{\sum_{i=1}^N \lambda_i}$$

avec:  $\lambda_i$ , taux d'occupation en surface du bloc  $i$  (proportion de surface)

$N$ , nombre total de blocs du microprocesseur

on a:

$$\sum_{i=1}^N \lambda_i = 1$$

$P_{NDi}$ , probabilité de non détection d'une panne du bloc  $i$

On a donc :

$$\boxed{\bar{C} = 1 - \sum_{i=1}^N \lambda_i P_{NDi}}$$

#### RESTRICTIONS:

- Si l'hypothèse d'équiprobabilité des pannes par rapport à la surface occupée n'est pas complètement vérifiée notamment lorsqu'on considère un bloc fonctionnel central et un bloc périphérique au circuit (REF.COU), le taux d'occupation en surface doit être pondéré par un coefficient traduisant la situation du bloc considéré (centrale ou périphérique) ou alors la probabilité  $P_{NOi}$  doit être majorée pour les blocs périphériques afin de déterminer le taux de couverture de pannes compte-tenu de la remarque précédente.

Les coefficients de pondération ou de majoration ne sont pas simples à déterminer; nous avons donc choisi de calculer la proportion de surface occupée en tenant compte de cette remarque. La surface des blocs périphériques est calculée en incluant dans les blocs les plots de sortie et les "zones interplots" faiblement actives.

La proportion de surface occupée par un bloc périphérique est donc surestimée ceci permet alors de se rapprocher de l'hypothèse émise: la probabilité de pannes est plus importante mais la surface est surestimée, le rapport est donc peu différent de celui obtenu pour un bloc central.

- Le chiffre du taux de couverture de pannes obtenu est très grossier mais volontairement pessimiste. La connaissance du circuit étant incomplète, beaucoup de pannes sont déclarées comme non détectées par manque d'informations (un grand nombre de ces pannes est très probablement détecté).

Cette façon de procéder, même si elle ne permet pas de déterminer la valeur exacte du taux de couverture de pannes, en donne toutefois une borne inférieure ( $Z$  aura probablement une valeur (très) supérieure au chiffre obtenu).

- Quand la topographie exacte du circuit est inconnue, la détermination du taux partiel de couverture de pannes de chaque bloc est possible mais on ne peut en déduire le taux global du microprocesseur.

## III) APPLICATION AU SYSTEME ETUDIE.

Ce chapitre est consacré à l'application des méthodes qui viennent d'être exposées au système considéré.

Celui-ci se compose d'un microprocesseur 8031 et d'une mémoire EPROM 27128 (16 k Octets) surveillés par les tests temporel et fonctionnel.

### III.1) Connaissance de la structure interne du 8031.

L'application de la première méthode nécessite la connaissance de la structure interne du circuit.

Le dialogue auprès des constructeurs (Intel MHS France) afin d'obtenir ces informations s'étant avéré impossible, cette méthode ne pourra pas être appliquée. De plus, elle possède l'inconvénient d'être très proche de la structure réelle du circuit et donc très dépendante des évolutions technologiques rapides des différentes versions du circuit.

La seconde méthode, quant à elle, permet d'évaluer la sécurité d'un système sans être trop liée à une structure matérielle donnée.

Compte tenu de l'absence d'informations complémentaires, nos connaissances du microprocesseur utilisé se limitent aux données fournies par les manuels d'utilisation. Dans REF.INT se trouve un schéma topographique du 8051 (8031 avec ROM intégrée), ce schéma quoique insuffisamment précis, nous permet de déterminer l'ordre de grandeur du taux de couverture de pannes ( $\bar{C}$ ).

## II.2) Proportion de surface occupée par chaque bloc fonctionnel.

Le schéma est en fait une microphotographie du circuit sur laquelle les différents blocs fonctionnels sont délimités.

L'imprécision de ce document résulte de la taille des blocs considérés : ils sont parfois très généraux et remplissent plusieurs fonctions (un exemple: les interruptions et le port série sont dans le même bloc fonctionnel).

La proportion de surface occupée par chaque bloc fonctionnel a été déterminée. Les résultats sont donnés dans le tableau suivant ainsi que les moyens de mise en sécurité adoptés pour chacun des blocs (voir dans la 1<sup>e</sup> partie le détail du procédé de sécurité étudié).

| BLOCS FONCTIONNELS<br>CONSIDERES | PROPORTION DE<br>SURFACE (en %) | PROCEDURES DE TEST          |

|----------------------------------|---------------------------------|-----------------------------|

| port 0                           | 8,32                            | Test de la ROM              |

| port 1                           | 4,78                            | Sécurité liaisons, RDP      |

| port 2                           | 4,89                            | Test de la ROM              |

| port 3                           | 4,58                            | Sécurité liaisons, RDP      |

| port control                     | 2,84                            | Sécurité liaisons, test ROM |

| ROM (4 k0)                       | 15,20                           | Test de la ROM              |

| RAM                              | 5,84                            | Test de la RAM              |

| RAM SFR                          | 5,84                            | Test des SFR, test temporel |

| RAM control                      | 4,36                            | Test de la RAM              |

| Interrupt et                     | 7,44                            | Test temporel et            |

| Port série                       |                                 | Sécurité des transmissions  |

| PC / DPTR                        | 3,78                            | Test temporel               |

| Control logic                    | 8,24                            | Tests fonctionnel, temporel |

| PLA                              | 10,57                           | Tests fonctionnel, temporel |

| Timer                            | 1,97                            | Sécurité des transmissions  |

| Timing                           | 2,25                            | Test temporel               |

| Clock                            | 5,80                            | Test temporel               |

| ALU                              | 3,28                            | Test ALU                    |

\*RDP: sécurité introduite dans le réseau de Pétri de la commande

( traitement anti rebond par exemple)

### II.3) Détermination des taux partiels de couverture de pannes.

La détermination des taux partiels de couverture de pannes est faite en considérant chaque bloc fonctionnel séparément. Pour cela, il faut émettre des hypothèses de pannes et vérifier que celles-ci sont détectées par une ou plusieurs composantes du procédé de mise en sécurité du microprocesseur (test fonctionnel, test temporel, codage des transmissions,...).

Les paragraphes qui suivent vont donc reprendre le détails de ces déterminations.

#### II.4) Le bloc ROM.

##### II.4.1) hypothèses de pannes.

- changement du contenu d'une case mémoire

- mauvais adressage : la case mémoire effectivement adressée n'est pas celle attendue

- problème de lecture: la case adressée est la bonne, son contenu n'a pas été modifié mais la donnée transmise lors de la lecture n'est pas celle attendue.

D'un point de vue macroscopique, toutes ces pannes sont équivalentes à la première puisque la valeur lue n'est pas celle attendue quelle qu'en soit la raison.

##### II.4.2) Les tests.

Les pannes de la ROM sont détectées lors de son test: la checksum ( Cf 1ère partie).

La vérification du test de la ROM a été effectuée en modifiant tour à tour chacun des octets mémorisés ( Cf 2ème partie Chap.III). Il ne subsiste aucun cas non détecté; toutes les pannes simples décrites précédemment sont détectées, nous dirons donc que

$$P_{ND\ ROM} = 1 - Z_{ROM} = 0$$

### II.4.3) Remarques.

Les hypothèses de pannes présentées sont des cas de pannes simples, elles sont toutes détectées.

Examinons les cas de pannes multiples. La ROM contient les octets constituant les instructions du programme. Des modifications multiples des octets de la ROM vont donc aussi entraîner des modifications du programme exécuté. Il faudra donc, pour qu'une panne multiple ne soit pas détectée, qu'elle entraîne:

- une compensation lors de chacune des 16 sommes arithmétiques soient donc 16 résultats justes et,

- aucune altération du signal équitemps lorsque les instructions seront exécutées.

Un exemple simple de panne multiple détectée est le suivant:

16 pannes simultanées entraînant un octet faux dans chacun des 16 k Octets.

### II.5) Les blocs Port 0 et port 2.

Les port 0 et 2 servent d'intermédiaires entre la ROM extérieure et le microprocesseur (le port 0 pour les octets bas des adresses et les données, le port 2 pour les octets hauts des adresses).

Lors du test de la ROM, les adresses émises et les données lues transitent nécessairement par les ports 0 et 2; leur fonctionnement est donc indirectement vérifié par la checksum ainsi que par d'autres tests puisque les instructions du programme se trouvent dans la ROM.

#### II.5.1) Hypothèses de pannes.

Ce sont les collages à 0 et 1 de chacun des bits d'un port et les couplages entre eux.

### II.5.2) Taux partiel de couverture de pannes.

Une panne simple du port 0 ou du port 2 est équivalente, vue du microprocesseur, à des pannes multiples de la ROM, dispersées sur les 16 k Octets.

La détermination du taux de couverture de pannes est, dans ce cas, difficile à faire puisqu'il dépend du contenu de la ROM.

Exemple: Le couplage de deux bits du port 0 entraîne des modifications dans les adresses émises ainsi que dans les données reçues: les données sont lues au mauvais endroit et sont, de plus, modifiées.

La valeur du taux de couverture de pannes ne sera donc pas déterminée dans le cas d'une étude générale.

Néanmoins, lors d'une panne du port 0 ou du port 2, deux cas peuvent se présenter:

- le nombre d'octets modifiés est relativement faible et la détection est faite de la même façon que lors des pannes multiples de la ROM.

- le nombre d'octets modifiés est important et le programme n'est plus structuré, dans ce cas, la probabilité d'altération du signal équitemps est très grande.

On peut donc estimer que la probabilité de non détection d'erreurs du fonctionnement des ports 0 et 2 tend très fortement vers zéro.

$$P_{ND\text{ } P0} \longrightarrow 0 \text{ et } P_{ND\text{ } P2} \longrightarrow 0$$

## II.6) Le bloc ALU.

### II.6.1) Les hypothèses de pannes.

- Une fonction arithmétique ou logique de l'ALU ne fonctionne plus correctement

- Les fonctions arithmétiques et logiques sont sans défaillance mais les opérandes d'entrée ou les résultats observés sont erronés (les opérandes ne sont pas lus au bon endroit, les résultats ne se situent pas dans les bons registres, panne du bus entre les registres internes et l'ALU proprement dite,...etc).

Vu de l'utilisateur, le deuxième groupe de pannes est équivalent au premier puisque les registres internes ne lui sont pas accessibles et le seul constat qu'il peut faire est que le résultat n'est pas juste.

Une décomposition mathématique des fonctions arithmétiques et logiques a permis de faire des hypothèses de pannes au niveau des fonctions booléennes élémentaires constituant chaque fonction : (voir 1ère partie III)

- mauvais fonctionnement d'une fonction booléenne

- mauvaise transmission de contexte

- couplage ou collage des bits du résultat

- collage ou couplage des bits des opérandes.

### II.6.2) Taux partiel de couverture de pannes.

Par un choix particulier d'opérandes, toutes les pannes citées précédemment peuvent être détectées lors des tests. Des essais (voir le chapitre suivant) ont permis de confirmer l'idée que toutes les pannes sont détectées, on en déduit donc que:

$$P_{\text{ND ALU}} = 1 - \bar{Z}_{\text{ALU}} = 0$$

## II.7) Le bloc RAM.

### II.7.1) Hypothèses de pannes.

- collage à 0 ou 1 d'un ou plusieurs bits de la RAM

- diaphonie entre cases booléennes voisines:

- \* couplages entre bits voisins d'un même registre

- \* couplage entre bits voisins de registres voisins

### II.7.2) La RAM proprement dite.

Les tests fonctionnels font les vérifications suivantes:

- absence de collage d'un ou plusieurs bits

- absence de couplage entre bits voisins (d'un même registre ou de registres voisins)

La probabilité de non détection d'une panne de la RAM est donc presque nulle:

$$P_{\text{ND RAM}} = 1 - \zeta_{\text{RAM}} \# 0$$

Il est bien évident que cette détection ne concerne que les pannes constatées lors d'une écriture ou d'une lecture dans la RAM; des parasites modifiant de façon fugitive certains bits de la RAM ne peuvent être détectés avec certitude.

### II.7.3) La RAM SFR (Special Function Register).

Cette partie de la RAM contient les registres internes utiles au fonctionnement du microprocesseur. Certains sont connus et accessibles à l'utilisateur, d'autres non : leur rôle dans le fonctionnement du microprocesseur n'est pas explicité dans le manuel d'utilisation.

### III.7.3.1) Remarques sur les registres connus.

- l'accumulateur et le registre B sont testés

- le PSW (registre d'état) est indirectement testé, son utilisation fréquente lors du fonctionnement normal du microprocesseur entraîne la détection de ses défaillances (mauvais choix de banque de registre, conditions mal interprétées, erreurs arithmétiques,...etc)

- le SP (pointeur de pile) et le DPTR (pointeur de données) servent essentiellement à la sauvegarde des adresses, leurs défaillances sont détectées par les tests temporels

- les défaillances des ports "latch" sont détectées au même titre que les défaillances des ports eux mêmes

- les registres utilitaires pour les interruptions et le port série (IE, IP, TMOD, TCON, TH1, TL1, SCON, SBUF, PCON) sont intimement liés au fonctionnement des interruptions et du port série et donc, leurs défaillances sont détectées

- le timer 0 (TH0, TL0) est inutilisé. Ses défaillances sont sans effet (ce cas n'est pas dangereux) ou affectent la liaison série et sont détectées comme une défaillance de celle-ci.

### III.7.3.2) Remarques sur les registres inconnus.

Il est fort probable qu'une partie de ces registres sert de registres temporaires (pour l'unité arithmétique et logique par exemple) ou de buffer. Leurs défaillances sont détectées comme celles des blocs fonctionnels (ALU, bus interne,...).

Les défaillances des registres inconnus inutilisés doivent probablement être sans effet.

La méconnaissance de cette partie de RAM ne permet pas d'en déterminer la probabilité de non détection de pannes; on suppose simplement que ces registres sont utiles au fonctionnement du microprocesseur (optimisation de la surface de silicium occupée par composant) et donc que les effets de leurs défaillances se font sentir au niveau du fonctionnement de zones accessibles à l'utilisateur.

Compte tenu du manque d'informations, la probabilité de non détection est grossièrement estimée à:

$$P_{ND \text{ RAMSFR}} = 1 - \zeta_{RAMSFR} = 0,5$$

valeur certainement très supérieure à la réalité

## II.8) Le bloc PC/DPTR.

### II.8.1) Hypothèses de pannes du PC (Program Counter).

Ne connaissant pas le fonctionnement interne du PC, les hypothèses de pannes se situent au niveau du fonctionnement externe:

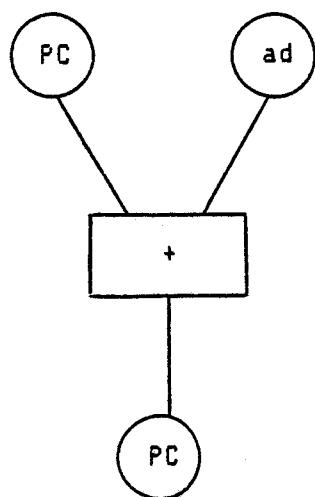

- mauvaise incrémentation du PC au cours du déroulement normal du programme (quelle qu'en soit la raison)

- lors de la rupture de séquence (saut), le PC n'est pas chargé par la valeur exacte (quelle qu'en soit la raison)

### II.8.2) Détection de pannes.

Le fonctionnement du PC est intimement lié au déroulement du programme, lui même lié à la génération du signal équitemps de test temporel.

Lors de l'exécution du programme, le cheminement, quoique très structuré, n'est absolument pas linéaire et l'émission du signal équitemps est permanente (un décalage de 1  $\mu$ s correspondant à la durée d'exécution de l'instruction la plus rapide est détecté); ceci nous amène à la constatation suivante:

Un disfonctionnement du PC ne pourra pas constamment donner lieu à une génération correcte de ce signal de test temporel d'où, une très forte présomption de détection.

### II.8.3) Hypothèses de pannes du DPTR (Data Pointer Register).

Le DPTR est un registre 16 bits et donc toutes les hypothèses de pannes relatives aux registres sont retenues à savoir:

- collage ou couplage d'un ou plusieurs bits

- panne du (ou des) bus de liaison entre le DPTR et un bloc utilisateur de la donnée contenue dans ce registre.

Pour l'utilisateur, toutes ces pannes sont équivalentes à une donnée fausse dans le DPTR.

### II.8.4) Détection de pannes.

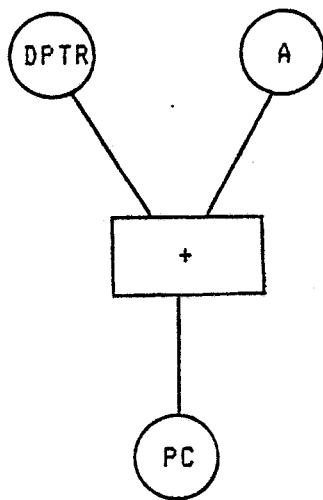

Le DPTR sert essentiellement (dans le cas étudié) à la sauvegarde des adresses des routines à exécuter (traitement des places de réseau de Pétri, routines de test fonctionnel). Si l'adresse sauvegardée est inexacte, le signal de test temporel n'est pas émis correctement ou, si l'adresse de la place à traiter est remplacée par une autre, le réseau de Pétri n'évolue pas correctement et la détection est faite au niveau du programme de traitement.

### II.8.5) Taux partiel de couverture de pannes.

La probabilité de non détection des pannes de ce bloc PC/DPTR tend donc très fortement vers zéro, le chiffre exact reste cependant impossible à déterminer.

$$P_{ND \text{ PC/DPTR}} = 1 - \zeta_{PC/DPTR} \longrightarrow 0$$

## II.9) Les blocs PLA - Control Logic - Timing.

Ces blocs constituent l'essentiel de la partie contrôle du microprocesseur dont le fonctionnement est très peu explicité dans les manuels d'utilisation.

La modélisation de son fonctionnement ainsi que les hypothèses de pannes font référence à REF.BRA et REF.BEL1 et sont plutôt de nature intuitive.

### II.9.1) Hypothèses de pannes.