$N^{0}$  d'ordre : 511

# **THESE**

## présentée à

# L'UNIVERSITE DES SCIENCES ET TECHNIQUES DE LILLE FLANDRES ARTOIS

pour obtenir le grade de

# DOCTEUR EN ELECTRONIQUE

par

# **Laurent GUILBERT**

Ingénieur ISEN

# CONTRIBUTION A DES OUTILS DE CONCEPTION DE CIRCUITS INTEGRES

# Soutenue le 27 Avril 1990, devant la commission d'examen :

Président Rapporteurs

Directeur de Thèse Examinateurs CONSTANT DERRYCKE DECARPIGNY CONSTANT RAMBERT RACZY

PETITPREZ

Université Lille 1 CUEEP – Lille ISEN – Lille Université Lille 1

RTC COMPELEC - Caen

USTL - Lille 1 ISEN - Lille Mener à bien un travail de thèse n'est pas chose facile. Mais la tâche aurait été impossible sans l'aide de toutes les personnes de mon entourage. Je les en remercie vivement, qu'elles soient citées ou non dans cette page.

L'ISEN a mis à ma disposition tous les moyens matériels et humains nécessaires pour mener à bien ce travail. Plus particulièrement, le département informatique et son responsable Mr PETITPREZ m'ont aidé et soutenu tout au long de ces années.

Mr CONSTANT, Président du jury, a eu la patience d'encadrer mes travaux, et m'a servi de lien permanent avec l'Université des Sciences et Techniques de Lille Flandres-Artois.

Mms DECARPIGNY et DERRYCKE par leurs critiques m'ont permis une meilleure formulation de mes idées. Tous deux m'ont fait le plaisir d'être rapporteur officiel.

Mr RACZY a accepté le rôle d'examinateur.

Mr RAMBERT, malgré la distance a accepté le rôle d'examinateur.

Christelle SOYEZ a assuré la mise en page de ce rapport.

# LA CONCEPTION DES CIRCUITS INTEGRES

| <u>PAGES</u>                     |                                                                                                                                                                                                                              |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>1<br>4<br>6<br>10           | <ul> <li>I- Les étapes de réalisation d'un circuit intégré</li> <li>1) La conception</li> <li>2) Les simulations</li> <li>3) L'implantation</li> <li>4) Les vérifications</li> </ul>                                         |

| 11<br>11<br>13<br>15<br>16       | <ul> <li>II- Les logiciels nécessaires</li> <li>1) La conception</li> <li>2) Les simulations</li> <li>3) L'implantation</li> <li>4) Les vérifications</li> </ul>                                                             |

| 17                               | III- Récapitulatif                                                                                                                                                                                                           |

| 19                               | IV- La position des travaux réalisés                                                                                                                                                                                         |

|                                  | L'EDITEUR GRAPHIQUE                                                                                                                                                                                                          |

| 21                               | I- Introduction                                                                                                                                                                                                              |

| 21<br>21<br>22<br>22<br>23       | <ul> <li>II- Les objectifs visés</li> <li>1) La description hiérarchique</li> <li>2) La portabilité</li> <li>3) La base de données</li> <li>4) La communication avec l'extérieur</li> </ul>                                  |

| 23<br>23<br>24<br>26<br>26<br>27 | <ul> <li>III- La norme graphique GKS</li> <li>1) Les stations de travail</li> <li>2) Les transformations</li> <li>3) Les primitives graphiques</li> <li>4) La segmentation</li> <li>5) Les routines d'intéraction</li> </ul> |

| 27                               | IV- Les données manipulées                                                                                                                                                                                                   |

| 28<br>28<br>31<br>34             | <ul> <li>V- La structure d'information</li> <li>1) Exemple de hiérarchie</li> <li>2) Construction de la structure</li> <li>3) Présentation de la structure</li> </ul>                                                        |

| 35<br>35<br>37<br>38<br>38       | <ul> <li>VI- Description de la base de données</li> <li>1) Importance de la base de données</li> <li>2) Généralités</li> <li>3) Proposition de structure</li> <li>4) Les fonctions d'accès évoluées</li> </ul>               |

| 40         | VII – Quelques fonctions disponibles à l'utilisateur        |

|------------|-------------------------------------------------------------|

| 40         | 1) La convivialité                                          |

| 41         | 2) L'environnement d'accueil                                |

| 41         | 3) Environnement de visualisation/placement de circuit/bloc |

| 42         | 4) Environnement d'édition de bloc                          |

| 42         | 5) Sous environnements                                      |

| 43         | VIII- Conclusion                                            |

| 43         | 1) La portabilité                                           |

| 43         | 2) La convivialité                                          |

| 44         | 3) Les performances                                         |

| 44         | 4) Le coût                                                  |

|            | LE VERIFICATEUR DE REGLES DE GARDE                          |

| 45         | I- Introduction                                             |

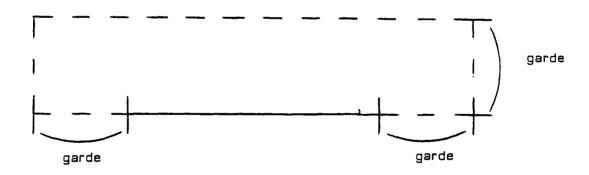

| 47         | II- Les principes généraux                                  |

| 47         | 1) Les fonctions de vérification                            |

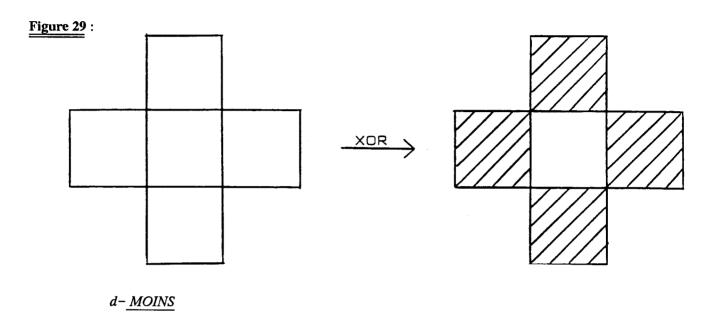

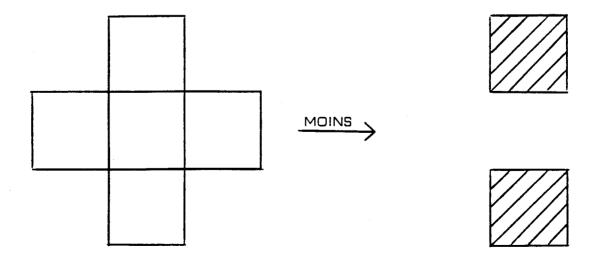

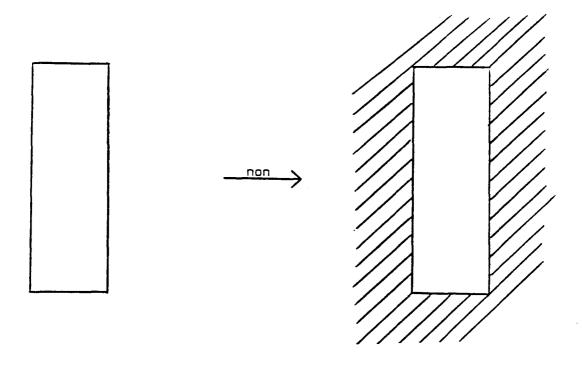

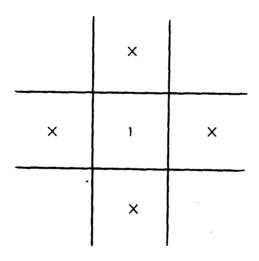

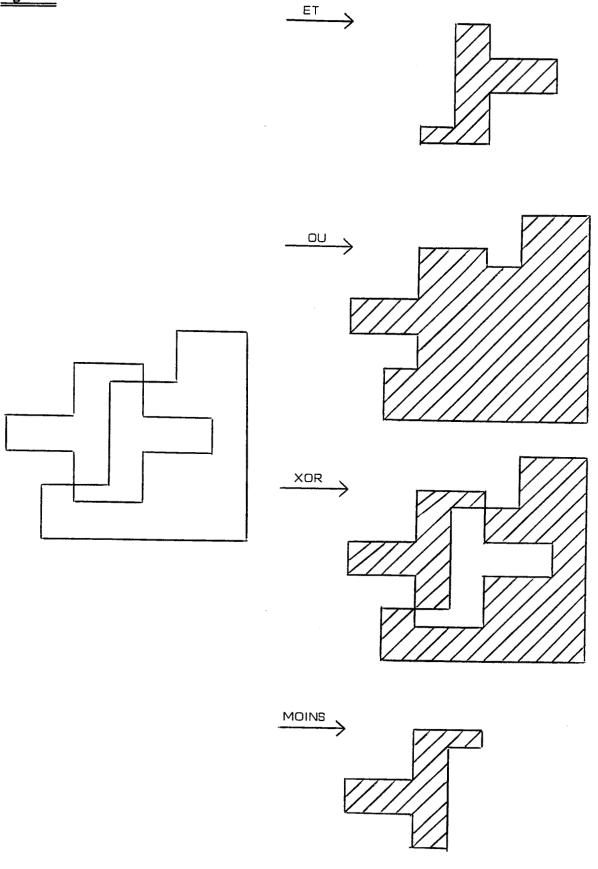

| 52         | 2) Les opérateurs logiques                                  |

| 54         | 3) Les fonctions particulières                              |

| 55         | III- Les différentes méthodes existantes                    |

| 55         | 1) "Bit-map"                                                |

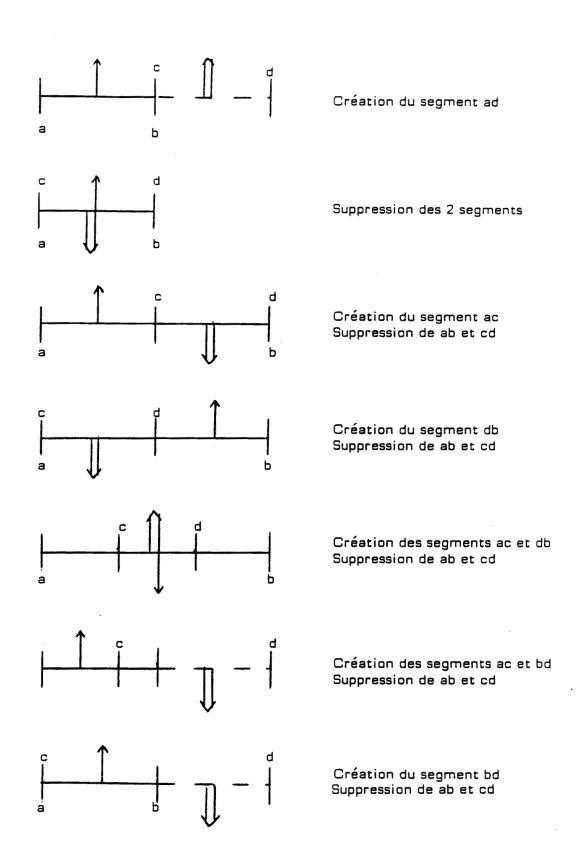

| 59         | 2) "Segments"                                               |

| 66         | 3) "Rectangles"                                             |

| 70         | IV- Comparaison des différentes méthodes                    |

| 71         | V- Les fonctions disponibles                                |

| 71         | 1) La vérification d'un masque                              |

| 72         | 2) La vérification de plusieurs masques                     |

| 73         | 3) Les fonctions logiques                                   |

| 74         | 4) Les fonctions particulières                              |

| 75         | VI- Les lignes obliques                                     |

| <i>7</i> 5 | 1) Position du problème                                     |

| 77         | 2) La vérification de garde                                 |

| <i>7</i> 7 | 3) Les opérateurs logiques                                  |

| 78         | 4) Les fonctions particulières                              |

| 78         | VII- La hiérarchisation du vérificateur                     |

| 78         | 1) Principe de la vérification hiérarchique                 |

| 81         | 2) La découpe des cellules                                  |

| 85         | VIII- Comparaison avec les produits du marché               |

| 86         | IX- Conclusion                                              |

# L'EXTRACTEUR DE SCHEMAS

| 88         | I- Introduction                                                             |

|------------|-----------------------------------------------------------------------------|

| 88         | II- L'extraction de schéma pour comparaison                                 |

| 89         | 1) Détermination des éléments électriques                                   |

| 91         | 2) Détermination de la connectique                                          |

| 92         | <ol> <li>Détermination des équipotentielles</li> </ol>                      |

| 92         | 4) La génération des résultats                                              |

| 93         | 5) Exemple d'extraction                                                     |

| 97         | III- L'extraction fine pour simulation                                      |

| 97         | 1) Les éléments parasites                                                   |

| 99         | 2) La détermination des noeuds intermédiaires                               |

| 102        | 3) La constitution des éléments                                             |

| 103        | IV- La comparaison de schémas                                               |

| 103        | 1) Description du problème                                                  |

| 104        | 2) L'explosion numérique                                                    |

| 104        | 3) Les solutions envisageables                                              |

| 105        | V- Conclusion                                                               |

|            | REFERENCES                                                                  |

|            |                                                                             |

| 106        |                                                                             |

|            |                                                                             |

|            | 4275                                                                        |

|            | ANNEXES                                                                     |

| 109        | I- Annexe 1                                                                 |

| 109        | 1) Les masques utilisés                                                     |

| 109        | 2) Les règles de garde                                                      |

| 117        | II- Annexe 2                                                                |

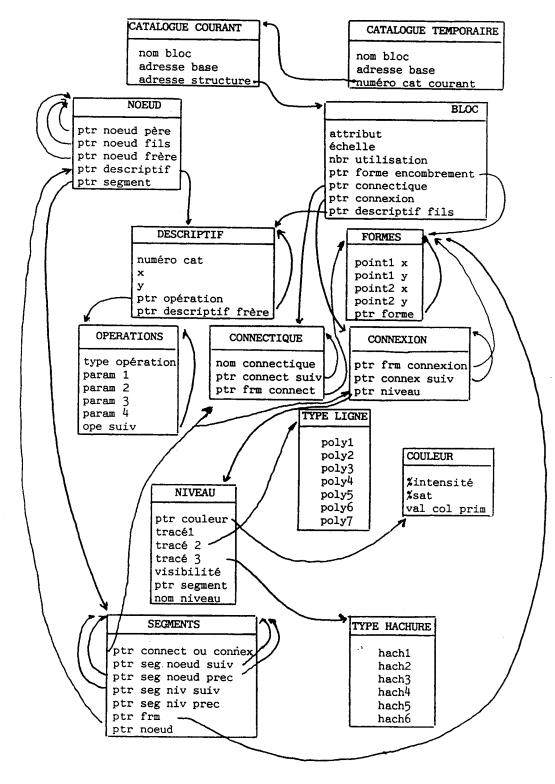

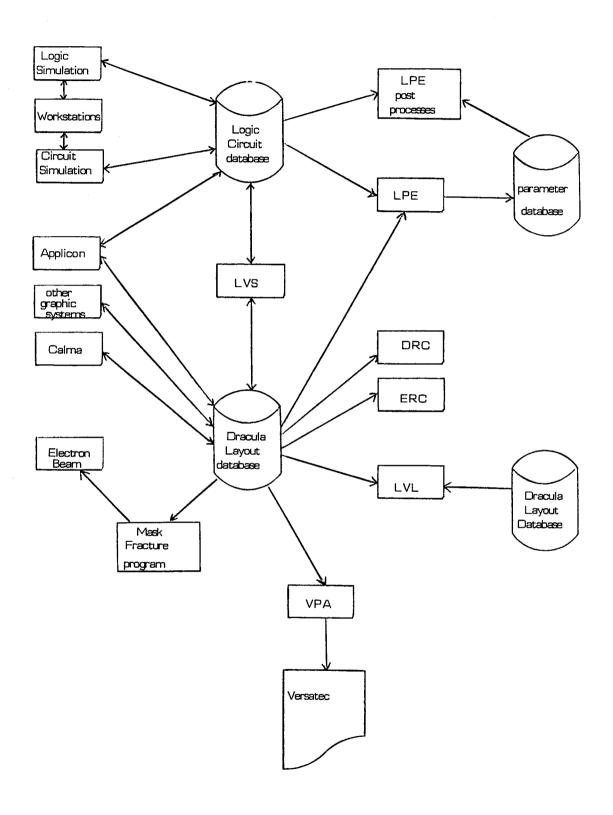

| 117        | 1) Schéma général                                                           |

| 118        | 2) Le catalogue courant                                                     |

| 119        | 3) Le catalogue temporaire                                                  |

| 119        | 4) Les blocs                                                                |

| 120        | 5) Les descriptifs                                                          |

| 121        | 6) Les opérations                                                           |

| 122        | 7) Les formes                                                               |

| 123        | 8) Les connections                                                          |

| 124<br>124 | 9) Les connectiques<br>10) Les noeuds                                       |

| 125        | 11) Les segments                                                            |

| 126        | 12) Les niveaux                                                             |

| 127        |                                                                             |

|            | 13) Les types de nachures                                                   |

| 127        | <ul><li>13) Les types de hachures</li><li>14) Les types de lignes</li></ul> |

| 128 | III – Annexe 3                                              |

|-----|-------------------------------------------------------------|

| 128 | 1) Structure fonctionnelle                                  |

| 130 | 2) Implémentation physique                                  |

| 135 | IV- Annexe 4                                                |

| 135 | 1) L'environnement d'accueil                                |

| 136 | 2) Environnement de visualisation/placement de circuit/bloc |

| 138 | 3) Environnement d'édition de bloc                          |

| 140 | V- Annexe 5                                                 |

| 140 | 1) Dracula de ECAD                                          |

| 145 | 2) UDRC de NCA                                              |

|     |                                                             |

Ce travail a pour sujet la conception assistée par ordinateur appliquée au domaine de la synthèse des circuits intégrés, numériques ou analogiques.

La réalisation de tels circuits comporte plusieurs phases :

# \* L'étape de conception :

Elle consiste en la définition des spécifications et une étude de faisabilité.

#### \* L'étape de réalisation :

Celle-ci se décompose en plusieurs niveaux :

- la réalisation des masques,

- les vérifications,

- l'inversion de schémas.

La réalisation des masques est une étape longue et fastidieuse dont le but est de dessiner l'ensemble des couches constituant le circuit désiré. A partir de ces dessins, le fabricant peut piloter les différents processus industriels conduisant au produit fini.

La vérification des masques est une opération manuellement impossible. En effet, suite à l'étape précédente, on se trouve en possession de schémas constitués de millions d'entités graphiques élémentaires (rectangles, triangles, ...). Ces éléments doivent respecter des contraintes géométriques liées à la technologie de fabrication. Un non respect des règles peut entrainer des disfonctionnements graves du circuit ou des chutes de rendement en production.

L'inversion des schémas est une étape permettant de vérifier que le produit final réalise bien la fonction désirée. En effet, lors du passage de la représentation électrique à la représentation graphique du circuit, des erreurs peuvent être commises provoquant la génération d'un composant non conforme. Une vérification de la cohérence des différentes représentations permet d'éviter un passage inutile en production, opération très couteuse.

De nombreux logiciels d'aide à la conception de circuits intégrés existent sur le marché. Nous pouvons classer ces produits en deux grandes catégories :

\* Les logiciels d'aide à la conception de circuits intégrés numériques.

Ces produits utilisent au départ une représentation algorithmique de haut niveau décrivant le fonctionnement du circuit. De cette description, par des moyens plus ou moins automatiques, une découpe en blocs fonctionnels est réalisée. Ces blocs sont ensuite placés et connectés. Cette approche ressemble assez fortement à la méthode de conception d'un circuit imprimé. Pour de tels logiciels, les étapes de vérification et d'inversion de schémas ne sont pas nécessaires, ces contraintes étant respectées à la fabrication.

\* Les logiciels d'aide à la conception de circuits intégrés analogiques.

On ne trouve ici aucun produit complet, mais simplement divers logiciels réalisant des fonctions bien précises et ayant des interfaces plus ou moins normalisées entre eux. Dans ce domaine, les efforts ont essentiellement portés sur les phases de dessins des masques et de vérification des masques.

Différents problèmes existent pour chacune de ces catégories de logiciels. Pour la première, le problème majeur est celui de la surface occupée par le circuit réalisé. Ce point est génant dans la mesure où le prix de revient est proportionnel à la surface. De plus, ces produits ne permettent pas la réalisation de circuits analogiques. Pour la seconde catégorie, l'inconvénient majeur vient du manque d'unité de l'offre logicielle. De plus, ces programmes ne permettent généralement pas la conception de circuits numériques nécessitant une structuration des données plus rigoureuse et formalisée.

Notre but était dans cette étude, de trouver un compromis entre ces deux approches et d'offrir un ensemble cohérent de logiciels permettant la réalisation de circuits intégrés numériques et analogiques. Ceci c'est fait par la réalisation de logiciels suffisamment performants pour traiter le numérique, ayant suffisamment de souplesse pour autoriser les réalisations analogiques et parfaitement interfacés entre eux. De plus, nous tenions à faire fonctionner ces logiciels sur du matériel moyenne gamme afin de pouvoir généraliser ces techniques.

Le travail présenté dans ce rapport vise à atteindre au mieux ces objectifs.

Ce document est composé de quatre parties.

# - La conception de circuits intégrés.

Une analyse des différentes méthodes et logiciels disponibles sur le marché dans le domaine considéré permet de justifier nos axes de développement.

#### - L'éditeur graphique.

Le logiciel présenté permet de faire de la schématique pour circuits imprimés, circuits intégrés analogiques et circuits intégrés numériques.

# - Le vérificateur de règles de garde.

#### - L'extracteur de schémas.

Une simplification des modèles permet d'obtenir des résultats satisfaisants sans nécessité la puissance de calcul d'un super-ordinateur.

Un couplage serré avec l'éditeur de masques, permettant un gain de temps important, est justifié au travers des fonctionnalités du produit.

# LA CONCEPTION DES CIRCUITS INTEGRES

Dans ce chapitre, les différentes possibilités s'offrant aux concepteurs pour la réalisation des circuits intégrés sont présentées par un rapprochement de méthodes de conceptions et des outils disponibles actuellement sur le marché. Les points faibles sont énoncés.

#### Le plan du chapitre est le suivant :

- Les étapes de réalisation d'un circuit intégré,

qui fait état des différentes méthodologies de conception existantes.

- Les logiciels nécessaires, présentant les outils nécessaires et leurs fonctionnalités.

- Récapitulatif, effectuant la relation entre les besoins et les outils et indiquant les manques.

- La position des travaux réalisés, présentant les différents points traités dans l'étude et justifiant nos choix.

#### I- LES ETAPES DE REALISATION D'UN CIRCUIT INTEGRE

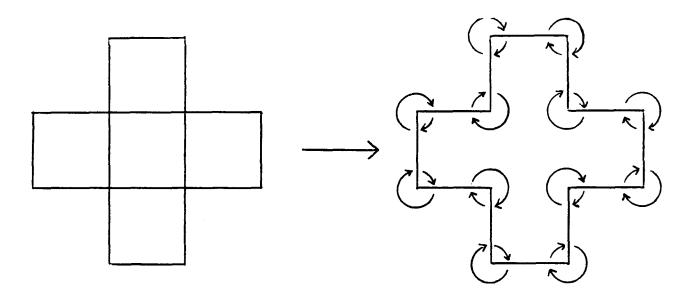

La complexité et la taille des circuits intégrés ne cessent d'augmenter. Ce développement a nécessité la mise en oeuvre de méthodes de travail et d'outils informatiques qui facilitent le travail de conception. Parmi ces méthodes, on peut citer en particulier la conception hiérarchique des circuits [1] [2].

En effet, pour la phase initiale, le concepteur fait une analyse descendante (TOP-DOWN). Il considère d'abord le système complet, puis le découpe en sous-ensembles de plus en plus simples, jusqu'à arriver aux éléments de base. Par contre, pour l'implantation, la démarche du concepteur sera ascendante (BOTTOM-UP). Il créera d'abord des cellules de base qu'il assemblera pour former des blocs plus complexes, et ceci jusqu'à définir le circuit complet.

Quant aux outils, ce sont essentiellement des programmes de conception assistée par ordinateur, utilisant fortement le graphique [3]. Ce besoin se fait sentir à tous les niveaux : architecture, conception logique, conception électrique, "layout", vérification, test, mais aussi dans les liaisons entre ces différentes étapes de la conception d'un circuit.

#### 1) LA CONCEPTION

Les étapes initiales de la réalisation d'un circuit sont la définition du problème, l'analyse des besoins et la décomposition du système en sous-systèmes. Les fonctionnalités du circuit et les contraintes à respecter (vitesse, coût...) sont établies pendant la phase de définition des besoins.

La définition finale du circuit nécessite de faire des compromis entre les contraintes et les besoins. De cette phase découle la structure du système qui est ensuite découpée en sous-systèmes interconnectés avec des interfaces clairement définies. Pour les grands circuits, les sous-systèmes peuvent être considérés comme des systèmes à part entière et faire l'objet du même travail de définition.

Ce n'est que très récemment (début des années 80) que l'automatisation de cette phase a donné naissance à des outils opérationnels. Ces outils sont essentiellement des langages de description tels que VHDL, en cours de normalisation.

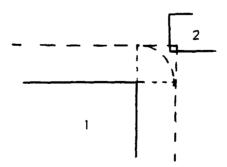

Cette première phase de conception d'un circuit intégré aboutit à l'élaboration d'un ou deux schémas du circuit :

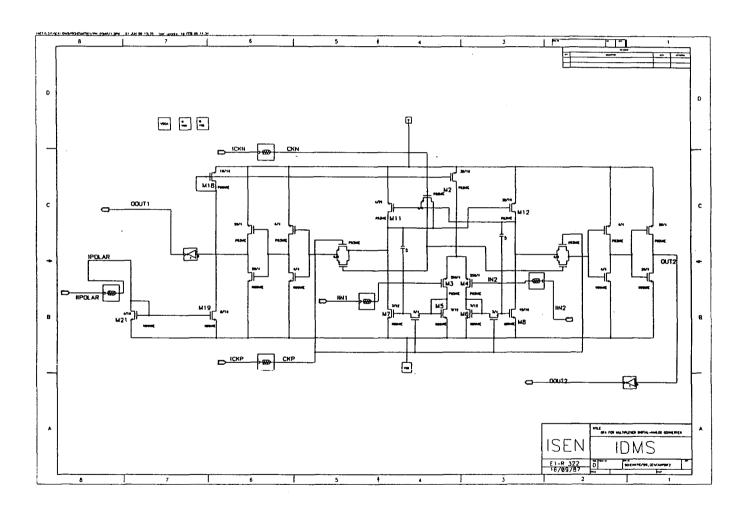

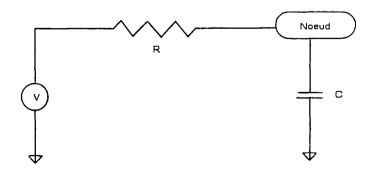

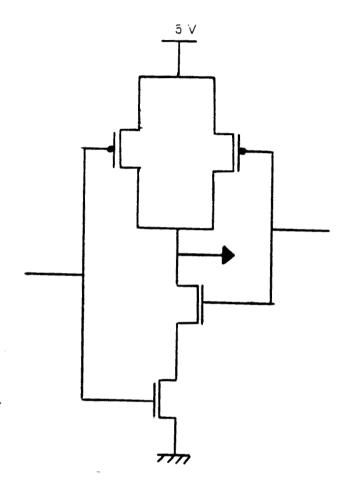

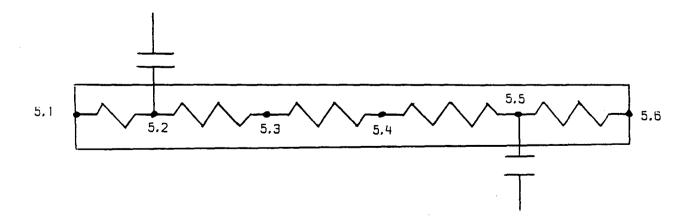

- un schéma électrique où les entités de base sont des transistors et des composants passifs (résistances, capacités...) comme dans l'exemple donné en figure 1. Ce schéma sera implanté sur silicium.

Figure 1:

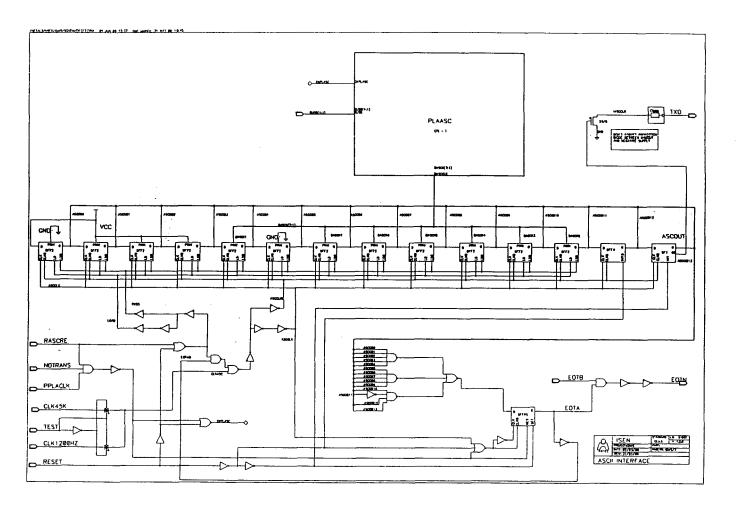

– un schéma logique où les entités de base sont des éléments logiques (portes, registres, multiplexeurs ...) comme dans l'exemple donné en figure 2. Ce schéma doit par la suite être transformé en schéma électrique, de manière manuelle ou automatique. Cette étape n'a pas lieu d'être dans la réalisation d'un circuit analogique.

Figure 2:

#### 2) LES SIMULATIONS

Sur ces schémas (ou descriptions) sont effectuées des simulations qui permettent au concepteur de vérifier la validité de son étude théorique.

La simulation fonctionnelle permet de vérifier que le système réalise correctement les fonctions définies avant de commencer une conception plus fine. Le résultat de cette simulation est aussi utilisé pour la génération des tests.

A ce niveau, le concepteur doit fournir l'algorithme décrivant le fonctionnement de son circuit. A cause du coût de fabrication, la détermination de la testabilité du circuit doit se faire avant de commencer la conception détaillée. Il faut être sûr de pouvoir tester le circuit après la fabrication.

Le but est de produire des circuits où toute erreur potentielle peut être isolée en appliquant des entrées connues au circuit et en observant les sorties. Cela suppose que toute faute soit contrôlable et observable. Il faut donc que pour chaque faute, il existe une combinaison des entrées faisant apparaître une sortie inexacte.

La simulation logique repose sur une technique d'exécution dirigée par événements. Un tel simulateur peut considérer le temps de 2 façons :

- une succession d'intervalles élémentaires. Ce genre de simulateur est particulièrement inefficace car le temps de simulation dépend de la durée, et non du nombre d'événements. Ceci est particulièrement sensible dans le cas où des circuits rapides (nécessitant un intervalle de temps court) sont pilotés par une horloge lente.

- des intervalles de temps variables déterminés par les portes et les entrées. Dans ce cas, le temps de simulation ne dépend que du nombre de changements d'états à l'intérieur du circuit.

Très souvent, les simulateurs logiques et les simulateurs fonctionnels sont présents dans le même logiciel. Ceci permet de faire de la simulation mixte et d'éviter ainsi une simulation complète du circuit en terme de portes de base (ET, OU, NON, bascules, registres...). C'est la seule façon de simuler entièrement un circuit complexe en conservant des temps de réponse acceptables.

Pour la simulation au niveau "switch", chaque transistor est modélisé comme un interrupteur contrôlé par une tension. Trois états différents sont utilisés :

OFF (circuit ouvert), ON (circuit fermé), R (résistif).

Cette simulation n'est utile que si l'on s'intéresse au comportement logique ou temporel du circuit. Les résultats sont généralement proches de ceux produits par une simulation électrique détaillée.

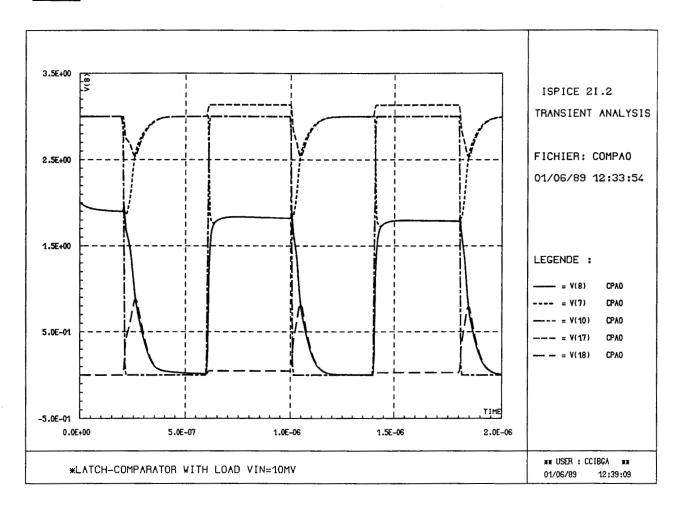

La simulation électrique travaille au niveau des transistors et des composants actifs ou passifs. Elle est rarement effectuée sur l'ensemble du circuit, mais plus généralement sur les chemins critiques. Le but de cette simulation est de fournir des courbes de fonctionnement du circuit telles que celles-ci :

Figure 3:

Elle doit aussi intégrer les paramètres de la technologie utilisée. Cette contrainte est primordiale pour la validité des résultats de simulation et pose beaucoup de problèmes au concepteur. En effet, la plupart des simulateurs offrent peu de possibilités de modification des caractéristiques des composants. Pour connaître ces paramètres, deux solutions sont envisageables :

- une simulation fine du process technologique permet maintenant de déterminer les caractéristiques des composants générés. Malheureusement, peu de fabricants fournissent le détail de leur technologie pour des raisons évidentes de protection.

- La deuxième solution consiste à réaliser un circuit test, sur lequel on effectue des mesures précises des caractéristiques. On adapte ensuite les paramètres de description des composants dans le simulateur, afin d'obtenir la meilleure correspondance possible entre le réel et le théorique. Généralement, ces itérations sont réalisées par un programme qui prend le simulateur en boucle. Il faut noter que cette méthode est gourmande en ressource machine.

#### 3) L'IMPLANTATION

Une fois achevée la conception détaillée du circuit, l'étape suivante consiste à réaliser le dessin des masques (ou "layout") qui seront utilisés pour la fabrication du circuit.

Cette phase consiste à placer des milliers (millions) de rectangles ou polygones sur une large surface. Le placement de ces rectangles définit les éléments fonctionnels du circuit tels que les transistors et les interconnexions. De plus, la largeur et l'espacement de ces rectangles doivent respecter un certain nombre de contraintes fonction de la technologie afin d'éviter des erreurs de fabrication.

Cette étape peut être longue et fastidieuse ou très rapide suivant la méthode employée. Par contre, la surface du circuit résultant, donc le coût, est généralement inversement proportionnel au temps passé. Les techniques existantes visent toutes un seul objectif : minimiser le temps de réalisation du layout pour une surface de circuit.

#### Les méthodes les plus courantes sont :

#### - Le dessin manuel:

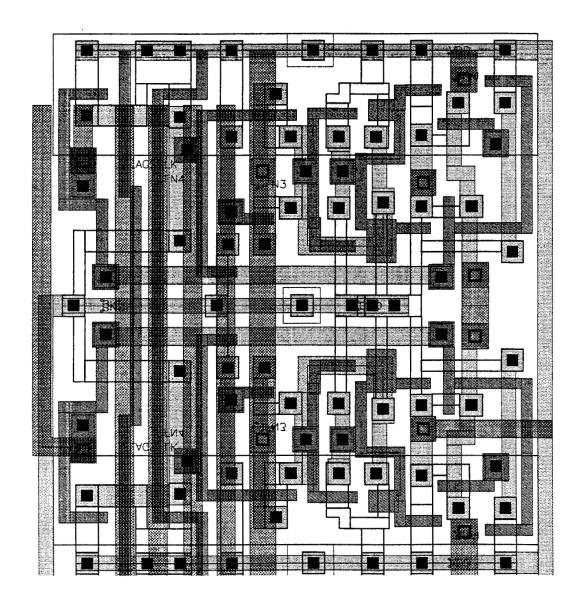

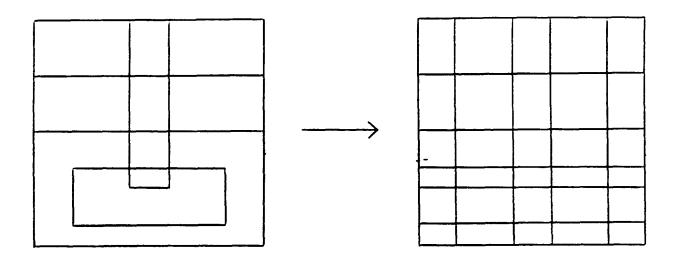

Dans ce cas, il existe peu ou pas de structures prédéfinies. Le concepteur commence par la réalisation de ses cellules de base, puis il les interconnecte pour réaliser des cellules plus grandes qu'il assemble pour former des blocs encore plus grands, et ainsi de suite jusqu'à la réalisation du circuit complet. Cette méthode donne le meilleur résultat sur le plan de la place occupée, et donc du coût de fabrication, mais est la plus coûteuse en ressources humaines : voici un exemple de layout manuel.

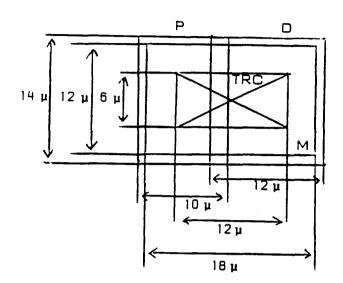

Figure 4:

#### - Le dessin symbolique:

dans ce cas, le concepteur introduit également des données de façon manuelle, mais il ne génère que la topologie du dessin : on dessine librement des lignes de largeur nulle ; ces lignes remplacent les pistes ; les transistors et les contacts, représentés par des symboles, sont placés aux intersections de ces lignes. Une fois la topologie déterminée, un programme transforme le dessin en fonction des règles technologiques et on obtient un "layout" assez dense. Plusieurs systèmes de ce genre existent : STICK [4] et CABBAGE [5] .

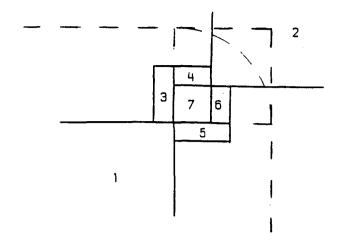

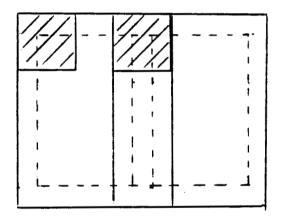

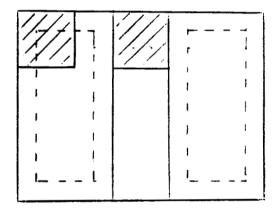

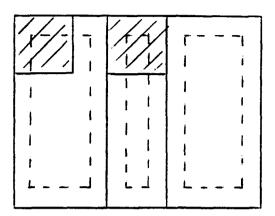

#### - Les cellules standards :

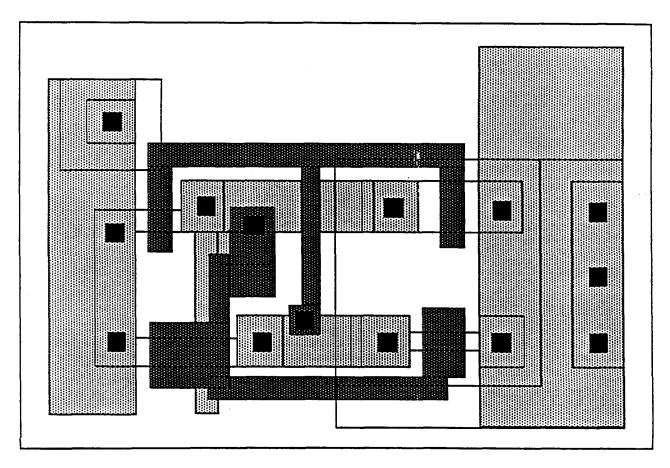

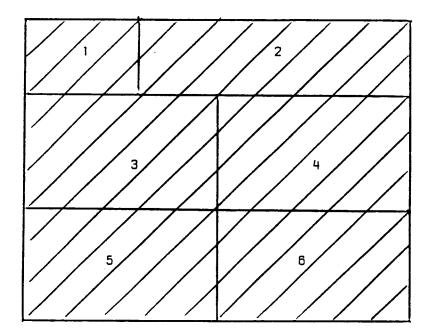

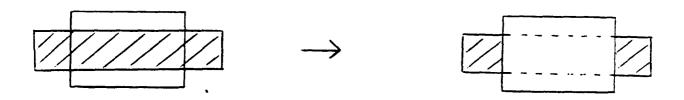

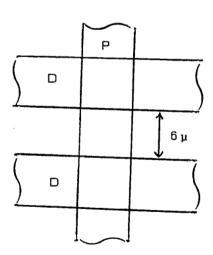

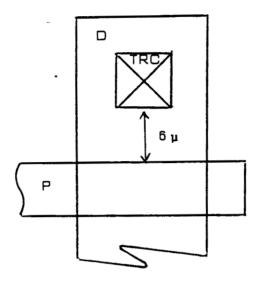

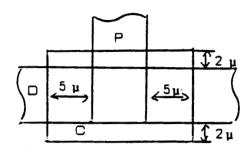

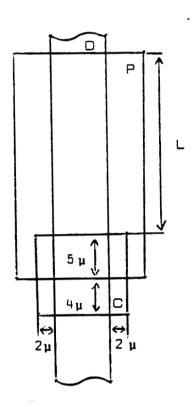

le concepteur dispose d'une bibliothèque de cellules de base dont le layout est optimisé. Toutes les cellules sont contenues dans un rectangle dont l'une des dimensions est une constante. Chaque cellule réalise une fonction et elle est traversée par au moins deux bus, un pour la Masse et un pour l'Alimentation : voici un exemple de cellule standard.

Figure 5:

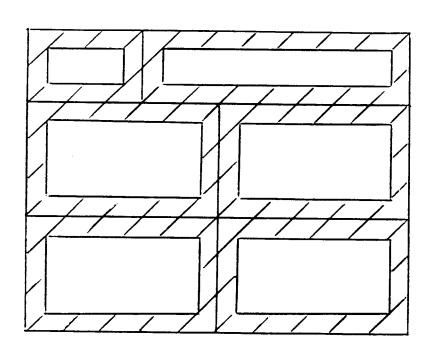

Le concepteur assemble ces cellules par rangées ou colonnes et effectue ensuite les interconnexions. Il lui est possible d'utiliser des logiciels de placement et de routage pour la réalisation de son circuit. Le gain de temps est important, mais la perte de place est non négligeable, principalement à cause du routage canal utilisé dans cette méthode. On peut citer deux systèmes basés sur cette approche : CALMOS [6], LTX [7]: voici un exemple de circuit obtenu par cette méthode.

Figure 6:

#### - Les compilateurs de silicium :

la méthode développée par Johansen s'applique à tous les niveaux de la conception, depuis l'architecture jusqu'au "layout" ([8], [9]). On n'évoquera ici que ce dernier. Des cellules sont conçues pour être accolées deux à deux. Elles sont paramétrables : selon les paramètres spécifiés, on obtient pour une même cellule, différentes vitesses de fonctionnement, différentes puissances consommées.

La cellule peut être agrandie suivant une dimension : il est ainsi possible de relier directement les sorties de cette cellule avec les entrées de celle qui lui est accolée. Johansen a appliqué cette méthode pour réaliser la partie opérative, souvent appelée "data path", d'un microprocesseur. Cette technique semble donc très intéressante et pourra sûrement remplacer dans l'avenir le dessin manuel avec de bons résultats.

#### - Les "gate arrays":

ici, on utilise des circuits préfabriqués contenant des transistors ou des cellules réalisant des fonctions très simples, et des lignes d'alimentation sans aucune connexion. Le fabricant peut donc produire des quantités importantes de circuits non routés, et faire la connexion à la demande du client. Comme la fabrication des couches de connexions est fiable et bon marché, les prix sont tirés vers le bas. De plus, la mise en place d'un seul niveau de connexion est peu coûteuse en ressources machine. Cette méthode est donc très rapide. Par contre, la place occupée est très moyennement optimisée.

#### 4) LES VERIFICATIONS

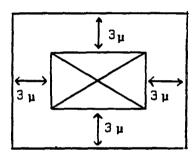

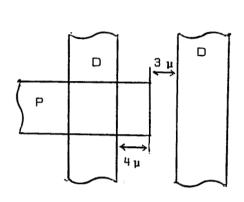

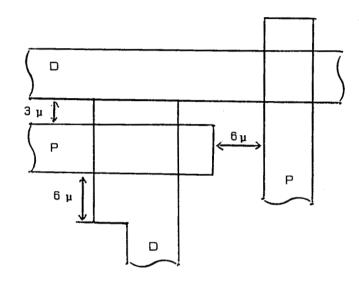

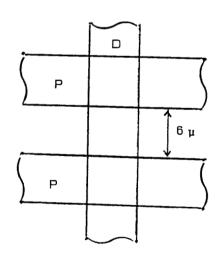

La vérification constitue la dernière étape de conception du layout. Celui-ci comporte plusieurs milliers (millions) d'éléments graphiques de base (rectangles, lignes, polygones, trapèzes...). Les processus de fabrication imposent des contraintes géométriques sur ces différents éléments, tels que :

- largeur minimale des lignes

- espacements entre deux éléments d'un même niveau

- recouvrement minimal entre éléments de niveaux différents ...

Un exemple de toutes les règles à vérifier sur une technologie NMOS est donné en annexe 1.

La quantité d'informations à traiter est telle qu'une vérification manuelle est impossible. L'existence de vérificateurs de garde est donc indispensable.

Une deuxième vérification importante est la cohérence entre le circuit qui a été simulé et le circuit obtenu effectivement (oubli d'un contact, mauvais dimensionnement d'un transistor...). Ici aussi, une vérification manuelle est impossible. Il est donc nécessaire d'extraire le schéma réellement implanté au niveau du circuit à partir du dessin des masques.

Après extraction, il devient possible, par l'intermédiaire d'un outil de comparaison, de valider le schéma réel du circuit. Un autre avantage de cette étape est de déterminer, en fonction de l'implantation, les éléments parasites tels que les résistances, les capacités, les diodes qui seront implicitement ajoutées à la fabrication. De cette extraction fine, il est possible de simuler les chemins critiques et par conséquent de valider de façon exacte le comportement du circuit.

#### **II- LES LOGICIELS NECESSAIRES**

Nous reprenons ci-après les différentes étapes de réalisation d'un circuit et pour chacune d'elles, les logiciels nécessaires et les fonctions qu'ils doivent réaliser.

#### 1) LA CONCEPTION

Cette phase est essentiellement du domaine du concepteur. A ce niveau, la seule aide informatique envisageable est une aide au dessin. Les logiciels utilisés sont donc des logiciels de "schématique" dont la seule fonction est une aide à la réalisation et à la maintenance des schémas. Il existe maintenant quelques logiciels d'aide à la conception. Venues du monde du logiciel, des méthodes telles que SADT (Structured Analysis and Design Technique) permettent de décrire le flot des données et des signaux de contrôle à l'intérieur d'un système.

Ces outils sont tout à fait adaptés à la conception de circuits intégrés car ils ont été créés pour décrire le fonctionnement de systèmes complexes. De plus, ils sont indépendants de la technologie. Quelques approches théoriques telles que les réseaux de PETRI ont été développées pour la description de systèmes asynchrones, mais à l'heure actuelle, peu de choses sont disponibles.

Le département américain de la défense a mis au point un langage de description standard VHDL (VHSIC Hardware Description Language) qui permet de décrire un système et ses contraintes en termes de structure et de fonctionnalités. La description d'un additionneur 1 bit en VHDL est la suivante :

```

architecture GATE VIEW of FULL ADDER is view:

block

- Local component declarations

component AND GATE port(A,B:in BIT;C:out BIT);

component XOR GATE port(A,B:in BIT;C:out BIT);

component OR GATE port(A,B:in BIT;C:out BIT);

- Local signal declarations

signal S1,S2,S3:BIT;

begin

- Component instantiations

X1:XOR GATE port(X,Y,S1);

X2:XOR GATE port(S1,Cin,SUM);

A1:AND GATE port(Cin,S1,S2);

A2:AND GATE port(X,Y,S3);

O1:OR GATE port(S2,S3,Cout);

end block;

end GATE VIEW;

```

On peut remarquer que cette description est très proche de la programmation en langage ADA.

Une autre approche pour aider le concepteur est de lui fournir des outils de simulation et de synthèse travaillant au niveau système.

Par exemple, lors d'une première analyse, le concepteur se pose des questions telles que : combien de mémoires faut-il, à quelle vitesse doit fonctionner la machine ?

Pour évaluer ces besoins, deux méthodes existent.

#### - La simulation du système :

- Ecrire un simulateur dédié

- Utiliser un simulateur existant tel que N.2 [10] qui permet de faire des simulations à ce niveau de conception.

#### - La compilation de silicium:

- Approche structurelle

- Approche fonctionnelle

La plupart des développements de circuit occasionne l'écriture d'un simulateur dédié. Cette méthode présente l'inconvénient de ne pas pouvoir explorer rapidement plusieurs architectures. L'utilisation de simulateurs tels que N.2 supprime ce problème.

La compilation de silicium existe sous 2 formes. Dans l'approche structurelle, le concepteur décrit chaque bloc du système en fournissant des informations telles que la taille des mots, les contraintes temporelles et les interconnexions.

A partir de ces informations, le compilateur génère le layout qui peut être simulé et fabriqué. Cette approche impose une description d'assez bas niveau. Dans l'autre approche, la compilation de silicium commence par une description fonctionnelle du circuit et produit automatiquement le layout. La simulation est faite au niveau fonctionnel. Malheureusement, les produits de cette nature sont encore en laboratoire, sauf un : MetaSyn de Metalogic.

#### 2) LES SIMULATIONS

La simulation est de plus en plus liée à la conception. En effet, il paraît logique d'offrir au concepteur la possibilité de valider son travail au fur et à mesure de son avancement. C'est pourquoi la plupart des logiciels de schématique offre des interfaces plus ou moins évoluées avec les simulateurs. Ceci permet d'éviter une description supplémentaire du circuit dans le langage propre au simulateur.

On effectue en général une simulation électrique détaillée des chemins critiques ou des cellules afin d'obtenir des informations précises sur les temps de propagation et le fonctionnement de ces parties. Ces simulations sont rarement effectuées sur des circuits de plus de 100 transistors pour des problèmes de temps de calcul. Le plus connu des simulateurs électriques est SPICE [12], qui permet la modélisation de composants en tenant compte des paramètres technologiques tels que la capacité de grille ou la mobilité des électrons.

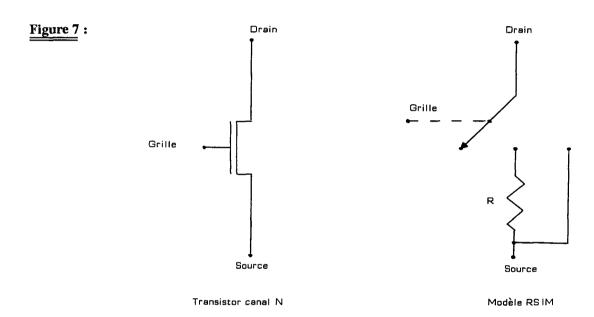

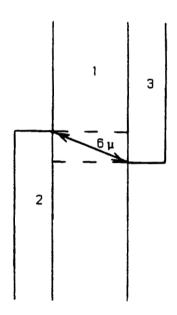

La simulation au niveau "switch" permet de valider le fonctionnement global du circuit. Dans des produits comme RSIM [14] développé à Carnegie-Mellon, les transistors sont modélisés de la façon suivante :

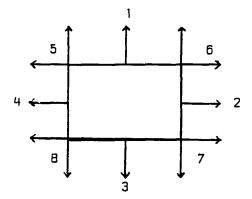

Dans ce modèle, l'impédance drain-source est 0, 1 ou R en fonction de la position du switch. Chaque noeud du réseau a le circuit équivalent suivant :

Figure 8:

V, R et C sont calculés à partir des paramètres du transistor et des tensions appliquées au noeud. RSIM a modélisé des circuits comportant jusqu'à 400.000 transistors.

Les simulateurs logiques tels que HILO de GENRAD acceptent en entrée différentes représentations du circuit. On peut mixer des descriptions fonctionnelles, au niveau portes de bases (ET, OU, NON, registres...) et au niveau circuits prédéfinis (circuits de base tels que ceux des familles 74LSXX, AMDXXX ou autres). Il est aussi possible, pour des raisons de performance, de lui adjoindre un simulateur "hardware", où on utilise le composant réel, et non une description de son fonctionnement. Dans ces logiciels, des modules de calcul de la testabilité d'un circuit et de la détermination des données de tests sont en général disponibles.

L'utilisation de ces produits de simulation entraîne un besoin important en ressource machine. En effet, l'espace disque et la mémoire centrale nécessaires sont importants. Pour HILO par exemple, un espace disque de 15 méga-octets est le minimum requis pour pouvoir stocker le produit et la bibliothèque de base. Pour certains produits de CAO comme CBDS d'IBM, la bibliothèque occupe un espace disque de plus de 60 méga-octets. De façon générale, la mémoire centrale utilisée par ces produits est de l'ordre de 6 méga-octets. De plus, ces logiciels réalisent énormément d'entrées-sorties, ce qui impose l'utilisation de disques et de bus très rapides.

En conséquence, une station de travail haut de gamme (SUN 4, VAXSTATION 3000 ...) est la machine minimale pour obtenir un temps de traitement acceptable par le concepteur. Il faut cependant noter que ces simulateurs fonctionnent sur presque toutes les machines de grande diffusion, ce qui permet à l'utilisateur de ne pas être lié à un constructeur.

#### 3) L'IMPLANTATION

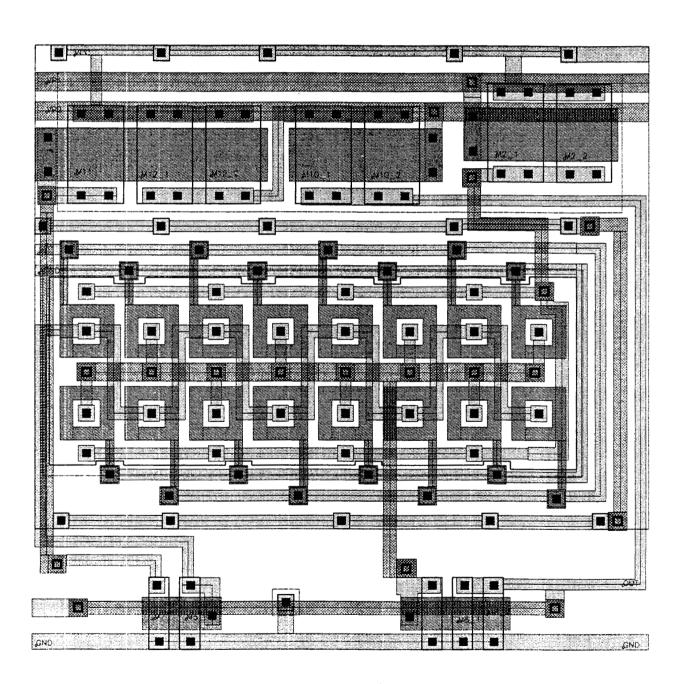

Cette étape a pour but de fournir les masques du circuit au fabricant. Un layout peut être très complexe, et les concepteurs doivent utiliser ordinateurs et graphisme pour avoir de l'aide. La plupart des concepteurs utilise des systèmes graphiques interactifs pour réaliser les masques. Le layout se construit de façon purement hiérarchique, en construisant des cellules de plus en plus complexes [15]. Partout où cela est possible, des structures régulières telles que les mémoires ou les PLA sont utilisées de préférence à la logique "sauvage", ceci afin de réduire la complexité de la conception. Des éditeurs graphiques tels que MAGIC [13] de l'université de Californie, permettent de créer des composants ou des cellules sur un écran graphique couleur.

Quand les composants sont créés et interconnectés, ils sont stockés dans une base de données, puis simulés et fabriqués. Ce logiciel offre des fonctionnalités supplémentaires. A chaque fois qu'un nouvel objet est ajouté à l'écran, une vérification des règles de garde est effectuée. Si une erreur de dessin existe, l'utilisateur est immédiatement prévenu à l'écran. Une autre fonction intéressante de ce produit, est le rétablissement automatique des connexions quand le concepteur bouge un composant ou une cellule. De plus, MAGIC est capable de faire du placement et du routage automatique.

Les besoins varient beaucoup en fonction de la méthode utilisée. Ils peuvent aller de la nécessité d'un "simple" éditeur graphique (dessin manuel), à l'emploi d'un ensemble complet de conception (compilateur de silicium). Il faut cependant noter que la réalisation d'un circuit analogique impose quasiment de faire un dessin manuel, les efforts d'automatisation de la conception de circuits intégrés étant très faibles dans ce domaine. Seuls les circuits logiques sont actuellement du ressort des compilateurs de silicium.

#### 4) LES VERIFICATIONS

Pour cette phase, deux fonctionnalités différentes sont nécessaires :

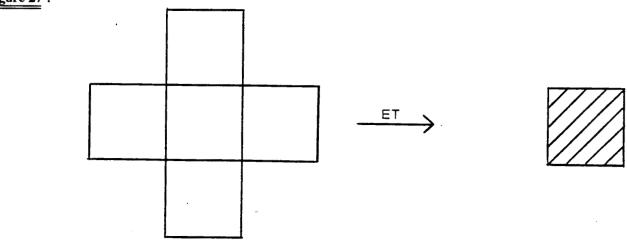

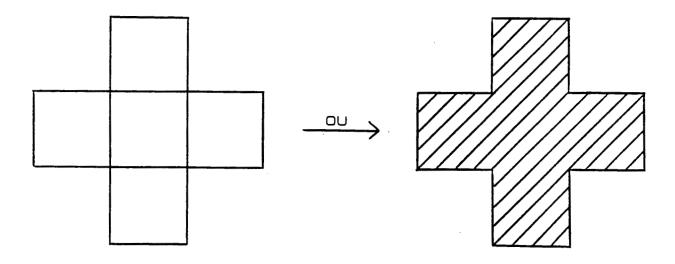

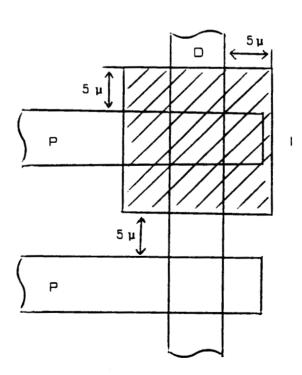

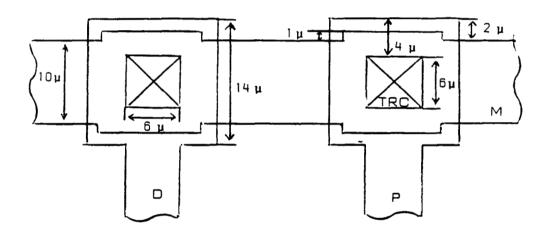

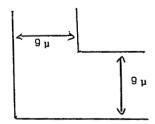

La vérification des règles de garde nécessite peu ou pas de connaissance des différents composants du circuit. Dans cette étape, les masques sont manipulés comme un ensemble d'éléments graphiques qui doivent respecter un certain nombre de contraintes géométriques (voir annexe 1 pour une technologie NMOS). Afin d'être indépendant de la technologie employée, le logiciel sera constitué d'un ensemble d'opérateurs de masques. Le concepteur devra créer un fichier contenant la suite des opérations à effectuer, ainsi que les opérandes à manipuler. Les opérateurs de ce logiciel sont des opérateurs de vérification de garde intérieure ou extérieure mono ou multi masques, et un ensemble de fonctions logiques telles que le ET, le OU, le NON....

Les fonctions logiques permettent d'extraire des sous-ensembles du layout pour lesquels existent des contraintes spécifiques (débordement de 4  $\mu$ m du polysilicium au delà du transistor dans la technologie NMOS 6  $\mu$ m). Les algorithmes du DRC (Design Rule Checking) nécessitent un temps d'exécution proportionnel à la complexité dans le meilleur des cas, et à la complexité au carré dans le plus mauvais. La complexité d'un layout peut s'exprimer de différentes manières, soit comme étant le nombre de rectangles (ou figures élémentaires) du dessin, soit comme étant le nombre de transistors du circuit. Nous retiendrons la première définition qui est indépendante de la technologie employée.

Après l'étape de dessin des masques, il est important de réaliser une simulation du circuit complet pour vérifier son bon fonctionnement. Les éléments tels que les transistors et les interconnexions doivent donc être extraits afin de permettre une simulation au niveau "switch". L'extraction de schémas impose de retrouver les composants constituant le circuit et leurs interconnexions. Les opérateurs de ce logiciel sont les opérateurs logiques du produit précédent pour la reconnaissance des éléments (par exemple, pour une technologie NMOS, un ET entre le polysilicium et la diffusion donnera les transistors), un ensemble de fonctions permettant de déterminer les différentes équipotentielles du circuit (ce qui nous donnera les interconnexions), ainsi que les composants qui s'y rattachent. A partir de ces renseignements, on peut générer la liste des noeuds (Netlist).

De nombreux programmes existent. Un exemple typique est ACE [11], développé à l'université de Carnegie-Mellon. Pour ce produit, on peut estimer un temps de traitement de 220 minutes sur un VAX 11/780 pour le traitement d'un circuit de 100.000 transistors. Ce résultat est obtenu par interpolation linéaire de résultats de traitements moins importants. Il est à noter que 40% du temps est employé pour le tri et la préparation des données. Ce facteur temps est aussi valable pour le DRC. Peu de logiciels réalisent la comparaison de deux netlists. Il est plus courant de faire une simulation du circuit extrait et de vérifier son bon fonctionnement, plutôt que de vérifier la cohérence entre le schéma désiré et le schéma implanté.

#### III- RECAPITULATIF

Quels sont les outils informatiques disponibles pour la conception des circuits intégrés ?. Le tableau suivant présente les principales tâches qui peuvent être simplifiées par les outils de CAO dans le cadre de la réalisation d'un circuit intégré logique.

| TACHE                               | OBJECTIFS DE LA TACHE                                                                                                                         | ACTEUR                 |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| conception générale                 | description du circuit au niveau bloc                                                                                                         | concepteur             |

| simulation<br>fonctionnelle         | simulation du circuit décrit<br>comme un ensemble de registres<br>et de fonctions logiques                                                    | logiciel               |

| conception<br>détaillée             | description de chaque sous<br>système au niveau portes<br>logiques ou transistors                                                             | concepteur             |

| simulation logique                  | simulation du circuit décrit<br>comme un ensemble de portes<br>et de bascules                                                                 | logiciel               |

| évaluation de<br>la testabilité     | évaluation du taux de<br>testabilité du circuit                                                                                               | logiciel               |

| génération<br>des tests             | génération de listes d'entrées<br>de tests et des sorties<br>attendues pour le test du<br>circuit après fabrication                           | logiciel               |

| dessin des<br>masques               | transformation du schéma<br>logique détaillé en masques<br>utilisés pour la fabrication                                                       | concepteur<br>logiciel |

| vérification des<br>règles de garde | vérification que toutes les<br>contraintes géométriques<br>de largeur, espacements et<br>recouvrements sont corrects<br>pour tous les masques | logiciel               |

| extraction<br>de schéma             | extraction d'un schéma<br>au niveau transistors<br>à partir des masques                                                                       | logiciel               |

| simulation au<br>niveau "switch"    | simulation du circuit extrait<br>en considérant tous les<br>transistors comme des<br>transistors de passage                                   | logiciel               |

| simulation du circuit               | simulation de tout ou partie<br>du circuit au niveau composant                                                                                | logiciel               |

Beaucoup d'outils de CAO ont pour but d'accélérer la conception et la validation. Cependant, personne ( à l'exception d'IBM et son système LDS), ne prend en compte la standardisation du format des données et des langages de description. Il en est de même pour les problèmes d'archivage de l'énorme quantité de données générées pendant la création d'un circuit. En effet, chacun de ces logiciels possède en général son propre mode de stockage des informations. Ceci conduit à une multiplicité des bases de données, ce qui entraîne des risques d'incohérence entre ces différents modes de représentation des informations.

#### IV- LA POSITION DES TRAVAUX REALISES

L'étude décrite dans le document ci-après porte sur les étapes d'implantation et de vérification. Son but a été d'analyser les algorithmes envisageables pouvant fonctionner sur du matériel peu coûteux. Nous avons restreint le champ de l'étude au cas de circuits intégrés analogiques, car dans le domaine de la logique, de nombreux produits existent, comme nous l'avons vu précédemment.

Le premier centre d'intérêt a porté sur la réalisation d'un éditeur graphique pour les étapes de saisie de schémas et de dessin des masques. Notre objectif était de montrer qu'un seul logiciel pouvait remplir correctement les deux fonctions. Nous ne nous sommes pas intéressés à la simulation. Les produits existent, et peu de choses innovantes restent à faire de ce côté.

Notre deuxième centre d'intérêt a porté sur les phases de vérification, que ce soit la vérification des règles de garde ou la validation du circuit implanté. Pour le DRC, nous sommes partis du constat que la majeure partie d'un layout est constitué de rectangles. Aussi, il nous a semblé intéressant d'utiliser le rectangle comme entité de base. L'étude a prouvé que même si ce choix n'est pas parfait, le résultat était intéressant et que la piste méritait d'être creusée.

Pour l'extraction de schémas, nous voulions savoir si une comparaison de netlists n'était pas plus intéressante ou plus performante qu'une simulation du circuit obtenu au niveau "switch". De plus, les produits existants n'extraient que les transistors et les interconnexions. Nous avons prouvé qu'il est possible de retrouver les éléments parasites induits par la fabrication.

Nous avons choisi ces produits car ils sont réputés consommer beaucoup de place mémoire et d'espace disque, et nécessiter une puissance de calcul importante. Notre étude a montré que ces logiciels, moyennant des algorithmes adaptés, peuvent fonctionner sur du matériel de type PC, avec des temps de réponse tout à fait acceptables. De plus, dans le cas des circuits intégrés , ces étapes prennent énormément de temps. Par conséquent, il est intéressant de ne mobiliser que du matériel peu coûteux, offrant malgré tout un confort d'utilisation acceptable par le concepteur.

# L'EDITEUR GRAPHIQUE

Les concepts mis en oeuvre pour la réalisation d'un éditeur graphique pour circuits intégrés sont présentés.

Le "gigantisme" des données manipulées ainsi que la limitation des outils existants contraignent à mettre en oeuvre des structures et bases de données complexes. Néanmoins, cette complexité interne n'est pas visible pour l'utilisateur, grâce à une ergonomie soignée.

## Le plan du chapitre est le suivant :

- Les objectifs visés, rappelant l'objet du travail.

- La norme graphique GKS, (Graphic Kernel System) présentant les avantages et inconvénients des outils existants à ce niveau.

- Les données manipulées, leur "gigantisme" et leur complexité.

- La structure d'informations, permettant de résoudre les problèmes lié à l'utilisation de GKS.

- La base de données, stockant dans un espace minimal les informations nécessaires à la description d'un circuit.

- Quelques fonctions disponibles, montrant qu'une ergonomie soignée peut cacher la complexité interne d'un logiciel.

#### I- INTRODUCTION

La plupart des logiciels de C.A.O proposés actuellement sur le marché présente l'inconvénient de ne pas être portables, cette caractéristique entraı̂ne inévitablement les inconvénients suivants :

- Une dépendance vis-à-vis du constructeur du matériel informatique.

- Une difficulté d'évolution en puissance de calcul, les produits n'étant pas toujours disponibles sur l'ensemble de la gamme d'un constructeur. Par exemple IBM, qui commercialise des outils CAO sous VM, alors que ce système ne sait pas exploiter les capacités des plus grands ordinateurs du constructeur. Ce problème est en cours de résolution.

- le concepteur doit dans certains cas connaître plusieurs produits différents bien que ceux ci présentent les mêmes fonctionnalités. En effet, peu de fournisseurs proposent actuellement la schématique logique, électrique et le dessin des masques en un seul produit.

La plupart des produits de C.A.O ont été développés initialement sur de gros systèmes, par la force des choses puisque seules ces machines étaient suffisamment puissantes à l'époque. L'apparition des stations de travail, au cours de ces dernières années, a entraîné une évolution très nette des mentalités et des techniques. L'existence de micro-ordinateurs de faible coût doit maintenant conduire à proposer des produits utilisables sur l'ensemble de la gamme, même si l'utilisation de systèmes moins performants entraîne une certaine perte de confort. Cet inconvénient ne devrait plus en être un très longtemps étant donnée la montée en puissance des PC ou des PS qui ont maintenant des performances qui sont tout à fait comparables à celles des stations de travail.

# II- LES OBJECTIFS VISES

#### 1) LA DESCRIPTION HIERARCHIQUE

Un des buts recherchés est d'offrir à l'utilisateur un produit s'adaptant à sa méthode de conception. Celle-ci étant hiérarchique, notre produit le sera aussi. De plus, le concepteur peut réaliser son étude de façon descendante ou ascendante en fonction de son avancement. Cela nous a conduit à créer un logiciel où la hiérarchie peut être manipulée dans les deux sens, et ceci de manière conviviale.

#### 2) LA PORTABILITE

La portabilité d'un logiciel graphique sur des systèmes provenant de plusieurs constructeurs peut se résoudre à condition de prendre en compte les points suivants :

- choix du langage de programmation

- choix des normes graphiques

Le langage de programmation retenu est le FORTRAN 77 en raison de sa disponibilité sur l'ensemble des systèmes informatiques ayant une vocation de calcul scientifique. Ce choix peut apparaître surprenant en raison de l'existence de langage tel que PASCAL ou C. Cependant, il faut noter que PASCAL n'est pas encore normalisé, et que C ou ADA ne sont pas implantés sur tous les systèmes (notamment sur les machines les plus puissantes).

L'indépendance vis-à-vis des équipements graphiques utilisés est garanti en s'appuyant sur des normes graphiques internationales (GKS, PHIGS). L'utilisation de ces bibliothèques normalisées impose quasiment l'utilisation de FORTRAN, qui est le seul interface fourni en standard sur tous les environnements. Des interfaces avec le langage C commencent à apparaître sur tous les systèmes, mais n'étaient pas disponibles au début de notre étude.

#### 3) LA BASE DE DONNEES

Le logiciel s'appuie sur une base de données qui permettra le stockage de tous les schémas. Afin de garantir une indépendance vis-à-vis d'autres produits nécessaires dans les différentes phases de conception (simulation, vérification, extraction...), l'éditeur graphique possède son propre format. Ceci peut paraître contraignant, mais c'est la seule solution pour garantir la portabilité. Cette base est constituée d'un ensemble de fichiers standards du FORTRAN, ne posant aucun problème de migration. De plus, le fait d'avoir une base de données propre à l'éditeur était indispensable pour pouvoir stocker à la fois les schémas logiques, les schémas électriques et les dessins de masques. Nous avons en effet généralisé notre éditeur afin d'offrir un interface graphique unique au concepteur, ce qui ne peut que lui faciliter la tâche. Le rôle du concepteur n'est pas d'apprendre à se servir d'outils informatiques, mais de réaliser un circuit. Dans ce cas, l'informatique doit être un outil et non un but.

#### 4) LA COMMUNICATION AVEC L'EXTERIEUR

Pour garantir la communication avec l'extérieur, le produit offre des interfaces dans les formats GDS2 (Graphic Data Stream) et CIF (Caltech Intermediate Format) qui sont les deux représentations les plus utilisées pour l'échange de données en CAO électronique. Ces interfaces fonctionnent dans les deux sens et permettent donc de lire et d'écrire du GDS2 et du CIF.

# III- LA NORME GRAPHIQUE GKS

#### 1) LES STATIONS DE TRAVAIL

Au sens GKS (Graphic Kernel System), on appelle station de travail (workstation) tout périphérique sur lequel on peut faire des tracés et/ou des entrées sorties.

Ces stations peuvent être de différents types :

- écrans graphiques

- traceurs

- fichiers (métafichiers)

Plusieurs stations peuvent être ouvertes simultanément, mais une seule est active à un instant donné.

#### 2) LES TRANSFORMATIONS

Trois espaces (surfaces planes abstraites caractérisées par un système de coordonnées) sont définis :

- WC-SPACE : World coordinate space

Système de coordonnées utilisateur avec lequel le programme d'application composera son dessin.

## - NDC-SPACE : Normalized device coordinate space

Espace de coordonnées normées qui peut être considéré comme une surface de visualisation abstraite indépendante des postes de travail. Les coordonnées sont comprises entre 0 et 1 dans les deux dimensions.

#### - DC-SPACE : Device coordinate space

Espace des coordonnées de l'écran. On définit ici la taille de l'écran (ou autre station de travail) utilisé exprimée en mètres.

Il existe aussi 4 régions rectangulaires distinctes :

- NT-WINDOW : Région définie dans le WC-SPACE. C'est dans cette zone que le graphique est tracé. Plusieurs NT-WINDOWS peuvent être définies dans une même application.

- NT-VIEWPORT : Région définie dans le NDC-SPACE. C'est la projection de la NT-WINDOW dans l'espace de coordonnées normalisées. On a une NT-VIEWPORT par NT-WINDOW.

- WORKSTATION-WINDOW : Région définie dans le NDC-SPACE. Tout graphique contenu dans l'intersection de cette fenêtre et de la NT-VIEWPORT sera visualisé à l'écran.

- WORKSTATION-VIEWPORT : Région définie dans le DC-SPACE. Zone de l'écran dans laquelle sera effectivement visualisé le graphique.

Une fois ces 3 espaces et ces 4 fenêtres définies, il ne manque plus que la définition de 2 transformations pour pouvoir travailler :

- Transformation de normalisation

- Transformation de poste de travail

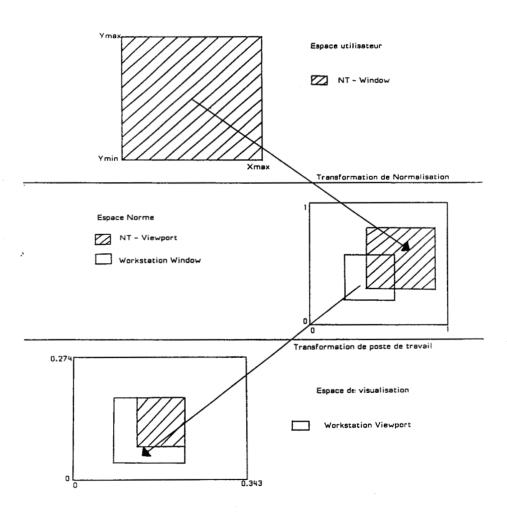

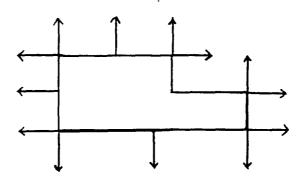

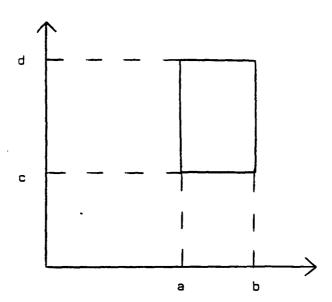

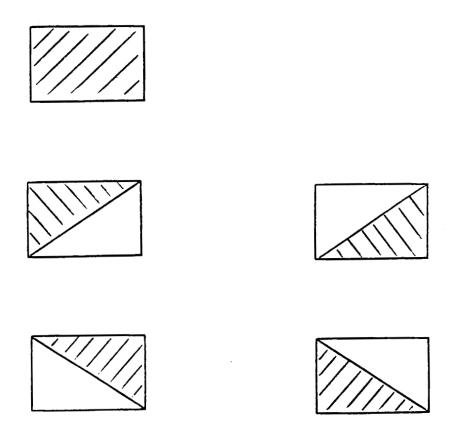

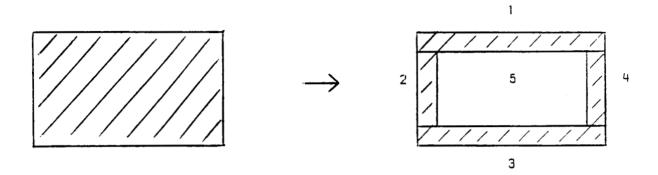

La figure 9 illustre le principe des transformations des fenêtres de GKS.

Figure 9:

Principe de transformation de fenêtre de GKS

#### 3) LES PRIMITIVES GRAPHIQUES

On distingue 4 grandes primitives de tracé :

- GPL : Tracé d'un polygone fermé ou non. Les attributs modifiables sont la couleur et le type de tracé (plein, pointillés, tirets...).

- GFA : Tracé d'un polygone fermé avec remplissage. Les attributs modifiables sont le type de remplissage (plein,creux,hachuré...) et la couleur.

- GCA: Tracé d'une matrice de carrés pleins. Ceci permet d'afficher, par exemple, des palettes de couleurs ou des images. Le seul attribut modifiable est la couleur de chaque élément. Tous les carrés constituant la matrice ont la même taille.

- GTX : Tracé d'un texte. Les attributs modifiables sont la couleur, la police de caractères, l'angle d'écriture et le sens d'écriture (haut-bas, droite-gauche...).

## 4) LA SEGMENTATION

On appelle segment graphique, un ensemble d'entités de base (GPL, GFA, GCA, GTX) regroupées dans un objet que l'on désire manipuler dans son ensemble. Ces segments sont repérés par des numéros. Il est possible de distinguer des sous-parties à l'intérieur d'un segment. Les opérations disponibles sont la translation, la rotation et le changement d'échelle. Toute combinaison de ces opérations est possible. L'utilisateur peut aussi renommer, copier ou insérer un segment.

L'utilisation des segments est indispensable pour la réalisation d'un éditeur graphique, car ce sont les seules entités pour lesquelles on peut définir des attributs de visibilité et de détectabilité, et auxquelles on peut attribuer une priorité d'affichage et de sélection.

#### 5) LES ROUTINES D'INTERACTION

Afin de rendre le logiciel interactif, le programmeur dispose d'un ensemble de fonctions permettant d'interagir avec l'utilisateur. Il est possible de :

- saisir les coordonnées d'un point à l'écran (request locator).

- sélectionner un segment et l'un de ses sous ensembles (request pick).

- demander à l'utilisateur de fournir une chaîne de caractères (request string).

- sélectionner une réponse parmi un ensemble (request choice).

- saisir une suite de points de manière continue (request stroke).

## IV- LES DONNEES MANIPULEES

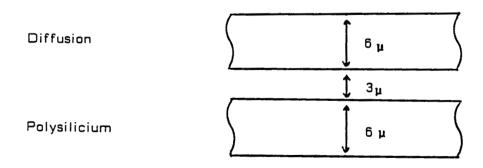

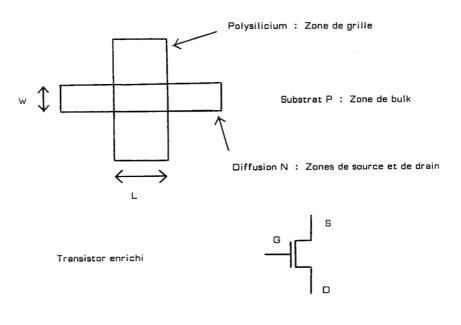

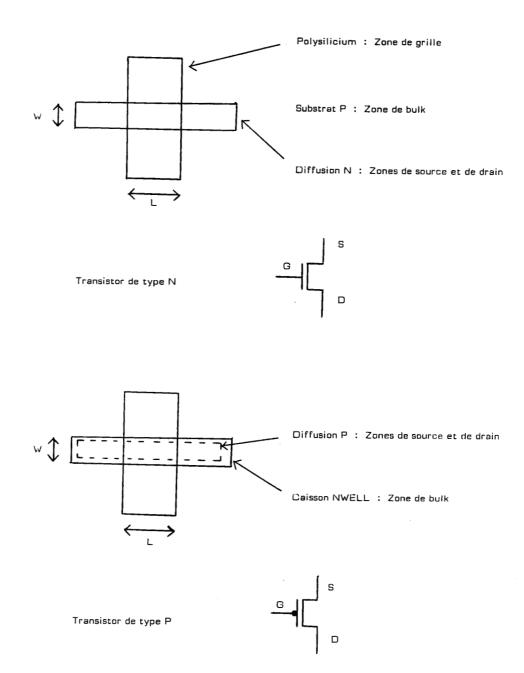

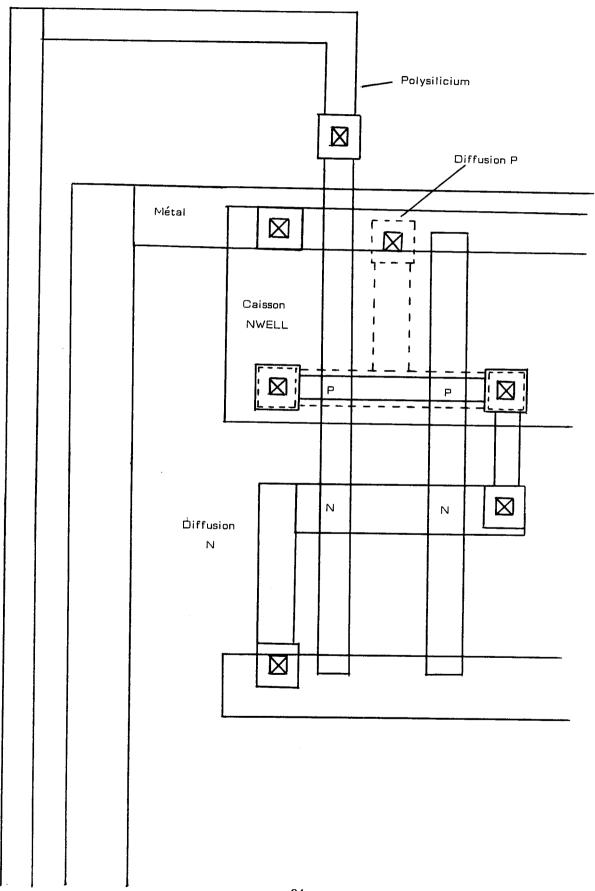

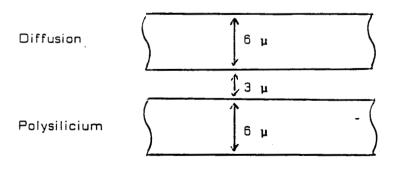

Un circuit intégré est composé de couches superposées dépendantes de la technologie utilisée. Chaque niveau (ou layer) est composé d'un ensemble de contours fermés (rectangles, polygones...). Dans le cas d'une technologie NMOS, on compte 9 niveaux :

- <u>Diffusion</u>: Ce niveau sert à réaliser les source et drain des transistors, mais aussi des interconnexions,

- <u>Transistors naturels</u>: Ce niveau permet d'indiquer les transistors qui ne sont ni enrichis ni déplétés. Ces transistors servent essentiellement à la protection des entrées contre l'électricité statique.

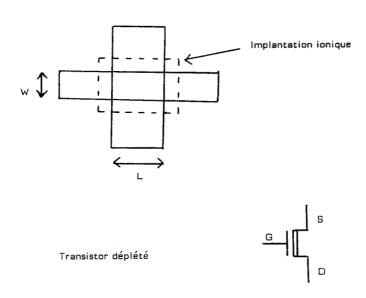

- <u>Implantation ionique</u>: Un transistor qui subit une implantation ionique devient un transistor déplété. Les autres sont enrichis.

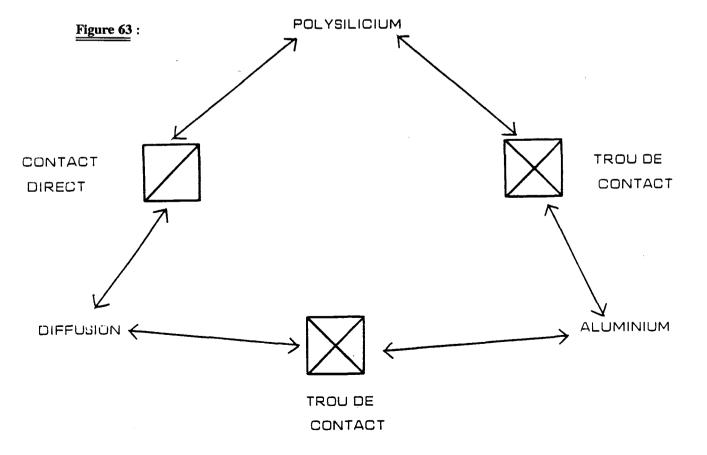

- <u>Contact direct</u>: Ce masque permet d'établir des contacts entre le niveau de polysilicium et le niveau de diffusion.

- <u>Polysilicium</u> : Ce niveau sert à réaliser les grilles des transistors, mais aussi des interconnexions.

- <u>Trou de contact</u> : Ce masque permet de réaliser des liaisons entre différentes couches technologiques.

- Surtrou : Ce niveau représente le débordement de métal autour du trou.

- Aluminium : Ce niveau ne sert qu'à réaliser des connexions.

- <u>Passivation</u>: Ce masque représente les zones du circuit qui ne doivent pas être passivées (couvertes de verre). Seuls les plots de contact ne sont pas passivés.

Chacun de ces niveaux peut être composé de plusieurs milliers (ou millions) de figures élémentaires. Le traitement d'une telle quantité de données est impensable sans la mise en oeuvre d'une description hiérarchique du circuit. Ceci n'est pas limitatif dans la mesure où le raisonnement du concepteur, comme nous l'avons vu précédemment, est lui aussi hiérarchique.

## V- LA STRUCTURE D'INFORMATION

#### 1) EXEMPLE DE HIERARCHIE

L'exemple traité ci-après pose correctement la plupart des problèmes de la représentation d'un schéma au sens général.

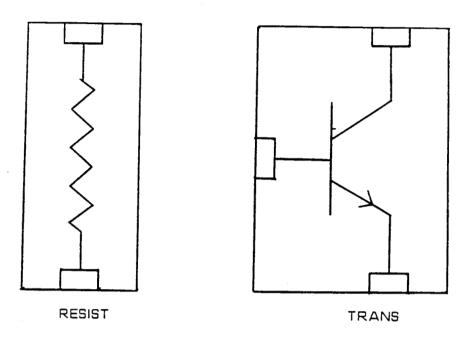

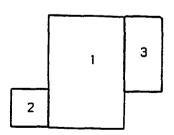

Soit à représenter la construction d'un étage différentiel. Dans un premier temps, le concepteur doit se définir deux éléments de base : la résistance et le transistor.

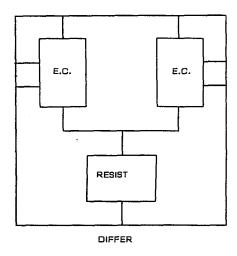

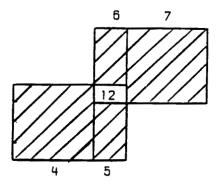

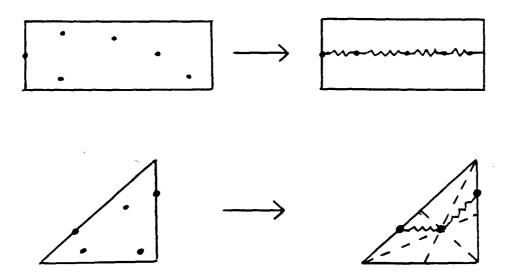

Figure 10:

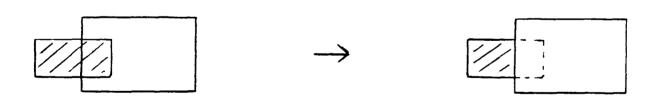

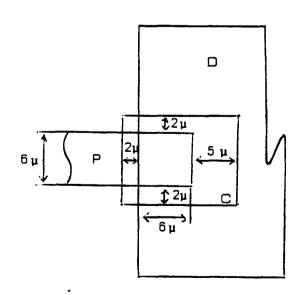

Chacun de ces éléments de base occupe une certaine surface décrite par un contour fermé que l'on appelera ENCOMBREMENT. Les différents éléments pourront être interconnectés les uns aux autres par des CONNEXIONS qui réunissent des points d'entrée et de sortie. Ces points seront appelés CONNECTIQUES.

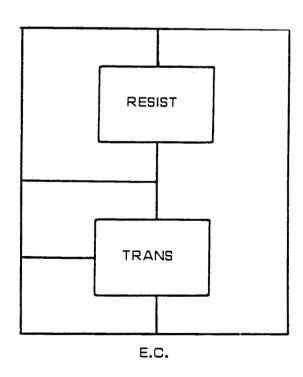

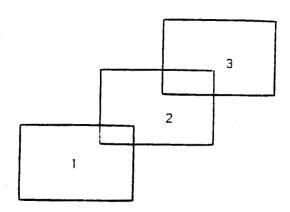

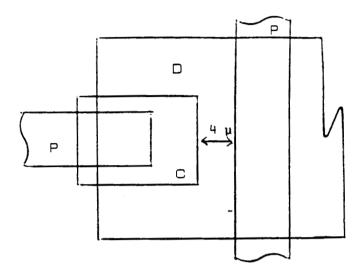

Après création des éléments de base, le concepteur peut réaliser un montage plus complexe : émetteur commun, réalisé par l'assemblage de deux cellules de base.

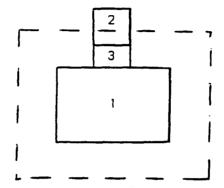

Figure 11:

Ce circuit est défini par un certain encombrement, ses connectiques, les cellules qui la composent : RESIST et TRANS et les connexions qui réunissent les points d'entrée et de sortie des cellules.

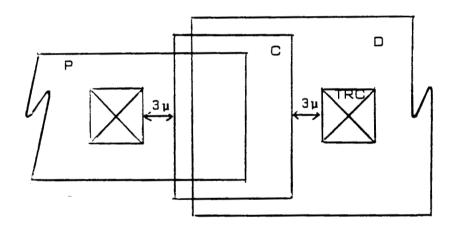

La construction de l'étage différentiel se fait en réalisant une symétrie suivant l'axe des Y pour la cellule émetteur commun et en insérant la cellule "resist". Cette nouvelle cellule comporte son propre encombrement, ses propres connectiques. Elle est constituée de trois cellules "filles" qui sont reliées par des connexions.

Figure 12:

Si on ne prend pas certaines précautions sur le plan de la représentation des informations en mémoire centrale, les volumes de données seront vite incompatibles avec des équipements de type micro-ordinateurs. La cellule qui vient d'être définie, comporte certaines cellules "filles" identiques sur le plan du tracé, seule la position origine de ces cellules diffère.

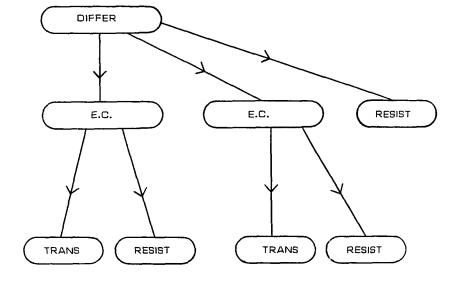

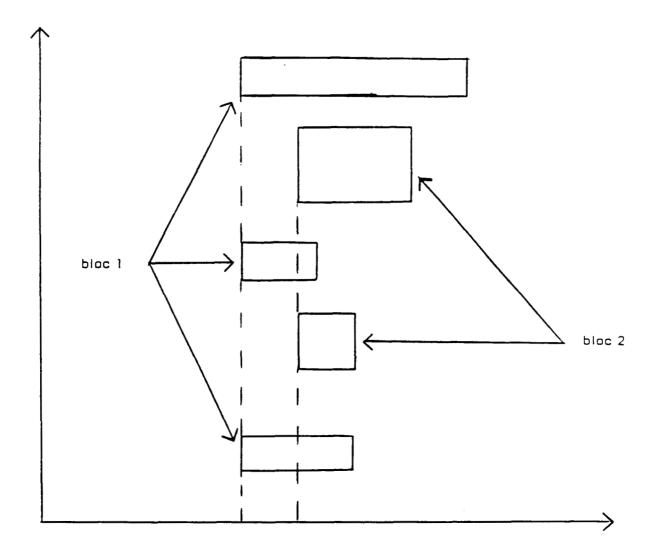

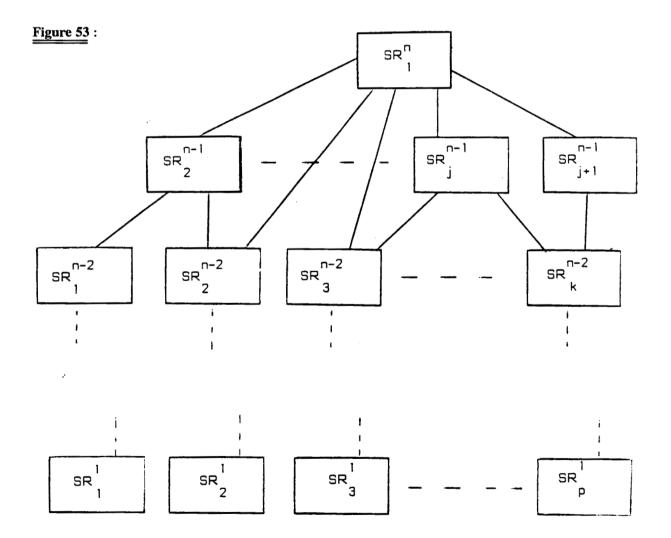

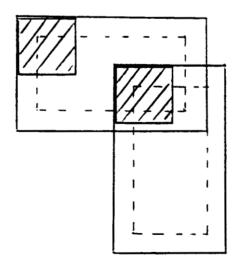

L'exemple traité précédemment introduit une notion de dépendance PERE FILS dans la construction de cellules complexes. Ceci conduit immédiatement à une représentation de type arborescente.

Figure 13:

## 2) CONSTRUCTION DE LA STRUCTURE

La description arborescente d'un circuit doit viser plusieurs objectifs :

- réduire au maximum la place requise par la structure de donnée. La description géométrique de tout objet identique ne devra être présente qu'une fois et une seule en mémoire centrale.

- Permettre la sélection de tout élément graphique visible à l'écran et pouvoir déterminer le plus rapidement possible l'entité à laquelle il appartient.

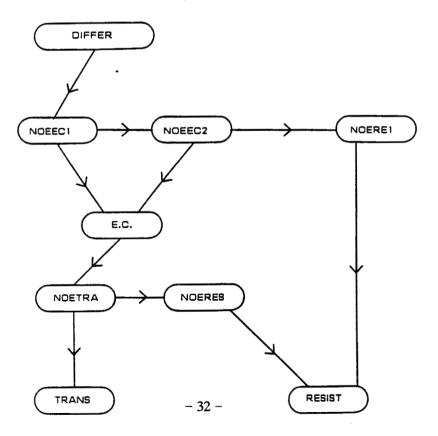

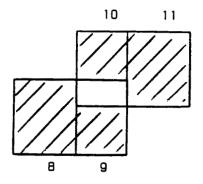

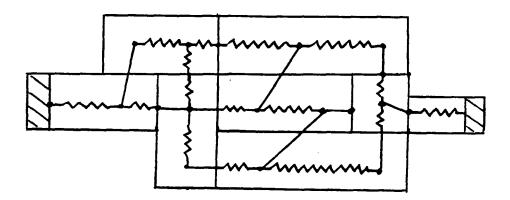

Reprenons l'exemple de l'étage différentiel vu au paragraphe E.1. On définit une entité BLOC permettant de contenir une seule fois les figures nécessaires à l'affichage d'un élément (transistor, résistance...). Chaque transistor est défini dans un autre élément de la structure appelé NOEUD qui pointe vers le BLOC correspondant.

Si l'utilisateur construit l'étage différentiel par assemblage direct de 2 transistors et 3 résistances, la structure sera la suivante :

Figure 14:

Les entités NOExxx contiennent les positions et les opérations (rotations, symétries, translations, répétitions) subies par les dessins qu'elles pointent. Les autres entités contiennent l'ensemble des informations permettant de réaliser le dessin (dimensions, couleur, type de figure...). Ainsi, DIFFER ne contiendra que les lignes servant à lier les résistances et les transistors.

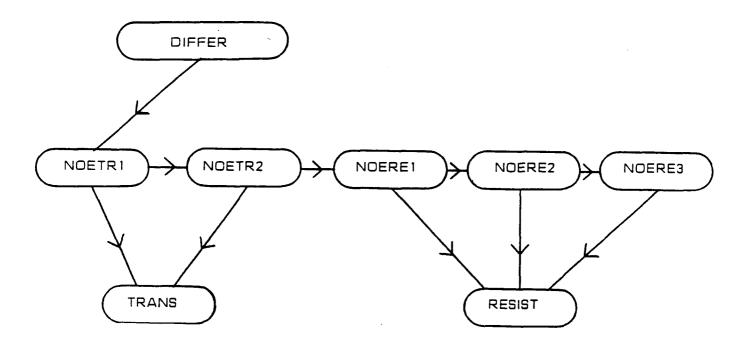

La construction d'un étage émetteur commun donnerait la structure suivante :

Figure 15:

La construction de l'étage différentiel à partir de l'étage émetteur commun nous donnerait, en suivant cette méthode, la structure suivante :

Figure 16:

Cette structure ne permet pas de représenter entièrement DIFFER. En effet, on constate qu'il n'y a que deux noeuds pointant sur la résistance et un seul sur le transistor, alors qu'il nous en faudrait un pour chacune des résistances et des transistors du circuit.

On ne pourrait conserver cette structure que pour une arborescence à 2 niveaux.

Cette structure étant insuffisante, il convient d'ajouter une nouvelle entité : le DESCRIPTIF, qui contient les informations caractérisant l'utilisation qui est faite d'un bloc (position par rapport au père, symétrie...) dans le cas où ce bloc est utilisé dans la descendance d'un autre bloc. Les noeuds ne sont plus que des entités graphiques représentant les divers éléments du circuit.

Cette nouvelle entité pointe naturellement vers le bloc qu'elle décrit, mais elle est à son tour pointée par le bloc père afin qu'un bloc soit défini par ses figures graphiques et sa descendance.

Les noeuds pointeront eux aussi les blocs qu'ils représentent, mais il faudra auparavant qu'ils aient pris en compte les opérations et positions du bloc. Le pointeur sera donc en direction d'un descriptif, qui pointera le bloc.

L'étage différentiel précédent sera donc obtenu par l'utilisation de 8 noeuds, 6 descriptifs et 4 blocs.

Figure 17:

- : Liaison d'un bloc vers ses descriptifs fils

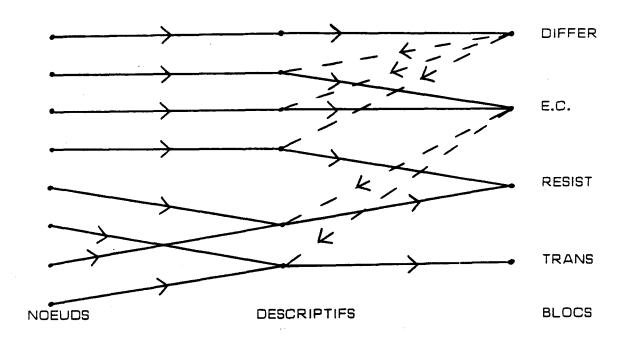

#### 3) PRESENTATION DE LA STRUCTURE

La structure de données décrite précédemment peut paraître complexe. Une description détaillée est donnée en annexe 2. Cette complexité pourrait être réduite par l'utilisation d'une bibliothèque graphique gérant la hiérarchie, ce qui n'est pas le cas de GKS. PHIGS répond à ce besoin, mais n'est actuellement disponible que dans l'environnement IBM. Reprenons point par point les différents éléments de cette structure, et regardons plus en détail.

- Le catalogue courant : à un instant donné, le concepteur ne dispose que d'une base de données en lecture-écriture. En effet, nous pensons qu'il faut une base par circuit.

- Le catalogue temporaire : le point précédent ne doit pas empêcher l'utilisateur de réutiliser des cellules existantes. Il doit pour cela, copier ces éléments dans sa base. Ceci est logique, puisque la technologie peut changer d'un circuit à l'autre.

- Les formes : ces éléments contiennent les coordonnées des graphiques, sous forme de paires de points.

- Le bloc : cet élément décrit le contenu d'une cellule. Il contient un pointeur vers les formes représentant l'encombrement (ce qui permet de créer des encombrements de forme quelconque, ce qui autorise la schématique logique et électrique) vers les connectiques et connexions du bloc et vers ses descriptifs fils pour la description de la hiérarchie du circuit.

- Le descriptif : il pointe vers le bloc qu'il décrit. Il contient la position de son bloc par rapport au point origine de son père, ce qui autorise des opérations sur des cellules composées. Ainsi les opérations subies par un bloc sont la composition des opérations subies par ses pères et ses propres transformations. Ses fils héritent de ses opérations.

- Le noeud : il décrit l'arborescence visible. A chaque occurrence d'un bloc dans le circuit est associé un noeud, alors qu'une seule entité BLOC existe. C'est le noeud qui permet de faire la relation entre les segments GKS et la structure du circuit (descriptifs et blocs). L'utilisation d'une bibliothèque graphique hiérarchique telle que PHIGS autorise la suppression de cette entité.

- La connectique : cette entité est utilisée lors d'une visualisation de niveau 1 d'un bloc. Dans ce cas, on affiche seulement l'encombrement et la connectique d'un bloc, ce qui permet d'accélérer le chargement du circuit, et allège le schéma. Chaque connectique est nommée (VDD, VSS, IN, OUT...)

- Les connexions : on appelle connexion tout ensemble de formes appartenant à un niveau donné. Ces entités pointent donc vers les formes constituant les cellules de base, mais aussi vers les formes connectant des blocs fils à l'intérieur d'un bloc père.

- Les opérations : ici, on décrit les opérations (rotation, symétrie, translation...) subies par une occurrence d'un bloc.

- Les "segments" : dans ces entités, on effectue la correspondance entre les segments GKS, et les noeuds. Les "segments" (au sens de notre éditeur et non au sens GKS) sont indispensables pour la gestion de l'interactivité graphique. Ces "segments" sont aussi chaînés par niveaux afin de pouvoir rendre un niveau visible ou non.

- Les niveaux : pour chaque niveau de la technologie employée, il faut définir la couleur, le type de tracé et la visibilité.

Cette structure de données est indépendante de la base de données. Ceci est réalisé par l'emploi de fonctions de haut niveau, indépendantes de la structure physique de la base. Ainsi, seuls quelques sous-programmes simples seront à modifier en cas de changement de la base (ou en cas de changement de système, ce qui entraîne toujours quelques problèmes dans la gestion des entrées-sorties).

## VI- DESCRIPTION DE LA BASE DE DONNEES

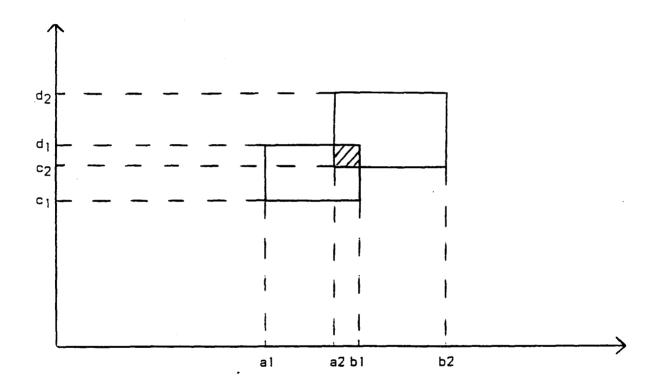

## 1) IMPORTANCE DE LA BASE DE DONNEES

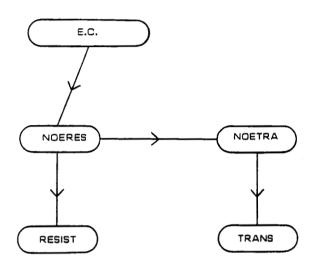

La base de données est un élément clé de la chaîne de conception de circuit intégré. Comme nous l'avons vu, cette chaîne est constituée de nombreux logiciels. Chacun de ces produits possède sa propre structure de données et sa propre représentation des informations.

Partant de là, il est très probable que chaque maillon possèdera sa propre base de données. Ceci impose donc beaucoup de changements de formats entre ces différentes bases. Notre but était de faire une base unique commune à l'ensemble des logiciels développés. Pour ce faire, nous avons d'abord regardé les besoins de l'éditeur graphique. Nous avons ensuite vérifié que les autres produits n'utilisaient que des sous-ensembles de cette base. Une fois ce point validé, nous nous sommes attachés à la définition précise de la base de données de l'éditeur graphique, et à la définition des fonctions d'accès de haut niveau communes à tous les produits. Pour ces raisons, la base de données ne sera décrite que dans le chapitre de l'éditeur graphique, car elle est la même pour tous nos logiciels.

Cette unicité de la base de données permet donc un couplage étroit entre l'éditeur, le vérificateur des règles de garde qui extrait les données dont il a besoin directement de la base, et qui met à jour cette base en cas de détection d'erreurs. Il en est de même pour l'extracteur de schémas, en ce qui concerne la prise en compte des données. Ce produit, pour le moment, ne met pas à jour la base, car nous ne générons pas le schéma électrique sous forme graphique.

Figure 18:

# 2) **GENERALITES**

Dans la base, ne doivent être stockées que les informations minimales permettant de reconstituer le travail réalisé par le concepteur.

- Informations générales sur chaque bloc :

- . son nom

- . son attribut

- . son échelle

- Les figures décrivant le bloc, i.e. l'ensemble des formes (2 points), leur qualificateur (type de formes : rectangles, polygones, lignes...) et le niveau de référence (encombrement, connectique, connexions (polysilicium, diffusion...)).

- Les noms des connectiques du bloc.

- La description de la descendance :

- . les blocs fils

- . leur position relative par rapport au père

- . les opérations éventuellement subies

- Toutes les informations concernant les segments se révèlent inutiles dans la base, car elles sont liées à l'entité noeud qui n'apparaît plus ici. De plus elles n'ont de signification que pour l'aspect visualisation du circuit.

- Les caractéristiques des tracés pourraient être stockées dans la base. Si ceci n'est pas réalisé, on ne peut plus modifier de façon quelconque les types de tracés, en particulier le numéro associé à un niveau. Ceci pourrait, à terme, se révéler gênant, et devrait être corrigé prochainement.

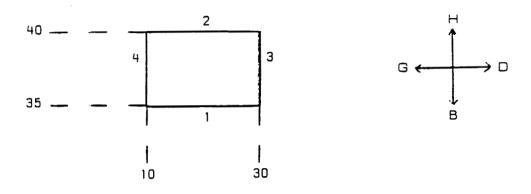

#### 3) PROPOSITION DE STRUCTURE

Une base sera implantée sous forme d'un fichier en accès direct. Une description détaillée de la structure est donnée en annexe 3. D'une façon générale, ce fichier peut être décomposé en quatre sous-ensembles :

- L'entête de base. Premier enregistrement de la base, il contient les valeurs décrivant l'état de la base (nombre total d'enregistrements, nombre d'enregistrements utilisés, premier enregistrement de la directory et le nombre de blocs dans la base).

- La directory. Cet ensemble peut être considéré comme le catalogue de la base. Il contient l'ensemble des blocs et leurs caractéristiques générales (attribut de lecture-écriture, échelle...), et pointe vers les autres éléments constituant ce bloc.

- La description des blocs. Dans cette zone, on trouvera les enregistrements contenant les formes, les connectiques, les descriptifs et les opérations. Ces différents enregistrements sont chaînés entre eux.

- La zone libre. Cette partie est constituée d'enregistrements non occupés. Ils sont gérés sous forme de liste chaînée et/ou de liste contiguë (la liste contiguë n'a de sens que si on travaille sur un système ne disposant pas d'allocation dynamique d'espace disque tel que VM/CMS).

#### 4) LES FONCTIONS D'ACCES EVOLUEES

Les fonctions d'accès évoluées s'appuient sur un ensemble de fonctions de plus bas niveau éventuellement appelables directement. L'interface entre ces programmes et l'application se fait par l'utilisation de buffers permettant une indépendance des fonctions d'accès à la base vis-à-vis de la structure de données de l'application. Ces programmes remplissent les fonctions suivantes :

- Obtention de la liste des bases accessibles à l'utilisateur.

- Ouverture d'une base en lecture-écriture ou en lecture seule.

- Fermeture d'une base.

- Obtention de la liste des éléments de la base. Ces éléments sont des blocs ou des circuits.

- Lecture des caractéristiques d'un bloc. Cette fonction nous retourne l'échelle du bloc, ainsi que les pointeurs permettant d'aller lire les autres entités constituant ce bloc.

- Lecture des entités du bloc à partir du pointeur fourni par la fonction précédente. Chaque élément possède son propre programme de lecture.

- Obtention d'un emplacement libre dans la base pour un type d'entité donné. Le programme appelé est différent pour un emplacement libre dans la directory de la base ou pour un emplacement dans le reste du fichier.

- Ecriture d'un enregistrement dans la directory. Cette fonction permet d'écrire un bloc dans la base. Il faut fournir à ce programme les pointeurs du bloc vers les autres entités le composant, ce qui impose d'écrire d'abord ces éléments.

- Ecriture d'une partie de bloc dans le fichier. Chaque type d'élément possède son propre programme d'écriture.

- Destruction d'un élément dans la directory de la base. Cette fonction doit être appelée après la destruction des entités constituant le bloc à détruire.

- Destruction d'une entité dans le fichier.

- Changement du nom d'un bloc.

Partant de là, il est possible de créer des fonctions d'accès beaucoup plus évoluées, mais dépendantes de la structure de données de l'éditeur graphique. Voici quelques exemples de fonctions évoluées.

- Chargement d'un bloc et de sa descendance dans la structure.

- Lecture du niveau de hiérarchie inférieure pour un bloc donné.

- Ecriture d'un bloc et des entités le composant.

- Ajout d'entités à un bloc existant.

- Suppression d'un bloc et de sa descendance.

Et bien d'autres fonctions dont l'énumération serait fastidieuse.

## VII- QUELQUES FONCTIONS DISPONIBLES A L'UTILISATEUR

#### 1) LA CONVIVIALITE

Quand on réalise un logiciel, la convivialité doit être maximale. C'est encore plus vrai pour les produits comme notre éditeur. En effet, l'utilisation du graphique doit permettre l'utilisation minimale du clavier, objet généralement peu apprécié du concepteur, une présentation plus claire de certaines fonctions (un dessin vaut souvent mieux qu'un long discours), et autoriser une gestion de menus moins hiérarchique grâce à la grande taille de l'écran.

Pour faciliter le dialogue avec l'utilisateur, l'ensemble des fonctions proposées dans notre éditeur graphique sont regroupées dans différents menus qui caractérisent un environnement de travail particulier. On distingue ainsi 3 menus chaînés :

- Le menu1, environnement d'accueil

- Le menu2, environnement de visualisation et de placement de blocs

- Le menu3, environnement d'édition d'un bloc

Pour ne pas pénaliser l'utilisateur par une structure trop hiérarchisée des menus qui le contraindrait à des changements d'environnement trop fréquents, certaines fonctions d'un environnement donné restent disponibles dans les autres.

De plus, certaines fonctions peuvent provoquer le passage dans un sous-environnement particulier. Lorsque l'utilisateur quitte ce sous-environnement, il retrouve l'état précédent : voici quelques fonctions proposées par l'éditeur, classées par environnement (le schéma des écrans est donné en annexe 4 avec la liste des fonctions).

# 2) L'ENVIRONNEMENT D'ACCUEIL

Cet environnement propose des fonctions :

- de manipulation des circuits de la base. Le concepteur dispose d'opérations de suppression, recopie et changement de noms de blocs ou circuits dans la base.

- utilitaires. On y trouve des fonctions permettant la communication avec l'extérieur telles que la lecture ou l'écriture de fichiers externes à la base en format GDS2 ou CIF. Les fonctions de sortie de schémas sur traceur ou fichier texte sont aussi disponibles à ce niveau. Une fonction d'aide permet au concepteur de visualiser les différentes bases qu'il possède, et leur contenu.

- de mise à jour des paramètres d'utilisation de l'éditeur, tels que la palette des couleurs et la représentation des différents niveaux.