LABORATOIRE D'INFORMATIQUE FONDAMENTALE DE LILLE

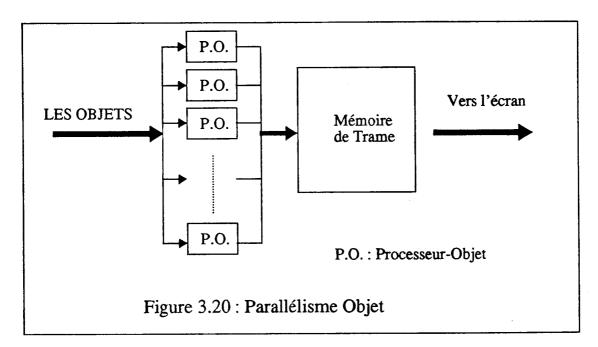

Année 1991

Numéro d'ordre: 672

# **THESE**

présentée à

l'Université des Sciences et Techniques de LILLE FLANDRES ARTOIS

Pour Obtenir le titre de

Docteur en Informatique

Titre:

Etude d'un processeur de visualisation d'images de synthèse en temps réel exploitant un parallélisme massif objet: le projet I.M.O.G.E.N.E

Par Christophe CHAILLOU

soutenue le 16 Janvier 1991 devant la commission d'Examen

Membres du Jury:

Vincent CORDONNIER Michel LUCAS Jean Paul SANSONNET Ute CLAUSSEN Michel MERIAUX Bernard PEROCHE Président Rapporteur Rapporteur Examinateur Directeur de Thèse Examinateur

## UNIVERSITE DES SCIENCES ET TECHNIQUES DE LILLE FLANDRES ARTOIS

## DOYENS HONORAIRES DE L'ANCIENNE FACULTE DES SCIENCES

M.H. LEFEBVRE, M. PARREAU.

# PROFESSEURS HONORAIRES DES ANCIENNES FACULTES DE DROIT ET SCIENCES ECONOMIQUES, DES SCIENCES ET DES LETTRES

MM. ARNOULT, BONTE, BROCHARD, CHAPPELON, CHAUDRON, CORDONNIER, DECUYPER, DEHEUVELS, DEHORS, DION, FAUVEL, FLEURY, GERMAIN, GLACET, GONTIER, KOURGANOFF, LAMOTTE, LASSERRE, LELONG, LHOMME, LIEBAERT, MARTINOT-LAGARDE, MAZET, MICHEL, PEREZ, ROIG, ROSEAU, ROUELLE, SCHILTZ, SAVARD, ZAMANSKI, Mes BEAUJEU, LELONG.

## PROFESSEUR EMERITE

M. A. LEBRUN

#### ANCIENS PRESIDENTS DE L'UNIVERSITE DES SCIENCES ET TECHNIQUES DE LILLE

MM. M. PAREAU, J. LOMBARD, M. MIGEON, J. CORTOIS.

# PRESIDENT DE L'UNIVERSITE DES SCIENCES ET TECHNIQUES DE LILLE FLANDRES ARTOIS

M. A. DUBRULLE.

#### PROFESSEURS - CLASSE EXCEPTIONNELLE

M. CONSTANT Eugène

M. FOURET René

Physique du solide

M. GABILLARD Robert

Electronique

M. MONTREUIL Jean

Biochimie

M. PARREAU Michel

Analyse

M. TRIDOT Gabriel

Chimie Appliquée

#### PROFESSEURS - 1ère CLASSE

M. BACCHUS Pierre

M. BIAYS Pierre

Géographie

M. BILLARD Jean

Physique du Solide

M. BOILLY Bénoni

Biologie

M. BONNELLE Jean-Pierre

M. BOSCQ Denis

Probabilitéss

M. BOUGHON Pierre

Algèbre

M. BOURIQUET Robert Biologie Végétale

M. BREZINSKI Claude Analyse Numérique

M. BRIDOUX Michel M. CELET Paul M. CHAMLEY Hervé M. COEURE Gérard

M. CORDONNIER Vincent

M. DAUCHET Max

M. DEBOURSE Jean-Pierre

M. DHAINAUT André

M. DOUKHAN Jean-Claude

M. DYMENT Arthur M. ESCAIG Bertrand M. FAURE Robert

M. FOCT Jacques

M. FRONTIER Serge

M. GRANELLE Jean-Jacques

M. GRUSON Laurent M. GUILLAUME Jean M. HECTOR Joseph

M. LABLACHE-COMBIER Alain

M. LACOSTE Louis

M. LAVEINE Jean-Pierre

M. LEHMANN Daniel

Mme LENOBLE Jacqueline

M. LEROY Jean-Marie

M. LHOMME Jean

M. LOMBARD Jacques

M. LOUCHEUX Claude M. LUCQUIN Michel

M. MACKE Bruno

M. MIGEON Michel

M. PAQUET Jacques

M. PETIT Francis

M. POUZET Pierre M. PROUVOST Jean

M. RACZY Ladislas

M. SALMER Georges

M. SCHAMPS Joel

M. SEGUIER Guy M. SIMON Michel Melle SPIK Geneviève

M. STANKIEWICZ François

M. TILLIEU Jacques

M. TOULOTTE Jean-Marc

M. VIDAL Pierre

M. ZEYTOUNIAN Radyadour

Chimie-Physique Géologie Générale Géotechnique Analyse

Informatique Informatique

Gestion des Entreprises

Biologie Animale Physique du Solide

Mécanique

Physique du Solide

Mécanique Métallurgie

Ecologie Numérique Sciences Economiques

Algèbre

Microbiologie Géométrie

Chimie Organique Biologie Végétale Paléontologie Géométrie

Physique Atomique et Moléculaire

Spectrochimie

Chimie Organique Biologique

Sociologie

Chimie Physique Chimie Physique

Physique Moléculaire et Rayonnements Atmosph.

E.U.D.I.L.

Géologie Générale Chimie Organique

Modélisation - calcul Scientifique

Minéralogie Electronique Electronique

Spectroscopie Moléculaire

Electrotechnique

Sociologie Biochimie

Sciences Economiques

Physique Théorique

Automatique Automatique Mécanique

## PROFESSEURS - 2ème CLASSE

M. ALLAMANDO Etienne M. ANDRIES Jean-Claude

M. ANTOINE Philippe

M. BART André

M. BASSERY Louis

Composants Electroniques Biologie des organismes

Analyse

Biologie animale

Génie des Procédés et Réactions Chimiques

Mme BATTIAU Yvonne

M. BEGUIN Paul

M. BELLET Jean

M. BERTRAND Hugues

M. BERZIN Robert

M.BKOUCHE Rudolphe

M. BODARD Marcel

M. BOIS Pierre

M. BOISSIER Daniel

M. BOIVIN Jean-Claude

M. BOUQUELET Stéphane

M. BOUQUIN Henri

M. BRASSELET Jean-Paul

M. BRUYELLE Pierre

M. CAPURON Alfred

M. CATTEAU Jean-Pierre

M. CAYATTE Jean-Louis

M. CHAPOTON Alain

M. CHARET Pierre

M. CHIVE Maurice

M. COMYN Gérard

M. COQUERY Jean-Marie

M. CORIAT Benjamin

Mme CORSIN Paule

M. CORTOIS Jean

M. COUTURIER Daniel

M. CRAMPON Norbert

M. CROSNIER Yves

M. CURGY Jean-Jacques

Melle DACHARRY Monique

M. DEBRABANT Pierre

M. DEGAUQUE Pierre

M. DEJAEGER Roger

M. DELAHAYE Jean-Paul

M. DELORME Pierre

M. DELORME Robert

M. DEMUNTER Paul

M. DENEL Jacques

M. DE PARIS Jean Claude

M. DEPREZ Gilbert

M. DERIEUX Jean-Claude

Melle DESSAUX Odile

M. DEVRAINNE Pierre

Mme DHAINAUT Ni∞le

M. DHAMELINCOURT Paul

M. DORMARD Serge

M. DUBOIS Henri

M. DUBRULLE Alain

M. DUBUS Jean-Paul

M. DUPONT Christophe

**Mme EVRARD Micheline**

M. FAKIR Sabah

M. FAUQUAMBERGUE Renaud

Géographie

Mécanique

Physique Atomique et Moléculaire

Sciences Economiques et Sociales

**Analyse**

Alaèbre

Biologie Végétale

Mécanique

Génie Civil

Spectroscopie

Biologie Appliquée aux enzymes

Gestion

Géométrie et Topologie

Géographie

Biologie Animale

Chimie Organique

Sciences Economiques

Electronique

Biochimie Structurale

Composants Electroniques Optiques

Informatique Théorique

Psychophysiologie

Sciences Economiques et Sociales

Paléontologie

Physique Nucléaire et Corpusculaire

Chimie Organique

Tectolique Géodynamique

Electronique

Biologie

Géographie

Géologie Appliquée

Electronique

Electrochimie et Cinétique

Informatique

Physioliogie Animale

Sciences Economiques

Sociologie

Informatique

**Analyse**

Physique du Solide - Cristallographie

Microbiologie

Spectroscopie de la réactivité Chimique

Chimie Minérale

Biologie Animale

Chimie Physique

Sciences Economiques

Spectroscopie Hertzienne

Spectroscopie Hertzienne

Spectrométrie des Solides

Vie de la firme (I.A.E.)

Génie des procédés et réactions chimiques

Algèbre

Composants électroniques

M. FONTAINE Hubert

M. FOUQUART Yves

M. FOURNET Bemard

M. GAMBLIN André

M. GLORIEUX Pierre

M. GOBLOT Rémi

M. GOSSELIN Gabriel

M. GOUDMAND Pierre

M. GOURIEROUX Christian

M. GREGORY Pierre

M. GREMY Jean-Paul

M. GREVET Patrice

M. GRIMBLOT Jean

M. GUILBAULT Pierre

M. HENRY Jean-Pierre

M. HERMAN Maurice

M. HOUDART René

M. JACOB Gérard

M. JACOB Pierre

M. Jean Raymond

M. JOFFRE Patrick

M. JOURNEL Gérard

M. KREMBEL Jean

M. LANGRAND Claude

M. LATTEUX Michel

Mme LECLERCQ Ginette

M. LEFEBVRE Jacques

M. LEFEBVRE Christian

Melle LEGRAND Denise

Melie LEGRAND Solange

M. LEGRAND Pierre

Mme LEHMANN Josiane

M. LEMAIRE Jean

M. LE MAROIS Henri

M. LEROY Yves

M. LESENNE Jacques

M. LHENAFF René

M. LOCQUENEUX Robert

M. LOSFELD Joseph

M. LOUAGE Francis

M. MAHIEU Jean-Marie

M. MAIZIERES Christian

M. MAURISSON Patrick

M. MESMACQUE Gérard

M. MESSELYN Jean

M. MONTEL Marc

M. MORCELLET Michel

M. MORTREUX André

Mme MOUNIER Yvonne

Mme MOUYART-TASSIN Annie Françoise

M. NICOLE Jacques

M. NOTELET Francis

M. PARSY Fernand

Dynamique des cristaux

Optique atmosphérique

Biochimie Sturcturale

Géographie urbaine, industrielle et démog.

Physique moléculaire et rayonnements Atmos.

**Algèbre**

Sociologie

Chimie Physique

Probabilités et Statistiques

I.A.E.

Sociologie

Sciences Economiques

Chimie Organique

Physiologie animale

Génie Mécanique

Physique spatiale

Physique atomique

Informatique

Probabilités et Statistiques

Biologie des populations végétales

Vie de la firme (I.A.E.)

Spectroscopie hertzienne

**Biochimie**

Probabilités et statistiques

Informatique

Catalyse

**Physique**

Pétrologie

Algèbre

**Algèbre**

Chimie

**Analyse**

Spectroscopie hertzienne

Vie de la firme (I.A.E.)

Composants électroniques

Systèmes électroniques

Géographie

Physique théorique

Informatique

Electronique

Optique-Physique atomique

**A**utomatique

Sciences Economiques et Sociales

Génie Mécanique

Physique atomique et moléculaire

Physique du solide

Chimie Organique

Chimie Organique

Physiologie des structures contractiles

Informatique

Spectrochimie

Systèmes électroniques

Mécanique

M. PECQUE Marcel

M. PERROT Pierre

M. STEEN Jean-Pierre

Chimie organique Chimie appliquée Informatique

# Remerciements

Je remercie Monsieur le Professeur Vincent Cordonnier de me faire l'honneur de présider ce jury et d'avoir été l'initiateur de ce projet en me proposant un sujet de thèse.

Je remercie Messieurs Michel Lucas, Professeur à l'E.N.S.M. Nantes, et Jean-Paul Sansonnet, Directeur de Recherche CNRS au L.R.I., d'avoir porté une attention particulière à ce travail en acceptant d'en être rapporteurs.

Je remercie Monsieur Bernard Peroche, Professeur à l'école des Mines de Saint-Etienne, et Mademoiselle Ute Claussen, de la société AITEC, de leur participation au jury.

Je remercie chaleureusement Monsieur Michel Mériaux, Professeur à l'EUDIL, qui a encadré la majeure partie de ce travail. Je lui suis particulièrement gré d'avoir accepté d'être dérangé, jusqu'à plusieurs fois par jour, pour discuter et répondre à mes questions.

Je remercie toutes les personnes ayant travaillé sur I.M.O.G.E.N.E:

- Sylvain Karpf qui a réalisé le premier prototype dans le cadre de son D.E.A. et avec qui j'ai discuté de très nombreux après-midis pour définir I.M.O.G.E.N.E.

- Eric Nyiri qui réalise un excellent simulateur d'I.M.O.G.E.N.E.

- Samuel Degrande pour avoir conçu le premier circuit intégré.

- Isabelle Bourrust, Patrice Normand, Zhigang Nie, Vincent Lefévère de leur contribution.

- Dominique Gonzalez sans qui ce projet ne serait pas I.M.O.G.E.N.E.

Je remercie tous les membres de l'Equipe Graphique, pour les échanges que nous avons eus, ainsi que toutes les personnes qui font du L.I.F.L un lieu de travail efficace et agréable.

Je remercie Monsieur Henri Glanc qui a reproduit, avec soin et célérité, les différentes versions de cette thèse.

Merci aussi à Bénédicte et Clémence.

# **SOMMAIRE**

# INTRODUCTION

| I. PREMIER  | S ELEMENTS                                                   | 6          |

|-------------|--------------------------------------------------------------|------------|

| Le suje     | .t                                                           | 7          |

| •           | Réaliser un processeur de visualisation d'images de synthèse | 7          |

|             | Le temps réel                                                |            |

| Le Prod     | cessus de Visualisation                                      | 8          |

|             | Schéma global                                                | 8          |

|             | Exclusion des méthodes de lancer de rayons et de radiosité   | 9          |

|             | Organisation classique des processeurs de visualisation      | 11         |

|             | L'affichage, les écrans                                      | 12         |

| Le Para     | allélisme en synthèse d'images                               | 14         |

|             | Le Parallélisme                                              | 14         |

|             | Parallélisme et Processus de Visualisation                   | 14         |

|             | Vocabulaire                                                  |            |

| II. PRESENT | TATION ANALYTIQUE DES MACHINES DE RENDU                      | 18         |

| Les Ma      | chines                                                       | 19         |

|             | Geometry System                                              |            |

|             | Le circuit intégré PRC                                       | 21         |

|             | Le circuit intégré SAGE                                      | 22         |

|             | La machine Silicon Graphics 4D/240GTX                        |            |

|             | La machine Stellar GS1000                                    | 27         |

|             | Autres machines commerciales                                 | 29         |

|             | La Pixel Machine                                             | 30         |

|             | CAP                                                          | 32         |

|             | Experts                                                      | 33         |

|             | La Machine de Torborg                                        | 35         |

|             | GSP-NVS                                                      |            |

|             | Pixel-planes 4                                               |            |

|             | Pixel-planes 5                                               |            |

| Les Tal     | oleaux et Enseignements                                      | <b>4</b> 8 |

|             | Organisation des machines présentées                         | 50         |

|             | Parallélismes et effets pipe-lines exploités                 | 53         |

|             | Algorithmes utilisés                                         | 55         |

|             | Le processus de conversion en pixels                         |            |

|             | Performances annoncées                                       |            |

|             | Conclusion                                                   | 59         |

# SOMMAIRE

| III. VERS UN RENDU TEMPS REEL, ALGORITHMES ET ARCHITECTUR                    | E61 |

|------------------------------------------------------------------------------|-----|

| Organiser le processus de visualisation: Algorithmes                         | 62  |

| Les Opérations inter-objets:                                                 |     |

| les Eclairements                                                             |     |

| Organisation globale d'une machine d'affichage en temps réel                 |     |

| La mémoire de trame                                                          |     |

| Les Phénomènes d'aliassage                                                   |     |

| La modélisation, les primitives visualisables                                |     |

| Les solutions matérielles pour réaliser un processeur d'affichage temps réel | l84 |

| Parallélisme Massif et Réalisation Matérielle                                |     |

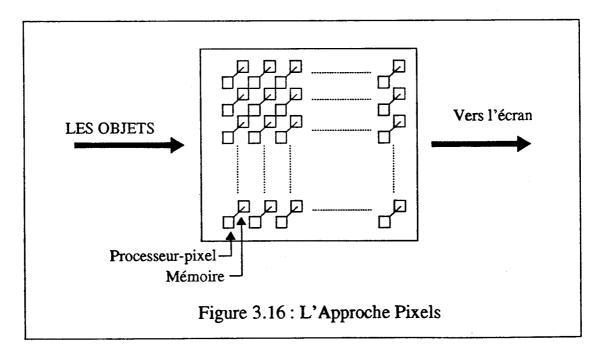

| L'Approche Pixels                                                            |     |

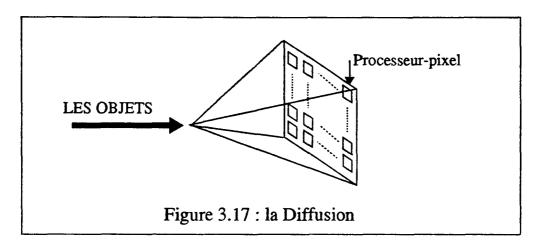

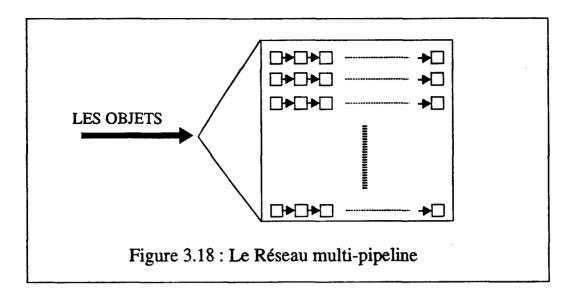

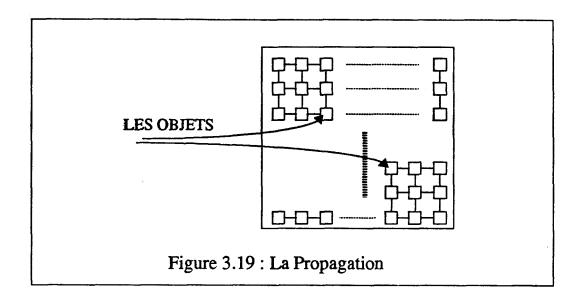

| L'Approche Objets                                                            | 89  |

| Comparaisons des deux approches                                              |     |

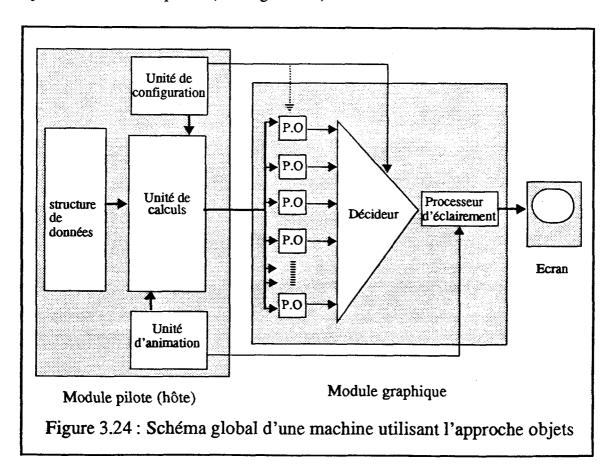

| Notre choix: L'Approche Objets                                               | 94  |

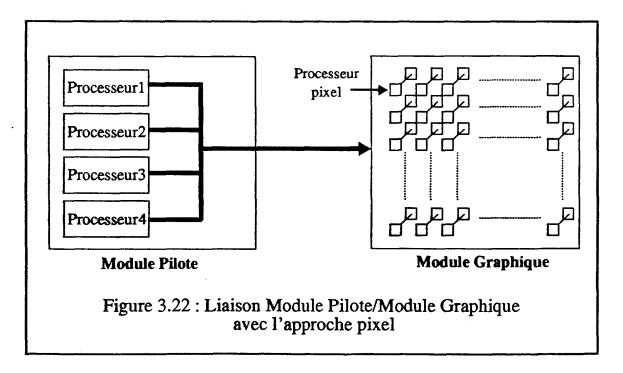

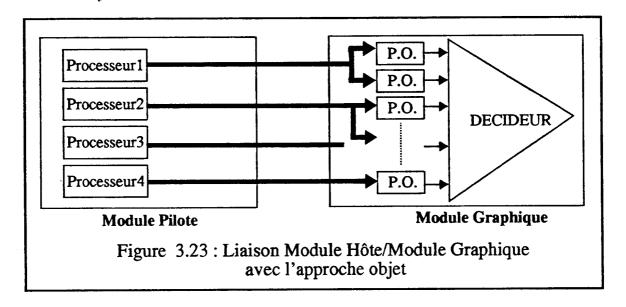

| Le module pilote                                                             |     |

| Le module graphique                                                          |     |

| Conclusion du chapitre                                                       |     |

| IV. I.M.O.G.E.N.E                                                            |     |

| Les Processeurs Elémentaires                                                 |     |

| Introduction                                                                 |     |

| Définition du Processeur Elémentaire                                         | 97  |

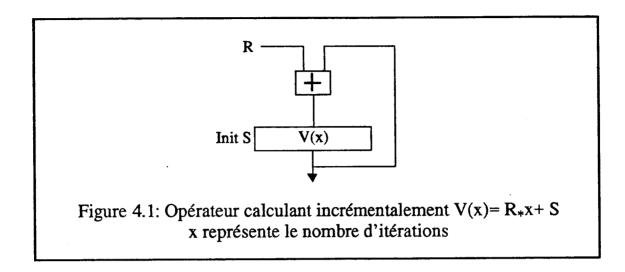

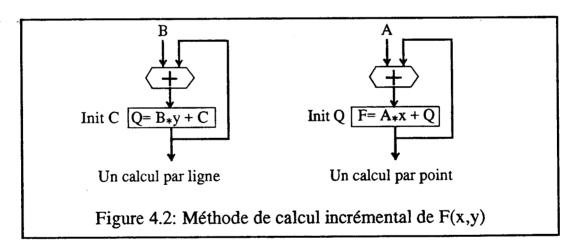

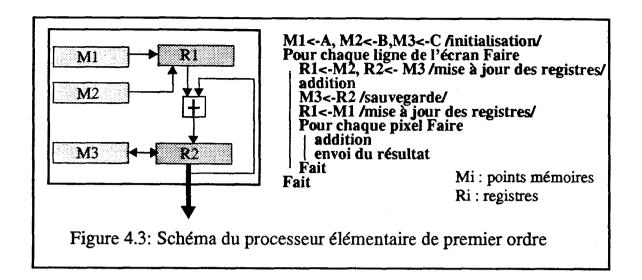

| Le Processeur Elémentaire de premier ordre                                   | 97  |

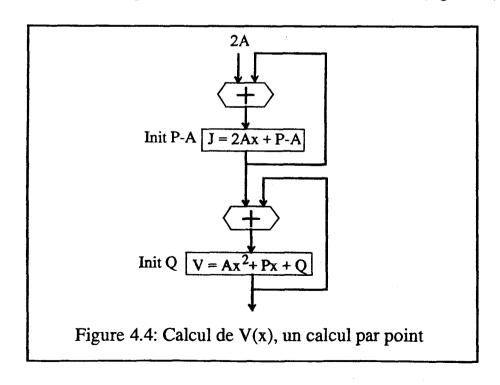

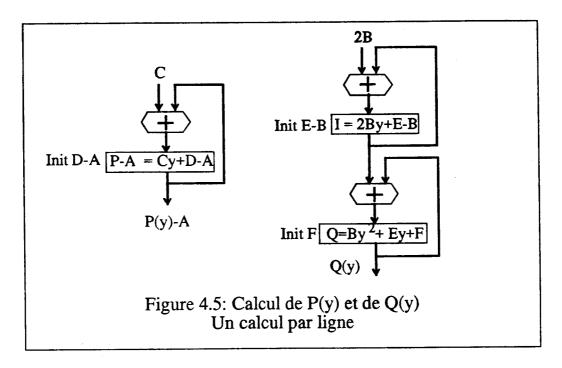

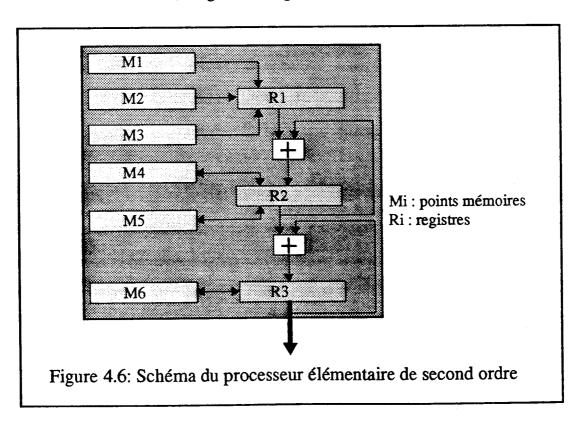

| Le Processeur Elémentaire de second ordre                                    | 99  |

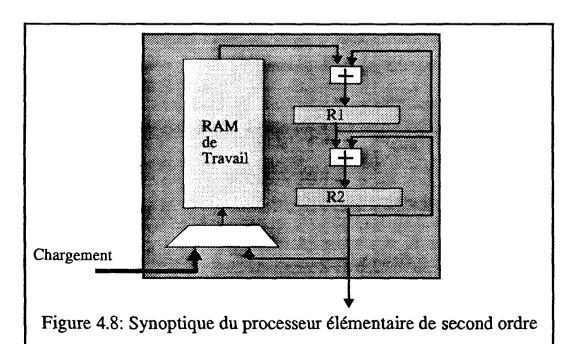

| Solution matérielle                                                          | 101 |

| Choix du nombre de bits                                                      | 102 |

| Le Processeur Elémentaire programmable                                       |     |

| Un autre Processeur Elémentaire                                              |     |

| Réalisation                                                                  |     |

| Les Processeurs Objets                                                       | 106 |

| Définition                                                                   | 106 |

| Le Processeur Facette plane                                                  |     |

| Le processeur Polyèdre                                                       |     |

| Le Processeur Sphère                                                         |     |

| Le Processeur Cylindre                                                       |     |

| Autres Processeurs Objets                                                    |     |

| Réalisation, contraintes physiques                                           |     |

| Le Décideur                                                                  | 115 |

| Présentation                                                                 | 115 |

| Elimination des parties cachées                                              |     |

| Traitement des objets transparents                                           |     |

# **SOMMAIRE**

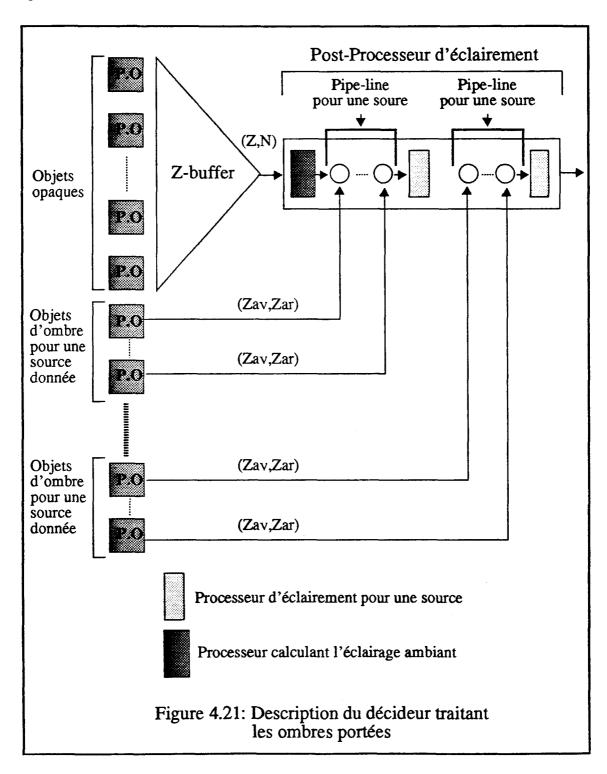

|           | Traitement des ombres portées               | 117 |

|-----------|---------------------------------------------|-----|

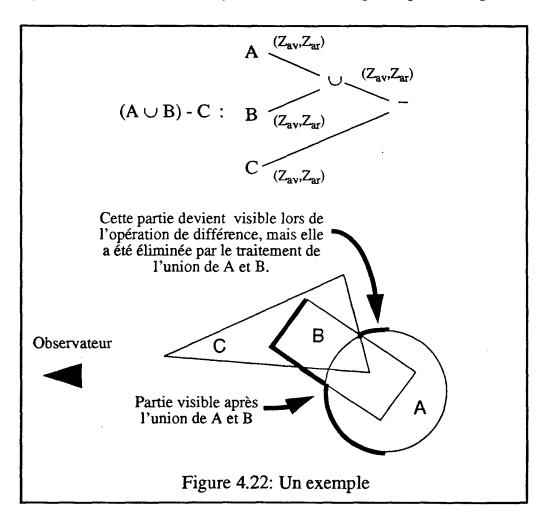

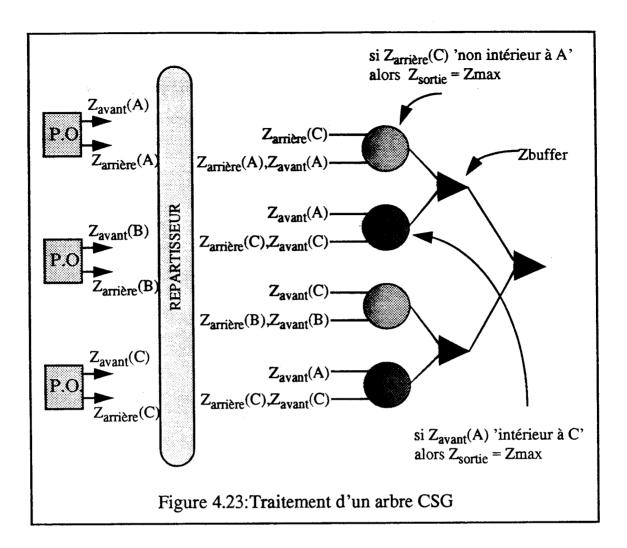

|           | Visualisation directe d'arbre CSG           |     |

|           | Problèmes d'ordre matériel                  |     |

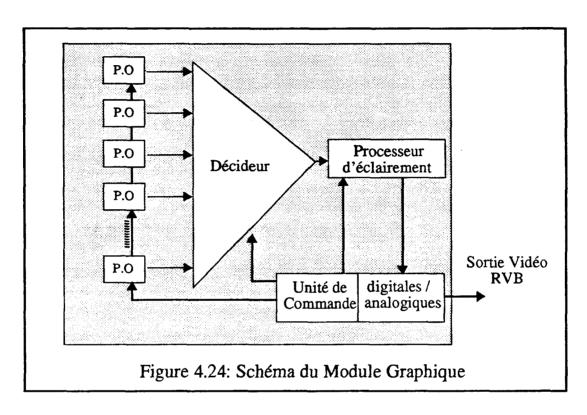

| Le mo     | odule Graphique                             | 122 |

|           | Schéma d'ensemble                           | 122 |

|           | Le Processeur d'Eclairement                 |     |

|           | L'Antialiassage                             |     |

|           | L'Unité de Commande                         | 123 |

|           | La liaison Module Pilote / Module Graphique | 123 |

|           | Schéma d'implantation                       | 124 |

|           | La mémoire de trame                         |     |

|           | Performances                                |     |

|           |                                             |     |

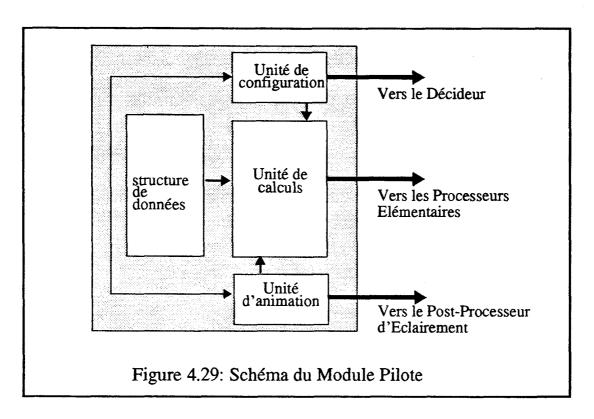

| Le Mo     | odule Pilote                                |     |

|           | Présentation                                |     |

|           | L'unité de configuration                    |     |

|           | L'unité d'animation                         |     |

|           | L'unité de calculs                          |     |

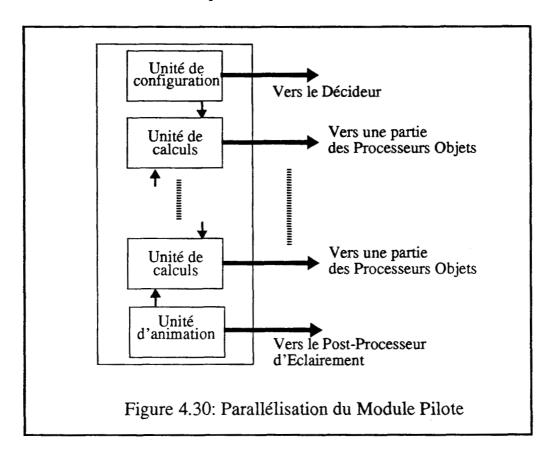

|           | Parallélisation du Module Hôte              | 129 |

|           |                                             |     |

| CONCLUSI  | ION                                         | 130 |

|           |                                             |     |

| V. COMPLI | EMENTS                                      | 132 |

|           |                                             |     |

| Index     | des Machines citées                         | 133 |

| Inday     | des Algorithmes décrits                     | 124 |

| nidex     |                                             |     |

|           | Eclairement                                 |     |

|           | Elimination parties cachées                 |     |

|           | Ombres portées                              | 134 |

|           | Visualisation directe d'arbres C.S.G        | 134 |

| Index     | des mots-clés                               | 135 |

| BIBLI     | IOGRAPHIE                                   | 136 |

|           |                                             |     |

# INTRODUCTION

Ce travail est l'étude de l'architecture d'une machine destinée à afficher des images de synthèse en temps réel. Ce projet se nomme I.M.O.G.E.N.E: Images au Moyen d'Objets Générés par Expressions NumériquEs.

L'énorme volume de calculs nécessaire pour visualiser des images de synthèse incite, depuis déjà longtemps, à réaliser des processeurs (souvent appelés modules graphiques) spécifiques à cette fonction. Les modules graphiques ont fait d'énormes progrès ces dernières années, principalement grâce aux avancées technologiques qui permettent d'augmenter les fréquences, l'intégration et par conséquent les performances.

Actuellement sont définis de nouveau concepts architecturaux pour réaliser des modules graphiques dont les performances devraient dépasser le million de facettes par seconde. La machine I.M.O.G.E.N.E s'inscrit dans ce cadre avec la contrainte stricte suivante: recalculer intégralement l'image à chaque affichage, c'est-à-dire tous les vingt-cinquièmes de seconde pour visualiser des images animées.

Contrairement à ce qu'on pourrait croire, définir des modules graphiques très performants ne permet pas forcément d'obtenir le temps réel. Nous exposons les différentes solutions actuellement étudiées en mettant l'accent sur ces problèmes temporels.

Pour atteindre notre objectif nous proposons de définir un module graphique comprenant un processeur (appelé processeur objet) par primitive graphique. Le parallélisme massif, que nous préconisons, nous impose de faire une étude des algorithmes du processus de visualisation pour déterminer ceux qui autorisent un tel parallélisme. Nous en déduisons une organisation du processus de visualisation adapté à nos contraintes.

Afin de limiter le nombre de processeurs nécessaire pour visualiser une scène et d'augmenter la qualité des images, nous définissons des processeurs objets capables de traiter des primitives plus complexes que les facettes triangulaires utilisées par tous les modules graphiques existants.

Ce document comporte quatre parties:

Un premier chapitre nommé 'Premiers Eléments' délimite le sujet de ce travail et fixe les bases sur lesquelles nous travaillons.

Le second chapitre est une présentation, suivie d'une comparaison des principales machines d'affichage définies ces dernières années pour visualiser efficacement des images de synthèse.

Le troisième chapitre présente une analyse des algorithmes du processus de visualisation. Cette analyse nous conduit à proposer différentes architectures massivement parallèles permettant d'afficher en temps réel.

Le dernier chapitre est une présentation de la machine I.M.O.G.E.N.E.

# I PREMIERS ELEMENTS

L'objet de ce premier chapitre est de délimiter le sujet de ce travail; en particulier nous indiquons quels sont nos objectifs. Le choix de ces objectifs nous impose des limites que nous cernons avec précision. Nous donnons ensuite quelques généralités qui servent de base à cette thèse.

# I.1 Le sujet

# I.1.1 Réaliser un processeur de visualisation d'images de synthèse

Le travail que nous présentons dans cette thèse porte sur la conception d'un module graphique permettant de visualiser des images de synthèse en temps réel. Notre objectif n'est pas de réaliser une machine exploitable commercialemment dans un proche avenir mais de proposer une solution architecturale qui permettra à terme d'afficher des images complexes en temps réel. Les processeurs actuellement commercialisés sont encore très loin d'avoir de telles performances et les concepts qu'ils utilisent ne permettront jamais d'obtenir le temps réel.

De très nombreux travaux sont actuellement faits pour exploiter le parallélisme dans les modules graphiques. L'approche que nous préconisons est d'utiliser un nombre très important de processeurs simples et identiques. Exploiter un parallélisme massif entraine de nouvelles contraintes que nous tentons de répertorier. Envisager un parallélisme massif n'est raisonnable que depuis la commercialisation de logiciel de CAO permettant de définir des circuits intégrés spécifiques à une application.

Définir de nouveaux algorithmes pour le processus de visualisation n'est pas notre but. Nous déterminons parmi les algorithmes existants ceux qui se prêtent à une parallélisation massive et nous en déduisons une nouvelle organisation pour le processus de visualisation.

Notre objectif principal est d'obtenir une machine "temps réel vrai".

# I.1.2 Le temps réel

Nous appelons "temps réel vrai" le fait que l'image soit intégralement redéfinie à chaque affichage, un nouvel affichage étant nécessaire tous les vingt-cinquièmes de seconde pour visualiser des objets animés.

Si nous utilisons un balayage entrelacé (voir I.2.4.2) à une fréquence de 50 Mhz, une image complète est effectivement affichée en un vingt-cinquième de seconde. En utilisant un balayage non entrelacé l'image est affichée cinquante fois par seconde. Le module graphique travaille alors deux fois plus vite. Dans ce travail nous fixons à 25 images par seconde l'animation temps réel. C'est le nombre d'images par seconde utilisé par les caméras. Si le module graphique travaille en non entrelacé, il est possible d'afficher deux fois chaque image.

La solution que nous préconisons est de n'utiliser aucune mémorisation dans le module graphique et de recalculer l'image complète à chaque balayage écran. Cette approche très stricte a les conséquences suivantes:

- La mémoire de trame utilisée par tous les modules graphiques actuels est abandonnée.

- Une solution ne sera choisie que si nous avons la certitude qu'elle pourra afficher des images animées.

Définir l'architecture d'une machine avec la contrainte "temps réel vrai" nous conduit à proposer une structure matérielle originale.

# L2 Le Processus de Visualisation

# I.2.1 Schéma global

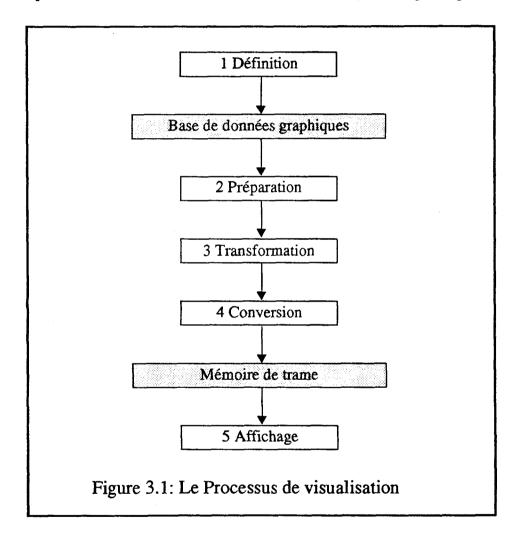

Le processus de visualisation d'images de synthèse peut se découper en cinq parties:

## 1) DEFINITION

Cette partie recouvre la création, la modification ou la suppression d'objets graphiques. Une fois définis, les objets sont placés dans la structure de données graphique.

## 2) PREPARATION

Pour préparer une image, les objets graphiques à afficher sont extraits de la base de données et fournis au(x) processeur(s) qui vont les traiter.

La préparation d'une image recouvre aussi la mise en place des différentes sources lumineuses, des objets et de l'observateur.

## 3) TRANSFORMATION

Les transformations géométriques sont l'ensemble des opérations à appliquer à chaque objet pour permettre sa visualisation. Ces opérations sont au minimum un changement de repère, du repère absolu dans celui de l'observateur, le découpage de l'objet dans le polyèdre de vision et la projection dans le repère écran.

#### 4) CONVERSION

Cette partie réalise la transformation des objets graphiques en pixels (PIcture ELement). En général cela est fait en déterminant les pixels de contour de l'objet et en effectuant un remplissage de la zone délimitée.

Les valeurs ainsi déterminées sont stockées dans une mémoire appelée mémoire de trame.

## 5) AFFICHAGE

L'affichage consiste à envoyer les valeurs calculées en tous les pixels vers l'écran graphique.

De nombreuses tâches essentielles pour la visualisation ne figurent pas dans ce découpage. En effet elles peuvent être effectuées à différents stades du processus. Ces tâches sont, au minimum, l'élimination des parties cachées et les calculs d'éclairement. D'autres opérations inter-objets (traitement des ombres portées, visualisation d'objets partiellement transparents) sont aussi envisageables. Dans le chapitre II nous décrirons comment sont organisées les machines actuellement définies pour implanter de façon performante les cinq parties du processus de visualisation et nous préciserons où sont réalisées les différentes tâches n'apparaissant pas dans notre découpage.

Pour atteindre une animation temps réel les quatre dernières parties du processus de visualisation doivent être réalisables dans le temps imparti à l'affichage d'une trame. L'objet du chapitre III sera de proposer une implantation matérielle du processus de visualisation permettant l'affichage en temps réel.

# I.2.2 Exclusion des méthodes de lancer de rayons et de radiosité

#### I.2.2.1 Le lancer de rayons

Cette méthode a été popularisée au début des années 80 par Whitted [Whitte80][Roth82]. La méthode de lancer de rayons se présente comme suit:

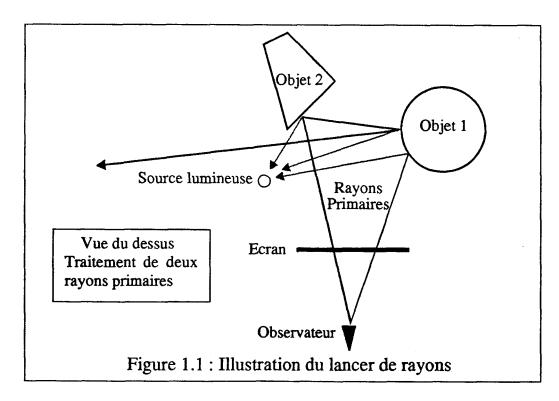

- 1) De l'observateur on envoie un rayon primaire par pixel (voir Figure 1.1). Pour chacun de ces rayons on détermine ses points d'intersection avec tous les objets de la scène, ceci pour trouver l'objet le plus proche de l'observateur. Cette première phase revient à déterminer l'objet visible en chaque pixel c'est-à-dire à éliminer les parties cachées.

- 2) Dans un second temps on envoie de chaque point précédemment calculé plusieurs rayons secondaires:

- Un vers chaque source lumineuse qui, s'il ne rencontre aucun objet jusqu'à celle-ci permet de préciser si l'objet est éclairé par la source. Ces rayons permettent de prendre en compte les ombres portées.

- Un dans la direction symétrique de celle du rayon primaire par rapport à la normale à l'objet pour calculer les réflexions spéculaires. Ces rayons sont placés sur la figure 1.1.

- Eventuellement un dans la direction de réfraction pour les objets transparents.

- 3) On peut poursuivre le suivi des rayons de réflexion et de réfraction pour prendre en compte les objets éclairés indirectement par d'autres objets. Un exemple de rayon de ce type est représenté Figure 1.1.

Les calculs pour afficher une scène, même de complexité raisonnable, sont considérables. Les temps pour une image se comptent en minutes, voire en heures.

#### Chapitre I: Premiers Eléments

Les calculs les plus nombreux sont des calculs d'intersection de droites (les rayons) avec les objets généralement définis par des équations. Pour diminuer le nombre de calculs complexes, on évalue l'intersection des rayons avec des englobants simples des objets (sphères, parallélépipèdes).

De très nombreux travaux sont en cours pour réaliser des machines parallèles de lancer de rayons.

#### I.2.2.2 Paralléliser le lancer de rayon

La plupart des machines parallèles pour le lancer de rayon utilisent le procédé suivant: la scène tridimensionnelle englobant l'ensemble des objets est découpée en plusieurs parties gérées chacune par un processeur. Ces parties sont de taille fixe ou variable pour équilibrer la charge en objets sur les différents processeurs. Au cours du traitement les rayons transitent dans le réseau de processeurs. Chaque processeur traite les rayons atteignant des objets dans sa zone, et envoie les rayons engendrés qu'il ne peut traiter aux processeurs voisins.

Citons quelques machines de ce type:

La machine CM<sup>2</sup> [Cleary86] de l'université de Calgary est constituée d'un réseau matriciel de 10\*10 processeurs Motorola 68000.

La machine Voxar [PitoCD89][CaubDG88] utilise un réseau de Transputers.

Une implémentation d'un algorithme de lancer de rayons est développée sur un Hypercube d'Intel [BouaPr88][Priol89].

Cette parallélisation par découpage de la scène nécessite d'avoir des liaisons entre processeurs ayant des débits considérables pour les tranferts de rayons. Plus le découpage est fin, moins chaque processeur traite d'objets et donc plus les communications entre processeurs sont importantes. Les performances maximales pour ce genre de découpage sont atteintes en utilisant une centaine de processeurs. Le gain en temps est du même ordre de grandeur. Les temps de calcul sont de l'ordre de quelques secondes par image pour les machines que nous avons citées.

L'Equipe de l'I.R.I.S.A propose une autre solution permettant de limiter les transferts entre processeurs, en faisant transiter les objets de la scène et non les rayons. Ils utilisent un mécanisme d'adressage par pages où la mémoire répartie est considérée comme une virtuelle mémoire partagée [BadoPr91].

Le lancer de rayons est une méthode qui permet d'obtenir des images de très bonne qualité au prix d'un grand nombre de calculs. Il n'est pas envisageable d'afficher des images en temps réel avec cette technique dans un avenir proche.

Actuellement des études sont menées pour afficher rapidement, avec cette méthode, en utilisant un processeur par pixel (le Projet RC <sup>2</sup> [AtamML91]).

#### I.2.2.3 Méthodes de radiosité

La technique de radiosité [GoraTG84] considère que toutes les surfaces sont modélisées par de petits polygones plans. Le flux émis en tout point d'un polygone est constant.

On appelle radiosité d'une surface la quantité de lumière quittant cette surface. Elle s'exprime pour un polygone par la formule:

$$Ri = Ei + \rho i * \sum_{j=1}^{N} Fij * Rj$$

[1]

Ei est la quantité de lumière émise par la surface i.

pi le coefficient de réflexion de la surface.

Fij facteur de forme géométrique (fraction du flux émis par le polygone i reçue par le polygone j). Les facteurs de formes sont des intégrales doubles sur les surfaces et sont fonction des angles entre les facettes.

Le calcul d'éclairement pour une scène donnée se fait en deux temps:

- 1) calcul de tous les facteurs de forme. Cohen [CoheGr85] a introduit une méthode permettant de déterminer ces coefficients sans calculer les intégrales.

- 2) résolution du système linéaire formé par les N équations de la forme de l'expression [1], N étant le nombre de facettes de la scène. Ceci pour déterminer les radiosités Ri de chaque surface polygonale.

Pour une scène de N facettes il faut calculer N<sup>2</sup> facteurs de forme et résoudre un système linéaire de N équations à N inconnues. Un tel procédé, bien que parallélisable, n'est pas actuellement utilisable en temps réel.

# I.2.3 Organisation classique des processeurs de visualisation

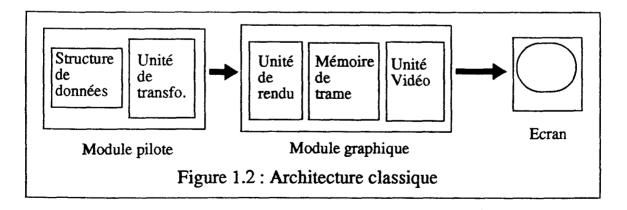

La figure 1.2 représente l'architecture des machines de visualisation actuellement commercialisées [Martin86]:

L'unité de transformation gère la préparation à l'affichage et les transformations géométriques. L'unité de rendu s'occupe de la conversion des objets en pixels et de toutes les opérations de rendu. Le plus souvent les calculs d'éclairement sont effectués par le module pilote, l'unité de rendu faisant de l'interpolation sur ces valeurs exactes.

### Chapitre I: Premiers Eléments

Le module pilote est en général un logiciel sur un processeur d'usage général. Le module graphique est réalisé par automates câblés ou VLSI spécialisés dans les machines les plus performantes.

# I.2.4 L'affichage, les écrans

## I.2.4.1 le principe des écrans TRC

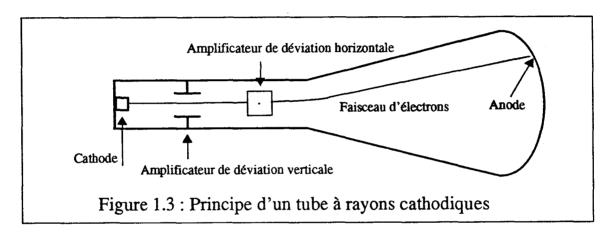

Les écrans TRC, Tubes à Rayons Cathodiques, sont composés d'un écran de luminophores (anode), d'un canon à électrons (cathode) et d'un système de déviation verticale et horizontale des électrons. Les faisceaux envoyés par le canon à électrons excitent les luminophores voulus à l'aide du système de déviation (voir Figure 1.3).

#### 1.2.4.2 Le principe du balayage vidéo

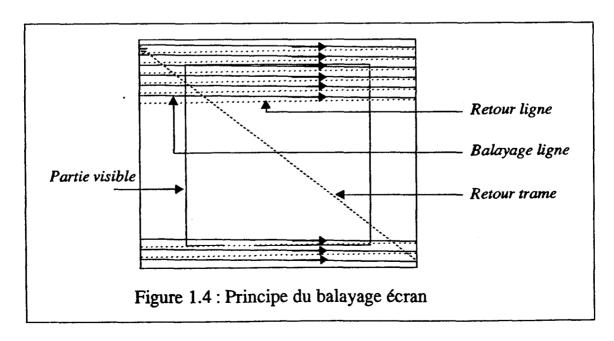

L'écran est balayé en continu ligne par ligne et est rafraîchi systématiquement à une fréquence compatible avec la persistance rétinienne (voir Figure 1.4).

## Chapitre I: Premiers Eléments

Avec une fréquence de 50 Hz et en utilisant une zone visible 512x512, il faut afficher une ligne tous les 38 micro-secondes et donc afficher un point tous les 60 nano-secondes environ. Ces valeurs sont imposées par l'utilisation d'un retour ligne de 7 micro-secondes et d'un retour trame de 600 micro-secondes.

Une solution pour diminuer la fréquence est d'utiliser un balayage entrelacé, c'est à dire qu'à chaque trame seulement une ligne sur deux est traitée. Valoriser totalement l'écran nécessite deux balayages de trame. C'est cette solution qui est utilisée par les écrans de type télévision.

Le tableau 1.1 récapitule les fréquences nécessaires pour des écrans 512x512 et 1024x1024 avec un balayage entrelacé ou non [Degran89].

|           | entrelacé                                                  | non entrelacé                                              |

|-----------|------------------------------------------------------------|------------------------------------------------------------|

| 512x512   | Pixel: 134 ns soit 7,4 MHz<br>Ligne: 75,8 µs soit 13,2 kHz | Pixel: 60 ns soit 16,6 MHz<br>Ligne: 38 µs soit 26,4 kHz   |

| 1024x1024 | Pixel: 30 ns soit 33,1 MHz<br>Ligne: 38 µs soit 26,4 kHz   | Pixel: 11,5 ns soit 85,7 MHz<br>Ligne: 19 µs soit 52,8 kHz |

Tableau 1.1: Fréquence pixel

#### I.2.4.3 Les Autres solutions

Il existe d'autres types d'écrans que les tubes cathodiques. Les principaux sont les systèmes dits à écran plat. Ces écrans sont soit émetteurs comme les écrans à plasma ou à diodes électroluminescentes, soit non-émetteurs comme les écrans à cristaux liquides.

Avec ces solutions il sera possible d'envisager d'autres méthodes d'affichage que le balayage vidéo. Ces écrans ont toutefois de nombreux défauts:

- Il est difficile de réaliser des écrans de grande taille.

- Les coûts sont très élevés.

- · Les couleurs obtenues sont peu satisfaisantes.

Il est donc raisonnable de penser que les tubes cathodiques et le balayage de trame resteront hégémoniques sur le marché des écrans encore au moins une dizaine d'années.

# I.3 Le Parallélisme en synthèse d'images

## I.3.1 Le Parallélisme

Dès que plusieurs processeurs traitent en commun un processus, il y a parallélisme. Cette notion recouvre des organisations très différentes que nous divisons en trois catégories pour un processus P s'éxécutant sur un ensemble de données (di).

## 1) Le Pipe-line

Le processus est divisé en une chaine de sous-processus P1, ... Pn à réaliser séquentiellement. Le flot des données est traité dans une chaine de processeurs M1,... Mn. Chaque processeur Mi exécute le processus Pi. Les données progressent de processeur en processeur en cours de traitement.

Cette solution n'est envisageable que si le processus initial se divise bien en un sous ensemble de processus dont les temps de traitement sont voisins. Le rythme de progression est imposé par le processeur le plus lent. Des mémoires tampons peuvent être intercalées entre les processeurs pour compenser ponctuellement les différences de vitesses d'éxécution.

#### 2) Le Parallélisme sur les données

Le processus P est intégralement implanté sur un ensemble de processeurs Mi. Les données à traiter sont réparties sur les différents processeurs. Il est alors indispensable d'utiliser un mécanisme de répartition des données aux processeurs.

Cette solution devient difficilement utilisable si les traitements des données ne sont pas disjoints, c'est-à-dire nécessitent des communications et des synchronisations entre processeurs.

## 3) La Parallélisation du processus

Le processus P est divisé en un ensemble de sous-processus fonctionnant en parallèle sur différents processeurs. Cette technique de parallélisation est délicate à mettre en oeuvre car elle remet en cause la structure séquentielle des algorithmes. De plus elle nécessite des liens de communication entre tous les processeurs, ceci pose d'énormes problèmes matériels quand le nombre de processeurs devient grand.

Cette solution de parallélisation est intéressante quand le traitement d'une donnée par le processus est très long.

## I.3.2 Parallélisme et Processus de Visualisation

Analyser les parallélismes exploités par une implantation donnée du processus de visualisation est fort difficile. Les raisons en sont multiples, les principales sont:

• Les données sont de deux types, les objets graphiques et les pixels de l'écran.

Le processus de visualisation est composé de nombreux sous-processus que nous avons choisis de regrouper en cinq phases dans le paragraphe I.2.1. Les différentes phases n'offrent pas les mêmes possibilités de parallélisation. De plus, pour chacune de ces phases du processus de visualisation, de nombreux algorithmes existent, certains aisément

#### Chapitre I: Premiers Eléments

parallélisables, d'autres absolument pas.

Nous classons en quatre catégories les différentes propositions de parallélisation du processus de visualisation.

## 1) Le pipe-line objets

Le processus est implanté en un pipe-line de processeurs dans lequel progressent les objets graphiques.

## 2) Le parallélisme objets

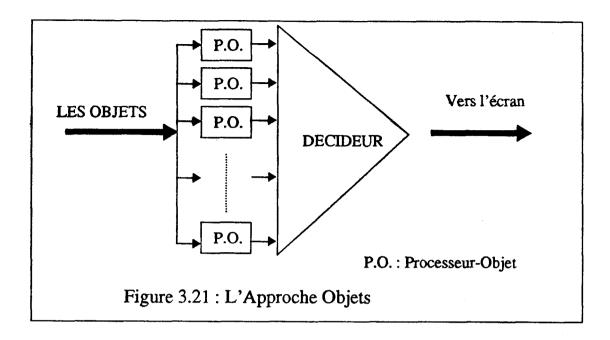

Le processus est implanté totalement sur un ensemble de processeurs traitant chacun une partie des objets.

#### 3) Le pipe-line pixels

Le processus est implanté en un pipe-line de processeurs dans lequel progressent les pixels.

## 4) Le parallélisme pixels

Le processus est implanté complétement sur un ensemble de processeurs qui traitent chacun une partie de l'écran.

C'est à partir de cette classification que nous allons construire notre travail d'analyse.

Il est malheureusement impossible de classer directement les propositions pour l'intégralité du processus de visualisation avec les catégories que nous venons d'établir. Toute solution utilise plusieurs de ces parallélismes à différentes phases du processus de visualisation. Dans l'analyse, il faudra être précis sur la partie du processus de visualisation qui est parallélisée.

Un autre critère important pour analyser le parallélisme dans le processus de visualisation est l'ordre de grandeur du parallélisme. Celui-ci recouvre aussi bien une machine bi-processeurs qu'une machine comprenant un millier de processeurs.

Nous n'avons pas fait figurer dans cette classification la "parallélisation du processus". En effet l'utilisation du parallélisme en synthèse d'image s'impose non parce que l'exécution du processus pour une donnée est trop complexe, mais parce que le nombre de données à traiter est considérable. Un scène peut contenir plus de 10 000 objets graphiques, un écran 1000\*1000 contient un million de pixels.

Il existe bien évidemment des algorithmes de rendu se prêtant à une "parallélisation du processus", par exemple l'algorithme d'élimination des parties cachées de Warnock (présenté au paragraphe III.1.1.1.1). Dans cet algorithme, l'angle d'étude n'est ni orienté pixels ni orienté objets mais repose sur un découpage récursif du volume englobant la scène à visualiser, ce qui impose de considérer que la donnée est une seule entité comprenant l'ensemble des objets. Une implémentation parallèle de cet algorithme serait à classer dans la catégorie: "Parallélisation du processus".

Toutes les propositions de réalisations matérielles utilisent des algorithmes exploitant des parallélismes ou effets pipe-line sur les objets ou sur les pixels, la parallélisation du processus n'est alors qu'une conséquence. Nous reviendrons en détail sur ce problème dans le chapitre III.

## I.3.3 Vocabulaire

#### I.3.3.1 Granularité

Le degré de parallélisme, parfois appelé granularité, des machines peut être classé en trois catégories:

- Faible si le nombre de processeurs est inférieur à une cinquantaine.

- Moyen si le nombre de processeurs est compris entre cinquante et deux cent.

- Massif si le nombre de processeurs est supérieur à deux cent.

## **1.3.3.2 SIMD, MIMD**

Les organisations parallèles sont caractérisées comme SIMD ou MIMD [Flynn72].

SIMD Single Instruction stream, Multiple Data stream : ce sont des machines ayant plusieurs unités de traitement contrôlés par la même unité de commande. Les différentes unités exécutent le même flot d'instructions au même rythme sur des données distinctes.

MIMD Multiple Instruction stream, Multiple Data stream : les différentes unités de traitement possèdent chacune une unité de commande. Les différentes unités peuvent traiter des flots d'instructions distincts sur des données distinctes.

### I.3.3.3 Efficacité, Accélération

Un processeur donné met un temps t pour effectuer une tâche. Si N processeur mettent un temps t' pour réaliser la même tâche on peut définir l'efficacité et l'accélération comme suit:

Efficacité =

$$t/(t'*N)$$

Accélération = N \* Efficacité = t / t'

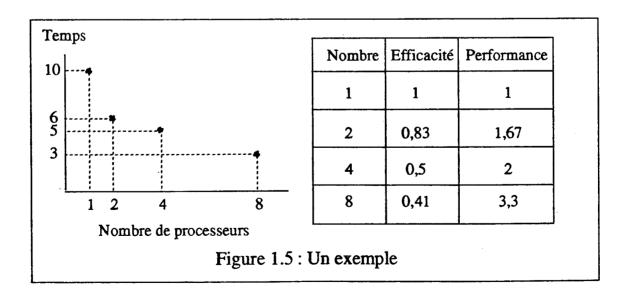

Illustrons ce vocabulaire sur un exemple (voir Figure 1.5)

Sur cet exemple l'efficacité diminue quand le nombre de processeurs croît, toutefois

les Accélérations augmentent.

Pour obtenir une machine d'affichage temps réel, seule l'Accélération est à prendre en compte, l'Efficacité n'est pas, dans ce cas, un critère essentiel.

Pour évaluer a priori l'Efficacité et les Accélérations des algorithmes et des machines d'affichage nous allons exprimer l'Efficacité comme le produit de deux valeurs qu'il est possible d'estimer de façon théorique.

Efficacité = Rendement \* Ratio-coopération

Le Rendement est le quotient du nombre d'opérations utiles sur le nombre total d'opérations.

Le Ratio-coopération est le rapport du temps de travail effectif sur le temps total d'exécution, c'est à dire en ajoutant les temps de communication entre processeurs, le temps d'attente et le temps passé à des tâches n'existant pas avec un processeur unique mais qui s'imposent en utilisant plusieurs processeurs.

Illustrons ces notions sur deux exemples.

#### Exemple 1:

Un processeur élémentaire de tracé de segment traite un pixel toutes les 10 ns. Pour augmenter la vitesse de traitement on utilise une matrice de 16 processeurs pour traiter des blocs de 4\*4 pixels.

Un préprocesseur détermine les blocs 4\*4 de la mémoire d'image à traiter pour un segment donné. Il met 5 ns pour choisir un bloc. Il n'y a aucune communication entre les différents processeurs élémentaires. Le temps total de traitement pour un bloc de 16 pixels est de 10+5 = 15 ns.

Le Ratio-coopération est donc sur cet exemple de 10 / 15.

On peut par ailleurs estimer que sur un bloc carré de 16 pixels, en moyenne 6 appartiennent au segment à tracer. Le Rendement est donc de 6 / 16.

Efficacité =

$$\frac{10}{15}$$

\*  $\frac{6}{16}$  = 0,25

L'Accélération de cette machine utilisant 16 processeurs en parallèle est donc de 4.

#### Exemple 2:

Exprimons avec le vocabulaire que nous venons de définir les résultats sur les machines parallèles de lancer de rayons par division de la scène tridimentionnelle.

Pour ces machines le Rendement est égal à 1, toutes les opérations effectuées sont utiles. Par contre le Ratio-coopération diminue extrêmement vite quand le découpage devient fin. Chaque rayon transite par de plus en plus de processeurs avant de rencontrer un objet. Ceci à tel point que l'Accélération décroit à partir d'un certain nombre de processeurs.

# II PRESENTATION ANALYTIQUE DES MACHINES DE RENDU

Nous présentons dans ce chapitre différentes machines conçues pour visualiser des images de synthèse. Nous dressons ensuite des tableaux permettant d'analyser et de comparer ces machines. Parallélement à ces tableaux, nous mettons en évidence certaines contraintes qui nous permettent de mieux cerner les solutions envisageables pour définir un module d'affichage temps réel.

# **II.1 Les Machines**

Le plan que nous allons suivre maintenant pour décrire chacune des machines est le suivant:

- i) Une description globale de l'architecture de la machine illustrée par un schèma. On précisera les algorithmes utilisables par cette machine. On insistera sur la méthode utilisée pour générer les pixels.

- ii) Une analyse des formes de parallélisme utilisées en reprenant la terminologie définie dans le premier chapitre. On mettra l'accent sur le degré de parallélisme utilisé.

- iii) Des précisions sur les éventuels circuits intégrés utilisés.

- iv) Un résumé des principales caractéristiques et une mise en évidence de l'originalité de la proposition.

Nous allons présenter 12 machines qui sont représentatives des différentes solutions architecturales envisagées à ce jour. Nous pouvons regrouper ces machines en 4 classes:

- A) les processeurs dédiés réalisés en VLSI

- 1 Geometry System

- 2 Le circuit intégré PRC

- 3 Le circuit intégré SAGE

- B) les machines commerciales de haut de gamme

- 4 La Silicon Graphics 4D/240GTX

- 5 La Stellar GS1000

- 6 Autres machines

- C) les machines utilisant des processeurs généraux en parallèle

- 7 La Pixel Machine

- 8 CAP

- D) les machines prototypes

- 9 Experts

- 10 La machine de Torborg

- 11 La machine GSP-NVS

- 12 Pixel-Planes 4

- 13 Pixel-Planes 5

Tous les algorithmes cités dans ce chapitre, généralement sous le nom de leur concepteur, seront développés dans les chapitres suivants. Une liste de ces algorithmes figure à la fin de ce document avec les références bibliographiques et le numéro du paragraphe où ils sont explicités.

# **II.1.1 Geometry System**

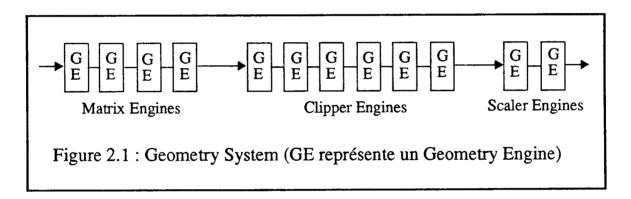

Le circuit intégré "Geometry Engine" [Clark82] a été développé pour accélérer la phase de transformation du processus de visualisation.

Ce circuit intégré effectue des calculs flottants en parallèle sur les 4 composantes d'un segment (ou vecteur) en coordonnées homogènes. Clark appelle "Geometry System" (voir Figure 2.1) un pipe-line de 12 circuits intégrés "Geometry Engine" qui effectue l'ensemble des transformations indispensables pour chaque segment. Les tâches sont découpées comme suit:

- Les 4 premiers circuits intégrés "Matrix Engines" réalisent le changement de repère du repère de la scène dans celui de l'observateur par calculs matriciels.

- Les 6 suivants "Clipper Engines" effectuent le découpage des segments dans le polyèdre de vision. Un circuit intégré réalise le découpage pour un coté du polyèdre.

- Les deux derniers "Scaler Engines" effectuent la projection dans le repère deux dimensions de l'écran.

Les parallélismes utilisés par cette machine sont les suivants:

- i) Un parallélisme objets de très bas niveau, les 4 coordonnées d'un segment sont traitées en parallèle.

- ii) Un pipe-line objets de 12 étages en utilisant plusieurs circuits intégrés pour effectuer la totalité des opérations de transformation.

Le circuit intégré "Geometry Engine" est un circuit ayant 40 broches, composé de 4 blocs identiques traitant chacun une composante.

Ce circuit intégré est la seule proposition que nous étudierons s'intéressant à la partie transformation du processus de visualisation. Il permet d'obtenir de bonnes performances: 100000 segments traités par seconde pour un circuit intégré et 4 fois plus en utilisant le pipeline de 12 circuits intégrés. Il est actuellement utilisé sur certaines stations graphiques, par exemple la station IRIS de Silicon Graphics. Vue la rapide augmentation des performances des processeurs généraux de calculs (processeur de signal, processeur vectoriel), les circuits intégrés de ce type deviendront rapidement obsolètes.

# II.1.2 Le circuit intégré PRC

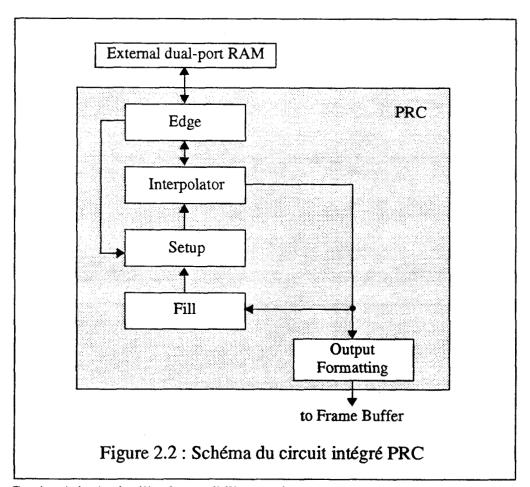

PRC (Polygon Rendering Chip) [SwanTh86] est un circuit permettant d'afficher rapidement des polygones 3D avec ombrage.

Les entrées de ce circuit intégré sont les valeurs X, Y, Z, R, V et B en tous les sommets du polygone à visualiser. A partir de ces valeurs le circuit intégré fournit en chaque pixel où le polygone est présent, la profondeur de celui-ci et les valeurs R, V et B à afficher. Ces calculs sont faits par interpolations linéaires sur les six variables. Cela revient pour l'ombrage à utiliser la méthode de Gouraud.

Ce circuit intégré est composé de 4 unités fonctionnant en pipe-line (voir Figure 2.2):

- L'unité "Edge" qui détermine les extrémités des segments horizontaux composant le polygone.

- L'unité "Setup" qui calcule les paramètres d'interpolations.

- L'unité "Interpolator" qui effectue tous les calculs d'interpolations. L'unité "Fill" qui génère tous les pixels.

Ce circuit intégré utilise le parallélisme suivant:

Un pipe-line objets entre les différents segments horizontaux d'un objet.

Ce processeur est composé de 150.000 transistors environ et travaille à la fréquence de 20 Mhz. Il est implanté dans les stations de CAO Hewlett-Packard.

Ce circuit intégré utilise peu le parallélisme, mais son organisation interne et sa réalisation VLSI lui permettent de génèrer les pixels au rythme d'un toutes les 50 ns. Il met environ 90 microsecondes pour engendrer un triangle de surface 1.000 pixels.

Il serait tout à fait possible de faire travailler plusieurs de ces circuits intégrés en parallèle. La vitesse serait multipliée par le nombre de circuits intégrés. Mais se produiraient des problèmes de conflit d'accès à la mémoire de trame.

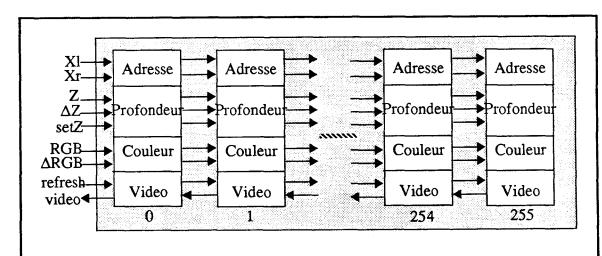

# II.1.3 Le circuit intégré SAGE

SAGE [GharGH88] est un circuit intégré CMOS contenant un million de transistors implémentant un pipe-line de 256 processeurs élémentaires "Pixel Processor" gérant chacun un pixel (voir Figure 2.3). Un circuit intégré s'occupe d'une partie d'une ligne écran.

Chaque 'Pixel Processor' incrémente linéairement des valeurs X, Z, R, G et B, ce qui permet de tracer des segments horizontaux en trois dimensions et d'effectuer un ombrage suivant la méthode de Gouraud. De plus ces processeurs effectuent l'élimination des parties cachées en utilisant un Z-buffer par ligne.

Figure 2.3 : Schéma des 256 "pixel processors" du circuit intégré SAGE

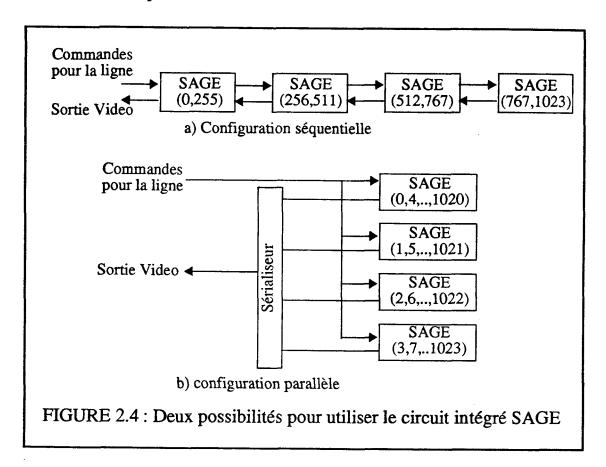

Les concepteurs de ce circuit intégré proposent d'en utiliser 4 pour réaliser une unité complète de génération des pixels. Deux configurations sont alors envisageables: les utiliser en série ou en parallèle (voir Figure 2.4).

4 circuits intégrés SAGE peuvent traiter 256 segments horizontaux au rythme du balayage écran pour un écran 1024\*1024 en configuration parallèle. S'il y a davantage de segments sur une des lignes, il est indispensable d'utiliser une mémoire de trame.

Pour visualiser des faces planes 3D, on utilise 6 processeurs d'interpolation verticale qui calculent les valeurs XI, Xr, Z, R, G et B pour chacun des segments horizontaux de chaque face afin d'alimenter les circuits intégrés SAGE pour exploiter au maximum leurs possibilités. La mémoire interne de ces processeurs d'interpolation est de 512 polygones.

Ces circuits intégrés permettent d'utiliser les parallélismes suivants:

- i) Un pipe-line objets de 256 étages pour générer les pixels des segments horizontaux, effectuer l'élimination des parties cachées et calculer l'ombrage.

- ii) Un parallélisme pixels entre les pixels des différents circuits intégrés quand ceuxci sont utilisés en parallèle.

- iii) L'utilisation de tels circuits intégrés permet une parallélisation des opérations situées au niveau du pixel.

Pour des scènes comprenant un grand nombre d'objets il n'est pas évident que les processeurs d'interpolation verticale puissent alimenter les circuits intégrés SAGE en les exploitant au maximum.

Le principal intérêt de cette réalisation est la très importante intégration en VLSI qui permet de générer les pixels à une vitesse remarquable. Pour des segments horizontaux de longueur moyenne 40 bits, le temps pour traiter un objet en un pixel est de 1 ns.

Les concepteurs de ce circuit intégré pensent pouvoir afficher 1 000 000 de polygones de 1000 pixels de surface avec ombrage de Gouraud et Z-buffer par seconde en utilisant la configuration 4 circuits intégrés en parallèle.

# II.1.4 La machine Silicon Graphics 4D/240GTX

Cette machine [Akeley89][AkelJe88] est l'une des plus performantes actuellement commercialisée.

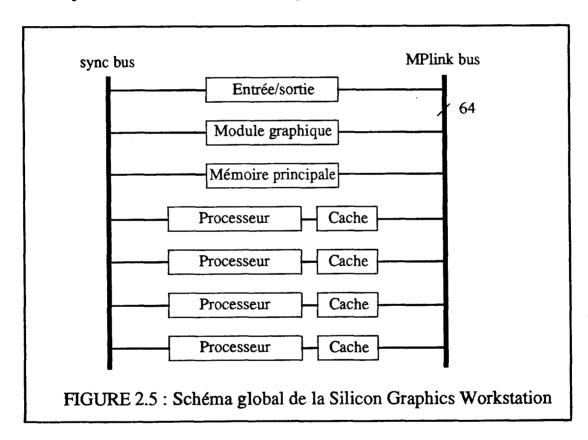

Elle est composée d'une mémoire centrale, d'un module graphique, d'un module d'entrées/sorties et de 4 processeurs (voir Figure 2.5) reliés entre eux par deux bus, "Sync bus" et "MPlink bus".

Le "Sync bus" permet de synchroniser les 4 processeurs pour les utiliser au mieux en parallèle par adressage direct dans les mémoires des processeurs. Le "MPlink bus" supporte les transferts de données entre les 4 processeurs, le module graphique, la mémoire et les entrées/sorties. Des caches sont utilisés pour optimiser l'utilisation de ce bus.

Chaque processeur est composé d'une unité centrale RISC, d'un coprocesseur de calculs flottants, d'une mémoire et de caches. Ces unités sont reliées entre elles par un bus interne au processeur. L'unité centrale est un processeur 32 bits à 25 MHz.

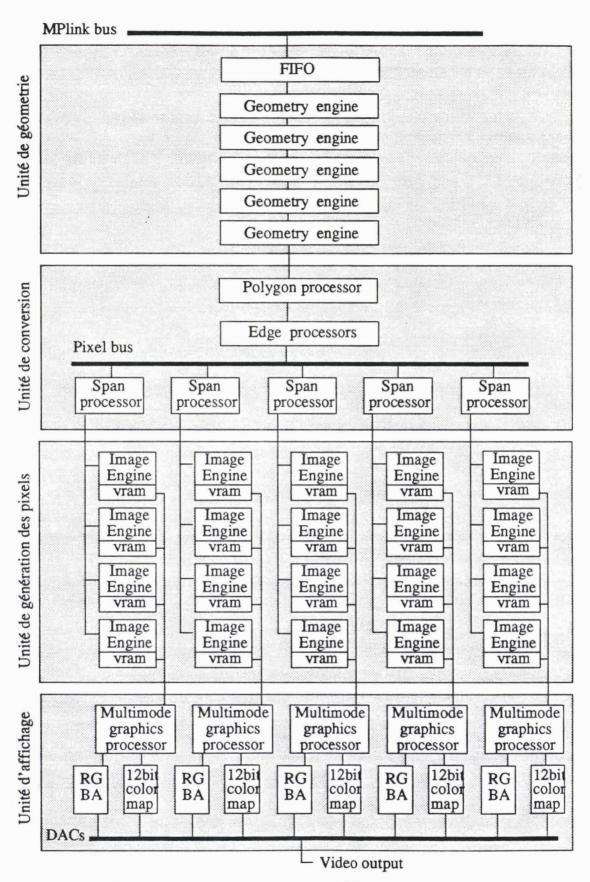

Le module graphique de la Silicon Graphics Workstation est composé de quatre unités différentes fonctionnant en pipe-line (voir Figure 2.6):

• Une unité de géométrie.

Les calculs géométriques sur les sommets des polygones sont effectués en coordonnées homogènes par cinq composants "Geometry Engine".

Une unité de conversion.

Cette unité décompose en plusieurs étapes les polygones en segments verticaux

(spans). Le "Polygon processor" décompose les polygones en trapèzes et triangles. Ensuite le "Edge processor" est un interpolateur qui détermine les sommets des différents segments verticaux composant chaque trapèze. Les cinq "Span processors" générent l'ensemble des pixels pour chaque segment vertical.

• Une unité de génération des pixels.

La génération des pixels dans la mémoire de trame est réalisée par 20 processeurs "Image Engine" gérant chacun un vingtième de la mémoire de trame. Ces processeurs éliminent les parties cachées en utilisant l'algorithme du Z-buffer. Ils peuvent aussi faire une combinaison linéaire de la couleur présente avec la nouvelle, ce qui permet de traiter les transparences en profondeur.

• Une unité d'affichage.

Cette unité composée de 5 "multimode graphics processors" affiche les informations fournies par le module de génération via une table de fausses couleurs.

L'éclairement est réalisé en utilisant la méthode d'interpolation de Gouraud.

Cette machine exploite de nombreux parallélismes:

- i) Un pipe-line objets pour les 4 unités du module graphique.

- ii) Un parallélisme pixels, les pixels étant traités en parallèle par les 20 "Image Engines" de l'unité de génération des pixels.

- iii) Il y a donc parallélisation du remplissage des objets et des opérations situées au niveau du pixel (par exemple l'élimination des parties cachées).

- iv) Un parallélisme algorithmique entre la génération des objets et la préparation à la visualisation d'une scène en utilisant les 4 processeurs RISC.

L'intégralité du module graphique est réalisé matériellement, et comprend en particulier 5 circuits intégrés Geometry Engine décrits précédemment. Le bus qui relie les 4 processeurs au module graphique détermine la capacité globale de la machine.

La principale caractéristique de cette machine est d'exploiter au mieux les possibilités de parallélisation qu'offrent le processus de visualisation tout en utilisant un processeur dédié d'une complexité matérielle raisonnable.

Les performances de cette machine sont les suivantes:

- 400000 segments de 10 pixels de long par seconde.

- 137000 triangles de surface moyenne 50 pixels avec ombrage de Gouraud et Z-buffer par seconde.

- 100000 polygones de surface moyenne 100 pixels avec ombrage de Gouraud et Zbuffer par seconde.

Les performances de cette machine reflètent non seulement celles de l'unité de rendu mais aussi celles du calcul des transformations géométriques.

Figure 2.6 : Le module graphique de la Silicon Graphics Workstation

## II.1.5 La machine Stellar GS1000

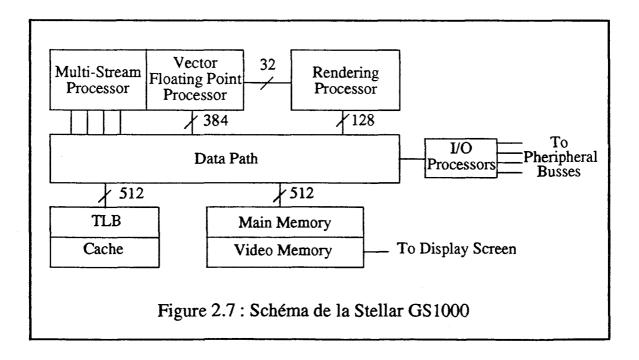

Cette machine [ApgaBM89] a pour coeur un réseau de connexions "Data Path" très performant reliant entre elles les différentes unités de la machine.

Les principales unités de cette architecture sont les suivantes (voir Figure 2.7):

- Un processeur "Multi-Stream Processor" qui exécute simultanément 4 flots indépendants d'instructions. Ce processeur est le module pilote de cette machine.

- Un processeur vectoriel de calcul "Vector Floating Point Processor", relié au réseau de connexions par un bus 512 bits, sur lequel sont exécutées les transformations géométriques. Ce processeur alimente directement par une liaison 32 bits le processeur de rendu.

- Des mémoires de 3 types: une mémoire cache avec une unité TLB "Translation Lookaside Buffer" qui permet aux processeurs de travailler avec des adresses virtuelles, une mémoire principale où est stockée la base de données images et une mémoire vidéo. La mémoire vidéo est directement reliée à l'écran TRC. Elle est organisée en blocs de 16 pixels pour augmenter la vitesse d'accès. Les mémoires principale et vidéo se partagent un bus de 512 bits pour accèder au réseau de connexions.

- Un processeur de rendu "Rendering Processor" qui pour chaque objet graphique génère les pixels le composant. Il réalise en particulier les calculs d'éclairement et de profondeur pour éliminer les parties cachées avec l'algorithme du Z-buffer. Les objets visualisables par ce processeur sont les segments, les triangles 3D et les sphères.

Les logiciels développés sur cette machine permettent d'utiliser pour l'éclairement les méthodes d'interpolation de Gouraud et de Phong (approximation de Bishop et Weiner) avec réflexions diffuse et spéculaire. Les sources lumineuses peuvent être à l'infini ou ponctuelles à distance finie.

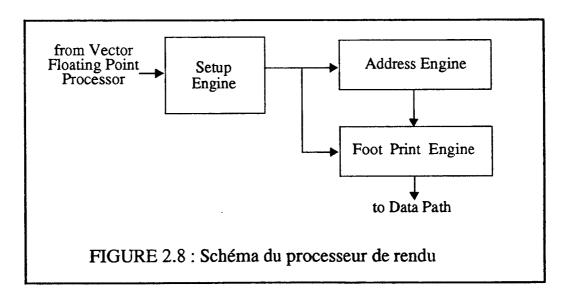

Le processeur de rendu de la machine est composé de trois unités fonctionnant en pipe-line (voir Figure 2.8) :

- 1) Une unité de préparation "Setup Engine" qui détermine les bornes et les coefficients des expressions qui sont utilisés pour faire le rendu. Elle fournit ces valeurs aux deux autres unités.

- 2) Une unité d'adressage qui détermine les blocs de 4\*4 pixels de la mémoire vidéo ayant une intersection avec l'objet en cours de traitement et fournit leur adresse virtuelle à l'unité de génération.

Les deux unités que nous venons de décrire sont réalisées autour d'un circuit intégré microprogrammé "Setup-Address" comprenant, comme éléments principaux, une ALU 32 bits et un multiplieur 16 bits. Ce circuit est un boîtier ayant 299 broches et environ 40000 portes logiques.

3) Une unité de génération "Foot Print Engine" qui traite les 16 pixels d'un bloc en parallèle. Elle est composée de 16 circuits intégrés "Toes" traitant chacun un pixel. Chacun de ces circuits contient une ALU 32 bits et un multiplieur de deux nombres 16 bits. Un accumulateur permet de réaliser des produits 32\*32 bits. Ce circuit est un boîtier contenant 25000 portes et ayant 155 broches.

A chaque cycle, cette unité de génération calcule en tout pixel du bloc 4\*4 la profondeur et l'attribut à afficher, acquiert via le réseau de connexions le contenu de la mémoire vidéo pour ce bloc, élimine les parties cachées et replace les valeurs dans la mémoire.

Les parallélismes exploités par cette solution architecturale sont les suivants:

- i) Un parallélisme pixels, avec l'utilisation de 16 circuits intégrés "Toes" en parallèle.

- ii) Un pipe line objets de quelques étages entre le processeur vectoriel et les trois unités du processeur de rendu.

- iii) Cette architecture a pour caractéristique de paralléliser toutes les opérations

situées au niveau du pixel, c'est-à-dire pour cette machine les calculs de profondeur et d'éclairement ainsi que l'élimination des parties cachées.

iv) Un parallélisme objets faible en utilisant un processeur multi-flots.

Cette machine utilise dans son module de rendu 18 circuits intégrés: 2 circuits intégrés "Setup-Address" et 16 circuits intégrés "Toes" que nous avons décrits précédemment. C'est cependant toujours cette unité qui est la plus lente de la machine.

La principale caractéristique de cette machine est d'obtenir d'excellentes performances tout en proposant de nombreuses possibilités pour les objets élémentaires directement visualisables (segments, triangles 3D et sphères) et pour les modèles d'éclairement. Ceci est rendu possible par le fait que le processeur de rendu de cette machine est partiellement programmable et que les processeurs travaillant sur chaque pixel peuvent faire des calculs assez complexes, par exemple des multiplications. Par ailleurs, la mémoire vidéo n'est pas liée au processeur de rendu, ce qui permet une utilisation plus souple. Il est par exemple possible d'effectuer un post-traitement sur l'image dans la mémoire de trame.

Les performances (en nombre de triangles par seconde) du logiciel effectuant les calculs de transformations sur le processeur multi-flots et le processeur vectoriel sont les suivantes:

- 143000 triangles de surface moyenne 100 pixels avec ombrage de Gouraud et Z-buffer pour une source lumineuse en utilisant une table de fausses couleurs. (134000 avec deux sources et 120000 avec trois sources)

- 40000 triangles de surface moyenne 100 pixels avec ombrage de Phong et Z-buffer pour une source lumineuse en prenant en compte l'éclairement diffus avec une table de fausses couleurs.

- 25000 triangles de surface moyenne 100 pixels avec ombrage de Phong et Z-buffer pour une source lumineuse en prenant en compte l'éclairement spéculaire et en utilisant une table de fausses couleurs.

Les performances (en nombre de triangles par seconde) du processeur de rendu sont:

- 155000 triangles de surface moyenne 100 pixels avec ombrage de Gouraud et Z-buffer en utilisant une table de fausses couleurs

- 100000 triangles de surface moyenne 100 pixels avec ombrage de Gouraud et Z-buffer en utilisant de vraies couleurs.

- 40000 triangles de surface moyenne 100 pixels avec ombrage de Phong et Z-buffer pour une source lumineuse en utilisant une table de fausses couleurs.

#### **II.1.6** Autres machines commerciales

Il existe bien évidemment d'autres machines de haut de gamme ayant des performances du même ordre de grandeur que celles des deux machines présentées. Citons par exemple les SRX de Hewlett Packard, la DN10000 du constructeur Apollo [KirkVo90][Voorhi89] ou Titan de Ardent [Borden89].

Cette dernière a pour particularité de n'utiliser aucun processeur dédié réalisé en VLSI afin d'être le plus souple possible d'utilisation. Elle utilise en parallèle des processeurs

comprenant un CPU RISC et un processeur vectoriel sur lequel sont réalisées en pipe-line les transformations et la conversion des objets en pixels. Le pipe-line doit être réparti sur les différents processeurs en fonction du nombre de processeurs disponibles, ce qui est une tâche difficile à réaliser efficacement. Cette machine a par ailleurs les mêmes défauts que les machines réalisées matériellement: si un étage du pipe-line nécessite beaucoup de temps, il ralentit tout le processus. Pour afficher à des vitesses importantes, un accélérateur graphique, faisant la conversion des objets en pixels, est ajouté à la machine. Cet accélérateur est alors considéré comme l'un des processeurs fonctionnant en parallèle.

#### II.1.7 La Pixel Machine

Cette machine [PotmHo89][PotmMH89] a pour caractéristique principale de posséder une unité graphique sans aucun processeur spécialisé, mais est composée de processeurs de signaux utilisés en parallèle.

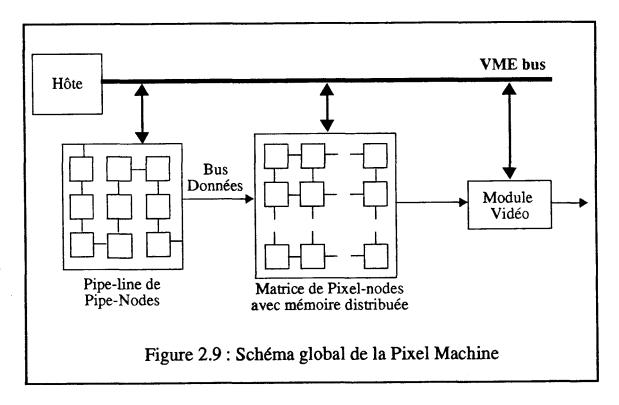

L'unité graphique de la Pixel Machine est composée de trois blocs (voir Figure 2.9) :

• Un (ou deux) pipe-line de 9 'Pipe-Nodes' calculant les transformations sur les objets graphiques (calcul matriciel, découpage dans le polyèdre de vision, projection...).

Chaque 'Pipe-Node' du pipe-line est composé d'une liste d'attente, d'une mémoire statique et d'un processeur de signal DSP32. Il reçoit les objets graphiques de son prédecesseur dans le pipe-line et les envoie à son successeur après traitement. Le dernier processeur du pipe-line alimente la matrice de 'Pixel-Nodes' via le bus de données.

• Une matrice comprenant de 16 à 64 processeurs "Pixel-Nodes" travaillant chacun sur une fraction de la mémoire de trame.

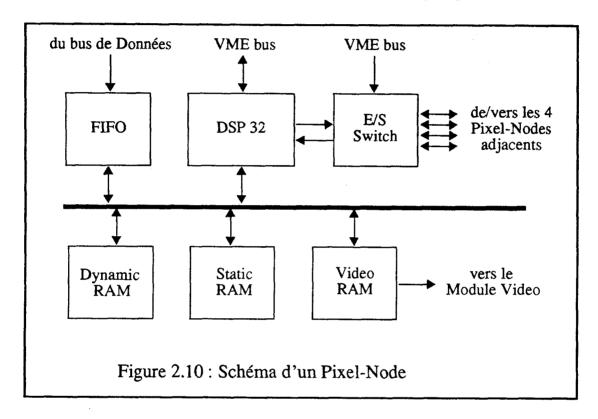

Un "Pixel-Node" a pour composants principaux (voir Figure 2.10): un processeur de signal DSP32 comme le "Pipe-Node", des mémoires statiques et dynamiques, une mémoire vidéo reliée au module vidéo, un contrôleur de synchronisation, une file d'attente pour recevoir les objets graphiques via le bus de données et des primitives d'entrées/sorties lui permettant de communiquer avec les 4 "Pixel-Nodes" adjacents.

• Un module Vidéo composé de deux parties: la première "Pixel Funnel" regroupe et synchronise les pixels distribués dans la mémoire vidéo des différents "Pixel-Nodes", la seconde contrôle l'écran et réalise la conversion digital/analogique.

Le module d'affichage a une capacité de calcul de 820 Mégaflops.

Les parallélismes exploités par cette machine sont faciles à déterminer:

- i) Un pipe-line objets pour traiter les transformations géométriques de 9 ou 18 étages dans le pipe-line de "Pipe-Nodes"

- ii) Un parallélisme pixels égal au nombre de "Pixel-Nodes" travaillant en parallèle sur la mémoire de trame.

- iii) L'utilisation de plusieurs processeurs de signaux travaillant en parallèle sur la mémoire de trame permet une parallélisation de toutes les opérations situées au niveau du pixel.

Cette machine ne permet probablement pas une visualistion très rapide (malheureusement aucun chiffre de performance n'est donné dans les présentations de cette machine). Mais, étant réalisée avec des processeurs généraux, elle est programmable: tous les algorithmes de visualisation peuvent donc être implantés, en particulier des algorithmes

exploitant le lancer de rayons. Quand elle est utilisée pour faire du rendu géométrique classique elle réalise l'antialiassage par suréchantillonage.

# **II.1.8 CAP**

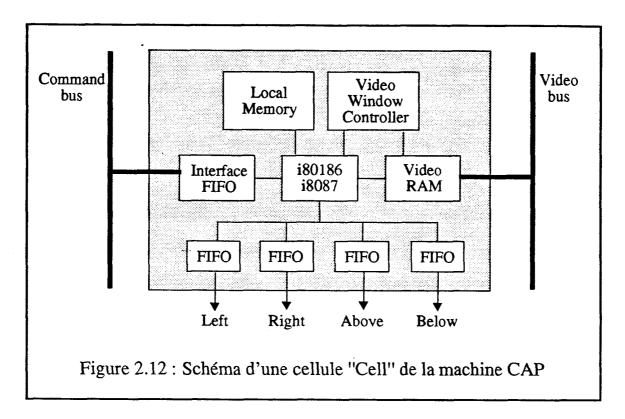

Comme celle que nous venons de présenter, la machine CAP (Cellular Array Processor) [SatoIS85] est réalisée autour d'une matrice de processeurs à usage général (voir Figure 2.11). Pour cette machine ce sont des i80186 couplés avec des i8087. Chacun de ces processeurs, appelé cellule (cell), gère une partie de la mémoire de trame. La répartition de la mémoire de trame aux différentes cellules est programmable par bandes, par blocs, ou point par point, afin d'adapter au mieux la machine à l'algorithme utilisé.

Cette matrice de cellules effectue la conversion des objets en pixels. Les objets visualisables par cette machine sont les facettes polygonales.

La préparation d'une image et les transformations géométriques sont réalisées sur le processeur hôte, un Apollo Domain DN640.

Chaque processeur "Cell" est composé des unités suivantes (voir Figure 2.12) :

- Une unité centrale comprenant un processeur i80186 et un coprocesseur arithmétique i8087.

- Des mémoires RAM, ROM et Video RAM.

- Une unité de répartition de la mémoire de trame entre cellules "Video Window

#### Controller".

- Une interface avec le bus de commande.

- Une voie de communication avec les 4 cellules voisines.

Les concepteurs de cette machine ont développé un logiciel implémentant l'algorithme d'Atherton pour visualiser directement un objet défini par un arbre CSG sans précalculer les intersections des objets sur le processeur hôte. Cela permet d'augmenter considérablement la vitesse d'affichage des objets définis par construction CSG.

Le parallélisme utilisé par cette machine est:

un parallélisme pixels entre les pixels traités par des cellules distinctes de la matrice.

Cette machine possède des caractéristiques architecturales assez similaires à la Pixel Machine. Cependant, comme elle est plus ancienne, ses performances sont moindres.

Cette machine met 8 secondes pour afficher une scène comprenant 5320 polygones avec ombrage de Gouraud et Z-buffer dans une configuration de 64 processeurs "Cell". Les performances sont plus faibles en visualisation directe d'objets définis par des arbres CSG.

# **II.1.9** Experts

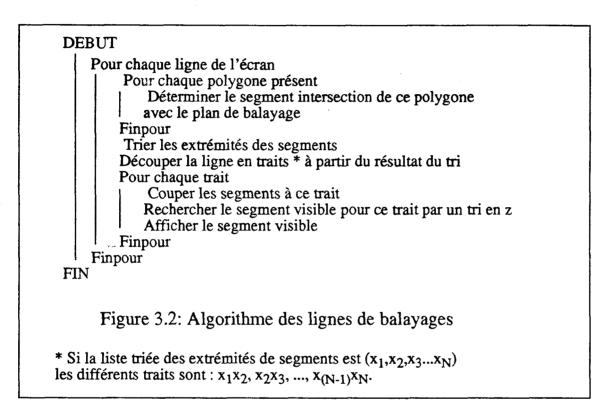

La machine Experts (EXpandable Parallel processor Enhancing Real Time Scan conversion) [NiimIM84] s'appuie sur le fait que l'algorithme d'élimination des parties cachées du Z-buffer par ligne est aisément parallélisable: les traitements des différentes lignes de l'écran sont indépendants les uns des autres.

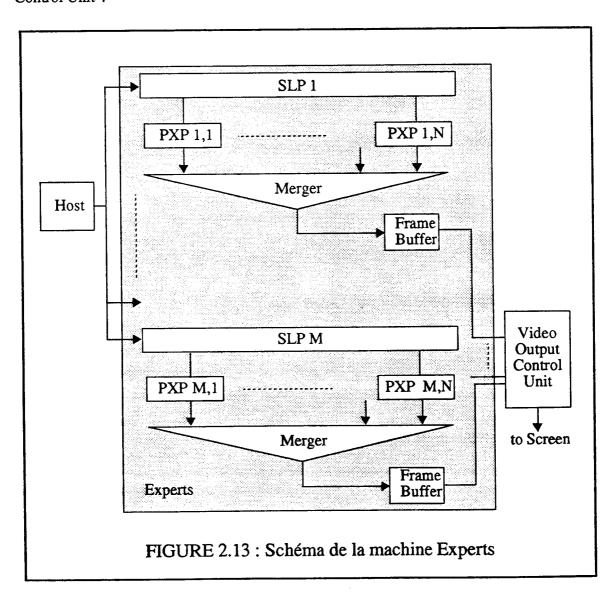

Cette machine est un multiprocesseur exploitant un découpage de l'écran à deux niveaux (voir Figure 2.13) :

- Un ensemble de M processeurs "SLP" (Scan Line Processor) traitant chacun une bande horizontale de l'écran. Chaque processeur décompose les objets graphiques fournis par le hôte en segments horizontaux pour les lignes écran dont il s'occupe. Pour chaque ligne il établit une liste de segments.

- Un ensemble de N processeurs "PXP" (PiXel Processor) associé à chaque processeur "SLP" traitant chacun une partie d'une ligne écran. Les différentes lignes écran traitées par un même "SLP" le sont séquentiellement. Ces processeurs exécutent l'élimination des parties cachées, effectuent les calculs d'ombrage suivant la méthode de Gouraud et effectuent un antialiassage aux extrémités des segments.

Les nombres N et M de processeurs sont bornés par 16, c'est-à-dire au maximum 16 processeurs "SLP" et 16\*16 processeurs "PXP".

M unités "Merger" fusionnent les résultats des différents "PXP" liés à un "SLP" et place les résultats dans la mémoire de trame. Celle-ci est lue par l'unité vidéo "Video Output Control Unit".

Cette machine exploite les parallélismes suivants:

- i) Un parallélisme objets entre les polygones traités par des processeurs "SLP" distincts.

- ii) Un parallélisme objets de plus bas niveau entre les segments horizontaux traités par des processeurs "PXP" distincts d'un même processeur "SLP".

- iii) Un parallélisme pixels. En effet les pixels sont générés en parallèle par N\*M processeurs 'PXP''.

Il faut, cependant, bien cerner les deux restrictions suivantes:

- Aucun effet pipe-line n'est utilisable, les processeurs "PXP" ne pouvant traiter une ligne écran que lorsque tous les objets de la scène ont été traités par le processeur "SLP" dont ils sont esclaves.

- Chaque processeur "SLP" doit considérer tous les objets graphiques, même ceux absents de la partie de l'écran dont il s'occupe pour créer les listes de segments pour chaque ligne. De même, les processeurs "PXP" doivent considérer tous les segments présents sur la ligne.

Ces deux limites restreignent considérablement les possibilités de travail en parallèle.

Les processeurs "SLP" et "PXP" sont des circuits réalisés spécifiquement pour cette machine. Ils sont microprogrammables.

Cette machine a des performances modestes, vu les structures matérielles développées. Ceci est en partie dû au fait que cette proposition a quelques années; avec les même concepts, on pourrait envisager aujourd'hui de meilleures performances.

Cete machine dans une configuration comprenant 8 processeurs "SLP" et 8\*8 processeurs "PXP" peut afficher environ 200 polygones avec ombrage de Gouuraud et Z-buffer en un quinzième de seconde.

# II.1.10 La Machine de Torborg

[DenaRT88][Torbor87]

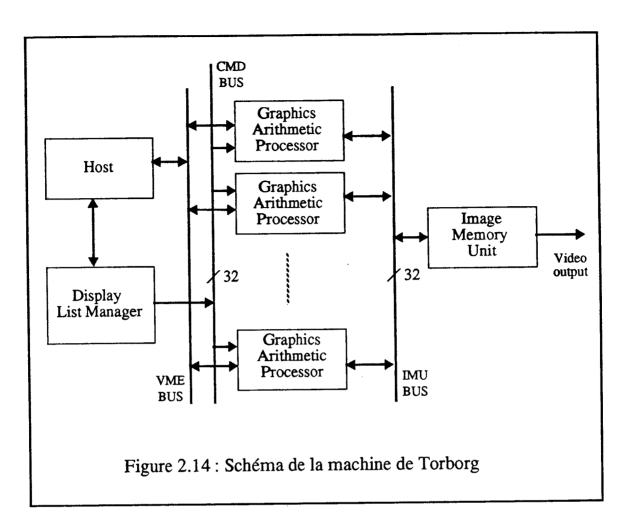

L'unité graphique de cette machine est composée (voir Figure 2.14) d'une structure de donnée "DLM" (Display List Manager) de plusieurs processeurs objets "GAP" (Graphics Arithmetic Processor) travaillant en parallèle (au maximum 8) et d'une unité de mémoire de trame "IMU" (Image Memory Unit). L'unité "DLM" contient les outils permettant la répartition des objets aux processeurs "GAP".

Les processeurs objets sont de puissants processeurs directement contrôlés par l'application via le "VME bus". A partir des objets de la structure de données à laquelle ils sont reliés via le "CMD bus", les processeurs objets produisent des objets de bas niveau (points, segments, rectangles, triangles...). Un second bus "IMU bus" relie les processeurs objets à l'unité de mémoire d'image.

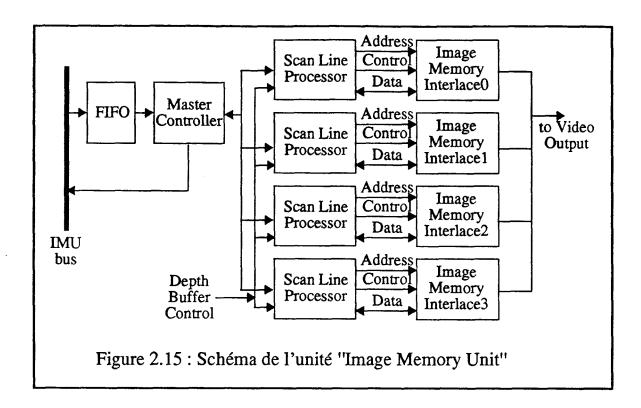

L'unité "IMU" traite des triangles 3D par interpolations linéaires à partir des valeurs X, Y, Z, R, V et B aux trois sommets du triangle. Elle est composée d'un contrôleur "Master Controller" qui prétraite les objets et de quatre processeurs "Scan Line Processor" gérant chacun un quart des lignes (voir Figure 2.15).

Le "Master Controller" détermine les extrémités des différents segments composant chaque triangle. Les unités "Scan Line Processor" génèrent les valeurs Z, R, V et B en tous les pixels de chacun des segments et effectuent l'élimination des parties cachées par l'algorithme du Z-buffer.

Le "Master Controler" et les "Scan Line Processor" sont des circuits intégrés VLSI. Le "Master Controller" contient environ 8700 portes et le "Scan Line Processor" 15000 portes. Les principaux éléments de ces circuits intégrés sont des mémoires, des interpolateurs et des générateurs d'adresses.

L'unité de mémoire d'image est contrôlée par l'ordinateur hôte via les processeurs objets. Une commande séquentielle graphique n'est exécutable que lorsque les différents processeurs objets ont terminé le traitement en cours. Cette machine ne peut donc être utilisée pour afficher une image en un vingt-cinquième de seconde.

Les parallélismes utilisés sont les suivants:

- i) Un parallélisme objets entre les objets traités par des processeurs "GAP" différents pour les traitements géométriques.

- ii) Un parallélisme objets de bas niveau entre les segments d'un même triangle traités par des "Scan Line Processors" distincts.

- iii) Un parallélisme pixels dans l'unité "IMU". Cette unité génére les pixels dans la mémoire de trame au rythme de 20 à chaque cycle.

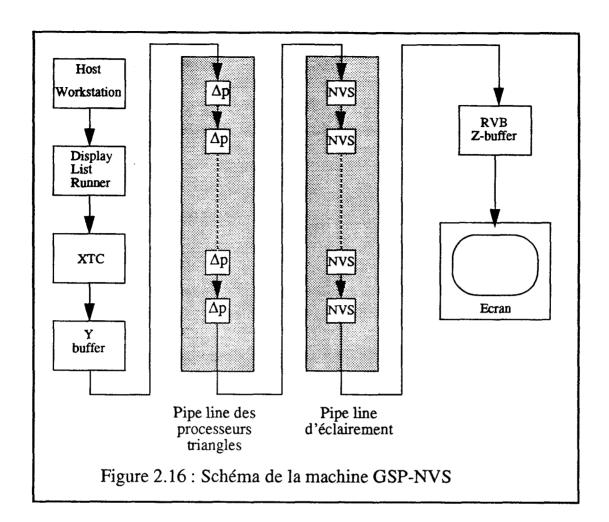

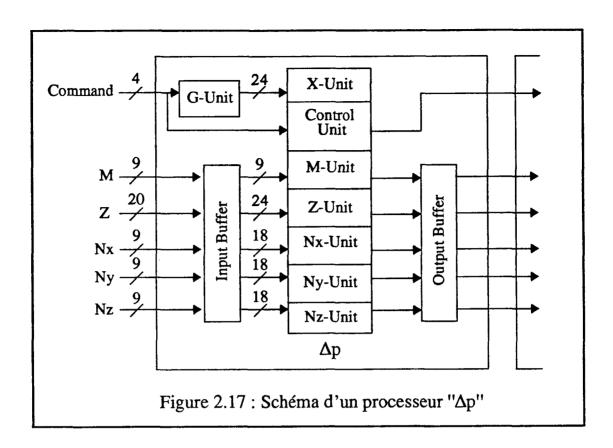

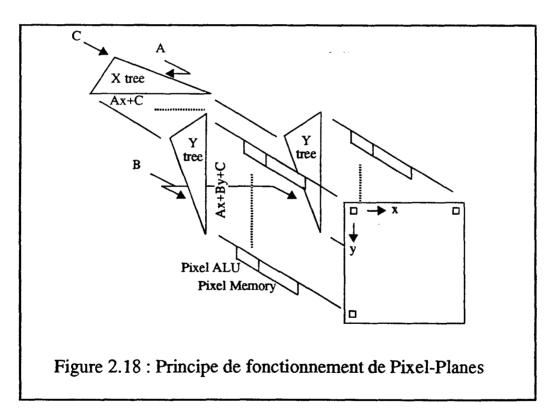

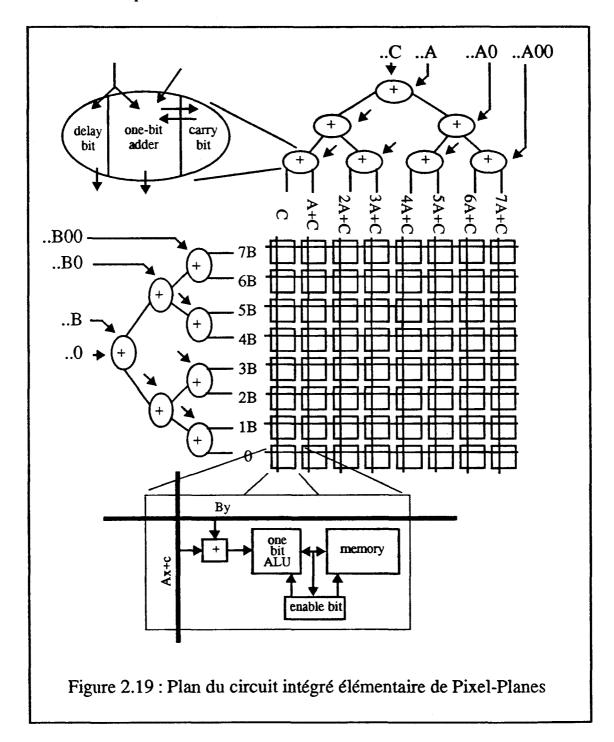

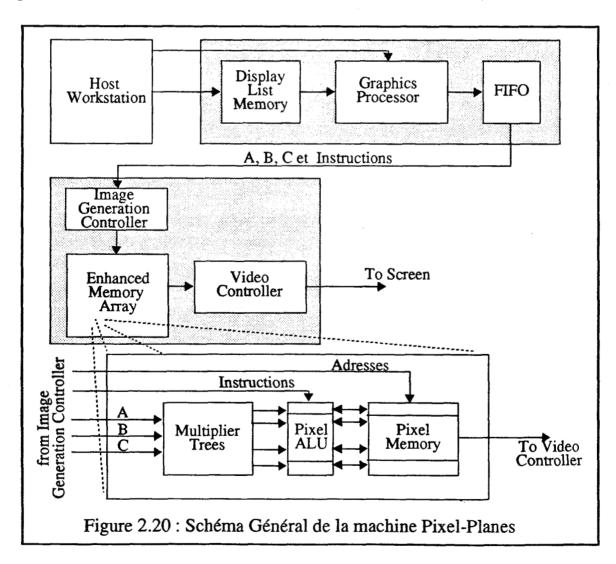

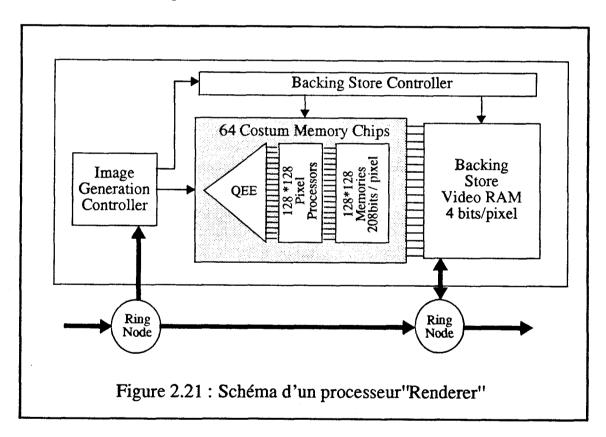

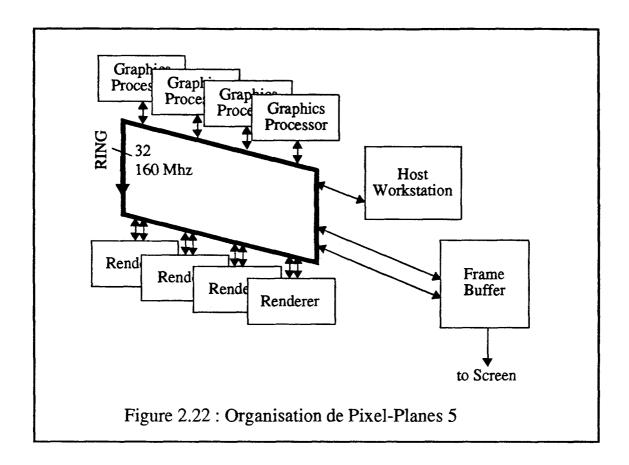

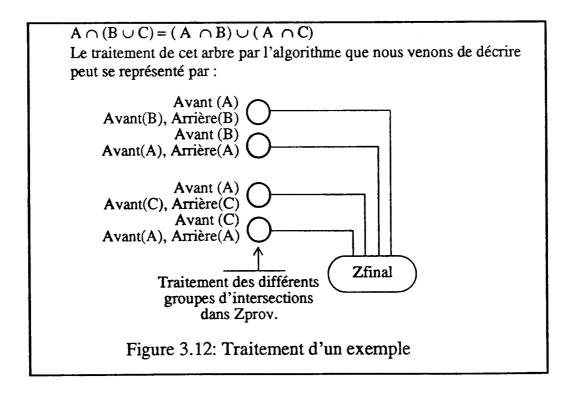

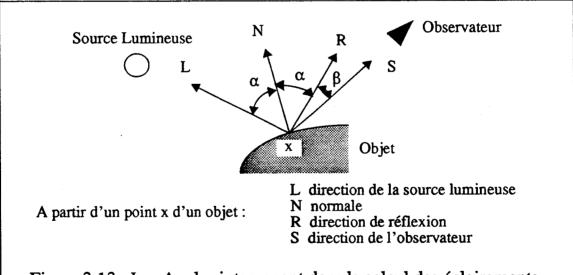

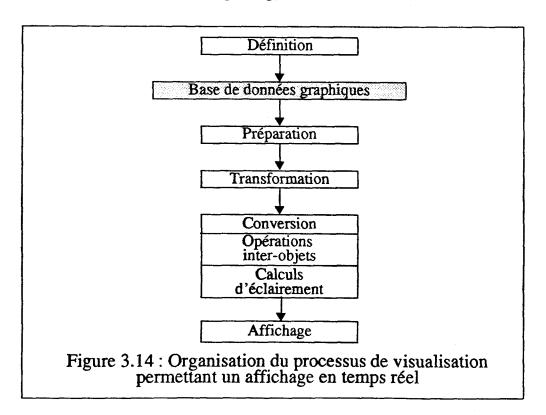

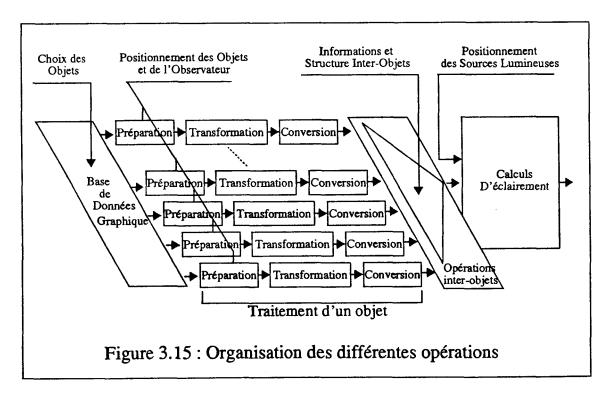

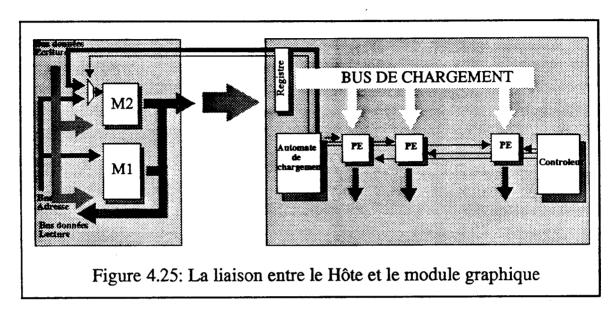

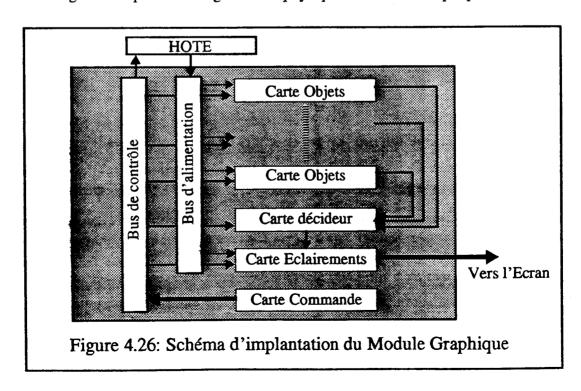

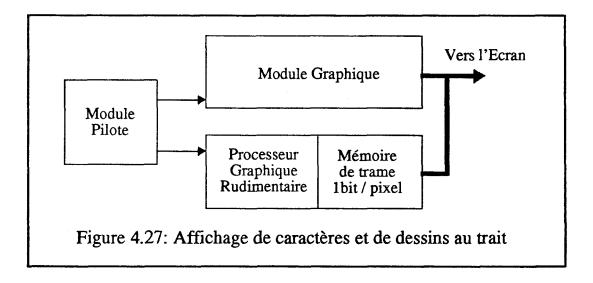

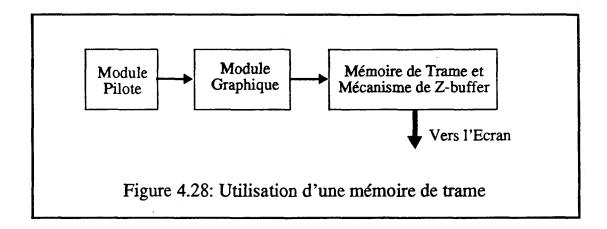

Seul le processeur "IMU" est réalisé avec des composants VLSI. Ce processeur permet de générer 60 millions de pixels par seconde.