gen 20000 200.

# **THESE**

présentée à

# L'UNIVERSITE DES SCIENCES ET TECHNOLOGIES DE LILLE

pour obtenir le titre de

#### DOCTEUR DE L'UNIVERSITE

spécialité: ELECTRONIQUE

par

## Jean-François THIERY

# ETUDE ET REALISATION DE TRANSISTORS HIGFETS COMPLEMENTAIRES EN TECHNOLOGIE **AUTO-ALIGNEE POUR CIRCUITS LOGIQUES** RAPIDES A FAIBLE CONSOMMATION

Soutenue le 11 octobre 1996 devant la commission d'examen :

Membres du jury : MM.

E. CONSTANT

Président

G. SALMER

Directeur de thèse

A. MARTINEZ

Rapporteur

L. NUYEN

Rapporteur

**B. DELMAS**

Examinateur

Examinateur

H. FAWAZ

G. GATTI

Examinateur

S. RIGOT

Examinateur

H. VERRIELE

Examinateur

| • |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

# **SOMMAIRE**

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| PARTIE 1 : Intérêt du HIGFET pour la logique rapide à faible consommation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15                                                             |

| CHAPITRE I : Les différentes familles de circuits intégrés numériques rapides                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                             |

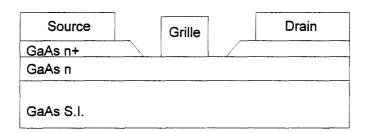

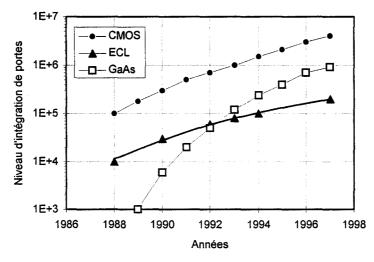

| I.1 Introduction : applications et tendances des circuits intégrés rapides à faible consommation  I.1.1 Ordinateurs rapides  I.1.2 Commutations optiques et mobiles  I.1.3 Exigences des circuits rapides et à faible consommation  I.2 Filières technologiques à CMOS et BiCMOS  I.2.1 Orientations de la technologie MOS  I.2.2 L'alternative BiCMOS  I.3 Les circuits intégrés en Arséniure de Gallium  I.3.1 Intérêts et problèmes de l'Arséniure de Gallium par rapport au silicium  I.3.2 Historique de l'évolution des composants en GaAs  I.3.3 Les différentes logiques à MESFET | 17<br>17<br>18<br>19<br>19<br>19<br>21<br>22<br>23<br>24<br>28 |

| I.3.4 Exemples de circuits numériques sur GaAs I.4 Comparaison de mémoires statiques (SRAM) réalisées en technologies Si et GaAs I.4.1 Justification de ce critère I.4.2 Comparatif de SRAMs I.4.3 Synthèse I.5 Vers une approche complémentaire sur GaAs I.5.1 Intérêts d'une filière de logique complémentaire sur GaAs I.5.2 Moyens et objectifs pour la recherche d'une structure optimale Bibliographie                                                                                                                                                                              | 30<br>30<br>31<br>32<br>33<br>33<br>34                         |

| CHAPITRE II : Le transistor HIGFET (Heterostructure Insulated-Gate Field-Effect Transistor)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39                                                             |

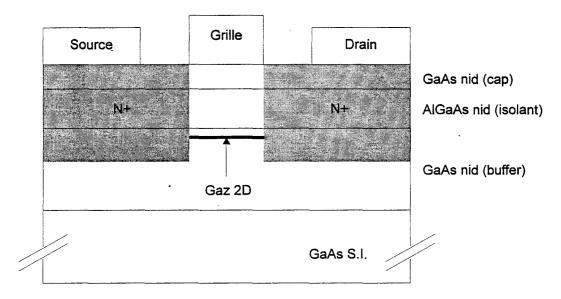

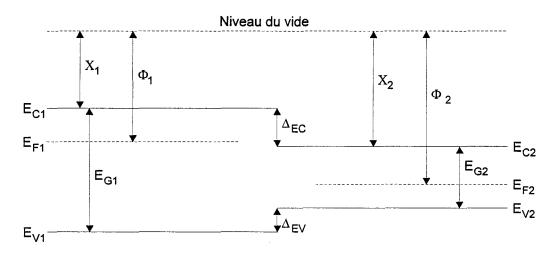

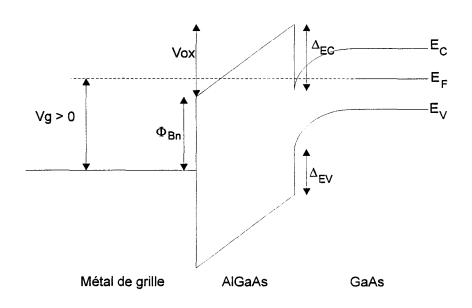

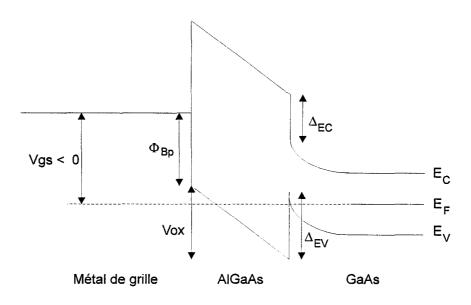

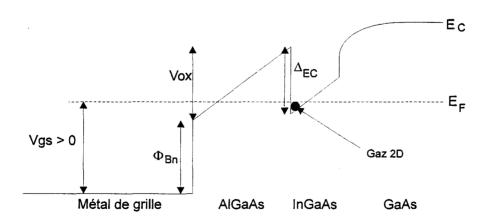

| <ul> <li>II.1 Principe de fonctionnement du HIGFET</li> <li>II.1.1 Structure MIS avec une couche d'Al<sub>x</sub>Ga<sub>1-x</sub>As</li> <li>II.1.2 Avantages d'une structure non dopée</li> <li>II.2 Description de la structure du matériau et de ses variantes</li> <li>II.2.1 Diagrammes de bandes d'énergie</li> </ul>                                                                                                                                                                                                                                                               | 39<br>39<br>40<br>41<br>41                                     |

| auto-aligné  III.1 Principes de la technologie auto-alignée  III.1.1 Pourquoi une technologie auto-alignée ?  III.1.2 Besoins d'une implantation ionique et d'un recuit à haute température  III.2 Procédé à grille en T existant à l'IEMN  III.2.1 Points clés du procédé à grille en T  III.3 Caractéristiques de notre technologie  III.3.1 Axes de développement  III.3.2 Diagramme du procédé technologique  III.4 Importance de réussir le recuit d'implantation  III.4.1 Caractéristiques d'un recuit non réussi  III.4.2 Précautions à observer pour réussir le recuit  III.5.1 Description de la matrice élémentaire  III.5.2 Niveaux du masque FTFET  III.5.3 Description de la matrice de test  III.5.4 Description de la matrice de test  III.5.5 Points clés du procédé  III.6 Points clés du procédé | II.2.2 HIGFET pseudomorphique                                                     | 44 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----|

| complémentaires rapides et à faible consommation  II.3.1 Temps de retard II.3.2 Consommation II.3.3 Tensions de seuil II.3.3 Tensions de seuil II.4 Etat de l'art du HIGFET pseudomorphique II.4.1 Composants II.4.2 Exemples de circuits et applications actuelles II.5 Structures semiconductrices utilisées dans notre étude II.6 Notre plan de travail II.5 Ontre plan de travail II.5 Bibliographie  PARTIE 2: Procédé technologique auto-aligné pour la réalisation de transistors HIGFETs complémentaires  PARTIE III : Caractéristiques essentielles du procédé technologique auto-aligné III.1 Principes de la technologie auto-alignée III.1.1 Pourquoi une technologie auto-alignée? III.1.2 Besoins d'une implantation ionique et d'un recuit à haute température III.2 Procédé à grille en T existant à l'IEMN III.2.1 Points clés du procédé à grille en T III.2.2 Résultats et problèmes à résoudre III.3.1 Axes de développement III.3.2 Diagramme du procédé technologique III.3.1 Axes de développement III.3.2 Diagramme du procédé technologique III.4 Importance de réussir le recuit d'implantation III.4.1 Caractéristiques d'un recuit non réussi III.4.2 Précautions à observer pour réussir le recuit III.5 Conception et dessin d'un jeu de masques FTFET III.5.1 Description de la matrice élémentaire III.5.2 Niveaux du masque FTFET III.5.3 Description de la matrice de test III.6 Points clés du procédé Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  81  CHAPITRE IV : Formation de la grille réfractaire des HIGFETS  82  IV.1 Utilisation d'un métal réfractaire IV.2 Choix du métal réfractaire IV.2 Chile en WNx IV.2.2 Grille en WNx IV.2.2 Gril | II.2.3 Insertion d'un plan de dopage en silicium                                  | 46 |

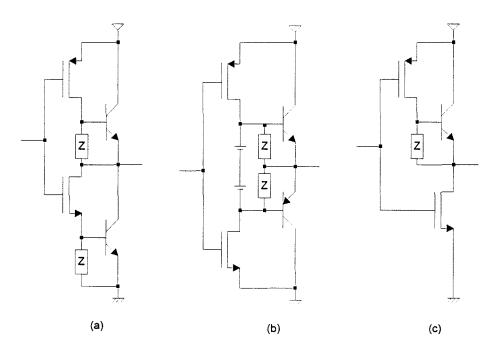

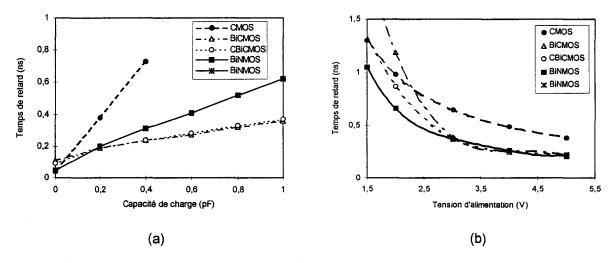

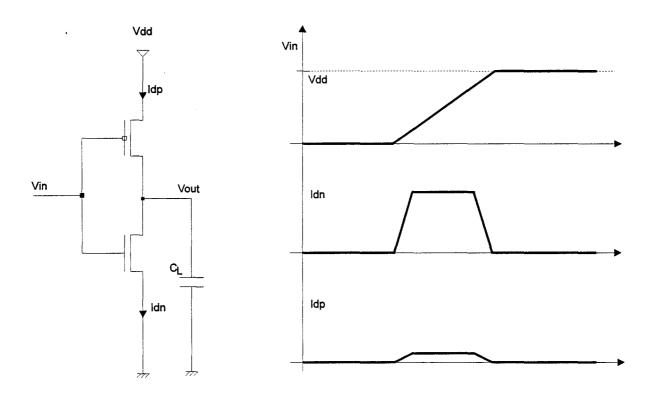

| II.3.1 Temps de retard II.3.2 Consommation II.3.3 Temsions de seuil II.3.3 Temsions de seuil II.4.1 Composants II.4.1 Composants II.4.1 Composants II.4.2 Exemples de circuits et applications actuelles II.5 Structures semiconductrices utilisées dans notre étude II.6 Notre plan de travail II.7 Principaraphie  CHAPITRE III: Caractéristiques essentielles du procédé technologique auto-aligné III.1 Principes de la technologie auto-alignée III.1 Principes de la technologie auto-alignée III.1.1 Pourquoi une technologie auto-alignée III.1.2 Besoins d'une implantation ionique et d'un recuit à haute température III.2 Procédé à grille en T existant à l'IEMN III.2.1 Points clés du procédé à grille en T III.3 Caractéristiques de notre technologie III.4 Importance de réussir le recuit d'implantation III.4 Importance de réussir le recuit d'implantation III.4 Importance de réussir le recuit d'implantation III.4 Inportance de réussir le recuit d'implantation III.5 Conception et dessin d'un reus plantation III.5 Conception et dessin d'un reus serve pour réussir le recuit III.5 Conception de la matrice élémentaire III.5.1 Description de la matrice élémentaire III.5.2 Niveaux du masque FTFET III.5.3 Discoription d'un transistor bi-doigts III.5.4 Description de la matrice de test III.6 Points clés du procédé III.6 Points clés du procédé III.7 Utilisation d'un métal réfractaire IV.2 Choix du métal réfractaire IV.2 Chile en WNx IV.2.2 Grille en WNx                                                                                    | II.3 Utilisation du HIGFET pour la réalisation de circuits intégrés en logique    |    |

| II.3.2 Consommation II.3.3 Tensions de seuil II.4 Etat de l'art du HIGFET pseudomorphique II.4.1 Composants II.4.2 Exemples de circuits et applications actuelles II.5 Structures semiconductrices utilisées dans notre étude II.6 Notre plan de travail Bibliographie  PARTIE 2: Procédé technologique auto-aligné pour la réalisation de transistors HIGFET's complémentaires  FORTIE 2: Procédé technologique auto-aligné pour la réalisation de transistors HIGFET's complémentaires  FORTIE III: Caractéristiques essentielles du procédé technologique auto-aligné  III.1 Principes de la technologie auto-alignée ? III.1.2 Desoins d'une implantation ionique et d'un recuit à haute température  III.2 Procédé à grille en T existant à l'IEMN 63 III.2.1 Points clés du procédé à grille en T 63 III.3 Caractéristiques de notre technologie III.3.1 Axes de développement 64 III.3.1 Axes de développement 64 III.3.1 Diagramme du procédé technologique 66 III.4 Importance de réussir le recuit d'implantation 111.4 Précautions à observer pour réussir le recuit 70 III.5 Conception et dessin d'un jeu de masques FTFET 71 III.5.1 Description de la matrice élémentaire 72 III.5.2 Niveaux du masque FTFET 73 III.5.3 Description d'un transistor bi-doigts 75 III.5.4 Description de la matrice de test 76 III.6 Points clés du procédé 18 III.6 Points clés du procédé 19 III.6 CHAPITRE IV: Formation de la grille réfractaire 48 IV.1 Utilisation d'un métal réfractaire 81 IV.2 Choix du métal réfractaire 82 IV.2.1 Grille en WNix 82 IV.2.2 Grille en WSix 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | complémentaires rapides et à faible consommation                                  | 47 |

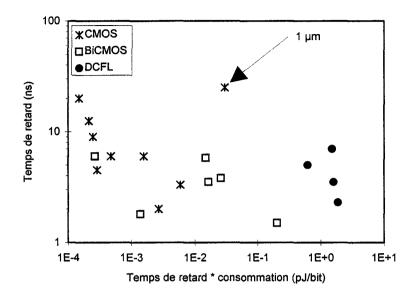

| II.3.3 Tensions de seuil II.4 Etat de l'art du HIGFET pseudomorphique II.4.1 Composants II.4.2 Exemples de circuits et applications actuelles II.5 Structures semiconductrices utilisées dans notre étude II.6 Notre plan de travail Bibliographie   PARTIE 2: Procédé technologique auto-aligné pour la réalisation de transistors HIGFET's complémentaires  59  CHAPITRE III: Caractéristiques essentielles du procédé technologique auto-aligné III.1 Principes de la technologie auto-alignée III.1.1 Pourquoi une technologie auto-alignée? III.1.2 Besoins d'une implantation ionique et d'un recuit à haute température III.2 Procédé à grille en T existant à l'IEMN III.2.1 Points clés du procédé à grille en T III.2.2 Résultats et problèmes à résoudre III.3 Caractéristiques de notre technologie III.3 Caractéristiques de notre technologie III.3 Laxs de développement III.3.1 Axes de développement III.3.1 Caractéristiques d'un recuit non réussi III.4.1 Caractéristiques d'un recuit non réussi III.4.1 Caractéristiques d'un recuit non réussi III.4.2 Précautions à observer pour réussir le recuit III.5.1 Description de la matrice élémentaire III.5.2 Niveaux du masque FTFET III.5.3 Description de la matrice de test III.6 Points clés du procédé Bibliographie  CHAPITRE IV: Formation de la grille réfractaire des HIGFET's  IV.1 Utilisation d'un métal réfractaire IV.2 Choix du métal réfractaire                                                                                          | II.3.1 Temps de retard                                                            | 47 |

| II.4 Etat de l'art du HIGFET pseudomorphique II.4.1 Composants II.4.2 Exemples de circuits et applications actuelles II.5 Structures semiconductrices utilisées dans notre étude II.6 Notre plan de travail Bibliographie  PARTIE 2 : Procédé technologique auto-aligné pour la réalisation de transistors HIGFETs complémentaires  59  CHAPITRE III : Caractéristiques essentielles du procédé technologique auto-aligné III.1 Principes de la technologie auto-alignée III.1.1 Pourquoi une technologie auto-alignée? III.1.2 Poscoins d'une implantation ionique et d'un recuit à haute température III.2 Procédé à grille en T existant à l'IEMN III.2.1 Proints clés du procédé à grille en T III.2.2 Résultats et problèmes à résoudre III.3 Caractéristiques de notre technologie III.3.1 Axes de développement III.3.2 Diagramme du procédé technologique III.4.1 Caractéristiques d'un recuit d'implantation III.4.1 Caractéristiques d'un recuit non réussi III.4.2 Précautions à observer pour réussir le recuit III.5.1 Description de la matrice élémentaire III.5.2 Niveaux du masque FTFET III.5.3 Description d'un transistor bi-doigts III.5.4 Description de la matrice de test III.6 Points clés du procédé Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  IV.1 Utilisation d'un métal réfractaire IV.2 Choix du métal réfractaire IV.2 Choix du métal réfractaire IV.2 Grille en WNx IV.2.2 Grille en WSix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | II.3.2 Consommation                                                               | 48 |

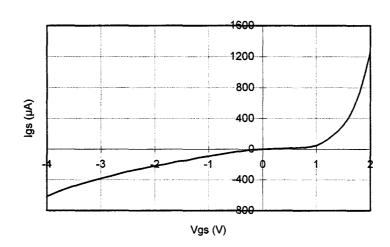

| II.4.1 Composants II.4.2 Exemples de circuits et applications actuelles II.5 Structures semiconductrices utilisées dans notre étude II.6 Notre plan de travail Bibliographie  PARTIE 2 : Procédé technologique auto-aligné pour la réalisation de transistors HIGFETs complémentaires  59  CHAPITRE III : Caractéristiques essentielles du procédé technologique auto-aligné  III.1 Principes de la technologie auto-alignée III.1.1 Pourquoi une technologie auto-alignée? III.1.2 Besoins d'une implantation ionique et d'un recuit à haute température  température  III.2 Procédé à grille en T existant à l'IEMN III.2.1 Points clés du procédé à grille en T III.2.2 Résultats et problèmes à résoudre III.3 Caractéristiques de notre technologie III.3 Caractéristiques de notre technologie III.4 Importance de réussir le recuit d'implantation III.4 Inportance de réussir le recuit d'implantation III.4.1 Precarctéristiques d'un recuit non réussi III.4.1 Prescription de la matrice de dementaire III.5.1 Description de la matrice de dementaire III.5.1 Description de la matrice de lémentaire III.5.2 Niveaux du masque FTFET III.5.3 Description de la matrice de test III.6 Points clés du procédé Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  81  V.1 Utilisation d'un métal réfractaire IV.2 Choix du métal réfractaire IV.2 Choix du métal réfractaire IV.2.2 Grille en WNx IV.2.2 Grille en WSix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | II.3.3 Tensions de seuil                                                          | 50 |

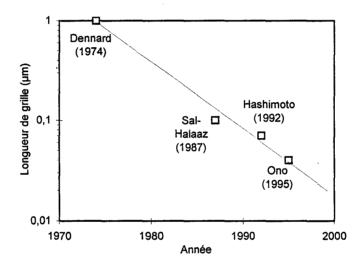

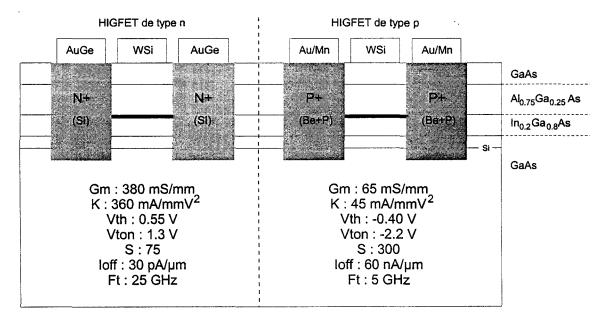

| II.4.2 Exemples de circuits et applications actuelles II.5 Structures semiconductrices utilisées dans notre étude II.6 Notre plan de travail Bibliographie  PARTIE 2 : Procédé technologique auto-aligné pour la réalisation de transistors HIGFETs complémentaires  CHAPITRE III : Caractéristiques essentielles du procédé technologique auto-aligné III.1 Principes de la technologie auto-alignée III.1.1 Prourquoi une technologie auto-alignée? III.1.2 Besoins d'une implantation ionique et d'un recuit à haute température III.2 Procédé à grille en T existant à l'IEMN III.2.1 Points clès du procédé à grille en T III.2.2 Résultats et problèmes à résoudre III.3.1 Axes de développement III.3.2 Diagramme du procédé technologique III.3.1 Description de la matrice démentaire III.4.1 Caractéristiques d'un recuit non réussi III.4.2 Précautions à observer pour réussir le recuit III.5.1 Description de la matrice élémentaire III.5.2 Niveaux du masque FTFET III.5.3 Description de la matrice de test III.5.4 Description de la matrice de test III.5.5 Niveaux du masque FTFET III.5.6 Points clés du procédé Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  IV.1 Utilisation d'un métal réfractaire IV.2.1 Grille en WNx IV.2.2 Grille en WSix  83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | II.4 Etat de l'art du HIGFET pseudomorphique                                      | 51 |

| II.5 Structures semiconductrices utilisées dans notre étude II.6 Notre plan de travail Bibliographie  PARTIE 2: Procédé technologique auto-aligné pour la réalisation de transistors HIGFETs complémentaires  59  CHAPITRE III: Caractéristiques essentielles du procédé technologique auto-aligné III.1 Principes de la technologie auto-alignée III.1.1 Pourquoi une technologie auto-alignée? III.1.2 Besoins d'une implantation ionique et d'un recuit à haute température III.2 Procédé à grille en T existant à l'IEMN III.2.1 Points clés du procédé à grille en T III.3 Caractéristiques de notre technologie III.3 Caractéristiques de notre technologie III.3.1 Axes de développement III.3.2 Diagramme du procédé technologique III.4 Importance de réussir le recuit d'implantation III.4.1 Caractéristiques d'un recuit non réussi III.4.2 Précautions à observer pour réussir le recuit III.5.1 Description de la matrice élémentaire III.5.1 Niveaux du masque FTFET III.5.1 Description de la matrice de test III.5.4 Description de la matrice de test III.5.5 Description de la matrice de test III.5.6 Points clés du procédé Bibliographie  CHAPITRE IV: Formation de la grille réfractaire des HIGFETs  IV.1 Utilisation d'un métal réfractaire IV.2 Choix du métal réfractaire IV.2.1 Grille en WNx IV.2.2 Grille en WSix  83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | II.4.1 Composants                                                                 | 51 |

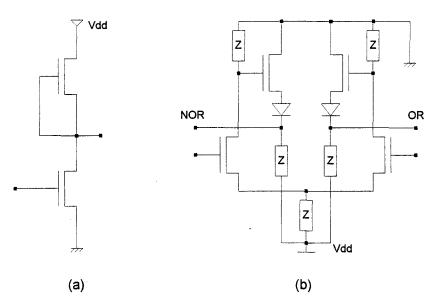

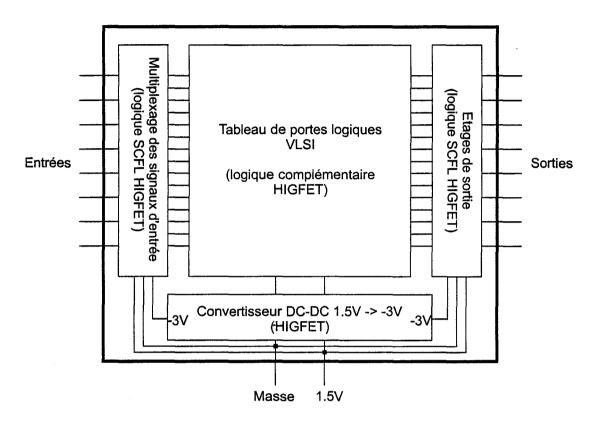

| II.6 Notre plan de travail Bibliographie  PARTIE 2 : Procédé technologique auto-aligné pour la réalisation de transistors HIGFETs complémentaires  59  CHAPITRE III : Caractéristiques essentielles du procédé technologique auto-aligné III.1 Principes de la technologie auto-alignée III.1.2 Besoins d'une implantation ionique et d'un recuit à haute température III.2 Procédé à grille en T existant à l'IEMN III.2.1 Points clés du procédé à grille en T III.2.2 Résultats et problèmes à résoudre III.3 Caractéristiques de notre technologie III.3.1 Axes de développement III.3.2 Diagramme du procédé technologique III.4.1 Caractéristiques d'un recuit d'implantation III.4.1 Caractéristiques d'un recuit non réussi III.4.2 Précautions à observer pour réussir le recuit III.5.1 Description de la matrice élémentaire III.5.2 Niveaux du masque FTFET III.5.3 Description de la matrice de test III.5.4 Niveaux du masque FTFET III.5.5 Niveaux du masque FTFET III.5.5 Description de la matrice de test III.6 Points clés du procédé Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETS  IV.1 Utilisation d'un métal réfractaire IV.2 Choix du métal réfractaire IV.2.1 Grille en WNx IV.2.2 Grille en WNx IV.2.2 Grille en WSix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | II.4.2 Exemples de circuits et applications actuelles                             | 53 |

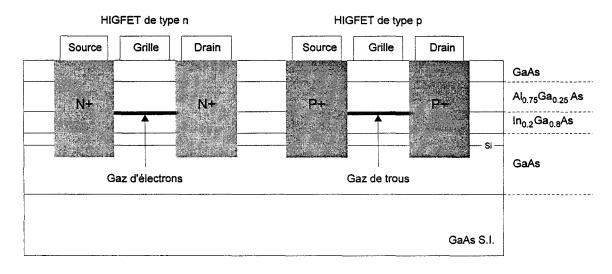

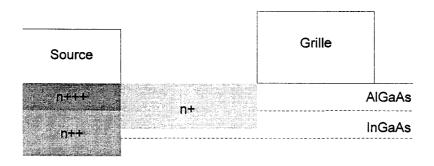

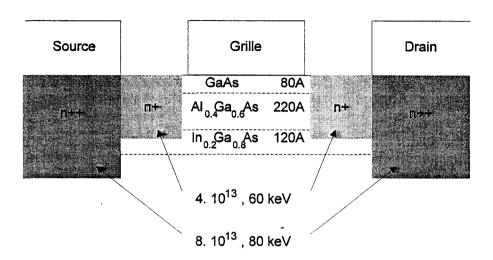

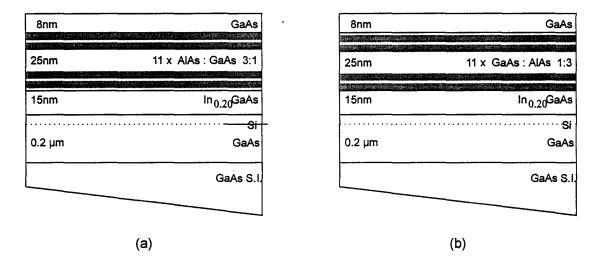

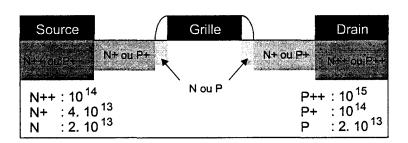

| PARTIE 2 : Procédé technologique auto-aligné pour la réalisation de transistors HIGFETs complémentaires  CHAPITRE III : Caractéristiques essentielles du procédé technologique auto-aligné 61  III.1 Principes de la technologie auto-alignée 7 61  III.1.2 Besoins d'une implantation ionique et d'un recuit à haute température 7 62  III.2 Procédé à grille en T existant à l'IEMN 7 63  III.2.1 Points clés du procédé à grille en T 7 63  III.2.2 Résultats et problèmes à résoudre 7 63  III.3 Caractéristiques de notre technologie 7 64  III.3.1 Axes de développement 7 64  III.3.2 Diagramme du procédé technologique 7 68  III.4.1 Caractéristiques d'un recuit non réussi 7 68  III.4.2 Précautions à observer pour réussir le recuit 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | II.5 Structures semiconductrices utilisées dans notre étude                       | 54 |

| PARTIE 2 : Procédé technologique auto-aligné pour la réalisation de transistors HIGFETs complémentaires  59  CHAPITRE III : Caractéristiques essentielles du procédé technologique auto-aligné  III.1 Principes de la technologie auto-alignée ? 61  III.1.2 Besoins d'une implantation ionique et d'un recuit à haute température 62  III.2 Procédé à grille en T existant à l'IEMN 63  III.2.1 Points clés du procédé à grille en T 63  III.2.2 Résultats et problèmes à résoudre 63  III.3 Caractéristiques de notre technologie 64  III.3.1 Axes de développement 64  III.3.1 Diagramme du procédé technologique 66  III.4 Importance de réussir le recuit d'implantation 68  III.4.1 Caractéristiques d'un recuit non réussi 68  III.4.2 Précautions à observer pour réussir le recuit 70  III.5 Conception et dessin d'un jeu de masques FTFET 71  III.5.1 Description de la matrice élémentaire 72  III.5.2 Niveaux du masque FTFET 73  III.5.3 Description de la matrice de test 76  III.6 Points clés du procédé 79  Bibliographie 80  CHAPITRE IV : Formation de la grille réfractaire des HIGFETS 81  IV.1 Utilisation d'un métal réfractaire 81  IV.2 Choix du métal réfractaire 82  IV.2.1 Grille en WNx 82  IV.2.2 Grille en WSix 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | II.6 Notre plan de travail                                                        | 55 |

| CHAPITRE III : Caractéristiques essentielles du procédé technologique auto-aligné 61  III.1 Principes de la technologie auto-alignée ? 61  III.1.2 Besoins d'une implantation ionique et d'un recuit à haute température 62  III.2 Procédé à grille en T existant à l'IEMN 63  III.2.1 Points clés du procédé à grille en T 63  III.2.2 Résultats et problèmes à résoudre 63  III.3 Caractéristiques de notre technologie 64  III.3.1 Axes de développement 64  III.3.2 Diagramme du procédé technologique 66  III.4 Importance de réussir le recuit d'implantation 68  III.4.2 Précautions à observer pour réussir le recuit 70  III.5 Conception et dessin d'un jeu de masques FTFET 71  III.5.1 Description de la matrice élémentaire 72  III.5.2 Niveaux du masque FTFET 73  III.5.3 Description d'un transistor bi-doigts 75  III.5.4 Description de la matrice de test 76  III.6 Points clés du procédé 79  Bibliographie 80  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs 81  IV.1 Utilisation d'un métal réfractaire 82  IV.2 Choix du métal réfractaire 82  IV.2.1 Grille en WNx 82  IV.2.2 Grille en WNix 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bibliographie                                                                     | 56 |

| auto-aligné 61  III.1 Principes de la technologie auto-alignée 7  III.1.1 Pourquoi une technologie auto-alignée 7  III.1.2 Besoins d'une implantation ionique et d'un recuit à haute température 62  III.2 Procédé à grille en T existant à l'IEMN 63  III.2.1 Points clés du procédé à grille en T 63  III.2.2 Résultats et problèmes à résoudre 63  III.3 Caractéristiques de notre technologie 64  III.3.1 Axes de développement 64  III.3.2 Diagramme du procédé technologique 66  III.4 Importance de réussir le recuit d'implantation 68  III.4.1 Caractéristiques d'un recuit non réussi 68  III.4.2 Précautions à observer pour réussir le recuit 70  III.5 Conception et dessin d'un jeu de masques FTFET 71  III.5.1 Description de la matrice élémentaire 72  III.5.2 Niveaux du masque FTFET 73  III.5.3 Description d'un transistor bi-doigts 75  III.5.4 Description de la matrice de test 76  III.6 Points clés du procédé 79  Bibliographie 80  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs 81  IV.1 Utilisation d'un métal réfractaire 81  IV.2 Choix du métal réfractaire 82  IV.2.1 Grille en WNx 82  IV.2.2 Grille en WSix 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~ · · · · · · · · · · · · · · · · · · ·                                           |    |

| III. 1.1 Pourquoi une technologie auto-alignée ?  III. 1.2 Besoins d'une implantation ionique et d'un recuit à haute température  III. 2 Procédé à grille en T existant à l'IEMN  III. 2.1 Points clés du procédé à grille en T  III. 2.2 Résultats et problèmes à résoudre  III. 3.1 Axes de notre technologie  III. 3.1 Axes de développement  III. 3.2 Diagramme du procédé technologique  III. 4.1 Importance de réussir le recuit d'implantation  III. 4.1 Caractéristiques d'un recuit non réussi  III. 4.2 Précautions à observer pour réussir le recuit  III. 5.1 Description de la matrice élémentaire  III. 5.2 Niveaux du masque FTFET  III. 5.3 Description d'un transistor bi-doigts  III. 5.4 Description de la matrice de test  III. 5.6 Points clés du procédé  III. 6 Points clés du procédé  III. 6 Points clés du procédé  IV. 1 Utilisation d'un métal réfractaire  IV. 2 Choix du métal réfractaire  IV. 2 Choix du métal réfractaire  IV. 2.1 Grille en WNx  IV. 2.2 Grille en WNx  IV. 2.2 Grille en WSix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CHAPITRE III : Caractéristiques essentielles du procédé technologique auto-aligné | 61 |

| III. 1.1 Pourquoi une technologie auto-alignée ?  III. 1.2 Besoins d'une implantation ionique et d'un recuit à haute température  III. 2 Procédé à grille en T existant à l'IEMN  III. 2.1 Points clés du procédé à grille en T  III. 2.2 Résultats et problèmes à résoudre  III. 3.1 Axes de notre technologie  III. 3.1 Axes de développement  III. 3.2 Diagramme du procédé technologique  III. 4.1 Importance de réussir le recuit d'implantation  III. 4.1 Caractéristiques d'un recuit non réussi  III. 4.2 Précautions à observer pour réussir le recuit  III. 5.1 Description de la matrice élémentaire  III. 5.2 Niveaux du masque FTFET  III. 5.3 Description d'un transistor bi-doigts  III. 5.4 Description de la matrice de test  III. 5.6 Points clés du procédé  III. 6 Points clés du procédé  III. 6 Points clés du procédé  IV. 1 Utilisation d'un métal réfractaire  IV. 2 Choix du métal réfractaire  IV. 2 Choix du métal réfractaire  IV. 2.1 Grille en WNx  IV. 2.2 Grille en WNx  IV. 2.2 Grille en WSix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                                                                 |    |

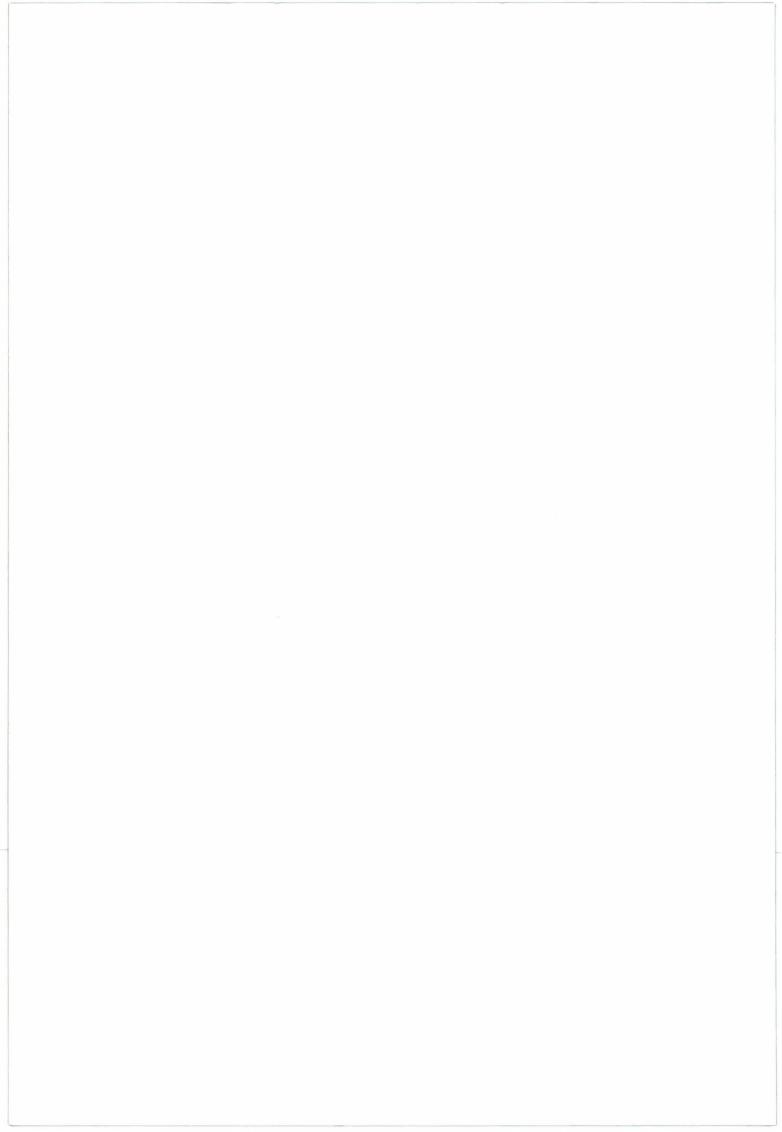

| III.1.2 Besoins d'une implantation ionique et d'un recuit à haute température  III.2 Procédé à grille en T existant à l'IEMN  III.2.1 Points clés du procédé à grille en T  III.2.2 Résultats et problèmes à résoudre  III.3.2 Caractéristiques de notre technologie  III.3.1 Axes de développement  III.3.2 Diagramme du procédé technologique  III.4.1 Importance de réussir le recuit d'implantation  III.4.1 Caractéristiques d'un recuit non réussi  III.4.2 Précautions à observer pour réussir le recuit  III.5.1 Description de la matrice élémentaire  III.5.2 Niveaux du masque FTFET  III.5.3 Description d'un transistor bi-doigts  III.5.4 Description de la matrice de test  III.6 Points clés du procédé  T9  Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  IV.1 Utilisation d'un métal réfractaire  IV.2 Choix du métal réfractaire  IV.2.1 Grille en WNx  IV.2.2 Grille en WSix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | III.1 Principes de la technologie auto-alignée                                    | 61 |

| température  III.2 Procédé à grille en T existant à l'IEMN  III.2.1 Points clés du procédé à grille en T  III.2.2 Résultats et problèmes à résoudre  III.3 Caractéristiques de notre technologie  III.3.1 Axes de développement  III.3.2 Diagramme du procédé technologique  III.4 Importance de réussir le recuit d'implantation  III.4.1 Caractéristiques d'un recuit non réussi  III.4.2 Précautions à observer pour réussir le recuit  III.5 Conception et dessin d'un jeu de masques FTFET  III.5.1 Description de la matrice élémentaire  III.5.2 Niveaux du masque FTFET  III.5.3 Description d'un transistor bi-doigts  III.5.4 Description de la matrice de test  III.6 Points clés du procédé  III.6 Points clés du procédé  T9  Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  81  IV.1 Utilisation d'un métal réfractaire  IV.2 Choix du métal réfractaire  IV.2 Choix du métal réfractaire  IV.2.1 Grille en WNx  IV.2.2 Grille en WSix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | III.1.1 Pourquoi une technologie auto-alignée?                                    | 61 |

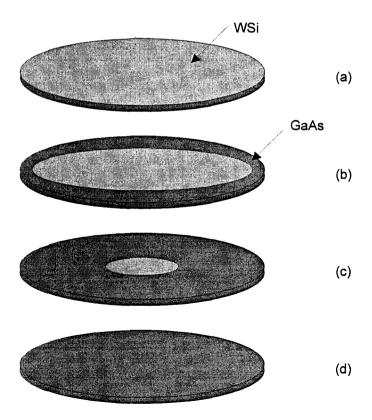

| III.2 Procédé à grille en T existant à l'IEMN  III.2.1 Points clés du procédé à grille en T  III.2.2 Résultats et problèmes à résoudre  III.3 Caractéristiques de notre technologie  III.3.1 Axes de développement  III.3.2 Diagramme du procédé technologique  III.4 Importance de réussir le recuit d'implantation  III.4.1 Caractéristiques d'un recuit non réussi  III.4.2 Précautions à observer pour réussir le recuit  III.5 Conception et dessin d'un jeu de masques FTFET  III.5.1 Description de la matrice élémentaire  III.5.2 Niveaux du masque FTFET  III.5.3 Description d'un transistor bi-doigts  III.5.4 Description de la matrice de test  III.6 Points clés du procédé  III.6 Points clés du procédé  Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  IV.1 Utilisation d'un métal réfractaire  IV.2 Choix du métal réfractaire  IV.2 Choix du métal réfractaire  IV.2 Grille en WNx  IV.2.2 Grille en WNx  82  IV.2.2 Grille en WSix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | III.1.2 Besoins d'une implantation ionique et d'un recuit à haute                 |    |

| III.2.1 Points clés du procédé à grille en T  III.2.2 Résultats et problèmes à résoudre  III.3 Caractéristiques de notre technologie  III.3.1 Axes de développement  III.3.2 Diagramme du procédé technologique  III.4 Importance de réussir le recuit d'implantation  III.4.1 Caractéristiques d'un recuit non réussi  III.4.2 Précautions à observer pour réussir le recuit  III.5 Conception et dessin d'un jeu de masques FTFET  III.5.1 Description de la matrice élémentaire  III.5.2 Niveaux du masque FTFET  III.5.3 Description d'un transistor bi-doigts  III.5.4 Description de la matrice de test  III.6 Points clés du procédé  III.6 Points clés du procédé  Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  81  IV.1 Utilisation d'un métal réfractaire  IV.2 Choix du métal réfractaire  IV.2 Choix du métal réfractaire  IV.2 Grille en WNx  IV.2.2 Grille en WNx  83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | température                                                                       | 62 |

| III.2.2 Résultats et problèmes à résoudre  III.3 Caractéristiques de notre technologie  III.3.1 Axes de développement  III.3.2 Diagramme du procédé technologique  III.4 Importance de réussir le recuit d'implantation  III.4.1 Caractéristiques d'un recuit non réussi  III.4.2 Précautions à observer pour réussir le recuit  III.5 Conception et dessin d'un jeu de masques FTFET  III.5.1 Description de la matrice élémentaire  III.5.2 Niveaux du masque FTFET  III.5.3 Description d'un transistor bi-doigts  III.5.4 Description de la matrice de test  III.6 Points clés du procédé  III.6 Points clés du procédé  T9  Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  81  IV.1 Utilisation d'un métal réfractaire  IV.2 Choix du métal réfractaire  IV.2 Choix du métal réfractaire  IV.2.1 Grille en WNx  IV.2.2 Grille en WSix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | III.2 Procédé à grille en T existant à l'IEMN                                     | 63 |

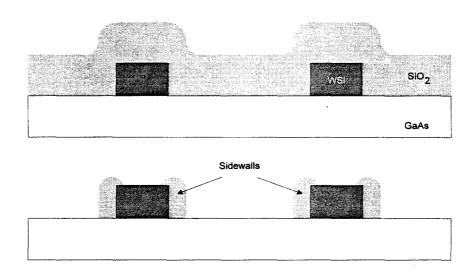

| III.3 Caractéristiques de notre technologie  III.3.1 Axes de développement  III.3.2 Diagramme du procédé technologique  66  III.4 Importance de réussir le recuit d'implantation  III.4.1 Caractéristiques d'un recuit non réussi  III.4.2 Précautions à observer pour réussir le recuit  70  III.5 Conception et dessin d'un jeu de masques FTFET  III.5.1 Description de la matrice élémentaire  72  III.5.2 Niveaux du masque FTFET  73  III.5.3 Description d'un transistor bi-doigts  III.5.4 Description de la matrice de test  76  III.6 Points clés du procédé  79  Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  81  IV.1 Utilisation d'un métal réfractaire  IV.2 Choix du métal réfractaire  IV.2.1 Grille en WNx  IV.2.2 Grille en WSix  83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | III.2.1 Points clés du procédé à grille en T                                      | 63 |

| III.3.1 Axes de développement  III.3.2 Diagramme du procédé technologique  III.4 Importance de réussir le recuit d'implantation  III.4.1 Caractéristiques d'un recuit non réussi  III.4.2 Précautions à observer pour réussir le recuit  III.5 Conception et dessin d'un jeu de masques FTFET  III.5.1 Description de la matrice élémentaire  III.5.2 Niveaux du masque FTFET  III.5.3 Description d'un transistor bi-doigts  III.5.4 Description de la matrice de test  III.6 Points clés du procédé  III.6 Points clés du procédé  Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  IV.1 Utilisation d'un métal réfractaire  IV.2 Choix du métal réfractaire  IV.2.1 Grille en WNx  IV.2.2 Grille en WSix  83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | III.2.2 Résultats et problèmes à résoudre                                         | 63 |

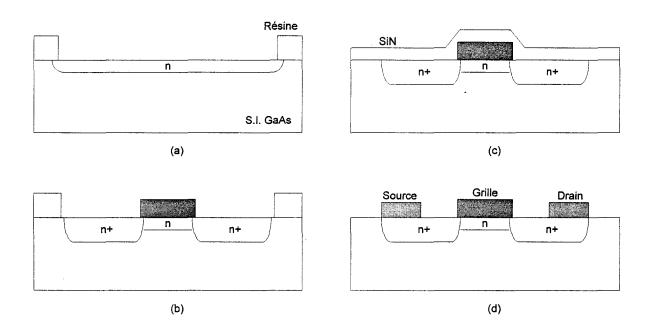

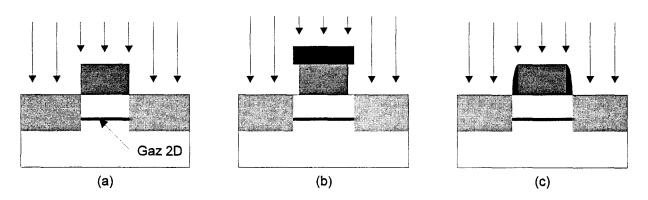

| III.3.2 Diagramme du procédé technologique  III.4 Importance de réussir le recuit d'implantation  III.4.1 Caractéristiques d'un recuit non réussi  III.4.2 Précautions à observer pour réussir le recuit  70  III.5 Conception et dessin d'un jeu de masques FTFET  III.5.1 Description de la matrice élémentaire  72  III.5.2 Niveaux du masque FTFET  73  III.5.3 Description d'un transistor bi-doigts  III.5.4 Description de la matrice de test  76  III.6 Points clés du procédé  79  Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  81  IV.1 Utilisation d'un métal réfractaire  IV.2 Choix du métal réfractaire  82  IV.2.1 Grille en WNx  1V.2.2 Grille en WSix  83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | III.3 Caractéristiques de notre technologie                                       | 64 |

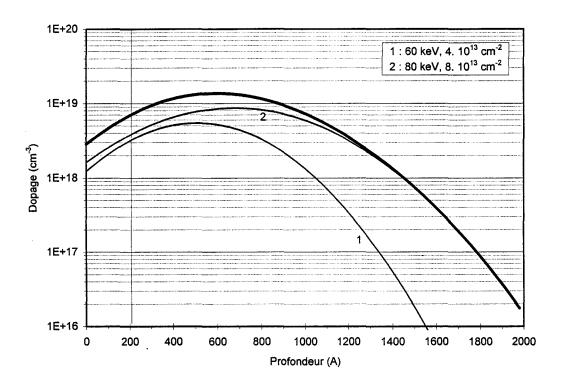

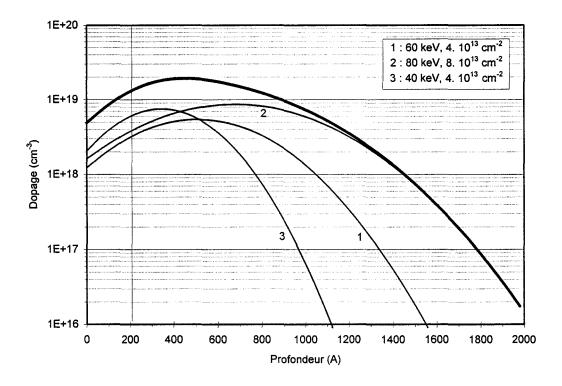

| III.4 Importance de réussir le recuit d'implantation  III.4.1 Caractéristiques d'un recuit non réussi  III.4.2 Précautions à observer pour réussir le recuit  70  III.5 Conception et dessin d'un jeu de masques FTFET  III.5.1 Description de la matrice élémentaire  III.5.2 Niveaux du masque FTFET  III.5.3 Description d'un transistor bi-doigts  III.5.4 Description de la matrice de test  III.6 Points clés du procédé  III.6 Points clés du procédé  Paibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  IV.1 Utilisation d'un métal réfractaire  IV.2 Choix du métal réfractaire  IV.2.1 Grille en WNx  IV.2.2 Grille en WSix  83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | III.3.1 Axes de développement                                                     | 64 |

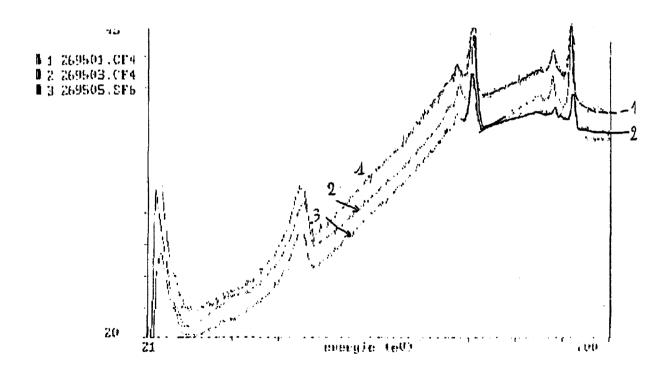

| III.4.1 Caractéristiques d'un recuit non réussi III.4.2 Précautions à observer pour réussir le recuit 70 III.5 Conception et dessin d'un jeu de masques FTFET 71 III.5.1 Description de la matrice élémentaire 72 III.5.2 Niveaux du masque FTFET 73 III.5.3 Description d'un transistor bi-doigts 75 III.5.4 Description de la matrice de test 76 III.6 Points clés du procédé 79 Bibliographie 80 CHAPITRE IV : Formation de la grille réfractaire des HIGFETs 81 IV.1 Utilisation d'un métal réfractaire 82 IV.2 Choix du métal réfractaire 83 IV.2.1 Grille en WNx 84 IV.2.2 Grille en WSix 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | III.3.2 Diagramme du procédé technologique                                        | 66 |

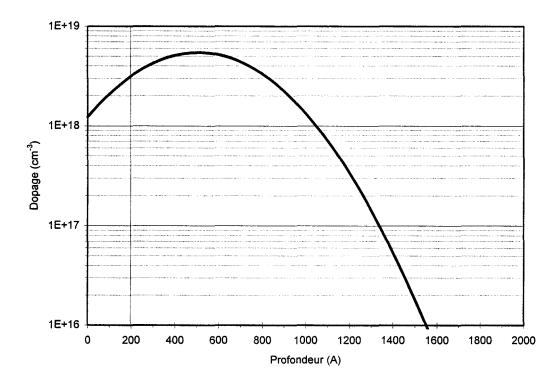

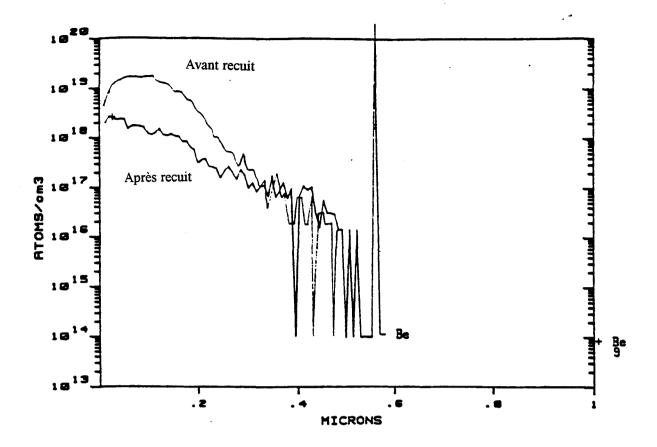

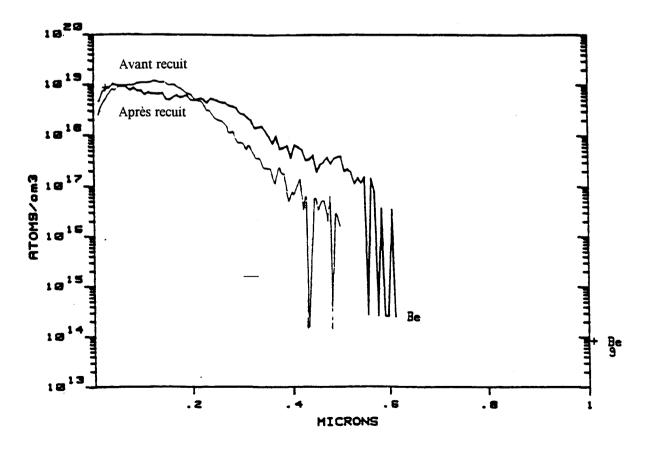

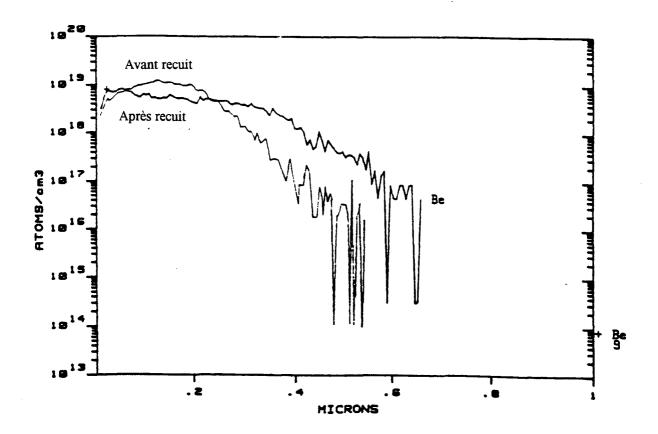

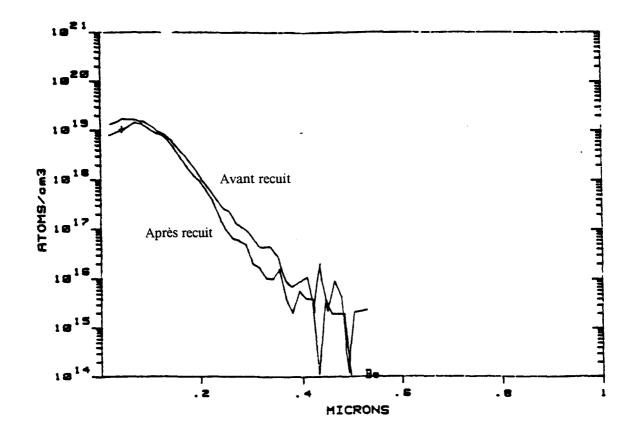

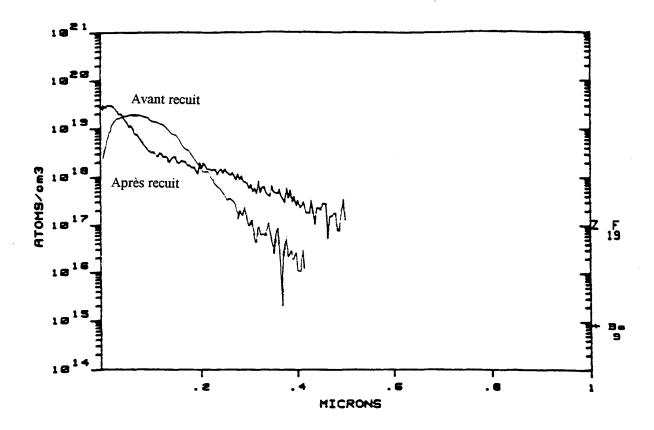

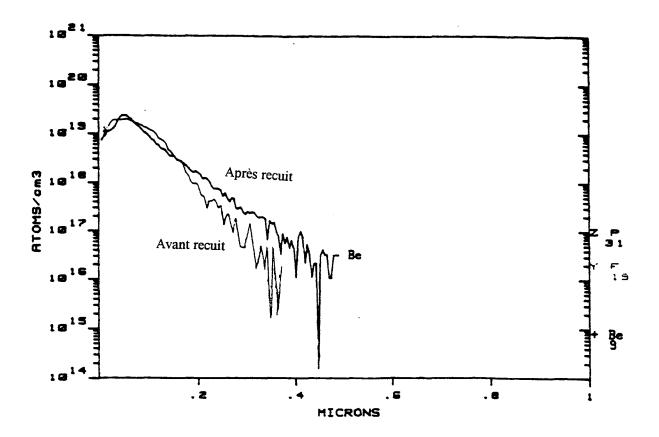

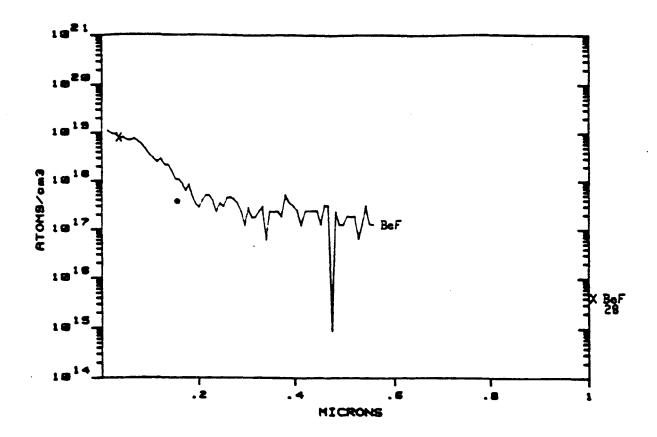

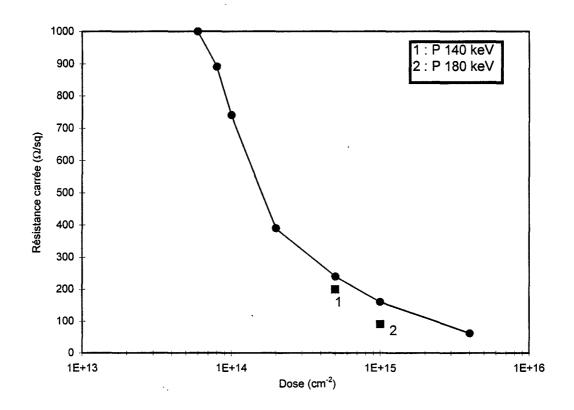

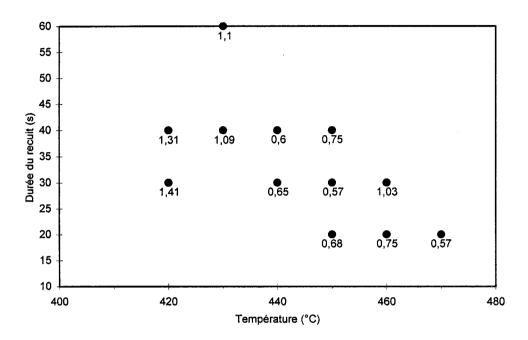

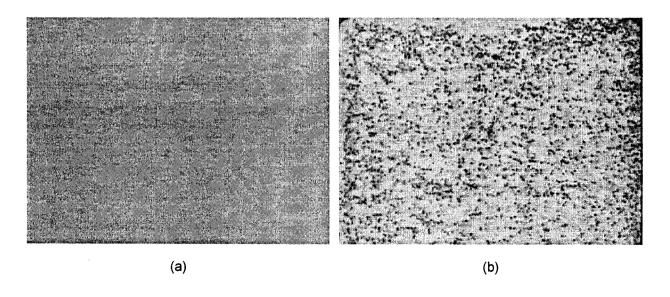

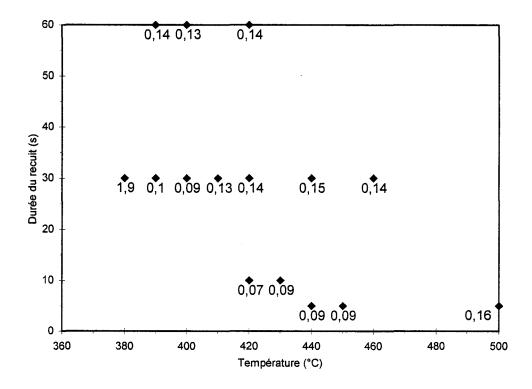

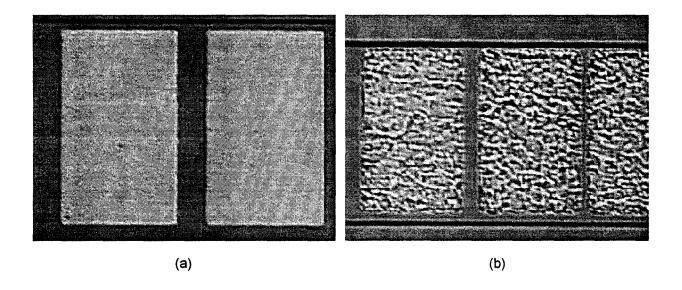

| III.4.2 Précautions à observer pour réussir le recuit  III.5 Conception et dessin d'un jeu de masques FTFET  III.5.1 Description de la matrice élémentaire  III.5.2 Niveaux du masque FTFET  III.5.3 Description d'un transistor bi-doigts  III.5.4 Description de la matrice de test  III.6 Points clés du procédé  III.6 Points clés du procédé  Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  IV.1 Utilisation d'un métal réfractaire  IV.2 Choix du métal réfractaire  IV.2.1 Grille en WNx  IV.2.2 Grille en WSix  83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | III.4 Importance de réussir le recuit d'implantation                              | 68 |

| III.5 Conception et dessin d'un jeu de masques FTFET  III.5.1 Description de la matrice élémentaire  III.5.2 Niveaux du masque FTFET  III.5.3 Description d'un transistor bi-doigts  III.5.4 Description de la matrice de test  III.6 Points clés du procédé  Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  IV.1 Utilisation d'un métal réfractaire  IV.2 Choix du métal réfractaire  IV.2.1 Grille en WNx  IV.2.2 Grille en WSix  83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | III.4.1 Caractéristiques d'un recuit non réussi                                   | 68 |

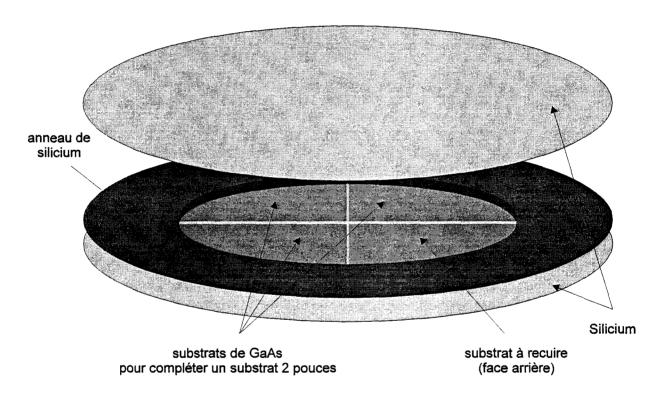

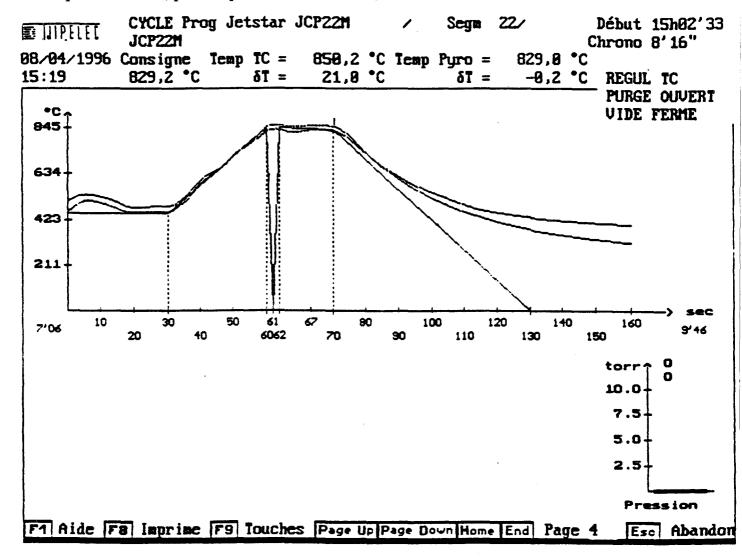

| III.5.1 Description de la matrice élémentaire  III.5.2 Niveaux du masque FTFET  III.5.3 Description d'un transistor bi-doigts  III.5.4 Description de la matrice de test  III.6 Points clés du procédé  Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  IV.1 Utilisation d'un métal réfractaire  IV.2 Choix du métal réfractaire  IV.2.1 Grille en WNx  IV.2.2 Grille en WSix  83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | III.4.2 Précautions à observer pour réussir le recuit                             | 70 |

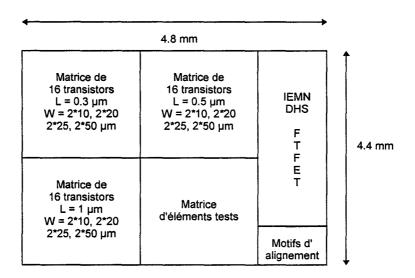

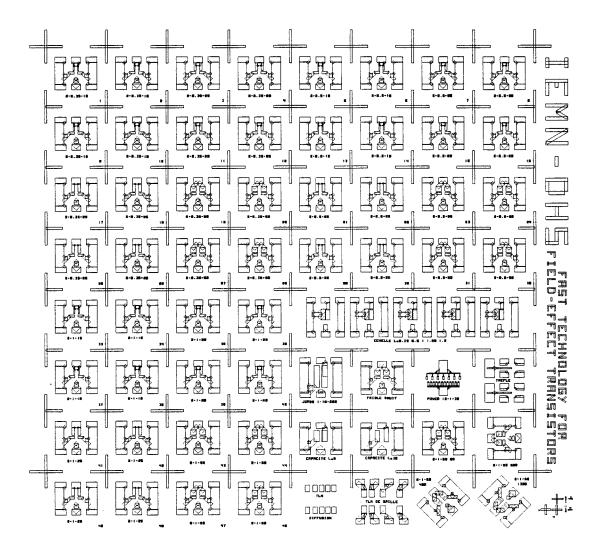

| III.5.2 Niveaux du masque FTFET  III.5.3 Description d'un transistor bi-doigts  III.5.4 Description de la matrice de test  III.6 Points clés du procédé  Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  IV.1 Utilisation d'un métal réfractaire  IV.2 Choix du métal réfractaire  IV.2.1 Grille en WNx  IV.2.2 Grille en WSix  73  73  73  74  75  75  76  76  77  78  78  78  79  80  81  81  81  81  81  82  83  83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | III.5 Conception et dessin d'un jeu de masques FTFET                              | 71 |

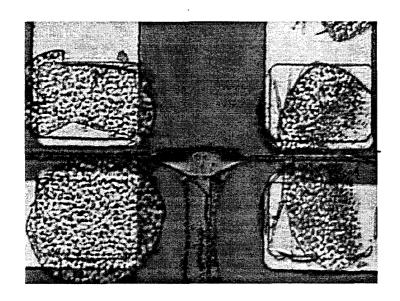

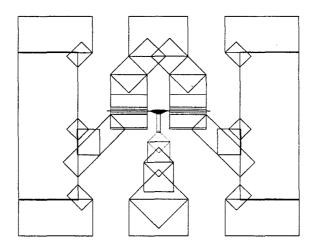

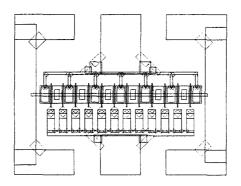

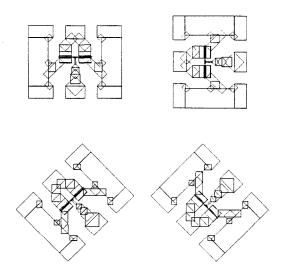

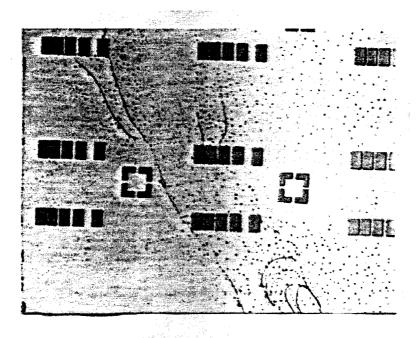

| III.5.3 Description d'un transistor bi-doigts III.5.4 Description de la matrice de test 76 III.6 Points clés du procédé 80 CHAPITRE IV : Formation de la grille réfractaire des HIGFETs 81 IV.1 Utilisation d'un métal réfractaire IV.2 Choix du métal réfractaire IV.2.1 Grille en WNx IV.2.2 Grille en WSix 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | III.5.1 Description de la matrice élémentaire                                     | 72 |

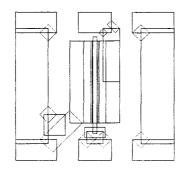

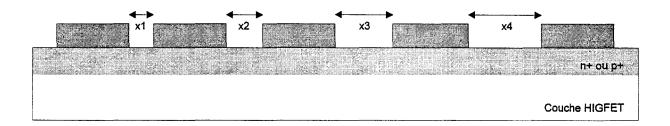

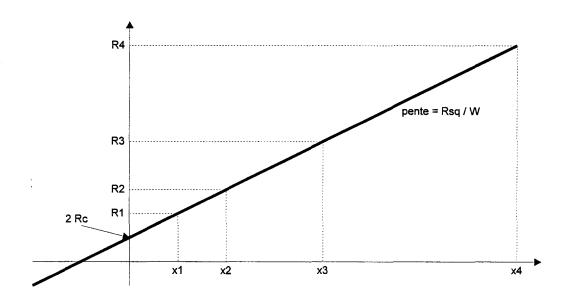

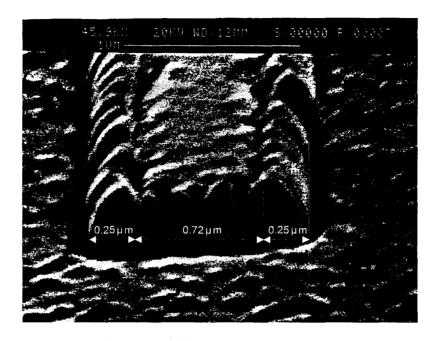

| III.5.4 Description de la matrice de test  III.6 Points clés du procédé Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  IV.1 Utilisation d'un métal réfractaire IV.2 Choix du métal réfractaire IV.2.1 Grille en WNx IV.2.2 Grille en WSix  76  78  89  80  81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | III.5.2 Niveaux du masque FTFET                                                   | 73 |

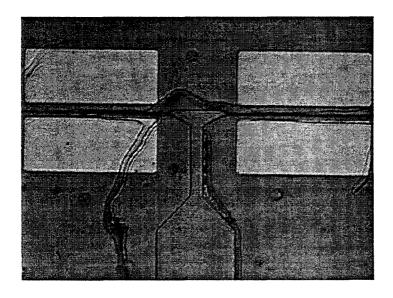

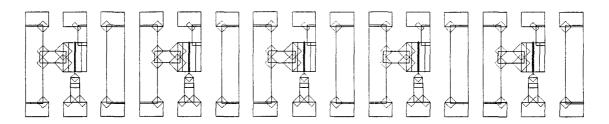

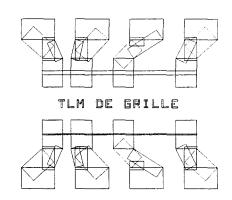

| III.6 Points clés du procédé Bibliographie  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs  IV.1 Utilisation d'un métal réfractaire IV.2 Choix du métal réfractaire IV.2.1 Grille en WNx IV.2.2 Grille en WSix  79 80 81 81 82 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | III.5.3 Description d'un transistor bi-doigts                                     | 75 |

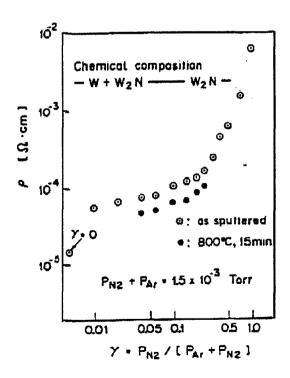

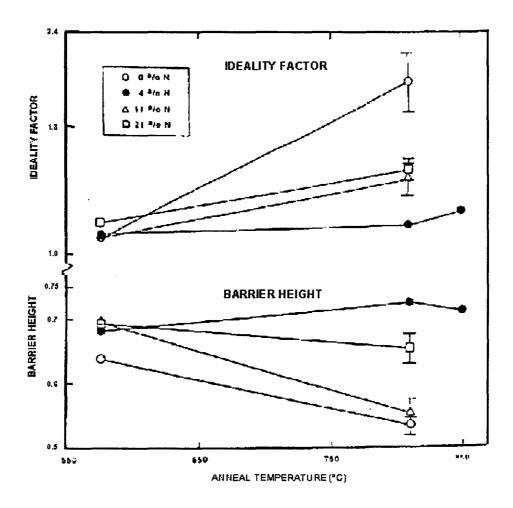

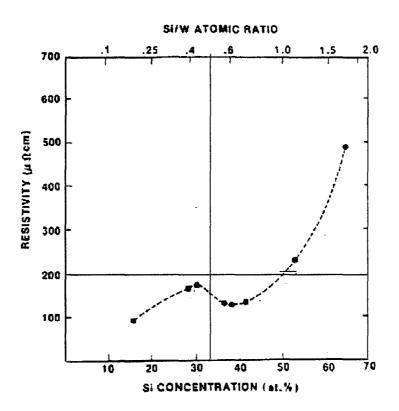

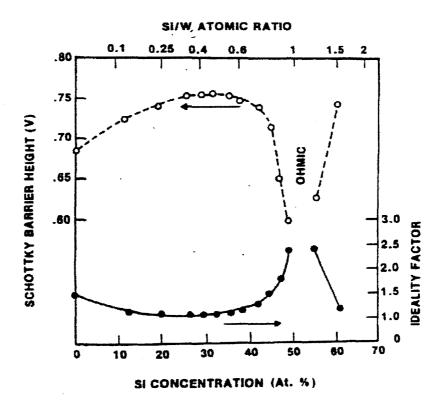

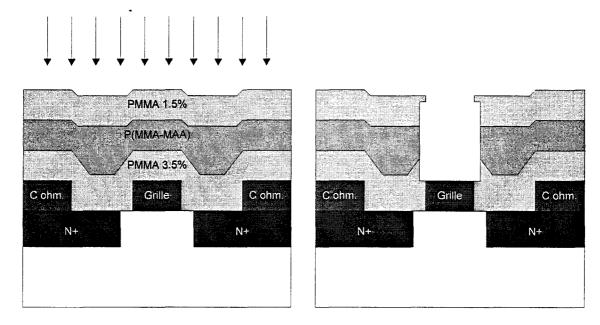

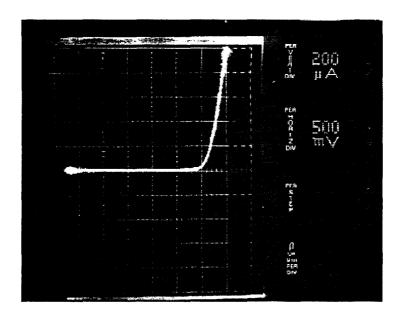

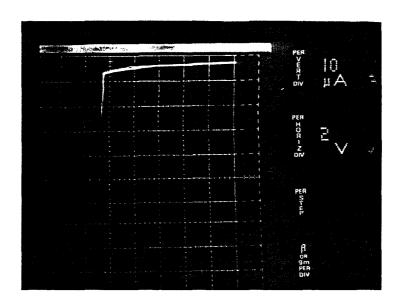

| Bibliographie 80  CHAPITRE IV : Formation de la grille réfractaire des HIGFETs 81  IV.1 Utilisation d'un métal réfractaire 81  IV.2 Choix du métal réfractaire 82  IV.2.1 Grille en WNx 82  IV.2.2 Grille en WSix 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | III.5.4 Description de la matrice de test                                         | 76 |