#### THESE

présentée à

L'Université des Sciences et Techniques de Lille Flandres-Artois

pour obtenir le grade de

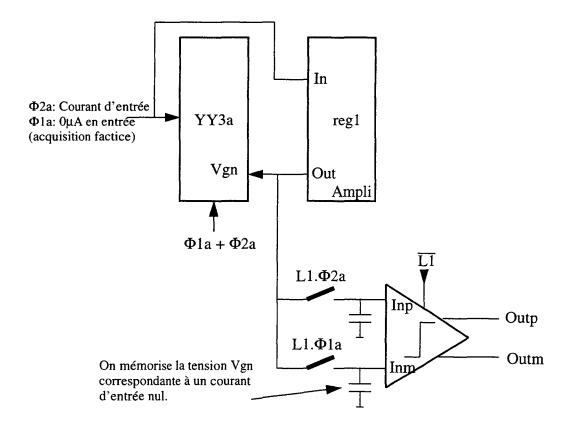

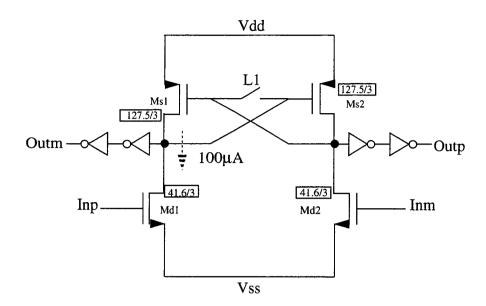

Docteur en Electronique

par

**Nicolas MOENECLAEY**

# CONVERTISSEURS ANALOGIQUES-NUMERIQUES A HAUTE RESOLUTION UTILISANT LA TECHNIQUE DES MEMOIRES DE COURANT

soutenue le 9 Septembre 1996, devant la commission d'examen:

Président:

E. CONSTANT

Rapporteurs:

W. REDMAN-WHITE

M. DECLERCQ

Examinateurs:

D. BILLET

Y. LEDUC

J.-N. DECARPIGNY

A. KAISER

à Sylvie à mon père et à ma mère à toute ma famille à mes amis Je remercie vivement Monsieur le Professeur Eugène CONSTANT d'avoir accepté la présidence de ce Jury.

Je tiens à adresser mes sincères remerciements à Monsieur William REDMAN-WHITE ainsi qu'à Monsieur la professeur Michel DECLERCQ pour le travail de rapporteur de thèse qu'ils ont accompli.

Monsieur le professeur Jean-Noël DECARPIGNY a accepté d'être mon directeur de thèse, je souhaite l'en remercier. Ce travail de thèse n'aurait pas été possible sans la précieuse aide de Messieurs Daniel BILLET et Thierry TORTELIER. Je les remercie pour leur précieuse collaboration.

Je tiens à remercier Messieurs Philippe N'GORAN et Andréas KAISER. Le simulateur à temps discret de circuits à mémoire de courant qu'ils ont mis au point a été un outil indispensable à la réalisation du convertisseur.

Monsieur le Professeur Andréas KAISER m'a accueilli au sein de l'équipe de recherche du département Electronique, il m'a guidé et a fortement contribué au travail accompli au cours de ces trois années passées à l'I.S.E.N. Je tiens donc tout particulièrement à lui exprimer ma profonde reconnaissance.

Je remercie aussi tout le personnel du laboratoire de micro-électronique de l'I.E.M.N.-département I.S.E.N. et tout particulièrement Messieurs Bruno STEFANELLI et Ian O'CONNOR pour leur précieuse aide dans le dessin du convertisseur, ainsi que Monsieur Jean-Michel DROULEZ pour son aide au cours du test des deux circuits.

Enfin un grand merci à Monsieur Yves LEDUC pour son aide et ses encouragements lors de la rédaction de ce manuscrit.

### INTRODUCTION CHAPITRE 1

| 1.1 La cellule à mémoire de courant                                   | 2  |

|-----------------------------------------------------------------------|----|

| 1.1.1 Principe de fonctionnement                                      | 2  |

| 1.1.2 Principaux effets limitatifs et leur caractérisation            | 2  |

| 1.1.2.1 L'injection de charge                                         | 3  |

| 1.1.2.2 conductance de sortie                                         | 4  |

| 1.1.2.3 Erreur de stabilisation                                       | 5  |

| 1.2 Modélisation temporelle de la cellule à mémoire de courant        | 6  |

| 1.2.1 Modèle petit signal classique                                   | 6  |

| 1.2.2 Modélisation approfondie de la cellule                          | 9  |

| 1.2.2.1 Modélisation de la caractéristique du transistor mémoire      | 10 |

| 1.2.2.2 Modélisation de la cellule à mémoire de courant               | 11 |

| 1.2.3 Influence du timing et de l'environnement de la cellule.        | 14 |

| 1.2.4 Modèle complet                                                  | 16 |

| 1.3 Validation numérique du modèle                                    | 19 |

| 1.4 Références bibliographiques                                       | 22 |

| CHAPITRE 2                                                            |    |

| 2.1 Méthodologie de caractérisation des Cellules à Mémoire de Courant | 24 |

| 2.1.1 Topologie du circuit de caractérisation                         | 24 |

| 2.1.2 Caractéristiques mesurées                                       | 25 |

| 2.1.2.1 Comportement transitoire de la cellule                        | 25 |

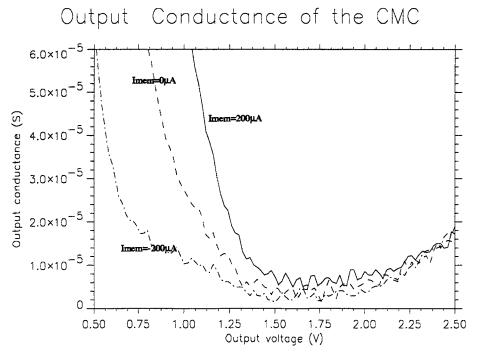

| 2.1.2.2 Conductance de sortie                                         | 26 |

| 2.1.2.3 L'erreur de recopie                                           | 27 |

| 2.1.2.4 la charge injectée par l'interrupteur d'échantillonnage.      | 28 |

| 2.2 Présentation de la manipulation et du circuit de test             | 29 |

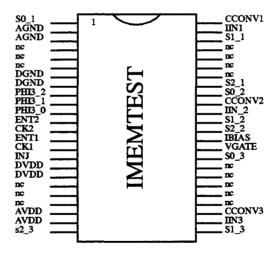

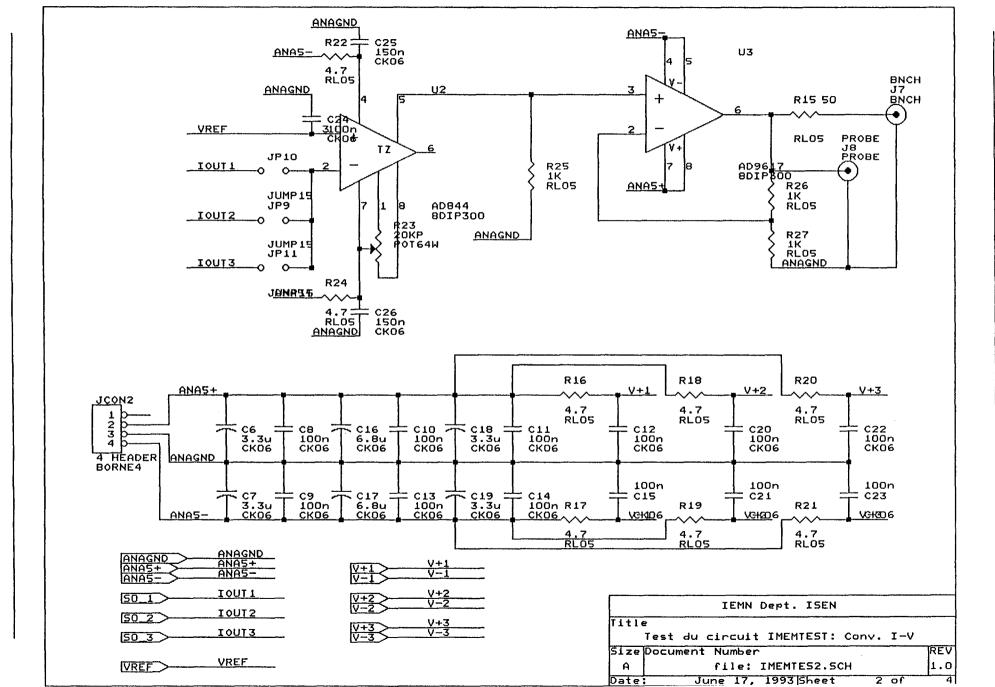

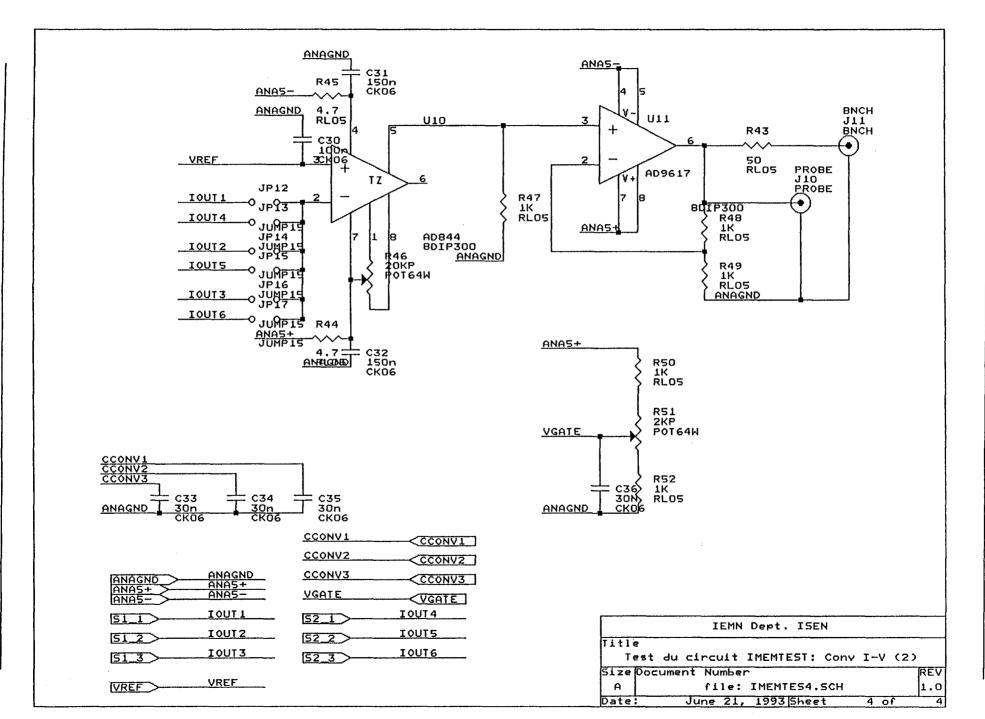

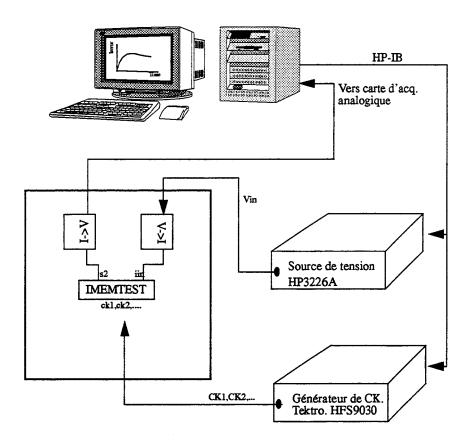

| 2.2.1 Circuit de caractérisation IMEMTEST                             | 29 |

| 2.2.2 Manipulation de test                                            | 33 |

| 2.3 Résultats de mesure et validation expérimentale                   | 40 |

| 2.3.1 Mesure du comportement transitoire et validation du modèle      | 40 |

| 2.3.2 Mesure de la conductance de sortie.                             | 41 |

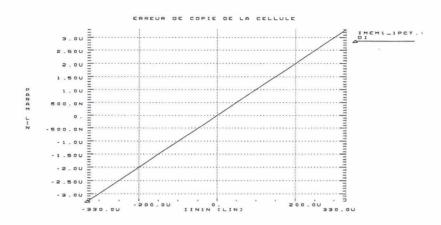

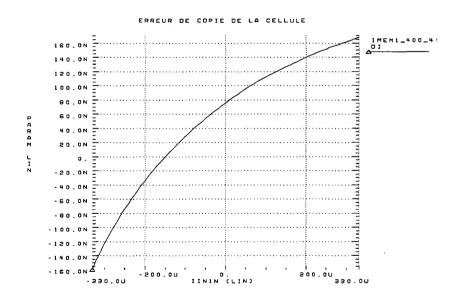

| 2.3.3 Mesure de l'erreur de copie                                     | 43 |

| 2.3.4 Caractérisation de l'injection de charge                        | 44 |

| 2.4 Références bibliographiques                                       | 48 |

| CHAPITRE 3                                                            |    |

| 3.1 Introduction                                                      | 50 |

| 3.1.1 Principes de la modulation sigma-delta                          | 50 |

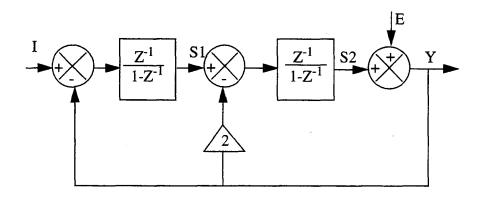

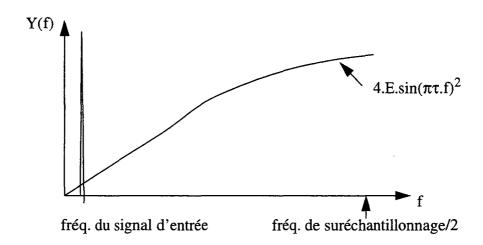

| 3.1.1.1 Fonctionnement du modulateur                                  | 50 |

| 3.1.1.2 Calcul approché de la fonction de transfert                   | 51 |

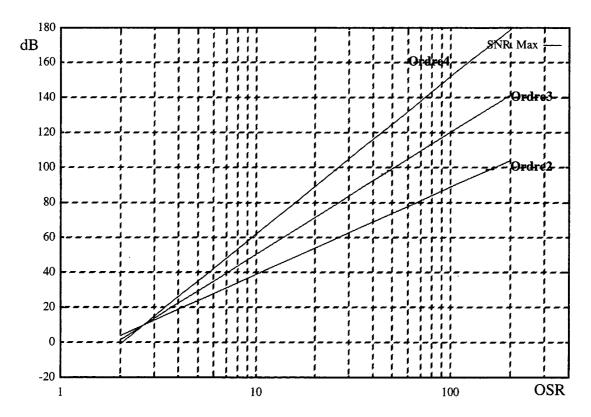

| 3.1.2 Performances du modulateur                                      | 54 |

| 3.1.2.1 Calcul du rapport signal sur bruit                                      | 54        |

|---------------------------------------------------------------------------------|-----------|

| 3.1.2.2 choix du modulateur                                                     | 54        |

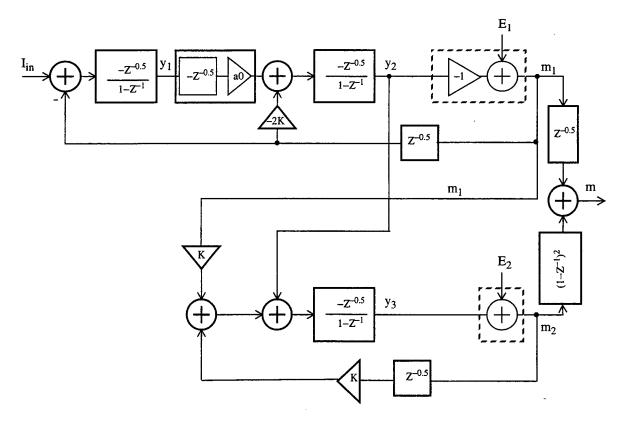

| 3.2 Modulateur sigma-delta d'ordre 2 en mode courant                            | 56        |

| 3.3 Modulateur sigma-delta d'ordre 3 en mode courant                            | 59        |

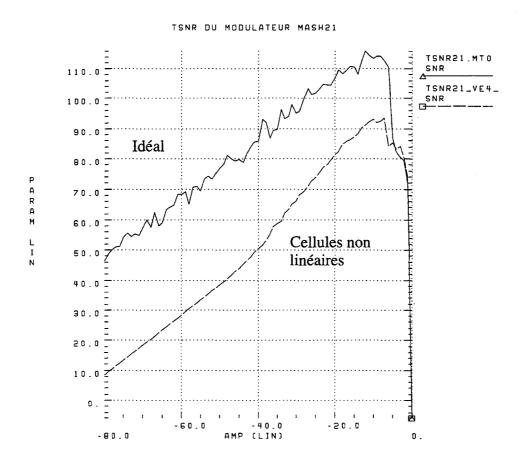

| 3.4 Influence des limitations de la cellule sur le M.A.S.H.21                   | 61        |

| 3.4.1 Dimensionnement des intégrateurs                                          | 61        |

| 3.4.2 Influence du gain de la cellule sur le comportement du modulateur         | 62        |

| 3.4.2.1 Cellule ayant un gain de 1                                              | 62        |

| 3.4.2.2 Cellule ayant une erreur linéaire (1%)                                  | 63        |

| 3.4.2.3 Cellule ayant une erreur quadratique                                    | 64        |

| 3.4.3 Sensibilité aux forts signaux                                             | 65        |

| 3.4.4 Evaluation du T.S.N.R.                                                    | 66        |

| 3.5 Modification de la structure du modulateur dans le but d'abaisser la con    | sommation |

|                                                                                 | 69        |

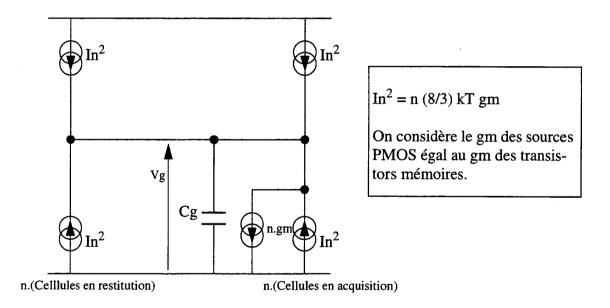

| 3.5.1 Forte consommation lié au bruit thermique des transistors                 | 69        |

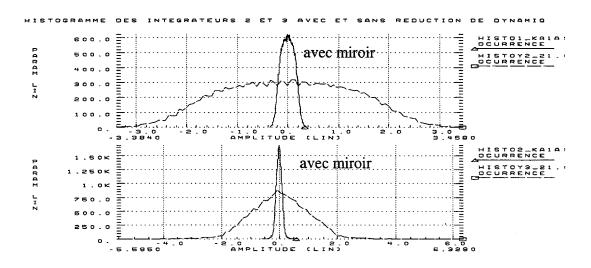

| 3.5.2 Limitation de la consommation par la division du signal dans la structure | 71        |

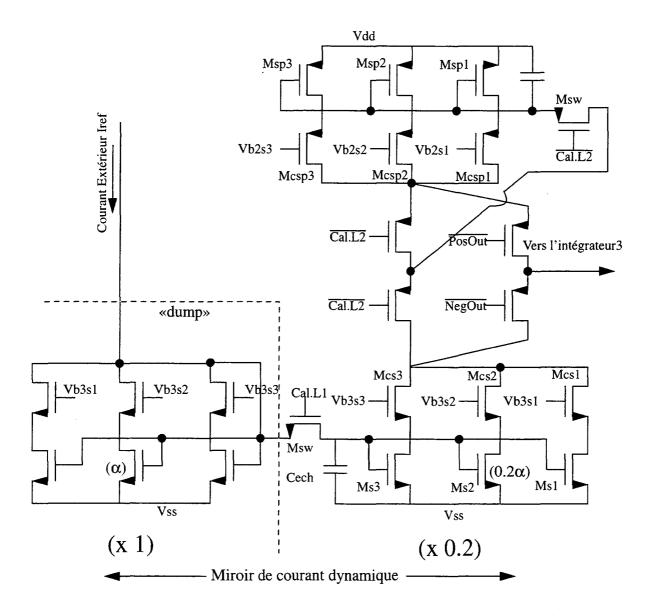

| 3.5.2.1 Utilisation de 2 miroirs de courant                                     | 71        |

| 3.5.2.2 Utilisation d'un seul miroir                                            | 73        |

| 3.6 Références                                                                  | 76        |

| CHAPITRE 4                                                                      |           |

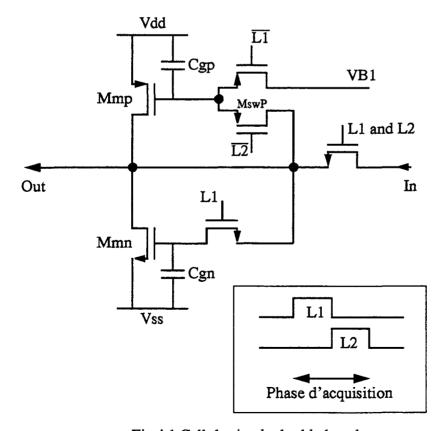

| 4.1 Principe de la cellule                                                      | 78        |

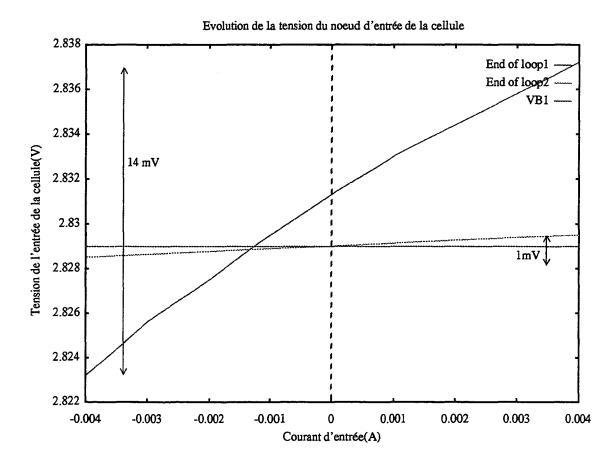

| 4.1.1 Cellule double boucle                                                     | 78        |

| 4.1.2 Régulation lors de la première boucle                                     | 79        |

| 4.1.3 Cellule proposée                                                          | 80        |

| 4.2 Mise en oeuvre de la cellule                                                | 83        |

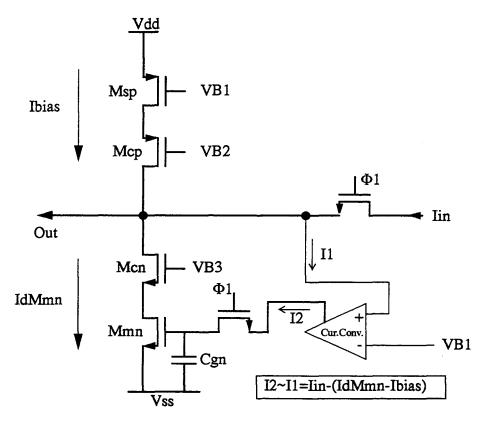

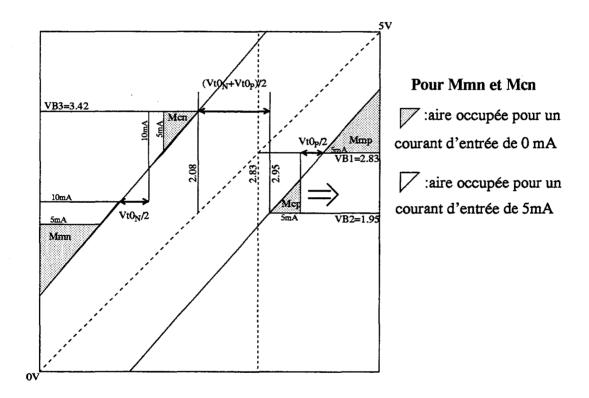

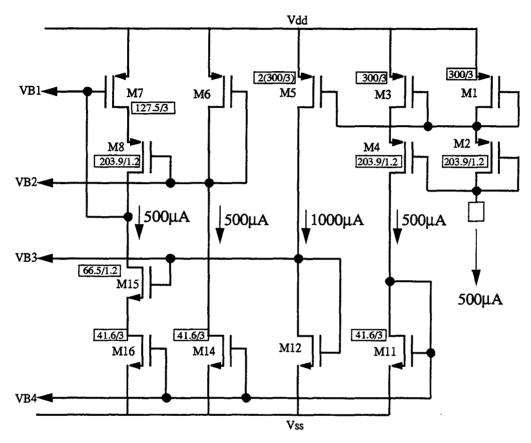

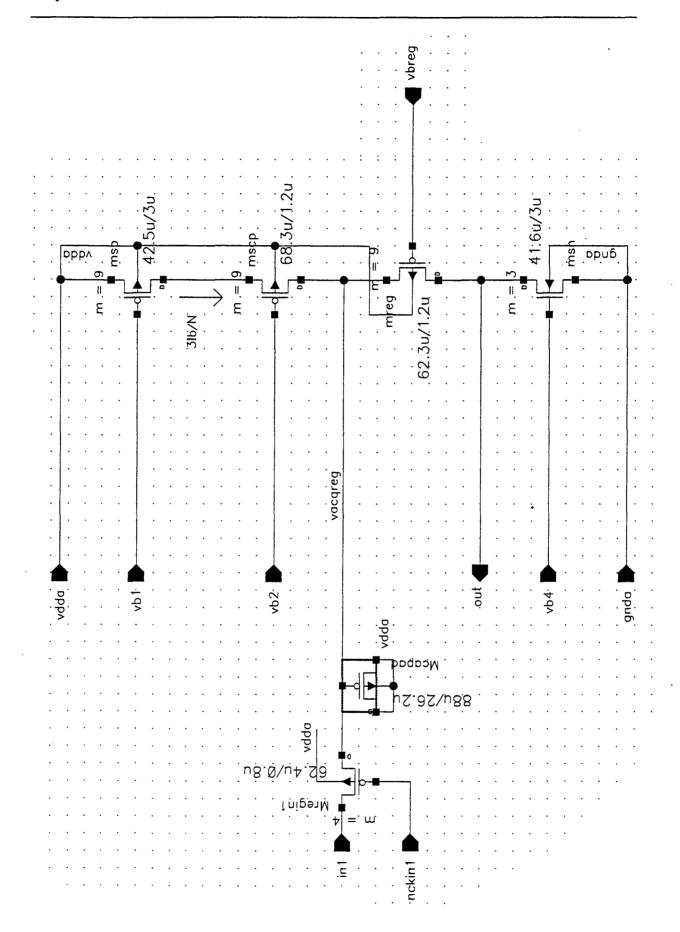

| 4.2.1 Polarisation de la cellule                                                | 84        |

| 4.2.1.1 Dimensionnement de la cellule                                           | 84        |

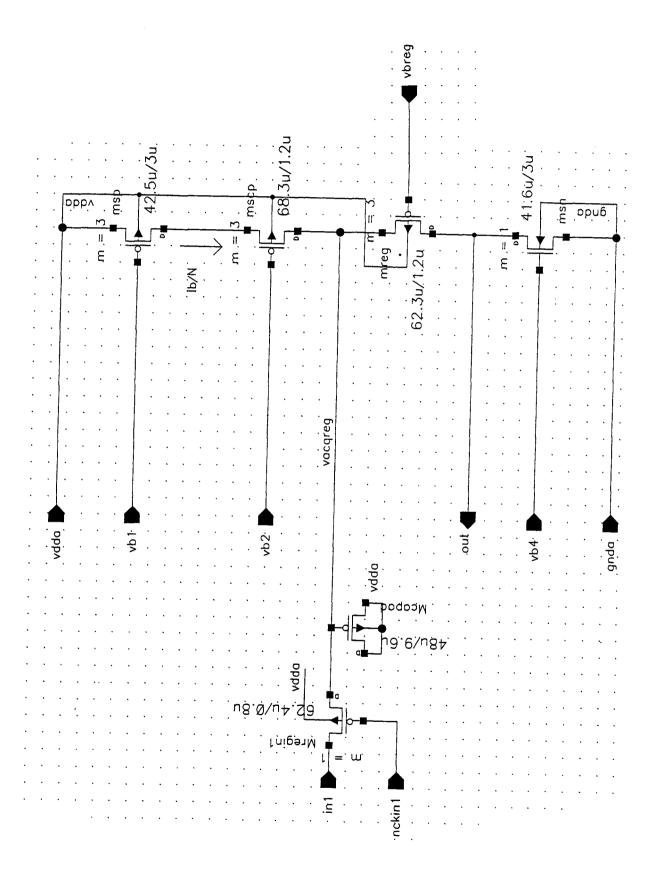

| 4.2.1.2 Circuit de polarisation de la cellule                                   | 87        |

| 4.2.1.3 Dimensionnement du convoyeur de courant                                 | 88        |

| 4.2.1.4 Polarisation du convoyeur de courant                                    | 91        |

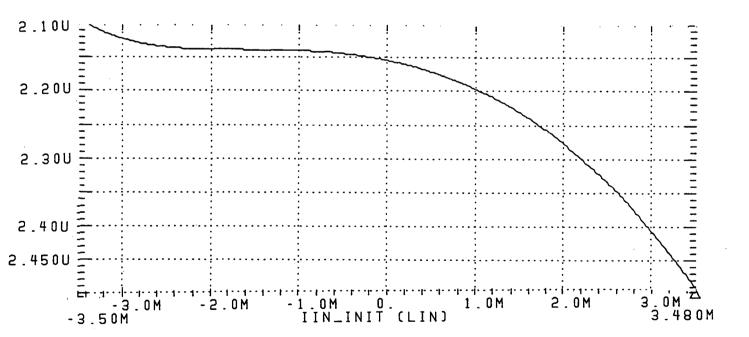

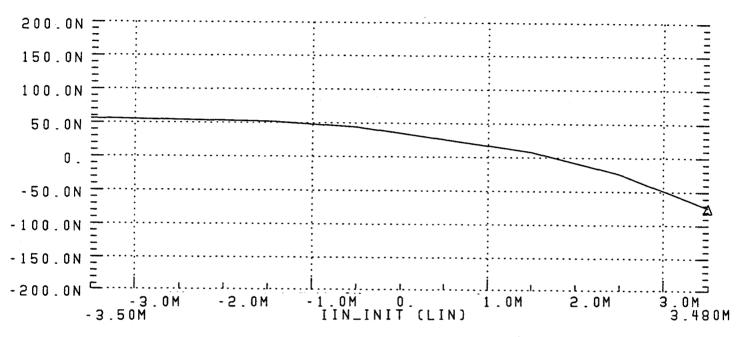

| 4.2.2 Etude statique du gain                                                    | 92        |

| 4.2.3 Etude de la cellule en transitoire                                        | 95        |

| 4.2.4 Bruit de la cellule                                                       | 98        |

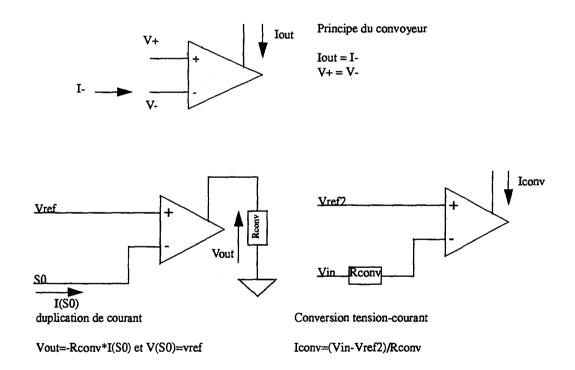

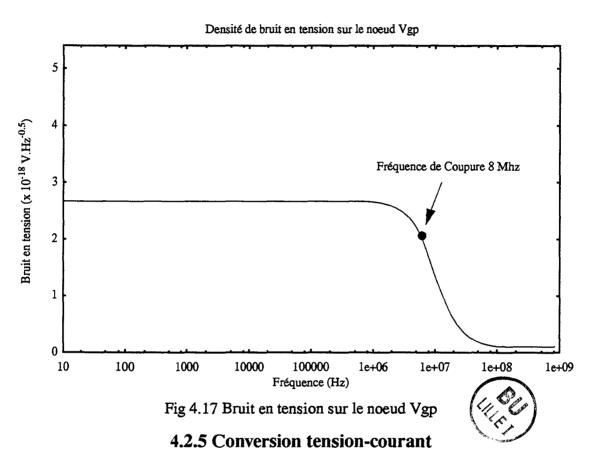

| 4.2.5 Conversion tension-courant                                                | 99        |

| 4.3 Références                                                                  | 101       |

| CHAPITRE 5                                                                      |           |

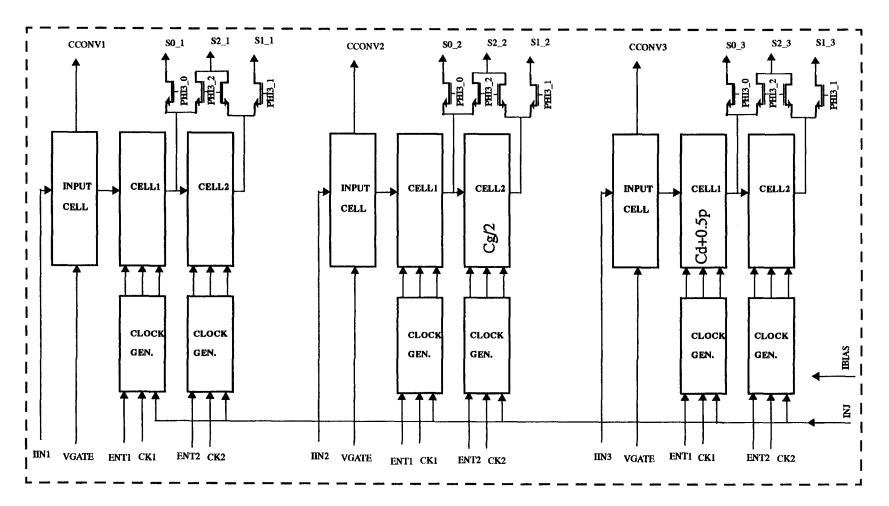

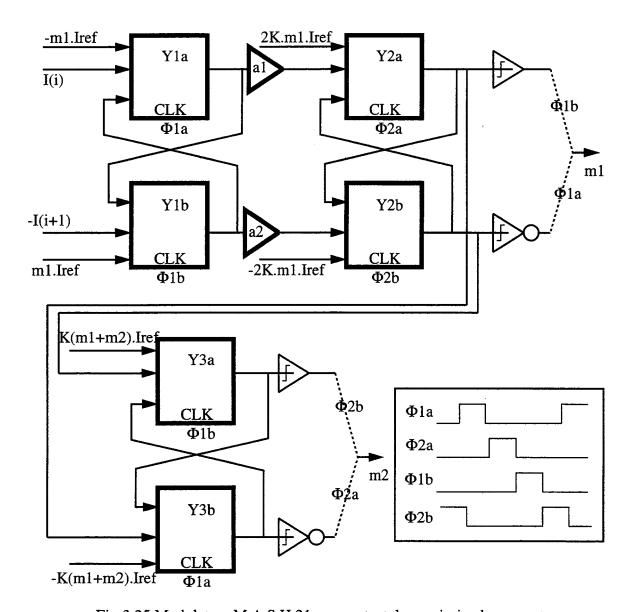

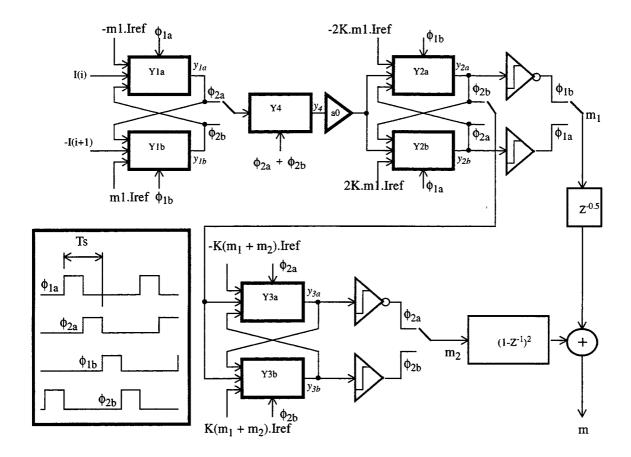

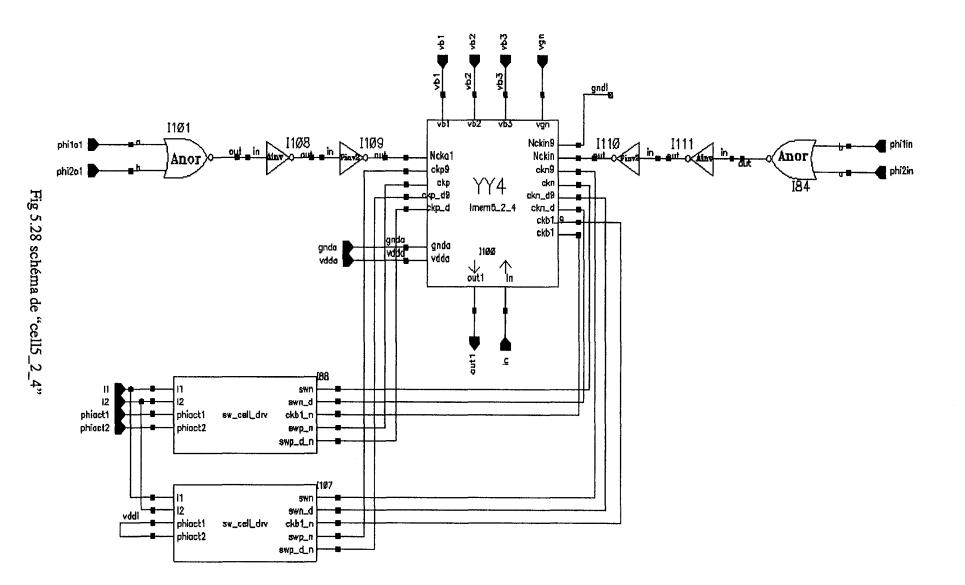

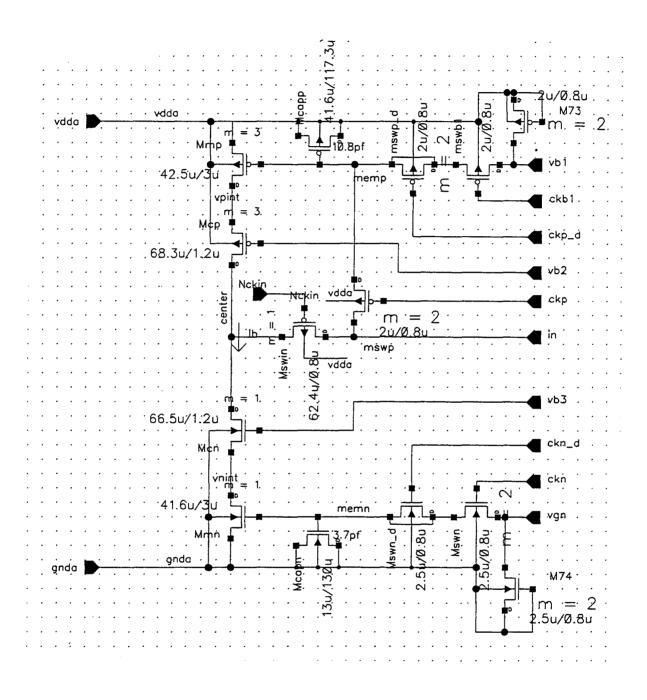

| 5.1 Modulateur réalisé                                                          | 104       |

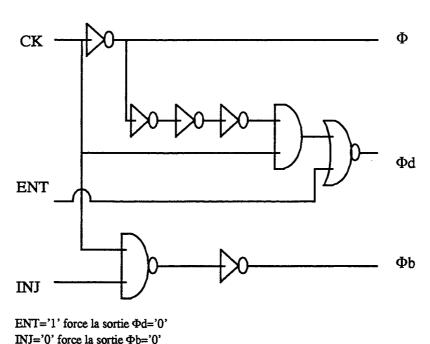

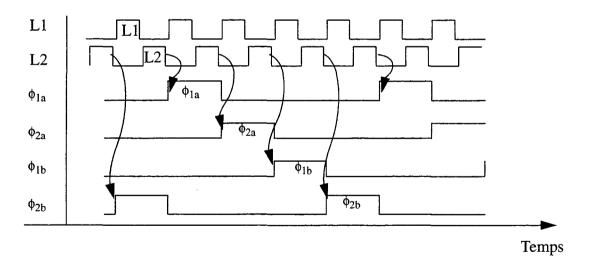

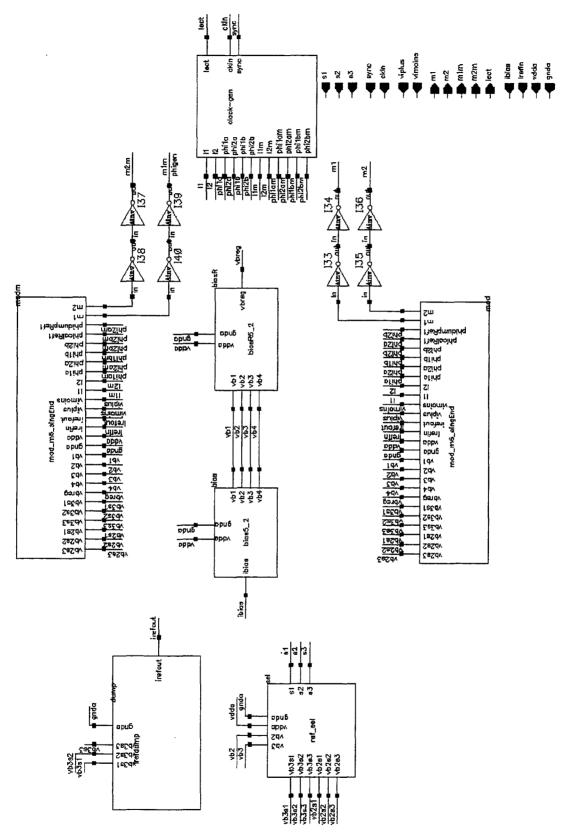

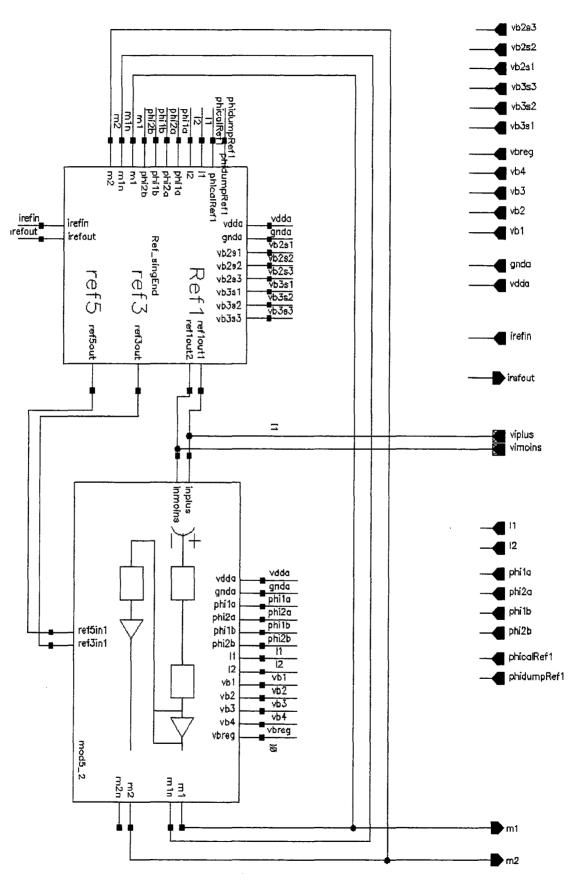

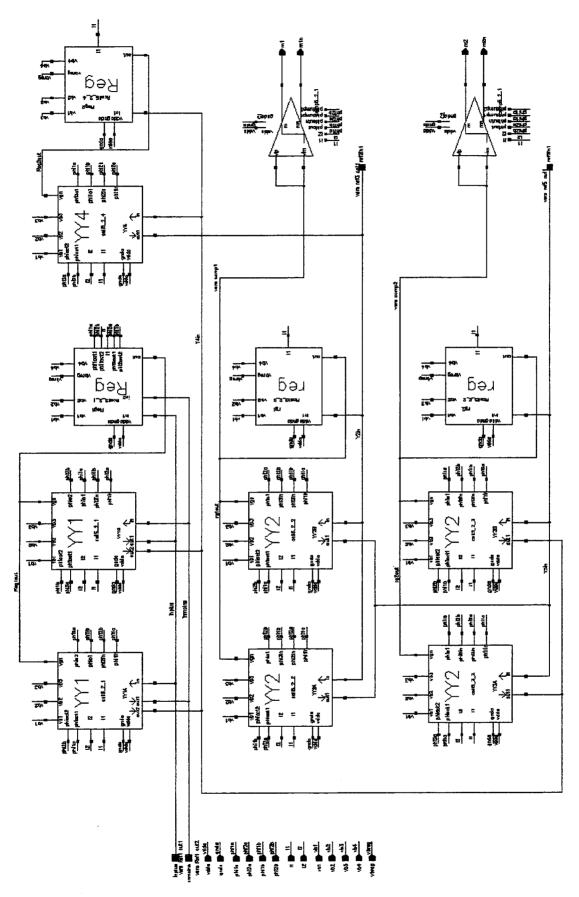

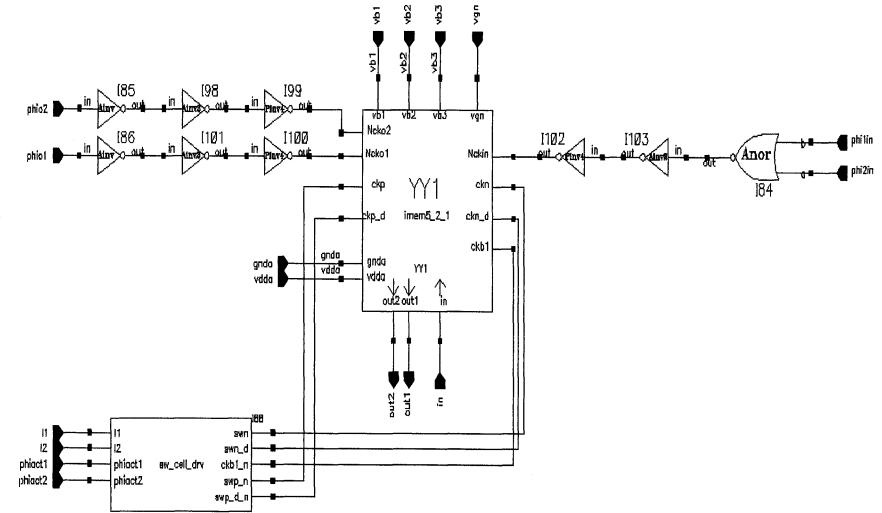

| 5.1.1 Schéma du modulateur                                                      | 105       |

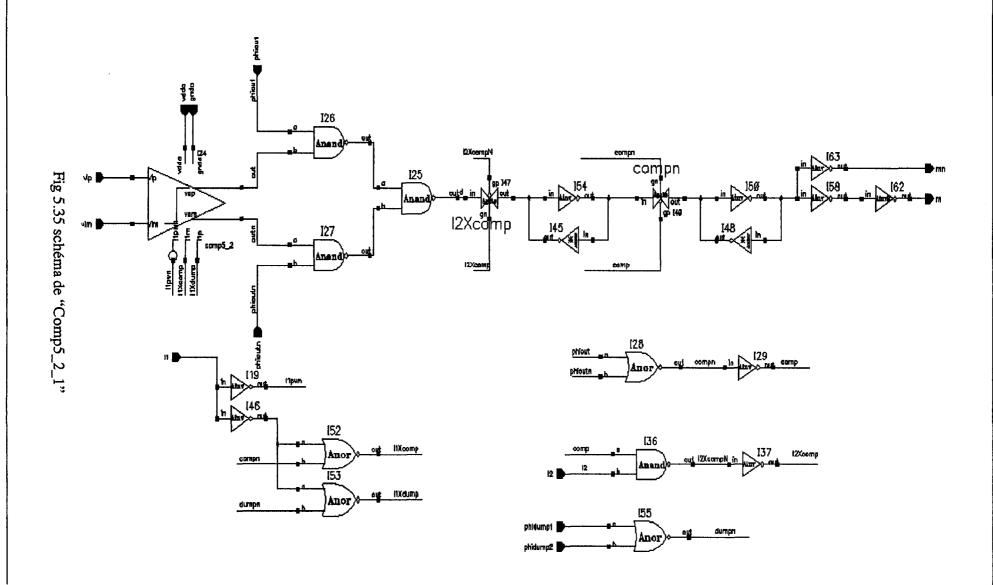

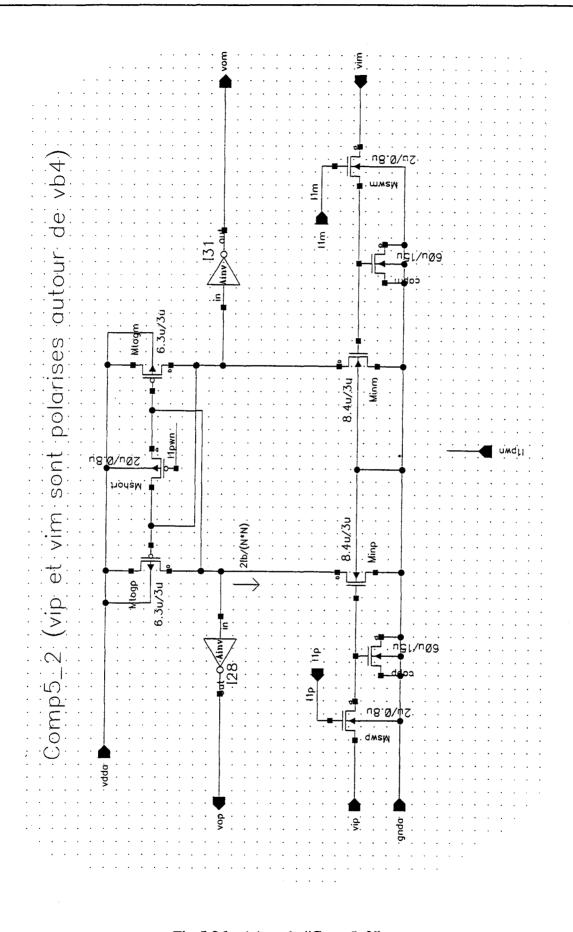

| 5.1.2 Fonctionnement du comparateur                                             | 107       |

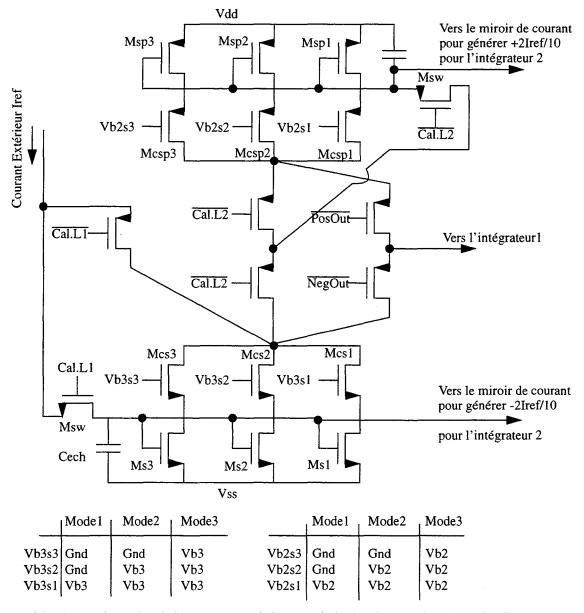

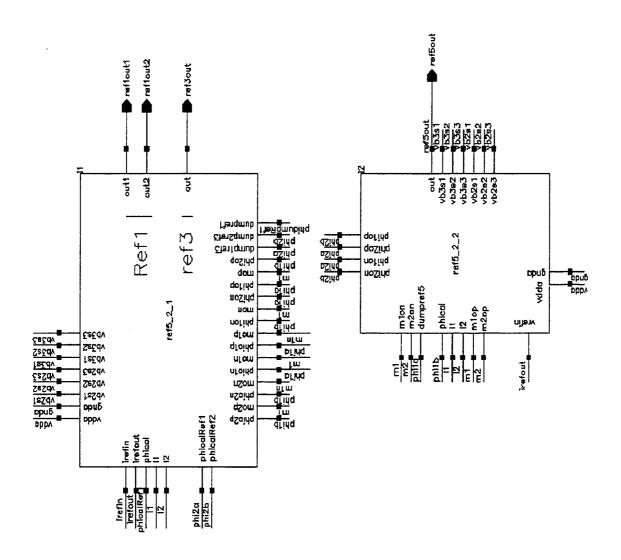

| 5.1.3 Génération des courants de référence                                      | 107       |

|                                                                                 | 113       |

| 5.2 Simulation des performances du modulateur                                   | 113       |

| 5.2.1 Modélisation de la cellule                                          | 113 |

|---------------------------------------------------------------------------|-----|

| 5.2.2 Validation des performances du circuit                              | 114 |

| 5.3 Simulation électrique                                                 | 117 |

| 5.3.1 Génération des courants de référence                                | 117 |

| 5.3.2 Test du comparateur                                                 | 118 |

| 5.3.3 Simulation du comportement transitoire sur 100 périodes             | 118 |

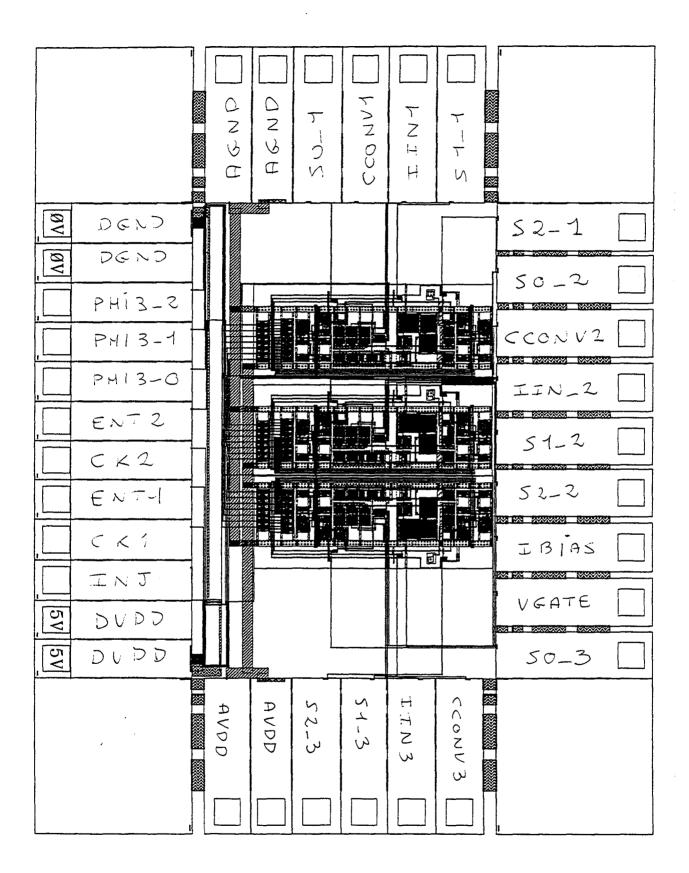

| 5.4 Layout du circuit                                                     | 120 |

| 5.5 Annexe: schéma électrique du circuit                                  | 124 |

| CHAPITRE 6                                                                |     |

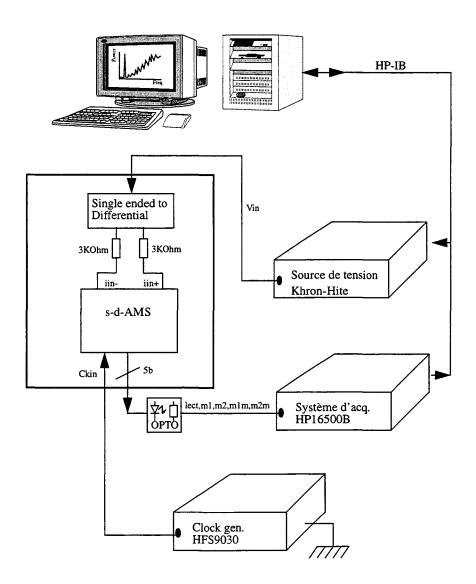

| 6.1 Manipulation de test                                                  | 150 |

| 6.2 Mesure de la polarisation du circuit                                  | 153 |

| 6.3 Caractérisation du circuit en fonctionnement                          | 154 |

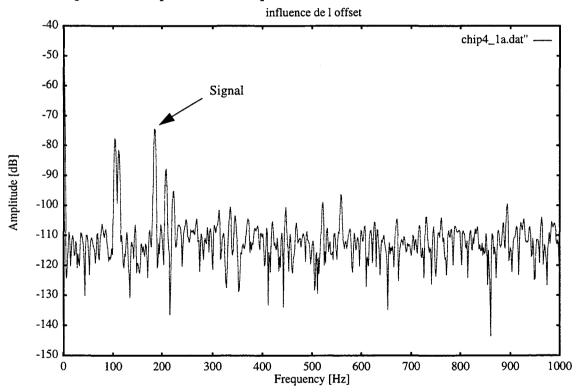

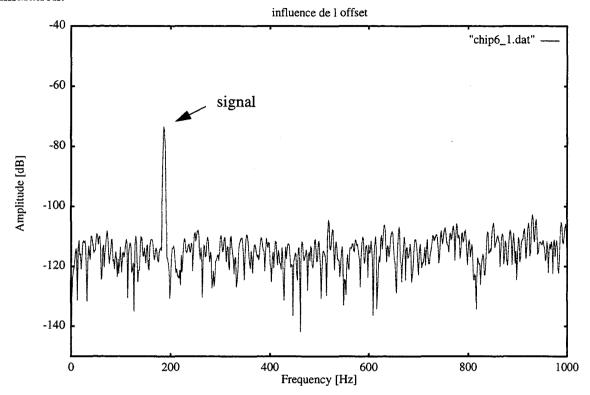

| 6.3.1 Influence de l'offset d'entrée                                      | 155 |

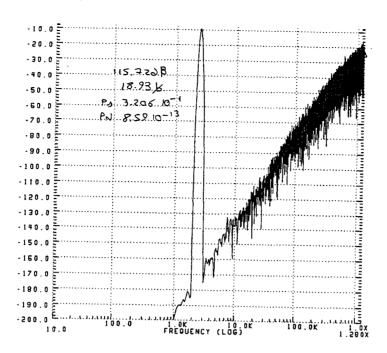

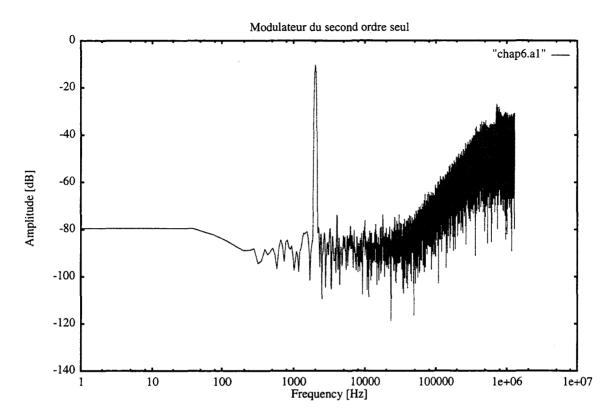

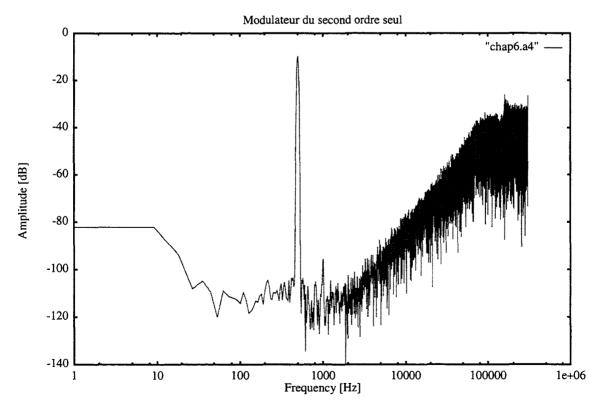

| 6.3.2 Modulateur du second ordre seul                                     | 156 |

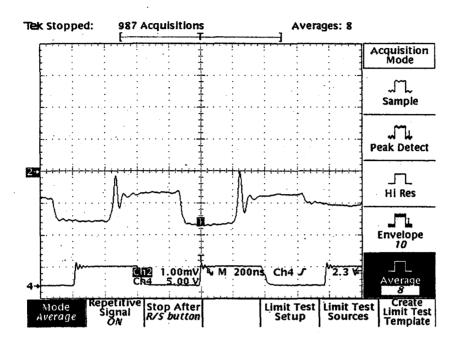

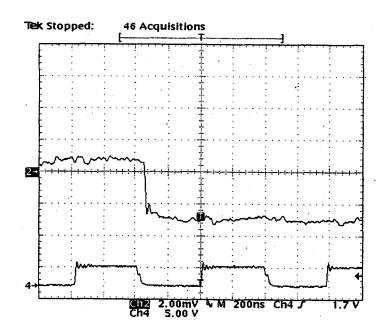

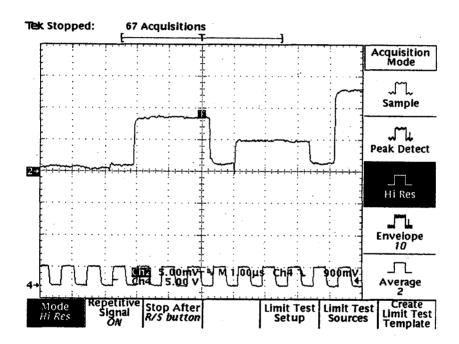

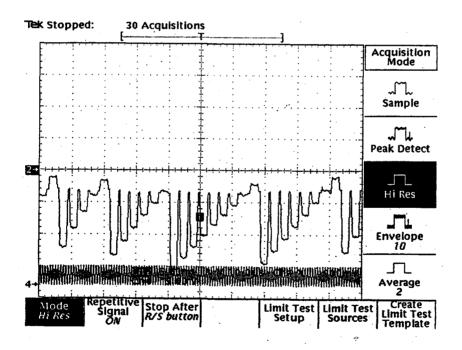

| 6.3.2.1 Problème d'établissement                                          | 156 |

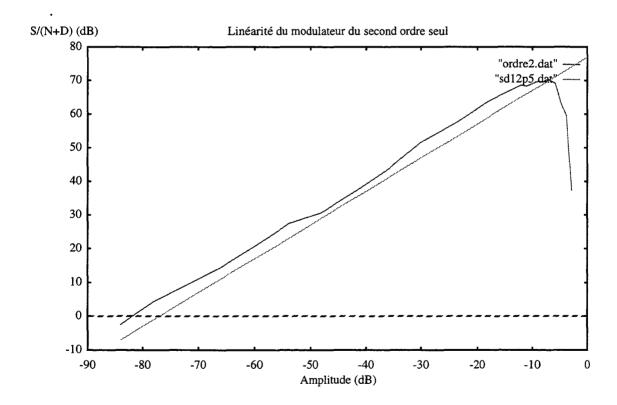

| 6.3.2.2 Mesure de la linéarité du modulateur du second ordre              | 158 |

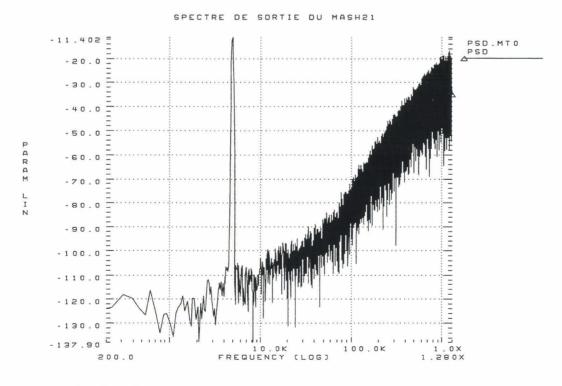

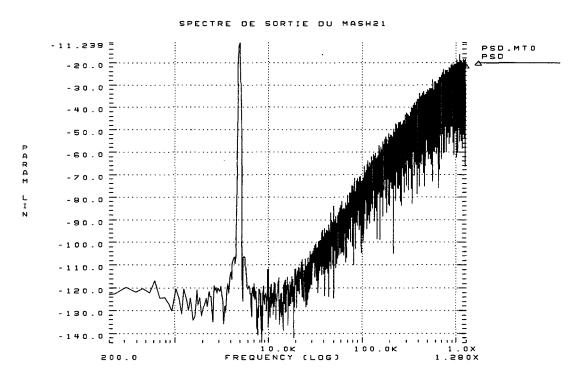

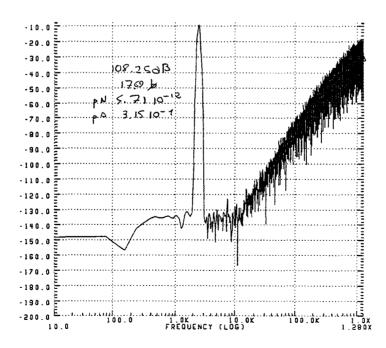

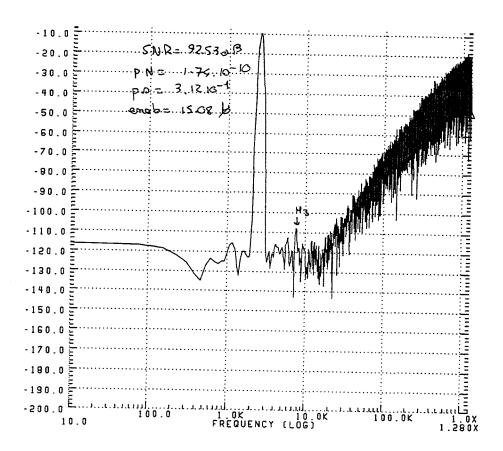

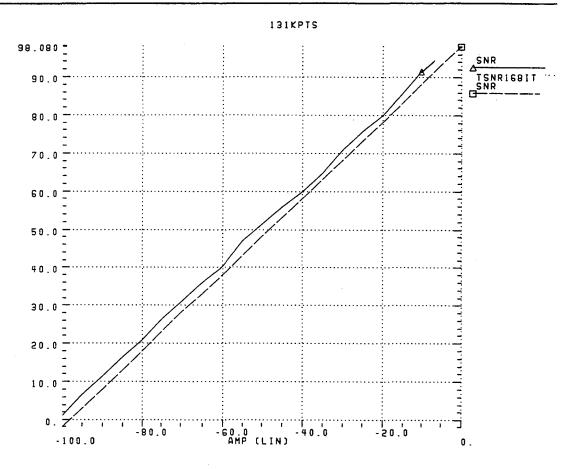

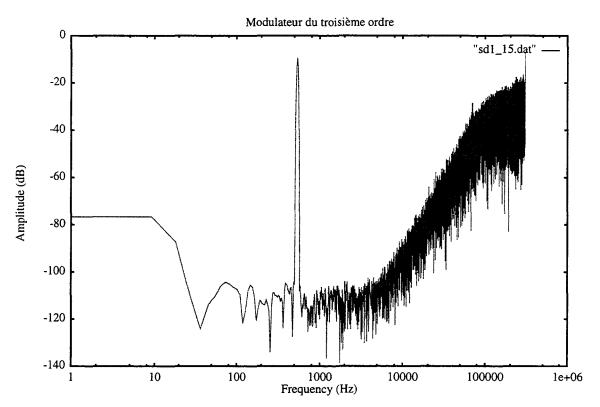

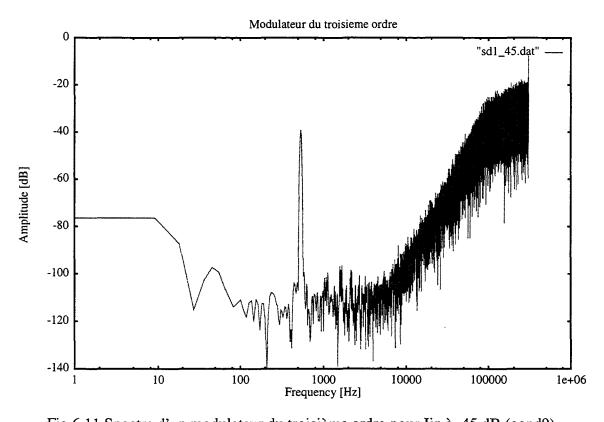

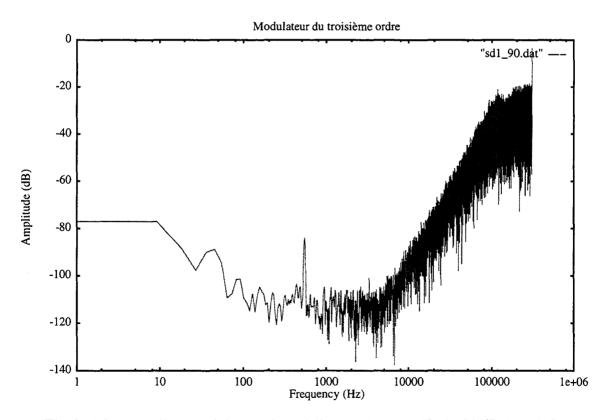

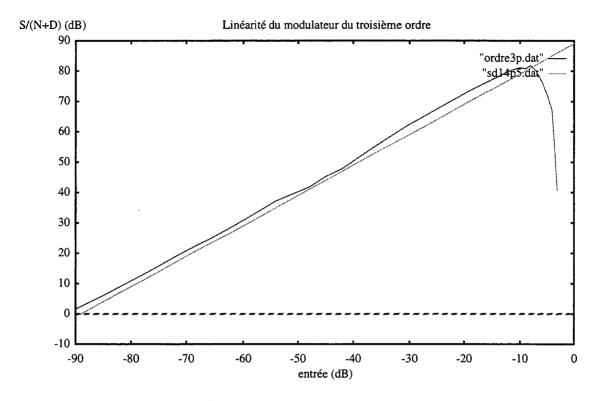

| 6.3.3 Modulateur du troisième ordre                                       | 159 |

| 6.4 Analyse des problèmes d'établissement                                 | 163 |

| 6.4.1 Mesures sous pointes                                                | 163 |

| 6.4.2 Influence de la durée de chaque boucle durant l'acquisition         | 165 |

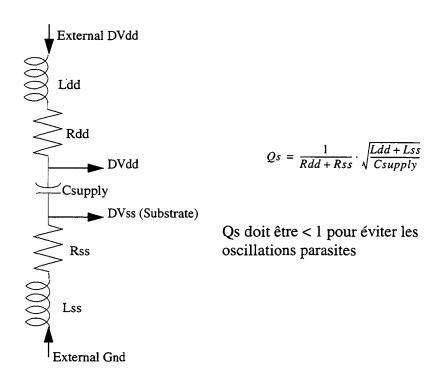

| 6.4.3 Problème d'oscillations parasites dues aux fils de «bounding»       | 166 |

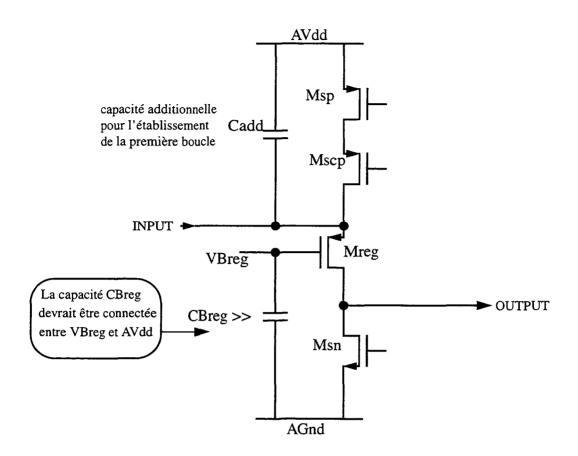

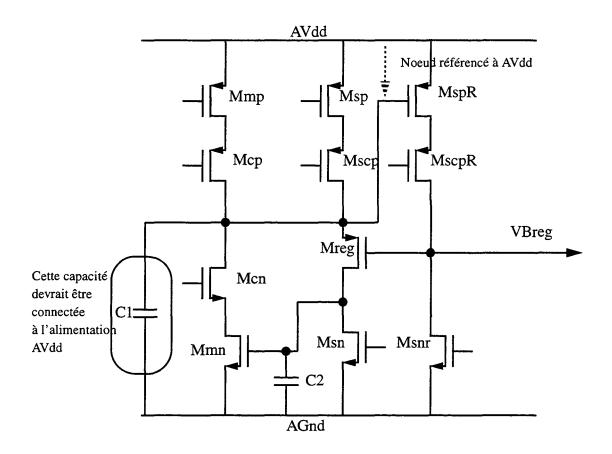

| 6.4.4 Problème de dessin dans la génération de tension de référence VBREG | 168 |

| 6.5 Conclusion                                                            | 170 |

| 6.6 Annexe A                                                              | 171 |

| 6.7 Annexe B                                                              | 172 |

| 6.8 Références                                                            | 173 |

#### **CONCLUSION**

#### Introduction

D'année en année, la diminution de la taille des transistors dans les procédés de fabrication CMOS permet une intégration toujours plus grande des systèmes numériques. Certaines fonctions comme le filtrage ou le traitement du signal, jusqu'alors réalisées de manière analogique, sont maintenant traitées numériquement sur un seul circuit intégré.

Cette évolution requiert la présence d'une interface analogique-numérique en entrée ainsi que d'une interface numérique-analogique en sortie pour communiquer avec le monde extérieur. Afin d'être compétitive par rapport au tout analogique, cette solution nécessite l'intégration de ces deux types d'interface et de la partie de traitement numérique sur un seul circuit.

La technique communément utilisée sur les applications commerciales pour réaliser les interfaces analogique-numérique est celle des capacités commutées. Toutefois cette méthode est difficilement compatible avec un procédé technologique CMOS digital puisqu'elle nécessite des capacités linéaires flottantes. Ce type de capacités est réalisé essentiellement de deux manières:

- avec deux couches de polysilicium, ce qui ajoute des étapes de fabrication supplémentaires et donc un coût du circuit plus élevé.

- en faisant un empilement poly-metal1-metal2, ce qui procure une capacité linéaire flottante dont la composante parasite vers la masse peut atteindre la moitié de la valeur de la capacité. La faible valeur de la capacité par surface augmente considérablement la taille du circuit.

Une alternative à cette technique est celle des courants commutés. Cette dernière présente l'avantage de ne pas nécessiter de capacités flottantes, elle est donc totalement compatible avec un procédé de fabrication CMOS digital. Un autre avantage vient du fait que la précision d'un intégrateur réalisé en courant commuté ne repose sur aucun appareillement de transistors ou de capacités. De plus, comme le signal est véhiculé sous forme de courant, sa dynamique n'est pas limitée par la tension d'alimentation. La tendance actuelle de baisser les tensions d'alimentation suite aux applications fonctionnant sur batterie et aux tensions de claquage des transistors plus faibles rends cette nouvelle technique encore plus intéressante.

La réalisation d'interfaces analogique-numérique utilisant la technique de courants commutés a fait l'objet de nombreux travaux de recherche récents. Les études de convertisseurs analogiques-numériques entreprises se divisent essentiellement en deux tendances, les convertisseurs algorithmiques cycliques ou pipelines et les convertisseurs suréchantillonnés (essentiellement des modulateurs sigma-delta).

La réalisation d'un convertisseur cyclique d'une précision de 14 Bits pour une puissance consommée de 3.5 mW et une surface de 1  $\mu$ m² dans un procédé CMOS 3  $\mu$ m [1], ou d'un convertisseur cyclique RSD ayant une fréquence d'échantillonnage de 550 Khz dans un procédé CMOS 2.4  $\mu$ m [2], sont des exemples réalistes qui confirment la possibilité de réaliser des convertisseurs algorithmiques, précis ou rapides, en mode courant dans un procédé digital classique.

Dans le domaine des convertisseurs suréchantillonnés, la réalisation de modulateurs sigma-delta rapides semble possible, pour exemple un convertisseur sigma-delta du quatrième ordre ayant une précision de 9 Bits pour une bande de base de 625 Khz, ce modulateur est réalisé dans un procédé CMOS 0.8 µm [3]. Par contre l'étude de convertisseurs analogique-numérique suréchantillonnés de haute précision à base de cellules à mémoire de courant n'a pas encore vraiment aboutie [3].

Le but de mon travail de thèse est la réalisation d'un convertisseur analogique-numérique de forte précision en mode courant intégré dans un procédé digital avancé. Ce mémoire décrit toutes les étapes qui nous ont permis d'atteindre ce but.

Dans un premier temps, je décris le principe de la cellule à mémoire de courant, élément de base des circuits à courant commuté, par l'intermédiaire des publications existantes. Cela m'a permis d'étudier la modélisation des mémoires de courant. Suite à cette étude, je propose un macro modèle du comportement temporel de la cellule à mémoire de courant [4]. Ce modèle a pu être validé par la mise au point d'une méthodologie de caractérisation des cellules à mémoire de courant [5], un circuit de test a été réalisé.

Au sein du laboratoire de recherche de l'I.E.M.N., P. N'Goran et A. Kaiser ont réalisé un simulateur de circuits à courant commuté ainsi qu'une modélisation précise de la cellule à mémoire de courant [6]. En utilisant ce simulateur nous avons mis en évidence que l'erreur de recopie de la cellule, sa non-linéarité inhérente ainsi que son rapport signal sur bruit sont les principaux facteurs qui limitent la précision des convertisseurs sigma-delta.

Comme solution nous proposons une nouvelle structure de cellule à mémoire de courant qui est caractérisé par une trés faible erreur de recopie ainsi qu'une bonne linéarité. Un exemple de cellule à mémoire de courant de ce type a été étudié et dimensionné. Nous avons pu réaliser un convertisseur sigma-delta cascadé du troisième ordre au moyen de cette cellule. Ce modulateur est la cascade d'un convertisseur du second ordre avec un convertisseur du premier ordre. Le modulateur est parfaitement fonctionnel, il atteint la précision de 14.5 Bits pour une bande passante de 5 Khz.

Ce convertisseur illustre la possibilité d'intégrer des convertisseurs suréchantillonnés de forte précision dans un procédé CMOS classique. La seule limitation à une utilisation commerciale est sa trop forte consommation.

Ce mémoire est composé de six chapitres. Dans le premier chapitre nous présentons le principe de la cellule à mémoire de courant. Les principaux effets qui limitent la précision de la cellule, soit la charge injectée par l'interrupteur d'échantillonnage, la conductance de sortie de la cellule ainsi que le temps nécessaire à la stabilisation du courant mémorisé, sont expliqués.

Nous avons fait une étude plus approfondie du régime transitoire de la cellule au cours de l'acquisition du courant d'entrée. Cette étude à donné lieu à un macro-modèle non-linéaire précis du comportement transitoire de la cellule à mémoire de courant de type cascodée. Nous voyons dans ce chapitre que le modèle prends en compte l'influence de la source en entrée de la cellule ainsi que du chronogramme des signaux de commande. Enfin, une comparaison avec des résultats de simulation SPICE valide le modèle.

La possibilité de mesurer les caractéristiques essentielles de la cellule est utile à son développement. Ces mesures faciliteront aussi la réalisation du convertisseur de haute précision. Le chapitre deux présente une méthodologie de test qui ne nécessite pas l'utilisation de matériel spécialisé tel un testeur sous pointes. Les caractéristiques obtenues sont les suivantes:

- La courbe d'évolution temporelle de la tension (ou du courant) de mémorisation au cours de la phase d'acquisition de la cellule. Cette mesure est faite pour plusieurs valeur du courant à l'entrée de la cellule.

- Le rapport entre la charge injectée par l'interrupteur d'échantillonnage en fin d'acquisition et la charge totale qui était dans cet interrupteur.

- La conductance de sortie de la cellule. nous pouvons en déterminer la partie statique, liée à l'effet Early, ainsi que la partie dynamique qui provient du couplage

capacitif entre la capacité de mémorisation et une capacité parasite.

• L'erreur de recopie de la cellule. Erreur qui prends en compte tous les effets limitatifs de la cellule. Cette erreur est mesurée en fonction du courant appliqué à l'entrée de la cellule.

Cette méthode de mesure a donné lieu à la réalisation d'un circuit de test. Nous avons mesuré les caractéristiques d'une cellule à mémoire de courant de type cascodée. Le circuit de test à été réalisé dans une technologie CMOS digital ES2 1.2 µm. Ce circuit nous a permis aussi de confronter la prédiction du modèle présenté au premier chapitre avec les résultats de mesure.

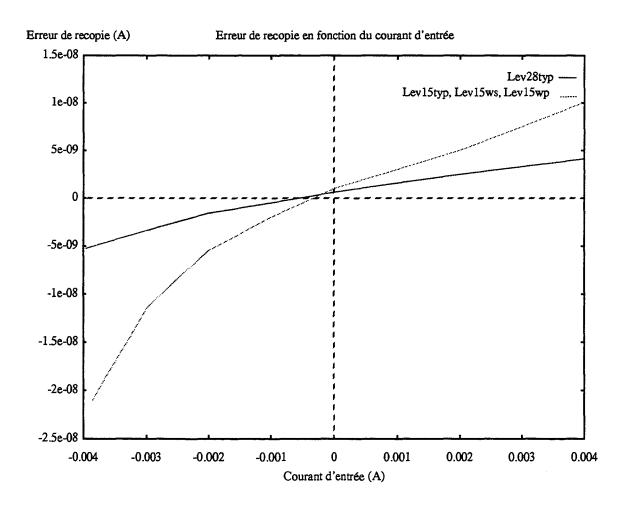

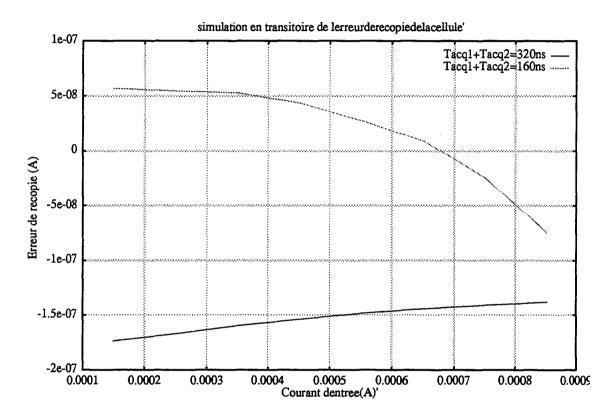

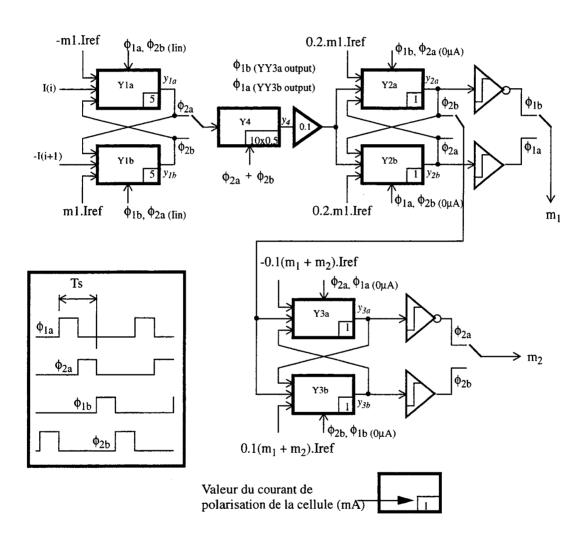

Le chapitre 3 détaille l'étude faite sur les convertisseurs analogique-numérique de type sigma-delta réalisés à base de mémoires de courant. En utilisant le simulateur de circuits à courant commuté mis au point à l'I.E.M.N. [6] nous avons évalué l'influence des caractéristiques de la cellule à mémoire de courant sur la précision du convertisseur. En partant d'une architecture spéciale de convertisseur sigma-delta du second ordre inventée par P. N'Goran et A. Kaiser [6], nous avons ajouté un modulateur du premier ordre afin de réaliser un convertisseur cascadé M.A.S.H. 2 + 1 plus apte à atteindre une forte précision. L'erreur de recopie de la cellule de type cascodée, de l'ordre de 2%, est largement insuffisante pour la précision requise, de plus cette cellule est fortement non-linéaire. Nous avons donc calculé au moyen de simulations l'erreur de recopie de la cellule nécessaire pour atteindre une précision de 16 Bits. La cellule doit surtout posséder une erreur de copie faiblement non-linéaire.

Nous voyons aussi dans ce chapitre que le bruit thermique des transistors de la cellule dégrade fortement le rapport signal sur bruit du modulateur. Le courant de polarisation de la cellule doit être dimensionné pour respecter le rapport signal sur bruit voulu. Cela cause alors une trop forte consommation du modulateur. nous proposons donc une modification de la structure du modulateur, celui ci comporte une division de la dynamique du signal entre le premier et le second intégrateur.

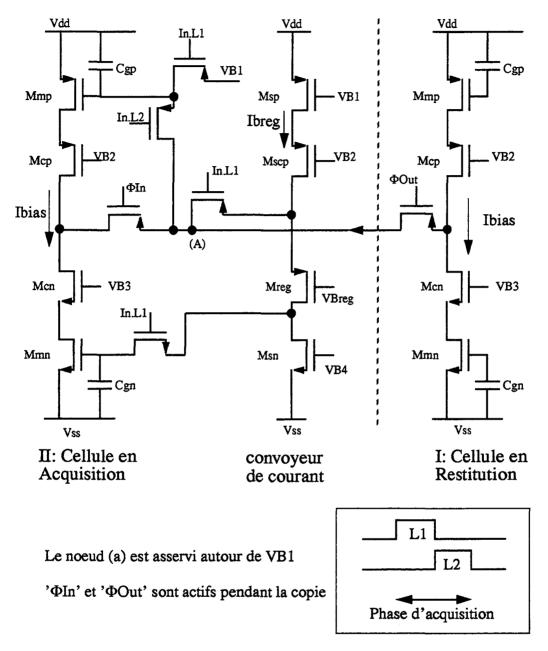

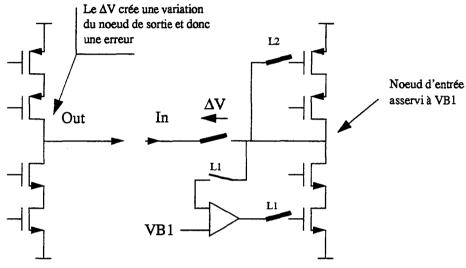

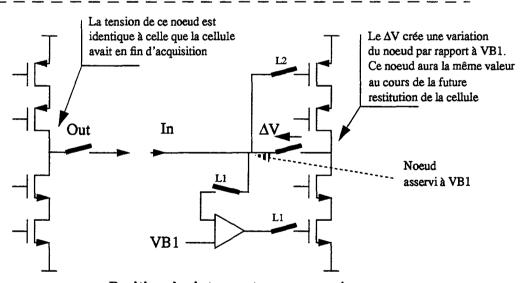

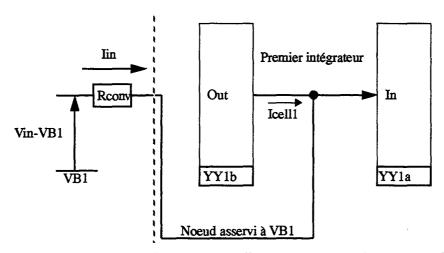

Dans le chapitre 4 nous détaillons la nouvelle structure de cellule à mémoire de courant mise au point, elle possède une erreur de recopie faible et fortement linéaire. Cette cellule utilise entre autre le principe des cellules double boucles [7]. Au cours de la première boucle d'acquisition, nous avons inséré un convoyeur de courant pour asservir le noeud d'entrée de la cellule à une tension fixe. Enfin une disposition particulière de l'interrupteur d'entrée de la cellule à permis de diminuer fortement l'erreur causée par ce dernier.

L'étude du principe de la cellule ainsi que de son dimensionnement sont détaillés dans ce chapitre. Nous présentons les résultats des simulations SPICE faites au cours de l'étude de la cellule. Les modèles utilisés sont ceux du procédé CMOS digital 0.8 mm du fondeur AMS, en effet nous avons réalisé le convertisseur sigma-delta dans cette technologie. L'erreur de recopie de la cellule prédite par la simulation est de l'ordre de 1 pour 50000 ce qui est largement suffisant pour la précision voulue.

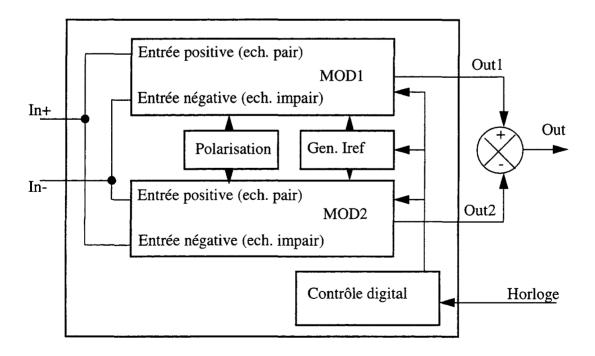

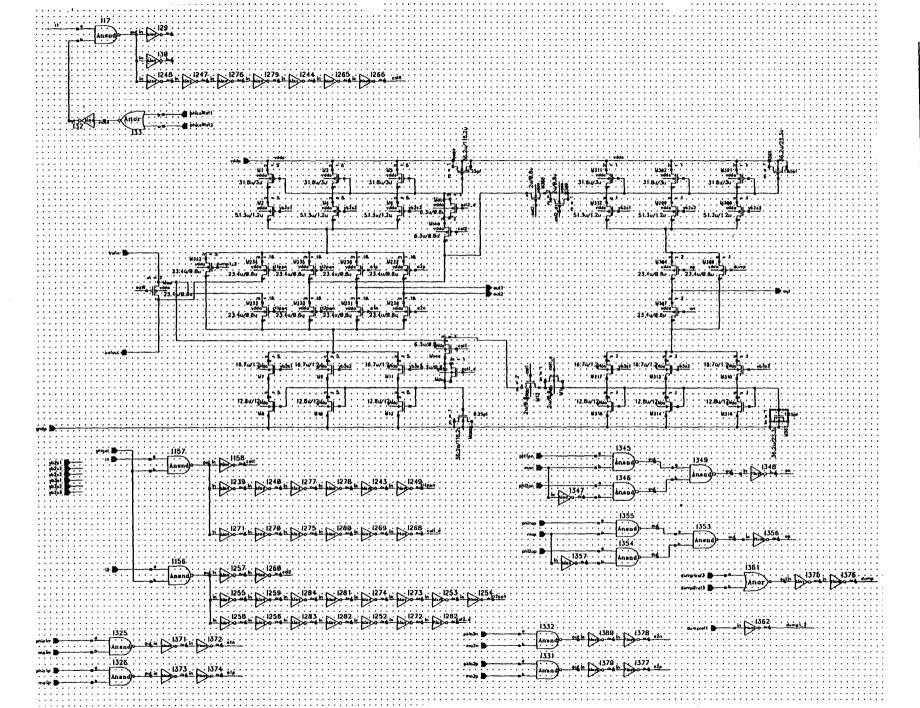

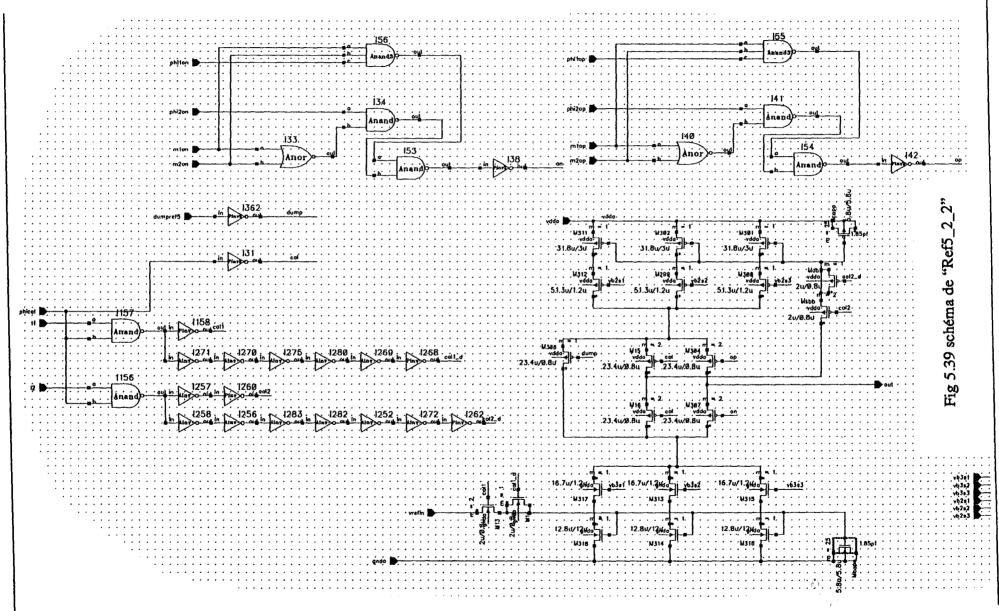

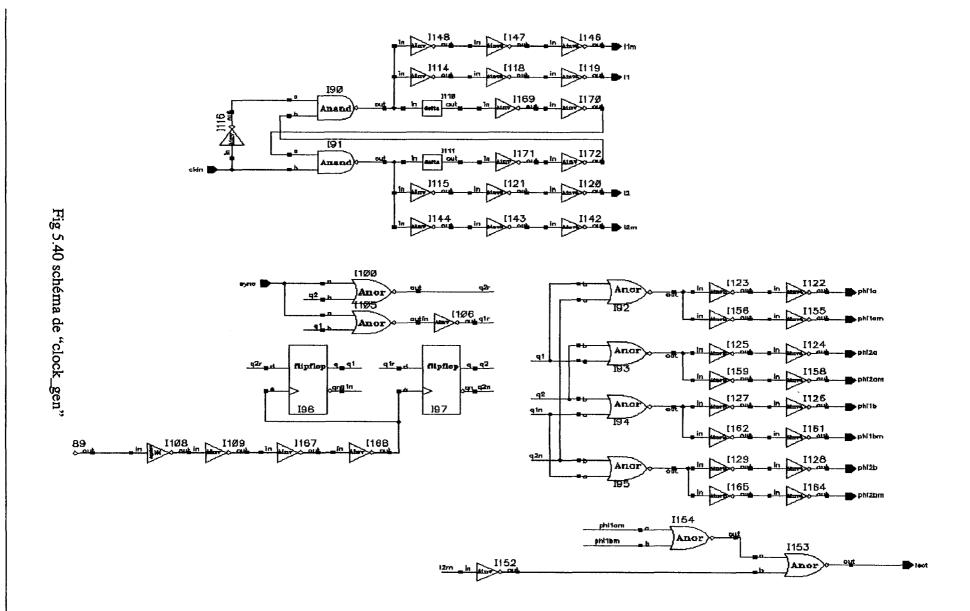

Le chapitre 5 décrit la conception du modulateur sigma-delta cascadé M.A.S.H. 2 + 1 réalisé avec la cellule à mémoire de courant proposée. Le circuit contient deux modulateurs sigma-delta identiques qui fonctionnent sur le même signal d'entrée mais de signe opposé. Cela a deux avantages:

- diminuer les perturbations de mode commun (notre cellule à mémoire de courant n'est pas une structure différentielle).

- Utiliser en permanence le courant d'entrée, ce qui évite toute désaturation du générateur de courant.

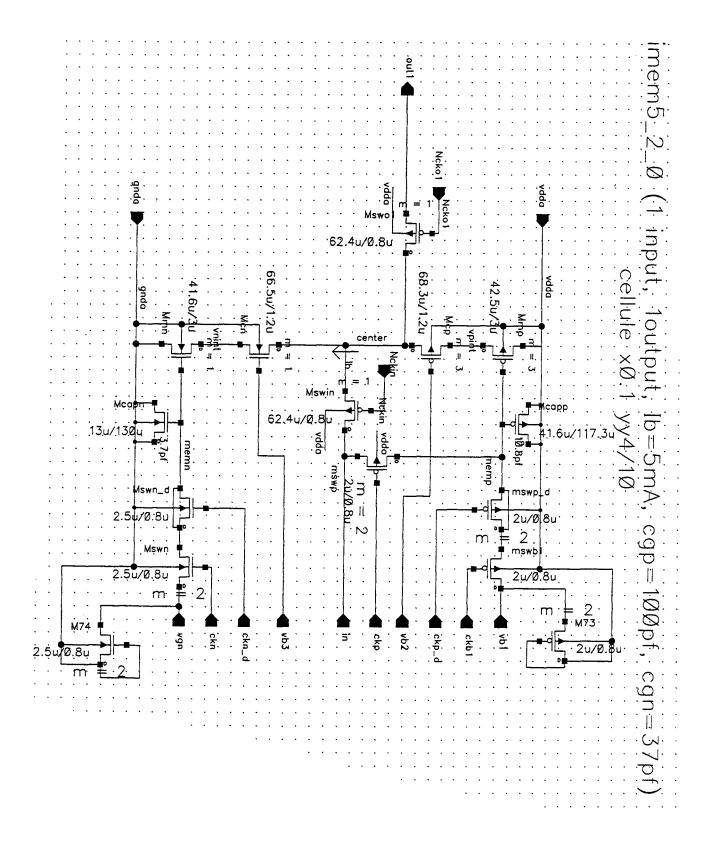

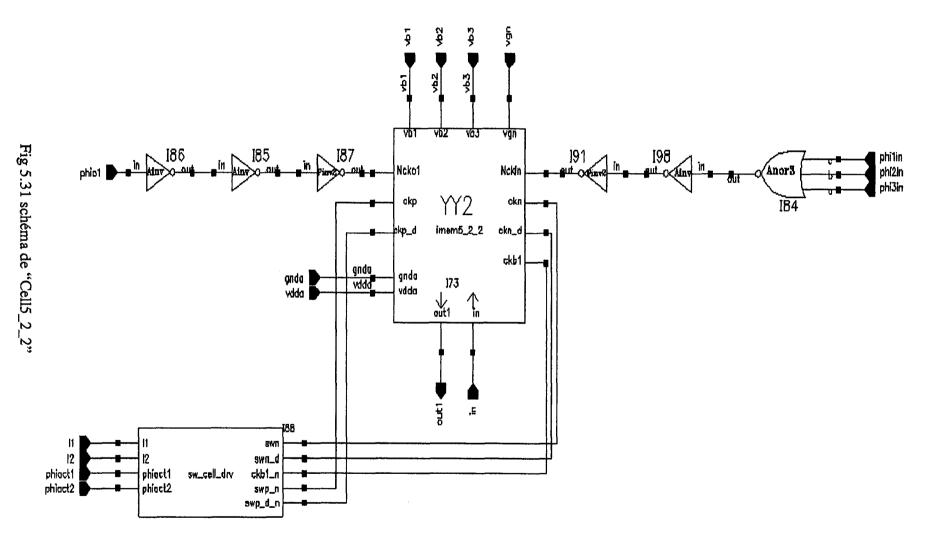

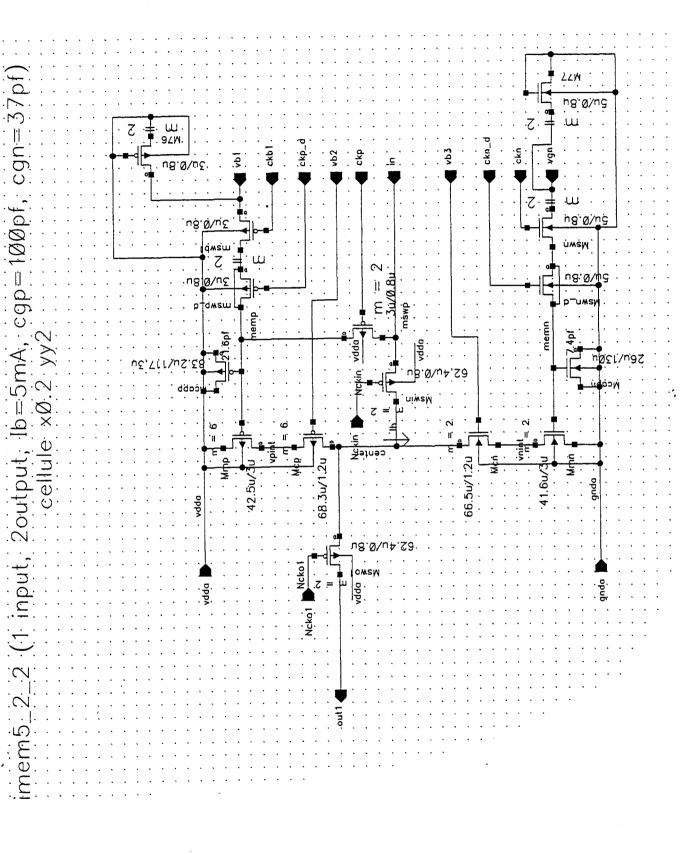

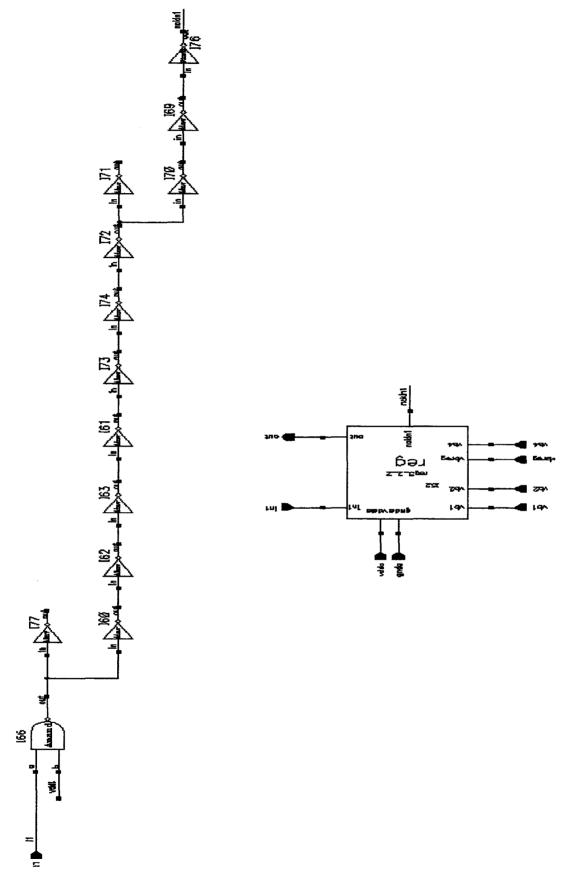

Nous détaillons l'étude de toutes les parties du modulateur et l'ensemble des simulations nécessaires au développement du circuit et à l'évaluation des performances qui valident la précision de 16 Bits voulue ainsi que la fonctionnalitée du circuit. Le schéma complet du circuit est inclus à la fin de ce chapitre, il comprends les tailles de tous les transistors.

Le circuit a été réalisé chez le fondeur AMS. Nous avons développé une maquette et un programme de test du circuit sur le logiciel "Lab View". Le schéma de la maquette de test est détaillé dans le chapitre 6. Nous y présentons aussi l'ensemble des manipulations et des mesures entreprises.

Le circuit est parfaitement fonctionnel, il atteint la précision élevée de 14.5 Bits pour une bande de base de 5 Khz. Ces performances sont moins bonnes que celles attendues (16 Bits, 10 Khz). A la fin de ce chapitre nous passons en revue les problèmes rencontrés ainsi que les écarts par rapport aux performances voulues. Nous tentons alors d'en expliquer la raison et de donner des solutions pour y remédier.

#### Références:

- [1] P. DEVAL & al.

A 14 bit CMOS A/D converter based on dynamic current memories.

CICC Proceedings, San Diego, May 1991, p. 24. 2. 1.

- [2] D. MACQ

Application des copieurs de courant dans les circuits analogiques CMOS

Thèse de Doctorat, Université Catholique de Louvain, Février 1994.

- N.TAN

Switched-Current Delta-Sigma A/D Converters.

Analog Integrated Circuits and Signal Processing, Vol. 9, No. 1, pp. 7-24, Jan. 1996.

- [4] N. MOENECLAEY, A. KAISER

Accurate modelling of the non-linear settling behaviour of current memory circuits ISCAS'94, Londres, UK, Mai 1994.

- [5] N. MOENECLAEY, A. KAISER

Measurement of the main limitations of current memory cells

MWSCS'94, Lafayette Louisiana USA, Août 1994.

- [6] P. N'GORAN Simulation à Temps Discret de Circuits à Mémoire de Courant et Application à l'Etude de Modulateurs Sigma-Delta. Thèse No. 1291, Université des Sciences et Techniques de Lille Flandres-Artois, 1994.

- [7] J. B. HUGHES & K. W. MOULDING S2I: A Switched-Current Technique for High Performance Electronics Letters, 5th August 1993, Vol. 29 No.16

## Chapitre 1

Etude et modélisation des principaux effets limitatifs des cellules à mémoire de courant

Les circuits à courant commuté sont composés d'éléments de base: les cellules à mémoire de courant. Afin de concevoir de tels circuits, une étude de ces cellules et de leurs principaux effets limitatifs tels la conductance de sortie de la cellule, la charge injectée par l'interrupteur d'échantillonnage... est présentée. Une modélisation de ces effets et notamment du comportement transitoire de la cellule est proposée. Le modèle de la cellule ainsi obtenu permettra une simulation rapide des circuits à courant commuté.

#### 1.1 La cellule à mémoire de courant

#### 1.1.1 Principe de fonctionnement

La cellule à mémoire de courant [1] [2] est un des éléments de base des circuits à courant commuté. Elle réalise trois opérations élémentaires: elle mémorise le courant, elle l'inverse lors de la restitution et elle somme les divers courants à son entrée.

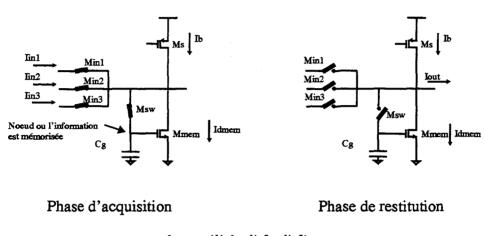

Il existe plusieurs types de cellules à mémoire de courant mais leur principe de fonctionnement est dérivé de celui de la cellule élémentaire. La Fig 1.1 en illustre le principe.

$Iout = -\left(Iin1 + Iin2 + Iin3\right)$

Fig 1.1 Cellule à mémoire de courant simple

La somme des courants en entrée de la cellule est convertie en une tension qui est mémorisée sur la capacité de grille du transistor mémoire M1. La conversion courant tension est réalisée par le transistor mémoire pendant la phase dite d'acquisition. Durant cette phase, le transistor mémoire est connecté en diode, il existe donc une relation entre son courant de drain et sa tension de grille. Pendant l'acquisition du courant les interrupteurs d'entrée Min et d'échantillonnage Msw sont passants.

Une fois la tension de grille établie, la grille est isolée du drain par l'ouverture du transistor Msw et la tension de grille est mémorisée. Il suffit alors pendant la seconde phase dite de restitution, que le transistor de mémorisation soit saturé pour qu'il restitue le courant de drain ainsi mémorisé. Cette restitution vers une autre cellule nécessite donc d'ouvrir l'interrupteur Min.

L'ajout d'une source de courant de polarisation Ib permet de mémoriser des courants positifs et négatifs. Il est impératif que l'interrupteur d'échantillonnage Msw soit coupé avant l'interrupteur d'entrée pour garantir une bonne mémorisation. L'ouverture de l'interrupteur d'entrée coupe l'arrivée du courant d'entrée, il y a un déséquilibre entre le courant de la source PMOS et le courant du transistor NMOS. Dans le cas ou l'interrupteur d'échantillonnage est encore passant, le transistor mémoire reste connecté en diode et il va changer son courant de drain pour égaler le courant de polarisation de la source PMOS. La mémorisation du courant d'entré sera détruite.

#### 1.1.2 Principaux effets limitatifs et leur caractérisation

Ce paragraphe liste les principales limitations des cellules à mémoire de courant ainsi

que la manière dont elles ont été calculées lors de la validation des résultats expérimentaux. Un sous chapitre entier est consacré à la modélisation temporelle de la cellule à mémoire de courant, ce modèle représente une partie importante de ce travail de thèse.

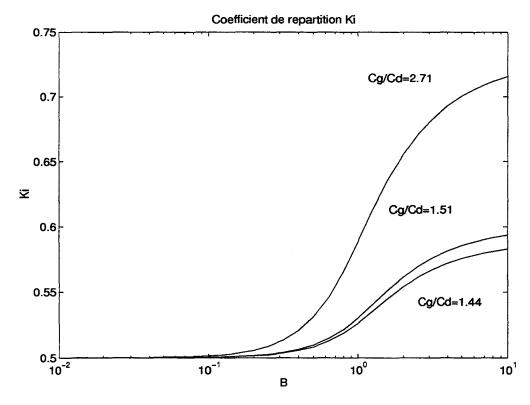

#### 1.1.2.1 L'injection de charge

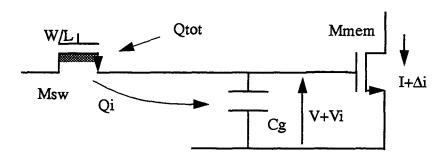

A la fin de la phase d'acquisition, le blocage du transistor d'échantillonnage permet d'isoler électriquement la grille du transistor mémoire. Au cours de ce blocage, la charge  $Q_{tot}$  qui était stockée dans le canal de l'interrupteur est libérée (Fig 1.2).

Fig 1.2 Mécanisme de l'injection de charge

Une partie de cette charge  $Q_i$  est transférée vers la capacité de grille du transistor mémoire Cg, ce qui modifie la tension mémorisée. Cette variation de tension  $\Delta V_i$  cause une erreur  $\Delta_i$  sur le courant de drain suivant la relation:

$$\Delta i = gm \cdot \Delta V_i = gm \cdot \frac{Q_i}{C_o} \tag{1.1}$$

$$K_i = \frac{Q_i}{Q_{tot}} \tag{1.2}$$

#### où gm est la transconductance du transistor mémoire

L'injection de charge se caractérise au moyen d'un coefficient de proportionnalité  $K_i$  entre la charge injectée  $Q_i$  sur la capacité mémoire et la charge totale stockée dans le canal du transistor d'échantillonnage  $Q_{tot}$  (1.2). Ce rapport donne l'importance de la perturbation apportée par la coupure de l'interrupteur, il permet donc de caractériser l'injection de charge. Il est principalement fonction de trois paramètres [3]:

- La valeur des deux capacités connectées à la source et au drain du transistor d'échantillonnage.

- La pente du signal de commande lors de la coupure du transistor d'échantillonnage.

- La tension de grille avant coupure ainsi que la tension de seuil du transistor d'échantillonnage.

Une technique couramment utilisée pour réduire l'injection de charge est l'utilisation d'un transitor auxiliaire de taille moitié [4]. Cette technique permet de compenser parfaitement l'injection de charge quand le coefficient de proportionnalité  $K_i$  a pour valeur 0.5. La Fig 1.3 en explique brièvement le principe.

Une fois l'interrupteur d'échantillonnage coupé, la charge  $Q_i$  a été injectée sur la capacité mémoire. Le transistor auxiliaire  $M_{dum}$  est alors bloqué. Comme son drain est connecté à sa source la totalité de la charge  $Q_{dum}$  qu'il stockera dans son canal va provenir de la capacité de mémorisation. Si la surface de ce transistor auxiliaire est la moitié de la surface du transistor d'échantillonnage, la charge de son canal sera  $Q_{tot}/2$ . On obtiendra donc une compensation optimale quand  $K_i$  sera égal à 0.5.

De la même façon on définit le ratio  $K_{ic}$  qui est le rapport entre la charge restante sur la capacité mémoire après compensation et la charge totale  $Q_{tot}$  (1.4). Ce ratio  $K_{ic}$  caractérise l'efficacité de la compensation d'injection de charge.

$$\Delta ic = gm \cdot \Delta V_{ic} = gm \cdot \frac{Q_i - Q_{dum}}{C_g}$$

(1.3)

$$K_{ic} = \frac{Q_i - Q_{dum}}{Q_{tot}} \tag{1.4}$$

On verra dans ce chapitre que le dispositif de compensation par demi transistor permet expérimentalement de mesurer le rapport  $K_i$ .

Fig 1.3 Compensation de l'injection de charge

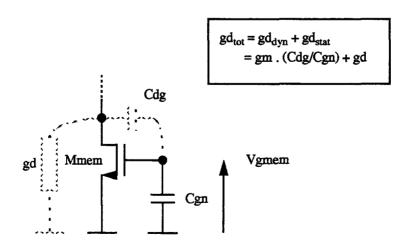

#### 1.1.2.2 conductance de sortie

Durant la phase d'acquisition, le noeud d'entrée de la cellule à mémoire de courant se stabilise vers une valeur qui dépend de la somme des courants entrants. Cette variation de tension d'entrée se répercute sur les cellules en restitution dont le courant est modulé du fait de la conductance de sortie  $g_o$  (1.5).

$$\Delta I_{out} = g_o \cdot \Delta V_{out} \tag{1.5}$$

La précision de la copie de courant est fonction du rapport entre la valeur de la conductance de sortie des cellules en restitution et la valeur de la transconductance vue a l'entrée de la cellule en acquisition.

La conductance de sortie de la cellule à mémoire de courant est due à:

l'effet Early des transistors composant la mémoire et la source de polarisation

- Ib. C'est la partie statique de la conductance de sortie (g<sub>stat</sub>).

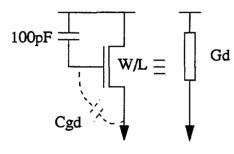

- Le couplage capacitif drain grille du transistor mémoire. Une variation de la tension de drain induit une légère modification de la tension mémorisée par l'intermédiaire du diviseur capacitif formé par  $C_{\rm gd}$  et  $C_{\rm g}$ . Il en résulte une modulation du courant de drain (1.6), ce processus peut donc se modéliser comme une conductance. C'est la partie dynamique de la conductance de sortie.

$$g_{dyn} = gm \cdot \frac{C_{gd}}{C_g + C_{gd}} \tag{1.6}$$

La conductance de sortie de la cellule est donc la somme de ces deux conductances (1.7). On montrera que la mesure de la conductance totale de sortie de la cellule ainsi que la mesure de la partie dynamique seule sont possibles.

$$g_o = g_{stat} + g_{dyn} \tag{1.7}$$

#### 1.1.2.3 Erreur de stabilisation

Une des limitations de la cellule est l'erreur de stabilisation durant la phase d'acquisition. La valeur du courant d'entrée force un nouveau point de polarisation et donc une nouvelle tension sur la capacité mémoire qu'il va falloir atteindre au cours du transitoire durant l'acquisition. La précision de la cellule sera donc fonction de la vitesse de stabilisation de la cellule, il convient donc d'étudier le transitoire d'établissement de la tension de mémorisation.

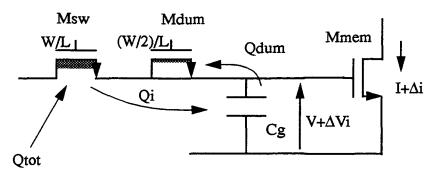

Fig 1.4 Modélisation petit signal de la cellule cascodée

Pour calculer la forme du transitoire une étude petit signal de la cellule soumise à un échelon de courant à son entrée s'avère insuffisante. En effet on ne peut considérer la cellule en fonctionnement petit signal puisque le courant d'entrée peut atteindre la moitié de la valeur du courant de polarisation de la cellule. De plus, le fait d'appliquer un échelon de courant en entrée ne tient pas compte du timing particulier des cellules à mémoire de courant qui a une certaine influence sur la nature du transitoire. La partie suivante du chapitre expose une approche nouvelle du calcul de l'erreur de stabilisation, un modèle implémentable dans le simulateur de circuits à courant commuté développé à l'I.E.M.N. [5] y est décrit.

#### 1.2 Modélisation temporelle de la cellule à mémoire de courant

Une cellule à mémoire de courant de type cascodée [6] a été modélisée. En effet ses performances sont bien meilleures en terme de précision de copie de courant. Le modèle proposé [7] est facilement modifiable pour d'autres types de cellules.

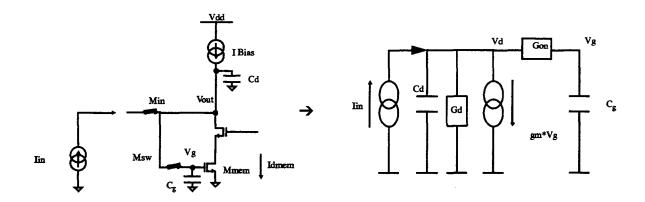

#### 1.2.1 Modèle petit signal classique

L'approche classique de la modélisation de la cellule à mémoire de courant pendant la phase d'acquisition [8] consiste en une description petit signal de la cellule. Le signal d'entrée est alors appliqué sous la forme d'un échelon de courant, le début de l'échelon marquant le démarrage de l'acquisition. La Fig 1.4 donne le schéma petit signal de la cellule.

La conductance Gd modélise la conductance de la source de courant Ibias ainsi que la conductance de l'ensemble transistor mémoire et transistor d'acquisition vue par le noeud Vd. La conductance de l'interrupteur d'échantillonnage est modélisé par g<sub>on</sub>. On considère que le transistor d'entrée Min est dimensionné de manière à ce que sa conductance soit négligeable. Gm est la transconductance du transistor mémoire.

Le modèle décrit l'évolution de la tension de mémorisation Vg ainsi que celle du courant de drain du transistor mémoire Idmem en fonction du temps, pour un courant d'entrée donné. La tension de grille du transistor de mémorisation Vg se déduit des deux équations suivantes:

$$Vd = Vg\left(1 + \frac{Cg \cdot p}{gon}\right) \tag{1.8}$$

$$Iin = Cg \cdot p \cdot Vg + gm \cdot Vg + gd \cdot Vd + Cd \cdot p \cdot Vd$$

(1.9)

A partir des deux équations (1.8) (1.9) on peut exprimer la tension Vg en fonction de Iin:

$$Vg = \frac{1}{\frac{Cd \cdot Cg}{gon} \cdot p^2 + \left(Cg + Cd + \frac{Cg \cdot gd}{gon}\right) \cdot p + gm + gd} \cdot Iin$$

(1.10)

La fonction de transfert est du second ordre, la stabilisation est donc similaire à celle d'un circuit oscillant. On va donc modifier l'équation de façon à utiliser la formulation classique (1.11).

$$Vg = \frac{Iin/(gm + gd)}{\frac{p^2}{w0^2} + \frac{2 \cdot z}{w0} \cdot p + 1}$$

$$avec \qquad w0 = \sqrt{\frac{gon \cdot (gm + gd)}{Cd \cdot Cg}} \qquad z = \frac{Cg + Cd + \frac{gd \cdot Cg}{gon}}{2 \cdot \sqrt{Cd \cdot Cg}} \cdot \sqrt{\frac{gon}{gm + gd}}$$

Le calcul des pôles de cette fonction donne deux solutions possibles suivant la valeur du paramètre z:

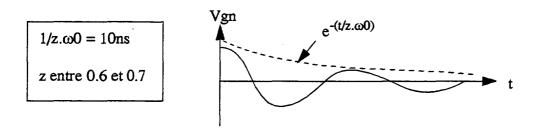

- si z>1 on se trouve en régime sur amorti soit une stabilisation lente mais sans aucune oscillation. On obtiendra ce régime pour une cellule possédant un interrupteur d'échantillonnage ayant un fort W/L ( $g_{on} \sim gm$ ) ainsi qu'une forte capacité de mémorisation Cg (Cg >> Cd).

- Si z<1 on se trouve en régime sous amorti ce qui correspond à une stabilisation rapide mais avec des oscillations de la tension Vg. Ce régime est le régime idéal de stabilisation lorsque z est compris dans l'intervalle {0.6,0.7} [9]. Pour dessiner une cellule ayant une stabilisation en régime sous amorti, il faut un interrupteur d'échantillonnage plutôt petit (g<sub>on</sub> << gm) et il faut que la capacité de sortie Cd ne soit pas trop petite comparée à celle de mémorisation (Cd ~ Cg). La cellule utilisée pour la validation du modèle proposé (cf 1.3) est de ce type, son coefficient d'amortissement z varie entre 0.67 et 0.85 en fonction de la valeur du courant d'entrée de la cellule.

Dans le cas du régime sous amorti, z<1, les deux pôles sont des complexes conjugués (1.12).

$$p1 = -z \cdot w0 + i \cdot w0 \cdot \sqrt{1 - z^2} \qquad p2 = -z \cdot w0 - i \cdot w0 \cdot \sqrt{1 - z^2}$$

(1.12)

Pour le régime sur amorti, z>1, les deux pôles sont réels (1.13).

$$p1 = -z \cdot w0 + w0 \cdot \sqrt{z^2 - 1} \qquad p2 = -z \cdot w0 - w0 \cdot \sqrt{z^2 - 1}$$

(1.13)

La modélisation temporelle de la cellule à mémoire de courant doit pouvoir prédire l'évolution de Vg au cours de la phase d'acquisition. L'équation (1.11) donne une solution temporelle générale de la forme suivante (1.14).

$$Vg(t) = Vg_0 + (Vg_f - Vg_0) \cdot (1 + A \cdot e^{p^{1} \cdot t} + B \cdot e^{p^{2} \cdot t})$$

$$avec \qquad Vg_f = \frac{Iin}{gm + gd} + Vg_0$$

(1.14)

La tension Vg<sub>0</sub> est la valeur grand signal de la tension de mémorisation au début de la phase d'acquisition, c'est à dire pour t=0. les constantes A et B sont calculées de manière à satisfaire les conditions initiales (1.15). La seconde condition initiale provient du fait que l'on considère que la tension Vg est égale à la tension Vd au début de la phase d'acquisition.

$$Vg(0) = Vg_0 \qquad \frac{d}{dt}Vg(0) = 0$$

(1.15)

Les valeurs de A et de B vérifiant la condition (1.15) permettent de calculer l'évolution

temporelle de la tension de mémorisation (1.16).

$$Vg(t) = Vg_0 + (Vg_f - Vg_0) \cdot \left(1 + \frac{p2}{p1 - p2} \cdot e^{p1 \cdot t} + \frac{p1}{p2 - p1} \cdot e^{p2 \cdot t}\right)$$

(1.16)

Pour un circuit oscillant du second ordre, le temps d'établissement optimal est atteint pour z=0,7 [9], ce qui correspond à un régime sous amorti. L'évolution temporelle de la tension de mémorisation Vg(t) sera alors de type sinusoïdal amorti (1.17).

(1.17)

$$Vg(t) = Vg_0 + (Vg_f - Vg_0) \cdot \left(1 - e^{(-z \cdot w0 \cdot t)} \cdot \left(\cos(\sqrt{1 - z^2} \cdot w0 \cdot t) + \frac{z}{\sqrt{1 - z^2}} \cdot \sin(\sqrt{1 - z^2} \cdot w0 \cdot t)\right)\right)$$

La modélisation temporelle du courant  $Id_{mem}$  est déduite de celle de la tension Vg. En effet, le courant de drain  $Id_{mem}$  du transistor mémoire est fonction de deux composantes, la part essentielle provenant de la transconductance gm du transistor mémoire (1.18).

$$Idmem = gm \cdot Vg + gd \cdot Vd \tag{1.18}$$

En utilisant l'équation (1.8) on remplace la tension Vd par son expression en fonction du potentiel Vg, le courant Id<sub>mem</sub> se déduit de la tension Vg de la manière suivante:

$$Idmem = (gm + gd) \cdot \left(1 + \frac{gd \cdot Cg}{gon \cdot (gm + gd)} \cdot p\right) \cdot Vg$$

(1.19)

L'équation (1.19) devient dans le domaine temporel une équation différentielle du premier ordre (1.20) qui permet de calculer l'évolution de  $Id_{mem}$  à partir de la fonction Vg(t) et de sa dérivée qui sont parfaitement connues.

$$Idmem(t) = (gm + gd) \cdot (Vg(t) - Vg_0) + \frac{gd \cdot Cg}{gon} \cdot \frac{d}{dt}Vg(t) + Idmem(0)$$

(1.20)

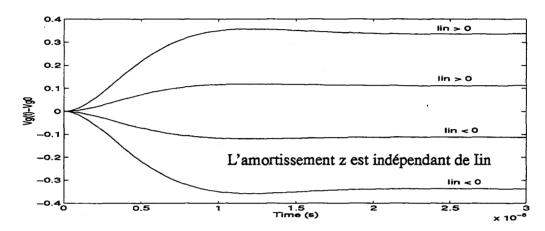

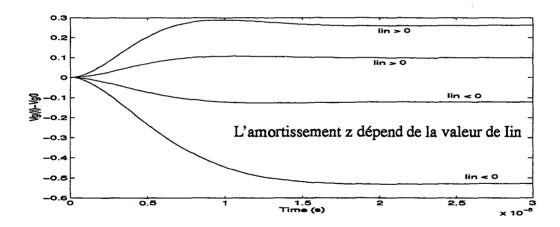

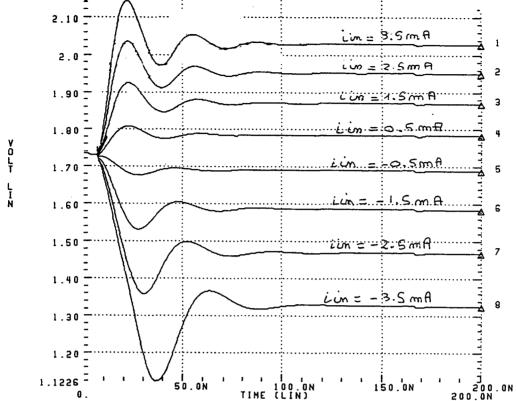

Pour un facteur d'amortissement z<1, une simulation de la cellule au cours de la phase d'acquisition en utilisant le modèle petit signal simple donne un résultat semblable aux courbes de la Fig 1.5. L'évolution typique de la tension de grille Vg pour plusieurs valeurs de courant d'entrée Iin y est représentée. La figure suivante (Fig 1.6) donne le type de réponse obtenue par simulation SPICE.

L'utilisation d'un tel modèle suppose l'approximation petit signal valable, c'est à dire que la valeur des paramètres petit signal tels la transconductance gm ou la conductance gon est considérée constante. La transconductance du transistor mémoire gm est proportionnelle à la racine carrée du courant de drain du transistor mémoire Id<sub>mem</sub>. Or le courant d'entrée de la cellule peut atteindre la moitié du courant de polarisation, ce qui veut dire que la

transconductance gm peut avoir de fortes variations au cours de la phase d'acquisition. Ceci est totalement incompatible avec l'hypothèse petit signal.

La prédiction d'un tel modèle petit signal ne sera valable que pour de petits signaux d'entrée. Une comparaison avec une simulation SPICE révèle plusieurs problèmes:

- L'amortissement au cours du transitoire est identique quelle que soit la valeur du courant d'entrée, ce qui n'est pas le cas en réalité.

- La valeur des surtensions sur Vg est largement sous-estimée.

- Le comportement du modèle est insensible au nombre de cellules à l'entrée, ce qui n'est pas le cas en simulation.

Fig 1.5 Evolution typique de Vg(t) pour un modèle petit signal

Fig 1.6 Evolution typique de Vg(t) obtenue par simulation SPICE

Il convient donc de faire une étude plus approfondie de l'environnement de la cellule ainsi que de la modélisation de la cellule elle-même.

#### 1.2.2 Modélisation approfondie de la cellule

Durant la phase d'acquisition, la cellule à mémoire de courant va passer d'un état initial correspondant au dernier courant mémorisé, à un état final induit par le courant en entrée de la cellule. Les paramètres tels que la tension de mémorisation Vg et le courant de drain du transistor mémoire Id<sub>mem</sub>, évoluent d'une valeur initiale Vg<sub>i</sub> et Idmem<sub>i</sub> vers un valeur finale

Vgf et Idmemf au cours du transitoire de l'acquisition.

La transconductance gm du transistor mémoire est fonction du courant Idmem:

$$gm \approx \sqrt{\frac{2 \cdot K_{mem} \cdot Idmem}{\lambda_{mem}}} \tag{1.21}$$

ou

$$K_{mem} = \mu \cdot Cox \cdot \frac{W}{L}$$

pour le transistor mémoire.

Comme le courant d'entrée Iin peut atteindre la moitié du courant de polarisation Ib, la transconductance gm a de fortes variations au cours de l'acquisition.

La conductance de l'interrupteur d'échantillonnage g<sub>on</sub> est fonction de la tension de mémorisation Vg de la manière suivante.

$$gon \approx K_{sw} \cdot (Vdd - Vt_0 - \lambda_{sw} \cdot Vg)$$

(1.22)

ou

$$K_{sw} = \mu \cdot Cox \cdot \frac{W}{L}$$

pour le transistor d'échantillonnage.

La tension de mémorisation varie au cours du transitoire, et donc la conductance gon n'est pas constante. Une forte variation du courant Idmem n'est causée que par une assez faible variation de la tension Vg du fait de la loi quadratique entre le courant de drain et la tension de grille du transistor mémoire. De ce fait la variation de gon résultante sera négligeable puisque la conductance n'est pas directement proportionnelle à la tension Vg mais à la différence entre Vg et la tension d'alimentation Vdd. La conductance gon de l'interrupteur pourra donc être considérée constante durant le transitoire de la phase d'acquisition de la cellule à mémoire de courant.

La principale erreur faite dans l'approximation petit signal de la cellule est de considérer la transconductance gm du transistor mémoire constante. La prédiction du modèle petit signal classique peut être nettement améliorée en utilisant une modélisation "linéaire par segments" de la caractéristique Idmem en fonction Vg du transistor mémoire.

#### 1.2.2.1 Modélisation de la caractéristique du transistor mémoire

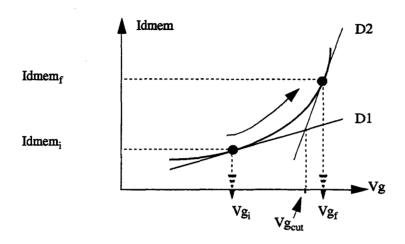

La caractéristique courant de drain en fonction de la tension de grille d'un transistor, s'il est saturé, est de type quadratique. Au cours du transitoire de la phase d'acquisition, le courant Idmem varie de sa valeur initiale Idme $m_i$  à sa valeur finale Idme $m_f$ . Il en est de même pour la transconductance qui part de la valeur  $gm_i$  pour atteindre la valeur  $gm_f$ . La Fig 1.7 illustre le changement du point de polarisation du transistor mémoire du début à la fin de phase d'acquisition.

$$D1, Idmem = gm_i(Vg - Vg_i) + Idmem_i$$

(1.23)

$$D2, Idmem = gm_f(Vg - Vg_f) + Idmem_f$$

(1.24)

Un moyen simple d'approximer cette caractéristique est de tracer deux droites D1 et D2 qui tangentent la caractéristique du transistor au point (Vg<sub>i</sub>,Idmem<sub>i</sub>) pour D1 et au point

(Vg<sub>f</sub>,Idmem<sub>f</sub>) pour D2. Les deux droites se coupent pour une certaine tension Vg<sub>cut</sub>, on peut donc approximer la caractéristique du transistor de la manière suivante:

.Si Vg appartient à [Vg<sub>i</sub>,Vg<sub>cut</sub>] le courant Idmem est déterminé par l'équation de la droite D1 (1.23). La transconductance du transistor vaut gm<sub>i</sub>.

.Si Vg appartient à [Vg<sub>cut</sub>,Vg<sub>f</sub>] le courant Idmem est déterminé par l'équation de la droite D2. La transconductance du transistor vaut gm<sub>f</sub>.

Fig 1.7 approximation de la caractéristique du transistor mémoire

Cette approximation implique de pouvoir calculer le point de polarisation initial et le point de polarisation final, ce qui est possible puisque le courant Iin ainsi que l'état précédent de la cellule sont connus. La tension  $Vg_{cut}$  est alors calculée simplement suivant l'équation suivante:

$$Vg_{cut} = \frac{(Idmem_f - Idmem_i) + (gm_i \cdot Vg_i - gm_f \cdot Vg_f)}{gm_i - gm_f}$$

(1.25)

Cette approximation linéaire par segments de la caractéristique du transistor permet alors d'utiliser le modèle petit signal pour modéliser la cellule à mémoire de courant avec de forts courants en entrée, il suffira de faire varier brutalement la valeur de la transconductance gm lorsque la tension Vg sera égale à la valeur Vg<sub>cut</sub>.

La modélisation se résumera à la résolution de deux équations du second ordre (1.11) une pour chaque valeur de la transconductance gm.

#### 1.2.2.2 Modélisation de la cellule à mémoire de courant

En utilisant l'approximation du paragraphe 1.2.2.1 la cellule est modélisée par un schéma petit signal identique à celui de la Fig 1.4.

$$Vg(t) = Vg_i + \frac{\Delta Iin}{gm_i} \cdot \left(1 - e^{(-z \cdot w0 \cdot t)} \cdot \left(1 \cdot \cos\left(\sqrt{1 - z^2} \cdot w0 \cdot t\right) + \frac{z}{\sqrt{1 - z^2}} \cdot \sin\left(\sqrt{1 - z^2} \cdot w0 \cdot t\right)\right)\right)$$

$$z = \frac{Cg + Cd + \frac{gd \cdot Cg}{gon}}{2 \cdot \sqrt{Cd \cdot Cg}} \cdot \sqrt{\frac{gon}{gm_i + gd}} \qquad w0 = \sqrt{\frac{gon \cdot (gm_i + gd)}{Cd \cdot Cg}}$$

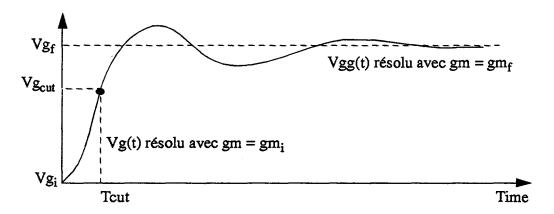

On considère à t=0, pour le début de la phase d'acquisition, que le courant de drain du transistor mémoire est Idmem<sub>i</sub> et la tension de mémorisation est  $Vg_i$ . La résolution du schéma petit signal donne la fonction de transfert de l'équation (1.11), la valeur de gm est  $gm_i$ . En considérant le cas le plus utilisé qui est sous amorti (z<1), la résolution temporelle de l'équation (1.11) avec les conditions initiales (1.15) permet de décrire l'évolution de la tension Vg(t) de la manière décrite dans l'équation (1.26).

Cette équation de l'évolution de la tension de mémorisation est valable tant que Vg appartient à l'intervalle  $[Vg_i, Vg_{cut}]$ . On calcule le moment  $T_{cut}$  où la tension Vg est égale à la valeur  $Vg_{cut}$ . On résoud donc l'équation:

$$Vg\left(T_{cut}\right) = Vg_{cut} \tag{1.27}$$

La résolution littérale de cet équation est quasiment impossible, alors que la résolution numérique est simple par convergence. On considère donc que l'évolution de la tension de mémorisation de la cellule est décrite par l'équation (1.26) dans l'intervalle de temps [0,Tcut].

Pour ne pas confondre la description de la tension Vg avant et après Tcut, l'évolution de la tension Vg est donnée par la fonction Vg(t) pour t < Tcut, elle est donnée par la fonction Vgg(t) pour t > Tcut.

Pour t > Tcut, la cellule est modélisée par un schéma petit signal identique à celui de la Fig 1.4 avec la transconductance gm égale à  $gm_f$ . On résoud aussi dans le domaine temporel l'équation (1.11) mais avec des conditions initiales différentes de celle du (1.15). Pour assurer la continuité électrique de la tension de mémorisation à t = Tcut, on se fixe:

$$Vgg(Tcut) = Vg(Tcut) = Vg_{cut}$$

$\frac{d}{dt}Vgg(Tcut) = \frac{d}{dt}Vg(Tcut)$  (1.28)

On considère aussi que  $Vgg(\infty) = Vg_f$  pour faire tendre la tension Vg vers sa valeur finale. En tenant compte de ces conditions on obtient comme solution la fonction décrite en (1.29) dans le cas sous amorti pour t > Tcut. Cette solution sera considérée comme valable dans l'intervalle [Tcut, $\infty$ ] même si, suite aux oscillations autour de  $Vg_f$ , il est possible que la tension Vg passe par la valeur Vgcut.

$$Vg(t) = Vg_f + (Vg_{cut} - Vg_f) \cdot e^{(-z \cdot w0 \cdot t)} \cdot (\cos(\sqrt{1 - z^2} \cdot w0 \cdot T) + F \cdot \sin(\sqrt{1 - z^2} \cdot w0 \cdot T))$$

$$T = t - Tcut \qquad F = \frac{1}{\sqrt{1 - z^2}} \cdot \left(z + \frac{\frac{d}{dt}Vg(Tcut)}{W0 \cdot (Vg_{cut} - Vg_f)}\right)$$

$$z = \frac{Cg + Cd + \frac{gd \cdot Cg}{gon}}{2 \cdot \sqrt{Cd \cdot Cg}} \cdot \sqrt{\frac{gon}{gm_f + gd}} \qquad w0 = \sqrt{\frac{gon \cdot (gm_f + gd)}{Cd \cdot Cg}}$$

La modélisation temporelle de la cellule à mémoire de courant de manière globale se déroulera de la manière suivante:

- . Calcul de tous les paramètres de la cellule ce qui comprend les valeurs statiques (Cg, Cd,  $g_{on}$ ,...) les valeurs initiales (Vg<sub>i</sub>, Idmem<sub>i</sub>, gm<sub>i</sub>,...) les valeurs finales correspondant au point de repos pour un temps d'acquisition infini (Vg<sub>f</sub>, Idmem<sub>f</sub>, gm<sub>f</sub>,...)ainsi que la tension Vg<sub>cut</sub>.

- Résolution de l'équation différentielle avec la transconductance gm égale à gm<sub>i</sub>. Ce qui donne l'évolution de la tension de mémorisation Vg (1.26) pour le premier intervalle de temps [0,Tcut].

- Calcul du temps  $T_{cut}$  qui vérifie la relation  $Vg(T_{cut}) = Vg_{cut}$ .

- Résolution de l'équation différentielle avec la transconductance du transistor mémoire égale à  $gm_f$  et les conditions initiales décrites par l'équation (1.28). On obtient l'évolution de la tension de mémorisation Vg (1.29) pour le second intervalle de temps [Tcut, $\infty$ ].

- Le modèle est alors défini par la figure suivante (Fig 1.8).

Fig 1.8 Modélisation "Linéaire par segments" de la cellule

Afin de valider ce modèle, des comparaisons ont été faites entre la prédiction du modèle et une simulation SPICE pour une cellule cascodée. Les résultats de cette comparaison, donnés au chapitre 1.3, montrent que le modèle reste prédictif même pour des amplitudes de courant d'entrée élevées. Le fait de décomposer le temps d'acquisition en deux intervalles prend en compte les deux étapes du transitoire de la cellule:

- La première est la plus courte, elle correspond à t < Tcut. C'est le moment pendant lequel la tension de mémorisation Vg est loin de sa valeur finale. La cellule charge ou décharge la capacité de mémorisation vers la tension  $Vg_f$ .

- La seconde est la plus longue, elle correspond à t > Tcut. La tension de mémorisation est proche de sa valeur finale, elle oscille ou se rapproche de celle ci afin de l'atteindre de manière précise.

Le courant de drain du transistor mémoire Idmem est calculé simplement à partir de la tension de mémorisation. Pour t < Tcut, Idmem est calculé avec l'équation de la droite D1 (1.23). Pour t > Tcut, Idmem est calculé avec l'équation de la droite D2.

L'utilisation de ce modèle pour prédire le transitoire de la cellule à mémoire de courant reste valable si un générateur de courant idéal est à l'entrée de la cellule. Dans le cas réel, ou la cellule reçoit son courant d'une ou plusieurs autres cellules, le transitoire d'acquisition se révèle fort dépendant des commandes d'horloge appliquées aux deux cellules ainsi que du nombre de cellules à l'entrée. Ceci n'est pas encore pris en compte dans le modèle. La section suivante étudie ce problème.

#### 1.2.3 Influence du timing et de l'environnement de la cellule.

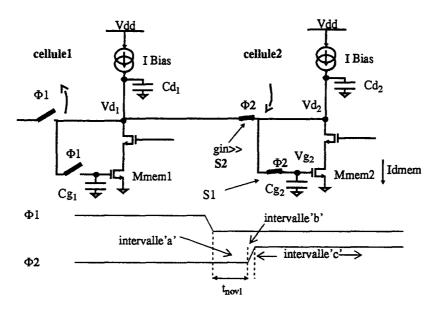

Fig 1.9 Interconnexion de deux cellules

Pour étudier précisément l'influence du timing ainsi que de l'environnement de la cellule à mémoire de courant sur le transitoire d'acquisition, nous allons considérer un cas réaliste d'interconnexion de deux cellules. Au cours de l'acquisition, une cellule à mémoire de courant reçoit son courant d'entrée d'une ou plusieurs autres cellules en phase de restitution (Fig 1.1). L'hypothèse du générateur de courant idéal en entrée de la cellule n'est donc pas réaliste car elle ne prend pas en compte la conductance et la capacité de sortie des cellules en entrée.

La Fig 1.9 donne un exemple de deux cellules interconnectées, la sortie de la cellule1 est connectée à l'entrée de la cellule2. Les interrupteurs Min et Msw des cellules sont commandés par le même signal d'horloge:  $\Phi$ 1 pour la cellule1 et  $\Phi$ 2 pour la cellule2. Le timing du début de la phase d'acquisition est donné par le petit diagramme temporel de la Fig 1.9, il correspond à la succession de trois intervalles distincts:

- L'intervalle'a' correspond au laps de temps entre la fin de l'acquisition de la cellule1 et le début de la phase d'acquisition de la cellule2. Ce temps est forcément non nul car il est nécessaire au bon fonctionnement du circuit. Sans cet intervalle de non recouvrement la cellule2 débuterait son acquisition juste à la fin de la phase d'acquisition de la cellule1 et donc l'information mémorisée par la cellule1 risquerait d'être modifiée.

- L'intervalle'b' est trés court, il correspond au temps de montée du signal d'horloge  $\Phi$ 2, temps pendant lequel les interrupteurs Min et Msw de la cellule2 passent de l'état ouvert à l'état fermé.

- L'intervalles'c' correspond à la phase d'acquisition de la cellule2, c'est donc durant cet intervalle que la cellule est décrite avec le modèle précédent. La durée de l'intervalle'a' correspond au non-recouvrement Tnovl des horloges Φ1 et Φ2.

Les noms des noeuds de sortie des cellule1 et cellule2 sont respectivement Vd1 et Vd2, le nom du noeud de mémorisation de la cellule2 est Vg2. Un exemple d'évolution des tensions

des différents noeuds au cours du timing est donné par la Fig 1.10. Les trois intervalles sont clairement mis en évidence.

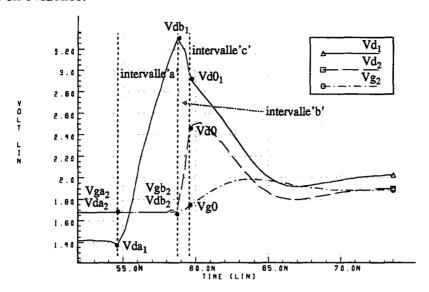

Fig 1.10 Simulation de l'évolution des tensions au cours de la phase d'acquisition

Les valeurs initiales des tensions Vd1, Vd2 et Vg2 sont respectivement appelées Vda1, Vda2 et Vga2. On considère que lors de l'acquisition précédente la cellule2 a mémorisé un courant d'entrée nul. Une telle hypothèse est faite de manière à pouvoir analyser plus simplement le transitoire puisque la valeur initiale de la tension de mémorisation Vg2 est alors connue et en milieu de dynamique.

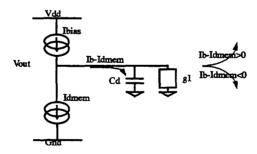

Pendant l'intervalle'a', la tension du noeud Vd1 augmente très rapidement alors que celle du noeud Vd1 reste presque constante. En effet les deux signaux d'horloge sont à l'état bas, les cellules sont donc déconnectées. La différence entre le courant de polarisation Ibias et le courant de drain Idmem mémorisé de la cellule1 crée une variation rapide de la tension du noeud de sortie de la cellule1 puisque cette différence de courant va charger la capacité Cd1 (Fig 1.11). Pour la cellule2 la tension Vd2 ne varie presque pas puisque le courant de drain du transistor mémoire est égal à celui de la source de polarisation.

Fig 1.11 Evolution de la tension de sortie de la CMC pendant l'intervalle'a'.

La variation de la tension du noeud de sortie Vd1 dépend de la différence de courant, de la capacité Cd1 ainsi que du temps de non-recouvrement Tnovl. Pour des valeurs importantes de Tnovl, la variation de Vd1 est telle qu'elle peut forcer l'un des transistors cascodes à se désaturer.

Les valeurs des tensions sur les noeuds Vd1, Vd2 et Vg2 à la fin de l'intervalle 'a' sont respectivement Vdb1, Vdb2 et Vgb2. On voit au cours de l'intervalle'b' que les tensions des

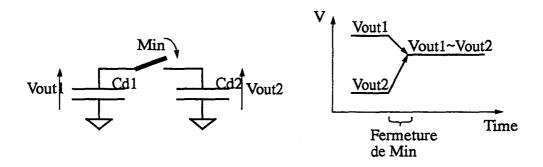

noeuds Vd1 et Vd2 se rapprochent l'une de l'autre rapidement. En effet, suite à la fermeture du transistor d'entrée de la cellule2, la différence entre ces deux tensions va donc créer une redistribution de charge instantanée entre ces deux capacités. A la fin de l'intervalle b les tensions des noeuds Vd1 et Vd2 seront presque identiques (Fig 1.12). La différence de potentiel résiduelle entre ces deux noeuds est due à la chute de potentiel dans l'interrupteur d'entrée de la cellule2.

Fig 1.12 Redistribution des charges instantanée lors de l'intervalle'b'.

Au début de l'intervalle c les tensions des noeuds Vd2, Vg2 et Vd1 sont respectivement Vd0, Vg0 et Vd0<sub>1</sub>. Ces tensions seront utilisées comme conditions initiales pour le modèle "linéaire par segments".

Ces conditions initiales sont différentes de celles utilisées lors de la description du modèle, en effet la tension du noeud de sortie de la cellule2, Vd2, est différente de sa tension de mémorisation Vg2 du fait de la redistribution de charge entre les capacités Cd1 et Cd2. Cette différence entre la tension Vg2 et la tension Vd2 aura pour conséquence sur le fonctionnement de la cellule d'augmenter la perturbation initiale et donc augmentera la valeur de l'overshoot.

Cette désaturation des cellules pendant le non-recouvrement des horloges doit être pris en compte pour avoir une modélisation temporelle précise de la cellule à mémoire de courant. La section suivante donne la description du modèle complet proposé qui prend en compte tout les problèmes énoncés.

#### 1.2.4 Modèle complet

Le modèle temporel complet de la cellule à mémoire de courant est décomposé en trois parties, décrivant le comportement de la cellule dans chacun des trois intervalles décrits précédemment.

intervalle 'a'. L'évolution de la tension des noeuds de sortie Vd1 et Vd2 lors du non-recouvrement des horloges Φ1 et Φ2 est modélisé. Pour cela, nous utilisons un modèle petit signal du premier ordre décrit dans la Fig 1.13. La conductance g1 modélise la conductance de sortie de la cellule à mémoire de courant. Une équation différentielle du premier ordre décrit le circuit.

Pendant l'intervalle 'a', une large variation de la tension du noeud de sortie Vd1 ou Vd2 peut désaturer l'un des transistors cascode. Il en résultera une brusque variation de la conductance g1, Une approximation "linéaire par segments" est alors utilisée pour modéliser cette brusque transition. On calcule les deux valeurs (Vdsatp et Vdsatn) de la tension de sortie qui limitent la région de fonctionnement saturé de la cellule. La conductance g1 est alors calculée dans cette région et en dehors.

On obtient donc trois valeurs de la conductance. L'équation différentielle est résolue pour les trois valeurs possibles de la conductance g1. La transition entre les trois solutions est assurée par la continuité électrique de la tension du noeud de sortie Vd1 ou Vd2.

Le modèle de la cellule permet de calculer la valeur de la tension du noeuds de sortie à la fin de l'intervalle 'a', soit Vdb1 et Vdb2, en fonction du temps de non-recouvrement Tnovl et des valeurs de tension initiales Vda1 et Vda2.

Fig 1.13 Modélisation petit signal de la désaturation des cellules

intervalle 'b'. Durant ce court laps de temps, la redistribution des charges entre les deux capacités de sortie des cellules Cd1 et Cd2 est modélisée. Cette redistribution des charges est causée par la différences entres les deux tensions Vdb1 et Vdb2 de sortie des cellules à la fin de l'intervalle 'a'. Après la redistribution des charges la tension de sortie des deux cellules est presque égale, la seule différence est due à la différence de potentiel aux bornes de l'interrupteur d'entrée de la cellule2. La valeur de la tension du noeud de sortie de la cellule2 Vd0 à la fin de l'intervalle 'b' est calculée de la manière suivante:

$$Vd0 = \frac{Cd_1Vdb_1 + Cd_2Vdb - \frac{Cd_1Iin}{gin}}{Cd_1 + Cd_2}$$

(1.30)

gin est la conductance de l'interrupteur d'entrée de la cellule2.

intervalle 'c'. A la fin de l'intervalle 'b' la tension du noeud Vd2 a pour valeur Vd0, cette valeur sera utilisée pour calculer les conditions initiales nécessaires au modèle de la cellule pendant la phase d'acquisition. En effet l'intervalle 'c' représente la phase d'acquisition effective de la cellule2, l'évolution de la tension de mémorisation Vg ainsi que du courant de drain du transistor mémoire y sont décrits. Pour cela on utilisera le modèle développé au souschapitre 1.2.2 avec trois modifications:

. La capacité de sortie Cd doit être la somme des capacités de sortie de la cellule1 et de la cellule2. En effet la conductance de l'interrupteur d'entrée de la cellule2 est assez faible pour considérer ces deux capacités en parallèle. on a donc:

$$Cd = Cd1 + Cd2 \tag{1.31}$$

- . Le temps t=0 du modèle correspond au début de l'intervalle 'c'.

- . Les conditions initiales données par l'équation (1.15) ne sont plus valables. La

valeur initiale de la tension de mémorisation Vg2 est égale à la tension de ce noeud au début de l'intervalle 'a' soit Vga2. La valeur initiale de la dérivée de la tension de mémorisation Vg2 par rapport au temps à t=0 n'est plus nulle mais est déduite de la valeur de la tension de sortie Vd2 avec l'équation suivante:

$$Vd2 = Vg2 + \frac{Cg2}{gon} \cdot \frac{d}{dt}Vg2 \tag{1.32}$$

Cette équation provient de la première partie de l'équation (1.8) appliquée à la cellule2. Elle permet donc de calculer la dérivée de la tension Vg2 à t=0 de la manière suivante:

$$\frac{d}{dt}Vg2(0) = \frac{gon}{Cg2} \cdot (Vd0 - Vg2(0)) \qquad Vg2(0) = Vga2$$

(1.33)

Les conditions initiales à t=0 pour le modèle de la cellule à mémoire de courant durant la phase d'acquisition sont donc données par l'équation (1.33).

Le modèle ainsi présenté permet de décrire de manière précise le comportement temporel de la cellule à mémoire de courant au cours de la phase d'acquisition. Ce modèle est facilement implémentable dans un simulateur de circuits à courant commuté.

Une validation de ce modèle avec une simulation SPICE est présentée dans le souschapitre suivant. Une méthodologie de test permettant de mesurer l'évolution du courant de drain du transistor mémoire durant la phase d'acquisition et donc de valider expérimentalement le modèle sera aussi présentée.

#### 1.3 Validation numérique du modèle

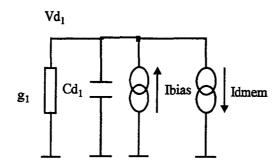

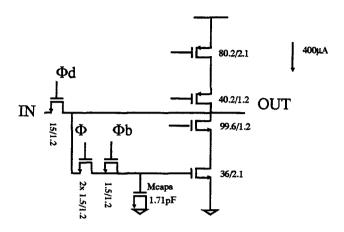

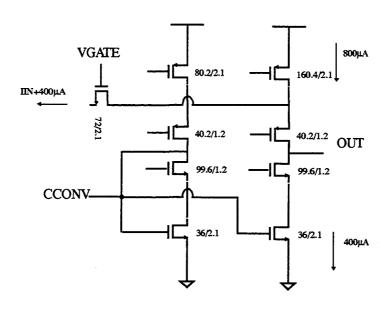

Pour valider le modèle une simulation électrique des deux cellules dans la configuration de la Fig 1.9 a été réalisée sur le simulateur HPSICE. La cellule à mémoire de courant est du type cascodée. Le courant de bias est fixé à 400µA, la dynamique d'entrée du courant est de +200µA à 200µA. Les tailles des transistors employés sont données dans la Fig 1.14.

Fig 1.14 Cellule à mémoire de courant implémentée

Cette cellule sera réalisée pour la confrontation expérimentale, la technologie utilisée est la 1.2µm ES2. Les paramètres petits signaux utilisés dans le modèle sont:

$$Cd_2 = 0.3pF$$

$Cd_1 = 0.33pF$   $Cg_2 = 1.71pF$

$$gon = 349\mu S$$

$$gmf = 611\mu S (-200\mu A) \qquad gmf = 978\mu S (200\mu A)$$

$$gin = 1.7mS \qquad gmi = 824\mu S$$

La transconductance finale  $gm_f$  est donnée pour les valeurs extrêmes du courant d'entrée. Les capacité  $Cd_1$  et  $Cd_2$  sont parasites. La capacité  $Cg_2$  est essentiellement due au transistor Mcapa. Le coefficient d'amortissement z varie entre 0.85 et 0.67 en fonction du courant d'entrée. La cellule à mémoire de courant est bien en régime sous amorti.

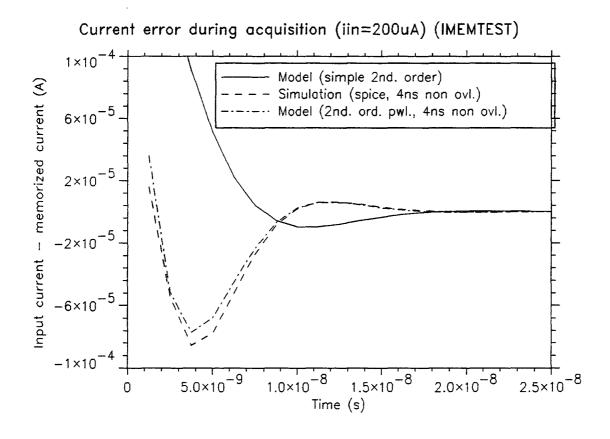

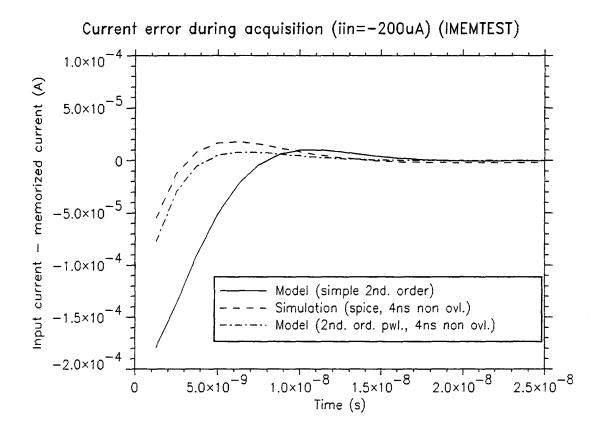

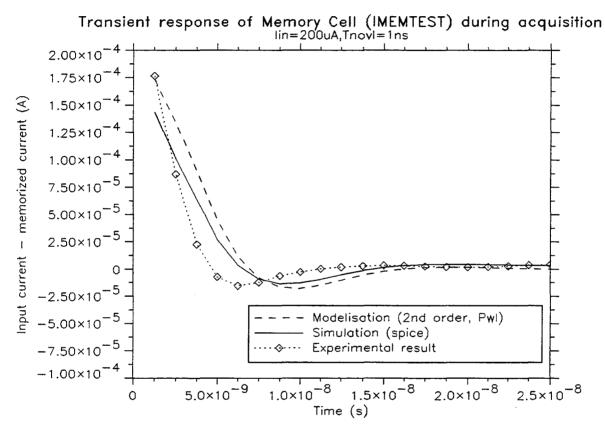

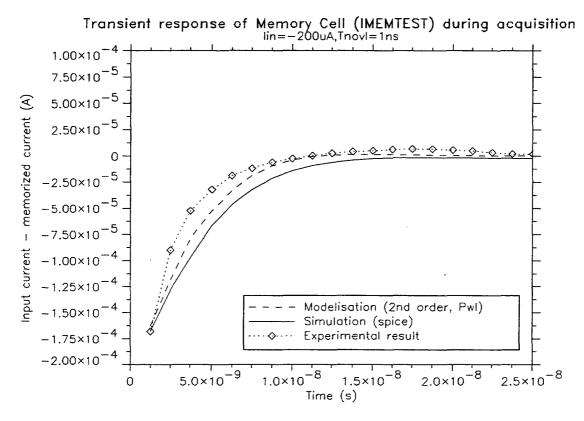

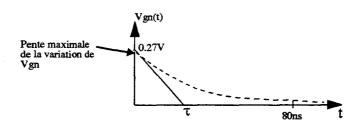

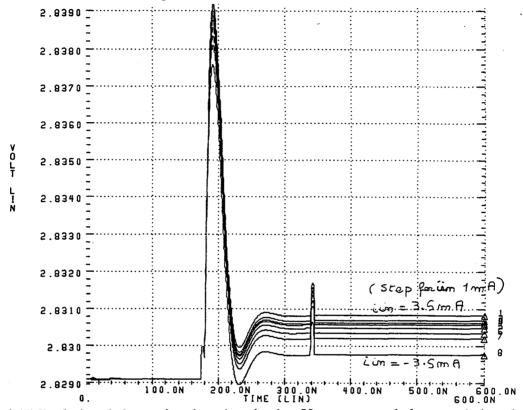

La simulation du régime transitoire a été faite sous matlab pour le modèle présenté. Afin de pouvoir comparer ultérieurement le modèle avec les résultats expérimentaux, on s'intéressera à l'évolution du courant de drain du transistor mémoire et non à la tension de mémorisation. Pour les résultats, on observe l'évolution de l'erreur d'acquisition en courant en fonction du temps de la phase d'acquisition. Cette erreur est calculée en faisant la différence entre le courant qui serait mémorisé si la phase d'acquisition était infinie et le courant mémorisé pour une phase d'acquisition de durée t (1.35). Cette différence représente en fait l'erreur de courant à l'instant t.

$$I\varepsilon(t) = Idmem(\infty) - Idmem(t) \tag{1.35}$$

Les Fig 1.15 et Fig 1.16 donnent une comparaison entre la simulation HSPICE, le modèle présenté (2nd. ord. pwl.) et le modèle classique du second ordre (2nd. order). Cette comparaison a été faite pour deux valeurs du courant d'entrée +200µA et -200µA. Le temps de non-recouvrement Tnovl entre les horloges de commande des cellules est de 4ns. On voit sur ces figures que le modèle du second ordre classique n'est pas prédictif, alors que le modèle proposé est trés prés de la simulation obtenue avec HSPICE. Pour le cas où Iin= +200µA, le fort overshoot de 80µA (40% du step de courant en entrée) est essentiellement du au non-recouvrement des horloges de 4ns. Le modèle du second ordre ne prends pas en compte ce temps de non-recouvrement ce qui explique la faible valeur de l'overshoot obtenu avec ce modèle. Pour Iin =200µA le temps d'établissement normalisé à 0.1% (l'erreur vaut 0.1% du step de courant) est de 22ns. La prédiction de ce temps d'établissement obtenue avec le modèle proposé est identique.

Dans le chapitre 2, le modèle sera validé expérimentalement. Ce modèle proposé permet donc de simuler le transitoire d'une cellule à mémoire de courant de manière précise. Comparé à HSPICE il est beaucoup moins gourmand en temps CPU. Une fois incorporé dans le simulateur de circuits à mémoire de courant, ce modèle permettra d'étudier l'influence de la fréquence d'horloge du circuit sur ses caractéristiques.

Fig 1.15 Evolution de l'erreur d'acquisition pour Iin= +200µA

Fig 1.16 Evolution de l'erreur d'acquisition pour Iin= -200µA

#### 1.4 Références bibliographiques

- [1] S.J. DAUBERT, D. VALLANCOURT and Y. TSIVIDIS Current Copier Cells. Electronics Letters, Vol. 24, No 25, 8th Dec. 1988, pp. 1560 - 1562.

- [2] G. WEGMANN, E. A. VITTOZ

Very Accurate Dynamic Current Mirrors.

Electronics Letters, Vol. 25, No 10, 11th May. 1989, pp.644 646.

- [3] G. WEGMANN, E. A. VITTOZ and F. RAHALI Charge Injection in Analog MOS Switches. IEEE Journal of Solid-State Circuits, Vol. 22, No. 6, Dec 1987, pp.1091 - 1097.

- [4] C. EICHENBERGER and W. GUGGENBUHL

On Charge Injection in Analog Switches and Dummy Switch Compensation

Techniques.

IEEE Transactions on Circuits and Systems, Vol. 37, No. 2, Feb 1990, pp.256 264.

- [5] P. N'GORAN, A. KAISER, B. STEFANELLI, N. MOENECLAEY Discrete-Time Simulation of Current-Memory Sigma-Delta Modulators. In proceedings of ESSCIRC'93, pp 29-32, Sep. 1993.

- [6] C. TOUMAZOU, J. B. HUGHES and D. M. PATTULO Regulated Cascode Switched-Current Memory Cell. Electronics Letters, Vol. 26, No. 5, 1st Mar. 1990, pp.303 - 305.

- [7] N.MOENECLAEY, A. KAISER

Accurate Modelling of the Non-Linear Settling Behaviour of Current Memory

Circuits.

in proceedings of ISCAS'94, CAD9.8, Vol. 1 pp 339-342, June 1994.

- [8] P. DEVAL

Convertisseurs Analogiques-Numériques Cycliques à Mémoire de Courant CMOS.

Thèse No. 1001, Ecole Polytechnique de Lausanne, Suisse, 1992, pp.34-48

- [9] P. E. ALLEN and D. R. HOLDERG

CMOS Analog Circuit Design.

Saunders College Publishing, 1987, pp. 685 693

## Chapitre 2

# Caractérisation des principaux effets limitatifs des cellules à mémoire de courant

L'étude et la modélisation des effets limitatifs de la cellule à mémoire de courant nécessite un moyen de caractérisation expérimental. Une méthodologie de test des cellules est proposée dans ce chapitre. Elle consiste en une topologie particulière reproduisant l'environnement de fonctionnement normal des cellules à mémoire de courant. Un circuit de caractérisation, la manipulation de test ainsi que les résultats obtenus sont détaillés à la fin de ce chapitre.

# 2.1 Méthodologie de caractérisation des Cellules à Mémoire de Courant

Les performances des circuits à courant commuté tels les convertisseurs analogiquesnumériques ou les lignes à retard, sont essentiellement déterminées par les limitations de la cellule à mémoire de courant. A ma connaissance, aucune méthode dédiée spécialement à la caractérisation des cellules à mémoire de courant n'a été proposée à ce jour, mis à part des approches d'analyse et de mesure de la charge injectée par l'interrupteur d'échantillonnage [1][2].

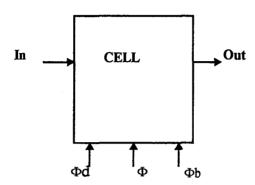

Fig 2.1 Symbole de la cellule à mémoire de courant.

La mesure des caractéristiques d'une cellule à mémoire de courant permet de valider son étude et son architecture ainsi que les performances obtenues par simulation avec SPICE ou le macro-modèle proposé. Une telle expérimentation nécessite a fabrication d'un circuit de test qui doit reproduire autour de la cellule son "environnement" normal de fonctionnement.

Cette section présente une topologie de circuit de test [4] qui a été utilisée pour caractériser une cellule à mémoire de type cascode. La méthode de mesure ainsi que le "timing" des horloges de commande sont présentés. Les caractéristiques étudiées dans cette section sont l'injection de charge, la conductance de sortie, l'erreur de copie ainsi que le comportement transitoire de la cellule. Par soucis d'alléger les schémas, un symbole simple de la cellule à mémoire de courant à été créé. La Fig 2.1 décrit ce symbole, les noms des différentes entrées et sorties correspondent à ceux de la Fig 1.14.

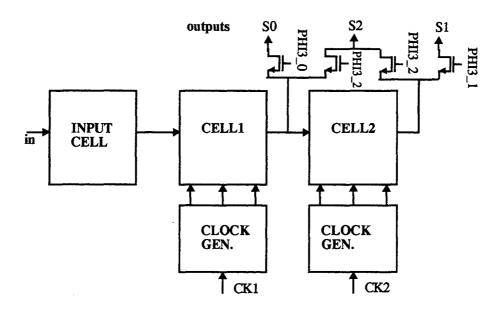

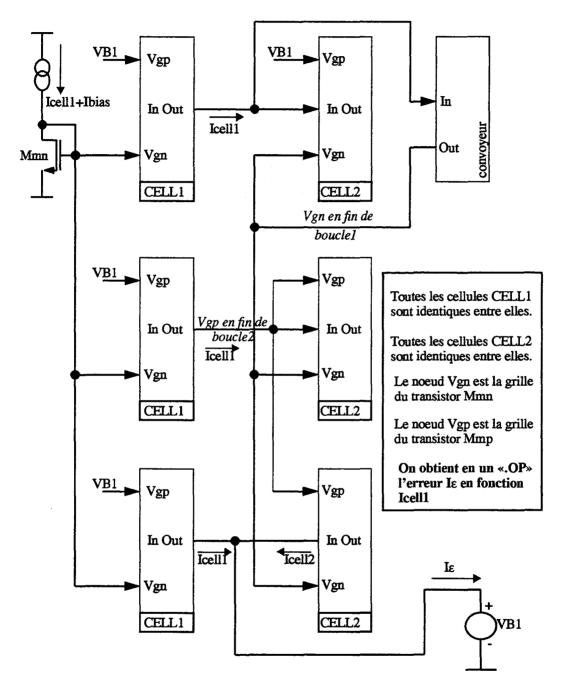

#### 2.1.1 Topologie du circuit de caractérisation

La topologie peut s'appliquer à n'importe quel type de cellule à mémoire de courant. La cellule doit seulement comporter un interrupteur auxiliaire de compensation de l'injection de charge dont le fonctionnement peut être inhibé par une commande externe. Cet interrupteur sera utile à la mesure du coefficient d'injection de charge  $K_i$ .

La topologie de caractérisation est décrite dans la Fig 2.2. Elle consiste en un circuit d'entrée suivi par deux cellules à mémoire de courant cascadées. Ce circuit d'entrée est dérivé d'une cellule, mais il fonctionne de manière statique. Chacune des cellules possède un circuit de génération de la commande des interrupteurs d'échantillonnage, d'entrée et de compensation. Des interrupteurs permettent d'orienter la sortie des cellules vers trois plots de mesure extérieure. Dans cette topologie, la CELL2 mémorise l'inverse du courant de sortie de la CELL1, le fait de lire directement la somme des sorties des deux cellules permet de mesurer la différence entre l'entrée et la sortie de la CELL2, soit son erreur de mémorisation. Cette

astuce sera trés largement utilisée pour caractériser le comportement transitoire de la cellule, l'erreur de recopie ainsi que la charge injectée sur la capacité de mémorisation.

Fig 2.2 Tolopogie de caractérisation des cellules à mémoire de courant.

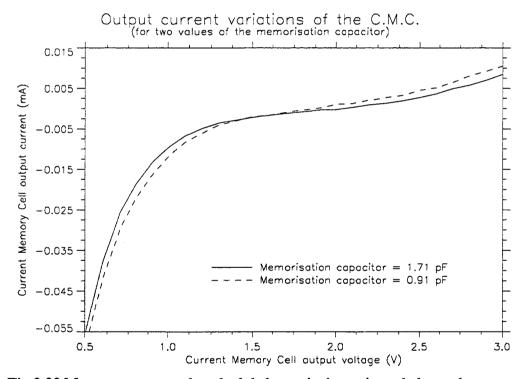

Le composant de test doit comprendre au minimum deux circuits utilisant cette topologie avec une valeur différente de la capacité de mémorisation Cg des cellules employées. Par exemple Cg pour le premier circuit et Cg/2 pour le second. Ceci permet de déterminer la part dynamique de la conductance de sortie de la cellule à mémoire de courant.

#### 2.1.2 Caractéristiques mesurées

#### 2.1.2.1 Comportement transitoire de la cellule

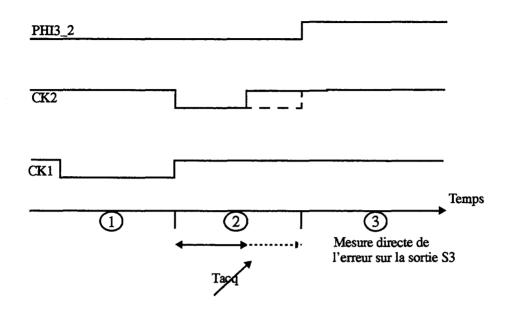

Une des caractéristiques importantes de la cellule est le temps de stabilisation en phase d'acquisition. L'erreur d'établissement correspond à la différence entre le courant acquis par la cellule en un temps d'acquisition infini et le courant acquis en un temps d'acquisition  $T_{acq}$  (1.35). L'évolution de cet erreur  $I_{\epsilon}$  en fonction du temps d'acquisition  $T_{acq}$  permet d'obtenir l'évolution du courant de drain du transistor mémoire au cours de la phase d'acquisition et donc de connaître la forme du transitoire. L'évolution de l'erreur d'acquisition en fonction du temps ne peut pas être mesurée au cours d'une seule acquisition. La méthode de mesure consiste donc à mesurer l'erreur sur le courant acquis par la cellule pour différentes valeurs du temps d'acquisition. On peut ensuite reconstituer l'évolution de l'erreur d'acquisition en fonction du temps.

La mesure de l'erreur de courant Ie se fait en trois opérations (la Fig 2.3 montre les signaux de commande correspondant à chaque opération):

- Premièrement, la CELL1 fait l'acquisition du courant d'entrée voulu pendant un intervalle de temps fixe et assez élevé pour considérer l'erreur de stabilisation de la CELL1 négligeable.

- La CELL2 fait l'acquisition du courant de sortie de la CELL1 pendant un temps d'acquisition donné  $T_{acq}$ .

- On mesure la somme des courants de sortie des deux cellules sur le plot de mesure S2. En raison du changement de signe introduit par la CELL2, ce signal est

égal à l'erreur d'acquisition que l'on cherche à mesurer.

Ces trois étapes ont permis d'obtenir l'erreur d'établissement de la CELL2 pour une valeur définie du temps d'acquisition  $T_{acq}$ . Pour obtenir la forme et le type de transitoire il faut répéter ces trois opérations pour plusieurs valeur du temps d'acquisition  $T_{acq}$ .

Fig 2.3 Chronogramme des horloges pour la mesure.

Pour que cette mesure soit valide, il faut s'assurer que le courant de fuite de l'interrupteur d'échantillonnage crée une variation négligeable de la tension mémorisée par les deux cellules durant la durée de la troisième opération.

On obtient ainsi une évolution de l'erreur d'acquisition pour un courant d'entrée Iin donné. Il faut recommencer la même manipulation pour les autres valeurs du courant Iin voulues.

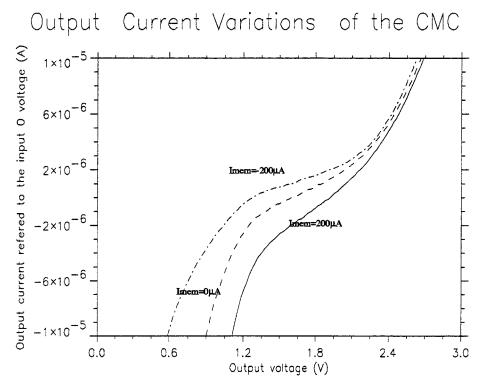

#### 2.1.2.2 Conductance de sortie

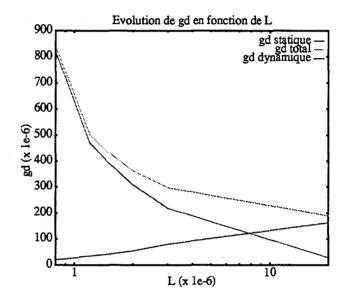

Fig 2.4 Conductance de sortie statique et dynamique

La conductance de sortie de la cellule à mémoire de courant contribue fortement à la

non-linéarité de l'erreur de recopie. il convient donc de pouvoir la mesurer pour plusieurs valeurs de courant de sortie et aussi pour plusieurs valeurs de tension de sortie. L'origine de la conductance de sortie est double, la partie statique provient de l'effet Early des transistors, la partie dynamique provient du couplage capacitif dû à la capacité grille-drain du transistor mémoire (Fig 2.4). Il est intéressant de pouvoir déterminer la répartition de la conductance entre ces deux contributions. La topologie de caractérisation proposée permet de mesurer la conductance totale ainsi que la partie dynamique de cette conductance, la partie statique est déduite de la différence des deux.

La caractéristique courant de sortie en fonction de la tension peut être aisément mesurée sur la sortie S0 ou S1 en mesurant la variation du courant de sortie induite par une variation du potentiel de sortie autour du potentiel moyen (1.7 V). La conductance de sortie à un potentiel donné est alors obtenue en calculant la dérivée en ce point. En répétant ce calcul autour de diverses valeurs de potentiel, on obtient l'évolution de la conductance en fonction de la tension de sortie.

La partie dynamique de la conductance de sortie est extrapolée de la conductance totale mesurée pour deux valeurs de la capacité de mémorisation  $C_g$  et  $C_g/2$ . En effet, comme la capacité parasite  $C_{gd}$  est négligeable devant la capacité de mémorisation  $C_g$ , l'équation (1.6) peut être approximée de la manière suivante:

$$g_{dyn} = gm \cdot \frac{C_{gd}}{C_g} \tag{2.1}$$

La conductance dynamique est donc proportionnelle à l'inverse de la capacité mémoire. En faisant la différence des deux conductances totales pour les deux valeurs de capacité mémoire, on obtient la valeur de la conductance dynamique:

$$g_{tot}\left(\frac{C_g}{2}\right) - g_{tot}(C_g) = gm \cdot \left(\frac{C_{gd}}{\left(\frac{C_g}{2}\right)} - \frac{C_{gd}}{C_g}\right) = g_{dyn}$$

(2.2)

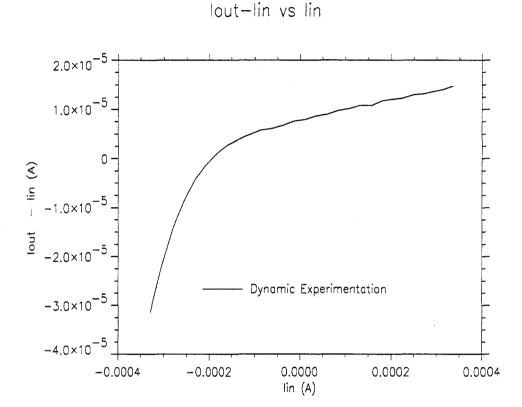

#### 2.1.2.3 L'erreur de recopie

L'erreur de recopie caractérise la précision de la cellule à mémoire de courant, en effet elle permet de quantifier l'erreur en fonction du courant d'entrée mais surtout elle permet de visualiser la non-linéarité de la cellule. Cette dernière résulte de la caractéristique tension-courant non-linéaire du transistor mémoire quand il est monté en diode. Cette variation de tension non-linéaire influe le courant mémorisé par l'intermédiaire de la conductance de sortie de la cellule en restitution. La valeur de la conductance de sortie joue donc un rôle important dans la précision de la cellule.

Pour obtenir l'évolution de l'erreur de recopie en fonction du courant d'entrée, il faut dérouler les trois étapes de la mesure de l'erreur d'établissement, mais pour une grande valeur de temps d'acquisition  $T_{acq}$ , de sorte à négliger l'erreur d'établissement face à l'erreur de recopie. Il faut répéter cette manipulation pour plusieurs valeurs de courant d'entrée de sorte à obtenir l'évolution de l'erreur de copie en fonction du courant d'entrée. Cette mesure est plus difficile, l'erreur de recopie est plus petite que l'erreur d'établissement.

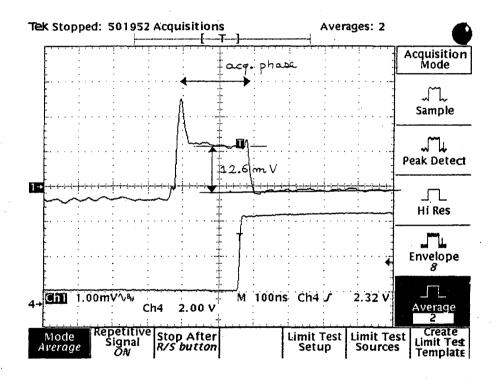

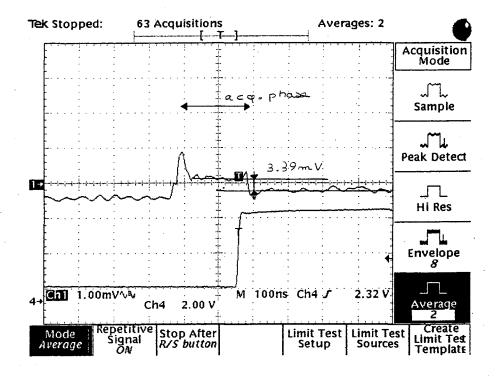

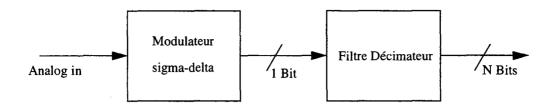

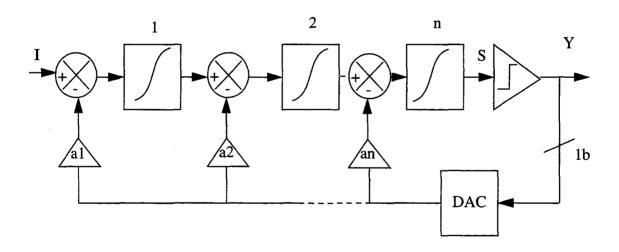

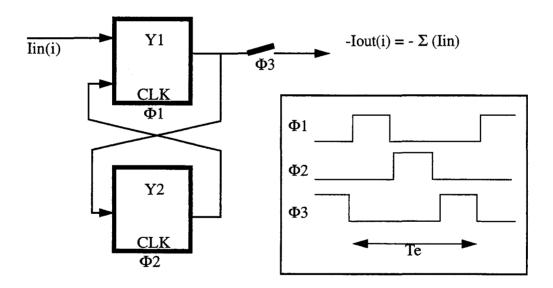

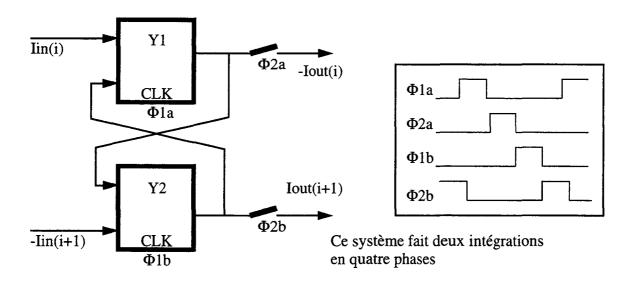

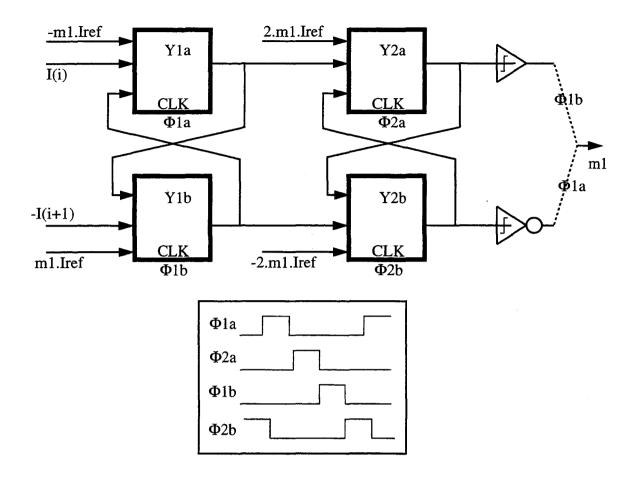

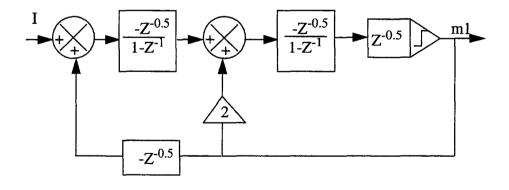

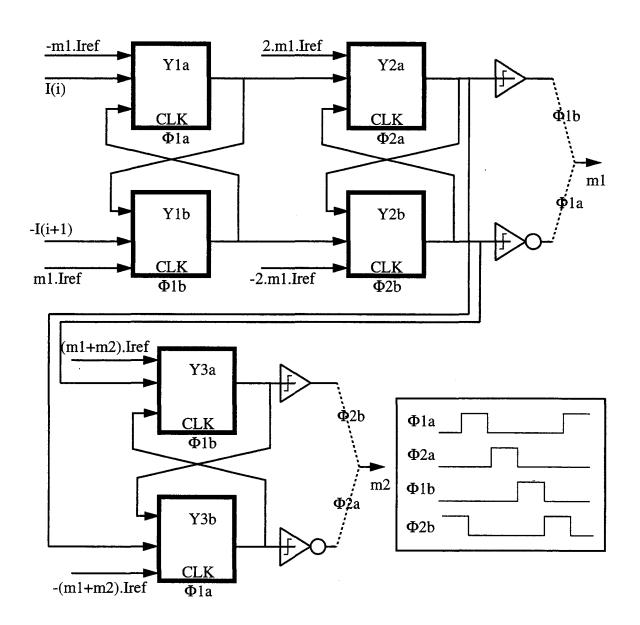

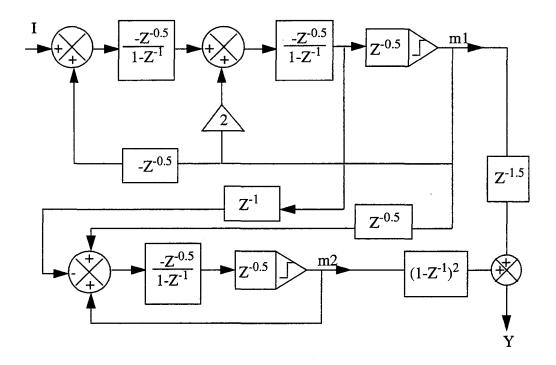

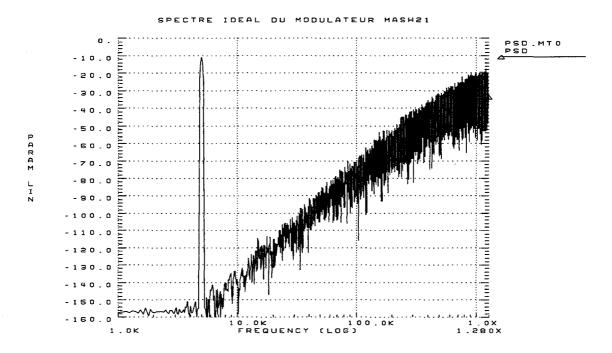

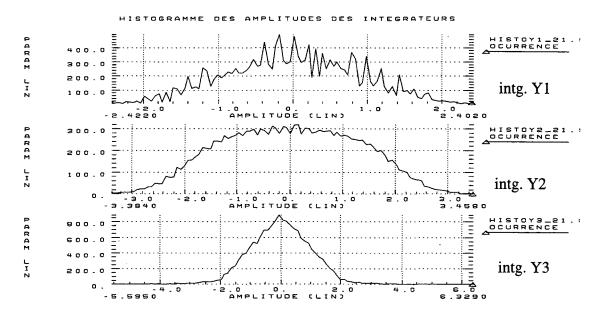

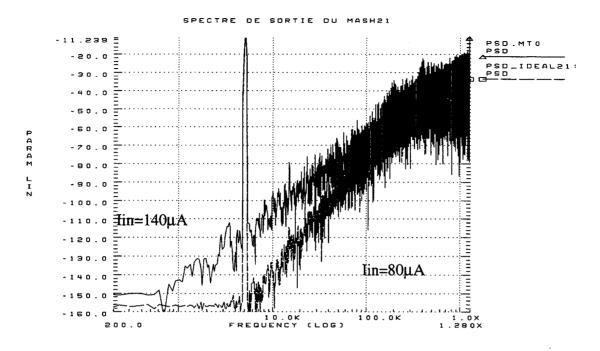

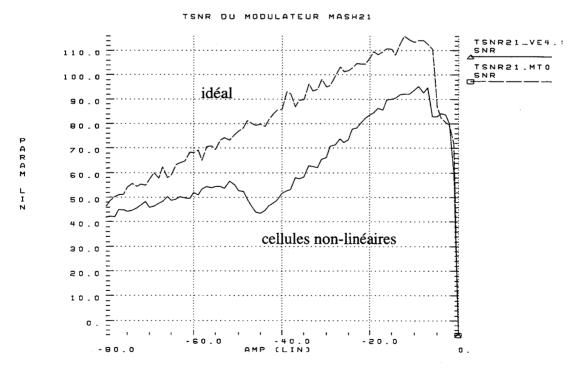

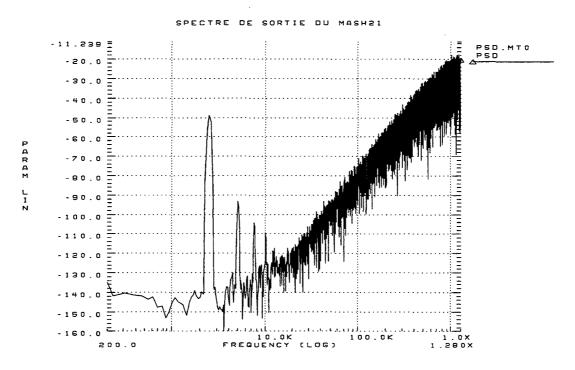

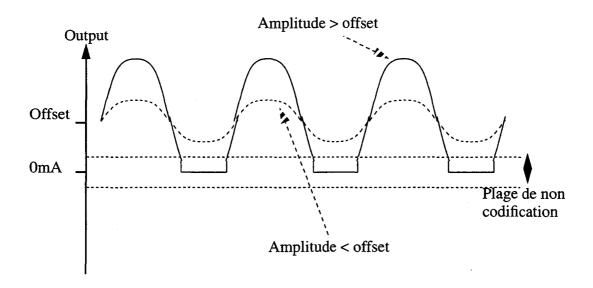

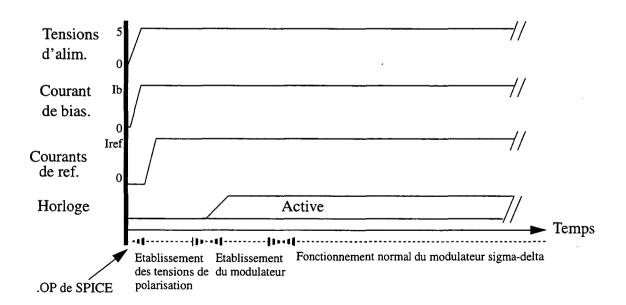

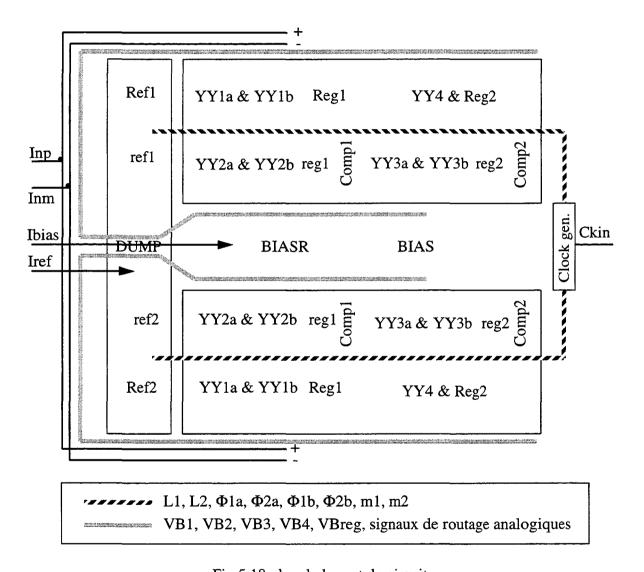

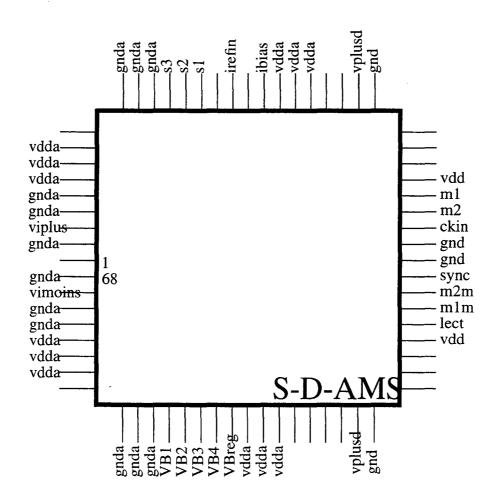

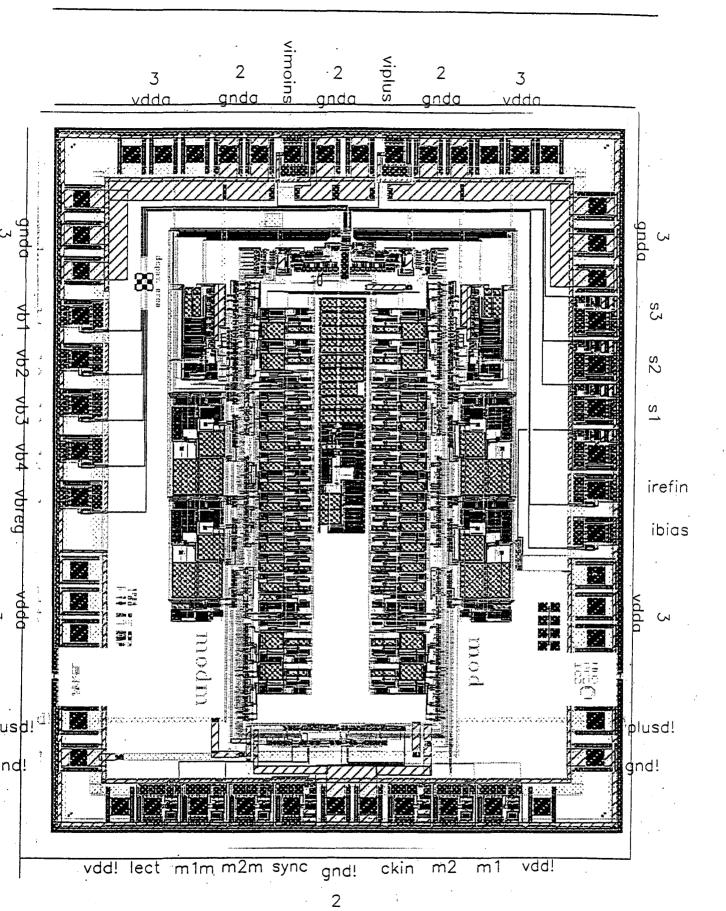

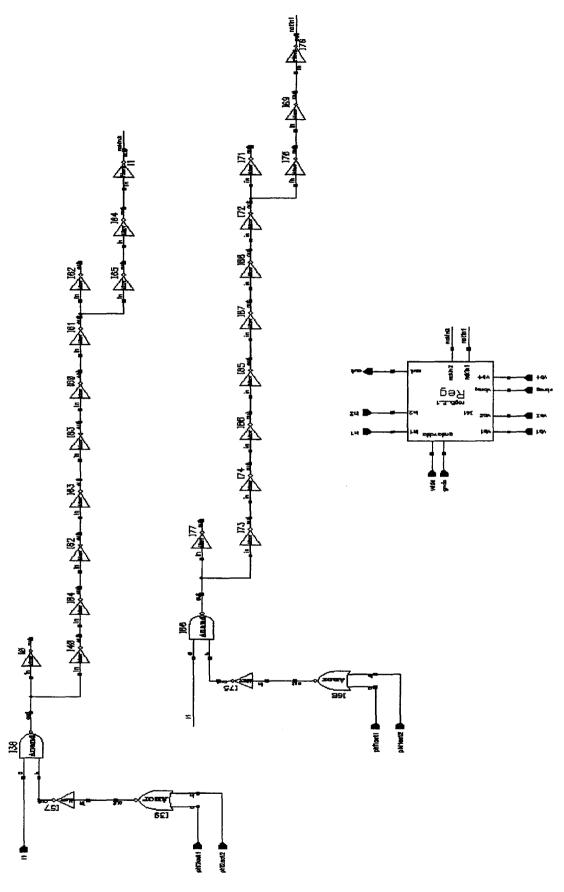

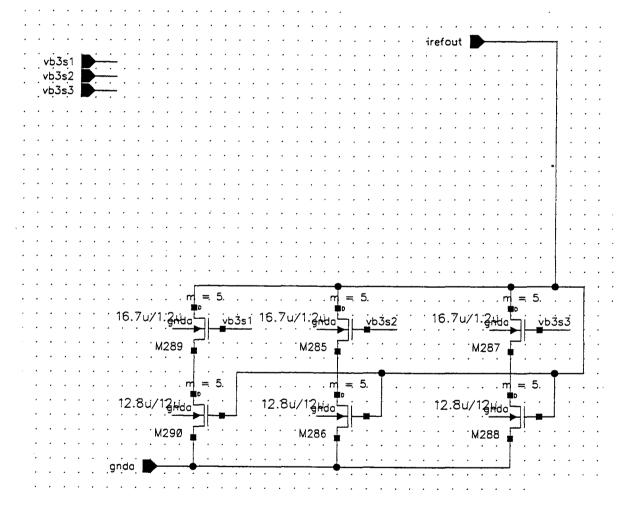

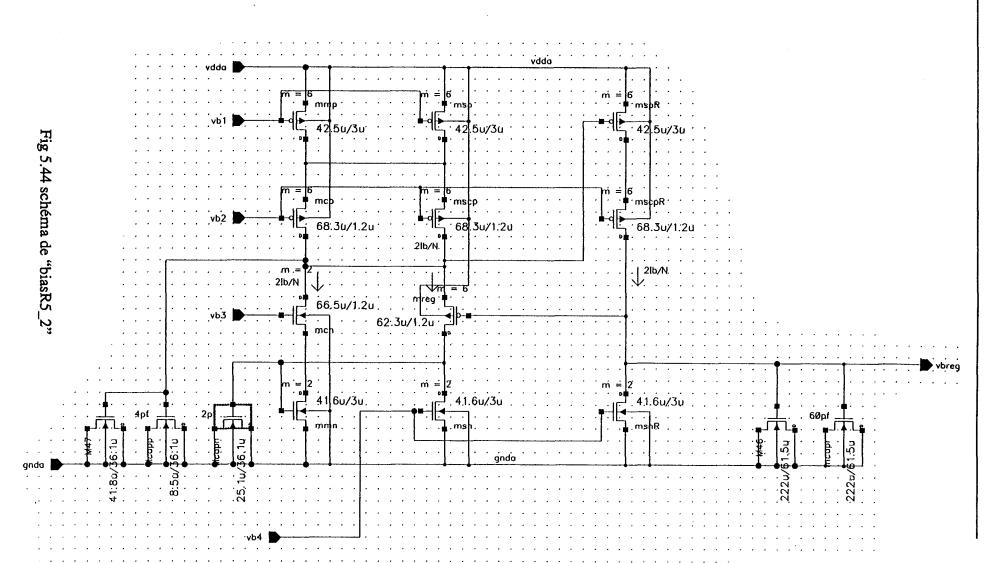

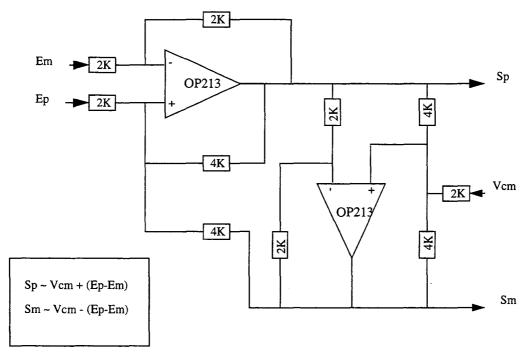

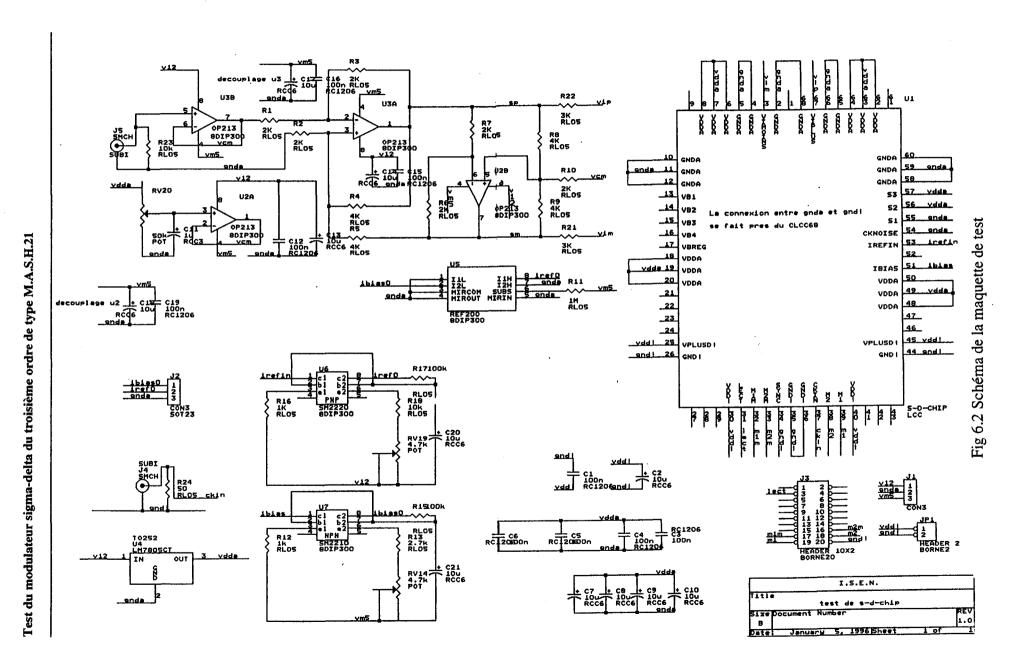

#### 2.1.2.4 la charge injectée par l'interrupteur d'échantillonnage.