## THÈSE

## présentée à L'UNIVERSITÉ DES SCIENCES ET TECHNOLOGIES DE LILLE

## pour obtenir le titre de DOCTEUR en INFORMATIQUE

## David GALINEC

Exécution asynchrone de programmes synchrones par transformations automatiques: application au traitement d'images temps-réel

Thèse qui sera soutenue le 27 janvier 1997, devant la commission d'examen:

Rapporteurs:

Dominique MERY

Université Henri Poincaré, Nancy 1 & IUF

Examinateurs:

Edwige PISSALOUX Mireille CLERBOUT PSI-La3I, Université de Rouen

Marie-Jean Colaïtis

LIFL, Université de Lille 1

Jean-Luc Dekeyser

THOMSON MULTIMEDIA, Rennes

LIFL, Université de Lille 1

Philippe MARQUET LIFL, Université de Lille 1

UNIVERSITE DES SCIENCES ET TECHNOLOGIES DE LILLE LIFL - URA 369 CNRS - Bât, M3 - UFR IEEA - 59655 VILLENEUVE D'ASCQ CEDEX Tel: (33) 63 20 43 44 92 - Fax: (33) 03 20 43 65 66 - E mail: direction@lift.fr

### DOYENS HONORAIRES DE L'ANCIENNE FACULTE DES SCIENCES

M. H. LEFEBVRE, M. PARREAU

# PROFESSEURS HONORAIRES DES ANCIENNES FACULTES DE DROIT ET SCIENCES ECONOMIQUES, DES SCIENCES ET DES LETTRES

MM. ARNOULT, BONTE, BROCHARD, CHAPPELON, CHAUDRON, CORDONNIER, DECUYPER, DEHEUVELS, DEHORS, DION, FAUVEL, FLEURY, GERMAIN, GLACET, GONTIER, KOURGANOFF, LAMOTTE, LASSERRE, LELONG, LHOMME, LIEBAERT, MARTINOT-LAGARDE, MAZET, MICHEL, PEREZ, ROIG, ROSEAU. ROUELLE, SCHILTZ, SAVARD, ZAMANSKI, Mes BEAUJEU, LELONG.

#### PROFESSEUR EMERITE

M. A. LEBRUN

## ANCIENS PRESIDENTS DE L'UNIVERSITE DES SCIENCES ET TECHNIQUES DE LILLE

MM. M. PARREAU, J. LOMBARD, M. MIGEON, J. CORTOIS, A.DUBRULLE

## PRESIDENT DE L'UNIVERSITE DES SCIENCES ET TECHNOLOGIES DE LILLE

M. P. LOUIS

#### PROFESSEURS - CLASSE EXCEPTIONNELLE

M. CHAMLEY Hervé

M. CONSTANT Eugène

M. ESCAIG Bertrand M. FOURET René

M. GABILLARD Robert

M. LABLACHE COMBIER Alain

M. LOMBARD Jacques M. MACKE Bruno

Géotechnique Electronique

Physique du solide Physique du solide

Electronique

Chimie Sociologie

Physique moléculaire et rayonnements atmosphériques

M. TURREL Georges

M. VANDIJK Hendrik

Mme VAN ISEGHEM Jeanine

M. VANDORPE Bernard

M. VASSEUR Christian

M. VASSEUR Jacques

Mme VIANO Marie Claude

M. WACRENIER Jean Marie

M. WARTEL Michel

M. WATERLOT Michel

M. WEICHERT Dieter

M. WERNER Georges

M. WIGNACOURT Jean Pierre

M. WOZNIAK Michel

Mme ZINN JUSTIN Nicole

## Spectrochimie infrarouge et raman

Modélisation, calcul scientifique, statistiques

Chimie minérale

Automatique

Biologie

Electronique

Chimie inorganique

géologie générale

Génie mécanique

Informatique théorique

Spectrochimie

Algèbre

M. MIGEON Michel M. MONTREUIL Jean M. PARREAU Michel M. TRIDOT Gabriel EUDIL Biochimie Analyse Chimie appliquée

## PROFESSEURS - 1ère CLASSE

M. BACCHUS Pierre M. BIAYS Pierre M. BILLARD Jean M. BOILLY Bénoni

M. BONNELLE Jean Pierre

M. BOSCQ Denis

M. BOUGHON Pierre

M. BOURIQUET Robert

M. BRASSELET Jean Paul

M. BREZINSKI Claude

M. BRIDOUX Michel

M. BRUYELLE Pierre

M. CARREZ Christian

M. CELET Paul

M. CARREZ Christian

M. CELET Paul

M. COEURE Gérard

M. CORDONNIER Vincent

M. CROSNIER Yves

Mme DACHARRY Monique

M. DAUCHET Max

M. DEBOURSE Jean Pierre

M. DEBRABANT Pierre

M. DECLERCQ Roger

M. DEGAUQUE Pierre

M. DESCHEPPER Joseph

Mme DESSAUX Odile

M. DHAINAUT André

Mme DHAINAUT Nicole M. DJAFARI Rouhani M. DORMARD Serge M. DOUKHAN Jean Claude

M. DUBRULLE Alain

M. DUPOUY Jean Paul

M. DYMENT Arthur

M. FOCT Jacques Jacques

M. FOUQUART Yves

M. FOURNET Bernard

M. FRONTIER Serge M. GLORIEUX Pierre M. GOSSELIN Gabriel M. GOUDMAND Pierre

M. GRANELLE Jean Jacques

M. GRUSON Laurent

M. GUILBAULT Pierre

M. GUILLAUME Jean

M. HECTOR Joseph

M. HENRY Jean Pierre

M. HERMAN Maurice

M. LACOSTE Louis

M. LANGRAND Claude

Astronomie Géographie

Physique du Solide

Biologie

Chimie-Physique Probabilités Algèbre

Biologie Végétale Géométrie et topologie Analyse numérique Chimie Physique Géographie Informatique Géologie générale

Analyse Informatique Electronique Géographie Informatique

Gestion des entreprises Géologie appliquée Sciences de gestion

Electronique

Sciences de gestion

Spectroscopie de la réactivité chimique

Biologie animale Biologie animale

Physique

Sciences Economiques Physique du solide Spectroscopie hertzienne

Biologie Mécanique Métallurgie

Optique atmosphérique Biochimie structurale Ecologie numérique

Physique moléculaire et rayonnements atmosphériques

Sociologie Chimie-Physique Sciences Economiques

Algèbre

Physiologie animale Microbiologie Géométrie Génie mécanique Physique spatiale Biologie Végétale

Probabilités et statistiques

M. LATTEUX Michel

M. LAVEINE Jean Pierre

Mme LECLERCQ Ginette

M. LEHMANN Daniel

Mme LENOBLE Jacqueline

M. LEROY Jean Marie

M. LHENAFF René

M. LHENAFF Rene

M. LHOMME Jean

M. LOUAGE Françis

M. LOUCHEUX Claude

M. LUCQUIN Michel

M. MAILLET Pierre

M. MAROUF Nadir

M. MICHEAU Pierre

M. PAQUET Jacques

M. PASZKOWSKI Stéfan

M. PETIT Francis

M. PETIT Francis

M. PORCHET Maurice

M. POUZET Pierre

M. POVY Lucien

M. PROUVOST Jean

M. RACZY Ladislas

M. RAMAN Jean Pierre

M. SALMER Georges

M. SCHAMPS Joël

Mme SCHWARZBACH Yvette

M. SEGUIER Guy M. SIMON Michel M. SLIWA Henri M. SOMME Jean Melle SPIK Geneviève

M. STANKIEWICZ François

M. THIEBAULT François

M. THOMAS Jean Claude

M. THUMERELLE Pierre

M. TILLIEU Jacques

M. TOULOTTE Jean Marc

M. TREANTON Jean René

M. TURRELL Georges

M. VANEECLOO Nicolas

M. VAST Pierre

M. VERBERT André

M. VERNET Philippe

M. VIDAL Pierre

M. WALLART Françis

M. WEINSTEIN Olivier

M. ZEYTOUNIAN Radyadour

Informatique Paléontologie Catalyse Géométrie

Physique atomique et moléculaire

Spectrochimie Géographie

Chimie organique biologique

Electronique Chimie-Physique Chimie physique Sciences Economiques

Sociologie

Mécanique des fluides Géologie générale Mathématiques Chimie organique Biologie animale

Modélisation - calcul scientifique

Automatique Minéralogie Electronique Sciences de gestion Electronique

Spectroscopie moléculaire

Géométrie Electrotechnique Sociologie Chimie organique Géographie

Biochimie Sciences Economiques Sciences de la Terre Géométrie - Topologie

Démographie - Géographie humaine

Physique théorique Automatique Sociologie du travail

Spectrochimie infrarouge et raman

Sciences Economiques Chimie inorganique

Biochimie Génétique Automatique

Spectrochimie infrarouge et raman

Analyse économique de la recherche et développement

Mécanique

## PROFESSEURS - 2ème CLASSE

M. ABRAHAM Francis

M. ALLAMANDO Etienne

M. ANDRIES Jean Claude

M. ANTOINE Philippe

M. BALL Steven M. BART André M. BASSERY Louis Mme BATTIALLYvo

Mme BATTIAU Yvonne M. BAUSIERE Robert

M. BEGUIN Paul M. BELLET Jean

M. BERNAGE Pascal M. BERTHOUD Amaud

M. BERTHOUD Amaud M. BERTRAND Hugues M. BERZIN Robert

M. BISKUPSKI Gérard M. BKOUCHE Rudolphe M. BODARD Marcel

M. BOHIN Jean Pierre

M. BOIS Pierre

M. BOISSIER Daniel

M. BOIVIN Jean Claude

M. BOUCHER Daniel

M. BOUQUELET Stéphane

M. BOUQUIN Henri

M. BROCARD Jacques

Mme BROUSMICHE Claudine

M. BUISINE Daniel

M. CAPURON Alfred

M. CARRE François

M. CATTEAU Jean Pierre

M. CAYATTE Jean Louis

M. CHAPOTON Alain

M. CHARET Pierre

M. CHIVE Maurice

M. CHIVE Maurice

M. COMYN Gérard

Mme CONSTANT Monique M. COQUERY Jean Marie M. CORIAT Benjamin Mme CORSIN Paule

M. CORTOIS Jean

M. COUTURIER Daniel

M. CRAMPON Norbert M. CURGY Jean Jacques

M. DANGOISSE Didier

M. DE PARIS Jean Claude

M. DECOSTER Didier

M. DEJAEGER Roger

M. DELAHAYE Jean Paul

M. DELORME Pierre M. DELORME Robert

M. DEMUNTER Paul

Mme DEMUYNCK Claire

M. DENEL Jacques M. DEPREZ Gilbert

Composants électroniques Biologie des organismes

Analyse Génétique Biologie animale

Génie des procédés et réactions chimiques

Géographie

Systèmes électroniques

Mécanique

Physique atomique et moléculaire

Physique atomique, moléculaire et du rayonnement

Sciences Economiques Sciences Economiques

Analyse

Physique de l'état condensé et cristallographie

Algèbre

Biologie végétale

Biochimie métabolique et cellulaire

Mécanique Génie civil Spectrochimie Physique

Biologie appliquée aux enzymes

Gestion

Chimie

Paléontologie

Mécanique

Biologie animale

Géographie humaine

Chimie organique

Sciences Economiques

Electronique

Biochimie structurale

Composants électroniques optiques

Informatique théorique

Composants électroniques et optiques

Psychophysiologie Sciences Economiques

Paléontologie

Physique nucléaire et corpusculaire

Chimie organique

Tectolique géodynamique

Biologie

Physique théorique

Analyse

Composants électroniques et optiques

Electrochimie et Cinétique

Informatique

Physiologie animale Sciences Economiques

Sociologie

Physique atomique, moléculaire et du rayonnement

Informatique

Physique du solide - christallographie

M. DERIEUX Jean Claude Microbiologie M. DERYCKE Alain Informatique Physique de l'état condensé et cristallographie M. DESCAMPS Marc M. DEVRAINNE Pierre Chimie minérale M. DEWAILLY Jean Michel Géographie humaine M. DHAMELINCOURT Paul Chimie physique M. DI PERSIO Jean Physique de l'état condensé et cristallographie M. DUBAR Claude Sociologie démographique M. DUBOIS Henri Spectroscopie hertzienne M. DUBOIS Jean Jacques Géographie M. DUBUS Jean Paul Spectrométrie des solides M. DUPONT Christophe Vie de la firme M. DUTHOIT Bruno Génie civil Mme DUVAL Anne Algèbre Mme EVRARD Micheline Génie des procédés et réactions chimiques M. FAKIR Sabah Algèbre M. FARVACQUE Jean Louis Physique de l'état condensé et cristallographie M. FAUQUEMBERGUE Renaud Composants électroniques M. FELIX Yves Mathématiques Tectonique - Géodynamique M. FERRIERE Jacky M. FISCHER Jean Claude Chimie organique, minérale et analytique M. FONTAINE Hubert Dynamique des cristaux M. FORSE Michel Sociologie M. GADREY Jean Sciences économiques M. GAMBLIN André Géographie urbaine, industrielle et démographie M. GOBLOT Rémi Algèbre M. GOURIEROUX Christian Probabilités et statistiques M. GREGORY Pierre I.A.E. Sociologie M. GREMY Jean Paul M. GREVET Patrice Sciences Economiques M. GRIMBLOT Jean Chimie organique M. GUELTON Michel Chimie physique M. GUICHAOUA André Sociologie M. HAIMAN Georges Modélisation, calcul scientifique, statistiques M. HOUDART René Physique atomique M. HUEBSCHMANN Johannes Mathématiques M. HUTTNER Marc Algèbre M. ISAERT Noël Physique de l'état condensé et cristallographie M. JACOB Gérard Informatique M. JACOB Pierre Probabilités et statistiques M. JEAN Raymond Biologie des populations végétales Vie de la firme M. JOFFRE Patrick M. JOURNEL Gérard Spectroscopie hertzienne M. KOENIG Gérard Sciences de gestion M. KOSTRUBIEC Benjamin Géographie M. KREMBEL Jean **Biochimie** Sciences Economiques Mme KRIFA Hadjila M. LANGEVIN Michel Algèbre M. LASSALLE Bernard Embryologie et biologie de la différenciation M. LE MEHAUTE Alain Modélisation, calcul scientifique, statistiques M. LEBFEVRE Yannic Physique atomique, moléculaire et du rayonnement M. LECLERCQ Lucien Chimie physique M. LEFEBVRE Jacques Physique M. LEFEBVRE Marc Composants électroniques et optiques M. LEFEVRE Christian Pétrologie

Algèbre

Astronomie - Météorologie

M. LEGRAND Pierre Chimie Mme LEGRAND Solange Algèbre

Mme LEHMANN Josiane Analyse

Melle LEGRAND Denise

M. LEGRAND Michel

M. LEMAIRE Jean Spectroscopie hertzienne M. LE MAROIS Henri M. LEMOINE Yves M. LESCURE François M. LESENNE Jacques M. LOCQUENEUX Robert Mme LOPES Maria M. LOSFELD Joseph M. LOUAGE Francis M. MAHIEU François

M. MAHIEU Jean Marie M. MAIZIERES Christian M. MANSY Jean Louis M. MAURISSON Patrick M. MERIAUX Michel M. MERLIN Jean Claude M. MESMACQUE Gérard

M. MESSELYN Jean M. MOCHE Raymond M. MONTEL Marc M. MORCELLET Michel

M. MORE Marcel

M. MORTREUX André Mme MOUNIER Yvonne

M. NIAY Pierre M. NICOLE Jacques M. NOTELET Francis M. PALAVIT Gérard M. PARSY Fernand

M. PECQUE Marcel M. PERROT Pierre M. PERTUZON Emile

M. PETIT Daniel

M. PLIHON Dominique M. PONSOLLE Louis M. POSTAIRE Jack M. RAMBOUR Serge M. RENARD Jean Pierre M. RENARD Philippe M. RICHARD Alain M. RIETSCH François

M. ROBINET Jean Claude M. ROGALSKI Marc

M. ROLLAND Paul M. ROLLET Philippe Mme ROUSSEL Isabelle M. ROUSSIGNOL Michel

M. ROY Jean Claude M. SALERNO Francis M. SANCHOLLE Michel

Mme SANDIG Anna Margarette M. SAWERYSYN Jean Pierre M. STAROSWIECKI Marcel

M. STEEN Jean Pierre

Mme STELLMACHER Irène M. STERBOUL François

M. TAILLIEZ Roger M. TANRE Daniel M. THERY Pierre

Mme TJOTTA Jacqueline M. TOURSEL Bernard M. TREANTON Jean René Vie de la firme

Biologie et physiologie végétales

Algèbre

Systèmes électroniques Physique théorique **Mathématiques** \*Informatique

Electronique Sciences économiques

Optique - Physique atomique

Automatique Géologie

Sciences Economiques

**EUDIL** Chimie

Génie mécanique

Physique atomique et moléculaire

Modélisation, calcul scientifique, statistiques

Physique du solide Chimie organique

Physique de l'état condensé et cristallographie

Chimie organique

Physiologie des structures contractiles

Physique atomique, moléculaire et du rayonnement

Spectrochimie

Systèmes électroniques

Génie chimique Mécanique Chimie organique Chimie appliquée Physiologie animale

Biologie des populations et écosystèmes

Sciences Economiques Chimie physique Informatique industrielle

Biologie

Géographie humaine Sciences de gestion Biologie animale Physique des polymères

EUDIL Analyse

Composants électroniques et optiques

Sciences Economiques Géographie physique

Modélisation, calcul scientifique, statistiques

Psychophysiologie Sciences de gestion

Biologie et physiologie végétales

Chimie physique Informatique Informatique

Astronomie - Météorologie

Informatique Génie alimentaire Géométrie - Topologie Systèmes électroniques Mathématiques

Informatique

Sociologie du travail

M. TURREL Georges M. VANDIJK Hendrik

Mme VAN ISEGHEM Jeanine

M. VANDORPE Bernard

M. VASSEUR Christian

M. VASSEUR Jacques

Mme VIANO Marie Claude

M. WACRENIER Jean Marie

M. WARTEL Michel

M. WATERLOT Michel

M. WEICHERT Dieter

M. WERNER Georges

M. WIGNACOURT Jean Pierre

M. WOZNIAK Michel

Mme ZINN JUSTIN Nicole

Spectrochimie infrarouge et raman

Modélisation, calcul scientifique, statistiques

Chimie minérale

Automatique

Biologie

Electronique

Chimie inorganique

géologie générale

Génie mécanique

Informatique théorique

Spectrochimie

Algèbre

#### Résumé

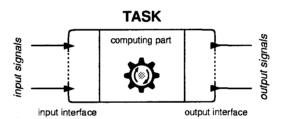

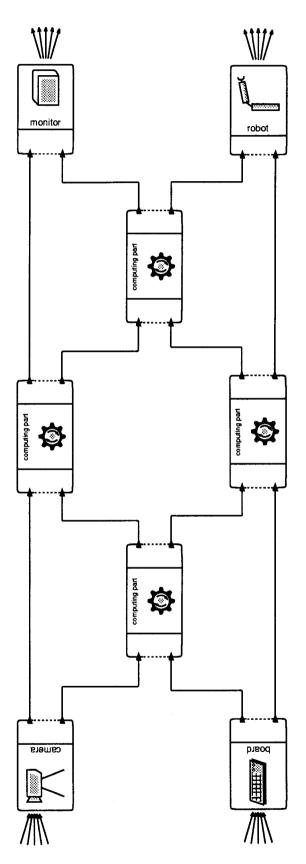

Le travail réalisé dans le cadre de cette thèse porte sur la transformation automatique de programmes synchrones en vue de leur implémentation asynchrone sur les architectures hétérogènes distribuées. Dans un contexte applicatif nous nous sommes plus particulièrement intéressés aux systèmes de traitements temps-réel de l'image. La démarche que nous avons suivie se base sur une phase préliminaire de conception et validation des systèmes temps-réel sous l'hypothèse de synchronisme. En pratique, nous avons utilisé un outil existant: le langage SIGNAL. Nous avons développé un ensemble de processus de transformation permettant d'automatiser l'implémentation de ces systèmes sous la forme de processus séquentiels communicants. Les caractéristiques de ce travail sont de garantir a priori la sûreté des programmes en transformant des systèmes prouvés, de répartir intégralement les échanges de données de manière à ne pas recourir à des mécanismes centralisés, de conserver à l'exécution un modèle dicté par la disponibilité des données. Les systèmes ainsi transformés sont constitués d'un ensemble fini de fonctions de calcul dotées d'interfaces de communications; elles constituent les tâches du système. Ces tâches ne communiquent entreelles que par l'intermédiaire de leurs entrées et sorties. L'émission et la réception de données sont conditionnées par des commandes gardées implémentées dans le corps des interfaces.

## Abstract

Work presented in this document concerns a set of automatic transformation processes of synchronous programs in order to implement them on distributed heterogeneous architectures. We particularly took an interest in the area of real-time image processing. Our approach is as follows; real-time systems are designed and validated on the assumption of synchronism. In practice we used an existing tool: the SIGNAL synchronous language. We then developed a set of transformation processes which allow to automatically implement real-time systems in a concurrent sequential processes model. Major features of this work are to guarantee safety properties by transforming proved programs, to distribute data exchanges in order to avoid centralized mecanism requirements, to preserve all dataflow aspects at run-time. Transformed systems are made of a finite set of computing functions with associated communication interfaces, called tasks. Tasks do not communicate except on entry and exit. Data transmissions are restricted by guarded commands which are implemented in the body of the interfaces.

Je tiens à remercier,

Les membres du jury qui ont acceptés de rapporter ce travail.

Les nombreux lecteurs et correcteurs attentifs.

L'ensemble de mes collègues de travail au sein de THOMSON MULTIMEDIA dont la diversité intellectuelle n'a d'égal que l'extrême compétence, pour leur sympathie.

# Table des matières

| In                                                | Introduction 1 |                                                            |                                                     |  |  |  |  |  |  |

|---------------------------------------------------|----------------|------------------------------------------------------------|-----------------------------------------------------|--|--|--|--|--|--|

| I                                                 | Cor            | ntexte de l'étude                                          |                                                     |  |  |  |  |  |  |

|                                                   | I.1            | Le tra                                                     | itement d'images                                    |  |  |  |  |  |  |

|                                                   |                | I.1.1                                                      | Les niveaux de traitement                           |  |  |  |  |  |  |

|                                                   |                | I.1.2                                                      | Degré du parallélisme                               |  |  |  |  |  |  |

|                                                   |                | I.1.3                                                      | Mise en œuvre                                       |  |  |  |  |  |  |

|                                                   |                | I.1.4                                                      | Niveau fonction                                     |  |  |  |  |  |  |

|                                                   |                | I.1.5                                                      | Niveau application                                  |  |  |  |  |  |  |

|                                                   |                | I.1.6                                                      | Conclusion                                          |  |  |  |  |  |  |

|                                                   | <b>I.2</b>     | Le ten                                                     | nps-réel                                            |  |  |  |  |  |  |

|                                                   |                | I.2.1                                                      | Taxinomie                                           |  |  |  |  |  |  |

|                                                   |                | I.2.2                                                      | Mise en œuvre                                       |  |  |  |  |  |  |

|                                                   |                | I.2.3                                                      | Modélisation                                        |  |  |  |  |  |  |

|                                                   |                | I.2.4                                                      | Conclusion                                          |  |  |  |  |  |  |

|                                                   | I.3            | L'hypo                                                     | othèse de synchronisme                              |  |  |  |  |  |  |

|                                                   |                | I.3.1                                                      | Propriétés du synchronisme                          |  |  |  |  |  |  |

|                                                   |                | 1.3.2                                                      | Mise en œuvre                                       |  |  |  |  |  |  |

|                                                   |                | I.3.3                                                      | Synthèse                                            |  |  |  |  |  |  |

|                                                   |                | I.3.4                                                      | Vers un squelette synchrone "idéal"                 |  |  |  |  |  |  |

|                                                   | I.4            | Appro                                                      | che mixte synchrone-asynchrone                      |  |  |  |  |  |  |

|                                                   |                | I.4.1                                                      | L'approche proposée                                 |  |  |  |  |  |  |

|                                                   |                | I.4.2                                                      | Quelques expériences                                |  |  |  |  |  |  |

|                                                   |                |                                                            | · · · · · · · · · · · · · · · · · · ·               |  |  |  |  |  |  |

| II                                                | Nor            | malisa                                                     | tion des horloges 39                                |  |  |  |  |  |  |

|                                                   | II.1           | Calcul                                                     | d'horloges de SIGNAL                                |  |  |  |  |  |  |

|                                                   |                | II.1.1                                                     | Le système d'équations d'horloges                   |  |  |  |  |  |  |

|                                                   |                | II.1.2                                                     | Expressions non contraintes                         |  |  |  |  |  |  |

|                                                   |                | II.1.3                                                     | Expressions contraintes                             |  |  |  |  |  |  |

|                                                   |                | II.1.4                                                     | Arbre d'horloges                                    |  |  |  |  |  |  |

|                                                   |                | II.1.5                                                     | La règle d'inclusion des événements                 |  |  |  |  |  |  |

| II.1.6 Introduction au processus de normalisation |                |                                                            |                                                     |  |  |  |  |  |  |

| II.2 La problématique sur un exemple              |                |                                                            |                                                     |  |  |  |  |  |  |

|                                                   |                | II.2.1                                                     | Approche directe                                    |  |  |  |  |  |  |

|                                                   |                | 11.2.2                                                     | Résolution à l'horloge racine                       |  |  |  |  |  |  |

|                                                   | II.3           | Expres                                                     | ssion à multiples fréquences                        |  |  |  |  |  |  |

|                                                   |                | 11.3.1                                                     | Généralisation                                      |  |  |  |  |  |  |

|                                                   |                | II.3.2 Le processus de substitution à multiples fréquences |                                                     |  |  |  |  |  |  |

|                                                   |                | II.3.3                                                     | Le processus de substitution à multiples fréquences |  |  |  |  |  |  |

|                                                   | II.4           |                                                            | ence complémentaire                                 |  |  |  |  |  |  |

|                                                   |                | II.4.1                                                     | Variables contraintes                               |  |  |  |  |  |  |

|                                                   |                | II.4.2                                                     | Variables non contraintes                           |  |  |  |  |  |  |

|                                                   |                |                                                            |                                                     |  |  |  |  |  |  |

|                           |              |         | Application                                       |     |     |   |   |   | ٠ |   | ٠   |     |   | 58  |

|---------------------------|--------------|---------|---------------------------------------------------|-----|-----|---|---|---|---|---|-----|-----|---|-----|

|                           | II.5         | Conclu  | sion                                              |     |     |   |   |   |   |   |     |     |   | 61  |

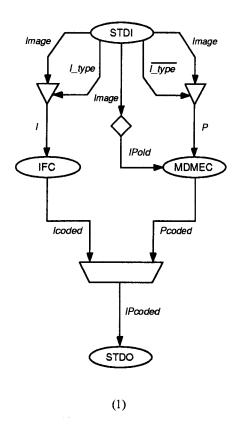

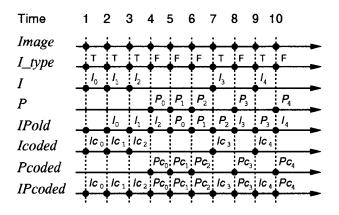

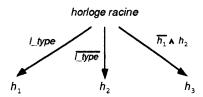

|                           | II.6         | Applic  | ation: Un codeur de type MPEG                     |     |     |   |   |   |   |   |     |     |   | 64  |

|                           |              | II.6.1  | Processus de normalisation                        |     |     |   |   |   | • |   |     |     |   | 64  |

|                           |              |         | Simplifications                                   |     |     |   |   |   |   |   |     |     |   |     |

|                           |              |         |                                                   |     |     |   |   |   |   |   |     |     |   |     |

| H                         |              |         | ation des expressions                             |     |     |   |   |   |   |   |     |     |   | 71  |

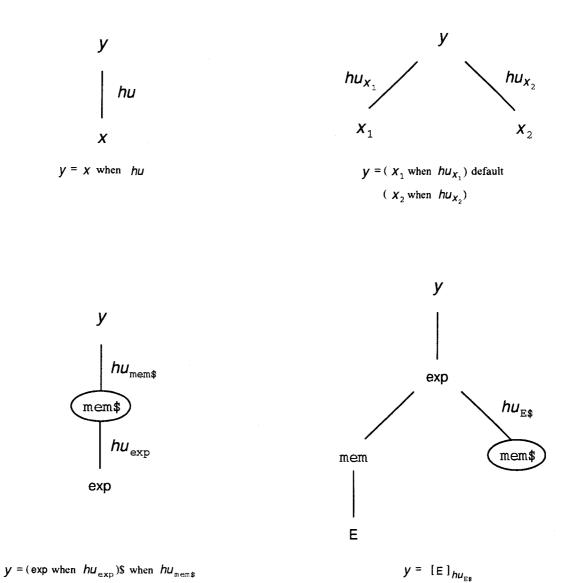

|                           | III.1        |         | sions de définition de signaux                    |     |     |   |   |   |   |   |     |     |   |     |

|                           |              | III.1.1 | Horloge d'utilisation                             |     |     |   |   |   |   |   |     |     |   | 72  |

|                           |              | III.1.2 | Expression de définition de signaux               |     |     |   |   |   |   |   |     |     |   | 73  |

|                           | <b>III.2</b> |         | isme                                              |     |     |   |   |   |   |   |     |     |   |     |

|                           |              | III.2.1 | Absence de signaux intermédiaires                 |     |     |   |   |   |   |   |     |     |   | 74  |

|                           | III.3        | Règles  | de transformation                                 |     |     |   |   |   |   |   |     |     |   | 77  |

|                           |              |         | Processus de transformation                       |     |     |   |   |   |   |   |     |     |   |     |

|                           |              | III.3.2 | Récursion temporelle                              |     |     |   |   |   |   |   |     |     |   | 80  |

|                           |              |         | Dépendances entre un signal et son signal retardé |     |     |   |   |   |   |   |     |     |   |     |

|                           |              |         | Plusieurs chemins                                 |     |     |   |   |   |   |   |     |     |   |     |

|                           | 111 4        |         | es contraintes par des signaux intermédiaires     |     |     |   |   |   |   |   |     |     |   |     |

|                           | 111.1        | Homog   | es constantes par des signada intermedianes       | • • | • • | • |   | ٠ | • |   | •   | •   |   | 04  |

| IV                        | Imp          | lément  | ation des interfaces                              |     |     |   |   |   |   |   |     |     |   | 87  |

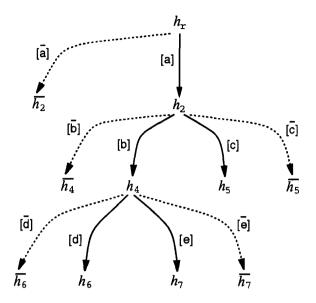

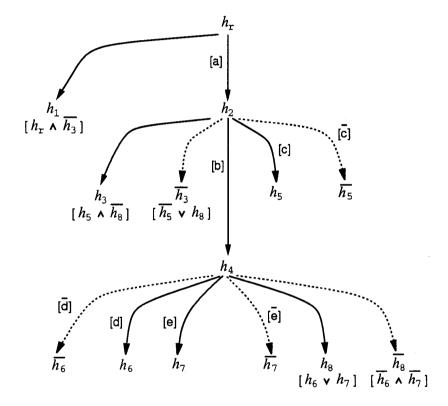

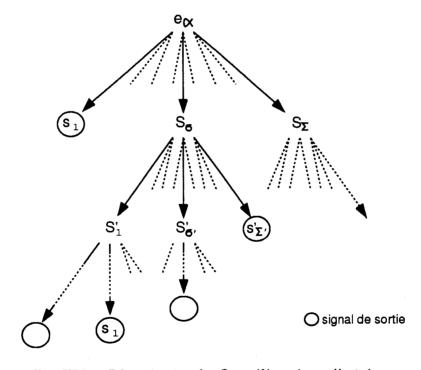

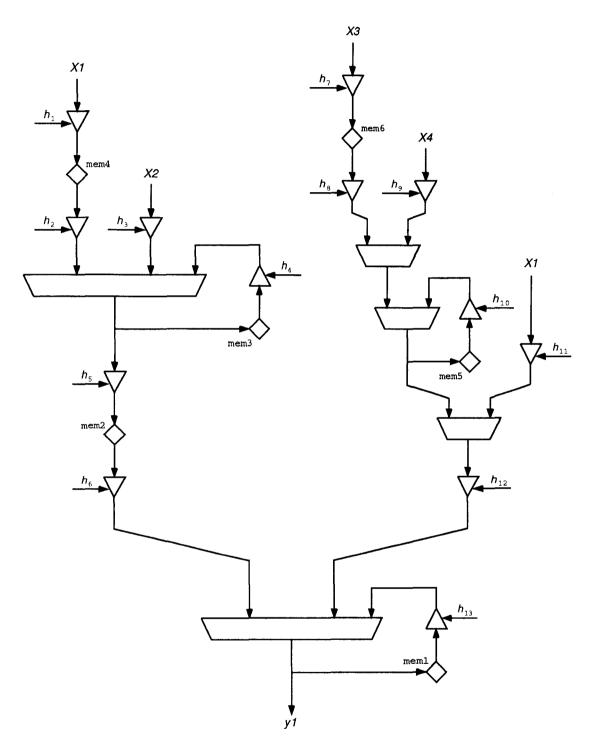

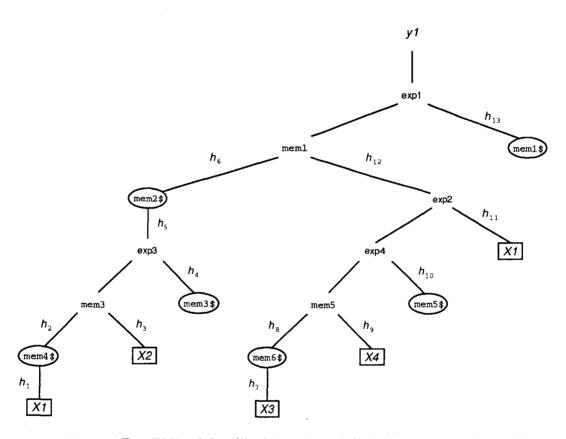

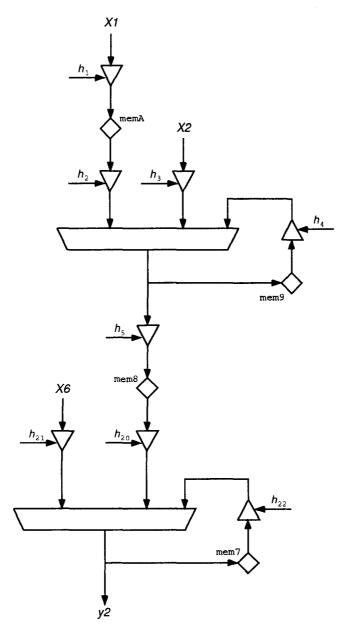

|                           |              |         | lances de calcul                                  |     |     |   |   |   |   |   |     |     |   | 87  |

|                           |              |         | Construction de l'arbre d'implémentation          |     |     |   |   |   |   |   |     |     |   |     |

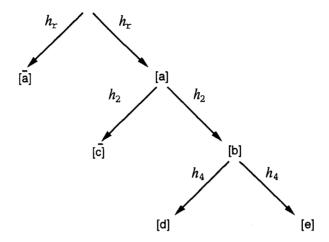

|                           |              | IV.1.2  | Parcours de l'arbre d'implémentation              |     |     |   |   |   |   |   |     |     |   | 90  |

|                           | IV.2         |         | e des mémoires                                    |     |     |   |   |   |   |   |     |     |   |     |

|                           |              |         | contrôle                                          |     |     |   |   |   |   |   |     |     |   |     |

|                           |              |         | Expression normale d'horloge sur signaux interméd |     |     |   |   |   |   |   |     |     |   | 98  |

|                           |              |         | Détermination de la fréquence des dépendances     |     |     |   |   |   |   |   |     |     |   |     |

|                           |              |         | Horloges                                          |     |     |   |   |   |   |   |     |     |   |     |

|                           | IV 4         |         | s de réception                                    |     |     |   |   |   |   |   |     |     |   |     |

|                           |              | Conclu  |                                                   |     |     |   |   |   |   |   |     |     |   |     |

|                           | 1 V .U       | Conciu  | 51011                                             |     |     | • | • | • |   | • | •   |     | • | 112 |

| V                         | Con          | clusion |                                                   |     |     |   |   |   |   |   |     |     |   | 113 |

| A                         | App          | licatio | n                                                 |     |     |   |   |   |   |   |     |     |   | 115 |

| В                         | SIG          | NAL     |                                                   |     |     |   |   |   |   |   |     |     |   | 135 |

|                           |              |         |                                                   |     |     |   |   |   |   |   |     |     |   |     |

| C Les fichiers Syndex     |              |         |                                                   |     |     |   |   |   |   |   |     | 147 |   |     |

| Liste de nos publications |              |         |                                                   |     |     |   |   |   |   |   |     | 151 |   |     |

| Ribliographio             |              |         |                                                   |     |     |   |   |   |   |   | 150 |     |   |     |

## Introduction

Le travail réalisé dans le cadre de cette thèse porte sur l'implémentation des systèmes temps-réel complexes sur les architectures hétérogènes distribuées Notre approche est appliquée au domaine plus spécifique du traitement d'images, mais pourrait être généralisée aux systèmes temps-réel qui manifestent des similarités en terme de traitement et de contrôle. (se reporter également à nos publications [JCR<sup>+</sup>96, GDM96a, GDM96b, GDM96c, GBDM96, Gal96, Gal95]).

Il s'inscrit dans la dynamique de deux projets: un programme de recherche européen, intitulé ESPRIT BRA PROJECT 8849 SM-IMP<sup>1</sup> [JCR<sup>+</sup>96] couvrant à la fois la conception d'architectures nouvelles pour le traitement temps-réel de l'image ainsi que la programmation et la mise au point de ces systèmes — et le projet  $P^3I$  [CJC<sup>+</sup>94, CJG<sup>+</sup>94b, CJG<sup>+</sup>94a, GBDL<sup>+</sup>94]<sup>2</sup>, une plateforme généraliste pour le traitement temps-réel de l'image. Par le truchement de ces deux projets, notre travail se situe donc au croisement de la recherche fondamentale et appliquée.

Les travaux menés conjointement par les différents partenaires ont ainsi abouti à la proposition d'un modèle architectural ouvert dans lequel machines généralistes (de la station de travail aux calculateurs parallèles) et unités cablées sont fédérées sous la forme d'un seul gros système parallèle de type MIMD appelé machine hétérogène distribuée. Ce modèle architectural peut être entrevu comme un réseau dont la nature n'a pas été précisément définie et pouvant accueillir différents types d'unités qui sont susceptibles d'être ajoutés ou retirés au cours du temps.

L'exploitation pour des propos industriels d'une plateforme de ce type dans le cadre du projet  $P^3I$ , a notamment permis de repositionner les problèmes sur le plan logiciel bien plus que matériel. Ainsi, le besoin crucial de décorréler complètement du modèle architectural sous-jacent, les phases de spécification des problèmes, de conception et de validation des systèmes a été souligné.

Notre propos n'est pas ici d'ajouter une nouvelle pierre au lourd édifice théorique déjà existant, mais au regard des problèmes spécifiques posés par la programmation des systèmes temps-réel complexes, de proposer une méthode d'implémentation directe sur une plateforme hétérogène distribuée.

Le domaine d'application du traitement temps-réel de l'image concerne des secteurs d'activité aussi sensibles que le nucléaire, l'aéronautique, le militaire, etc, qui posent des contraintes fortes en termes de sûreté des programmes, et pour lesquels il est fondamental d'être le plus efficace compte tenu des possibilités de l'architecture sous-jacente.

Un certain nombre de caractéristiques majeures sont liées aux applications temps-réel et à leur contexte d'utilisation [Maf93]:

• Les processus temps-réel maintiennent une interaction permanente avec leur environnement,

<sup>1.</sup> Le projet SM-IMP est un partenariat de recherche entre sociétés industrielles: THOMSON MULTIMEDIA R&D France — PARSYTEC, et laboratoires universitaires: DIST University of Genoa — DELFT University of Technology — University College London.

<sup>2. ©</sup> THOMSON MULTIMEDIA R&D France.

2 INTRODUCTION

• La portabilité et la ré-utilisabilité du code développé nécessite que la spécification d'une application soit complètement décorrélée de tout modèle architectural,

- La sûreté des programmes impose la maîtrise d'outils formels permettant de prouver l'existence et l'unicité de solution de tout problème traité,

- Finalement, les applications temps-réel mêlent deux caractéristiques importantes: un ensemble lourd de traitements et un système complexe de contrôle et de commande.

Exécuter des traitements complexes et tenir des performances proches du temps-réel<sup>3</sup> nécessite le plus souvent de s'adresser à des architectures hétérogènes distribuées exhibant des modes de contrôle différents (c.f. taxinomie de FLYNN [Fly66]).

Les langages apparus avec les architectures multi-processeurs et fondés sur le Communicating Sequential Processes (CSP) de Hoare [Hoard], comme par exemple OCCAM [LTD88], ont largement inspiré le modèle de programmation des architectures hétérogènes distribuées. Dès lors une grande expérience a été acquise par l'utilisation de ce modèle qui révèle un ensemble d'atouts majeurs:

- La décomposition d'une application en un ensemble de tâches est une manière intuitive et efficace d'appréhender les problèmes complexes,

- La spécification des programmes n'est pas liée à une architecture particulière,

- L'exécution concurrente est facilitée par l'existence d'un ensemble de tâches à réaliser.

- Ces langages ont l'avantage de posséder les primitives de gestion de processus indispensables à la programmation naturelle des systèmes temps-réel.

Il semble cependant difficile dans le cadre de la programmation asynchrone d'obtenir une définition précise et rigoureuse du comportement temporel des processus spécifiés. Même les modèles CSP de Hoare, et CCS qui proposent une restriction à un mode de communication synchrone sur *rendez-vous*, mis en œuvre dans des langages comme ADA [RCDS90], OCCAM [LTD88] ou CRSM [Sha92] ne résolvent pas ce problème.

En outre, l'asynchronisme et le non-déterminisme intrinsèque de ces langages compliquent considérablement la mise au point des applications, et rend difficile l'obtention de toute preuve formelle des programmes.

Les langages synchrones ont été introduits très récemment comme une réponse à ces problèmes, en fournissant des primitives "idéales", qui permettent de raisonner comme si le programme réagissait instantanément aux événements externes. Le contexte formel ainsi fourni par les langages synchrones permet à la fois d'exprimer simplement les relations temporelles complexes qui interviennent naturellement dans les problèmes temps-réel, et d'effectuer des preuves automatiques des programmes. Ces modèles posent par contre des difficultés sérieuses en termes d'implémentation.

De manière synthétique, on peut dire que: "In practice, each style tends to be weak where the other is strong" [BB91]. L'hypothèse synchrone définit en effet un cadre formel essentiel pour raisonner sur le temps, alors que le modèle asynchrone répond idéalement aux problèmes posés par l'implémentation <sup>4</sup>.

<sup>3.</sup> Les temps de réponse en entrée et sortie du système s'effectuent dans des délais suffisants pour pouvoir être logiquement considérés comme instantanés.

<sup>4.</sup> Synchronisme et asynchronisme ne se réfèrent pas à une réalité physique, mais à une manière de raisonner sur le temps. Dans le premier cas, communications et traitement sont supposés s'effectuer dans un temps logique nul, alors que dans le second ces délais sont pris en compte.

L'approche nouvelle que nous avons adoptée consiste à tirer parti des deux modèles plutôt que de les considérer comme définitivement antagonistes. Nous proposons donc une démarche visant à conjuguer les avantages respectifs des modèles synchrone et asynchrone. L'essentiel de notre apport réside dans un ensemble de processus formels de transformation permettant de passer automatiquement du squelette synchrone des applications à une implémentation asynchrone sous la forme de processus séquentiels communicants.

Notre objectif est de favoriser l'implémentation automatique de programmes "prouvés" sur les architectures hétèrogènes distribuées moyennement couplées. C'est-à-dire, pour lesquelles les coûts de communication ne peuvent pas être négligés.

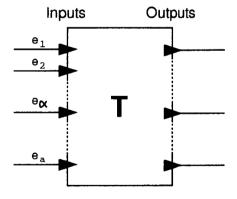

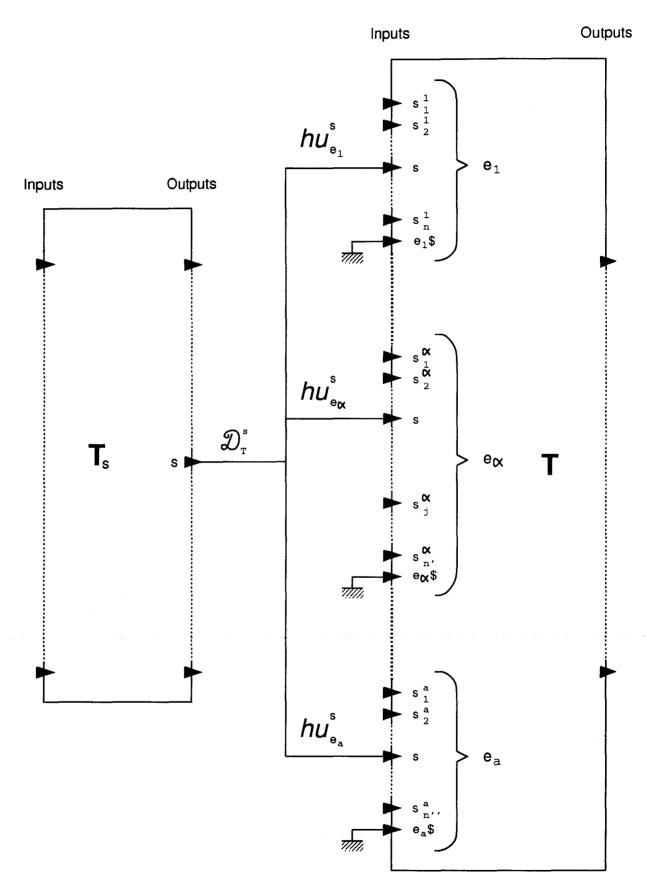

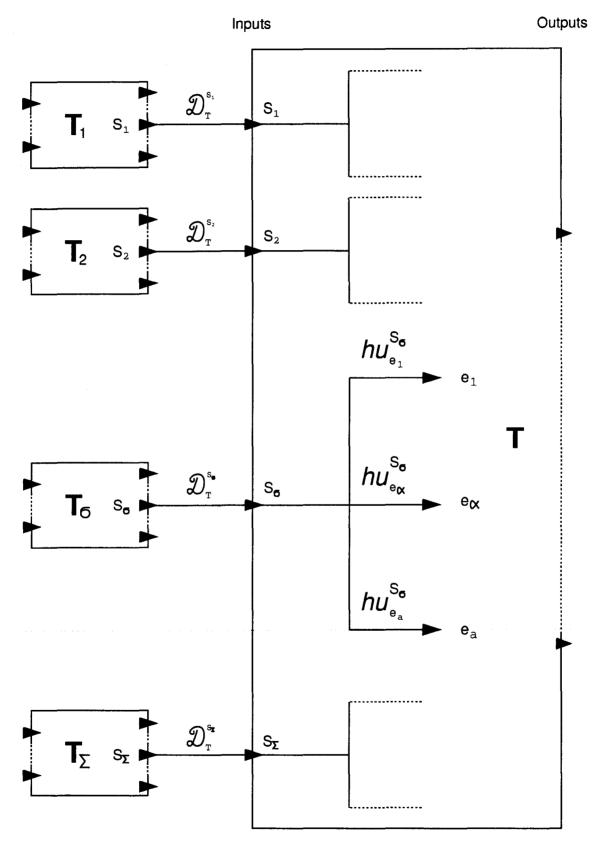

La démarche que nous avons adoptée est la suivante: les phases de spécification et conception des systèmes, sont effectuées sous l'hypothèse de synchronisme. Une application temps-réel de traitement de l'image est ainsi décrite comme un ensemble fini de fonctions élémentaires <sup>5</sup> s'exécutant concurremment dans le temps, et ne communiquant que sur leurs entrées et leurs sorties. Les relations temporelles sont exprimées au moyen d'un jeu minimal d'opérateurs empruntés aux langages synchrones. On admet ainsi que l'utilisateur dispose d'une architecture "idéale" sur laquelle les différentes fonctions du programme peuvent s'exécuter dans des délais suffisants (on les suppose bornés) pour tenir le temps-réel. Cette hypothèse vise à décorréler la phase de développement des problèmes liés à l'implémentation.

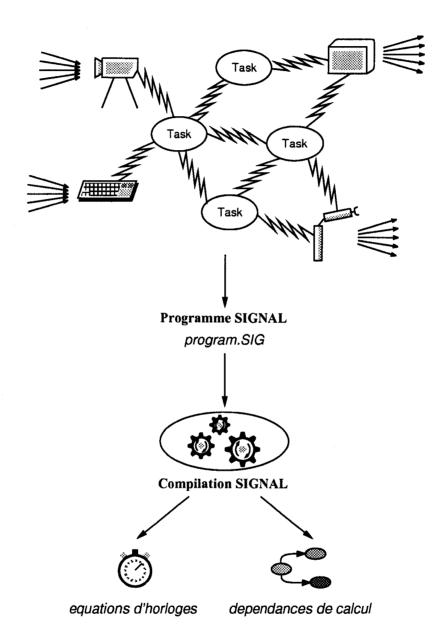

À partir de ce squelette synchrone de l'application, un processus automatique de vérification des propriétés temporelles est déclenché. En pratique nous avons utilisé un outil existant, il s'agit du calcul d'horloge de SIGNAL [BLG90, BB91, LGG90, LGM+91, MCL92, Maf93, Bes92, Ché91] 6.

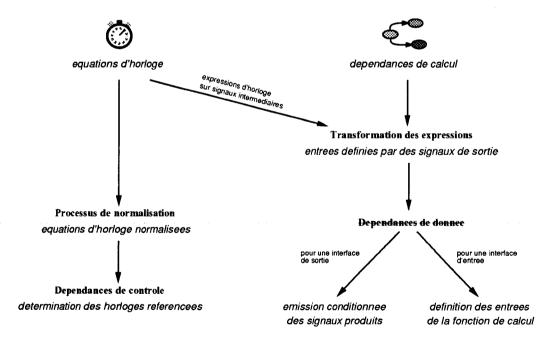

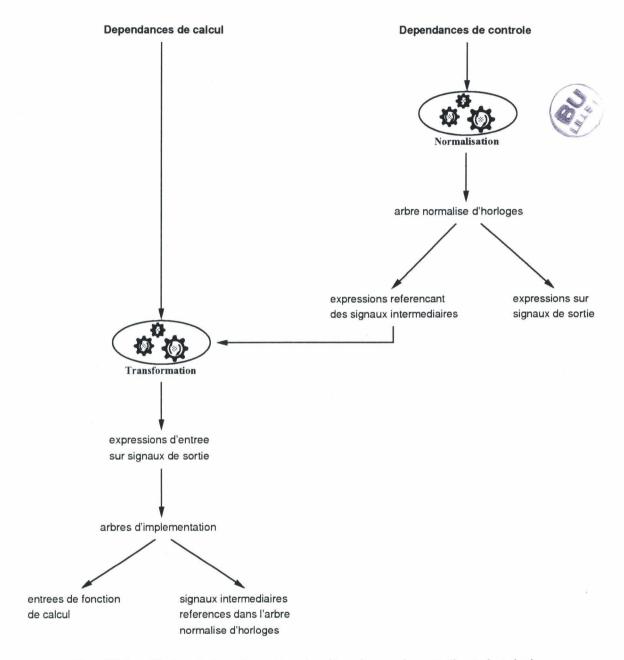

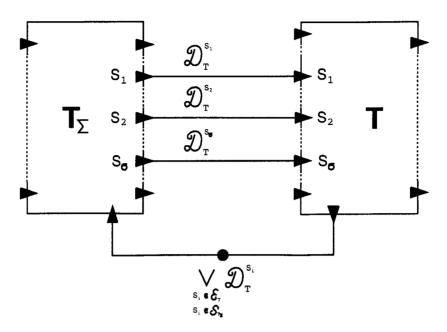

L'essentiel de notre travail opère sur les résultats produits par cette phase de résolution des contraintes temporelles. Il s'agit d'un ensemble de transformations automatiques portant sur la ré-écriture des équations d'horloge et des dépendances de calcul définies par le calcul d'horloge. Ces processus de transformation ont pour but de répartir les échanges de données entre les différentes taches du programme tout en minimisant le volume des flots transmis. Un autre point important est de maintenir les aspects dataflow à l'exécution.

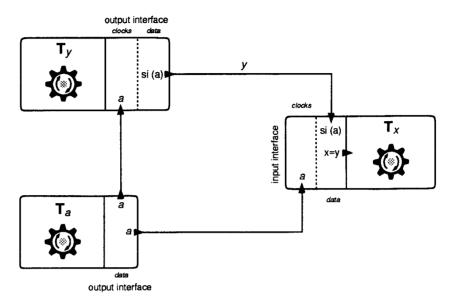

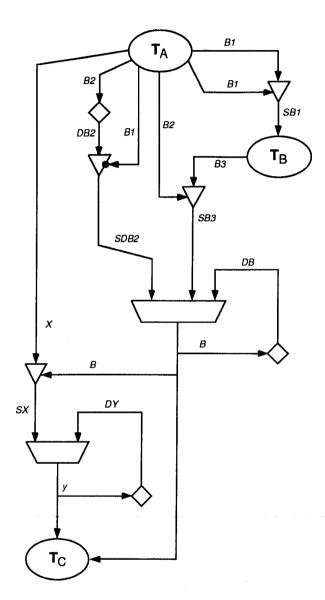

En fin de traitement, expressions d'horloge et dépendances de calcul sont synthétisées sous la forme de dépendances traditionnelles de données qui sont conditionnées au moyen de commandes gardées dans des interfaces de communication ajoutées aux fonctions élémentaires de traitement. Ces interfaces de communication sont destinées à être implémentées via une librairie standard de communication de type message passing (i.g. PVM [GBD+94a, GBD+94b], MPI [Uni94, SL94]).

Dans l'optique d'une implémentation automatique de systèmes temps-réel sur les architectures hétérogènes distribuées, les aspects novateurs de notre approche approche sont donc:

- De garantir a priori la sureté des programmes en implémentant des systèmes déjà prouvés.

- À partir d'une vue monolithique du programme sous la forme d'un graphe de dépendances de calcul et de contrôle nous montrons dans quelle mesure il est possible de répartir complètement entre les différentes tâches l'ensemble des échanges de données, de manière à ce que chaque tâche soit pleinement responsable de ses conditions d'activation. Il en ressort que ces tâches ont gagné une plus grande autonomie qui sied mieux à une implémentation sur une architecture hétérogène distribuée. En particulier, cela permet d'éviter les points de contention qui ne manqueraient pas de surgir si nous utilisions des mécanismes d'échange ou de contrôle centralisés. Cette autonomie correspond en outre à la contrepartie applicative de l'architecture ouverte qui a été définie.

<sup>5.</sup> La création dynamique de processus est prohibée. Cette condition est cruciale pour assurer la terminaison d'un programme

<sup>6. ©</sup> Institut National de Recherche en Informatique et en Automatique.

4 INTRODUCTION

• De préserver à l'exécution un système purement dicté par la disponibilité des données.

Le document est organisé de la manière suivante:

- CHAPITRE 1: Nous présentons ici les différents concepts liés à la programmation des systèmes complexes de traitement temps-réel de l'image, avec un éclairage particulier porté sur la théorie de la programmation synchrone. Et nous concluons par l'approche que nous préconisons.

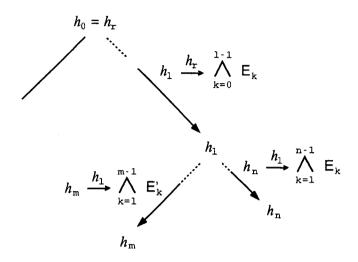

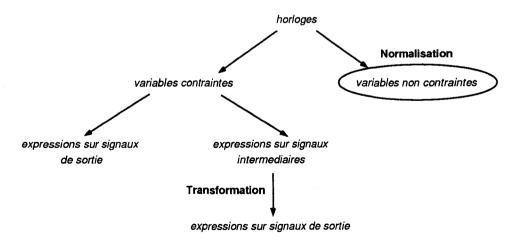

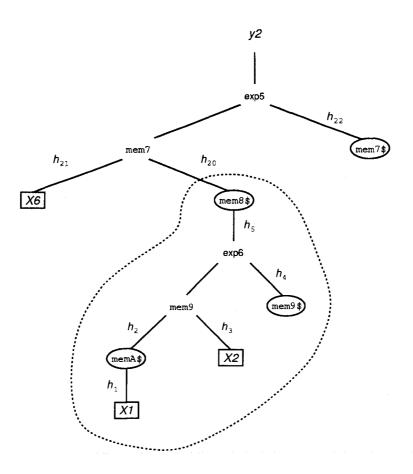

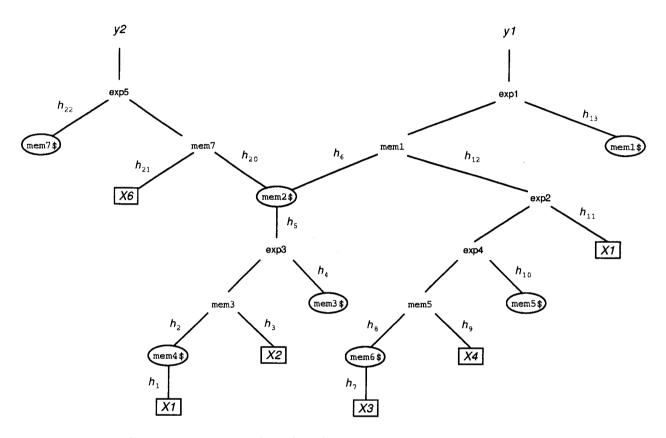

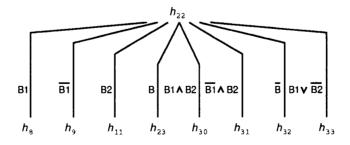

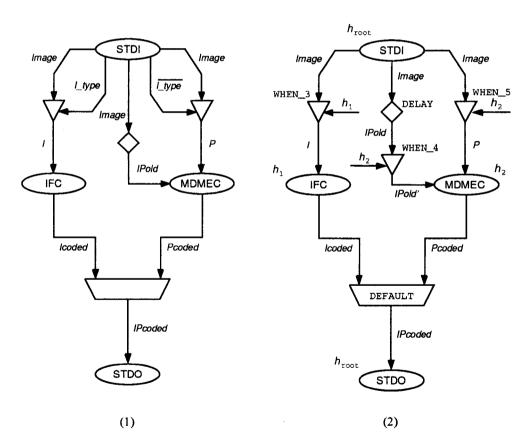

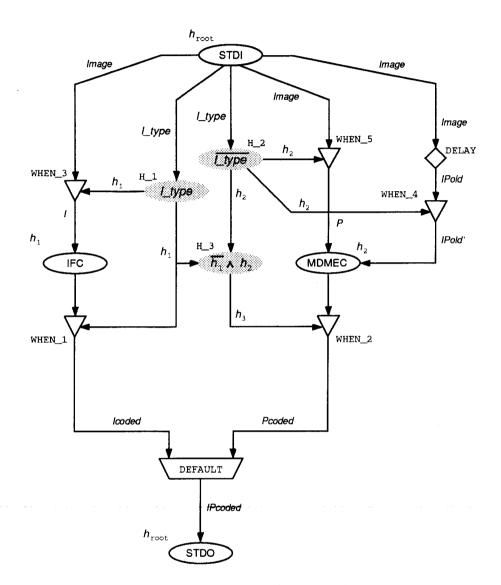

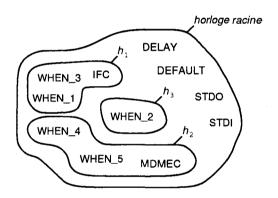

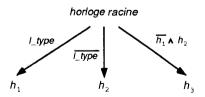

- Chapitre 2: Ce chapitre ainsi que les deux suivants, décrivent les outils formels que nous avons développés pour produire une implémentation CSP à partir d'un squelette synchrone. Ici nous traitons plus particulièrement la partie contrôle. La compilation SIGNAL permet d'isoler les aspects purement liés au contrôle des applications en produisant un système d'équations d'horloges. Ces expressions d'horloge sont soit directement définies à partir de flots du programme, soit par des formules de calcul sur horloges. À tout instant, le rôle des horloges diffusées dans l'intégralité des nœuds du réseau, et dont le calcul est centralisé, est de valider les dépendances de calcul. Cette gestion centralisée ou semi-centralisée est difficilement acceptable dans un contexte CSP. Nous proposons donc dans cette partie, de transformer toutes les équations d'horloges en expressions normales sur signaux booléens du programme. Cette transformation permettra ultérieurement de distribuer complètement entre les tâches le contrôle des dépendances de calcul.

- CHAPITRE 3: Pour les besoins de la phase de résolution des contraintes temporelles, les dépendances de calcul sont décomposées en un grand nombre d'expressions élémentaires. Ce qui se traduit par la démultiplication des nœuds et des signaux véhiculés dans le graphe synchrone de l'application. Une implémentation CSP efficace suppose de réduire au maximum la masse des signaux échangés par les tâches. Un processus formel d'agrégation des dépendances de calcul est ainsi proposé, afin de connecter directement sorties et entrées des fonctions de calcul.

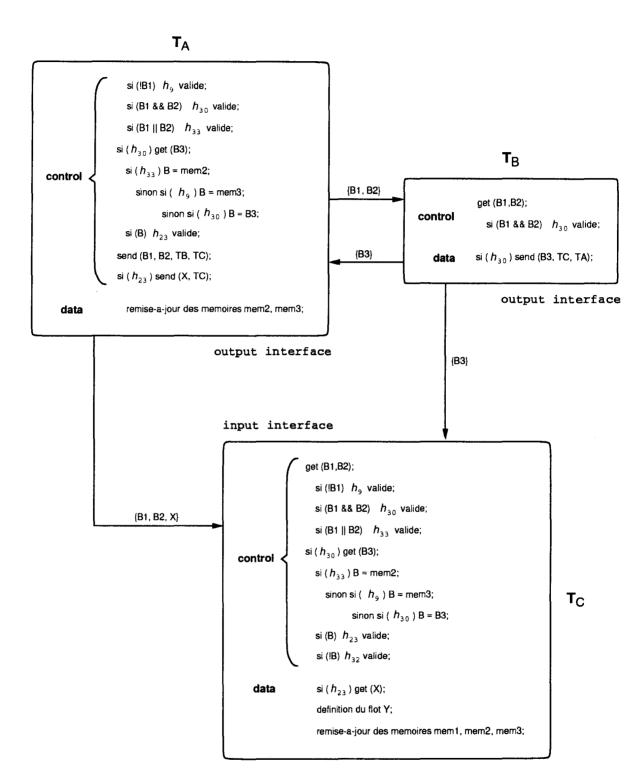

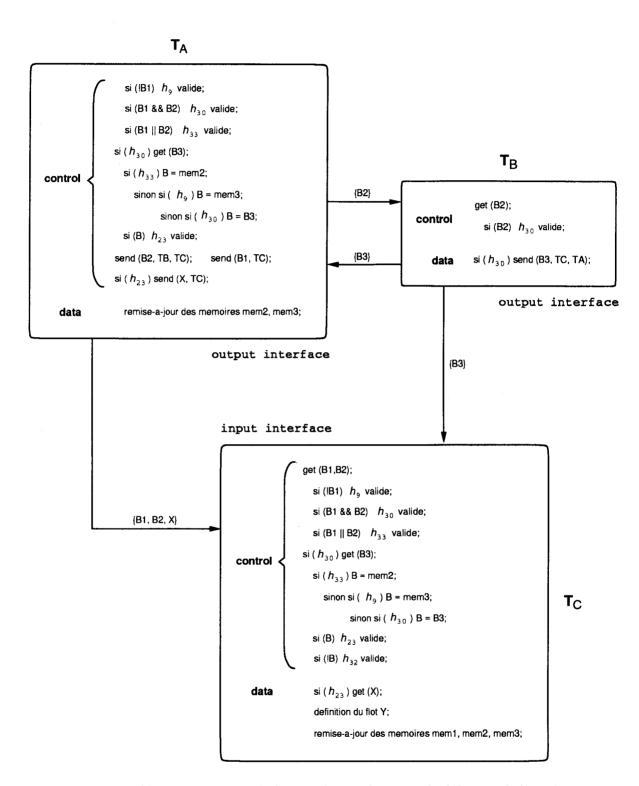

- Chapitre 4: Expressions normalisées d'horloges et expressions de calcul agrégées ne suffisent pas pour permettre une implémentation directe des applications. Encore faut-il disposer d'une méthode qui puisse être automatisée dans l'écriture d'un compilateur. La gestion des mémoires induites par les valeurs retardées pose en ce sens grand nombre de difficultés. Nous proposons ainsi une méthode simple de construction des interfaces de communication des tâches qui vont implémenter les parties contrôle normalisé et dépendances de calcul qui ont été obtenues précédemment.

- Chapitre 5: Nous concluons enfin sur notre travail, en rappelant quelles en sont les caractéristiques principales.

- Annexe A: Dans ce premier appendice nous présentons une implémentation des interfaces de l'application MPEG-2 version simple-profile utilisant la librairie de communication PVM.

- Annexe B: Présentation détaillée de la sémantique du langage synchrone SIGNAL sur lequel se fonde notre approche.

- Annexe C: Petit aparté technique sur les fichiers produits par le compilateur SIGNAL, et qui nous ont servi à construire les graphes de dépendances conditionnées, ainsi que les arbres d'horloges.

## Chapitre I

## Contexte de l'étude

Nous nous proposons dans cette partie préliminaire de décrire les particularités du traitement de l'image (SECTION I.1). Puis d'étendre cette présentation aux systèmes temps-réel (SECTION I.2) afin d'identifier les besoins et les mécanismes généraux mis en œuvre dans ce domaine d'activité. Il existe aujourd'hui deux grandes manières d'aborder les problèmes temps-réel: une approche purement synchrone — et une approche purement asynchrone. L'approche synchrone étant relativement récente, nous la décrirons largement dans la SECTION I.3. Puis nous conclurons ce chapitre par une présentation de la démarche que nous avons suivie (SECTION I.4).

## I.1 Le traitement d'images

Le traitement d'images est un domaine d'application qui englobe une variété importante de problèmes (SECTION I.1.1). A la base de ces problèmes on trouve le besoin d'acquérir, d'analyser, d'interpréter l'image. Une caractéristique essentielle dans ce domaine d'application est donc le volume énorme des structures élémentaires qui sont manipulées (cf. tableau I.1 emprunté à [Rob94]).

## I.1.1 Les niveaux de traitement

Il est communément établi en traitement d'images, d'identifier trois niveaux d'application: bas niveau — niveau intermédiaire — haut niveau. Cette catégorisation est établie sur le "degré d'intelligence" des traitements, et par voie de conséquence sur les types de structure et le volume des données consommées, traitées et produites par les algorithmes [DF88, Fau88, Kom90].

#### Traitements de bas niveau

Les algorithmes de bas niveau sont généralement dédiés à l'amélioration de la qualité des images, et à la simplification de leur contenu. La donnée en entrée du programme est une image de certaine dimension. Les données en sortie sont une ou plusieurs images de même dimension. Les pixels produits peuvent avoir été étiquetés en fonction de propriétés locales de l'image (types de texture, propriétés topologiques, etc) ou modifiés par une transformation locale (opérations morphologiques [Kom90], seuillage, filtrage, rotation, extraction de contour, étiquetage par *Shrinking* et par *Broadcast* [CSS90, HT89], convolution [ZXL89], etc).

#### Traitements de niveau intermédiaire

Les algorithmes de niveau intermédiaire extraient d'images pré-traitées (provenant du niveau inférieur), des informations sur les objets qui composent la scène (segmentation par Region growing, par transformée de Hough [KC90], suivi de contour, estimation de mouvement, etc). Les résultats sortis correspondent à des structures de données différentes de l'image (liste de segments de droite, centre d'inertie, champ de mouvement, etc).

| Algorithme                 | Structure  | Type                 |

|----------------------------|------------|----------------------|

| concerné                   | de données | de données           |

| Seuillage                  | Image      | de pixels            |

|                            | Tableau 2D | de caractères        |

| Filtrage                   | Image      | de pixels            |

|                            | Tableau 2D | d'entiers            |

| F.F.T.                     | Image      | de fréquence         |

|                            | Tableau 2D | de flottants         |

| Morphologie                | Image      | binaire              |

|                            | Tableau 2D | de booléens          |

| Rotation                   | Image      | de déplacements      |

|                            | Tableau 2D | d'entiers            |

| Labellisation              | Image      | de réduction binaire |

| (par Shrinking)            | Tableau 3D | de booléens          |

| Labellisation              | Image      | de labels            |

| (par Broadcast)            | Tableau 2D | d'entiers non signés |

| Histogramme                | Image      | de cumul             |

|                            | Tableau 2D | de vecteurs 1D       |

| Segmentation               | Arbre      | quaternaire          |

| (par Region growing)       | Tableau 2D | de tableaux 2D       |

| Segmentation               | Image      | de paramètres        |

| (par Transformée de Hough) | Tableau 3D | d'entiers            |

| Estimation de mouvement    | Champs     | de mouvement         |

|                            | Tableau 2D | d'entiers signés     |

Tab. I.1 - Structures de données en traitement d'image

#### Traitements de haut niveau

Les tâches de haut niveau ont pour objet d'interpréter la scène contenue dans une séquence d'images et font appel aux traitements de niveau inférieur. Basés sur la mise en relation d'objets, ces traitement permettent d'extraire du "sens" des données symboliques passées en entrée, en les associant avec une base de connaissances décrivant les caractéristiques du monde dont l'image est originaire.

#### I.1.2 Degré du parallélisme

Le grain du parallélisme varie fondamentalement en fonction des différents niveaux de traitement de l'image et du déroulement de l'application. La complexité des traitements évolue de la même manière. La catégorisation des algorithmes de traitement de l'image en trois niveaux illustre l'évolution des besoins en termes de contrôle et la nécessité d'utiliser des architectures hétérogènes exhibant les différents types de parallélisme requis (c.f. tableau I.1.2).

En pratique, l'exécution de certaines fonctions standards de traitement d'image est souvent laissée "entre les mains" d'unités câblées (ex. le reformateur de  $P^3I$  [CJC+94, CJG+94a, GBDL+94] une machine parallèle hétérogène dédiée au traitement temps-réel de l'image). L'exécution efficace d'applications en traitement d'images est donc l'apanage de machines dédiées à l'électronique totalement ou partiellement spécialisée.

"In the present state-of-the-art in machine and compiler design, it is not possible to adequately protect the programmer from the need to have knowledge of machine architecture if efficient programs are to be written and tasks are to be interpreted intelligently in the interests both of those specifying the tasks and of those attempting to carry them out." [Duf82, p.274].

|                       | Bas-Niveau               | Niveau-Intermédiaire     | Haut-Niveau  |

|-----------------------|--------------------------|--------------------------|--------------|

| Structures de données | images                   | listes, vecteurs, arbres | complexes    |

| Éléments de structure | centaines de milliers    | centaines                | dizaine      |

| Opérations            | élémentaires             | complexes                | complexes    |

| Communications entre  | très régulières          | irrégulières             | irrégulières |

| éléments de structure | voisinage local du pixel | distantes                | distantes    |

| Parallélisme exhibé   | SIMD                     | MIMD/SPMD                | aucun        |

Tab. I.2 - Les besoins du traitement de l'image

La difficulté porte davantage sur les aspects logiciel que matériel; puisqu'il est toujours possible, moyennant un coût supplémentaire, de concevoir des unités cablées qui réalisent efficacement un certain nombre de fonctions clefs en traitement d'images. Pourtant, les développements sur les machines dédiées continuent à se faire au détriment de la portabilité des applications et même de leur mise à jour lors de modifications éventuelles de l'architecture. Ce qui revient à mésestimer les couts de développement, d'exploitation et de maintenance du logiciel.

Si on raisonne en termes d'applications, n'importe quelle architecture distribuée hétérogène de type généraliste peut constituer "une bonne" plate-forme de développement. Et selon nous, les optimisations liées à l'architecture ne devraient pas transpirer au niveau global pour remettre en cause l'intégralité du processus de développement; elles doivent se restreindre à quelques nœuds fonctionnels sans qu'il soit nécessaire de repenser tout le système (notions de modularité, d'évolutivité, et d'efficacité).

## I.1.3 Mise en œuvre

En pratique, le développement d'applications complexes de traitement de l'image repose traditionnellement sur un découpage en deux niveaux du processus de développement: un niveau fonction et un niveau application. L'utilisateur décrit ainsi dans un premier temps ses algorithmes (niveau fonction), puis la manière selon laquelle ceux-ci vont collaborer pour obtenir le résultat attendu (niveau application).

## I.1.4 Niveau fonction

C'est sur le niveau fonctionnel que repose l'essentiel de la partie algorithmique du programme. Une fonction peut ainsi être simplement extraite de la bibliothèque de l'utilisateur, ou augurer le développement de nouvelles sections de code:

- 1. Utilisation des fonctions standards de la bibliothèque. Il s'agit de fonctions classiques telles que: le seuillage, la convolution, la détection de contours, l'histogramme, la transformée de Fourier, etc, pour lesquelles il existe un certain nombre d'algorithmes bien connus.

- 2. Développement de fonctions incluses dans la bibliothèque de l'utilisateur. Elles répondent à des besoins spécifiques de l'utilisateur, mais bien plus souvent à une carence de la bibliothèque standard ou à l'apport d'une nouvelle technologie (algorithmes récents, optimisations liées à l'architecture).

## I.1.5 Niveau application

La description du programme au niveau application repose sur la connexion des différentes tâches de traitement. En d'autres termes, les développements menés au niveau application consistent à programmer l'enchaînement logique des fonctions de traitement de l'image dont l'évolution dans

le cas des applications temps-réel est liée aux activations provenant de l'environnement (voir SECTION I.2).

Cette phase qui est souvent considérée comme le plus haut niveau d'abstraction, passe généralement par des développements de type graphique (ex. l'EDHN [JCR+96] une interface graphique pour le développement d'application temps-réel de traitement de l'image sur  $P^3I$ ).

Au niveau application, la nature des connexions entre les fonctions (dépendances de données), induit naturellement un formalisme de type data-flow. Cette particularité est d'ailleurs soulignée par le caractère résolument graphique des interfaces.

Le niveau application correspond donc à la description du graphe de contrôle global de l'application. Il s'agit d'un graphe data-flow dont les opérateurs sont des fonctions de traitement de l'image.

#### I.1.6 Conclusion

Le modèle traditionnel de développement d'une application complexe en traitement de l'image mélange donc deux approches. Le niveau fonction suggère une approche descendante, qui correspond à une méthode efficace de spécification pour les algorithmes implémentant une fonction unique, de haut niveau et non susceptible d'évoluer. Et l'emploi au niveau application d'une approche montante qui permet de construire une application (au sens large) en réutilisant et en combinant progressivement des éléments existants.

En d'autres termes, développer une application de traitement de l'image c'est définir une bibliothèque de fonctions élémentaires et décrire la manière dont celles-ci collaborent pour obtenir un résultat déterminé.

Les applications temps-réel se caractérisent de surcroît par les flots ou séquences potentiellement infinies qu'elles manipulent. Par exemple, une application temps-réel de l'image peut prendre ses entrées depuis des capteurs tels que caméras, magnétoscopes, etc, et délivrer des sorties vers des acteurs du monde physique tels que moniteurs, robots, etc. Une conséquence immédiate concerne les temps d'acquisition des entrées, aussi bien que les délais de réponse entrées/sorties qui sont strictes. Mais bien d'autres propriétés fondamentales sont liées à la notion de temps qui dans le domaine particulier d'application du traitement temps-réel constitue une contrainte logique de base.

## I.2 Le temps-réel

Le traitement temps-réel de l'image concerne des secteurs d'activité aussi sensibles et variés que: l'aéronautique, le nucléaire, les applications militaires, etc. Les caractéristiques principales des systèmes temps-réel sont:

- des contraintes de sûreté cruciales. C'est certainement, et de loin, le caractère principal des applications temps-réel. En effet, le dysfonctionnement de tels systèmes peut avoir des conséquences dramatiques. Par conséquent, dans de nombreux cas, la vérification formelle des systèmes temps-réel est fondamentale. Il faut donc pouvoir se doter d'outils et modèles mathématiques permettant de garantir statiquement le déterminisme des applications,

- un parallélisme intrinsèque. En effet, il est très souvent commode et même naturel de concevoir de tels systèmes comme un ensemble de composants coopérant et s'exécutant concurremment,

- des contraintes temporelles strictes. Ces contraintes concernent aussi bien le rythme d'acquisition des entrées que les temps de réponse entrées/sorties. Il faut être capable d'exprimer ces contraintes dans la spécification du problème, de les prendre en compte dans la conception du système, et de vérifier que l'implémentation les respecte.

I.2. LE TEMPS-RÉEL

Les problèmes qui peuvent apparaître lors de la spécification et la réalisation d'une application temps-réel ne sont généralement pas abordés en informatique classique: prise en compte du temps comme contrainte logique de base, et non comme facteur de performance, et impératifs de sûreté obligeant à considérer l'erreur de fonctionnement comme un phénomène qu'il faut prévoir [Cos91].

#### I.2.1 Taxinomie

Dans la littérature qui traite du temps-réel, on opère souvent une distinction entre les systèmes temps-réel et les systèmes plus généralement réactifs ou transformationnels. Cette classification est basée sur la notion de comportement du système.

#### Système Transformationnel

Un système transformationnel est un système qui accepte des entrées, les transforme, et produit des sorties [Dzi90]. Une notion d'interactivité intervient lorsque le processus de calcul (ou transformation) requiert des informations supplémentaires qui peuvent être fournies par l'utilisateur.

#### Système Réactif

On appellera réactif, un système qui maintient une interaction permanente avec son environnement physique [BB91]. Son rôle consiste à réagir instantanément à des entrées provenant de façon répétitive de son environnement en produisant lui-même des sorties vers cet environnement (on parle également de systèmes dirigés par les événements). Ces systèmes seront par conséquent décrits en termes de comportement.

La difficulté suivante est souvent évoquée à propos des systèmes réactifs: les événements peuvent arriver à des instants imprévisibles, et doivent être pris "rapidement" en compte par le système.

#### Système Temps-réel

Pour notre part, nous avons adopté la distinction faite notamment dans [BB91] qui assimile les systèmes temps-réel à une particularisation des systèmes réactifs.

La dénomination temps-réel est plutôt réservée aux systèmes réactifs qui sont de surcroît sujets à des contraintes de temps définies extérieurement. Ainsi, un système temps-réel est défini comme un système qui maintient une relation continuelle (en opposition avec événementielle) avec un environnement asynchrone; c'est-à-dire un environnement qui progresse indépendamment du système temps-réel, d'une manière non-coopérante; par conséquent, un système temps-réel est pleinement responsable de la propre synchronisation de ses opérations par rapport à son environnement.

#### Système Mixte

Un système temps-réel complexe est généralement constitué d'une partie transformationnelle, et d'une partie réactive. Lors de l'exécution d'une application, ces deux parties interagissent. La méthode de conception associée est donc mixte: une partie réactive pour permettre une gestion efficace des événements visant à satisfaire les contraintes temps-réel strictes, et une partie transformationnelle réalisant le traitement des données (exécution d'algorithmes complexes). À cet égard, les applications complexes de traitement temps-réel de l'image appartiennent bien à cet ensemble de problèmes mixtes.

#### I.2.2 Mise en œuvre

Programmées en premier lieu en utilisant des machines analogiques et des circuits relais, les applications temps-réel bénéficièrent du développement des microprocesseurs et des ordinateurs. Les outils de programmation restaient cependant de bas niveau et spécifiques.

Avec l'évolution rapide des technologies et des besoins, les techniques de programmation bas niveau sont vite devenues inacceptables et inadaptées au développement d'applications complexes, qui posent des contraintes fortes en termes de sécurité.

Pour la résolution de tels problèmes, l'utilisation de langages de haut niveau est indispensable. Il existe *en gros* aujourd'hui deux grandes approches: une approche asynchrone — et une approche synchrone. Toutes deux exhibent des avantages et inconvénients respectifs qui apportent des réponses partielles aux problèmes posés par le traitement temps-réel.

#### Approche asynchrone

Les langages asynchrones ont essentiellement émergé avec l'apparition des architectures multiprocesseurs. Nous nous référons principalement ici au modèle CSP de Hoare [Hoars].

Ces langages ont été conçus dès l'origine sur les principes de modularité et de concurrence (ex. ADA [RCDS90]). Ils ont l'avantage de posséder des primitives de gestion de processus indispensables à la programmation naturelle des systèmes temps-réel. Ils permettent en particulier de traiter à la fois les aspects calculatoires et les services de programmation parallèle et d'exécution répartie.

On trouve ainsi des primitives autorisant le démarrage, l'arrêt et la suspension de l'exécution des tâches. Des primitives de synchronisation et de partage de ressources sont également disponibles. De surcroît, la majeure partie de ces langages dispose d'environnements de développement.

En outre, la plupart des applications écrites à l'aide des langages asynchrones ont l'avantage d'être indépendantes des configurations matérielles et des systèmes d'exploitation. En théorie du moins, elles peuvent être exécutées sur des machines monoprocesseur ou sur un réseau de processeurs. Ce qui est appréciable lorsque l'on s'intéresse à la portabilité.

Finalement, beaucoup d'expériences a été acquise dans l'utilisation de ces techniques.

Toutefois, plusieurs inconvénients majeurs sont associés à l'utilisation de ces langages: ils sont tout d'abord intrinsèquement non déterministes. Bien qu'une communication soit vue comme une synchronisation entre deux processus, le temps pris entre la possibilité d'une communication et son accomplissement peut être arbitraire et est imprévisible. Lorsque plusieurs communications doivent être réalisées, leur ordre d'établissement est également aléatoire. Si bien qu'un même programme peut admettre plusieurs exécutions différentes pour une même séquence d'entrée. Ce non-déterminisme est inadapté au contrôle des applications temps-réel.

En outre, il n'est pas possible de réaliser des vérifications automatiques des programmes produits, et par conséquent impossible de garantir statiquement la sûreté des applications.

De plus, ces langages ne proposent aucune structure permettant de traiter le concept de temps autrement que comme simple facteur de performance.

Finalement, les langages de programmation asynchrones, s'ils présentent de nombreux avantages au niveau de l'implémentation des systèmes temps-réel, semblent mal adaptés à la spécification des problèmes où le temps apparaît comme contrainte logique de base, et aux raisonnements temporels.

#### Approche synchrone

Les langages synchrones ont été introduits très récemment en réponse aux besoins soumis par la prise en compte du temps dans la spécification de problèmes où des relations temporelles complexes doivent être modélisées.

Le contexte formel fourni par les langages synchrones permet non seulement de spécifier les relations temporelles complexes qui interviennent naturellement dans les systèmes temps-réel, mais également d'effectuer des preuves automatiques des programmes. Ils ont introduit pour cela un ensemble de primitives "idéales", non présentes jusqu'alors dans les langages de programmation classiques, et qui permettent de raisonner sur le temps comme n'importe quel autre domaine de valeur.

Toutefois, même si l'approche synchrone est idéale pour décrire des relations temporelles complexes et raisonner formellement sur le temps, elle pose néanmoins de sérieux problèmes en termes

I.2. LE TEMPS-RÉEL 11

d'implémentation. A contrario, les langages asynchrones conçus dès le début en termes d'implémentation ne pose pas de problème de ce point de vue.

Nous reprendrons plus en détail dans une partie ultérieure de ce chapitre (c.f. SECTION I.3), les caractéristiques qui sont particulièrement liées à l'hypothèse de synchronisme.

## Synthèse des approches

Sur les deux points précédents, on peut finalement conclure par: "In practice, each style tends to be weak where the other is strong" [BB91]. L'hypothèse de synchronisme pose en effet un cadre formel essentiel pour raisonner sur le temps, alors que le modèle asynchrone répond idéalement aux problèmes posés par l'implémentation.

Alors que l'on a longtemps considéré ces deux hypothèses comme plus ou moins antagonistes, il est clair qu'une approche mixte combinant les avantages respectifs des modèles synchrones et asynchrones serait de loin particulièrement séduisante.

## I.2.3 Modélisation

Les programmes temps-réel (au sens large) consomment des données en provenance de capteurs connectés au monde physique (par exemple des caméras). En réponse, ils doivent construire les commandes de sortie du système (par exemple affichage d'images traitées sur un moniteur).

Les systèmes temps-réel manipulent des valeurs, ou plus exactement des séquences de valeurs qui représentent des suites potentiellement infinies appelées signaux dans le langage SI-GNAL [BLG90] (ou encore tissu dans  $\mathbf{8}^{1/2}$  [GS93], ou flot dans LUSTRE [HCRP91a], etc). Par exemple, le signal x dénote la séquence infinie  $\{x_t\}_{t\geqslant 0}$ , où l'index de temps t est attaché à ce signal. Contrairement aux variables dans les langages classiques, les valeurs d'un signal ne sont pas persistantes; c'est-à-dire que l'accès au temps t de la valeur qui a été portée par l'occurrence  $x_{t-1}$  du signal x n'est pas direct.

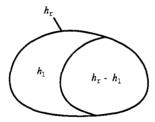

Un signal porte deux types d'informations:

- une information de contrôle liée à sa présence à un instant donné,

- une information de valeur.

L'exécution d'un système temps-réel est rythmée par l'émission et la réception de ces signaux.

Tout signal, en plus des valeurs qu'il prend normalement dans son intervalle de définition, peut être affecté d'une valeur spéciale représentant l'absence d'événement à un instant donné. Le symbole utilisé pour noter l'absence d'événement est:  $\bot$ . L'absence d'événement est une notion commune aux langages LUSTRE et SIGNAL.

À chaque signal est implicitement associée une horloge qui définit les instants où le signal est présent (on note généralement: T). La notion d'horloge est d'une certaine façon un moyen de décorréler la fonction de contrôle pure d'un signal de sa fonction de valeur. Deux signaux possédant la même horloge sont dits synchrones. L'horloge d'un signal ne fait pas référence à un temps de base (e.g. l'horloge du système), le rôle des horloges est de permettre de parler des relations temporelles existant entre les divers signaux d'un programme.

La préoccupation principale en SIGNAL est que toutes les questions de synchronisation soient complètement réglées à la compilation, de telle manière que la phase d'exécution n'ait pas à se préoccuper des  $\bot$ 's. Cet objectif est atteint par une représentation statique des relations temporelles exprimées par chaque opérateur (voir ANNEXE B).

#### I.2.4 Conclusion

Les problèmes temps-réel ont introduit un certain nombre de besoins nouveaux en informatique classique:

- besoin d'exprimer les contraintes temporelles complexes qui existent naturellement entre les différents signaux échangés par les tâches,

- besoin d'outils formels et de modèles mathématiques pour garantir statiquement l'existence et l'unicité de solution à un problème donné.

Ces besoins interviennent pour une part dès la spécification des problèmes: expression des relations temporelles complexes; et pour l'autre part au niveau des outils de compilation: preuve statique des programmes.

Les applications complexes de traitement temps-réel de l'image font partie des systèmes mixtes (c.f. SECTION I.2.1), c'est-à-dire qu'ils sont généralement dotés au niveau fonctionnel d'une lourde partie algorithmique, et au niveau application d'un système complexe de contrôle et de commande.

La méthode de conception associée est donc mixte: développement d'une bibliothèque de taches séquentielles traditionnelles de traitement d'images au niveau fonctionnel — description de l'enchaînement logique des tâches, ainsi que des relations complexes existant naturellement entre les signaux échangés par celles-ci au niveau application.

Le dernier point sous-entend le besoin d'introduire de nouveaux opérateurs qui permettent d'exprimer simplement les contraintes temporelles dans la spécification des problèmes. Ainsi que des méthodes formelles basées sur ces nouveaux opérateurs qui permettent de raisonner statiquement sur le temps comme n'importe quel autre domaine de valeur. Ces outils sont fournis par l'approche synchrone que nous décrivons dans la section suivante.

Au niveau implémentation, les langages de programmation concurrents constituent une piste intéressante:

- la décomposition d'une application en un ensemble de tâches comme le suggère la manière traditionnelle d'aborder les problèmes en traitement temps-réel de l'image, est inhérente au modèle de programmation concurrent,

- ces techniques sont relativement indépendantes des architectures ce qui facilite l'évolutivité et la ré-utilisabilité du code produit: ces deux propriétés constituent le minimum des services attendus lorsque l'on développe des bibliothèques de fonctions,

- enfin, et surtout, les langages de programmation concurrents fournissent un ensemble de primitives de manipulation de processus essentiels à l'implémentation des systèmes temps-réel.

L'approche que nous avons adoptée vise à combiner les avantages respectifs des modèles synchrones et asynchrones. En spécifiant et vérifiant les systèmes temps-réel sous l'hypothèse de synchronisme, et en fournissant les outils formels permettant d'obtenir automatiquement une implémentation asynchrone traditionnelle.

## I.3 L'hypothèse de synchronisme

Les langages synchrones ont été introduits pour faciliter la tâche du programmeur en lui fournissant des primitives "idéales", permettant de raisonner comme si le programme réagissait *ins*tantanément aux événements externes. Le modèle d'exécution est alors rendu déterministe. Et il est ainsi possible d'effectuer des preuves, des tests, de répéter l'exécution des programmes. L'approche synchrone permet de raisonner sur le temps comme n'importe quel autre domaine de valeur [LGG90]. Pour cela, elle ne considère l'évolution d'une application que sur une discrétisation du temps physique (ce qui suppose des temps de calcul et de communication bornés); autrement dit, elle réalise une abstraction logique du temps. La notion de synchronisme qualifie ici la manière de raisonner sur le temps, et ne se réfère absolument pas à une réalité physique.

"Ces langages (les langages synchrones) abandonnent tous l'hypothèse d'asynchronisme qui est à la base des langages classiques, pour la remplacer par une hypothèse de synchronisme plus ou moins forte. ( . . . ) On suppose ainsi que les sorties sont fournies de manière absolument synchrone aux entrées, donc que leur calcul  $\ll$  ne prend pas de temps  $\gg$ " [BCG87, p.306].

L'hypothèse de synchronisme n'est par ailleurs pas neuve: les physiciens savent bien qu'à un niveau assez fin les causes et les effets ne sont pas synchrones; cela ne les empêche pas d'appliquer les équations "instantanées" de NEWTON ou de MAXWELL aux phénomènes macroscopiques. En électricité, la plupart des raisonnements supposent une propagation instantanée du courant électrique. Dans tous les cas, l'hypothèse de synchronisme simplifie considérablement l'étude des phénomènes, pourvu qu'on soit dans son domaine de validité [BCG87].

## I.3.1 Propriétés du synchronisme

En pratique, l'hypothèse de synchronisme revient à supposer que le programme réagit assez vite pour percevoir les événements externes en bon ordre. Deux notions importantes en découlent: instantanéité et simultanéité.

#### L'instantanéité

La dynamique des systèmes synchrones s'inscrit dans un temps logique pour lequel les tâches élémentaires ont une durée nulle; tout se passe comme si les tâches étaient exécutées sur des processeurs de puissance infinie, elles sont instantanées [LG89].

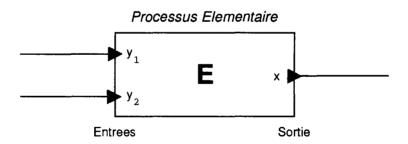

En pratique, si on considère par exemple un processus élémentaire comportant deux signaux d'entrée et un signal de sortie, la notion d'instantanéité s'exprime logiquement par le fait que: pour tout t, la  $t^{\text{ième}}$  occurrence sur la première entrée est évalué avec la  $t^{\text{ième}}$  occurrence de la seconde entrée, pour produire une  $t^{\text{ième}}$  occurrence en sortie.

## La simultanéité

Plusieurs temps logiques peuvent coexister (on parle de temps multiforme), cependant les instants où ces temps coïncident sont tous connus; si deux instants coïncident, ils sont simultanés [LG89].

La notion de simultanéité est liée aux relations de présence et d'absence des signaux les uns par rapport aux autres. Ainsi par exemple, si on considère un couple (x,y) de signaux, les événements possibles sont:

- (xt, yt) les deux signaux sont simultanément présents,

- $(x_t, \perp)$  le signal  $x_t$  est présent, le signal  $y_t$  est absent,

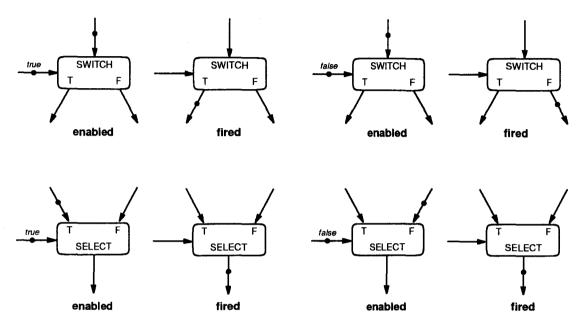

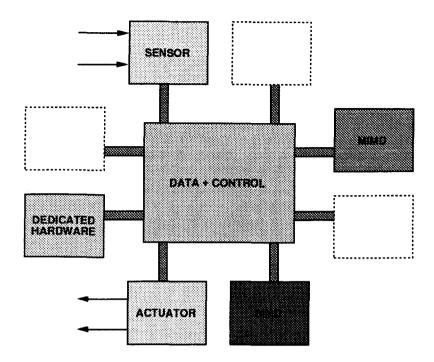

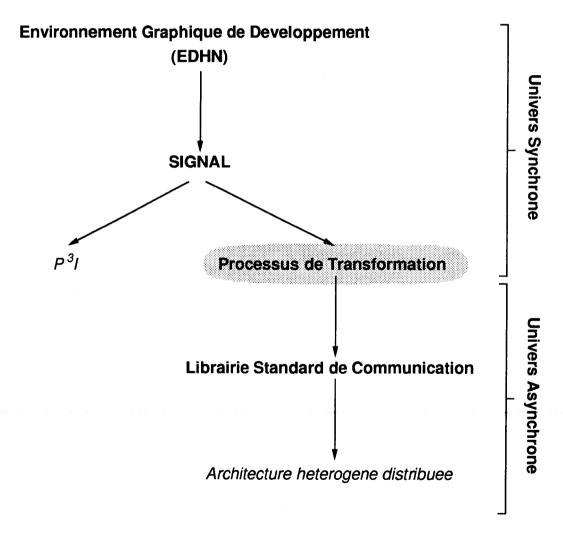

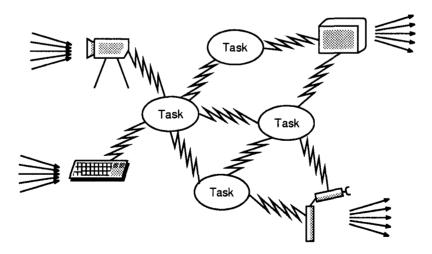

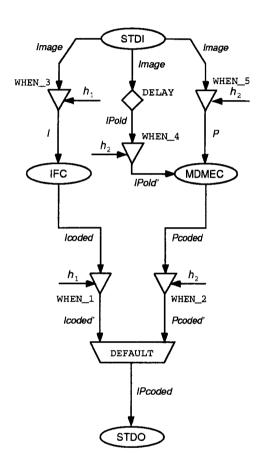

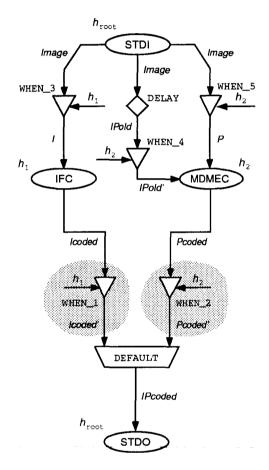

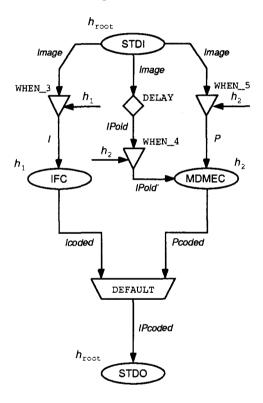

- $(\bot, y_t)$  le signal  $x_t$  est absent, le signal  $y_t$  est présent.