gar Zonoys I

Nº d'ordre: 2014

### **THESE**

Présentée à

## L'UNIVERSITE DES SCIENCES ET TECHNOLOGIES DE LILLE

pour obtenir le titre de

### DOCTEUR DE L'UNIVERSITE

Spécialité : ELECTRONIQUE

par

Laurent RULLIER Ingénieur E.U.D.I.L.

## CONTRIBUTION A LA MODELISATION NON-LINEAIRE DE HEMTS DE PUISSANCE. APPLICATION A L'AMPLIFICATION CLASSE B EN BANDE Ka.

Soutenue devant la Commission d'Examen le 18 juin 1997

Membres du Jury: MM. G. **SALMER** Président

Υ. **CROSNIER** Directeur de Thèse H. **GERARD** Co-Directeur de Thèse

J.L. **GAUTIER** Rapporteur C. **RUMELHARD** Rapporteur

**VERRIELE** H. Examinateur

P.A. **ROLLAND** Examinateur M.

**SOULARD** Examinateur

A Mickaële A toute ma famille Ce travail a été réalisé au Département Hyperfréquences et Semi-conducteurs (DHS) de l'Institut d'Electronique et de Micro-électronique du Nord (IEMN) dirigé par Monsieur le Professeur E. CONSTANT.

Je remercie vivement Monsieur le Professeur G. SALMER Directeur du DHS, de me faire l'honneur de présider la commission d'examen.

Je tiens à exprimer ma reconnaissance envers Monsieur H. GERARD et Monsieur le Professeur Y. CROSNIER qui ont assuré le direction de ce travail. Je leur exprime ma gratitude pour l'aide qu'ils m'ont apportée.

Je remercie sincèrement Monsieur le Professeur J. L. GAUTIER de l'ENSEA et Monsieur le professeur C. RUMELHARD du CNAM Physique des semi-conducteurs.

J'exprime également mes plus vifs remerciements à Messieurs H. VERRIELE, Docteur, Ingénieur au département Guerre Electronique de la DSP/STTC de la DGA, P. A. ROLLAND Professeur à l'USTL et M. SOULARD, Docteur, Responsable de la CAO MMIC à ALCATEL TELECOM. Je remercie, aussi, la DRET pour son soutien financier pendant ces trois années de thèse.

Que mes camarades du laboratoire veuillent bien trouver ici l'expression de ma reconnaissance pour la sympathie qu'ils m'ont témoignée.

Je voudrais également remercier Mesdames E. DELOS et S. LEPILLET et Monsieur D. VANDERMOERE qui m'ont aidé à réaliser l'expérimentation des circuits et des composants, ainsi que Monsieur E. PLAYEZ Directeur de la centrale de caractérisation.

Je remercie également Messieurs JENNEQUIN, MICHON et ANDRIES de l'atelier de mécanique et Monsieur DEHORTER pour la reproduction de ce mémoire.

### **TABLE DES MATIERES**

|              | TRODUCTION GENERALE                                                               |             |

|--------------|-----------------------------------------------------------------------------------|-------------|

| [ <b>-</b> , | AMPLIFICATION DE PUISSANCE                                                        | 4           |

|              | I-1. INTRODUCTION                                                                 | 4           |

|              | I-2. PRINCIPE, CLASSES DE FONCTIONNEMENT, ASSOCIAT                                | IONS        |

|              | D'AMPLIFICATEURS                                                                  |             |

|              | I-2.1. Amplification linéaire                                                     | 4           |

|              | I-2.1.a. Gain de transducteur                                                     | 5           |

|              | I-2.1.b. Gain en puissance                                                        | 8           |

|              | I-2.1.c. Gain en puissance disponible                                             | 9           |

|              | I-2.1.d. Gain unilatéral                                                          |             |

|              | I-2.1.e. Gain en courant de court-circuit                                         | 10          |

|              | I-2.2. Amplificateur non-linéaire                                                 | 11          |

|              | I-2.3. Associations d'amplificateurs                                              | 12          |

|              | I-2.3.a. Association sans déphasage entre les signaux                             | 13          |

|              | I-2.3.b. Association avec déphasage de 180° entre les signaux ou Amplificateur d  | e typ       |

|              | « Push-Pull »                                                                     | 13          |

|              | I-2.3.c. Association avec déphasage de 90° entre les signaux ou Amplificateur HRA | <b>\</b> 14 |

|              | I-2.4 Conclusion.                                                                 | 15          |

|              | 1-3. HISTORIQUE SUR LA CONCEPTION D'AMPLIFICATEURS DE PUISSA                      | NCE         |

|              | EN BANDE KA                                                                       | 15          |

|              | 1-3.1. Amplificateurs conçus autour de 35 GHz                                     | 15          |

|              | I-3.2. Amplificateurs conçus autour de 20 GHz                                     | 16          |

|              | I-3.3. Amplificateurs conçus autour de 28 GHz                                     |             |

|              | 13.4. Conclusion                                                                  | 18          |

|              | I-4. SCHEMAS EQUIVALENTS DU TEC ASGA                                              | 19          |

|              | I-4.1. Schéma linéaire                                                            |             |

|              | I-4.2. Schéma non - linéaire                                                      | 23          |

|              | I-5. CARACTERISATION DES TECS                                                     |             |

|              | I-5.1. Mesures statiques                                                          |             |

|              | I-5.2. Mesures quasi - statiques impulsionnelles                                  |             |

|              | I-5.3. Mesures hyperfréquences à l'analyseur de réseaux jusque 40 GHz             | 27          |

|              | I-5.4. Mesures hyperfréquences pulsées à l'analyseur de réseaux jusque 20 GHz     |             |

|              | I-5.5. Mesures sur le banc à charge active 26-40 GHz                              |             |

|              | I-6. CONCLUSION                                                                   |             |

|              |                                                                                   |             |

| 11-          | AUTOMATISATION D'UN BANC DE MESURES I (V) EN IMPULSIONS                           |             |

|              | II-1. INTRODUCTION                                                                | 37          |

|              | II-2. ETUDE PRELIMINAIRE ET PRINCIPE DE MESURE                                    |             |

|              | U.2.1. Phánamana tharmigua                                                        | 37          |

| II-2.2. Phénomènes de piégeage des électrons                        | 39            |

|---------------------------------------------------------------------|---------------|

| II-2.2.a. Influence de la fréquence du signal sur les pièges        |               |

| II-2.2.b. Influence de la polarisation du transistor sur les pièges |               |

| II-2.2.c. Influence de la température sur les pièges                |               |

| II-2.3. Principe de la mesure                                       |               |

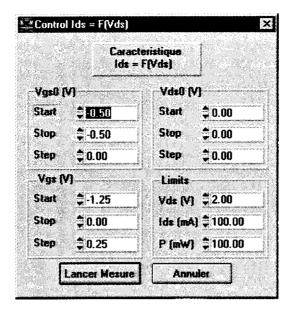

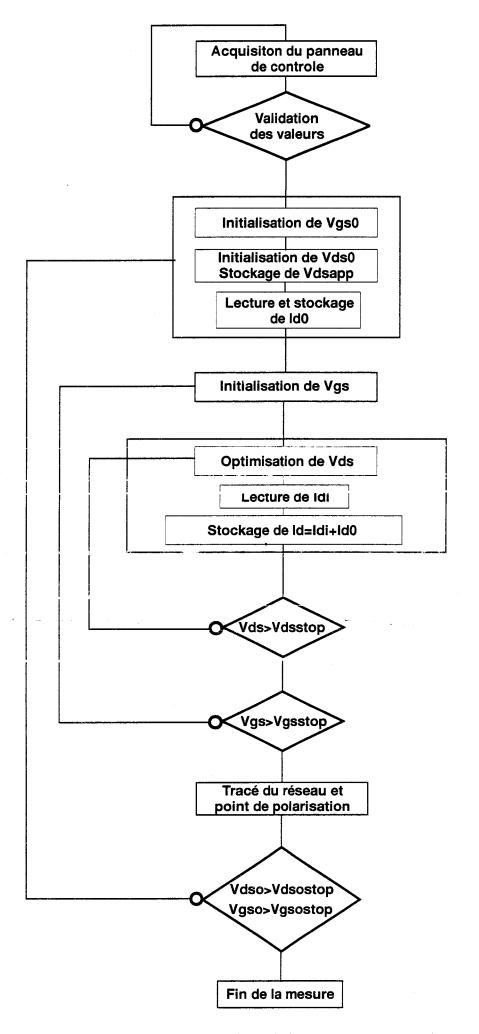

| II-2.4. Fonctionnalités du logiciel                                 |               |

| II-2.5. Mise en œuvre de l'automatisation                           |               |

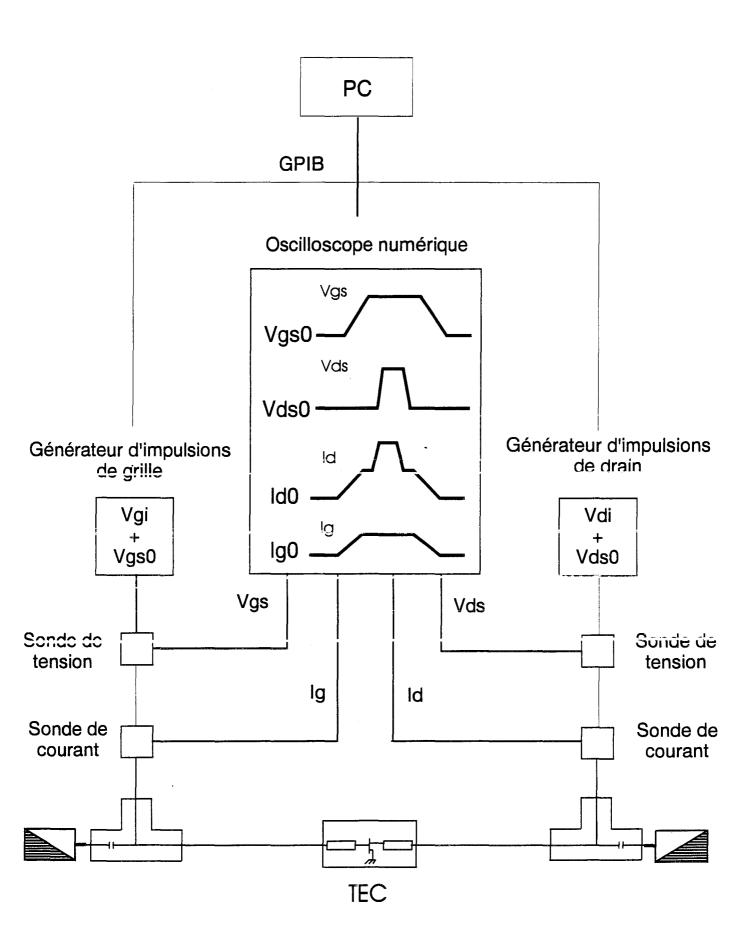

| II-3. BANC AUTOMATIQUE DE MESURES I/V EN IMPULSIONS - VERSION 1     |               |

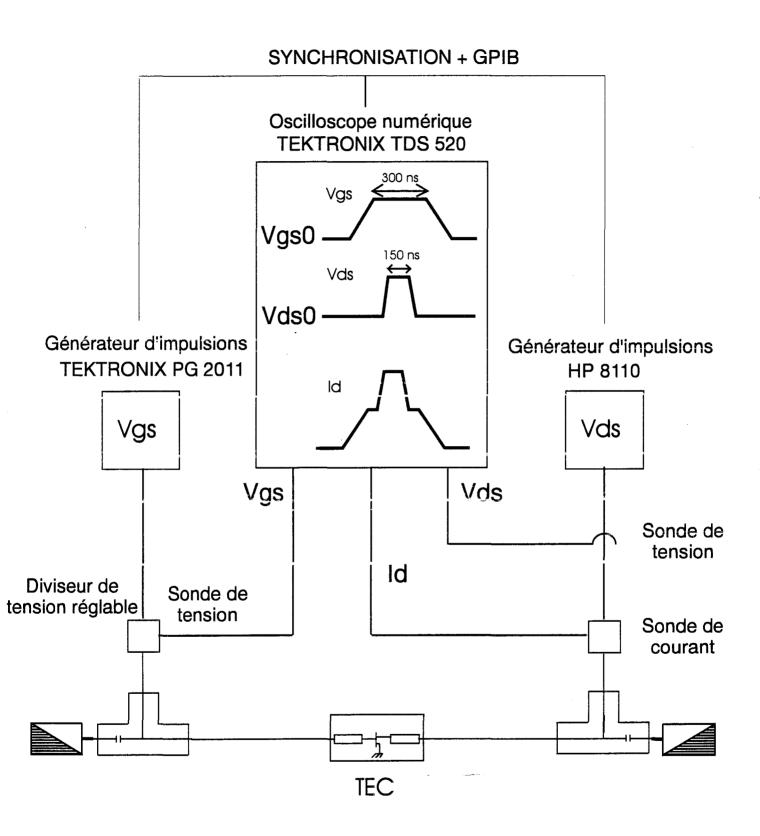

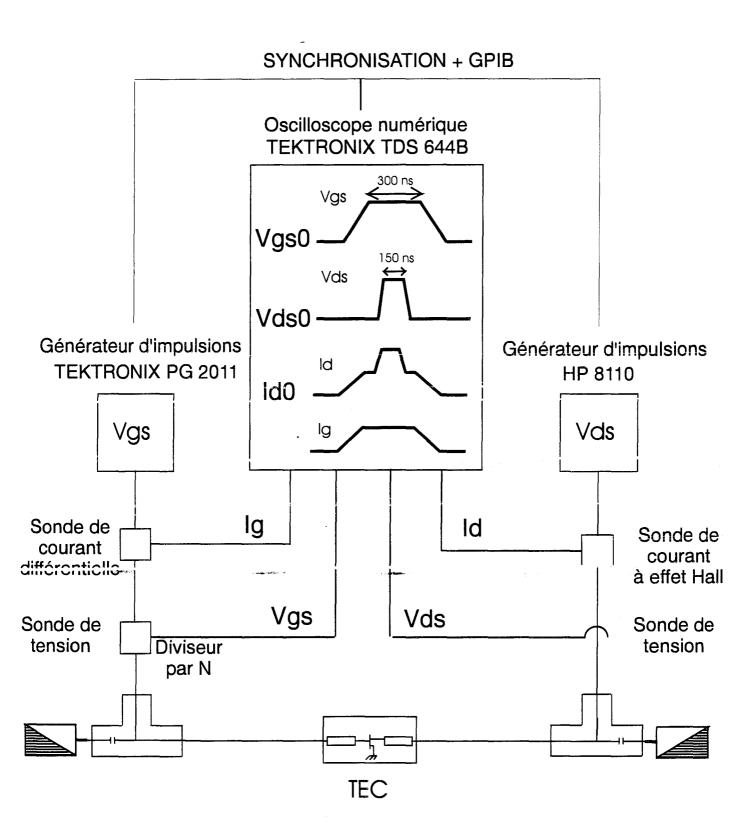

| II-3.1. Description du matériel                                     |               |

| II-3.1.a. Les générateurs d'impulsions                              |               |

| II-3.1.b. L'oscilloscope                                            |               |

| II-3.1.c. Les sondes de courant et de tension.                      |               |

| II-3.2. Problèmes rencontrés et solutions adoptées                  |               |

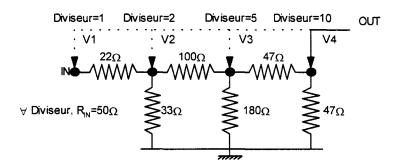

| II-3.2.a. Procédure d'ajustage de la tension de grille              |               |

| II-3.2.b. Procédure d'ajustage de la tension de drain               |               |

| II-3.2.c. Acquisition des niveaux de tension par l'oscilloscope     |               |

| II-3.2.c.1. Mesure de la tension grille - source                    |               |

| II-3.2.c.2. Mesure de la tension drain - source.                    |               |

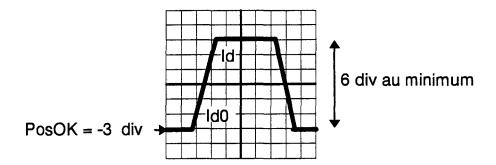

| II-3.2.d. Mesure du courant de drain pulsé                          |               |

| II-3.2.e. Mesure de la composante continue du courant de drain      | 59            |

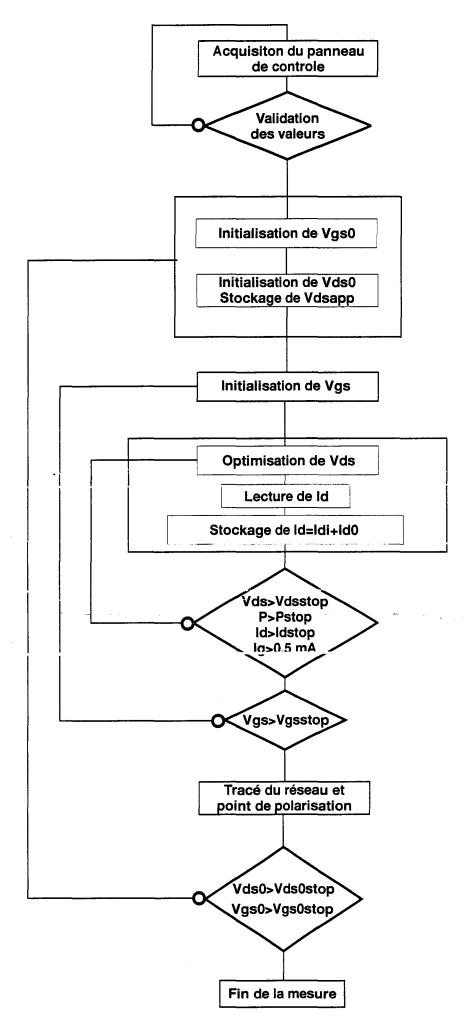

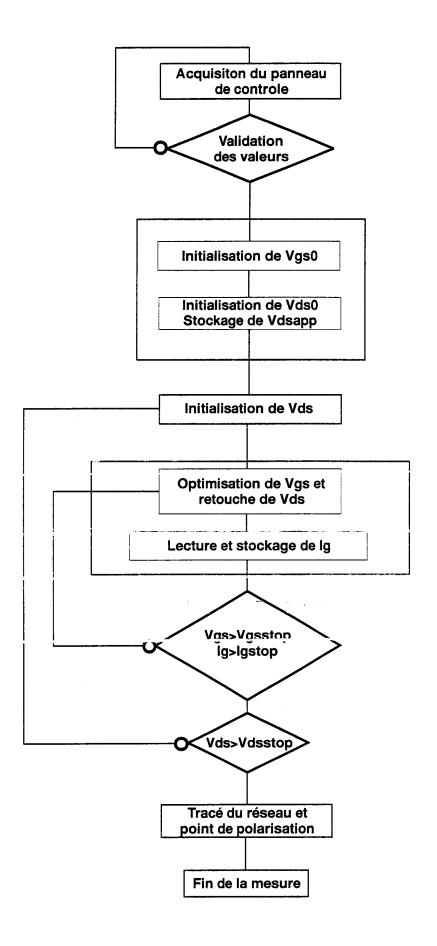

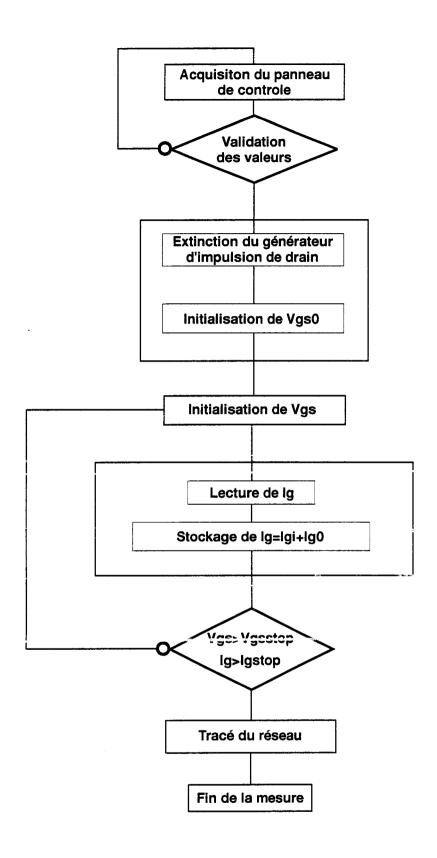

| II-3.3. Algorithme de la caractérisation I(V) pulsée                |               |

| II-3.4. Mesures effectuées                                          |               |

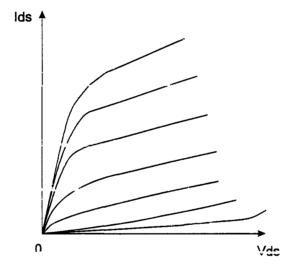

| II-3.4.a. Mise en évidence des effets de piège                      | 62            |

| 11-3.4.b. Mise en évidence des effets thermiques                    |               |

| II-3.4.c. Mesures pour le concepteur de circuit                     |               |

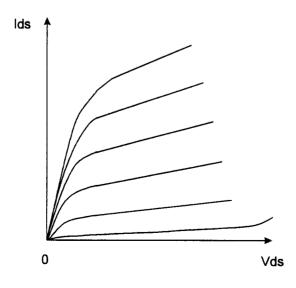

| U.3.4.c.1. Conception d'un amplificateur classe A                   | <del>64</del> |

| II-3.4.c.2. Conception d'un amplificateur classe B                  |               |

| II-3.5. Conclusion sur la première version du banc                  |               |

| II-4. BANC AUTOMATIQUE DE MESURES I/V EN IMPULSIONS - VERSION 2     |               |

| II-4.1. Description du matériel                                     |               |

| II-4.1.a. Oscilloscope 4 voies                                      | 66            |

| II-4.1.b. Les sondes de courant                                     | 67            |

| II-4.1.b.1. Sonde de courant du drain                               | 67            |

| II-4.1.b.2. Sonde de courant de la grille                           | 67            |

| II-4.2. Problèmes rencontrés et solutions adoptées                  | 68            |

| II-4.2.a. Mesure de la tension de drain                             | 68            |

| II-4.2.b. Mesure du courant de drain                                | 68            |

| II-4.2.c. Ajustage de la tension de grille                          | 69            |

| II-4.2.d. Mesure du courant de grille                               | 69            |

| II-4.3. Algorithmes des différents types de mesures                 | 69            |

| II-4.4. Mesures effectuées                                          | 70            |

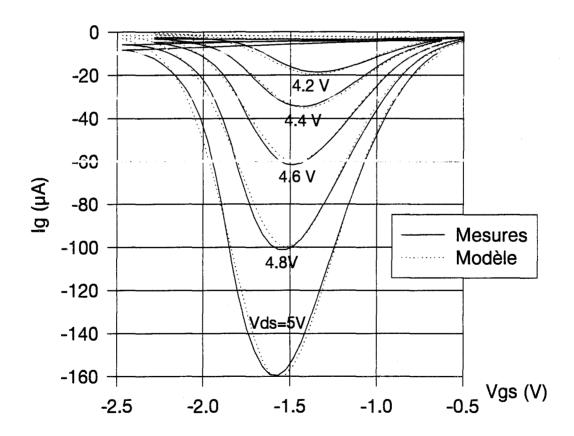

| II-4.4.a. Mesure du courant de grille en direct                     |               |

| II-4.4.b. Mesure du courant de grille en inverse                    | 70            |

| II-4.5. Conclusion sur la seconde version du banc                   | 71            |

| II-5. CONCLUSION                                                    | 71            |

| III- MODELISATION NON-LINEAIRE DES TECS                                       | 74   |

|-------------------------------------------------------------------------------|------|

| III-1. INTRODUCTION                                                           | 74   |

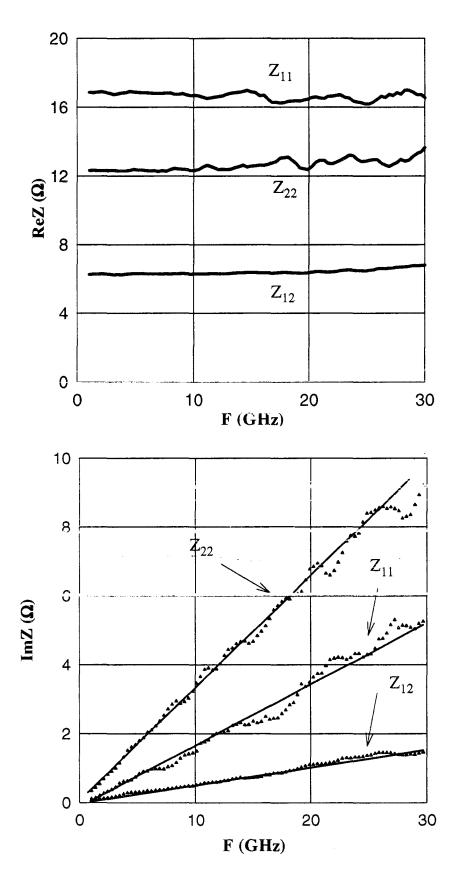

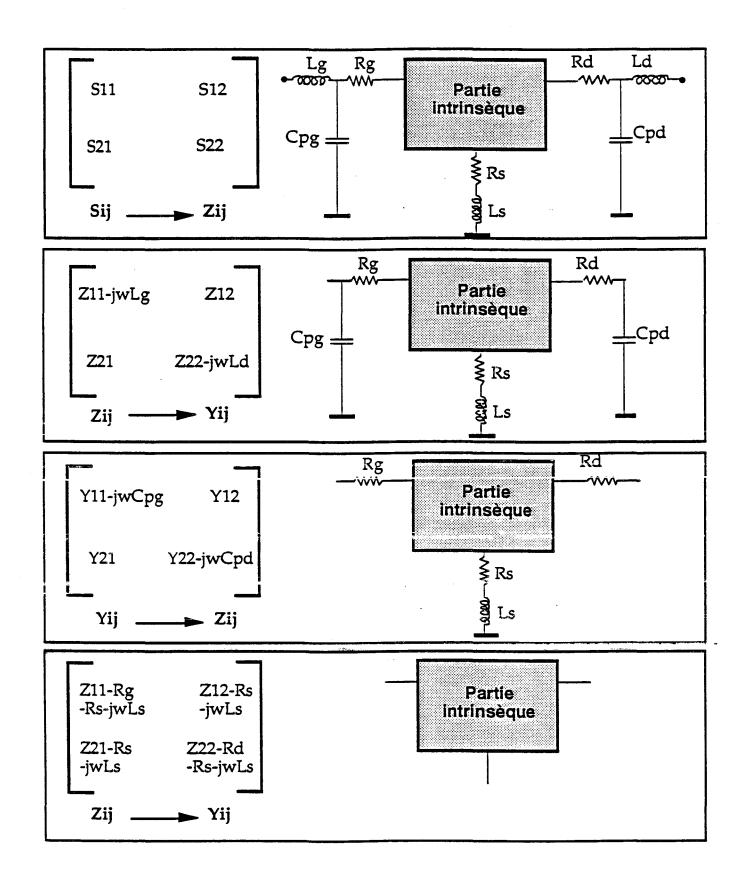

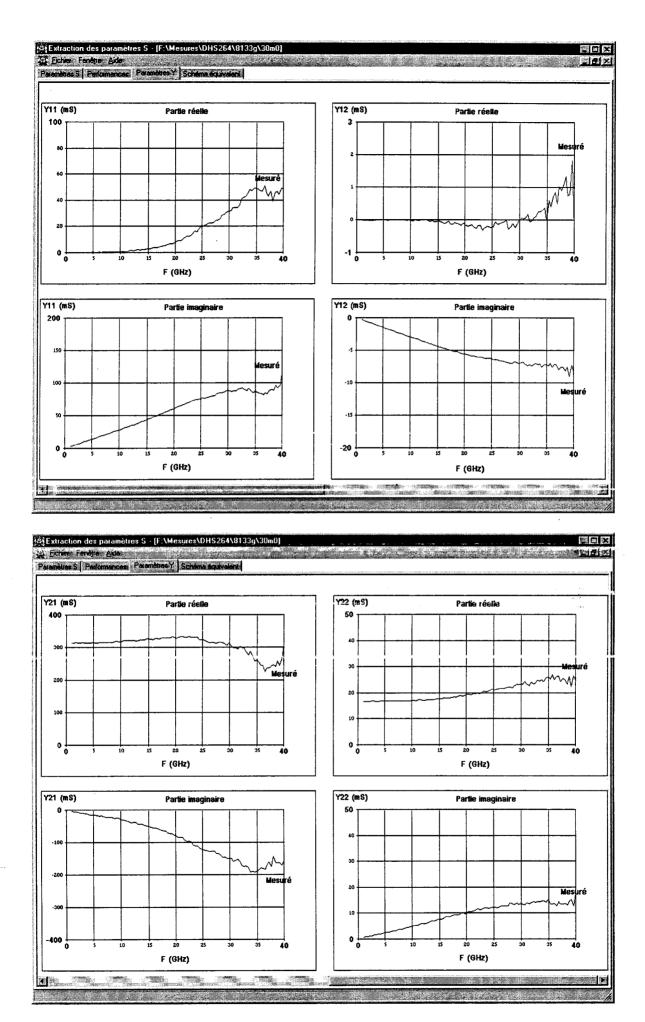

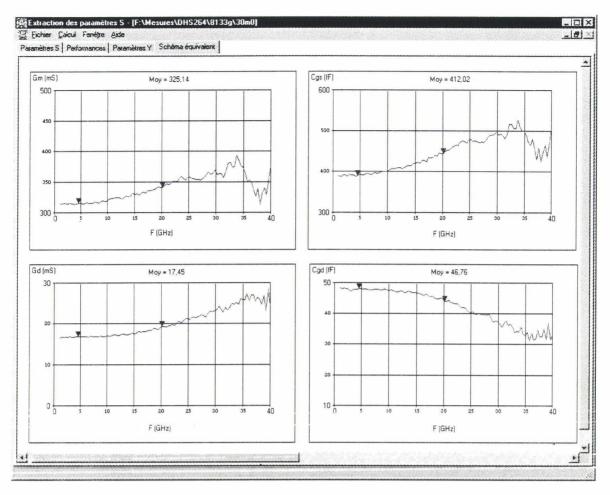

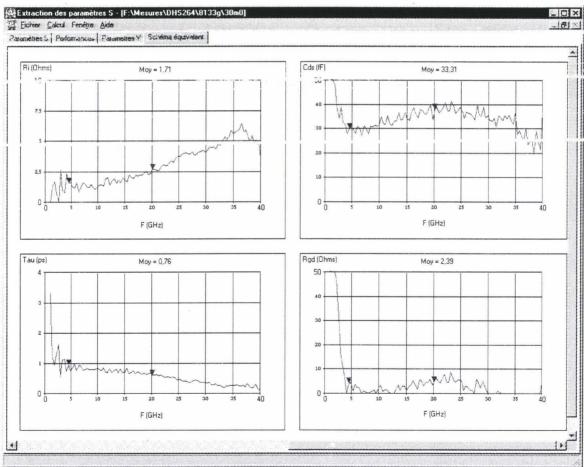

| III-2. EXTRACTION DU SCHEMA EQUIVALENT PETIT SIGNAL                           | 74   |

| III-2.1. Détermination des résistances et des selfs d'accès                   |      |

| III-2.2. Détermination des capacités des plots                                | 76   |

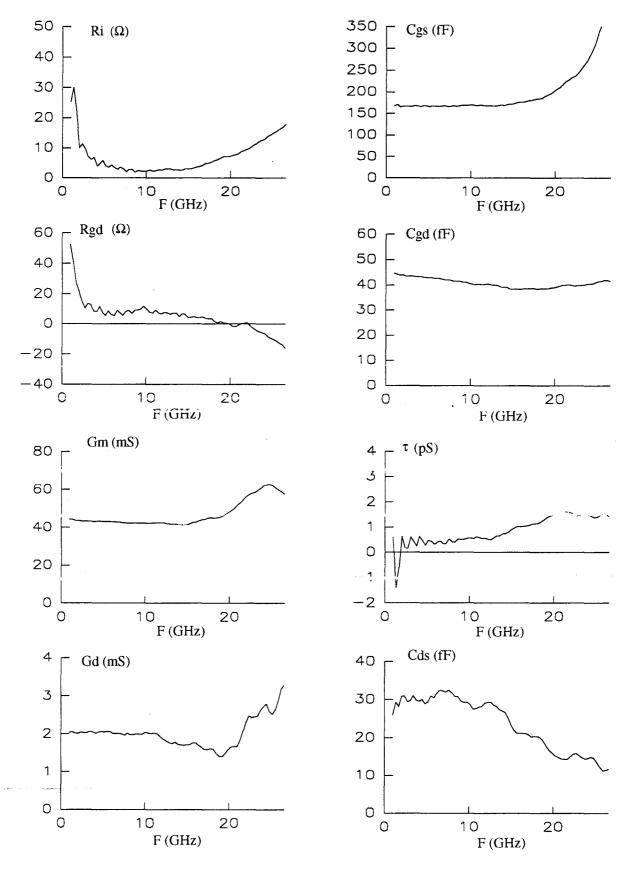

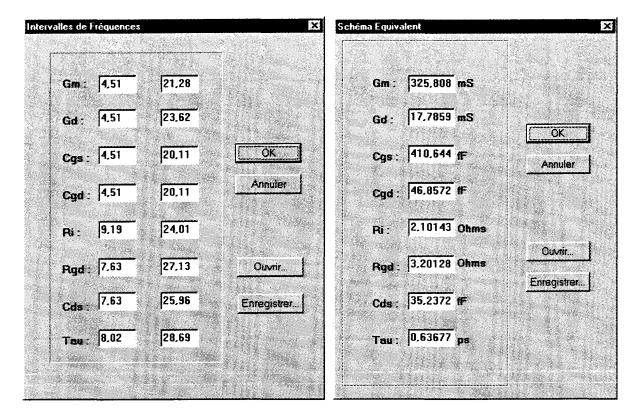

| III-2.3. Extraction des éléments du schéma équivalent intrinsèque             | 80   |

| III-2.3.a. Principe de la méthode                                             | 80   |

| III-2.3.b. Amélioration de la méthode : développement du logiciel « Extract » | 82   |

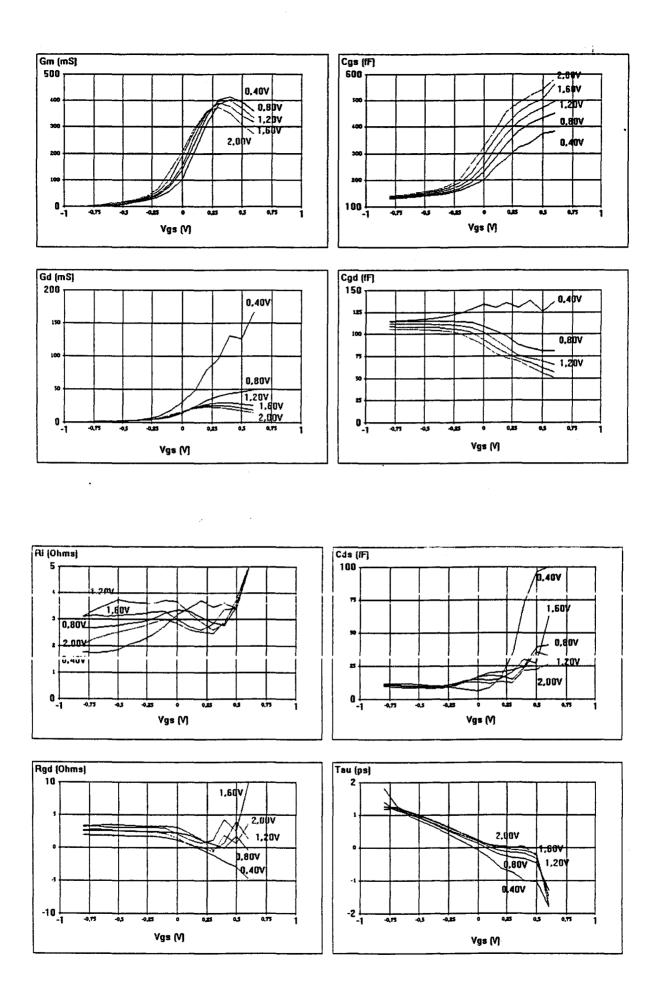

| III-2.4. Etude des éléments intrinsèques en fonction de la polarisation       |      |

| III-2.5. Conclusion                                                           |      |

| III-3. MODELISATION PAR FORMULES ANALYTIQUES                                  | 87   |

| III-3.1. Source de courant de drain Ids                                       |      |

| III-3.2. La source de courant Igs                                             | 90 · |

| III-3.3. La source de courant Igd                                             |      |

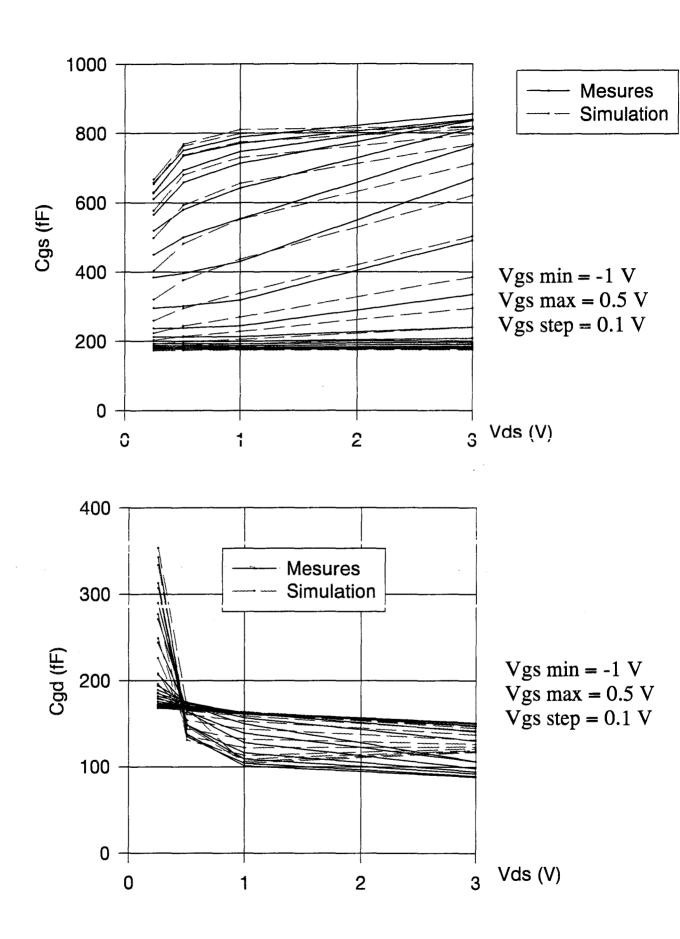

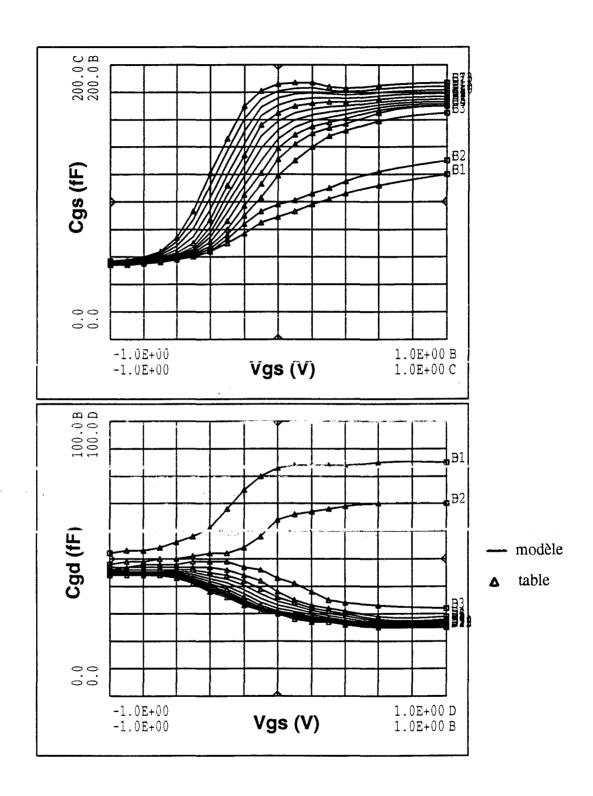

| III-3.4. Les capacités Cgs et Cgd                                             |      |

| III-3.5. Conclusion                                                           |      |

| III-4. MODELISATION PAR TABLES DE MESURES                                     | 93   |

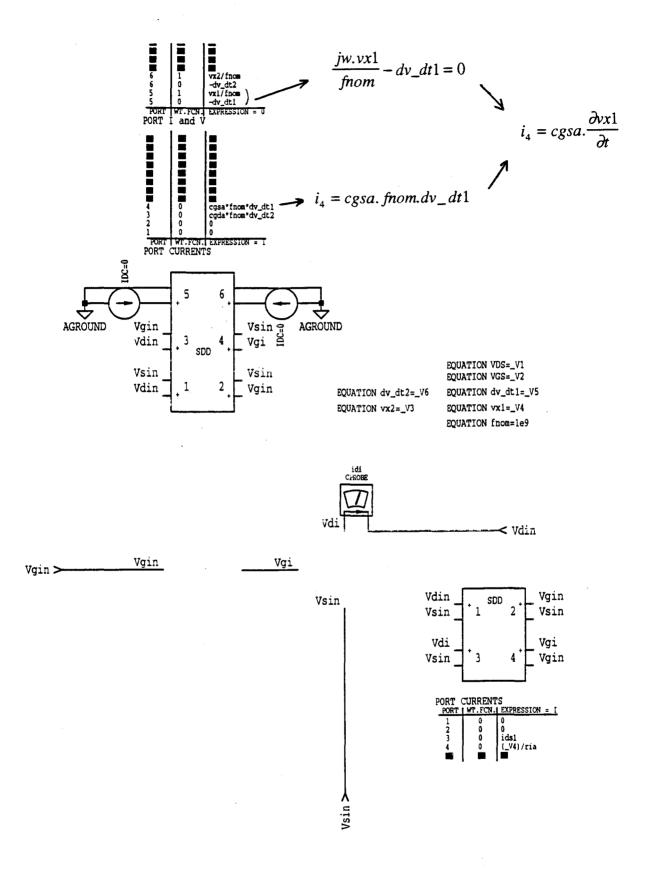

| III-4.1. Implantation du modèle tabulaire                                     |      |

| III-4.2. Simulation non-linéaire à l'aide du modèle tabulaire                 | 95   |

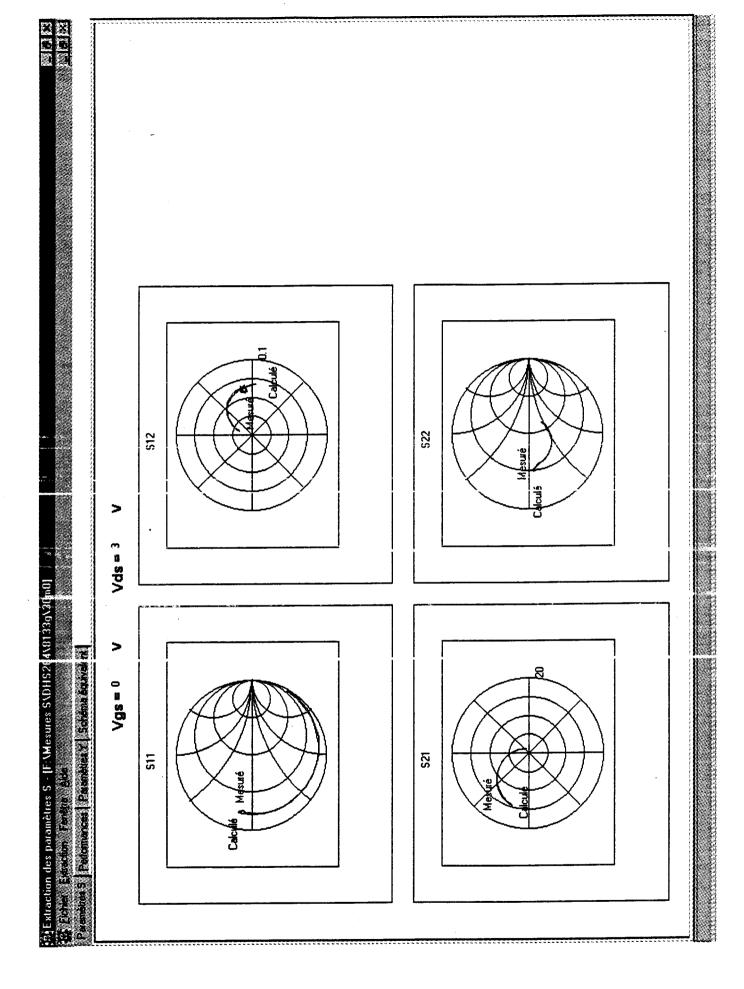

| III-4.3. Validation du modèle                                                 | 96   |

| III-4.3.a. Simulation à base de TA33420                                       | 97   |

| III-4.3.b. Comparaison mesures / simulations du DHS10264                      | 98   |

| III-4.4. Conclusion                                                           | 98   |

| III-5. CONCLUSION                                                             | 99   |

|                                                                               |      |

|                                                                               |      |

| IV- REALISATION D'AMPLIFICATEURS                                              |      |

| IV-1. INTRODUCTION                                                            |      |

| IV-2. PRINCIPE DE REALISATION DES CIRCUITS HYBRIDES                           |      |

| IV-2.1. Définition du substrat                                                |      |

| IV-2.2. Obtention d'un masque                                                 |      |

| IV-2.3. Lithographie                                                          |      |

| IV-2.4. La cellule de test                                                    |      |

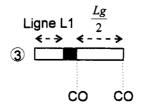

| IV-2.4.a. La transistion K / Microruban                                       |      |

| IV-2.4.b. Les inserts                                                         |      |

| IV-2.4.c. Performances de la cellule                                          |      |

| IV-2.5. Conclusion                                                            |      |

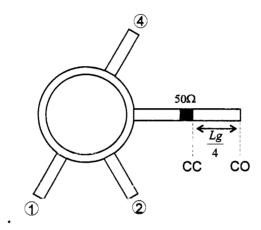

| IV-3. CONCEPTION DES COUPLEURS PASSIFS                                        |      |

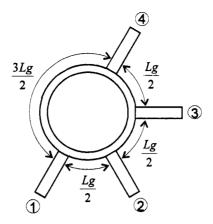

| IV-3.1. Le coupleur en anneau ou « Ratrace »                                  |      |

| IV-3.1.a. Description                                                         |      |

| IV-3.1.b. Réalisation                                                         |      |

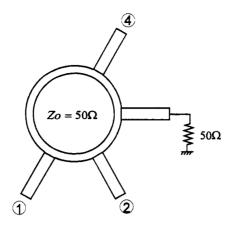

| IV-3.1.b.1. Réalisation de la charge adaptée de 50 $\Omega$                   | 111  |

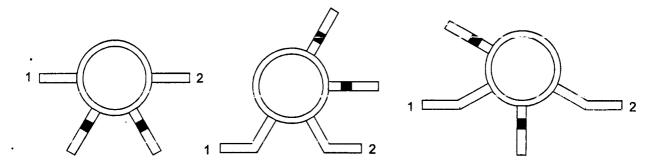

| IV-3.1.b.2. Circuits de caractérisation du ratrace                            | 111  |

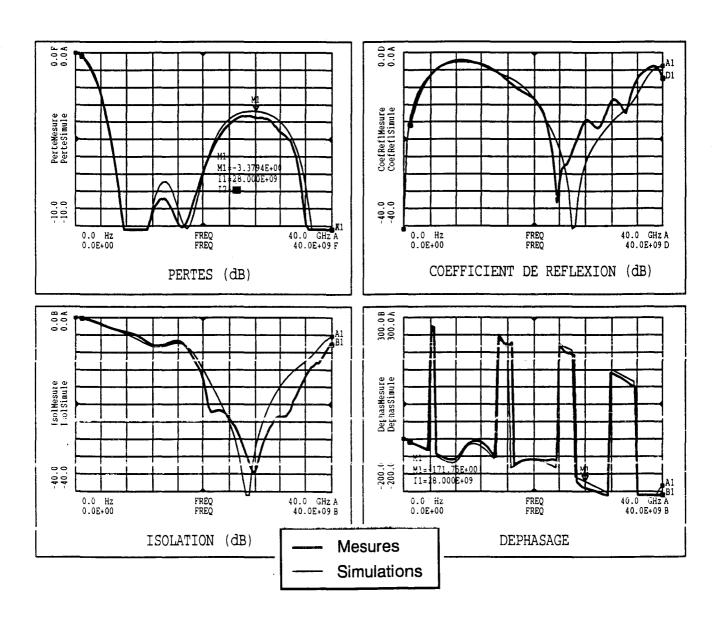

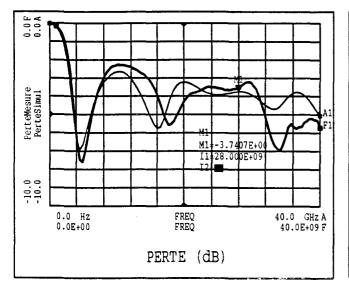

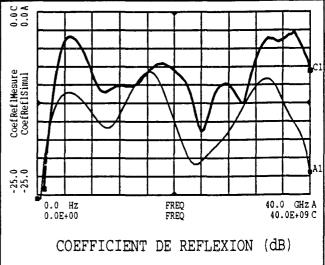

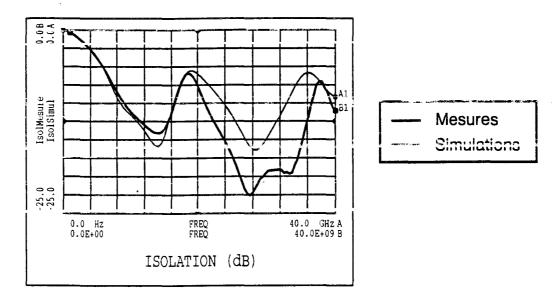

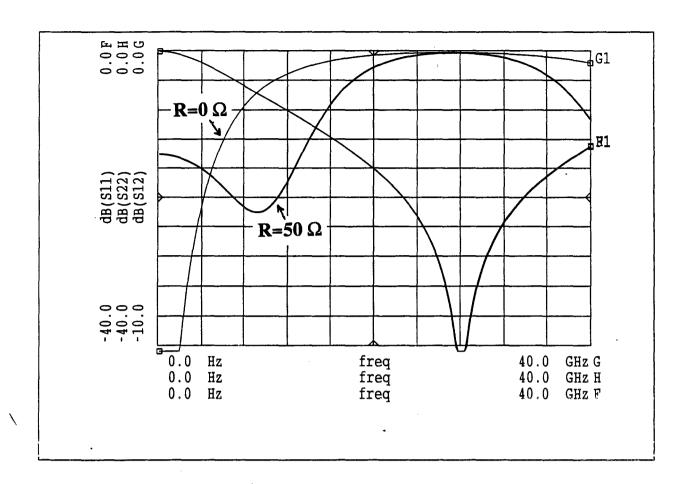

| IV-3.1.c. Comparaison simulation / mesure                    | 112 |

|--------------------------------------------------------------|-----|

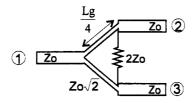

| IV-3.2. Le coupleur Wilkinson                                | 113 |

| IV-3.2.a. Description                                        | 113 |

| IV-3.2.b. Réalisation du circuit Wilkinson                   | 114 |

| IV-3.2.b.1. Réalisation de la résistance                     | 114 |

| IV-3.2.b.2. Caractérisation du coupleur                      | 115 |

| IV-3.2.c. Comparaison mesure / simulation                    | 116 |

| IV-3.3. Choix d'un coupleur pour l'amplification             | 116 |

| IV-3.3.a. Etude du comportement de l'harmonique 2            | 116 |

| IV-3.4. Conclusion                                           | 118 |

| IV-4. CONCEPTION DES AMPLIFICATEURS                          | 119 |

| IV-4.1. Choix de composants                                  | 119 |

| IV-4.1.a. Le Thomson TA33660                                 | 119 |

| IV-4.1.b. Le DHS10264                                        | 120 |

| IV-4.2. Conception d'amplificateurs                          | 121 |

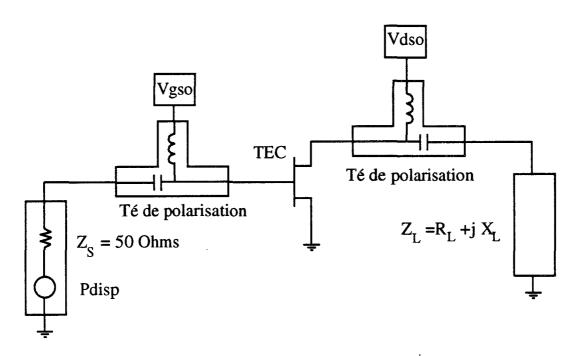

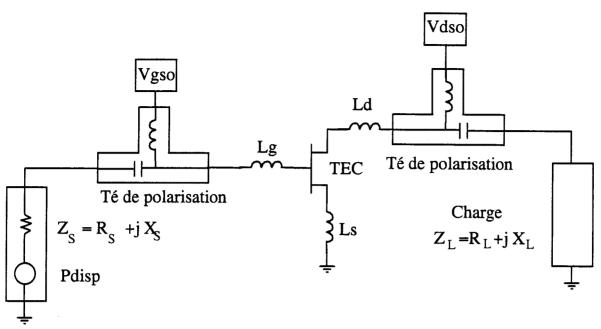

| IV-4.2.a. Les tés de polarisation                            | 122 |

| IV-4.2.b. Les circuits adaptateurs                           |     |

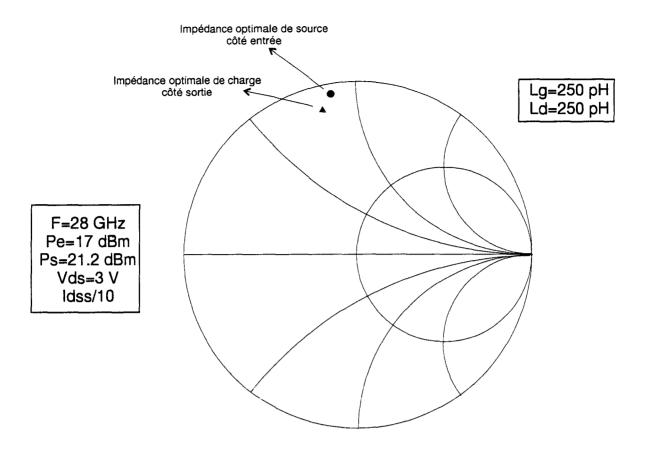

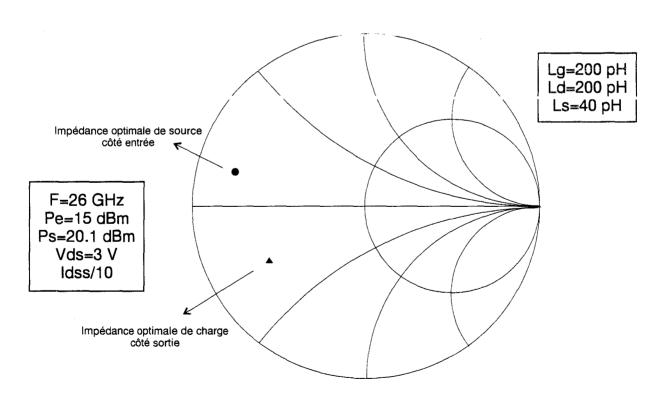

| IV-4.2.b.1. Obtention des impédances optimales non-linéaires | 124 |

| IV-4.2.b.2. Optimisation linéaire des circuits adaptateurs   | 125 |

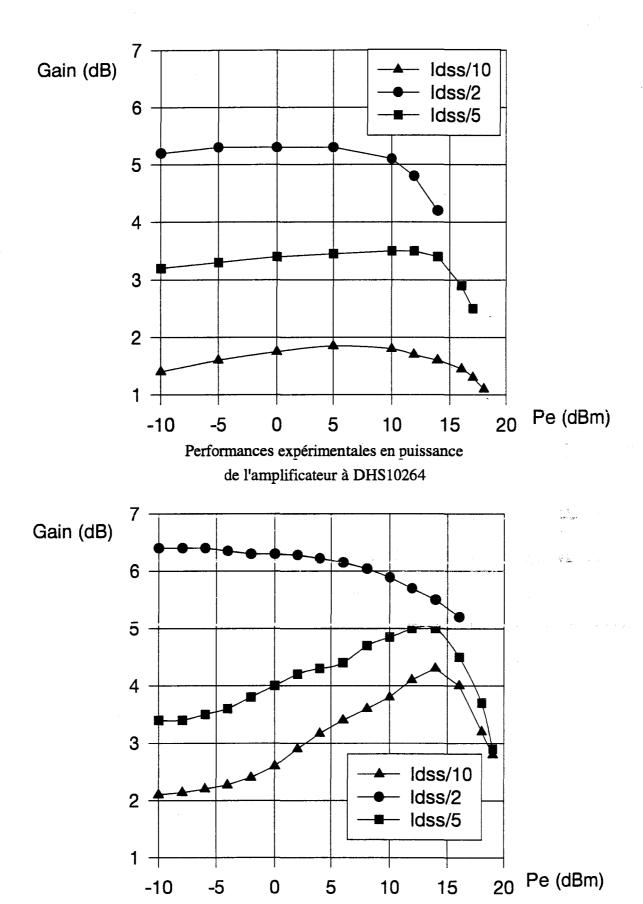

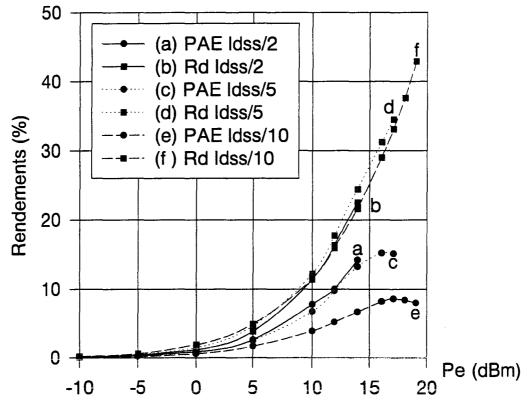

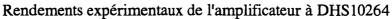

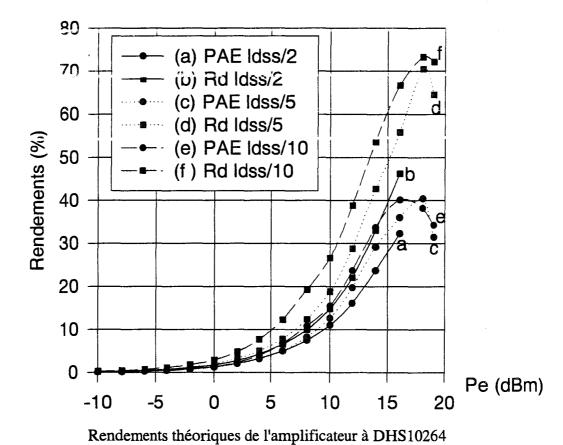

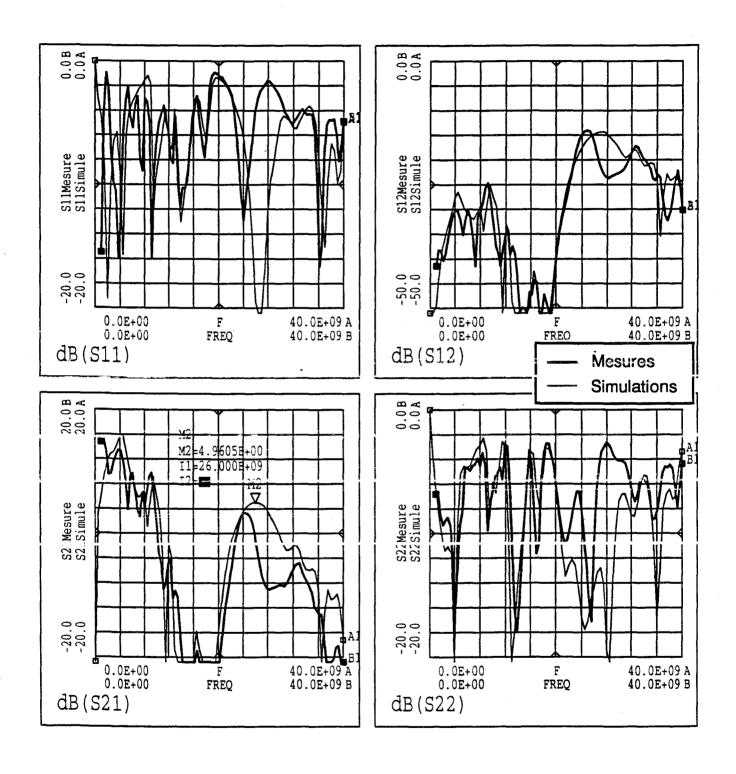

| 1V-4.3. Comparaisons simulations / mesures                   | 126 |

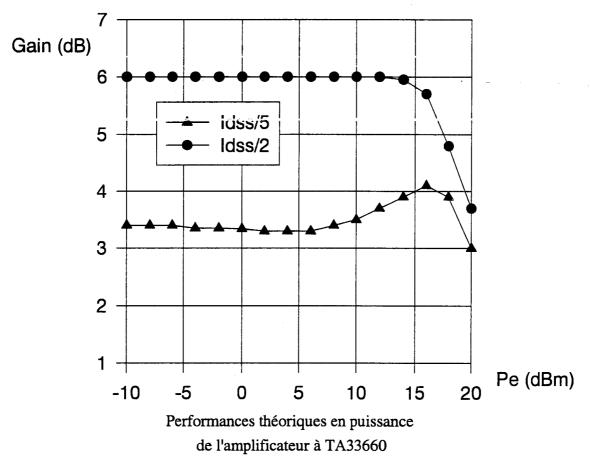

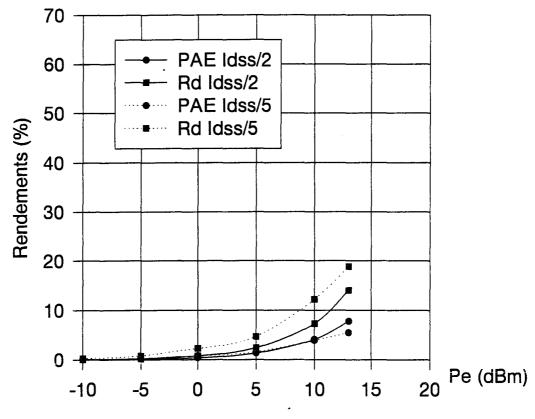

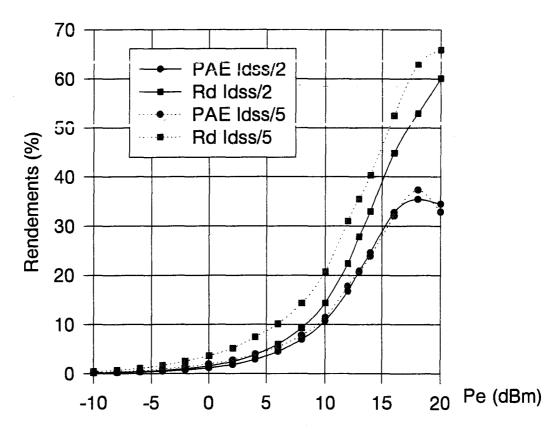

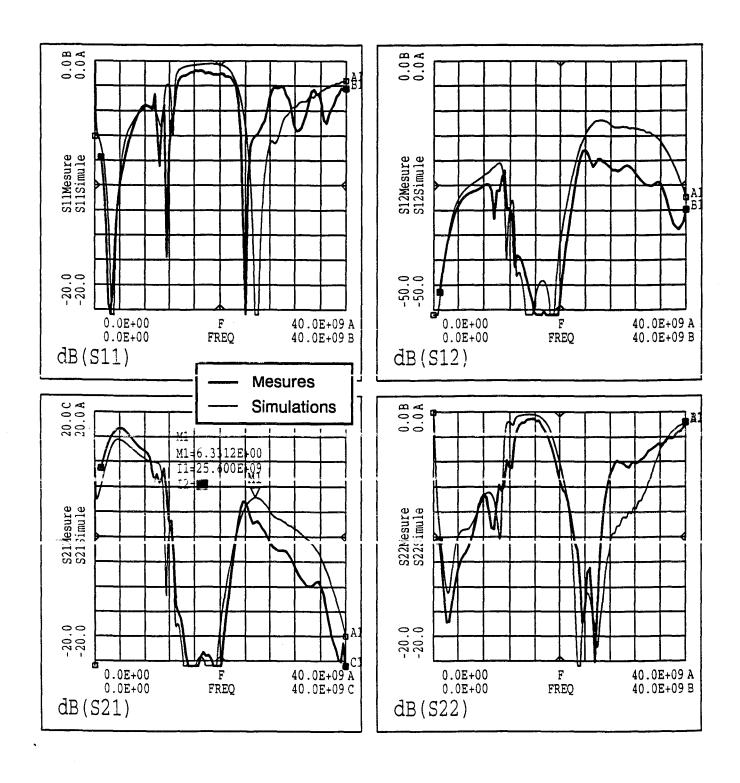

| IV-4.3.a. Amplificateur à TA33660                            | 126 |

| IV-4.3.b. Amplificateur à DHS10264                           | 127 |

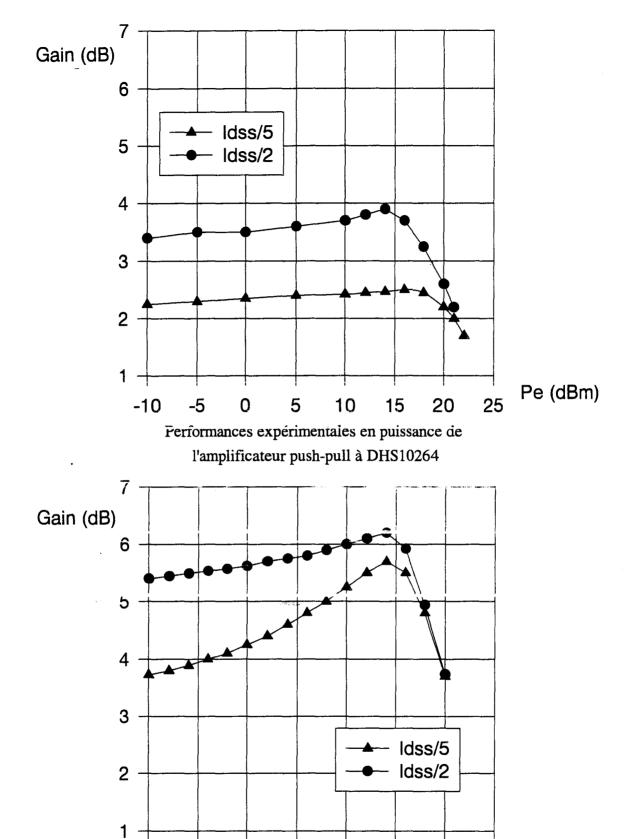

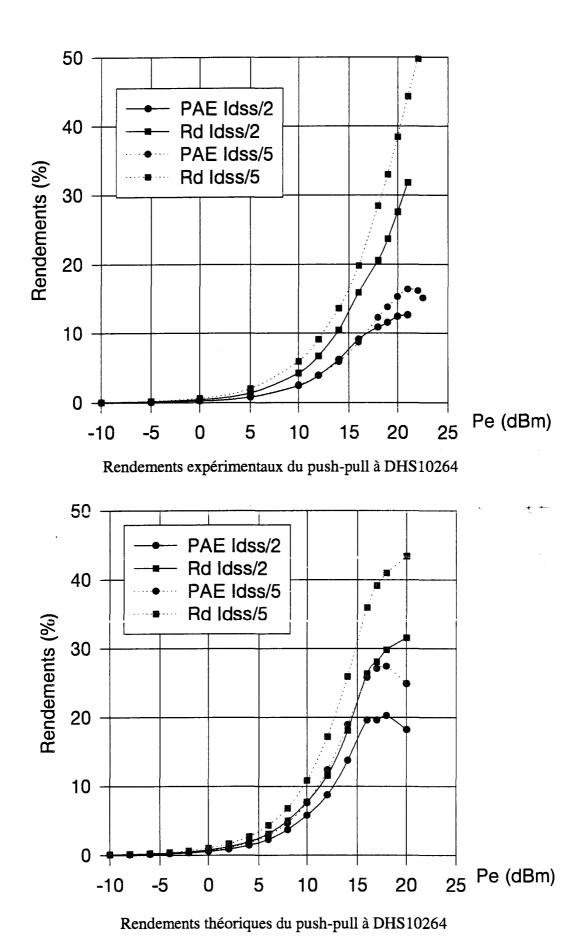

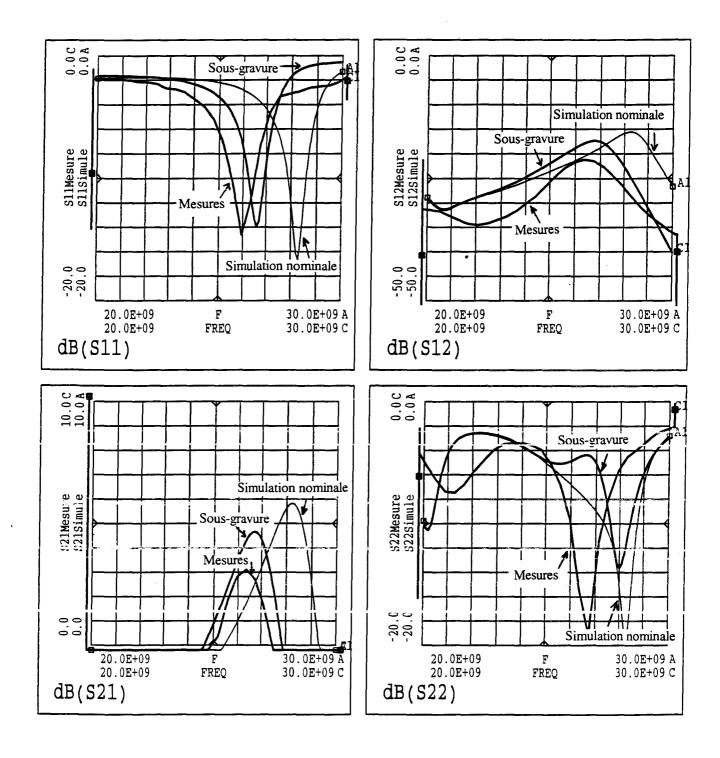

| IV-4.3.c. Amplificateur Push-Pull à DHS10264                 |     |

| IV-4.4. Rétro-simulations des circuits                       |     |

| IV-4.5. conclusion                                           |     |

| IV-5. CONCLUSION                                             | 132 |

| CONCLUSION GENERALE                                          | 136 |

## INTRODUCTION

#### **INTRODUCTION**

La conception des circuits hyperfréquences demande des outils de caractérisation et des techniques de modélisation des transistors de plus en plus pointus au fur et à mesure que la fréquence d'utilisation augmente. En bande Ka, notamment, la modélisation des composants doit prendre en compte beaucoup plus étroitement les effets secondaires ou parasites qu'en bande X ou à plus basse fréquence. Cette complication s'accroît encore pour les régimes de fonctionnement volontairement non-linéaires tels que l'amplification de puissance en classe B et dans le cas d'utilisation d'une technologie hybride. En milieu industriel où les critères de temps et de coût sont primordiaux, ces difficultés peuvent apparaître rapidement contraignantes, aussi il importe de trouver un juste milieu entre rigueur et efficacité. C'est vers cet objectif qu'est consacré l'ensemble du présent travail.

Depuis plusieurs années, le laboratoire travaille dans le domaine de l'amplification classe B. Plusieurs études ont dejà eté réalisées en bande X. Le fonctionnement en classe B permet de diminuer la consommation des circuits et s'impose pour les dispositifs embarqués. Toutefois n'importe quel transistor n'est pas apte à être utilisé en classe B car ce type de fonctionnement est particulièrement exigeant. Le laboratoire s'est penché sur cette question et, dans le cadre d'une étude supportée par la DGA (Convention DRET 91-100), a procédé à la mise en œuvre de nouvelles structures de transistors à effet de champ, en particulier des structures à double puits quantiques. C'est dans ce contexte que s'est placée notre contribution personnelle avec pour tache particulière de mettre au point une méthodologie de caractérisation permettant d'élaborer rapidement et précisément les modèles non-linéaires de ces transistors avec, pour objectif final, la réalisation de circuits démonstrateurs. Ce travail nous a amené à développer des outils spécifiques d'extraction des éléments des schémas équivalents des

transistors et des procédures de modélisation et de simulation. L'ensemble est décrit dans ce mémoire. Celui-ci s'articule suivant quatre parties.

Dans le premier chapitre, nous rappelons les différences entre l'amplification linéaire et l'amplification non-linéaire. Les principes étant fixés, nous avons ensuite présenté un bref historique sur les réalisations récentes d'amplificateurs de puissance hybrides en bande Ka. Dans un troisième temps, nous introduisons les schémas équivalents utilisés dans l'étude. Pour finir, nous présentons les différents bancs de mesures disponibles au laboratoire permettant de caractériser les transistors pour le fonctionnement grand signal ou de valider leurs modèles non-linéaires.

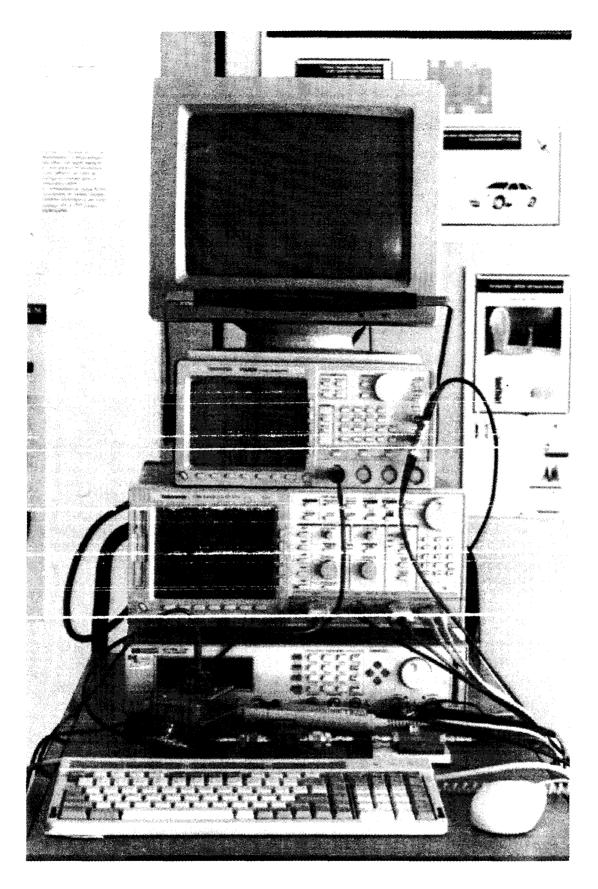

Dans le second chapitre, nous détaillons la mise en œuvre du banc de caractérisation en impulsions qui a constitué une partie importante de notre travail Celui-ci a été réalisé en deux temps. La première version a permis d'effectuer le relevé des caractéristiques du courant de drain tandis que la seconde a ajouté la possibilité d'obtenir les caractéristiques du courant de gritie. La fiabilité du banc a été démontrée par de nombreuses mesures et une étude des effets thermiques et de piégeage des composants a été également abordée.

Le troisième chapitre traite de la modélisation non-linéaire. Nous avons développé un logiciel d'analyse et d'aide à la modélisation qui permet notamment d'extraire les valeurs des capacités du transistor en fonction des tensions Vgs et Vds appliquées. Ainsi grâce aux tables de mesures générées par ce logiciel et à celles obtenues par le banc de caractérisation impulsionnelle ci-dessus, nous avons développé nos modèles non-linéaires. Nous décrivons son implantation dans le logiciel de conception MDS de Hewlett Packard. Enfin, nous le validons en

comparant les résultats de simulations aux mesures obtenues avec le banc à charge active en bande Ka du laboratoire.

Dans le dernier chapitre, nous passons à la réalisation des circuits démonstrateurs d'amplification de puissance classe B en bande Ka. Une étude comparative des configurations parallèle et push-pull est effectuée pour cerner leurs avantages et leurs inconvénients dans la réalisation de nos circuits. Ensuite, nous décrivons la méthodologie de conception dans le cas de la technologie hybride que nous avons utilisée. Cette technique est ensuite appliquée à un composant du laboratoire industriel Thomson et à un autre réalisé dans la centrale de technologie de l'IEMN. Après l'exposé des résultats expérimentaux obtenus, nous terminons par une analyse de ceux-ci à la lumière des indications fournies par nos simulations.

## **CHAPITRE I**

#### I- AMPLIFICATION DE PUISSANCE

#### I-1. INTRODUCTION

Dans cette partie, nous allons présenter les principales notions relatives à l'amplification de puissance linéaire et non-linéaire, les schémas équivalents usuels utilisés pour simuler le comportement des composants et les outils qui sont utilisés pour définir et valider les schémas équivalents. Nous effectuerons également un bref historique de récentes réalisations dans le domaine des amplificateurs de puissance en bande Ka.

# I-2. PRINCIPE, CLASSES DE FONCTIONNEMENT, ASSOCIATIONS D'AMPLIFICATEURS

En amplification de puissance, les grandes excursions de tension et de courant mises en œuvre font apparaître de nombreux effets non - linéaires dans les composants actifs utilisés. Ces effets, qui peuvent être très violents, rendent très compliquée l'estimation analytique précise des performances des étages amplificateurs de puissance. Seul un logiciel de simulation performant permet de prendre en compte la plupart des non - linéarités. Cependant une première approche analytique des performances amplificatrices est possible en considérant un régime de fonctionnement linéaire [1].

#### I-2.1. Amplification linéaire

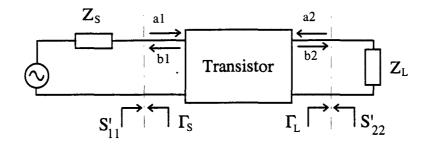

Sur la figure I-1 suivante la charge du transistor et l'impédance de la source sont respectivement  $Z_L$  et  $Z_S$ .

Figure I-1: Schéma synoptique d'un étage amplificateur

A ce stade, plusieurs expressions de gains peuvent être définis.

#### I-2.1.a.Gain de transducteur

Une représentation significative du gain en puissance peut être définie comme étant le rapport entre la puissance absorbée par la charge et la puissance disponible de la source. Classiquement, ce gain de transducteur est donné par l'expression :

$$G_{T} = \frac{P_{S}}{P_{AVS}} = \frac{\left|S_{21}\right|^{2} \left(1 - \left|\Gamma_{S}\right|^{2}\right) \left(1 - \left|\Gamma_{L}\right|^{2}\right)}{\left|1 - S_{11}^{'}\Gamma_{S}\right|^{2} \left|1 - S_{22}\Gamma_{L}\right|^{2}} = \frac{\left|S_{21}\right|^{2} \left(1 - \left|\Gamma_{S}\right|^{2}\right) \left(1 - \left|\Gamma_{L}\right|^{2}\right)}{\left|1 - S_{11}\Gamma_{S}\right|^{2} \left|1 - S_{22}^{'}\Gamma_{L}\right|^{2}}$$

$\Gamma_S$  et  $\Gamma_L$  sont les coefficients de réflexion des impédances de source  $Z_S$  et de charge  $Z_L$

S'11 est le coefficient de réflexion de l'entrée du transistor chargé par Z<sub>L</sub>:

$$S_{11}' = S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L}$$

S'22 est le coefficient de réflexion de la sortie du transistor dont l'entrée est fermée sur Z<sub>S</sub>:

$$S_{22}' = S_{22} + \frac{S_{12}S_{21}\Gamma_{S}}{1 - S_{11}\Gamma_{S}}$$

Classiquement les adaptations de l'entrée et de la sortie du composant sont obtenues lorsque les conditions  $S'_{11}=\Gamma_S^*$  et  $S'_{22}=\Gamma_L^*$  sont réalisées. Les valeurs de  $\Gamma_S$  opt et  $\Gamma_L$  opt, déduites des expressions de  $S'_{11}$  et  $S'_{22}$  avec les conditions précédentes, représentent respectivement celles des

coefficients de réflexion de la source et de la charge qui adaptent les composants en entrée et en sortie. Les expressions de  $\Gamma_S$  opt et  $\Gamma_L$  opt sont les suivantes :

$$\Gamma_{S}opt = \frac{1}{2C_{1}} \left( B_{1} \pm 2 | S_{12} S_{21} | \sqrt{K^{2} - 1} \right) + \sin B_{1} < 0$$

$$- \sin B_{1} > 0$$

$$\Gamma_L opt = \frac{1}{2C_2} \left( B_2 \pm |S_{12}S_{21}| \sqrt{K^2 - 1} \right) + \text{si } B_2 < 0$$

$- \text{si } B_2 > 0$

$$B_{1} = 1 + |S_{11}|^{2} - |S_{22}|^{2} - |\Delta|^{2}$$

$$C_{1} = S_{11} - \Delta S_{11}^{*}$$

$$C_{2} = S_{22} - \Delta S_{11}^{*}$$

$$C_{3} = S_{11} - \Delta S_{22}^{*}$$

$$C_{4} = S_{11} - \Delta S_{11}^{*}$$

$$C_{5} = S_{22} - \Delta S_{11}^{*}$$

$$K = \frac{1 - \left| S_{11} \right|^2 - \left| S_{22} \right|^2 + |\Delta|^2}{2 \left| S_{12} S_{21} \right|}$$

Le coefficient K caractérise la stabilité du transistor. Si K est supérieur à l'unité le composant est inconditionnellement stable et un gain en puissance peut être défini :

$$MAG = \frac{\left|S_{21}\right|}{\left|S_{12}\right|} \left(K \pm \sqrt{K^2 - 1}\right) + \sin B_1 < 0$$

$$- \sin B_1 > 0$$

Ce gain est appelé gain en puissance maximum disponible car il est obtenu dans des conditions d'adaptations idéales du composant. Le MAG, qui représente les performances maximales de gain en puissance des composants testés, est une des caractéristiques essentielles de l'amplification en régime de fonctionnement linéaire.

L'évolution du MAG, en fonction de la fréquence, permet de définir la fréquence particulière  $F_{MAG}$  pour laquelle la valeur du MAG est unitaire.

De manière plus générale, un fonctionnement en amplification de puissance est possible si un gain en puissance peut être défini : c'est à dire si le composant est stable. Dans ce qui suit, nous présentons de façon très résumée les conditions de stabilité.

#### Etude des risques d'instabilité

Dans le formalisme des paramètres S, un système devient instable lorsque  $|S'_{11}| > 1$  et  $|S'_{22}| > 1$ .

La limite de la stabilité est obtenue pour des valeurs de lS'<sub>11</sub>l et lS'<sub>22</sub>l égales à l'unité. Cette limite de stabilité est représentée sur un abaque de Smith par des cercles.

Côté entrée du quadripôle il est possible d'écrire :

$$\left| S_{11}^{'} \right| = \left| S_{11} + \frac{S_{12} S_{21} \Gamma_L}{1 - S_{22} \Gamma_L} \right| = 1$$

Cette relation représente un cercle de rayon R<sub>L</sub> et de centre C<sub>L</sub> tels que :

$$R_{L} = \frac{S_{12}S_{21}}{\left|S_{22}\right|^{2} - |\Delta|^{2}} \qquad C_{L} = \frac{S_{22}^{*} - \Delta^{*}S_{11}}{\left|S_{22}\right|^{2} - |\Delta|^{2}}$$

L'équation du cercle montre clairement que la stabilité de l'entrée est étroitement liée à la valeur de la charge. Une méthode pour déterminer si la zone d'instabilité est à l'intérieur ou à l'extérieur du cercle est d'étudier le cas particulier où  $\Gamma_L = 0$ . Le centre de l'abaque, représentatif de  $\Gamma_L = 0$ , est situé dans la zone de stabilité si  $|S_{11}| = |S'_{11}| < 1$ .

Côté sortie un raisonnement analogue peut être effectué sur la relation :

$$\left| S_{22}^{'} \right| = \left| S_{22} + \frac{S_{12} S_{21} \Gamma_{S}}{1 - S_{11} \Gamma_{S}} \right| = 1$$

Les caractéristiques du cercle représenté par cette équation sont :

$$R_{S} = \frac{S_{12}S_{21}}{\left|S_{11}\right|^{2} - |\Delta|^{2}}$$

$$C_{L} = \frac{S_{11}^{*} - \Delta^{*}S_{22}}{\left|S_{11}\right|^{2} - |\Delta|^{2}}$$

Un raisonnement analogue à celui effectué pour l'entrée, est utilisé pour déterminer la zone de stabilité en sortie (étude du cas où  $\Gamma_S = 0$ ).

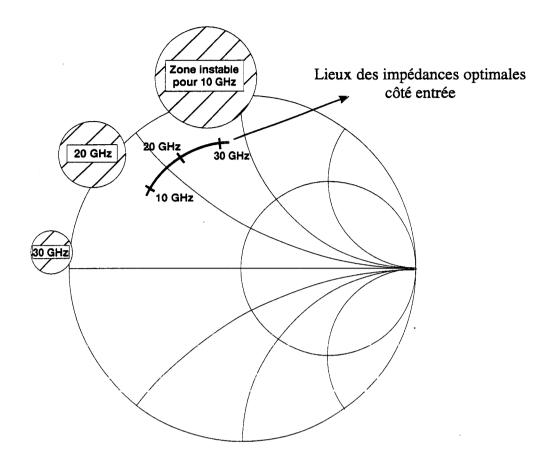

Figure I-2: Exemples typiques des zones d'instabilité dans le plan d'entrée de 10 à 30 GHz

Une instabilité inconditionnelle de l'étage amplificateur sera obtenue si deux conditions sont réalisées simultanément : les cercles d'instabilité doivent être localisés à l'extérieur de l'abaque et la zone d'instabilité proprement dite doit être la surface de ce même cercle. En pratique, on essaie de réaliser un amplificateur inconditionnellement stable quelle que soit la fréquence. Dans le cas contraire, une étude des impédances présentées au transistor s'avère indispensable ; cette étude peut être réalisée assez rapidement avec un logiciel de simulation. Un exemple simple d'étude est représenté sur la figure I-2 à titre indicatif.

Une autre méthode, utilisant le NDF (Normalized Determinant Function), peut également être utilisée pour l'étude de la stabilité des dispositifs micro-ondes; elle est basée sur la théorie des systèmes bouclés de Bode et le critère de Nyquist. Dans le cadre de notre travail, nous avons choisi l'analyse des variations du coefficient K pour étudier la stabilité des circuits.

#### I-2.1.b.Gain en puissance

Le gain en puissance Gp est le rapport entre la puissance absorbée par la charge et la puissance absorbée par l'entrée du transistor. Sa formulation est la suivante :

$$Gp = \frac{\left|S_{21}\right|^{2} \left(1 - \left|\Gamma_{L}\right|^{2}\right)}{\left|1 - S_{22}\Gamma_{L}\right|^{2} \left(1 - \left|S_{11}\right|^{2}\right)}$$

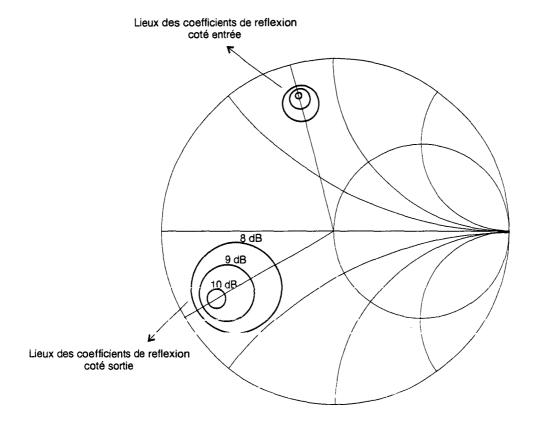

Ce gain n'est fonction que des conditions de charge en sortie et il est utilisé pour les mesures de puissance des systèmes micro ondes. On démontre également que les lieux des coefficients de réflexion  $\Gamma_L$ , obtenus pour un gain en puissances délivrées constant, sont des cercles de centres C et de rayons R tels que :

$$C = \frac{g_{P}(S_{22}^{*} - S_{11}\Delta^{*})}{1 + g_{P}(|S_{22}|^{2} - |\Delta|^{2})} \qquad R = \sqrt{\frac{1 - 2Kg_{P}|S_{12}S_{21}| + g_{P}^{2}|S_{12}S_{21}|^{2}}{1 + g_{P}(|S_{22}|^{2} - |\Delta|^{2})}} \qquad g_{P} = \frac{Gp}{|S_{21}|^{2}}$$

Figure I-3: Exemples de cercles à gains constants en entrée et en sortie obtenus dans le cas du transistor TA33420

La valeur de Gp est égale à celle du MAG dans le cas où le rayon du cercle devient nul. Une même démarche peut être faite pour la sortie.

#### I-2.1.c. Gain en puissance disponible

Le gain en puissance disponible Gd est le rapport entre la puissance disponible de sortie et la puissance disponible du générateur. Son expression est la suivante :

$$Gd = \frac{\left|S_{21}\right|^{2} \left(1 - \left|\Gamma_{S}\right|^{2}\right)}{\left|1 - S_{11}\Gamma_{S}\right|^{2} \left(1 - \left|S_{22}\right|^{2}\right)}$$

Ce gain n'est fonction que des conditions d'impédance de source.

Il est utilisé essentiellement lors des mesures de facteur de bruit. Les lieux des coefficients de réflexion  $\Gamma_S$ , où le gain en puissance disponible est constant, forment des cercles de centres C et de rayons R tels que :

$$C = \frac{g_{P}(S_{11}^{*} - S_{22}\Delta^{*})}{1 + g_{P}(|S_{11}|^{2} - |\Delta|^{2})} \qquad R = \sqrt{\frac{1 - 2Kg_{d}|S_{12}S_{21}| + g_{d}^{2}|S_{12}S_{21}|^{2}}{1 + g_{d}(|S_{11}|^{2} - |\Delta|^{2})}} \qquad g_{d} = \frac{Gd}{|S_{21}|^{2}}$$

Comme précédemment, le MAG est obtenu lorsque la valeur du rayon tend vers 0.

Une illustration des cercles à gains constants est donnée figure I-3.

Deux autres définitions du gain peuvent être rencontrées ; l'une est obtenue avec une réaction entrée-sortie, l'autre lorsque la sortie est court-circuitée.

#### I-2.1.d.Gain unilatéral

Le MAG n'est pas le gain le plus élevé qui puisse être obtenu ; une autre notion de gain en puissance peut être rencontrée lorsqu'une contre réaction entrée-sortie purement réactive est utilisée

pour annuler les effets du paramètre S12 du transistor. Ce gain appelé unilatéral en puissance, présente la formulation suivante :

$$U = \frac{1}{2} \frac{\left| \frac{S_{21}}{S_{12}} - 1 \right|^2}{K \left| \frac{S_{21}}{S_{12}} \right| - \text{Re} \left( \frac{S_{21}}{S_{12}} \right)}$$

Cette valeur de gain idéale est impossible à atteindre pratiquement avec les transistors à effet de champ actuels. Néanmoins sa fréquence de transition Fu définie pour U = 1 est souvent utilisée; on l'appelle fréquence maximum d'oscillation. Fu correspond, en première approximation, à la fréquence de coupure du gain maximum en puissance disponible.

#### I-2.1.e. Gain en courant de court-circuit

Le gain en courant de court-circuit est obtenu par conversion des paramètres Sij en paramètres Hij. Son expression est donnée par la relation :

$$\left|H_{21}\right|^2 = \left|\frac{-2S_{21}}{\left(1 - S_{11}\right)\left(1 - S_{22}\right) + S_{12}S_{21}}\right|^2$$

Ce gain est extrait de la caractérisation en petit signal du composant. Une autre formulation de ce gain, exprimée en fonction des éléments du schéma équivalent du TEC, est souvent utilisée; elle sera présentée ultérieurement.

La fréquence de transition (où  $|H_{21}| = 1$ ) est celle où le composant actif perd ses possibilités amplificatrices en courant. Toutes ces notions sont prises en compte dans un programme d'analyse et de dépouillement de mesures décrit dans le chapitre III.

Les principales définitions relatives à l'amplification linéaire étant rappelées, nous abordons celles qui concernent les amplificateurs de puissance.

Figure I-4: Analyse des signaux disponibles sur le transistor en classe A

#### I-2.2. Amplificateur non-linéaire

Dès que la valeur du gain évolue avec le niveau de puissance, les définitions précédentes ne sont plus valables et il devient difficile de cerner théoriquement les performances des transistors. Cependant, quelques considérations sur les puissances et les rendements peuvent être effectuées.

Le bilan des puissances d'un amplificateur se traduit par la formule suivante :

$$Pe + Pdc = Ps + Pd$$

dans laquelle:

- Pe est la puissance du signal à amplifier qui est absorbée par l'entrée du dispositif et Pdc la puissance fournie l'alimentation continue.

- Ps est la puissance absorbée par la charge et Pd la puissance dissipée par le transistor (en général, sous forme de chaleur).

Les rendements de drain \( \eta \) et en puissance ajoutée \( \eta\_{PAE} \) sont définis par les relations :

$$\eta d = \frac{P_S}{Pdc}$$

$$\eta_{PAE} = \frac{P_S - P_E}{Pdc} = \eta d \left( 1 - \frac{1}{Gp} \right) = 1 - \frac{Pd}{Pdc}$$

Le rendement en puissance ajoutée, très utilisé, prend en compte le bilan des puissances.

Les rendements et puissances étant définis, les coordonnées du point de polarisation du dispositif sont souvent prises en compte pour définir les classes de fonctionnement :

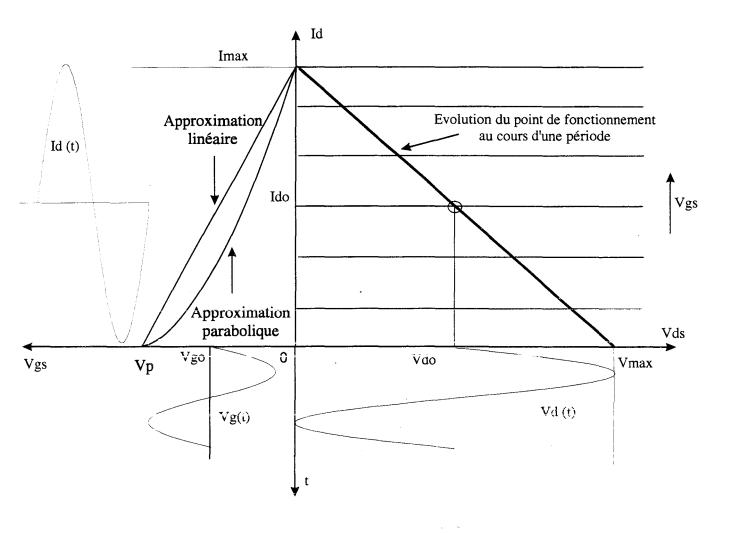

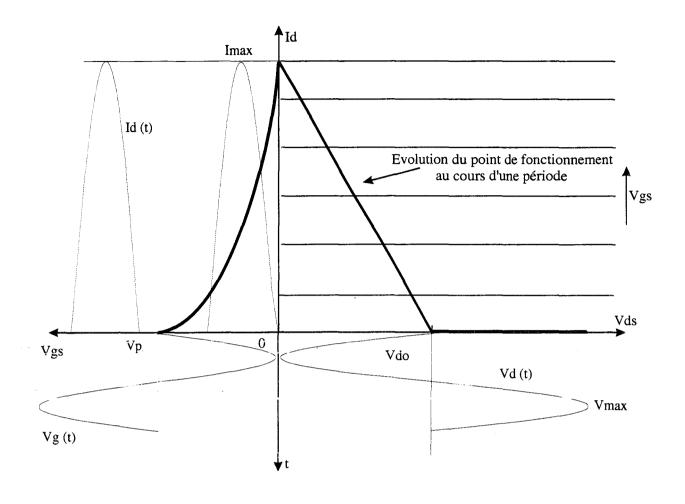

• La classe A: le transistor est polarisé à la moitié de son courant maximum. Le rendement drain maximum est de 50 % pour une approximation linéaire de Ids et de 66,5 % pour une approximation parabolique. Un descriptif des signaux disponibles au niveau du transistor est donné figure I-4.

#### • La classe B:

De manière générale, le fonctionnement classe B idéal est défini par un angle d'ouverture de 180° du composant actif; par ailleurs, la charge présentée à ce composant reste la même quelle que soit la fréquence. Dans notre cas, si l'impédance de charge du composant à la fréquence fondamentale (28 GHz) peut être assez correctement contrôlée, il n'en est pas de même aux fréquences harmoniques. En effet,

Figure I-5: Analyse des signaux disponibles sur le transistor en classe B

pour ces dernières les propriétés de propagation dans le circuit microstrip (utilisé dans notre réalisation hybride) sont beaucoup trop complexes pour être soit prises en compte avec un modèle simple au niveau théorique, soit définies expérimentalement avec des moyens de mesures classiques.

Néanmoins, pour ce fonctionnement très particulier des composants, nous utiliserons la terminologie "classe B" tout à long de ce mémoire.

Dans cette classe de fonctionnement, le transistor est polarisé au pincement. Le rendement drain maximum est voisin de 78,5 % pour l'approximation linéaire de la caractéristique Id=f(Vgs) et de 85 % pour l'approximation parabolique. Si la tension d'avalanche grille - drain n'affecte pas les excursions de tension, des puissances de sortie équivalentes à celles de la classe A peuvent être obtenues. En revanche, la tension d'entrée ayant une amplitude deux fois plus importante, il faut de 3 à 6 dB supplémentaires de puissance d'entrée pour obtenir le même niveau de sortie qu'en classe A. Les atouts majeurs de la classe B sont la consommation pratiquement nulle au repos et les performances de rendement. Une représentation des signaux disponibles au niveau du transistor est donnée figure I-5.

- La classe AB est un état intermédiaire entre les deux classes précédentes.

- La classe C, rarement utilisée en bande Ka, correspond au cas où le transistor est polarisé sous le pincement. Le rendement peut théoriquement atteindre 100 %.

- La classe F: le transistor est polarisé au pincement et on présente au composant des impédances particulières aux harmoniques [2].

Les fonctionnements non-linéaires étant très difficiles à étudier de manière analytique, seul un simulateur performant nous permettra d'en dégager tous les aspects au chapitre III.

La dernière partie de ce paragraphe décrit les différents types d'associations parallèles d'étages amplificateurs : en phase, en opposition de phase et en quadrature.

#### I-2.3. Associations d'amplificateurs

L'augmentation de la puissance de sortie peut être obtenue de deux manières :

- En utilisant des transistors à plus grand développement de grille.

- En associant des étages amplificateurs en parallèle.

C'est sur ce deuxième point que trois associations typiques peuvent être définies.

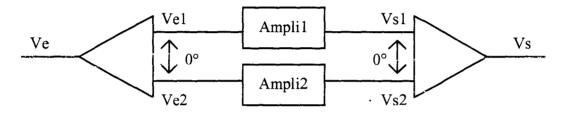

#### I-2.3.a. Association sans déphasage entre les signaux

C'est la solution la plus simple. Pratiquement cette association, où aucun filtrage n'affecte les harmoniques, s'effectue avec des coupleurs de type Wilkinson [3]. Son étude est décrite au chapitre IV et son synoptique est présenté sur la figure I-6.

Figure I-6: Association d'amplificateurs sans déphasage

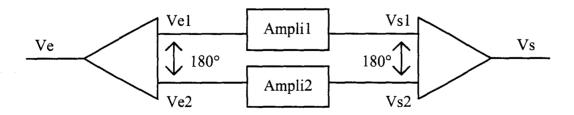

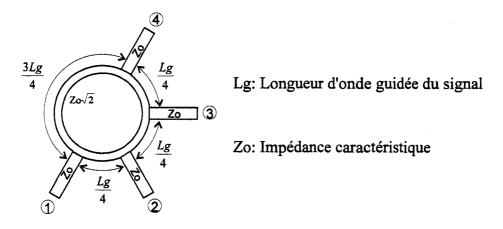

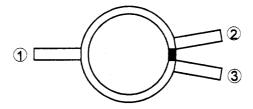

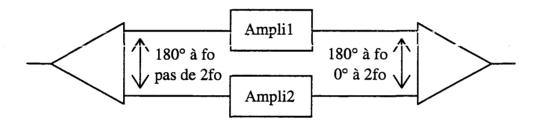

# I-2.3.b.Association avec déphasage de 180° entre les signaux ou \*\* Amplificateur de type « Push-Pull »

Des étages amplificateurs, fonctionnant en classe B et si possible appairés, sont utilisés [4, 5]. Chaque étage amplifie une demi - alternance du signal appliqué à l'entrée. Son synoptique est présenté sur la figure I-7.

Figure I-7: Association d'amplificateurs type Push-Pull

Pour les étages dont le fonctionnement peut être décrit avec des éléments localisés, les expressions des courants de conduction s'écrivent :

$$Idsa(t) = Ids_0 + Ids_1 \cdot \cos(\boldsymbol{\omega}_0 t) + Ids_2 \cdot \cos(2\boldsymbol{\omega}_0 t) + \sum_n Ids_n \cdot \cos(n\boldsymbol{\omega}_0 t)$$

$$Idsb(t) = Ids_0 + Ids_1 \cdot \cos(\boldsymbol{\omega}_0 t + \boldsymbol{\pi}) + Ids_2 \cdot \cos(2\boldsymbol{\omega}_0 t) + \sum_n Ids_n \cdot \cos(n\boldsymbol{\omega}_0 t + n\boldsymbol{\pi})$$

Les courants sont recombinés avec un déphasage de 180° qui élimine naturellement les harmoniques paires ; le courant résultant de sortie est :

$$Ids = Idsa - Idsb = 2Ids_1 \cdot \cos(\omega_0 t) + 2Ids_3 \cdot \cos(3\omega_0 t) + \dots$$

Le chapitre IV aborde la réalisation d'un tel amplificateur à base de coupleurs 3dB / 180° de type RatRace. Dans ce cas particulier les considérations théoriques précédemment effectuées sur les courants de conduction ne s'appliquent pas aussi simplement.

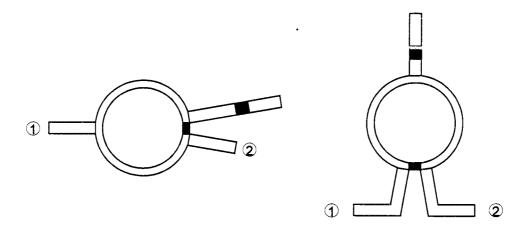

## I-2.3.c.Association avec déphasage de 90° entre les signaux ou Amplificateur HRA (Harmonic Reaction Amplifier)

Son synoptique est représenté figure I-8 [6].

Figure I-8: Association d'amplificateurs type HRA

Les étages amplificateurs sont toujours polarisés au voisinage du pincement. Un filtre additionnel est inséré en sortie pour éliminer la composante à 2fo.

Pour les étages dont le fonctionnement peut être décrit avec des éléments localisés, les expressions des courants de conduction s'écrivent :

$$\begin{aligned} Idsa(t) &= Ids_0 + Ids_1.\cos(\omega_0 t) + Ids_2.\cos(2\omega_0 t) + \sum_n Ids_n.\cos(n\omega_0 t) \\ Idsb(t) &= Ids_0 + Ids_1.\cos(\omega_0 t + \frac{\pi}{2}) + Ids_2.\cos(2\omega_0 t + \pi) + \sum_n Ids_n.\cos(n\omega_0 t + n\frac{\pi}{2}) \end{aligned}$$

Cette configuration, qui possède un filtrage des harmoniques paires, est rarement utilisée en bande Ka car elle complique notablement les circuits de sortie.

#### I-2.4. Conclusion

Nous avons rappelé dans cette première partie, les principales grandeurs caractéristiques de l'amplification de puissance, les classes de fonctionnement actuellement les plus utilisées et les associations parallèles d'étages les plus courants. Dans ce qui suit, nous présentons une étude bibliographique de quelques amplificateurs de puissance réalisés ces dernières années.

# I-3. HISTORIQUE SUR LA CONCEPTION D'AMPLIFICATEURS DE PUISSANCE EN BANDE KA

Depuis quelques temps, différents modèles d'amplificateurs de puissance en technologies hybride et MMIC ont été décrits dans des revues scientifiques [7..14]. Les étages amplificateurs de puissances, élaborés pour des applications dans la bande de fréquence 20-40 GHz, ont retenu notre attention.

#### I-3.1. Amplificateurs conçus autour de 35 GHz

En 1992, TRW a présenté deux circuits réalisés avec des composants de type HEMT pseudomorphique monopuit à double plans de dopage et de longueur de grille 0.25 μm. Les deux circuits, qui possèdent deux étages, sont adaptés pour obtenir des performances optimales autour de 35 GHz.

Le premier circuit [15] est susceptible de délivrer, avec un gain de 10 dB, une puissance de sortie de 800 mW (29 dBm); son rendement en puissance ajouté est proche de 26 %. Le dernier étage de ce circuit met en œuvre deux éléments actifs qui possèdent un développement de grille de 600 µm (8 doigts de 75 µm de largeur). Des coupleurs de type Wilkinson sont utilisés pour la mise en parallèle.

Les performances du second circuit [16] sont : un niveau de puissance de sortie proche de 30 dBm, un gain de 10 dB et un rendement en puissance ajouté voisin de 25 %. L'étage de sortie met en parallèle quatre transistors à effet de champ possédant 10 doigts d'une largueur de 50 µm. Côté entrée, les diviseurs de puissances utilisés sont des coupleurs Wilkinson classiques ; côté sortie, le couplage des puissances s'effectue avec un type de coupleur analogue dépourvu de résistance d'isolation. L'ajustage des éléments adaptateurs, qui ne semble pas avoir fait l'objet de simulations numériques, utilise une procédure manuelle.

En 1993, c'est encore TRW qui présente une série d'amplificateurs [17] à 35 GHz basé sur des HEMTs pseudomorphiques de 0,15 μm de longueur de grille. Ces circuits à simple étage mettent en œuvre des transistors élémentaires de 200 μm de développement de grille (2 doigts d'une largueur de 100 μm). Une puissance de sortie proche de 1,6 W (32,2 dBm), un rendement en puissance ajouté de 15 % et un gain de 8 dB sont obtenus avec la mise en parallèle de huit transistors (développement de grille total de 1600 μm). Des circuits de préadaptation mettant en parallèle les composants sont présentés ; les composants sont appairés et connectés en parallèle sur un même élément adaptateur

#### I-3.2. Amplificateurs conçus autour de 20 GHz

Le premier a été présenté en 1993 par Texas Instruments [18].

L'amplificateur est constitué de 2 étages. Il utilise des HEMTs traditionnels de longueur de grille 0,25 µm. Douze HEMTs possédant 600 µm de développement de grille sont mis en parallèles

(7200 μm) pour le deuxième étage. La puissance de sortie obtenu est proche de 4 W (36 dBm), le rendement en puissance ajoutée est voisin de 28 % et le gain de 16 dB. Une préadaptation est effectuée sur des circuits en GaAs. Le passage à 50 Ω est réalisé sur un substrat d'alumine. En sortie un combineur large bande de type Tchebichev est utilisé.

Le deuxième circuit a été réalisé par TRW [19]. L'amplificateur simple étage utilise des HEMTs pseudomorphique de longueur de grille de 0,2 µm. Quatre transistors, qui possèdent 16 doigts de 100 µm de largueur, sont mis en parallèle à l'aide de coupleurs Wilkinson arborescents. La puissance de sortie obtenue est voisine de 3,2 W avec un rendement en puissance ajouté de 35 % et un gain de 10 dB. Les circuits de couplage et d'adaptation sont constitués de plusieurs parties réalisées sur différents substrats : GaAs, Alumine et Quartz. Ces circuits semblent être ajustés manuellement.

Le dernier circuit retenu pour cette fréquence a été présenté par Avantek en 1994 [20]. Des HEMTs pseudomorphiques sont associés pour obtenir un développement total de 4860 µm. Deux amplificateurs à simple étage utilisant ces HEMTs sont mis en parallèle grâce à des coupleurs de Lange. La puissance de sortie à 2,5 dB de compression est de 4,7 W, le rendement en puissance ajouté est de 36 % et le gain aueint 7,5 dB.

#### I-3.3. Amplificateurs conçus autour de 28 GHz

Le circuit qui est le plus proche de notre étude a été publié très récemment par TRW [21]. Il aborde notamment la technique de transmission de données numériques LMDS par voie hertzienne à 28 GHz. Les transistors utilisés sont identiques à ceux précédemment abordés pour l'amplification de puissance autour de 20 GHz (HEMTs pseudomorphiques 0,2 x 16 x 100 μm). Quatre composants sont associés par des coupleurs Wilkinson. La puissance de sortie peut atteindre 5 W, le rendement en puissance ajouté est proche de 40 % et le gain de 8,75 dB.

Nous avons également retenu un circuit à base de transistors HBT à 25 GHz présenté par NEC [22]. Celui-ci utilise six HBTs de  $184 \,\mu\text{m}^2$ . La puissance de sortie obtenue est de 2,2 W pour un rendement en puissance ajoutée de 19 % et un gain de 5 dB.

#### I-3.4. Conclusion

Dans le tableau suivant, nous résumons les caractéristiques des différentes réalisations d'amplificateurs hybrides fournies par la littérature pour la bande 20-35 GHz.

| Fréquence | Puissance | Gain    | PAE    | Taille des puces de sortie | Nb de puces | Origine |

|-----------|-----------|---------|--------|----------------------------|-------------|---------|

| centrale  | de sortie |         |        | Lg (μm) x Wu (μm) x N      | en sortie   |         |

| 35 GHz    | 0.8 W     | 10 dB   | 26.6 % | 0.25*75*8                  | 2           | [15]    |

| 35 GHz    | 1 W       | 10 dB   | 25 %   | 0.25*50*10                 | 4           | [16]    |

| 35 GHz    | 1.6 W     | 8.1 dB  | 15.4 % | 0.15*100*2                 | 8           | [17]    |

| 20 GHz    | 4 W       | 16 dB   | 28 %   | 600 µm                     | 12          | [18]    |

| 20 GHz    | 3.2 W     | 10 dB   | 35 %   | 0.2*100*16                 | 4           | [19]    |

| 20 GHz    | 4.7 W     | 7.5 dB  | 38 %   |                            |             | [20]    |

| 28 GHz    | 5 W       | 8.75 dB | 39.6 % | 0.2*100*16                 | 4           | [21]    |

| 26 GHz    | 2.2 W     | 5 dB    | 19 %   |                            | 6           | [22]    |

Nous pouvons constater que ce domaine d'étude est en pleine expansion. L'amélioration des performances est obtenue par l'utilisation de substrats épitaxiés complexes, par l'optimisation des topologies des composants (nombre de doigts, longueur et largeur de grille) et des circuits passifs (adaptateurs et coupleurs). Il convient, cependant, de remarquer que les topologies réalisées pour

ces circuits sont plus du ressors d'un savoir-faire relativement artisanal, acquis après une longue expérience pratique, que le résultat de simulations électriques

Dans ce qui suit, sont présentés les schémas équivalents petit et grand signal d'un transistor.

#### I-4. SCHEMAS EQUIVALENTS DU TEC ASGA

#### I-4.1. Schéma petit signal

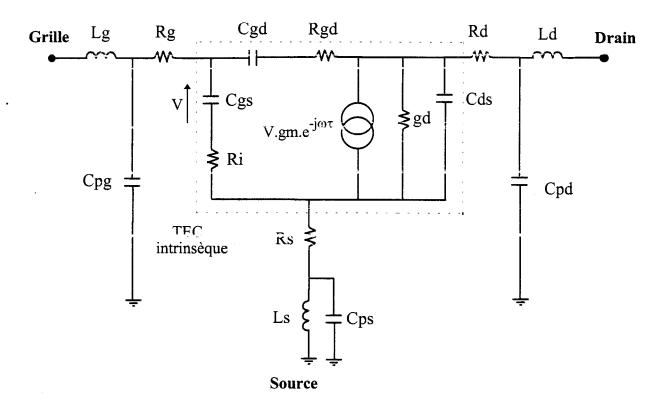

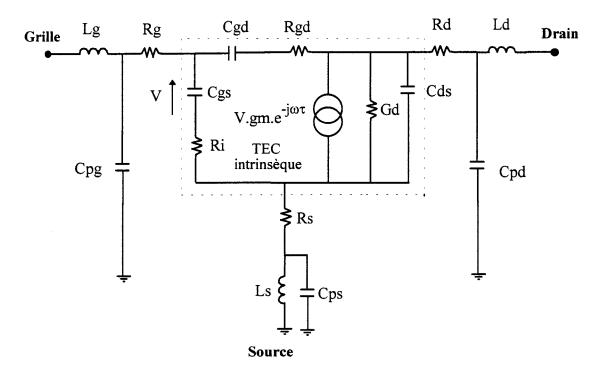

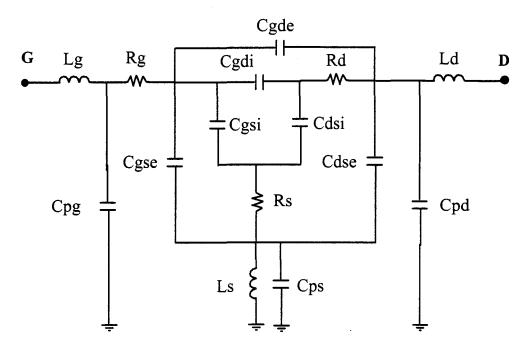

La représentation usuelle du schéma équivalent petit signal d'un transistor à effet de champ est donnée figure I-9.

Figure I-9: Schéma équivalent petit signal du TEC

Ce schéma se compose essentiellement de deux parties :

- La partie extrinsèque qui est constituée des éléments parasites d'accès à la zone active. Ces éléments sont considérés comme indépendants de la polarisation appliquée au transistor.

- La partie intrinsèque qui représente la zone active du composant. Des valeurs sont attribuées à ses éléments pour une polarisation fixée.

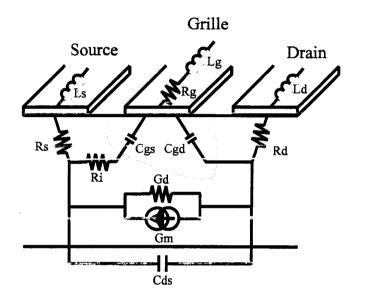

Une localisation des principaux éléments du schéma équivalent est donnée figure I-10.

Figure I-10: Localisation des éléments du schéma équivalent du TEC

Nous allons décrire succinctement les origines des éléments constitutifs de ce schéma équivalent petit signal.

• Les selfs Lg, Ld et Ls peuvent être très différentes suivant le type de mesures et le type de transistor. Pour les TEC en source commune à trous métallisés, la valeur de la self Ls est petite : elle représente l'inductance des métallisations des trous. Pour les mesures en cellule, les selfs traduisent essentiellement les effets induits par les fils de connexion. Pour les mesures sous pointes, l'existence de selfs met en évidence l'influence des métallisations des électrodes du composant.

- Les capacités Cpg, Cpd et Cps correspondent aux plots de métallisation nécessaires aux connexions avec les circuits. L'influence de la capacité Cps est rarement prise en considération puisque l'impédance présentée par cette dernière est généralement grande comparée à celle de la self Ls.

- Rs et Rd représentent les résistances entre les contacts ohmiques (de source et de drain) et la zone active. Rg est la résistance équivalente à celles des doigts de grille.

- Ri est une représentation de l'effet de distribution de résistance entre canal et grille côté source; Rgd entre canal et grille côté drain. Cette dernière est rarement prise en considération dans les schémas équivalents usuels.

- Gm est la transconductance. Elle traduit l'activité de l'élément considéré et est définie par :

$$g_m = \frac{\partial Id}{\partial Vgs}\bigg|_{Vds=cte}$$

• Gd est la conductance de sortie définie par :

$$g_d = \frac{\partial Id}{\partial Vds}\Big|_{V_{es=cle}}$$

- $\tau$  représente le temps de transit des porteurs dans le canal.

- Cgs, Cgd et Cds sont les capacités liées aux charges en présence autour de la zone désertée.

Ce schéma permet de simuler le fonctionnement du transistor autour d'un point de polarisation en lui appliquant des signaux de faibles amplitudes et compatibles avec les mesures de paramètres S détaillées dans la section suivante.

Le schéma équivalent permet également d'approcher les performances du transistor en fonction des valeurs prises par les éléments. Nous ne pouvons donc qu'extrapoler avec prudence les performances au-delà de la fréquence maximale de mesure.

Le MAG peut être exprimé par la relation ci-dessous en utilisant quelques simplifications [23]:

$$MAG = \left(\frac{Fc}{f}\right)^{2} \frac{1}{4g_{d}\left(Rg + Rs + Ri + \pi.Fc.Ls\right) + 4\pi.Fc.Cgd\left(2Rg + Ri + Rs + 2\pi.Fc.Ls\right)}$$

Fc étant la fréquence de coupure :

$$Fc = \frac{g_m}{2\pi . Cgs}$$

Une estimation de la fréquence de coupure du gain maximum disponible (MAG = 1) peut être déduite de l'expression précédente ; elle s'écrit :

$$F_{MAG} = \frac{Fc}{2\sqrt{gd}} \frac{1}{\sqrt{\left(Rs + Ri + Rg\right) + \pi.Fc.Ls + \pi.Fc\frac{Cgd}{gd}\left(Rs + 2Rg + Ri + 2\pi.Fc.Ls\right)}}$$

Le gain en courant de court-circuit H<sub>21</sub> peut également être exprimé en fonction des éléments du schéma équivalent. Il est différent de celui obtenu à partir des paramètres S puisque les éléments extrinsèques ne sont pas pris en compte. Le gain en courant de court-circuit est donné par la relation :

$$\left|H_{21}\right|_{\rm int}^2 = \left(\frac{gm}{\omega(Cgs + Cgd)}\right)^2$$

L'intérêt majeur de ces définitions est l'étude des performances du composant en fonction des éléments du schéma équivalent qui sont directement liés à des critères technologiques.

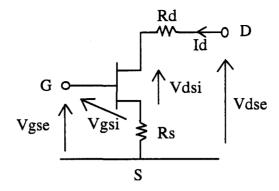

#### I-4.2. Schéma grand signal

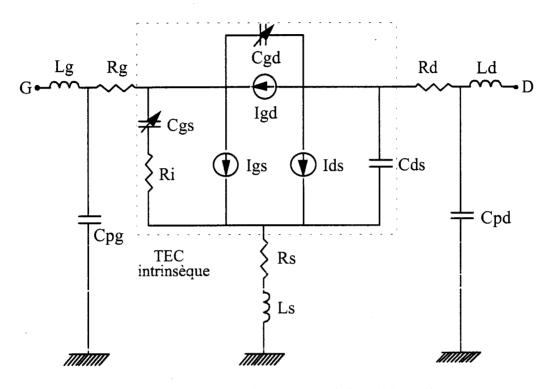

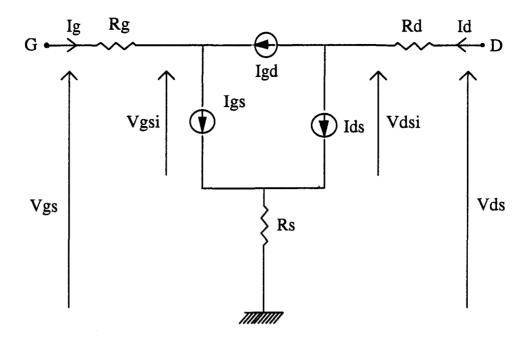

Une modélisation grand signal du transistor est possible avec le schéma équivalent de la figure I-11.

Figure I-11: Schéma équivalent grand signal du TEC

Les éléments extrinsèques sont indépendants de la polarisation du composant. Ils sont considérés identiques à ceux du schéma petit signal. Les éléments intrinsèques Ri, Cds,  $\tau$  varient avec la polarisation. Ces variations sont cependant faibles et souvent elles sont considérées faire partie des incertitudes de mesures d'autant qu'elles se produisent après le pincement ou dans la région ohmique.

Ces éléments sont donc généralement considérés fixes et identiques à ceux du schéma équivalent petit signal. En conséquence, les causes principales des non - linéarités sont donc les deux capacités Cgs et Cgd et les trois générateurs de courants de la figure I-11.

• Les capacités Cgs et Cgd représentent les charges accumulées entre grille - source et grille - drain. Ces capacités évoluent avec les tensions Vds et Vgs.

- Le générateur de courant Ids est généralement considéré comme la principale source de non-linéarités d'un transistor. Il traduit l'effet de commande des tensions Vgs et Vds dans un composant à effet de champ.

- Le générateur de courant Igd permet de traduire l'existence d'un phénomène d'avalanche entre la grille et le drain quand la tension Vgd devient importante. Cet effet limite la puissance fournie par le transistor en écrêtant le signal de sortie.

- Le générateur de courant Igs représente la mise en direct de la jonction Schottky grille canal pour des tensions de grille Vgs positives. C'est une limitation de la puissance

d'entrée par écrêtage du signal.

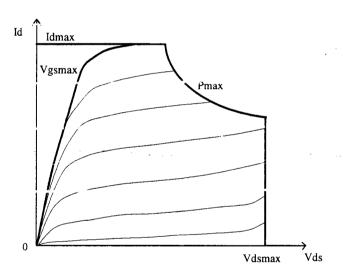

Les valeurs des éléments des modèles petit et grand signal sont extraites des mesures effectuées pour caractériser le composant. Cette caractérisation met en œuvre différents bancs de mesures ; ceux-ci sont décrits dans le paragraphe suivant.

#### **I-5. CARACTERISATION DES TECS**

La caractérisation comporte des mesures statiques, quasi - statiques et hyperfréquences qui permettent de modéliser complètement le composant. Des mesures en puissance sont également effectuées sur un bane à charge active ; elles constituent une validation de la modélisation non - linéaire.

Durant la caractérisation, le transistor est soumis à des conditions de fonctionnement différentes : évolutions du point de polarisation et du signal hyperfréquence. Celles-ci engendrent deux phénomènes majeurs dans le comportement du composant :

- Les phénomènes thermiques dus au niveau continu.

- Les phénomènes de piégeages des électrons en présence d'un signal hyperfréquence et d'un niveau continu.

Nous allons décrire les différents bancs de mesures que nous avons utilisés et comment se traduisent les deux phénomènes précités.

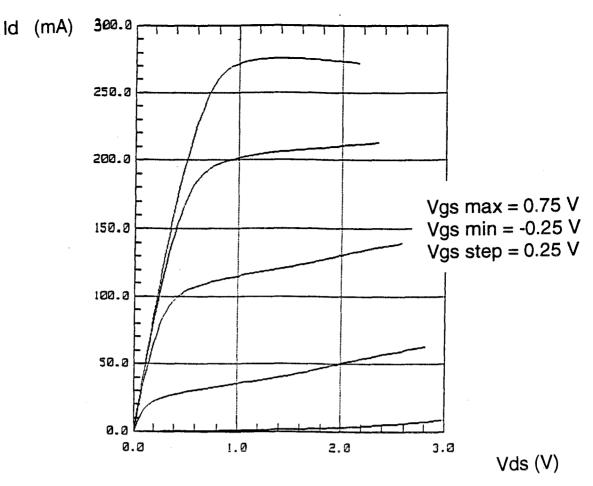

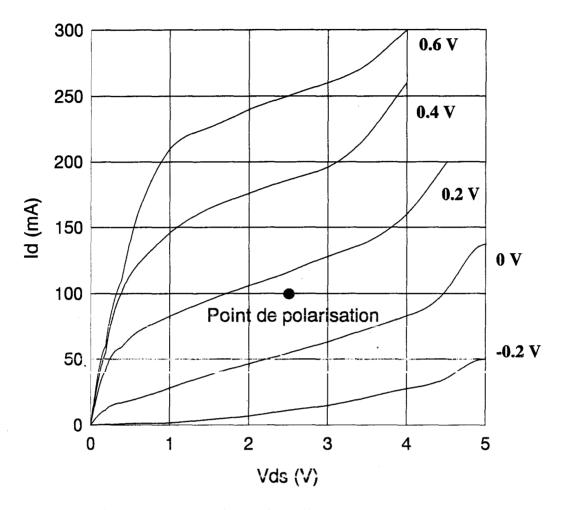

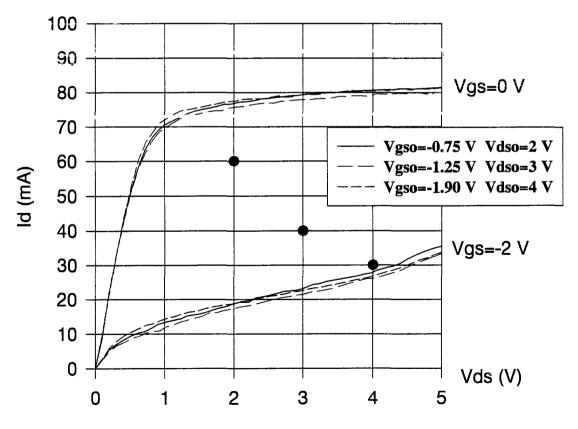

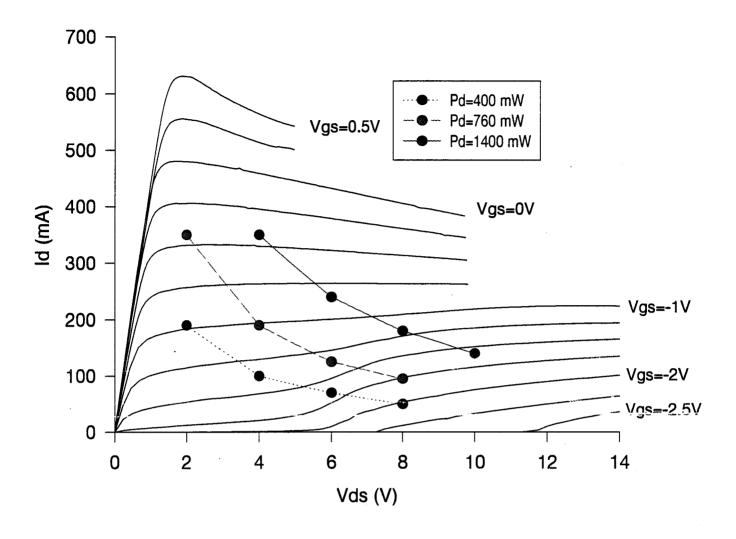

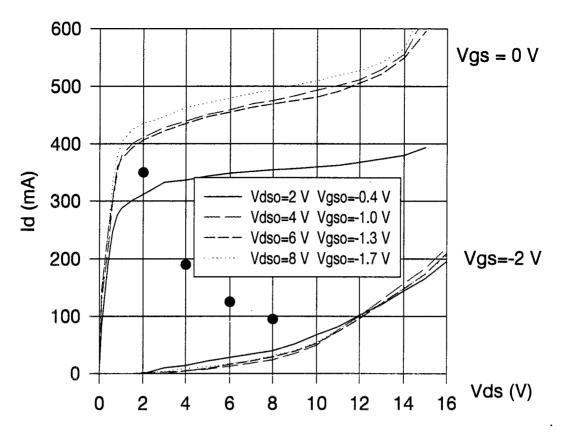

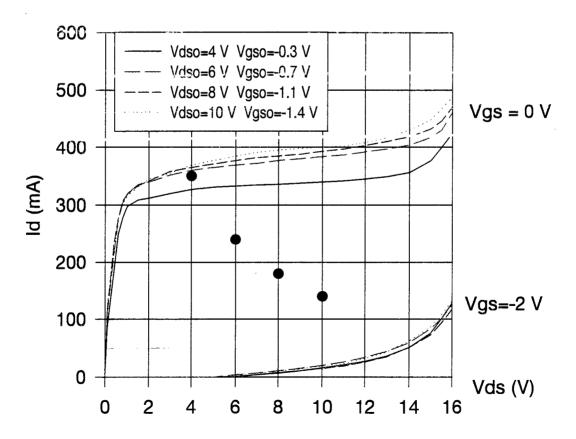

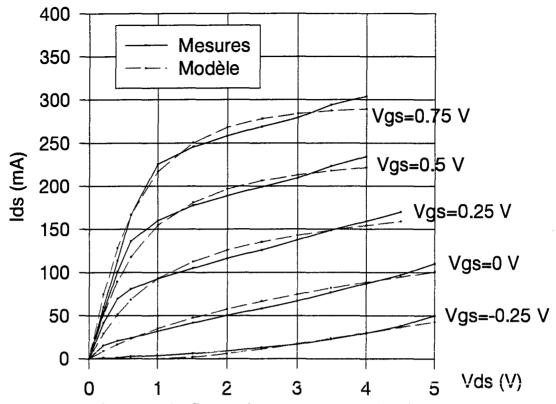

Figure I-13: Caractéristiques statiques Ids=f(Vgs, Vds) obtenues pour le HEMT Thomson TA33660

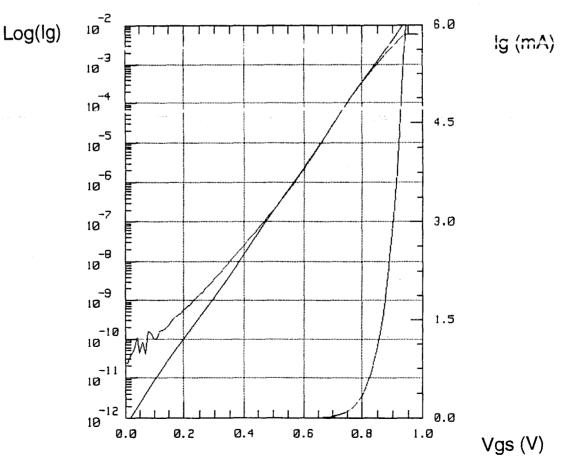

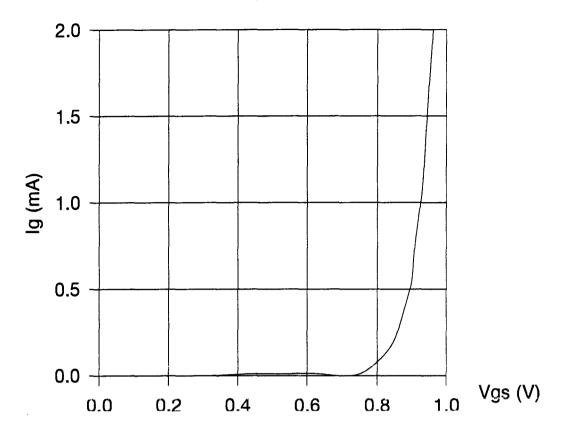

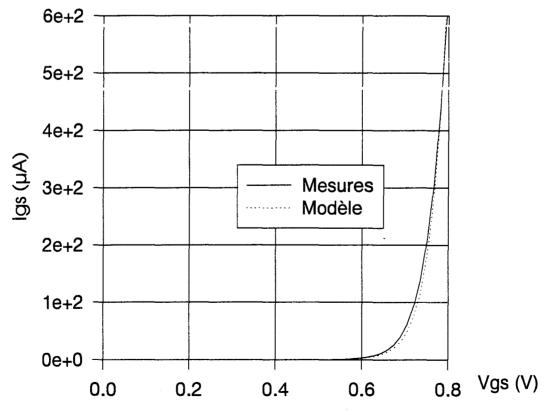

Figure I-14: Caractéristique statique de la diode Schottky Ig=f(Vgs) du HEMT Thomson TA33660

#### I-5.1. Mesures statiques

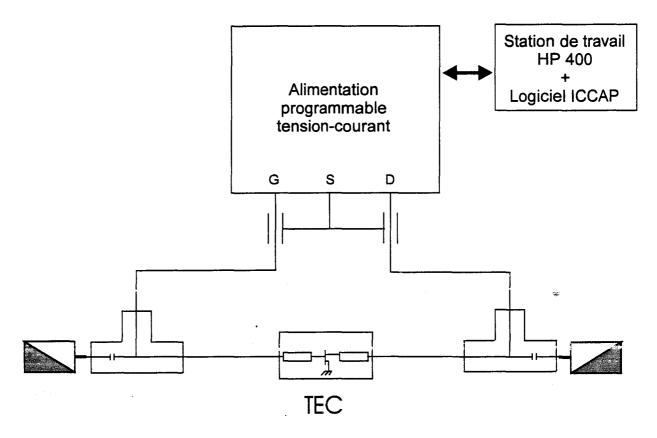

Cette caractérisation, qui utilisé le logiciel ICCAP de Hewlett Packard, est entièrement automatique ; son synoptique est donné figure I-12.

Figure I-12: Banc automatique de mesures statiques

Des tensions continues sont appliquées d'une part entre grille et source et d'autre part entre drain et source du composant ; les courants engendrés par ces tensions sont mesurés. Pour ce type de fonctionnent statique, le phénomène de piégeage d'électrons évolue avec les conditions de polarisation.

La puissance dissipée n'est pas la même à chaque point de mesures, ce n'est pas une caractérisation isotherme. Quelques mesures significatives sont maintenant présentées, les tracés des réseaux de caractéristiques Ids = f (Vds) et Ids = f (Vgs) permettent de connaître le courant de

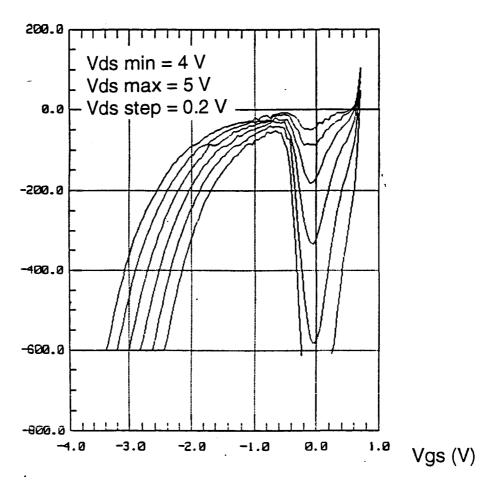

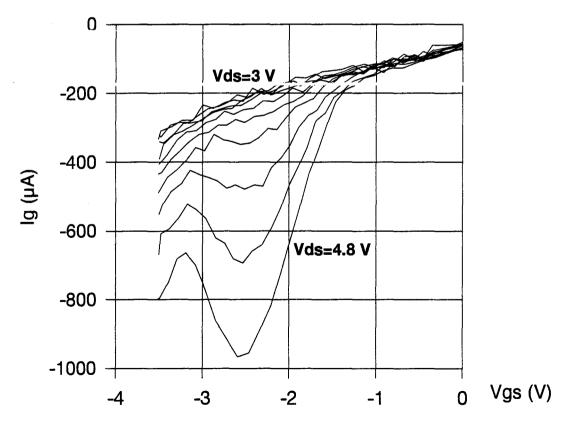

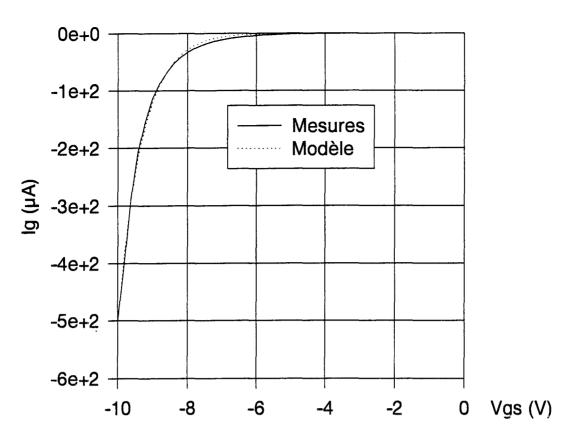

Figure I-15 : Caractéristiques statiques du courant de grille inverse Ig=f(Vgs, Vds) du HEMT Thomson TA33660

saturation et de la tension de pincement (figure I-13). Le logiciel permet également de déduire les évolutions de sa transconductance Gm et de la conductance de sortie Gd statiques.

La caractérisation Igs = f (Vgs) avec le drain en l'air permet de visualiser le courant de la mise en direct de la jonction Schottky. Le coefficient d'idéalité ainsi que la hauteur de barrière Vb et la valeur de la tension de built-in (figure I-14) peuvent être déduits de cette caractéristique.

Les caractéristiques Ig = f (Vds, Vgs) donnent le comportement du courant grille dans les conditions de pincement (figure I-15).

Une limitation du courant de grille est imposée pour éviter la destruction du composant : la densité de ce courant ne dépasse pas le milliampère par millimètre de développement de grille.

Sur ces caractéristiques, deux zones distinctes apparaissent :

- Pour une tension Vgs inférieure à la tension de pincement, on est présence du claquage de la diode grille-drain. Le phénomène physique reconnu comme dominant dans ce cas est un effet Tunnel pur ou assisté thermiquement [24].

- Pour une tension Vgs supérieure à la tension de pincement, une évolution en courbe en cloche est observée, avec un maximum de courant grille croissant avec la tension Vds. Ce comportement est maintenant reconnu comme résultant essentiellement d'un phénomène d'ionisation dans le canal [25]. Cette mesure donne des renseignements sur les limitations du composant liées à son courant grille..

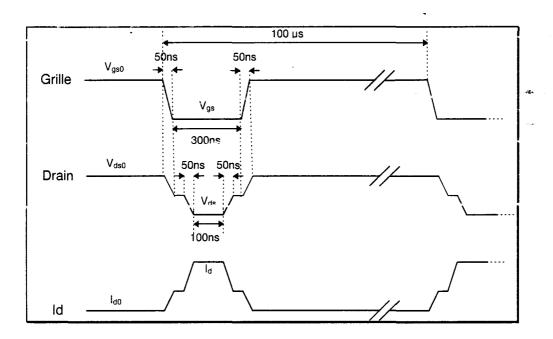

#### I-5.2. Mesures quasi - statiques impulsionnelles

Cette caractérisation permet d'imposer au composant une température constante correspondant à un point de polarisation et de balayer toute une gamme de tensions Vgs et Vds sans modifier cette température.

La durée des impulsions utilisées est choisie suffisamment courte pour que le piégeage des électrons se manifeste de la même façon que dans les conditions de fonctionnement microonde.

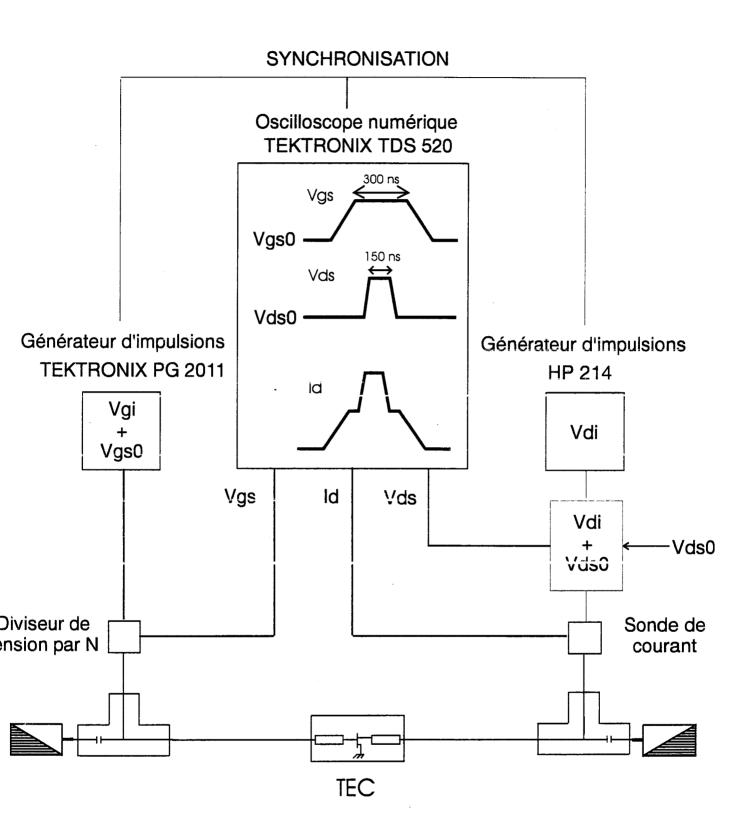

Figure I-16: Banc manuel de mesures en impulsions

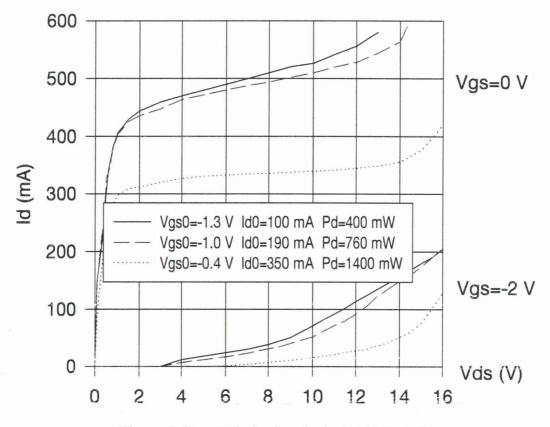

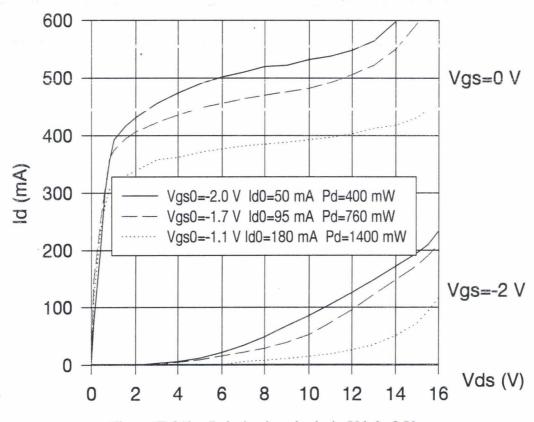

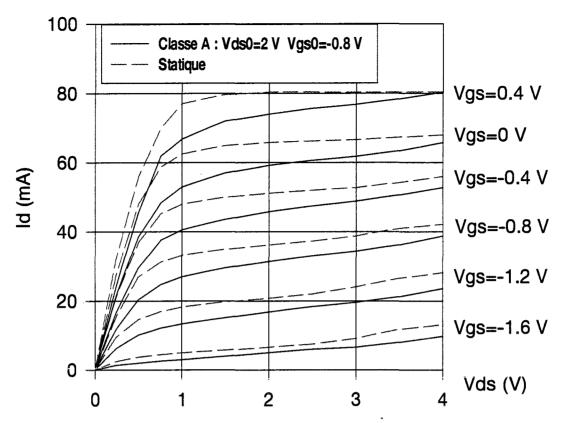

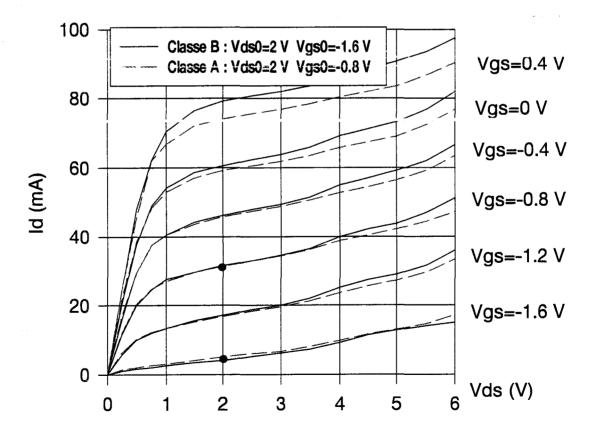

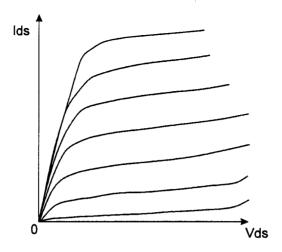

Figure I-17: Exemple de caractéristiques impulsionnelles obtenues pour le HEMT Thomson TA33660 autour d'un point de fonctionnement classe A

Ce banc initialement manuel, a été automatisé. Ce travail a constitué une partie de notre contribution et fait l'objet d'une étude détaillée au chapitre II.

La figure I-16 donne le schéma synoptique du banc dans sa version manuelle initiale [26].

Cette caractérisation consiste à appliquer sur le drain et la grille du transistor des impulsions synchrones de tensions.

Nous allons, comme pour la caractérisation statique, présenter quelques mesures significatives.

Les caractéristiques Ids = f(Vgs, Vds), pour différents points de polarisation, sont souvent utilisées par les concepteurs de circuits pour modéliser le générateur de courant de drain.

Un exemple des caractéristiques ainsi obtenues est donné figure I-17 dans le cas d'un point de polarisation classe A.

Ces mesures sont utilisées soit par le concepteur de composants, soit par le concepteur de circuits. Le concepteur de composants peut étudier les effets de piégeages d'électrons et les effets thermiques qui interviennent sur les transistors réalisés. Le concepteur de circuits utilise les mesures pour modéliser les générateurs de courants du composant. Ceci est développé de façon plus détaillée dans le chapitre II.

Passons maintenant aux mesures hyperfréquences.

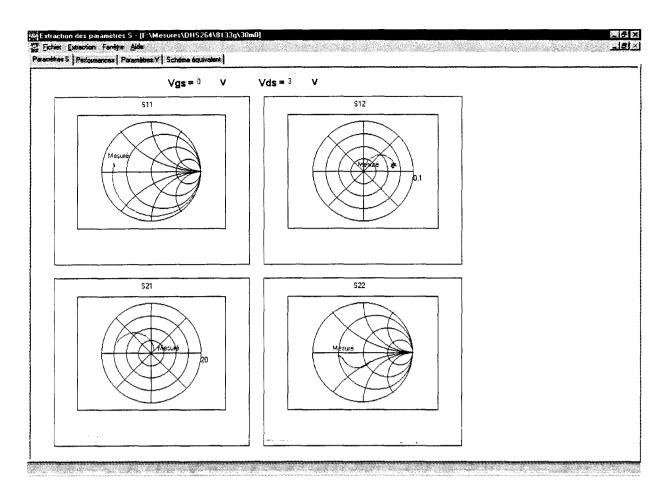

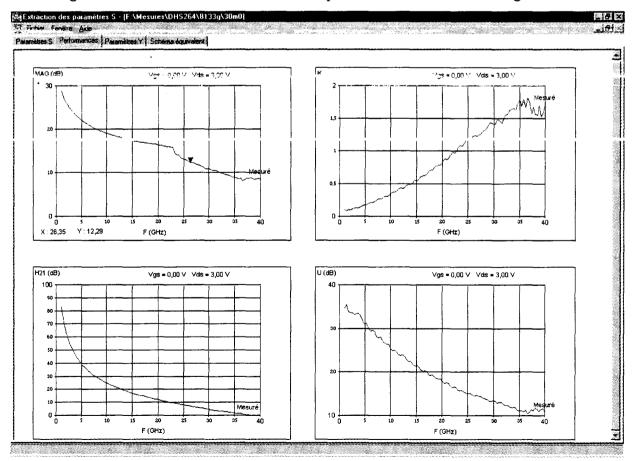

### I-5.3. Mesures hyperfréquences à l'analyseur de réseaux jusque 40 GHz

Ces mesures sont effectuées sur un analyseur de réseau HP 85107A de 45 MHz à 40 GHz pour de nombreux points de polarisation. Le programme de commande initial écrit en HP BASIC, a été modifié pour automatiser entièrement le processus de mesures. Ainsi nous pouvons générer les quelques centaines de fichiers de paramètres S, soit en fonction des tensions externes appliquées au transistor, soit en fonction des tensions internes. Une caractérisation complète effectuée, en fonction des tensions internes, peut prendre quelques heures.

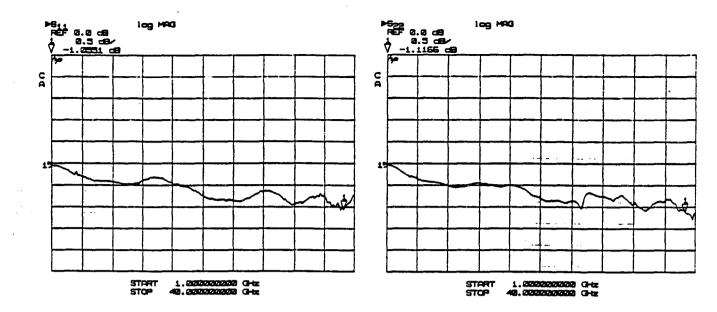

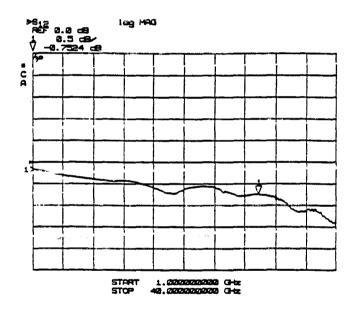

Figure I-19a : Mesure des demi - boitiers en circuit ouvert

Figure I-19b : Mesure de la cellule en Thru

Figure I-19 : Evolutions fréquentielles des paramètres de la cellule de mesure

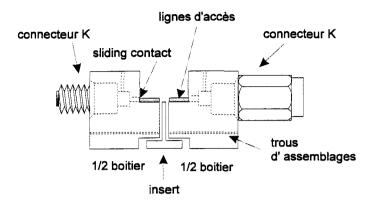

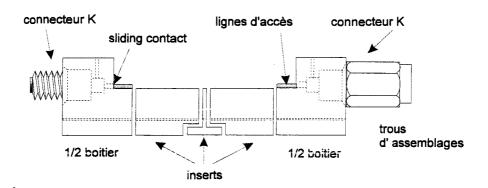

Le transistor peut être mesuré sous pointes ou bien dans une cellule réalisée au laboratoire (cellule « Dambrine »). Ce dernier dispositif est présenté figure I-18.

Figure I-18: Dispositif de mesure en cellule

La cellule est constituée de deux demi boîtiers qui réalisent les transitions coaxial - microruban à l'aide d'une pièce coulissante appelée « sliding contact ». La ligne microruban à une impédance caractéristique de 50 Ω. Le transistor est collé sur un insert. Un calibrage TRL est effectué pour chacune des cellules réalisées.

Nous rappelons que cette méthode utilise 3 étalons standards :

- Une connexion directe (Thru)

- Des circuits ouverts (Reflect)

- Une ligne microruban d'impédance caractéristique 50  $\Omega$  entre les demi boîtiers (Line).

Le calibrage obtenu permet selon la qualité de la cellule d'effectuer des mesures fiables jusque environ 35 GHz. La figure I-19 montre, à titre d'exemple, les mesures des paramètres S d'une cellule en Thru et en circuit ouvert.

Les mesures sous - pointes sont correctes jusque 40 GHz. A chaque fois que cela est possible, la mesure sous - pointes est choisie plutôt que la mise en cellule.

Après dépouillement des mesures, quelques éléments du schéma équivalent du TEC sont obtenus. Les procédures utilisées seront détaillées plus finement dans le chapitre III.

Figure I-20 : Schéma synoptique du banc à charge active 26-40 GHz

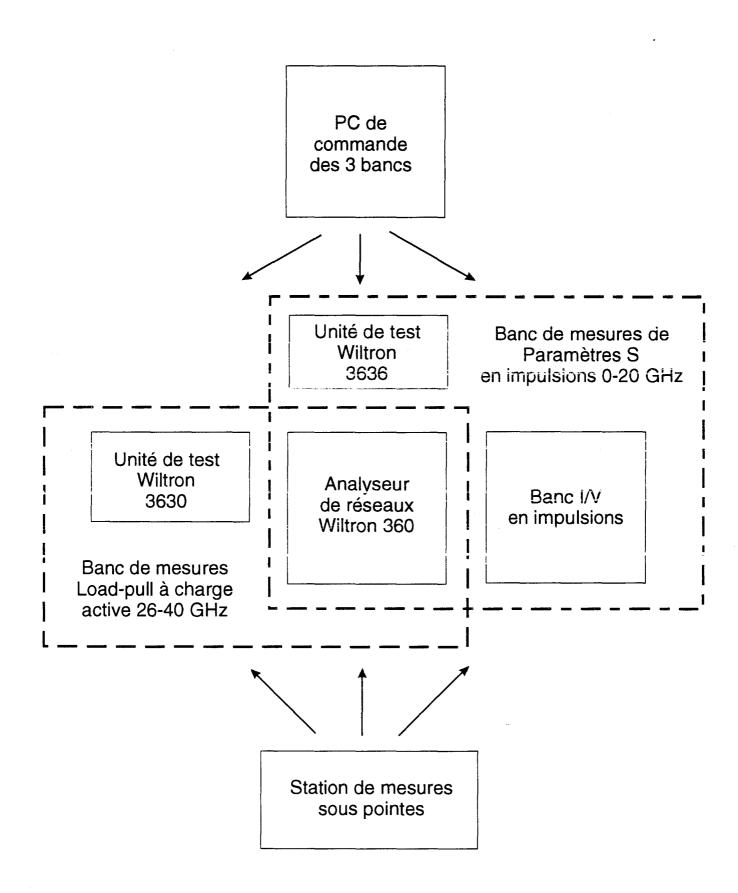

#### I-5.4. Mesures hyperfréquences pulsées à l'analyseur de réseaux jusque 20 GHz

Elles utilisent un analyseur de réseau Wiltron 360B couplé au TestSet 3636. Cet équipement permet d'appliquer un signal hyperfréquence de courte durée (quelques dizaines de nanosecondes) pendant laquelle la mesure des paramètres S est effectuée. Ce banc n'était pas encore opérationnel au laboratoire lorsque l'essentiel de notre travail a été réalisé. A terme, il sera couplé aux générateurs d'impulsions du banc quasi-statique pour permettre la mesure des paramètres S à température constante et à effet de piège constant.

# I-5.5. Mesures sur le banc à charge active 26-40 GHz

Ce procédé a été proposé par Takayama [27]. Il consiste à appliquer des signaux synchrones au transistor en entrée et en sortie. Un atténuateur et un déphaseur agissent sur un signal injecté en sortie du composant de manière à simuler une charge variable.

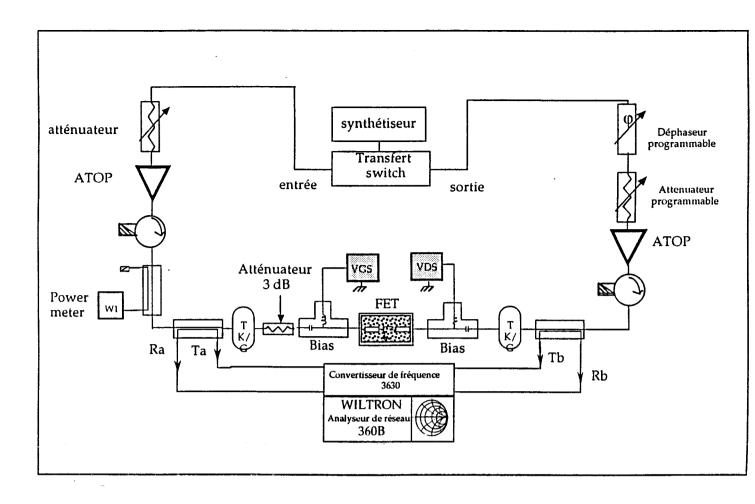

Une version entièrement automatique, sans adaptation d'entrée, [28, 29] a été réalisée au laboratoire pour la bande 26-40 GHz. Son synoptique est donné figure I-20.

Ce banc utilise un convertisseur de fréquence 3630 couplé à l'analyseur de réseau Wiltron 360B. Le synthétiseur fournit la puissance hyperfréquence à l'entrée et à la sortie du TEC. Le transfert Switch permet de passer du mode banc à charge active au mode analyseur de réseaux petit signal ou grand signal.

Deux ATOPS (Amplificateurs à Tubes à ondes progressives) sont présents en entrée et en sortie pour permettre de délivrer des puissances proches de 40 dBm (50 dB de gain à 33 GHZ).

Les ponts réflectomètriques utilisent des coupleurs ayant une directivité supérieure à 40 dB, des pertes d'insertion de l'ordre de 0,3 dB et un coefficient de réflexion de 30 dB.

Le composant peut être mesuré sous pointes ou en cellule. Dans les deux cas, un calibrage spécifique est effectué.

Le logiciel de commande permet, grâce au transfert Switch, de faire soit les mesures en load - pull soit les mesures des paramètres Sij petits et grands signaux. Pour ces dernières, des acquisitions des quatre paramètres S, du courant de drain Id, du courant de grille Ig et la puissance injectée en entrée du composant sont effectuées.

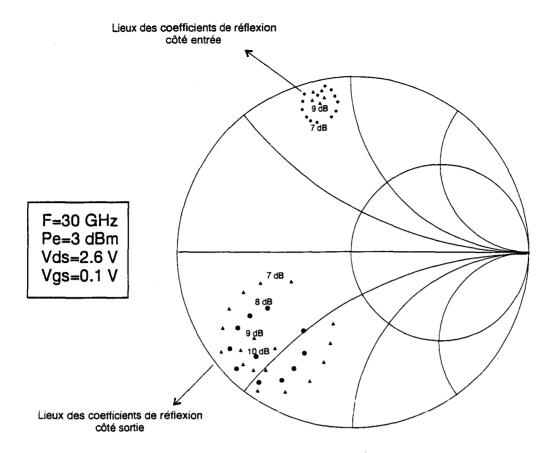

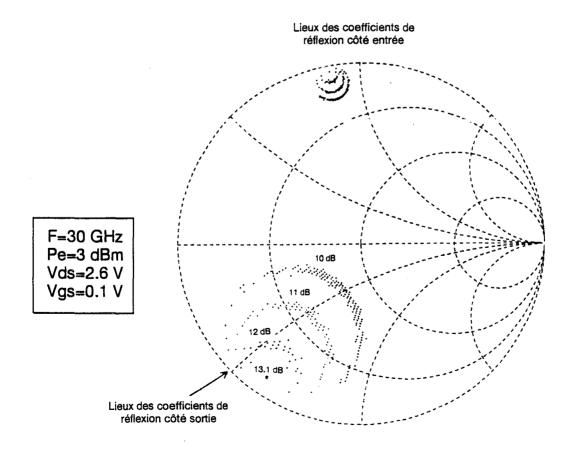

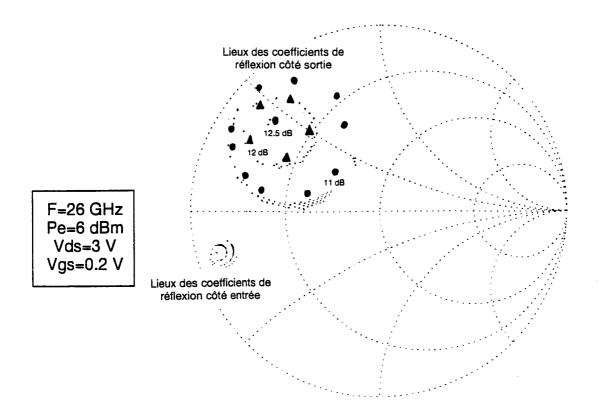

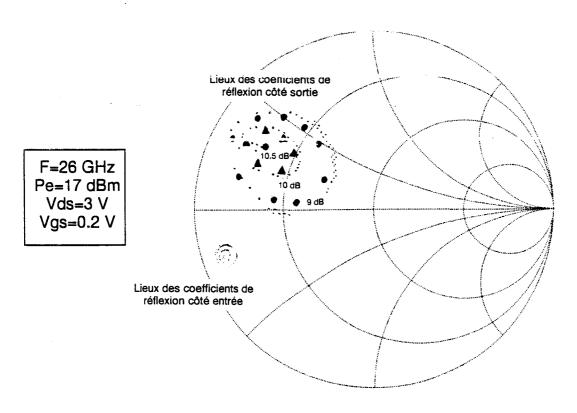

Les paramètres Sij expérimentaux permettent de déterminer les cercles à gain constant et les cercles de stabilité. Un cercle à gain constant est ensuite choisi dans une région de l'abaque où le composant est stable; c'est dans ce cercle que seront initialisées les mesures en load-pull. L'exploitation de ces dernières permet de visualiser deux types de représentations :

- Un abaque de Smith où sont repérés les lieux des coefficients de réflexion S'<sub>11</sub> et Γ<sub>L</sub> correspondants à un gain constant (G<sub>P</sub>, G<sub>T</sub> ou Gav), à une puissance de sortie constante (P<sub>S</sub>abs ou P<sub>S</sub>dis), à un courant de grille ou de drain constant ou, enfin à un rendement constant (η<sub>PAE</sub> ου η<sub>D</sub>)

- Un repère cartésien où sont représentées les évolutions du gain, du rendement ou des courants en fonction de la puissance d'entrée avec le coefficient de réflexion comme paramètre.

Ces mesures permettent une validation des schémas équivalents grand signal développés.

Cette validation est décrite en détail dans le troisième chapitre.

#### I-6. CONCLUSION

Dans ce premier chapitre, nous avons tout d'abord abordé les principes de base de l'amplification hyperfréquence, les aspects linéaires et non-linéaires ainsi que l'association d'étages amplificateurs.

Dans un deuxième temps, un bref historique des réalisations récentes a été présenté. Ces dispositifs donnent une idée de l'état de l'art du domaine des amplificateurs de puissance hybrides dans le bande 20-40 GHz.

Dans une troisième partie, nous avons défini les éléments du schéma équivalent d'un transistor à effet de champs qui sont utilisés pour l'étude des régimes d'amplifications linéaire et non-linéaire. Enfin, les mesures couramment utilisée pour extraire les éléments du schéma équivalent ou valider ceux-ci ont été présentées.

Dans le deuxième chapitre, nous allons développer l'automatisation du banc de mesures I/V en impulsions.

# **BIBLIOGRAPHIE DU PREMIER CHAPITRE**

#### [1] C. GENTILI

« Amplificateurs et oscillateurs micro-ondes »

Editions Masson.

#### [2] C. DUVANAUD

« Les classes de fonctionnement à haut rendement pour l'amplification de puissance microonde, en vue d'applications spatiales et de radiocommunications mobiles »

Doctorat de l'université de Limoges, 1993.

# [3] J. ROGERS and R. BHATIA

« A 6 to 20 GHz planar balun using a Wilkinson divider and Lange couplers » IEEE MTT Symposium Digest, 1991, pp 865-868.

#### [4] J. R. LANE and al

« High efficiency 1, 2, and 4 W class-B FET power amplifiers »

IEEE Transactions on Microwave Theory and Techniques, décembre 1986, pp 1318-1325.

#### [5] I. J. BAHL and al

« Class B power MMIC amplifiers with 70 percent power added efficiency »

IEEE Transactions on Microwave Theory and Techniques, septembre 1989, pp 1315-1320.

# [6] S. NISHIKI and T. NOJIMA

«Harmonic Reaction Amplifier - A novel high efficiency and high power microwave amplifier »

IEEE MTT-S Digest, 1987, pp 963-966.

# [7] F. N. SECHI

« Design Procedure for high-efficiency linear microwave power amplifiers »

IEEE Transactions on Microwave Theory and Techniques, décembre 1980, pp 1157-1163.

# [8] D. BECHTLE and al

« K and Ka band high efficiency amplifier modules using GaAs power FETs » IEEE MTT-S Digest, 1987, pp 849-851.

#### [9] D. HELMS and al

«Ku band power amplifier using pseudomorphic HEMT devices for improved efficiency»

IEEE MTT-S Digest, 1991, pp 819-821.

#### [10] S. TOYODA

« High efficiency single and push-pull power amplifiers »

IEEE MTT-S Digest, 1993, pp 277-280.

# [11] K. CHIBA and N. KANMURI

« GaAs FET power amplifier module with high efficiency » Electronics Letters, novembre 1983, pp 1025-1026.

# [12] L. C. HAL and R. J. TREW

« Maximum efficiency tuning of microwave amplifiers » IEEE MTT-S Digest, 1991, pp 123-126.

#### [13] D. M. SINDER

« A theoretical analysis and experimental confirmation of the optimally loaded and overdriven RF power amplifier »

IEEE Transactions on Electron Devices, décembre 1967, pp 851-857.

# [14] M. A. KHATIBZADEH and H. Q. TSERNG

« Harmonic tuning of power FETs at X band »

IEEE MTT-S Digest, 1990, pp 989-992.

#### [15] J. M. SCHELLENBERG and al

« A 0.8 watt Ka band power amplifier »

IEEE MTT-S Digest, 1992, pp 529-532.

# [16] G. S. DOW and al

« Ka band high efficiency 1 watt power amplifier »

IEEE MTT-S Digest, 1992, pp 579-582.

#### [17] A. K. SHARMA and al

« Ka band power PHEMT on-wafer characterisation using prematched structures » IEEE MTT-S Digest, 1993, pp 1343-1346.

# [18] R. YARBOROUGH and al

« Four watt 20 GHz partial monolithic amplifier »

IEEE MTT-S Digest, 1993, pp 1381-1383.

# [19] C. H. CHEN and al

« 20 GHz high power efficiency HEMT module »

IEEE MTT-S Digest, 1993, pp 1377-1380.

#### [20] B. KRAEMER and al

« Power PHEMT module delivers 4 watts, 38 % PAE over the 18 to 21.2 GHz band » .

IEEE MTT-S Digest, 1994, pp 801-804.

# [21] M. K. SIDDIQUI and al

«A high power and high efficiency power amplifier for local multipoint distribution service»

IEEE MTT-S Digest, 1996, pp 701-704.

# [22] S. TANAKA and al

« High power, high efficiency cell design for 26 GHz HBT power amplifier » IEEE MTT-S Digest, 1996, pp 843-846.

#### [23] F. MASUMI

« GaAs microwave power FET »

IEEE Transactions on Electron Device ED 32, avril 1976.

# [24] C. GAQUIERE and al

« Breakdown analysis of an asymmetrical double recessed power MESFET's »

IEEE Transactions on Electron Devices, février 1995, pp 209-213.

# [25] C. R. CROWELL and V. L. RIDEOUT

« Normalizd thermoionic field emission in metal-semiconductor barriers » Solid State Electronics, 1969, pp 89-105.

# [26] L. RULLIER

« Contribution à la modélisation non-linéaire de TEC en GaAs : Mise au point et utilisation d'un banc de mesure en impulsions »

Rapport DEA, Lille, juillet 1993.

# [27] Y. TAKAYAMA

« A new load-pull characterisation method for microwave power transistors » IEEE MTT Symposium Digest, 1976, pp 218-220.

# [28] A. AMAIRI

« Caractérisation en petit signal, en puissance et en impédances des transistors à effet de champ millimétrique. Etude et réalisation d'un banc de Load Pull à charge active 26.5-40 GHz »

Thèse d'Université, Lille, septembre 1991.

#### [29] C. GAQUIERE

« Analyse et optimisation de transistors à effet de champ à hétérojonction pour l'amplification de puissance dans la bande Ka »

Thèse d'Université, Lille, novembre 1995.

# **CHAPITRE II**

#### II- AUTOMATISATION D'UN BANC DE MESURES I (V) EN IMPULSIONS

#### II-1. INTRODUCTION

Cette partie décrit la démarche que nous avons suivie pour mettre au point notre banc de caractérisation pulsée de composants à effet de champ. Les premières mesures, effectuées avec ce banc automatique permettent de mettre en évidence les principaux phénomènes qui apparaissent dans les transistors à effet de champ utilisés en amplification de puissance hyperfréquence.

#### II-2. ETUDE PRELIMINAIRE ET PRINCIPE DE MESURE

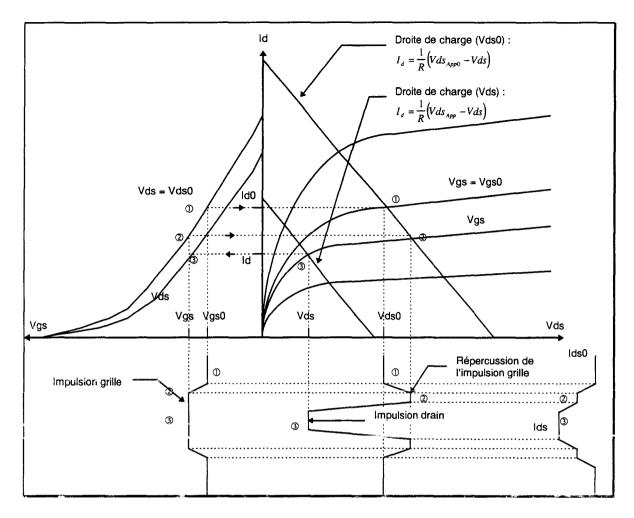

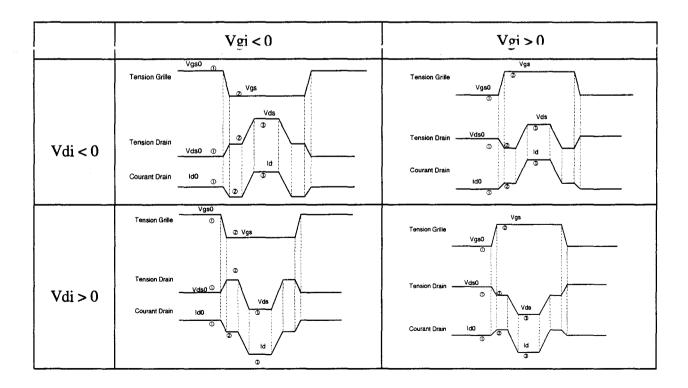

Le principal intérêt de cette méthode de caractérisation, signalé succinctement dans le premier chapitre, est de reproduire les conditions de fonctionnement d'un transistor inséré dans un circuit : autour d'un point de polarisation préalablement fixé, des excursions de signal sont appliquées au transistor à effet de champ testé [1, 2].

Deux phénomènes importants sont induits par ce mode de fonctionnement : l'un est unermique, l'autre est un effet de piegeage des porteurs majoritaires. Nous nous intéressons dans un premier temps au phénomène thermique.

#### II-2.1.Phénomène thermique [3, 4]

La température du composant n'est pas uniquement celle imposée par son milieu ambiant; elle est étroitement corrélée à la puissance continue dissipée par le composant. L'écart thermique, induit par une variation du niveau de puissance continue dissipée, est classiquement donné par la relation :

$$\Delta T = R_{ih} \cdot \Delta P$$

# V (10E7 cm/s) 2.5 2.0 1.5 1.0 0.5 0.0 10 20 30 E (kV/cm)

Figure II-1: Vitesse des porteurs en fonction du champ électrique pour différentes températures

Dans cette expression  $\Delta T$  et  $\Delta P$  sont respectivement les variations de température et de puissance ;  $R_{th}$  est la résistance thermique du composant. Cette dernière est liée aux dimensions du composant par la relation :

$$R_{th} = \frac{e}{K.S}$$

où e est l'épaisseur du substrat, S sa surface et K la conductivité thermique du matériau.

Dans l'hypothèse où les effets de dilatation avec la température du matériau semi-conducteur sont négligés, une élévation de température induit plusieurs phénomènes : des diminutions de la hauteur de barrière de potentiel des jonctions, de la tension de pincement et de la mobilité des porteurs. Les variations de température influencent donc fortement le comportement électrique des composants.

L'effet principal, observé sur les transistors à effet de champ de puissance, est la réduction de la mobilité des porteurs quand la température croit. Une illustration de ce phénomène est donnée sur la figure II-1. Les caractéristiques statiques Id=f(Vds, Vgs) montrent clairement, qu'à canal ouvert, le courant de drain décroît lorsque la tension Vds augmente. En revanche lorsque le canal est très pincé le courant de drain se réduit fortement et, même si la tension Vds présente des valeurs élevées, la puissance continue dissipée reste faible et le composant se refroidit.

En régime dynamique grand signal hyperfréquence une température moyenne est obtenue dans la mesure où le point de fonctionnement du composant polarisé traverse rapidement et alternativement les régions à canal pincé et à canal ouvert.

Suite à ces remarques sur les problèmes thermiques une question se pose : quelles précautions doit-on prendre pour que la caractérisation impulsionnelle, qui consiste à appliquer des impulsions synchrones de faibles durées autour d'un point de polarisation, permette de reproduire fidèlement les conditions de fonctionnement réelles d'un composant ?

Des éléments de réponse peuvent être apportés à cette question en considérant deux types de fonctionnement.

Le premier est celui où les coordonnées du point de polarisation ne sont pratiquement pas modifiées quand un signal hyperfréquence est appliqué au transistor. Ce type de fonctionnement s'apparente à l'amplification classe A linéaire ou faiblement non-linéaire. Dans ce cas le point de polarisation choisi pour effectuer la caractérisation pulsée est identique à celui de l'étage amplificateur au repos.

Dans le second type de fonctionnement, observé en régime non-linéaire et particulièrement en classe B, les coordonnées du point de polarisation évoluent en fonction du niveau de puissance hyperfréquence délivré par le composant. En conséquence, pour les mesures impulsionnelles , il n'est pas possible de choisir un point de polarisation analogue à celui de l'étage amplificateur au repos. Néanmoins, moyennant un compromis acceptable, l'expérimentation présentée à la fin de ce chapitre permet de définir un point de polarisation pour effectuer les mesures pulsées.

Les problèmes de mesure liés à l'influence de la température sur le composant étant évoqués, nous nous intéressons maintenant à ceux qui sont introduits par les effets de piège.

#### II-2.2.Phénomènes de piégeage des électrons [5, 6]

Les pièges d'électrons sont des niveaux accepteurs ; leur densité dans le matériau dépend très fortement de la filière technologique d'où provient le semi-conducteur.

L'effet des pièges, sur les caractéristiques des transistors à effet de champ, est étroitement lié aux conditions dans lesquelles le composant fonctionne. Les paramètres qui influencent le plus l'activité des pièges sont la fréquence, la température et la polarisation; d'autres paramètres peuvent également intervenir mais leurs effets sont moindres et très souvent considérés comme du second ordre.

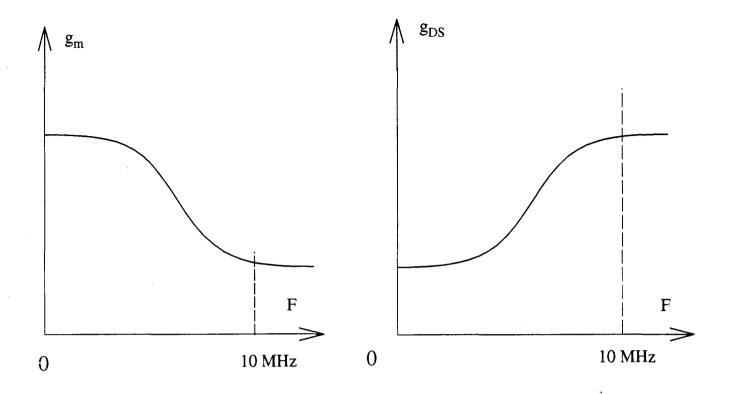

Figure II-2 : Evolutions fréquentielles de la transconductance et de la conductance d'un TEC.

#### II-2.2.a.Influence de la fréquence du signal sur les pièges

La fréquence est un paramètre auquel les pièges sont très sensibles. Les effets de piège sont particulièrement marqués sur les évolutions, en fonction de la fréquence, de la conductance et de la transconductance d'un transistor à effet de champ. La figure II-2 donne un exemple typique des évolutions de gd et gm avec la fréquence. Cette figure montre, qu'au dessus de 10 MHz, les effets des pièges ne sont plus à prendre en considération : les valeurs de gd et gm se sont stabilisées.

La présence de pièges est l'un des phénomènes qui permet d'expliquer la différence entre les mesures RF et statique d'une même caractéristique d'un composant (le Gd par exemple).

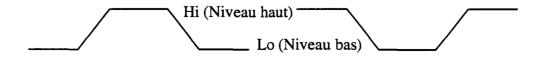

Une des conclusions à tirer de cette première analyse est que la caractérisation impulsionnelle doit être réalisée de façon à imposer au transistor un signal dont la fréquence est supérieure à 10 MHz. A ce titre nous rappelons que le fonctionnement en pulsé doit être représentatif de celui obtenu en radiofréquences.

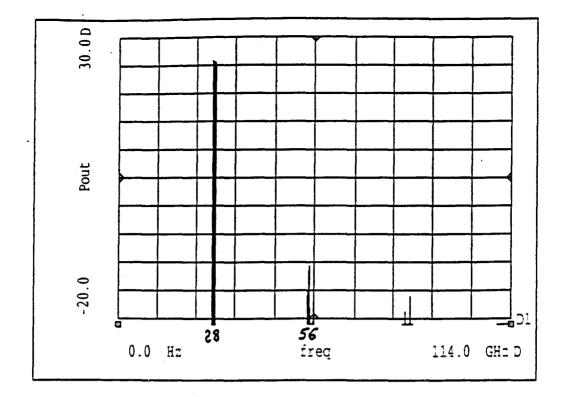

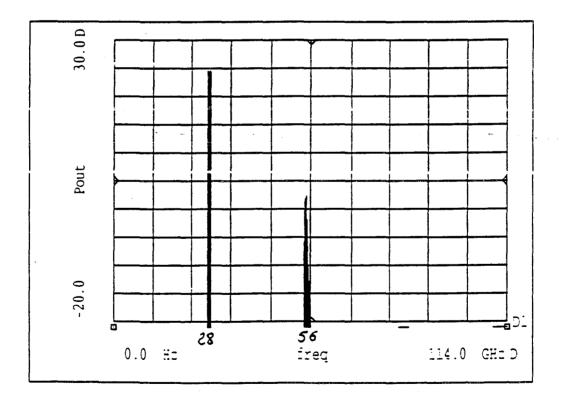

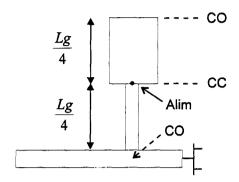

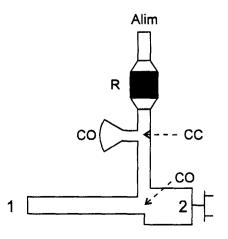

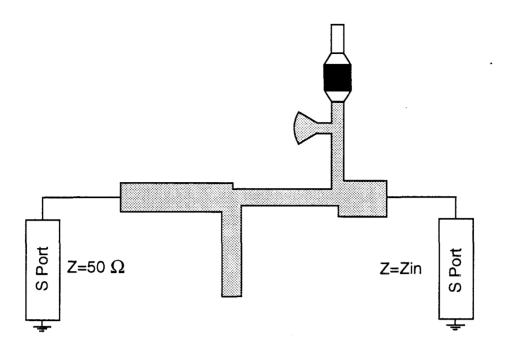

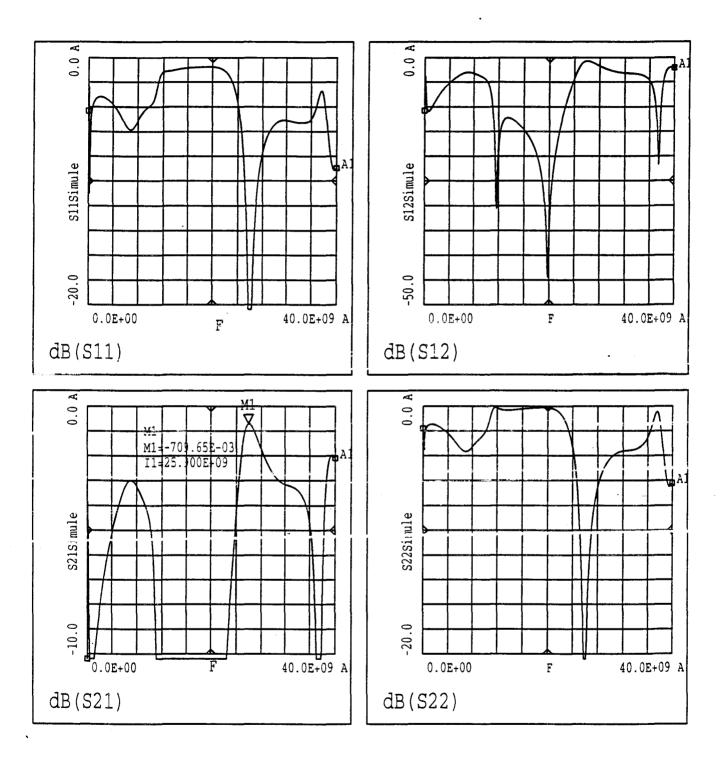

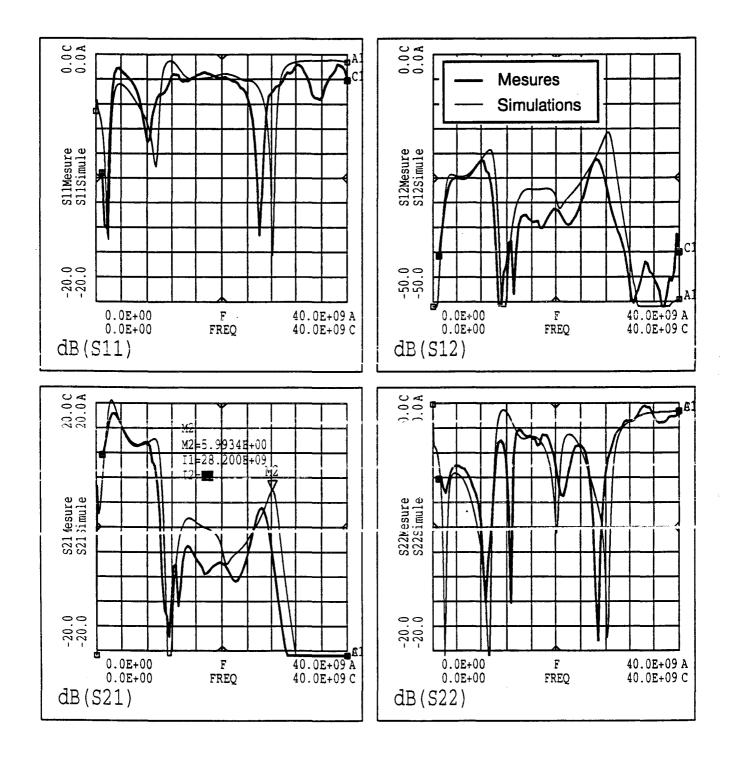

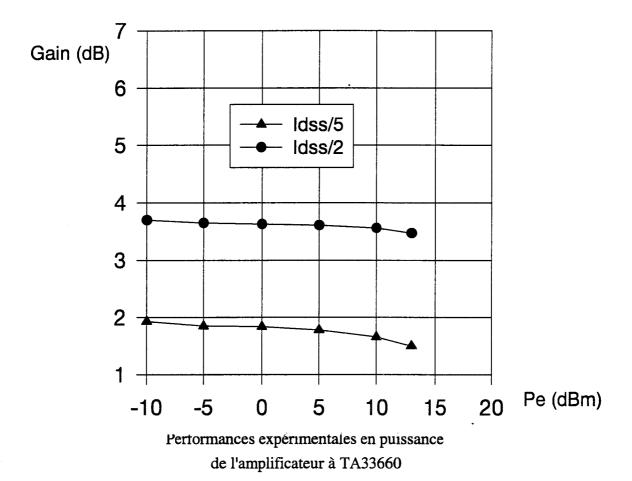

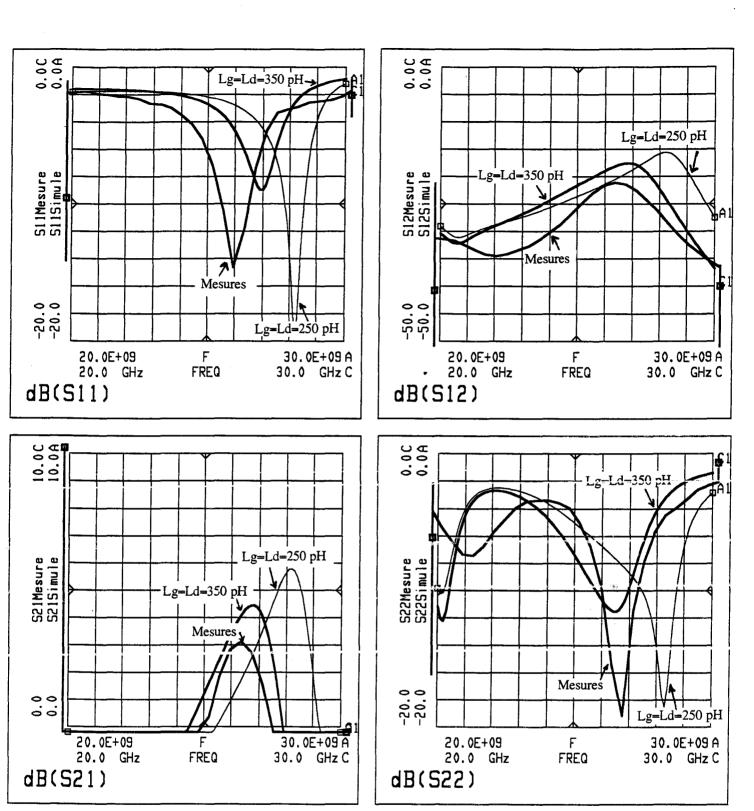

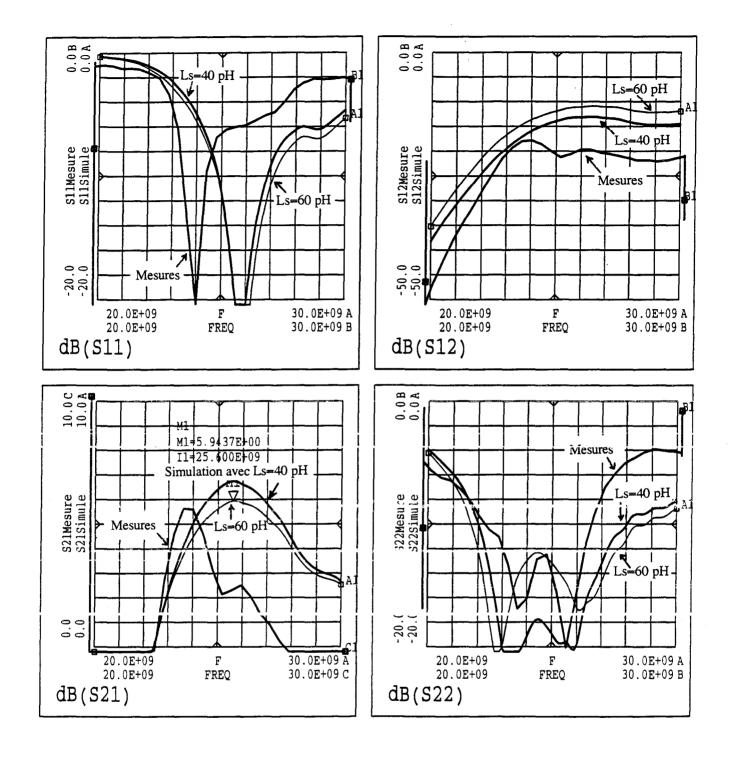

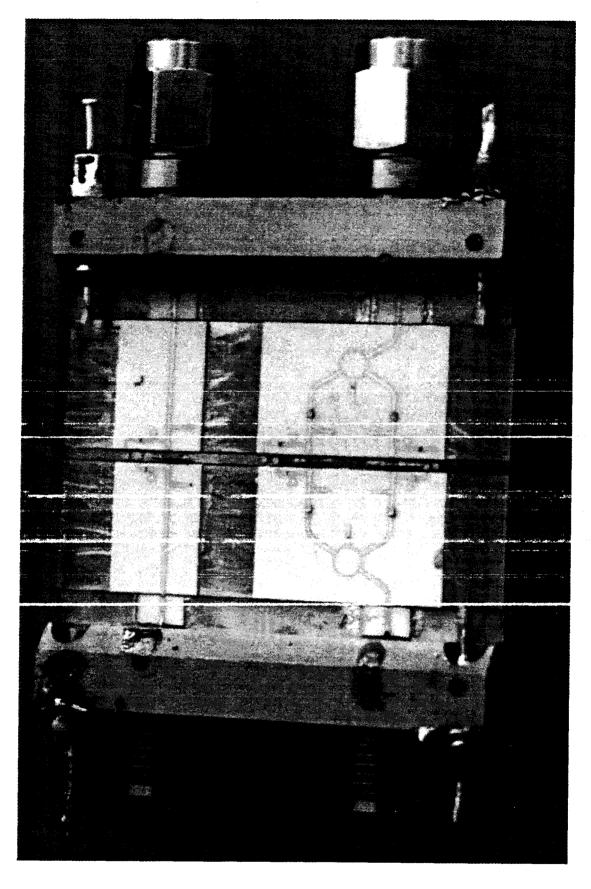

#### II-2.2.b.Influence de la polarisation du transistor sur les pièges