N° d'ordre: 1962

# THESE

intitulée

# "ETUDE DE MULTIPLICATEURS DE FREQUENCE A HEMT APPLICATION A UN TRIPLEUR 10-30 GHz"

Présentée à

# L'UNIVERSITE des SCIENCES et TECHNOLOGIES de LILLE

Soutenue le

04 février 1997 devant la commission d'examen

par

# **Christophe BROSTEAUX**

pour obtenir le titre de

# DOCTEUR de l'UNIVERSITE, spécialité ELECTRONIQUE

Membres du jury: MM.

G. SALMER Y. CROSNIER J. GRAFFEUIL

J.-L. GAUTIER C. TOLANT E. BERGEAULT P.A. ROLLAND Président

Directeur de thèse

Rapporteur Rapporteur examinateur examinateur

examinateur

# Sommaire

| INTRODUCTION GENERALE                                                                         | 1          |

|-----------------------------------------------------------------------------------------------|------------|

| CHAPITRE I ASPECTS FONDAMENTAUX DE LA MULTIPLICATION DE FREQUEN                               | CE ET      |

| ETAT DE L'ART                                                                                 | 3          |

| INTRODUCTION                                                                                  | 4          |

| I-A FONCTIONNEMENT DE BASE                                                                    |            |

| I-B CAS PRATIQUES DE TRAITEMENTS DES HARMONIQUES                                              |            |

| I-C ETAT DE L'ART                                                                             |            |

| CONCLUSION                                                                                    |            |

| BIBLIOGRAPHIE DU CHAPITRE I                                                                   |            |

| CHAPITRE II ETUDE ET OPTIMISATION DES PERFORMANCES D'UN TRIPLEUR                              |            |

| INTRODUCTION                                                                                  | 32         |

| II-A CARACTERISTIQUES ET MODELES DES TRANSISTORS UTILISES                                     | 33         |

| II-B CHOIX DE LA TECHNOLOGIE                                                                  |            |

| II-C ETUDE PRELIMINAIRE D'UN TRIPLEUR 12-36 GHZ                                               | 66         |

| II-D COMPARAISON DOUBLEUR 18-36 GHZ / TRIPLEUR 12-36 GHZ                                      | 72         |

| II-E SIMULATIONS D'UN TRIPLEUR 27-81 GHZ                                                      | 76         |

| II-F OPTIMISATION D'UN TRIPLEUR 10-30 GHZ ET PRISE EN COMPTE DES LIMITATIONS PHYSIQUES DU TRA | NSISTOR.82 |

| CONCLUSION                                                                                    | 89         |

| BIBLIOGRAPHIE DU CHAPITRE II                                                                  | 90         |

| CHAPITRE III CONCEPTION, REALISATION ET MESURES D'UN TRIPLEUR HY                              | RDINE      |

| 10-30 GHZ                                                                                     |            |

|                                                                                               |            |

| INTRODUCTION                                                                                  |            |

| III-A METHODOLOGIE DE CONCEPTION                                                              |            |

| III-B RECHERCHE DES TOPOLOGIES OPTIMALES DES CIRCUITS D'ENTREE ET DE SORTIE                   |            |

| III-C REALISATION ET TEST DES CIRCUITS                                                        |            |

| III-D MESURE DES TRIPLEURS REALISES                                                           |            |

| CONCLUSION                                                                                    |            |

| III-E MESURE DU BRUIT DE PHASE AJOUTE                                                         |            |

| BIBLIOGRAPHIE DU CHAPITRE III                                                                 | 153        |

| CONCLUSION GENERALE                                                                           | 155        |

| LISTE DES FIGURES                                                                             | 157        |

| LISTE DES TABLEAUX                                                                            | 162        |

| TABLE DES MATIERES                                                                            | 163        |

# Introduction générale

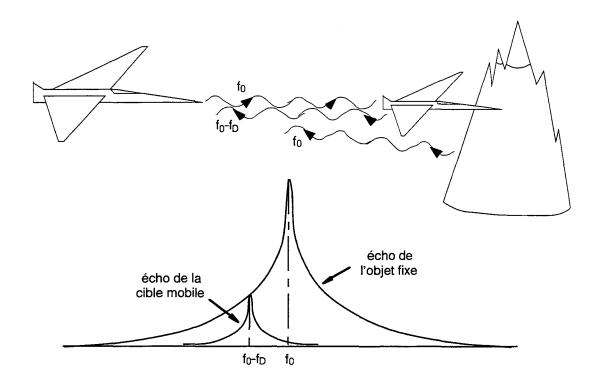

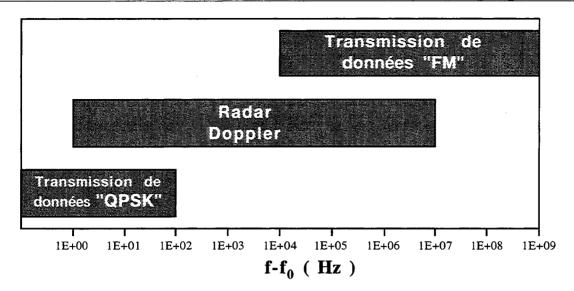

Principalement en raison de l'encombrement de l'espace Hertzien, des fréquences de plus en plus élevées doivent être employées pour les applications telles que : radars continus et pulsés, communications terrestres et inter satellite, radiomètrie, spectrométrie...

Les systèmes électroniques devant assurer ces fonctions doivent donc intégrer une source capable de délivrer un signal dans la gamme des longueurs d'ondes millimétriques.

Pour les applications mentionnées, cette source doit être le plus souvent très stable et pure. Or, la génération directe d'une onde millimétrique, à l'aide de diodes ou de transistors, ne permet d'obtenir que des sources ayant une stabilité et une pureté moyennes. Les synthétiseurs de fréquence à quartz et à boucle à verrouillage de phase, utilisés conjointement avec des multiplicateurs de fréquence, constituent actuellement la technique la plus répandue pour répondre aux exigences de qualité requises.

Les multiplicateurs de fréquence utilisés jusqu'à maintenant reposent sur l'emploi de diodes en tant qu'éléments non linéaires générateurs d'harmoniques. Ces dispositifs autorisent des rangs de multiplication élevés avec des rendements intéressants et des pertes de conversion raisonnables. Malheureusement, les circuits à diodes se prêtent peu à la réalisation de circuits intégrés micro-ondes (MMIC). Or, l'intégration complète de toutes les fonctions, y compris la multiplication de fréquence, est une condition indispensable pour diminuer significativement les coûts de production qui constituent un frein pour les applications grand public.

Des travaux ont donc, naturellement, été menés ces dernières années sur l'utilisation de transistors pour réaliser de la multiplication de fréquence. L'emploi de ces composants actifs doit conduire à l'obtention de circuits intégrés ayant un gain de conversion positif au lieu de pertes. Il est cependant apparu que les difficultés de mise en œuvre de ces circuits n'ont permis de réaliser des systèmes avec des performances utilisables pratiquement que dans le cas de doubleurs de fréquence.

Cette limitation restreint fortement l'utilisation de transistors en remplacement de diodes. L'étude et la réalisation de multiplicateurs de fréquences de rang plus élevé que deux et présentant un gain de

conversion constituent donc un sujet de recherche d'actualité. C'est pourquoi, une des tâches du projet Européen ESPRIT-5032 AIMS\*, dans lequel s'est trouvé engagé le laboratoire, consistait à étudier la faisabilité de tripleurs de fréquences performants à transistors fonctionnant dans le domaine des ondes millimétriques. La prise en charge par notre laboratoire de cette partie du projet a donc permis d'initier ce travail sur la multiplication de fréquence à transistors millimétriques.

Nous présentons, dans le premier chapitre de ce manuscrit, le principe de la multiplication de fréquence à transistor à effet de champ et les différentes techniques utilisables pour réaliser des doubleurs, tripleurs et quadrupleurs de fréquence. Un état de l'art de ce type de dispositifs est également réalisé.

Le deuxième chapitre comporte la présentation des modélisations non linéaires des différents transistors HEMTs utilisés dans cette étude, suivie de simulations de multiplicateurs de fréquence réalisées avec ces transistors dans des conditions opératoires idéalisées.

Les différents circuits ainsi simulés permettent d'étudier les points suivants :

- choix de la technologie de transistor à employer

- validité des modèles de transistor et des simulations

- intérêt du tripleur par rapport au doubleur

- potentialités de fonctionnement d'un tripleur en bande W.

Ce chapitre se termine avec l'étude et l'optimisation d'un circuit tripleur 10-30 GHz, prélude à la réalisation d'un démonstrateur en technologie hybride (MIC) qui fera l'objet du troisième chapitre

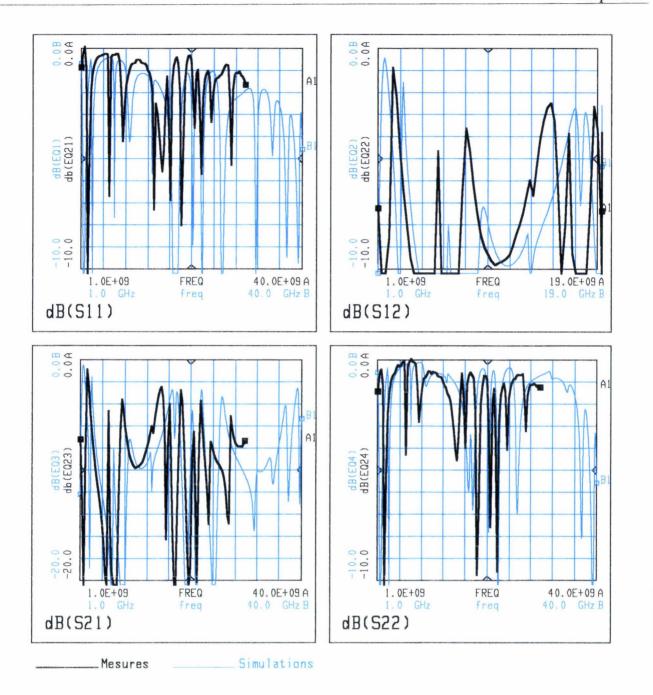

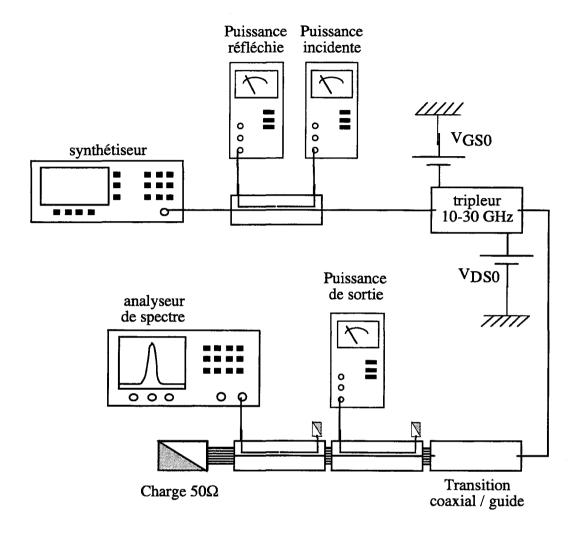

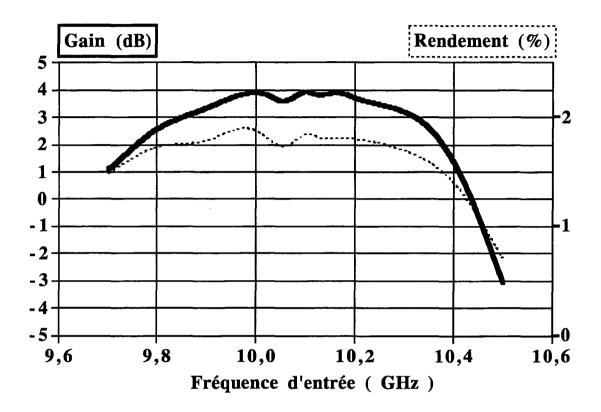

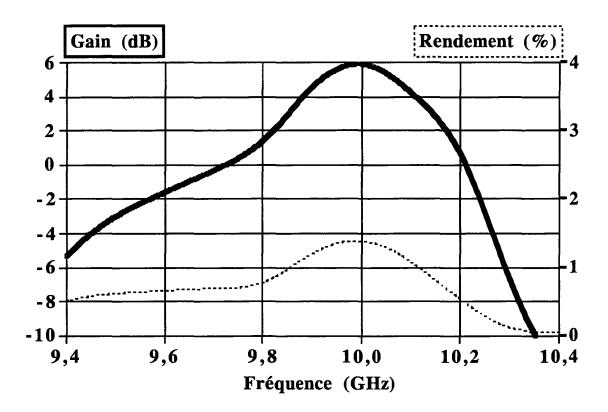

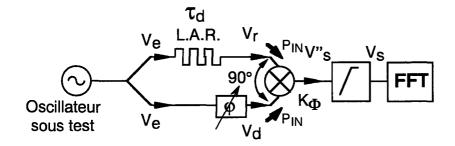

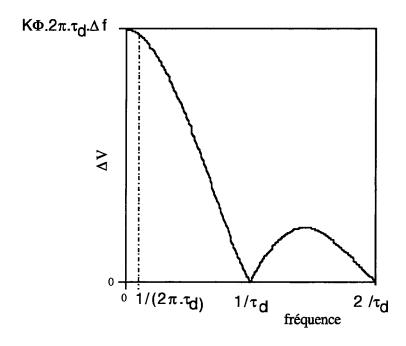

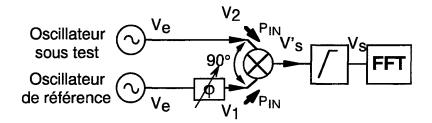

Enfin, le troisième chapitre présente, successivement, la conception, la réalisation et les mesures de ce circuit tripleur 10-30 GHz. Aux mesures de gain et de rendement de ce dispositif, nous avons également adjoint une étude expérimentale du bruit de phase ajouté afin d'estimer l'accroissement de bruit de phase que pourrait engendrer notre dispositif au niveau du signal de sortie. Cet aspect, bien que quelque peu à part du reste de l'étude, revêt un intérêt fondamental dans bien des applications et trouve sa justification dans la réputation des transistors à effet de champ de présenter un bruit de phase originel relativement important.

AIMS: Advanced Integrated Millimeter wave Sub-assemblies

<sup>\*</sup> ESPRIT: European community's Specific Programm for research and technology developpement in the field of Information Technologies

# chapitre I

Aspects fondamentaux de la multiplication de fréquence et état de l'art

## **Introduction**

Ce chapitre, après un rappel du principe de la multiplication de fréquence à transistor, examine les différentes techniques de mise en œuvre des doubleurs, tripleurs et quadrupleurs de fréquence.

La multiplication de fréquence à transistor a fait l'objet de nombreuses publications ces dernières années mais les principaux travaux ont concerné les doubleurs qui, jusqu'à ce jour, étaient les seuls à fournir un gain supérieur à un. Les pertes obtenues avec les circuits de multiplication de rang plus élevés ont limité leur développement. Le choix de leur utilisation, plutôt que celle de multiplicateurs à diode, ne pouvait donc être justifiable que dans le cas d'une intégration monolithique.

Pour situer les performances atteintes par les différents circuits de multiplication de fréquence, nous présentons également un état de l'art le plus exhaustif possible.

## I-A fonctionnement de base

#### I-A-1 Principe fondamental

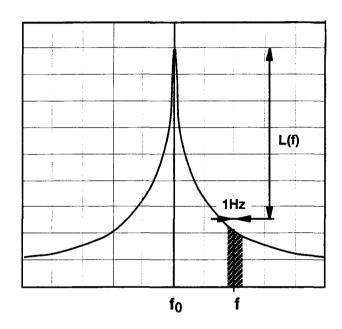

La multiplication de fréquence analogique est basée sur la génération d'une harmonique de rang n par un système non linéaire excité par un signal à une fréquence fondamentale f0.

La non linéarité peut être obtenue à l'aide de systèmes passifs ou actifs. Comme notre étude porte sur les systèmes actifs à transistor à effet de champ (TEC), nous n'exposerons par la suite que ce qui a trait à la multiplication de fréquence avec ce type de composant.

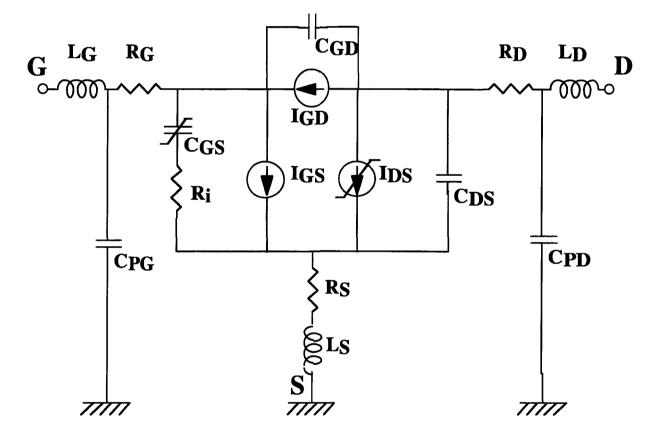

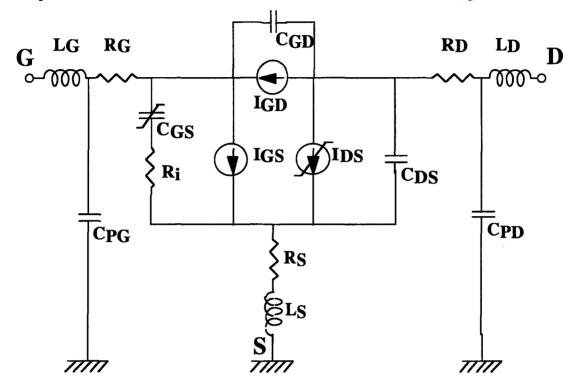

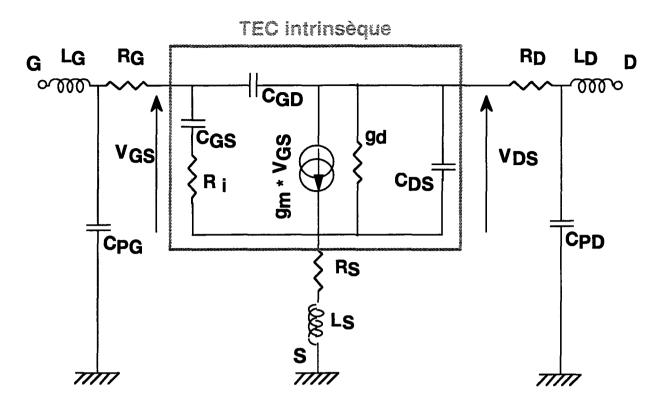

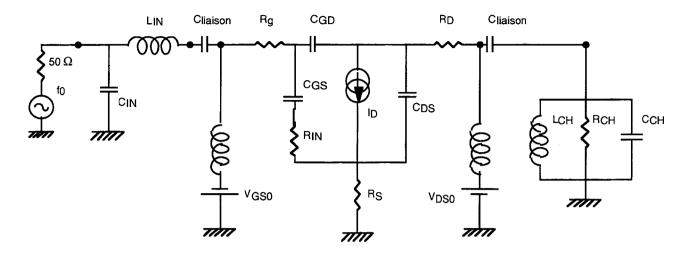

Le schéma équivalent du modèle non linéaire usuel du transistor est présenté figure I-1.

Figure I-1 : Schéma équivalent du TEC

Pour la multiplication de fréquence, la description du fonctionnement non linéaire du transistor peut être valablement limité aux deux éléments non linéaires CGS et IDS.

L'expérience a montré que la principale non linéarité génératrice d'harmoniques est celle liée au

générateur de courant commandé IDS=f(VGS,VDS). L'effet "varactor" que l'on pourrait escompter de la part de CGS demeure généralement du second ordre.

On peut alors considérer deux cas théoriques concernant ce générateur de courant :

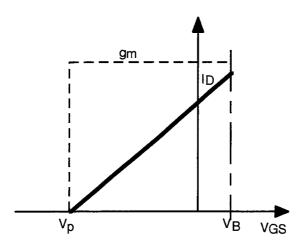

Figure I-2 : Cas 1 : Commande quasi-linéaire entre Vp et VB

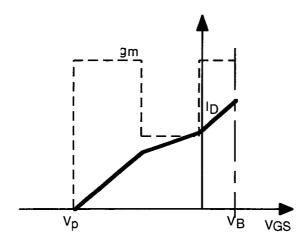

Figure I-3: Cas 2: Commande non-linéaire entre V<sub>p</sub> et V<sub>B</sub>

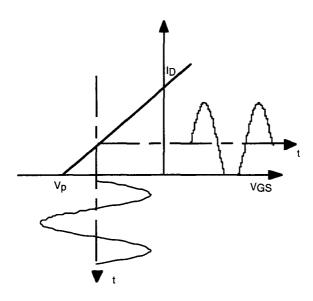

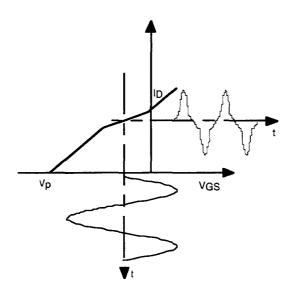

Dans le premier cas la source de courant peut être modélisée par un générateur IDS=f(VGS,VDS) ayant une réponse quasi-linéaire entre la tension Vp de pincement et la tension VB de mise en conduction directe de la diode grille-source (figure I-2). Il faut alors obligatoirement que le signal de commande balaye en dehors de cette zone linéaire pour obtenir des harmoniques : la tension VGS doit donc atteindre des valeurs inférieures à Vp (figure I-4).

Le deuxième cas est celui où la réponse du transistor présente des non linéarités importantes dans la zone Vp - VB(figure I-3). La réponse non linéaire du générateur de courant engendre, "naturellement", des harmoniques sans qu'il soit forcément nécessaire que le balayage de la tension VGS aille en dessous de la tension de pincement Vp (figure I-5).

Figure I-4: Création d'harmoniques dans le cas d'une commande quasi-linéaire

Figure I-5: Création d'harmoniques dans le cas d'une commande non linéaire

Ce cas d'importante non linéarité de la caractéristique ID(VGS), pour VGS comprise entre Vp et VB, ne peut être obtenu qu'exceptionnellement avec des structures de couches spéciales. Un exemple en a

été fourni par la réalisation, au laboratoire, de HEMTs double puits<sup>1</sup>. L'inconvénient de ce type de non linéarité est que son utilisation implique la présence d'un courant de repos important et que, par conséquent, le rendement ne peut être que très faible.

C'est la raison pour laquelle la non linéarité liée au pincement demeure actuellement le moyen le plus efficace d'obtenir de la multiplication de fréquence. Nous allons donc nous limiter uniquement à ce cas dans ce qui suit en développant ce que l'on peut attendre de l'influence de la polarisation

#### I-A-2 Choix de la polarisation

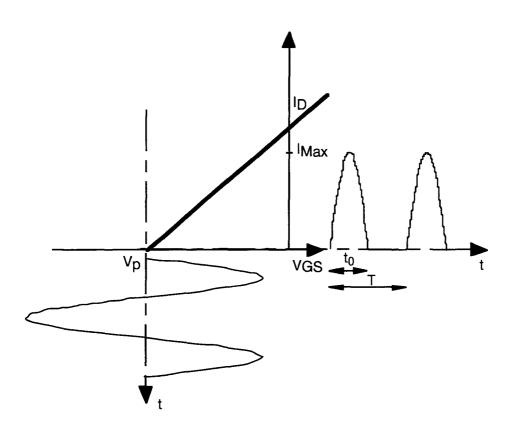

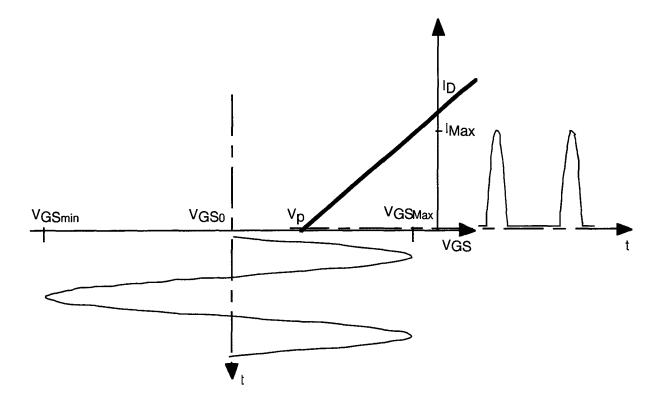

Lorsque la tension de polarisation VGS0 est inférieure à la tension Vp de pincement du transistor, on est en présence d'un redressement monoalternance où le temps de conduction t0 est lié à la valeur de VGS0 ( pour une amplitude donnée du signal d'entrée) : Si  $V_{GS_0} \approx V_p$ , alors  $\frac{t_0}{T} = \frac{1}{2}$  (figure I-6-a), par contre si  $V_{GS_0} < V_p$ , alors  $\frac{t_0}{T} < \frac{1}{2}$  (figure I-6-b).

Figure I-6-a: Polarisation du transistor à VGS0=Vp

Figure I-6-b: Polarisation du transistor à VGS0<Vp

Dans les deux cas, le signal Id(t) peut être décomposé en série de fourier<sup>2</sup> :

$$\begin{split} & Id(t) = I_0 + I_1 * cos(\omega_0 t) + I_2 * cos(\omega_1 t) + ... + I_n * cos(\omega_n t) \\ & A vec, pour : \end{split}$$

$$n = 0$$

:  $I_0 = I_{Max} * \frac{2}{\pi} * \frac{t_0}{T}$

• n \neq 0: quelque soit

$$\frac{t_0}{T} \neq \frac{1}{2n}$$

:  $I_n = I_{\text{Max}} * \frac{4}{\pi} * \frac{t_0}{T} * \left| \frac{\cos(n\pi \frac{t_0}{T})}{1 - (2n\frac{t_0}{T})^2} \right|$

quelque soit

$$\frac{t_0}{T} = \frac{1}{2n}$$

:  $I_n = I_{Max} * \frac{t_0}{T}$

Le courant  $I_{\it Max}$  représentant la valeur maximale du courant Id(t)

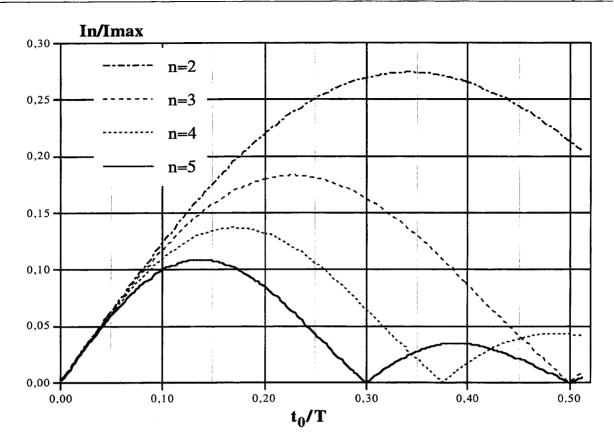

L'allure de la fonction  $\frac{I_n}{I_{Max}}$  est donnée figure I-7 pour n variant de 2 à 5.

Figure I-7: Valeurs du rapport In/Imax en fonction du temps d'ouverture pour différents rangs d'harmonique

Le tableau Ta.I-1 suivant présente les valeurs optimales de  $\frac{t_0}{T}$  permettant de maximaliser le rapport  $\frac{I_n}{I_{Max}}$  en fonction du rang n de l'harmonique recherchée.

| n                     | 2    | 3    | 4    | 5    |

|-----------------------|------|------|------|------|

| $\frac{t_0}{T}$       | 0,34 | 0,23 | 0,17 | 0,14 |

| $\frac{I_n}{I_{Max}}$ | 0,27 | 0,18 | 0,14 | 0,11 |

<u>Tableau Ta.I-1: Valeurs maximales du rapport In/Imax en fonction du temps d'ouverture pour différents rangs d'harmonique</u>

On peut alors calculer la tension de polarisation  $V_{GS_0}=\frac{V_{GS_{Max}}+V_{GS_{min}}}{2}$  et la tension  $V_{GS_{min}}$  en fonction de  $\theta_0=2\pi*\frac{t_0}{T}$ .

En effet, on a:

$$V_{GS_0} = V_p - \frac{V_{GS_{Max}} - V_{GS_{min}}}{2} * \sin(\frac{\pi}{2} - \frac{\theta_0}{2})$$

$$V_{GS_0} = V_p - \frac{V_{GS_{Max}} - V_{GS_{min}}}{2} * \cos(\frac{\theta_0}{2})$$

$$V_{GS_0} = V_p - (V_{GS_{Max}} - V_{GS_0}) * \cos(\frac{\theta_0}{2})$$

$$d'o : V_{GS_0} = \frac{V_p - V_{GS_{Max}} * \cos(\frac{\theta_0}{2})}{1 - \cos(\frac{\theta_0}{2})}$$

Par ailleurs, de la relation :

$$\frac{(V_{GS_{Max}} - V_{GS_{min}})}{2} * \cos(\frac{\theta_0}{2}) = V_p - V_{GS_0}$$

on tire:

$$V_{GS_{\min}} = \frac{V_{GS_0} * (1 + \cos(\frac{\theta_0}{2})) - V_p}{\cos(\frac{\theta_0}{2})}$$

Les limites d'utilisation des expressions de VGS0 et VGSmin sont fixées par le fait que, d'une part, VGSmax doit rester inférieur à VB (tension de mise en conduction en direct de la jonction grillesource), et que, d'autre part, VGSmin doit rester supérieure à VBR (tension de claquage de la jonction grille-drain).

La puissance disponible à la fréquence f<sub>n</sub> dans une résistance R<sub>L</sub> est :

$$P_n = R_L * \frac{I_n^2}{2}$$

$$\Rightarrow P_n = R_L * \frac{I_{Max}^2}{2} * \left(\frac{4}{\pi} * \frac{t_0}{T}\right)^2 * \left| \frac{\cos(n\pi \frac{t_0}{T})}{1 - (2n\frac{t_0}{T})^2} \right|^2$$

La puissance continue consommée PDC est :

$$P_{DC} = V_{DS_0} * I_0$$

$$\Rightarrow P_{DC} = \frac{2}{\pi} * \frac{t_0}{T} * I_{Max} * V_{DS_0}$$

Il importe de noter que les considérations précédentes sont basées sur une configuration théorique où le transistor est chargé par une résistance uniquement à la fréquence  $f_n$  retenue, toutes les autres composantes fréquentielles étant court-circuitées. Une autre hypothèse implicite est que la tension appliquée en entrée du transistor est purement sinusoïdale et donc que les harmoniques sont également court-circuitées en entrée.

Il s'agit de conditions opératoires idéales. Dans la réalité, on ne peut qu'approcher ces conditions. Pour arriver à ce résultat, plusieurs méthodes de traitement des harmoniques sont possibles :

- utilisation de filtres.

- utilisation de circuits à structure équilibrée,

- combinaison des deux.

Des choix technologiques doivent être fait suivant la bande passante, le gain, la puissance ou le rendement désirés.

Nous présentons maintenant quelques solutions possibles suivant le rang de multiplication recherché.

## I-B cas pratiques de traitements des harmoniques

#### I-B-1 Doubleur de fréquence

#### I-B-1-a Doubleur simple

Le plus souvent, dans la pratique, la configuration suivante (Figure I-8) est retenue pour la réalisation de doubleurs :

Figure I-8: Configuration de fonctionnement d'un TEC en doubleur

Le transistor est adapté en entrée et en sortie. Un stub, de longueur  $\frac{\lambda}{4}$  à f0, terminé par un circuit ouvert, est placé en sortie pour éliminer le fondamental<sup>3,4,5,6</sup>. Un autre, à 2f0, peut éventuellement être placé en entrée<sup>7,8</sup> pour court-circuiter le deuxième harmonique présent côté grille à cause de la capacité CGD qui n'est généralement pas négligeable.

En théorie, le courant en sortie du transistor a pour amplitude :

- dans le cas d'un redressement mono-alternance  $\left(\frac{t_0}{T} = \frac{1}{2}\right)$ :  $I_{2 \text{ théorique}} = I_{Max} * \frac{2}{3\pi} = I_{Max} * 0.21$

- dans le cas  $\frac{t_0}{T}=0,34$ , correspondant au maximum théorique que l'on puisse obtenir, on a :  $I_2_{th\acute{e}orique}=I_{Max}*0,27$

La tension de polarisation VGSO doit donc être inférieure à la tension de pincement du transistor.

Le principal avantage de ce doubleur est sa simplicité de mise en œuvre.

## I-B-1-b Doubleur équilibré

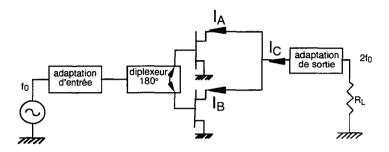

Le principe de ce doubleur est de sommer deux signaux électriques dont les composantes harmoniques indésirables sont en opposition de phase.

Figure I-9: Configuration de fonctionnement de TECs en doubleur équilibré

Figure I-10: Formes des courants dans un doubleur équilibré

Pour ce faire, comme le montre la figure I-9, un système diplexeur ayant des sorties déphasées de 180° à f0 est utilisé. Les deux signaux obtenus sont appliqués sur l'entrée de deux transistors polarisés en classe B (  $\frac{t_0}{T} = \frac{1}{2}$  ).

La somme des deux signaux de sortie des transistors correspond à un 'redressement double alternance' classique en électronique. Un tel signal a pour décomposition harmonique :

$$I_C(t) = I_{Max} * \left(\frac{2}{\pi} + \frac{4}{3\pi} * \cos(2\omega_0 t) - \frac{4}{15\pi} * \cos(4\omega_0 t) + \dots\right)$$

Les composantes impaires n'existent donc pas et la première harmonique à éliminer ( à 4f0) est déjà très atténuée.

Le déphasage de 180° est le plus souvent obtenu à l'aide d'un "rat-race" mais des coupleurs de Lange<sup>10</sup>, associés à des longueurs de lignes <sup>11, 3</sup>, peuvent être utilisés.

Ce type de doubleur permet de réaliser des montages compacts, sans "stub"<sup>3</sup>, avec une bonne réjection du fondamental.

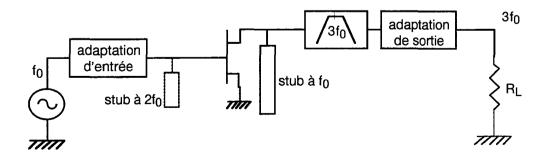

### I-B-2 Tripleur de fréquence

#### I-B-2-a Tripleur simple

L'étude de ce type de tripleur a constitué l'essentiel de notre travail. La simulation, la réalisation et la mesure d'un tripleur seront présentés aux chapitres II et III.

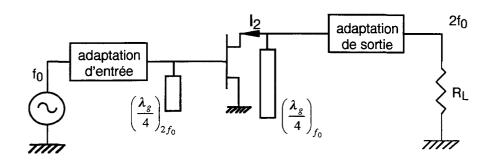

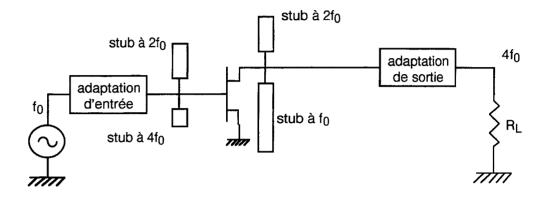

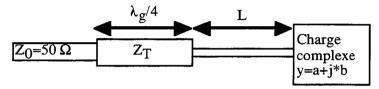

Le schéma, figure I-11, représente la configuration adoptée.

Figure I-11: Configuration de fonctionnement d'un TEC en tripleur simple

Le transistor est adapté en entrée. Sa sortie est filtrée et adaptée à la charge RL. Des "stubs" quart d'onde peuvent être placés en entrée<sup>12</sup> et en sortie avec, pour fréquences respectives de fonctionnement, 2f0 et f0.

Il est nécessaire de placer un filtre en sortie car il est impossible de rejeter correctement à la fois f0 et 2f0 avec des "stubs". Les solutions à passe-bande empêchent de transmettre à la charge R<sub>L</sub> les harmoniques f0, 2f0 et celles supérieures à 3f0. On garantit ainsi une meilleure pureté spectrale. Néanmoins, l'adaptation en sortie du transistor, nécessitant le traitement des trois harmoniques, constitue un problème très délicat. Celui-ci fait l'objet de notre étude dans le chapitre II.

Notons que, dans ce cas de fonctionnement en tripleur, la théorie indique que le transistor doit être polarisé à une tension très inférieure à sa tension de pincement (  $\frac{t_0}{T} = 0,23$  ). Cela implique l'utilisation de transistors ayant une tension élevée de claquage en inverse.

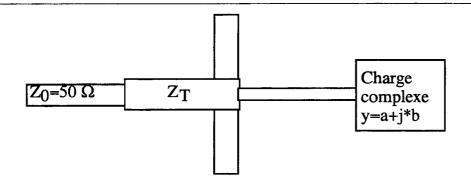

#### I-B-2-b Tripleur à charges dissipatives

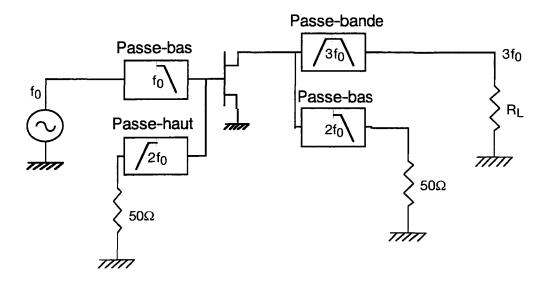

Figure I-12: Configuration de fonctionnement d'un TEC en tripleur à charges dissipatives

Ce montage (figure 12-I) devrait théoriquement permettre d'obtenir un tripleur ayant une bande passante relativement importante (20%).

Son principe consiste à aiguiller chaque harmonique vers des charges résistives en utilisant des filtres en entrée et en sortie du transistor. Ce principe de circuit, apparemment très simple, est en fait de réalisation difficile. Les performances connues et obtenues<sup>13</sup> à ce jour restent très modestes (gain de conversion de l'ordre de -10 dB en bande X).

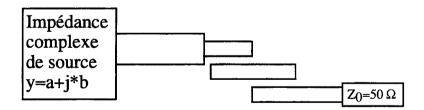

#### I-B-2-c Tripleur équilibré

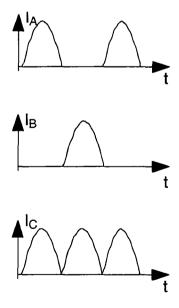

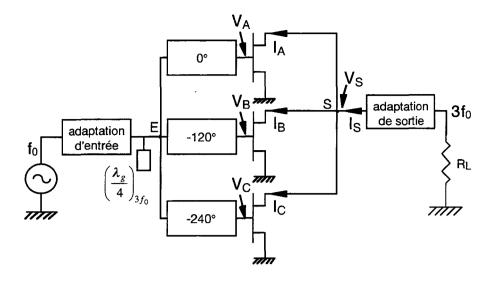

Ce montage (figure I-13) reprend le principe du moteur triphasé équilibré : la somme de trois signaux de même fréquence et de même amplitude mais déphasés de 120° est égale à zéro. Cela est vrai pour le fondamental et pour toutes les harmoniques différentes de  $k*3f_0$  quelque soit  $k \in \mathbb{N}^*$  au niveau du point S de recombinaison en sortie des transistors.

La démonstration mathématique est la suivante :

Soit  $\sum_n$ , la somme de trois signaux de fréquence  $n*f_0$   $(n \in N^*)$  ayant 0 et  $\pm n*\phi$  pour phases respectives.  $\sum_n = \cos(n*\omega t) + \cos(n*\omega t + n*\phi) + \cos(n*\omega t - n*\phi)$   $\sum_n = \cos(n*\omega t) + 2*\cos(n*\omega t)*\cos(n*\phi)$   $\sum_n = \cos(n*\omega t)*\left[1 + 2*\cos(n*\phi)\right]$  Quelque soit t,  $\sum_n = 0$  si  $\left[1 + 2\cos(n*\phi)\right] = 0$  ce qui est équivalent à :  $n*\phi = \pm \frac{2}{3}\pi + z*2\pi$   $(z \in N)$  si  $\phi = \frac{2}{3}\pi$ , on a :  $n = 3z \pm 1$  Donc, si n = 1,2,4,5,7,... :  $\sum_n = 0$  et si n = 3,6,9,... :  $\sum_n = 3*\cos(n*\omega t)$

Figure I-13: Configuration de fonctionnement de TECs en tripleur équilibré

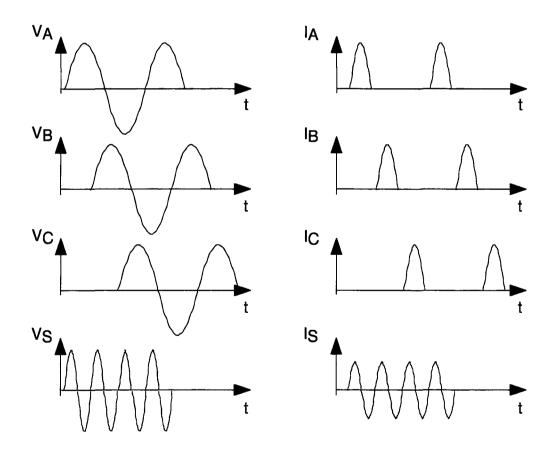

Figure I-14: Formes des tensions et des courants dans un tripleur équilibré

Dans le cas des multiples du troisième harmonique, les trois ondes s'ajoutent. Cette propriété, qui est généralement un inconvénient en électrotechnique<sup>14</sup>, est, par contre, un avantage lors de la réalisation

d'un tripleur de fréquence. Les principales formes d'ondes des tensions et des courants présents dans un tripleur équilibré sont présentées figure I-14 pour en illustrer le fonctionnement.

On peut remarquer que le phénomène d'annulation d'ondes se produit également en sens inverse, en amont des circuits déphaseurs, au niveau du point E. En effet, les harmoniques, générées par chaque transistor, se retrouvent sur les grilles de ceux-ci via leur capacité CGD. Dans l'hypothèse d'une réflexion identique en sortie des trois transistors, ces signaux reviennent au point E avec des déphasages respectifs de :

$$\begin{pmatrix} A^{\circ} \\ A-240^{\circ} \\ A-120^{\circ} \end{pmatrix} \text{ pour } f_{0}, \begin{pmatrix} B^{\circ} \\ B-120^{\circ} \\ B-240^{\circ} \end{pmatrix} \text{ pour } 2*f_{0}, \begin{pmatrix} C^{\circ} \\ C^{\circ} \\ C^{\circ} \end{pmatrix} \text{ pour } 3*f_{0}, \text{ etc...}$$

A, B, C étant des constantes

Le signal résultant au point E est nul pour les harmoniques de fréquence différente de  $k*3*f_0$ . Seules la composante  $3*f_0$  et ses multiples seront donc présents en entrée.

#### Le circuit est constitué:

- d'une adaptation en entrée à f0 et d'une en sortie à  $3*f_0$ ,

- d'un système de déphasage pouvant être réalisé par des longueurs de lignes,

- d'un éventuel "stub", de longueur  $\frac{\lambda}{4}$  à 3f0, terminé par un circuit ouvert ou bien d'un filtre passe-bas en entrée pour limiter le retour des harmoniques à  $k*3*f_0$  sur le générateur.

La présence des harmoniques  $(k+1)*3*f_0$  (6f0, 9f0, ...) en entrée ou en sortie est heureusement un problème d'ordre secondaire étant donné leur faible puissance due à la rapide décroissance des cœfficients de Fourier.

Remarquons, enfin, que ce type de fonctionnement en tripleur équilibré nécessite que les transistors soient polarisés en dessous du pincement comme dans le cas du tripleur simple.

A ce jour et à notre connaissance, cette structure n'a fait l'objet d'aucune réalisation ou étude prospective théorique.

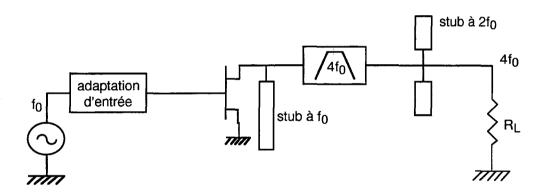

#### I-B-3 Quadrupleur de fréquence

Les réalisations de tripleurs à TEC sont déjà très rares, celles de quadrupleurs le sont encore d'avantage. Nous en présentons ci-dessous deux exemples très récents ayant fait l'objet d'une réalisation.

#### I-B-3-a Quadrupleur à transistor "unilatéral"

Dans ce premier cas<sup>15</sup>, l'hypothèse a été faite que le transistor est quasiment unilatéral et que, par conséquent, le retour d'harmoniques est supposé très faible. La figure I-15 illustre la configuration retenue.

Figure I-15: Première configuration de fonctionnement d'un TEC en quadrupleur

L'entrée ne comporte qu'un circuit d'adaptation.

En sortie, un "stub", de longueur  $\frac{\lambda}{4}$  à f0, court-circuite le fondamental et un filtre passe bande atténue la transmission des harmoniques indésirables dans la charge RL. Deux "stubs", de longueur  $\frac{\lambda}{4}$  à 2f0, sont également ajoutés pour augmenter la pureté spectrale.

#### I-B-3-b Quadrupleur à transistor "non-unilatéral"

Dans ce deuxième cas<sup>16</sup>, l'hypothèse d'unilatéralité n'a pas été retenue et un traitement des harmoniques a été introduit en entrée (figure I-16).

Figure I-16: Deuxième configuration de fonctionnement d'un TEC en quadrupleur

Sur celle-ci, en plus de l'adaptation à f0, deux "stubs", de longueur  $\frac{\lambda}{4}$  à 2f0 et à 4f0, court-circuitent les harmoniques 2f0 et 4f0.

La sortie comporte deux "stubs" de longueur  $\frac{\lambda}{4}$  à f0 et 2f0, qui court-circuitent le fondamental et le deuxième harmonique, ainsi qu'une adaptation à la charge RL pour l'harmonique 4f0 recherchée.

Dans les deux cas, la tension de polarisation VGS0 est choisie proche de la tension de pincement Vp du transistor (  $\frac{t_0}{T} \approx \frac{1}{2}$  et  $I_{4 \text{ th\'eorique}} \approx I_{Max} * 0,043$ ). On peut penser qu'une polarisation telle que  $\frac{t_0}{T} = 0,17$  impliquant  $I_{4 \text{ th\'eorique}} = I_{Max} * 0,14$  n'a pas été choisie pour des raisons de tenue en tension des composants.

Bien que peu performants en terme de gain, les systèmes quadrupleurs de fréquence sont à priori intéressants en remplacement d'une chaîne de deux doubleurs.

## I-C état de l'art

Toutes les publications connues et ayant fait l'objet de réalisations dans le domaine de la multiplication de fréquence à transistor sont regroupées dans le Tableau Ta.I-2.

Le graphique, figure I-17, situe les performances, en terme de gain de conversion des différentes réalisations en fonction de leur fréquence de sortie. Le type de multiplicateur (Doubleur, Doubleur équilibré, Tripleur ou Quadrupleur) et la technologie employée (Circuit intégré micro-ondes : M.I.C. ou Circuit intégré monolithique micro-ondes : M.M.I.C.) sont spécifiés pour chaque résultat.

Un résumé des principales indications fournies dans chaque publication est présenté dans le tableau Ta.I-3.

On constate immédiatement que ce sont les applications "doubleur de fréquence" qui ont fait l'objet de la plus part des travaux en multiplication de fréquence. Ce sont également celles-ci qui obtiennent les meilleurs performances en gain de conversion et en rendement.

Les travaux de ces dernières années (références 34, 74 et 99) semblent toutefois montrer la faisabilité de multiplicateurs de rang plus élevé ayant des caractéristiques potentiellement intéressantes. Même si les quadrupleurs ont encore des gain inférieurs à l'unité, notre contribution (référence 99) démontre la possibilité de réaliser des tripleurs de fréquence ayant un gain de conversion positif de plusieurs décibels.

| 1  | Soares Augusto, J.; Rosario, M.J.; Vaz, J.C.; Costa Freire, J. Optimal design of MESFET frequency multipliers 23rd European Microwave Conference Proceedings p. 402-4 vol.1                                                               |  |  |  |  |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 2  | Nassef, M.A. Computer simulation and design of non-linear microstrip 2.5 to 5 GHz frequency doubler Proceedings of the 35th Midwest Symposium on Circuits and Systems p. 643-6 vol.1                                                      |  |  |  |  |  |  |

| 3  | Angelov, I.M. Study of the output circuit influence on the efficiency of balanced FET doublers Bulgarian Journal of Physics Vol: 18 Iss: 4 p. 321-30 Date: 1991                                                                           |  |  |  |  |  |  |

| 4  | Angelov, I.M.; Stoev, I.K.; Spasov A.I. Balanced transistor frequency doublers Internationales Wissenschaftliches Kolloquium - technische hochschule ilmenau 1987 Vol.32 pp109-11                                                         |  |  |  |  |  |  |

| 5  | Shveshkeyev MESFET multiplier analyses and design Mikrowellen & HF Magazin.  Telecommunications Vol: 18 Iss: 6 p. 389-99 Date: Dec. 1992                                                                                                  |  |  |  |  |  |  |

| 6  | Henkus, J.C.; Overduin, R.; Koomen, P.J. A wideband tripler for X-band in microstrip Microwave Journal Vol: 36 Iss: 3 p. 106, 108-9, 111 Date: March 1993                                                                                 |  |  |  |  |  |  |

| 7  | Piloni, M.; Brambilla, M. MESFET frequency multipliers including detectorless ALC Conference<br>Proceedings. 22nd European Microwave Conference 92 p. 845-9 vol.2                                                                         |  |  |  |  |  |  |

| 8  | Le, D.L.; Ghannouchi, F.M.; Bosisio, R.G. A novel approach for designing GaAs FET frequency multipliers with optimum conversion gain and power efficiency Microwave and Optical Technology Letters Vol: 5 Iss: 9 p. 403-8 Date: Aug. 1992 |  |  |  |  |  |  |

| 9  | Khanna, A.P.S.; Creamer, C.; Topacio, E. A 45 GHz highly stable +15 dBm low noise GaAs MESFET source using a GaAs PHEMT as a frequency doubler Microwave Journal Vol: 34 Iss: 11 p. 117-18, 121, 125-7 Date: Nov. 1991                    |  |  |  |  |  |  |

| 11 | Lott, U. Low-loss MESFET frequency quadrupler from 5 to 20 GHz Conference Proceedings. 21st European Microwave Conference, Microwave '91 p. 1502-7                                                                                        |  |  |  |  |  |  |

| 16 | Iyama, Y.; Iida, A.; Takagi, T.; Urasaki, S. Second-harmonic reflector type high-gain FET frequency doubler operating in K-band IEEE 1989 MTT-S International Microwave Symp Digest p. 1291-4 vol.3                                       |  |  |  |  |  |  |

| 18 | Creamer, C.; Chye, P.; Sinclair, B. 43.5 to 45.5 GHz active times-4 frequency multiplier with 1.4 Watt output power 1991 IEEE MTT-S International Microwave Symposium Digest p: 939-42 vol.3                                              |  |  |  |  |  |  |

| 19 | Kondoh, H.; Cognata, A. A 20-50 GHz MMIC amplifier with 21 dBm output power and its application as a frequency doubler IEEE 1993 Microwave and Millimeter-Wave Monolithic Circuits Symposium. Digest of Papers p: 35-8                    |  |  |  |  |  |  |

<u>Tableau Ta.I- 2 : Correspondance entre les références-de l'état de l'art et les articles</u>

<u>bibliographiques</u>

| 20 | Kato, H.; Ohira, T.; Ishitsuka, F.; Tokumitsu, T.; Kihata, Y.; Imai, N. A 30 GHz MMIC receiver for satellite transponders IEEE Transactions on Microwave Theory and Techniques Vol. 38 Iss: 7 p. 896-903 Date: July 1990                                                        |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21 | Chow, P.D.; Hwang, Y.; Garske, D.; Velebir, J.; Yen, H.C. A 44-GHz HEMT doubler/amplifier chain 1990 IEEE MTT-S International Microwave Symposium Digest p: 603-6 vol.1                                                                                                         |

| 22 | Ogawa, K.; Ishizaki, T.; Hashimoto, K.; Sakakura, M.; Uwano, T. A 50 GHz GaAs FET MIC transmitter/receiver using hermetic miniature probe transitions IEEE Transactions on Microwave Theory and Techniques Vol: 37 Iss: 9 p: 1434-41 Date: Sept. 1989                           |

| 24 | Abdo-Tuko, M.; Bertenburg, R.; Wolff, L. A balanced Ka-Band GaAs FET MMIC frequency doubler IEEE Microwave and Guided Wave Letters Vol: 4 Iss: 7 p: 217-19 Date: July 1994                                                                                                      |

| 25 | Angelov, I.; Zirath, H.; Rorsman, N.; Gronqvist, H. A balanced millimeter wave doubler based on pseudomorphic HEMTs 1992 IEEE MTT-S International Microwave Symposium Digest p: 353-6 vol.1                                                                                     |

| 27 | Kwon, Y.; Pavlidis, D.; Marsh, P.; Ng, G.I.; Brock, T.; Munns, G.; Haddad, G.I. A fully integrated monolithic D-band oscillator-doubler chain using InP-based HEMTs GaAs IC Symposium. 14th Annual IEEE Gallium Arsenide Integrated Circuit Symposium Technical Digest p: 51-4  |

| 28 | Hiraoka, T.; Tokumitsu, T.; Akaike, M. A minaturized broad-band MMIC frequency doubler IEEE Transactions on Microwave Theory and Techniques Vol: 38 Iss: 12 p: 1932-7 Date: Dec. 1990                                                                                           |

| 30 | Takenaka, T.; Ogawa, H. An ultra-wideband MMIC balanced frequency doubler using line-unified HEMTs IEEE Transactions on Microwave Theory and Techniques Vol: 40 Iss: 10 p: 1935-40 Date: Oct. 1992                                                                              |

| 31 | Lester, J.A.; Jones, W.L.; Huang, P.; Garske, D.; Chow, P.D. High performance HEMT MMICs for low cost EHF SATCOM terminals IEEE 1992 Microwave and Millimeter-Wave Monolithic Circuits Symposium. Digest of Papers p: 113-16                                                    |

| 34 | Huei Wang; Chang, K.W.; Lo, D.C.W.; Tan, K.L.; Streit, D.; Dow, G.S.; Allen, B.R. Monolithic 23.5 to 94 GHz frequency quadrupler using 0.1 mu m pseudomorphic AlGaAs/InGaAs/GaAs HEMT technology IEEE Microwave and Guided Wave Letters Vol. 4 Iss: 3 p: 77-9 Date: March 1994  |

| 35 | Huei Wang; Yatsun Hwang; Shaw, L.; Ahmadi, M.; Siddiqui, M.; Monolithic V-band frequency converter chip set development using 0.2 mu m AlGaAs/InGaAs/GaAs pseudomorphic HEMT technology Transactions on Microwave Theory and Techniques Vol: 42 Iss: 1 p: 11-17 Date: Jan. 1994 |

<u>Tableau Ta.I- 2 (suite) : Correspondance entre les références-de l'état de l'art et les articles</u>

<u>bibliographiques</u>

| 36 | Abdo-Tuko, M.; Naghed, M.; Wolff, I. Novel 18/36 GHz (M)MIC GaAs FET frequency doublers in CPW-techniques under the consideration of the effects of coplanar discontinuities IEEE Transactions on Microwave Theory and Techniques Vol: 41 Iss: 8 p: 1307-15 Date: Aug. 1993 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38 | Guo, C.; Ngoya, E.; Quere, R.; Camiade, M.; Obregon, J. Optimal CAD MESFETs frequency multipliers with and without feedback 1988 IEEE MTT International Microwave Symposium Digest p: 1115-18 vol.2                                                                         |

| 41 | Hirota, T.; Ogawa, H. Uniplanar monolithic frequency doublers IEEE Transactions on Microwave Theory and Techniques Vol: 37 Iss: 8 p: 1249-54 Date: Aug. 1989                                                                                                                |

| 44 | Funabashi, M.; Inoue, T.; Ohata, K.; Maruhashi, K.; Hosoya, K.; Kuzuhara, M.; Kanekawa, K.; Kobayashi, Y. A 60 GHz MMIC stabilized frequency source composed of a 30 GHz DRO and a doubler 1995 IEEE MTT-S International Microwave Symposium Digest Part vol.1 p.71-4       |

| 51 | CAD review: the 7 GHz doubler circuit Journal: Microwave Engineering Europe p.43-4, 47-8, 53 Publication Date: May 1994                                                                                                                                                     |

| 57 | Boch, E. A High Efficiency 40 GHz Power FET Frequency Doubler MicrowaveJournal, August89 p154-8                                                                                                                                                                             |

| 58 | DBS Microwave Inc. Low Cost Front-ends for Digital Radio Microwave Journal, July 1995                                                                                                                                                                                       |

| 59 | Dougherty, R.M. A Design Method for FET Applications Microwave Journal, September 1993                                                                                                                                                                                      |

| 62 | Cordier, C.; Gamand, P. Doubleur de fréquence 28 GHz / 56 GHz Neuvièmes journées Nationales Microondes Avril 1995 p5D12                                                                                                                                                     |

| 71 | Lê, D.L.; Ghannouchi, F.M.; Bosisio, R.G. Conception optimale d'un GaAs FET tripleur de fréquence 2.5 @ 7.5 GHz Canadian aeronautcs and space journal, 1991, Vol.37, No.3, pp134-8                                                                                          |

| 73 | Zhang, G.; Pollard, R.D.; Snowden, C.M. A nove technique for HEMT tripler design IEEE MTT-S Digest 1996, WE2E-5, pp663-6                                                                                                                                                    |

| 74 | Shirakawa, K.; Kawasaki, Y.; Ohashi, Y.; Okubo, N. A 15/60 GHz one-stage MMIC frequency quadrupler IEEE 1996 Microwave and mm-wave Monolithic Circuits Symposium                                                                                                            |

| 75 | Shirakawa, K.; Shimizu, M.; Kawasaki, Y.; Ohashi, Y.; Okubo, N. A new empirical large-signal HEMT model IEEE MTT Vol.44, No.4, April 1996                                                                                                                                   |

| 99 | Brosteaux ; Crosnier A high performance Ka band P-HEMT MIC tripler ; à paraître                                                                                                                                                                                             |

Tableau Ta.I- 2 (suite) : Correspondance entre les références-de l'état de l'art et les articles bibliographiques

| N° ChB | Année | Туре | f sortie (GHz) | Transistor | Techno | G (dB) | Pout(dBm) | Rendement(%) |

|--------|-------|------|----------------|------------|--------|--------|-----------|--------------|

| 1      | 93    | D    | 10             | MESFET     | MIC    | 6      | 8         |              |

| 2      | 92    | D    | 5              | MESFET     | MIC    | 5      |           |              |

| 3      | 91    | DE   | 3              | MESFET     | MIC    | 1,5    | 12        | 5            |

| 4      | 88    | DE   | 2,4            | BIPOLAIRE  | MIC    | 0      | . 13      |              |

| 5      | 92    | D    | 9              | MESFET     | MIC    | -3     |           |              |

| 6      | 93    | T    | 9,3            | MESFET     | MIC    | -10    | 0         | 1            |

| 7      | 92    | D    | 24             | MESFET     | MIC    | -4     | 8         |              |

| 8      | 92    | Т    | 7,5            | FET        | MIC    | -2,4   | 1,6       | 10,5         |

| 9      | 91    | D    | 45             | PHEMT      | MIC    | -6     | 7         |              |

| 11     | 91    | Q    | 20             | MESFET     | MIC    | -6,5   | -5,5      | 0,44         |

| 16     | 89    | D    | 24             | FET        | MIC    | 6      | 13        |              |

| 18     | 91    | Q    | 44,5           | PHEMT      | MMIC   | -21    | -1        |              |

| 19     | 93    | D    | 50             | PHEMT      | MMIC   | -5     | 10        |              |

| 20     | 90    | D    | 30             | MESFET     | MMIC   | -6     |           |              |

| 21     | 90    | D    | 44             | HEMT       | MIC    | -1,4   | 0,4       |              |

| 22     | 89    | D    | 50             | FET        | MIC    | -2,6   | 4         |              |

| 24     | 94    | DE   | 36             | FET        | MMIC   | 3      | 5         |              |

| 25     | 92    | DE   | 42             | HEMT       | MIC    | -1     | 4         |              |

| 27     | 92    | D    | 132            | Hemt InP   | MMIC   | -10    | -12       |              |

| 28     | 90    | DE   | 10             | FET        | MMIC   | -8     | 2         | 3            |

| 30     | 92    | DE   | 40             | HEMT       | MMIC   | -9     | -3        | 0,5          |

| 31     | 92    | D    | 44             | PHEMT      | MMIC   | -4     | 5         |              |

| 34     | 94    | Q    | 94             | PHEMT      | MMIC   | -6     | -1        |              |

| 35     | 94    | D    | 54             | PHEMT      | MMIC   | 0      | 10        |              |

| 36     | 93    | DE   | 36             | FET        | MMIC   | 6      | 10        |              |

| 38     | 88    | D    | 20             | MESFET     | MIC    | 2      | 16        |              |

| 41     | 89    | DE   | 26             | FET        | MMIC   | -4     | 6         |              |

| 44     | 95    | D    | 60             | FET        | MMIC   | 0      | 7         |              |

| 51     | 94    | D    | 14             | FET        | MIC    | 3      | 10        |              |

| 57     | 89    | D    | 40             | FET        | MIC    | -6     | 12        | 25           |

| 58     | 95    | Т    | 39             | FET        | MMIC   | -4     |           |              |

| 59     | 93    | D    | 1,85           | MESFET     | MIC    | 3      | 9         |              |

| 62     | 95    | D    | 56             | HEMT       | MMIC   | 8      | 5,5       |              |

| 71     | 91    | Т    | 7,5            | FET        | MIC    | -3     | 2         | 10           |

| 73     | 96    | Т    | 34,5           | HEMT       | MIC    | -9     | -9        |              |

| 74     | 96    | Q    | 60             | HEMT       | MMIC   | -5,2   | -5        |              |

| 75     | 96    | D    | 60             | HEMT       | MMIC   | -4,8   | -5        | _            |

| 99     | 96    | Т    | 30             | PHEMT      | MIC    | 4      | 4         | 6            |

Légende : D : Doubleur, DE : Doubleur équilibré, T : Tripleur, Q : Quadrupleur

Tableau Ta.I- 3: Résumé des caractéristiques des multiplicateurs des références citées

### **Conclusion**

Ce premier chapitre nous a permis d'exposer le principe de la multiplication de fréquence à transistor en fonction des non linéarités des composants utilisés et en fonction des polarisations appliquées.

Nous avons ensuite décrit les différentes solutions pratiques pouvant être appliquées pour réaliser des multiplicateurs de fréquence. Cela nous permet de prendre conscience des principales contraintes et difficultés liées à la conception de chaque type de multiplicateur.

L'état de l'art que nous avons dressé met en évidence les piètres performances des tripleurs et quadrupleurs. Ces derniers ont, au mieux, des pertes de 2,4 et 5,2 dB respectivement. Pour ce qui est des doubleurs, leur gain peut atteindre 8 dB, ce qui explique leur position prédominante en multiplication de fréquence à transistor.

Notre travail, présenté dans les chapitres suivants, consiste à montrer qu'une étude rigoureuse peut permettre d'atteindre, en tripleur de fréquence à transistor, des performances quasi comparables à celles obtenues actuellement en doubleur de fréquence.

# Bibliographie du chapitre I

1 Théron, D.; Bonte, B.; Gaquière, C.; Playez, E.; Crosnier, Y.

Characterization of GaAs and InGaAs Double-Quantum Well Heterostructure FET's IEEE Transactions on Electron Devices Vol: 40 No.11 p: 1935-41 Date: November 1993

"Nonlinear Microwave Circuits", Artech HouseNorwood, MA, 1988

<sup>3</sup> Abdo-Tuko, M.; Naghed, M.; Wolff, I.

Novel 18/36 GHz (M)MIC GaAs FET frequency doublers in CPW-techniques under the consideration of the effects of coplanar discontinuities IEEE Transactions on Microwave Theory and Techniques Vol: 41 Iss: 8 p: 1307-15 Date: Aug. 1993

<sup>4</sup> Khanna, A.P.S.; Creamer, C.; Topacio, E.

A 45 GHz highly stable +15 dBm low noise GaAs MESFET source using a GaAs PHEMT as a frequency doubler Microwave Journal Vol: 34 Iss: 11 p. 117-18, 121, 125-7 Date: Nov. 1991

<sup>5</sup> Chow, P.D.; Hwang, Y.; Garske, D.; Velebir, J.; Yen, H.C.

A 44-GHz HEMT doubler/amplifier chain 1990 IEEE MTT-S International Microwave Symposium Digest (Cat. No.90CH2848-0) p: 603-6 vol.1 Publisher: IEEE New York, NY, USA Date: 1990 3 vol. 1371 pp.

<sup>6</sup> Ogawa, K.; Ishizaki, T.; Hashimoto, K.; Sakakura, M.; Uwano, T.

A 50 GHz GaAs FET MIC transmitter/receiver using hermetic miniature probe transitions IEEE Transactions on Microwave Theory and Techniques Vol: 37 Iss: 9 p. 1434-41 Date: Sept. 1989

<sup>7</sup> Soares Augusto, J.; Rosario, M.J.; Vaz, J.C.; Costa Freire, J.

Optimal design of MESFET frequency multipliers 23rd European Microwave Conference Proceedings p. 402-4 vol.1 Publisher: Reed Exhibition Companies Tunbridge Wells, UK Date: 1993 2 vol.(xxii+1021+x+134 pp.)

<sup>8</sup> Iyama, Y.; Iida, A.; Takagi, T.; Urasaki, S.

Second-harmonic reflector type high-gain FET frequency doubler operating in K-band IEEE 1989 MTT-S International Microwave Symposium Digest (Cat. No.89CH2725-0) p. 1291-4 vol.3

<sup>9</sup> I. M. Angelov, I. K. Stoev,

"Balanced transistor frequency doublers", International Wissenschaftliches Kolloquium, Vol. 32, pp 109-111, 1987.

<sup>10</sup> J.Rogers, R.Bhatia,

"A 6 to 20 GHz planar balun using a Wilkinson divider and a Lange coupler", 1991 IEEE MTT-S International Microwave Symposium Digest (Cat. No.91CH2870-4) p: 865-8 Date: 1991

<sup>&</sup>lt;sup>2</sup> S.A.MAAS

A balanced Ka-Band GaAs FET MMIC frequency doubler IEEE Microwave and Guided Wave Letters Vol: 4 Iss: 7 p: 217-19 Date: July 1994

A novel approach for designing GaAs FET frequency multipliers with optimum conversion gain and power efficiency Microwave and Optical Technology Letters Vol: 5 Iss: 9 p. 403-8 Date: Aug. 1992

A wideband tripler for X-band in microstrip Microwave Journal Vol. 36 Iss. 3 p. 106, 108-9, 111 Date: March 1993

Low-loss MESFET frequency quadrupler from 5 to 20 GHz Conference Proceedings. 21st European Microwave Conference, Microwave '91 p. 1502-7

One-Stage MMIC Frequency Quadrupler IEEE 1996 Millimeter-Wave Monolithic Circuits Symposium p. 35-38 III-1

<sup>&</sup>lt;sup>11</sup> Abdo-Tuko, M.; Bertenburg, R.; Wolff, L.

<sup>&</sup>lt;sup>12</sup> Le, D.L.; Ghannouchi, F.M.; Bosisio, R.G.

<sup>&</sup>lt;sup>13</sup> Henkus, J.C.; Overduin, R.; Koomen, P.J.

<sup>&</sup>lt;sup>14</sup> "Un harmonique 3 encombrant", Electronique International Hebdo N°218, 4 avril 1996.

<sup>15</sup> Lott. U.

<sup>&</sup>lt;sup>16</sup> Shirakawa, K. A 15/60

# chapitre II

étude et optimisation des performances d'un tripleur

### introduction

Dans le cadre du contrat Européen ESPRIT-5032 AIMS, nous devions montrer la faisabilité et l'intérêt de tripleurs de fréquences à transistor délivrant des fréquences dans la bande W. Pour ce faire, nous avons procédé par étapes :

- 1) Choix de la technologie à employer : Comme nous l'avons montré dans le chapitre I ( I-

- 1-1 : principe fondamental ), il existe essentiellement deux façons de commander le générateur de courant particulaire de drain, pour obtenir des harmoniques, suivant que la réponse de ce générateur est quasi linéaire ou bien non-linéaire.

Des simulations ont été réalisées en se basant sur des composants présentant ces deux types de comportements pour comparer les potentialités de chaque solution. Les résultats de cette étude sont présentés dans la partie II-B.

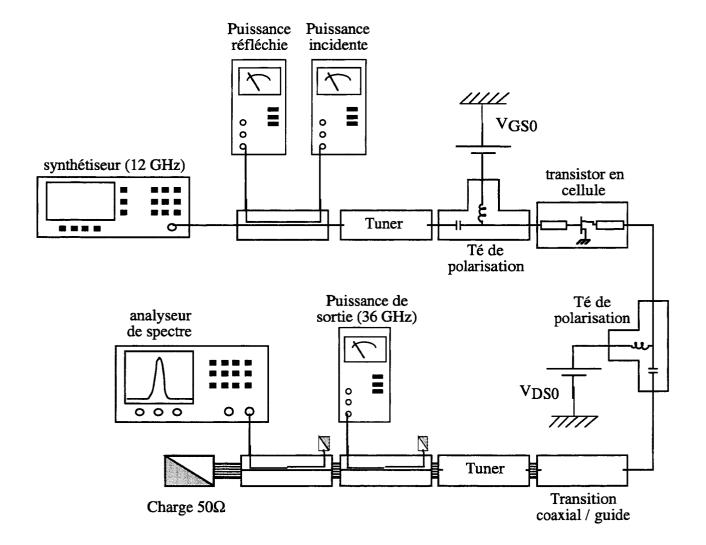

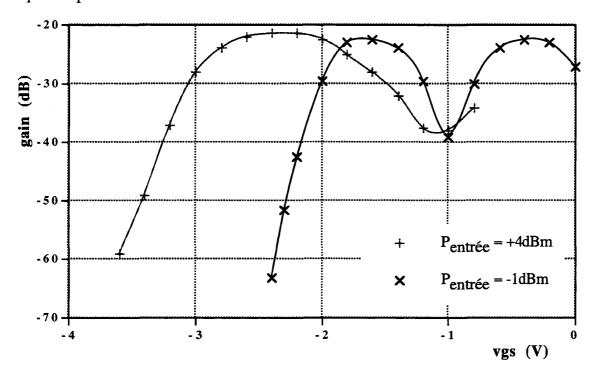

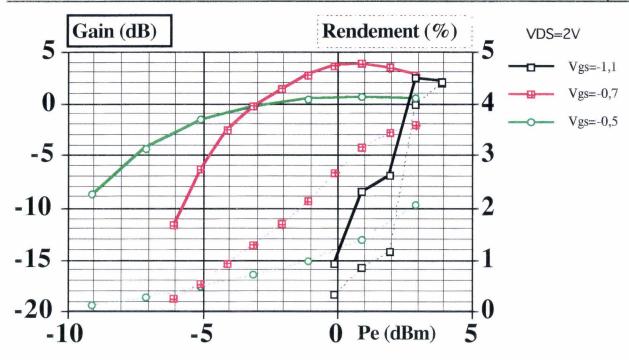

- 2) Étude préliminaire d'un tripleur 12-36 GHz : La partie II-C présente à la fois des résultats de simulation utilisant un transistor FUJITSU (FHX04) et des mesures réalisées à l'aide d'un banc de table sur ce même composant. Les manipulations ont permis d'étayer les simulations en montrant des réponses similaires.

- 3) Comparaison du fonctionnement en doubleur 18-36 GHz et en tripleur 12-36 GHz d'un même transistor : Pour prouver l'intérêt du tripleur par rapport au doubleur, nous avons réalisé, dans la partie II-D, les deux types de simulation en employant le même transistor.

- 4) Simulation d'un tripleur 27-81 GHz: Nous avons simulé le fonctionnement en tripleur de fréquences de deux transistors différents dans plusieurs configurations différentes. La partie II-E précise ces configurations et présente les performances que l'on peut atteindre à ces fréquences de fonctionnement.

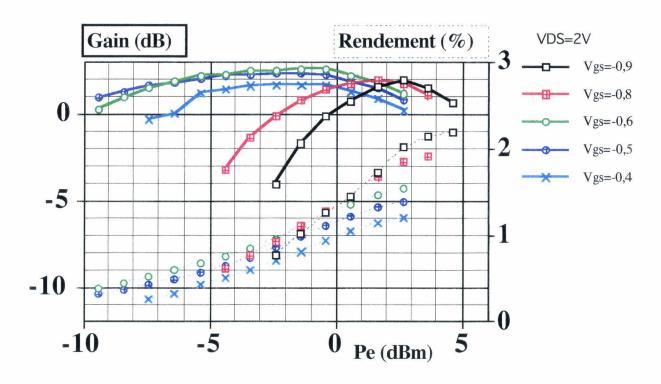

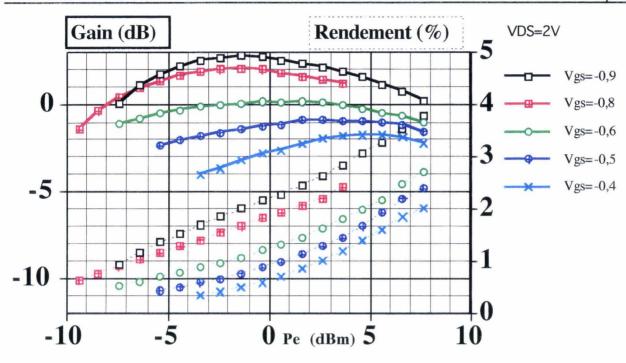

Après cette étude théorique contractuelle, nous nous sommes attachés à optimiser, en simulation, un tripleur 10-30 GHz dans le but de réaliser un démonstrateur en technologie hybride. Ce travail est décrit dans la partie II-F qui regroupe l'optimisation des impédances à présenter au transistor et la prise en compte des limitations de tenue en tension du composant devant être physiquement utilisé.

Mais avant toute chose, nous présentons dans la première partie (II-A) les caractéristiques et les modèles des transistors utilisés tout au long de ce travail.

# II-A caractéristiques et modèles des transistors utilisés

Tout au long de l'étude en simulation de multiplicateurs de fréquence, nous avons été amenés à utiliser les modèles de 6 transistors différents.

Les noms et les principales caractéristiques de ces transistors se trouvent regroupés dans le tableau Ta.II-1.

| Nom              | Fabricant | Туре                                 | Structure    | Dévelop-<br>pement<br>( µm <sup>2</sup> ) | Vp<br>(V) | IDSS<br>(mA) | gm <sub>Max</sub><br>(mS) | CGS <sub>Max</sub> |

|------------------|-----------|--------------------------------------|--------------|-------------------------------------------|-----------|--------------|---------------------------|--------------------|

| CHS450           | IEMN-DHS  | HEMT<br>AlGaAs/<br>GaAs              | Simple puits | 2*100*0,4                                 | -0,7      | 45           | 74                        | 170                |

| CHS453           | IEMN-DHS  | HEMT<br>AlGaAs/<br>GaAs              | Double puits | 2*75*0,4                                  | -4,3      | 150          | 43                        | 250                |

| FHX04            | FUJITSU   | HEMT<br>AlGaAs/<br>GaAs              | Simple puits | 2*100*0,2<br>5                            | -0,9      | 45           | 70                        | 150                |

| TOUTATIS TA33210 | THOMSON   | P-HEMT<br>AlGaAs/<br>InGaAs/<br>GaAs | Simple puits | 2*50*0,25                                 | -0,5      | 15           | 95                        | 130                |

| TOUTATIS TA33420 | THOMSON   | P-HEMT<br>AlGaAs/<br>InGaAs/<br>GaAs | Simple puits | 4*50*0,25                                 | -0,5      | 49           | 190                       | 270                |

| GRINGO           | THOMSON   | P-HEMT<br>AlGaAs/<br>InGaAs/<br>GaAs | Simple puits | 2*40*0,15                                 | -0,7      | 26           | 67                        | 68                 |

Tableau Ta.II-1: Caractéristiques des 6 transistors utilisés.

Les transistors CHS450 et CHS 453 ont été retenus pour avoir la possibilité de comparer deux composants de même type ayant des structures différentes (simple ou double puits).

Le choix du FHX04 s'est effectué en considérant ses caractéristiques électriques, compatibles avec notre application, et sa disponibilité commerciale.

Nous avons ensuite choisi d'utiliser un transistor plus performant : le TOUTATIS TA33210, fabriqué par THOMSON, de façon à accroître le gain en tripleur de fréquence.

La comparaison entre le TOUTATIS et le GRINGO nous a permis d'évaluer et de comparer les potentialités, en tripleur 27-81 GHz, de transistors ayant des longueurs de grille différentes (0,25 et 0,15 µm respectivement).

Enfin le choix d'un TOUTATIS TA33420, ayant un développement de grille plus important que le TA33210 (200  $\mu$ m contre 100  $\mu$ m), a été fait dans le but d'obtenir davantage de puissance de sortie dans le cas d'un tripleur 10-30 GHz.

#### II-A-1 Caractérisation des transistors

Les différentes étapes de caractérisation des transistors doivent permettre de déterminer leurs caractéristiques et tous les éléments du schéma du modèle non-linéaire usuel (figII-1).

Figure II-1: Schéma équivalent du TEC

Notre travail étant basé sur le fonctionnement non-linéaire des transistors, il nous est indispensable de réaliser une modélisation très fine et la plus exacte possible sur une large gamme de polarisations. Pour arriver à ce résultat, nous avons utilisé deux outils " classiques " au laboratoire : la caractérisation statique et la caractérisation hyperfréquence.

#### II-A-1-a Caractérisation statique

Ce type de mesure est réalisé sur des composants en cellule ou sous pointes à l'aide d'un banc automatisé piloté par le logiciel ICCAP ( Hewlett Packard ).

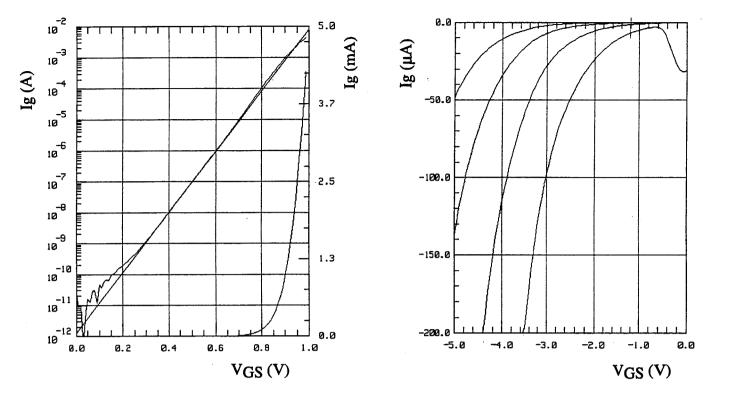

Les principales informations que l'on peut en tirer sont :

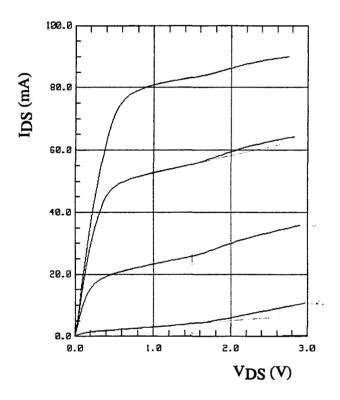

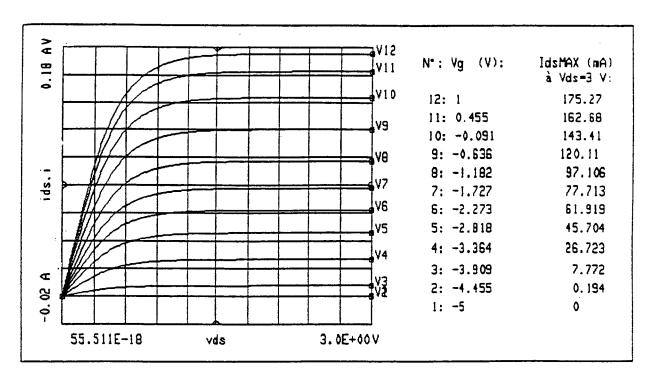

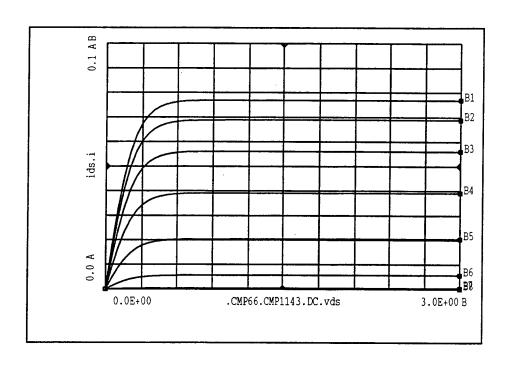

- Le réseau IDS(VDS) pour différents VGS (exemple figure II-2).

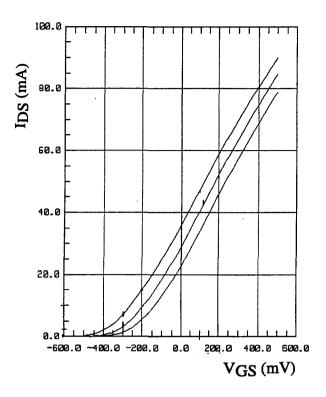

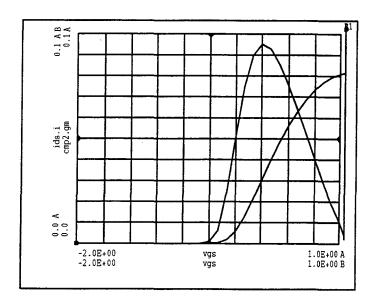

- Le réseau IDS(VGS) pour différents VDS (exemple figure II-3).

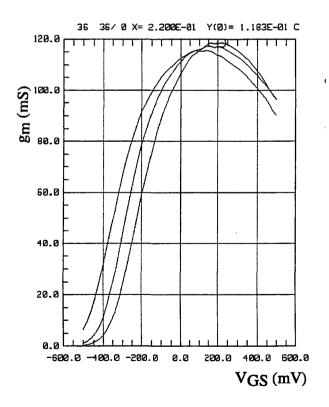

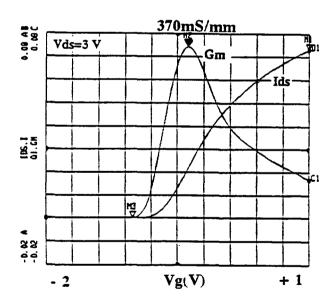

- La transconductance statique gm (exemple figure II-4).

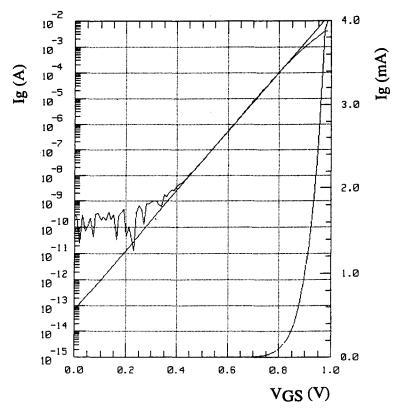

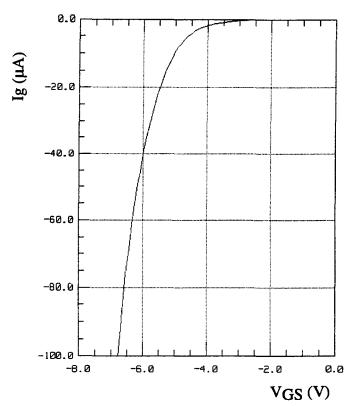

- Les caractéristiques des diodes Grille-Source et Grille-Drain, en direct et en inverse (exemple figure II-5).

Cette caractérisation permet, en plus de la vérification du bon fonctionnement du composant, de connaître ses caractéristiques en tension (tension de pincement et tensions maximales de fonctionnement).

Les caractéristiques des diodes Grille-Source et Grille-Drain seront utilisées dans nos modèles lorsque les simulations auront pour but la réalisation matérielle d'un circuit.

Figure II-2 : Exemple de réseau IDS(VDS) pour différents VGS ( transistor TOUTATIS TA33420).

Figure II-3 : Exemple de réseau IDS(VGS) pour différents VDS ( transistor TOUTATIS TA33420).

Figure II-4: Exemple de mesure de la transconductance statique gm ( transistor TOUTATIS TA33420).

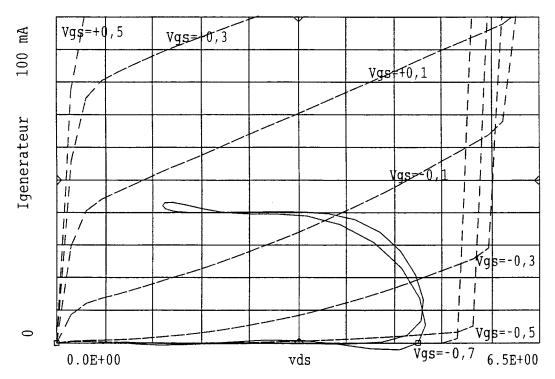

Figure II-5 : Exemple de caractéristique des diodes Grille-Source et Grille-Drain ( transistor TOUTATIS TA33420 ).

# II-A-1-b Caractérisation hyperfréquence

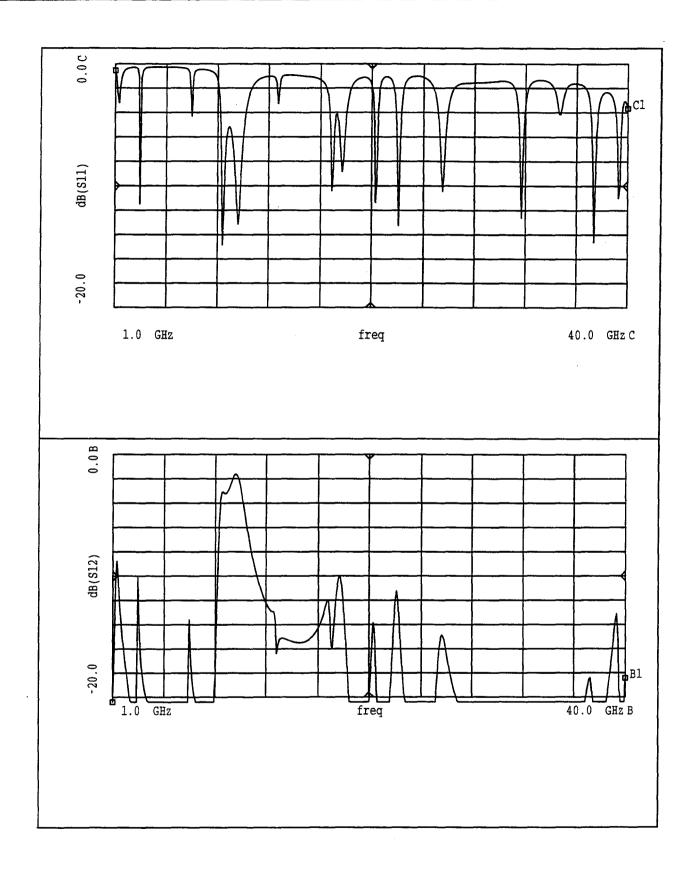

La caractérisation hyperfréquence est effectuée entre 45 MHz et 40 GHz à l'aide d'un analyseur de réseau HP85107A.

Les mesures des paramètres "S" sont réalisées en de nombreux points de polarisation et une procédure de dépouillement informatisée permet d'accéder aux valeurs de tous les éléments du schéma équivalent petit signal <sup>17</sup>. La figure II-6 présente les éléments extrinsèques et intrinsèques du schéma équivalent petit signal du TEC. Les évolutions obtenues pour les éléments intrinsèques en fonction des tensions de polarisation sont utilisées pour élaborer nos modèles "grand signal".

Cette caractérisation peut être réalisée indifféremment sur des composants montés dans des cellules de mesure -Dambrine- ou sur des composants, sur "wafer", contactés à l'aide de pointes hyperfréquences.

Figure II-6: Schéma équivalent petit signal du TEC

Une fois ces deux caractérisations effectuées, tous les éléments du schéma équivalent grand signal (figure II-1) sont connus et peuvent être alors intégrés dans les modèles devant représenter les transistors lors des simulations.

#### II-A-2 Description des modèles

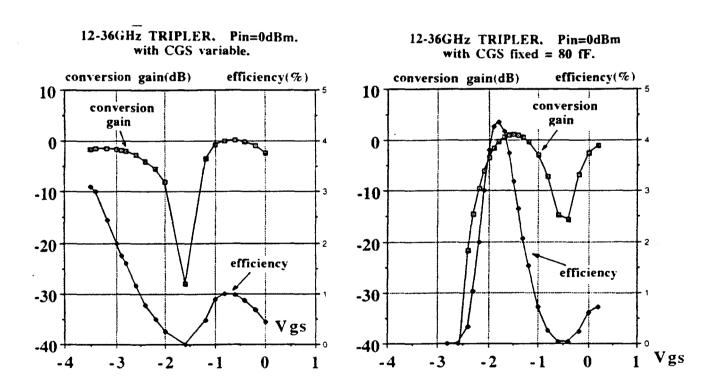

Comme nous l'avons rappelé chapitre I, seules les non linéarités CGS et IDS seront présentes dans nos modèles de transistors. Les justifications de ces choix sont les suivantes :

- Le générateur de courant, fonctionnant en deçà de la tension de pincement Vp du transistor, constitue la source potentielle majeure des harmoniques. De ce fait, il doit donc être obligatoirement représenté par un modèle non-linéaire complet dépendant des tensions VGS et VDS.

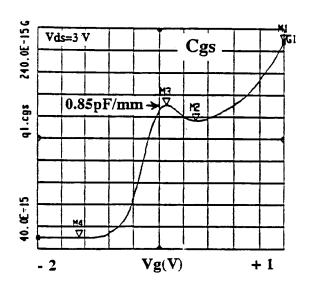

- La capacité CGS, fortement non-linéaire en fonction de la tension interne VGS, doit être représentée par un modèle non-linéaire dépendant au moins de cette tension. Cela est nécessaire, non pas à cause de l'effet "Varactor" ( création directe d'harmoniques) qu'elle

pourrait créer, mais parce qu'une valeur moyenne de la capacité CGS ne saurait rendre compte des variations d'impédance d'entrée du transistor dues à la variation de la valeur de cette capacité en fonction de la puissance injectée sur la grille du transistor.

Cette variation d'impédance d'entrée du transistor modifie la forme du signal VGS(t) et donc, la commande du générateur de courant.

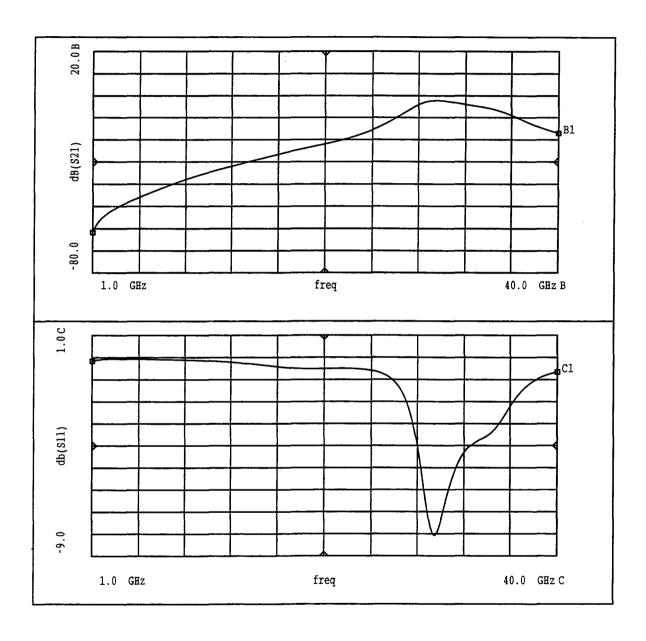

De nombreuses simulations ont montré la nécessité de cette modélisation. Un exemple, figure II-7, présente, dans le cas d'un transistor TOUTATIS TA 33210, la différence de gain obtenue en prenant une capacité CGS fixe moyenne, ou bien une capacité variable.

- Les autres éléments du schéma équivalent ne modifient que très peu les résultats obtenus en simulation lorsqu'ils sont choisis fixes. Nous avons donc décidé de considérer constants ces éléments pour simplifier le modèle et, de ce fait, diminuer quelque peu les temps de calcul lors des simulations.

Figure II-7 : Comparaison des gains obtenus en prenant la capacité CGS fixe ou variable, dans le cas du transistor TOUTATIS TA33210.

Les caractéristiques des diodes Grille Source et Grille-Drain ne seront implantées dans nos modèles que lorsque nous désirerons vérifier la compatibilité des excursions en tension de nos simulations avec les caractéristiques de tenue en tension des transistors simulés.

Lorsque nous réaliserons des simulations dans le but de fabriquer un démonstrateur, nous nous imposerons d'obtenir des tensions VGS et VGD n'entraînant pas une conduction en direct ou en inverse des diodes Grille Source et Grille-Drain. Cette limitation est indispensable lorsque l'on désire réaliser un système à transistor qui soit fiable et qui ait une durée de vie significative.

Les caractéristiques non-linéaires de ces diodes ne seront donc pas, en principe, responsables du comportement non-linéaire du transistor.

Les différents éléments, constants ou non, des transistors caractérisés sont introduits dans le logiciel MDS (Hewlett Packard) en se basant sur un modèle pré défini de transistor à effet de champ.

Les éléments constants sont insérés directement. Le générateur de courant IDS peut être formulé par une équation dépendant des tensions VGS et VDS. La capacité CGS doit être décrite par sa charge QGS qui peut dépendre des tensions VGS et VDS.

Les expressions mathématiques, plus ou moins complexes, des courants IDS et charges QGS sont choisies en fonction des caractéristiques de chaque transistor.

Pour illustrer cela, nous détaillons la modélisation de deux des six transistors ; ces deux transistors étant assez différents l'un de l'autre.

Les modèles des quatre autres transistors sont calqués sur les précédents : seules leurs caractéristiques seront indiquées.

# II-A-2-a Modélisation du transistor CHS453

Ce transistor est un composant AlGaAs / GaAs double puits particulièrement non-linéaire.

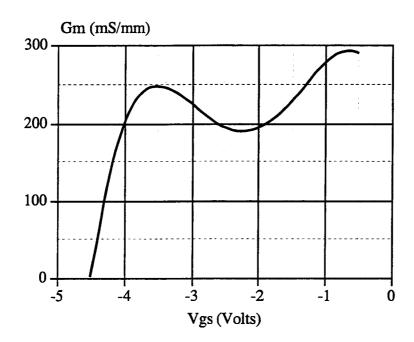

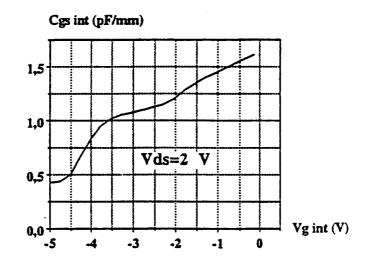

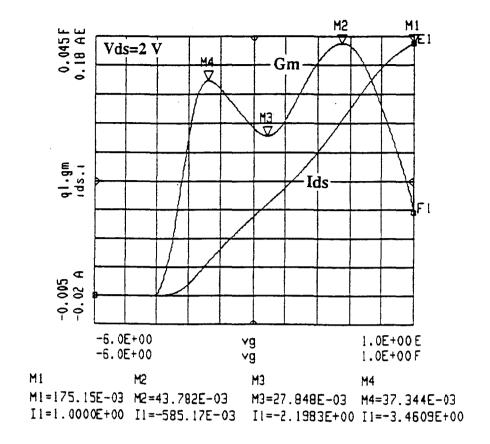

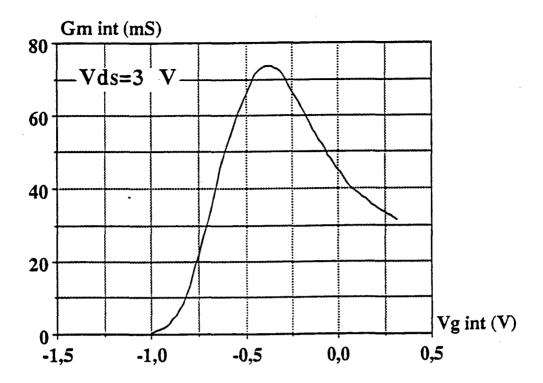

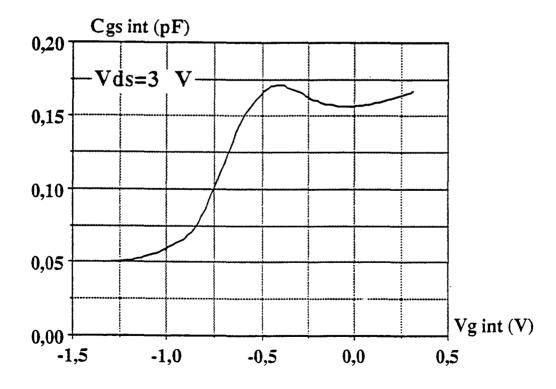

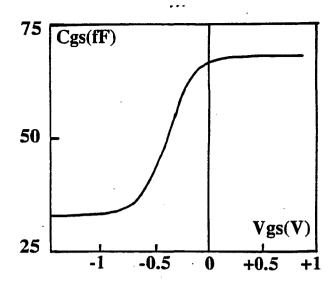

Les mesures de la transconductance gm et de la capacité CGS sont données figures II-8 et II-9.

Figure II-8: Transconductance hyperfréquence du transistor CHS453 en fonction de la tension de grille.

Figure II-9: Capacité Grille-Source du transistor CHS453 en fonction de la tension de grille.

L'équation du générateur de courant est déterminée en intégrant celle du gm. La variation du gm est représentée par une équation polynomiale déterminée à partir de la mesure du gm à une tension VDS de 2 Volts.

L'expression finale de IDS est sous la forme :

$$I_{DS}(V_{GS}, V_{DS}) = \left(\sum_{k=0}^{19} I_k * V_{GS}^k\right) * 5 * 10^{-3} * \left(1 + th \left[40 * \left(V_{GS} + 4,63\right)\right]\right) * th \left(2 * V_{DS}\right)$$

Les coefficients Ik du polynôme sont répertoriés dans le tableau Ta.II-2.

| 10         | 14,70 | 17          | -0,19 | I14 | -2,27 |

|------------|-------|-------------|-------|-----|-------|

| I1         | 3,88  | 18          | -4,00 | I15 | -6,50 |

| 12         | -0,83 | 19          | 0,14  | I16 | -1,19 |

| 13         | -0,36 | I10         | 0,15  | I17 | -1,37 |

| <b>I</b> 4 | 0,20  | <b>I</b> 11 | 3,07  | I18 | -9,06 |

| 15         | 9,52  | I12         | -4,82 | I19 | -2,63 |

| 16         | -0,13 | I13         | -4,84 |     |       |

<u>Tableau Ta.II-2 : Coefficients Ik du polynôme représentant le courant de drain du transistor</u>

<u>CHS453</u>

Bien que cette formulation ne soit rigoureusement valable que pour la valeur de VDS à laquelle a été faite la caractérisation (2V), le terme supplémentaire th(2VDS) permet de bâtir le réseau de caractéristiques dynamiques simulé IDS(VGS,VDS) (figure II-10).

Dans le cas de nos simulations, la petite erreur de modélisation induite par cette représentation n'aura qu'une répercussion minime. En effet, comme le montre la figure II-11, la partie du réseau de caractéristiques où IDS et VDS sont importants n'est pas explorée par le cycle de charge du transistor.

Les caractéristiques simulées du courant dynamique de drain et de la transconductance sont présentées figure II-12 en fonction de la tension de grille pour une polarisation VDS=2 V.

Figure II-10: Réseau des caractéristiques dynamiques simulées IDS(VGS,VDS) du transistor CHS453.

Figure II-11: Exemple de cycle de charge en mode tripleur et réseau des caractéristiques dynamiques simulées IDS(VGS,VDS) du transistor TOUTATIS TA33420.

Figure II-12: Caractéristiques simulées du courant dynamique de drain et de la transconductance du transistor CHS453 en fonction de la tension VGS.

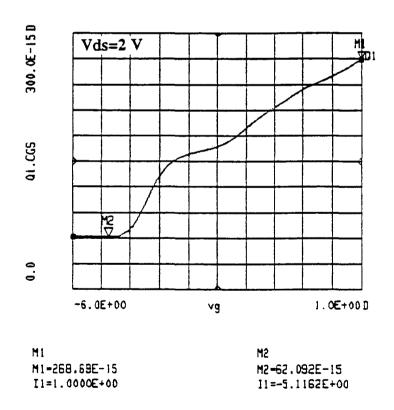

De la même façon que pour le générateur de courant, l'équation de la charge QGS est déterminée en intégrant une équation polynomiale de CGS. La formule implantée dans le simulateur est la suivante :

$$Q(V_{GS}) = \left[ \left( \sum_{k=0}^{21} Q_k * V_{GS}^k \right) * 50 * \left( 1 + th \left[ 9 * \left( V_{GS} + 4,78 \right) \right] \right) + 62 * V_{GS} \right] * 10^{-15}$$

Les coefficients Qk du polynôme sont répertoriés dans le tableau Ta.II-3.et la caractéristique simulée de la capacité CGS est présentée figure II-13 en fonction de la tension de grille pour une polarisation VDS=2 V.

La modélisation de la capacité CGS ne tient pas compte des variations de VDS car celles-ci sont relativement faibles étant donné que l'on court-circuite les fréquences f0 et 2f0 en sortie du transistor.

| Q0 | 5,23  | Q8  | 8,76  | Q16 | 4,62 |

|----|-------|-----|-------|-----|------|

| Q1 | 1,81  | Q9  | 2,06  | Q17 | 7,80 |

| Q2 | 0,10  | Q10 | -4,84 | Q18 | 9,14 |

| Q3 | 1,79  | Q11 | -2,88 | Q19 | 7,11 |

| Q4 | 3,98  | Q12 | -1,33 | Q20 | 3,32 |

| Q5 | -5,63 | Q13 | 8,19  | Q22 | 7,02 |

| Q6 | -6,81 | Q14 | 5,29  |     |      |

| Q7 | 5,49  | Q15 | 1,91  |     |      |

Tableau Ta.II-3: Coefficients Ik du polynôme représentant la charge QGS du transistor CHS453

Figure II-13: Caractéristique simulée de la capacité CGS(VGS) du transistor CHS453.

Les valeurs des autres éléments, considérés constants, sont regroupées dans le tableau Ta.II-4.

| RG (Ω) | RD (Ω) | RS (Ω) | Ri (Ω) | CGD (fF) | CDS (fF) |

|--------|--------|--------|--------|----------|----------|

| 2,5    | 3,4    | 2,6    | 1,7    | 59       | 150      |

Tableau Ta.II-4: Valeurs des éléments constants du transistor CHS453

#### II-A-2-a Modélisation du transistor TOUTATIS TA33210.

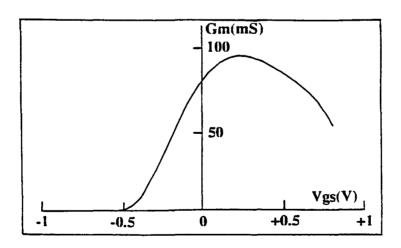

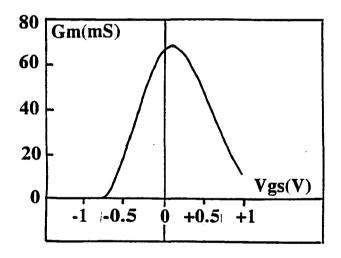

Ce composant AlGaAs / InGaAs / GaAs monopuits n'est pas particulièrement non-linéaire. Sa transconductance (figure II-14) ne possède qu'un maximum, contrairement au CHS453.

La mesure de la capacité CGS est donnée figure II-15.

Figure II-14: Transconductance du transistor TA33210 en fonction de la tension de grille.

Figure II-15: Capacité Grille-Source du transistor TA33210 en fonction de la tension de grille.

L'expression mathématique du générateur de courant est déterminée en utilisant la même méthode que pour le transistor CHS453. La forme moins tourmentée de la transconductance du transistor TA33210 permet l'utilisation d'un polynôme limité à l'ordre 10. Nous avons donc la formulation suivante pour le courant IDS:

$$I_{DS}(V_{GS}, V_{DS}) = \left(I_0 + \sum_{k=1}^{10} I_k * V_{GS}^k\right) * 10^{-3} * \left(1 + th \left[40 * \left(V_{GS} + 0, 6\right)\right]\right) * th \left(4, 5 * V_{DS}\right)$$

Le terme supplémentaire th(4,5VDS) permet également de bâtir le réseau de caractéristiques dynamiques simulé IDS(VGS,VDS) (figure II-16).

Les coefficients Ik du polynôme sont répertoriés dans le tableau Ta.II-5.; les caractéristiques simulées du courant dynamique de drain et de la transconductance sont présentés figure II-17 en fonction de la tension de grille pour une polarisation VDS=3 V.

Figure II-16: Réseau des caractéristiques dynamiques simulées IDS(VGS,VDS) du transistor TA33210.

| 10 | 10,17   | I4 | 59,16   | 18  | 1250,93  |

|----|---------|----|---------|-----|----------|

| I1 | 44,86   | 15 | 618,85  | 19  | -1032,66 |

| 12 | 50,72   | 16 | -874,95 | I10 | 276,26   |

| 13 | -244,44 | I7 | -143,51 |     |          |

<u>Tableau Ta.II-5 : Coefficients Ik du polynôme représentant le courant de drain du transistor</u>

<u>TA33210</u>

Figure II-17: Caractéristiques simulées du courant dynamique de drain et de la transconductance du transistor TA33210 en fonction de la tension VGS.

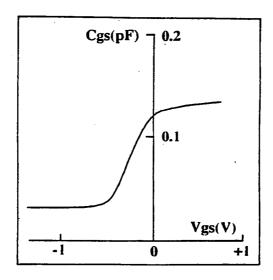

L'équation de la charge QGS est déterminée en intégrant une équation non polynomiale de CGS. En effet, nous remarquons qu'en raison de la forme particulière de l'évolution de la capacité CGS, une équation du type "tangente hyperbolique" convient mieux pour la décrire :

$$C_{GS}(V_{GS}) = [31,4+52*(1+th[5*(V_{GS}+0,2)])]*10^{-15}$$

La charge QGS est alors la suivante :

$$Q_{GS}(V_{GS}) = \left[4,51 + (31,4+52) * V_{GS} + \frac{52}{5} * \ln(\cosh[5*(V_{GS}+0,2)])\right] * 10^{-15}$$

La figure II-18 présente la caractéristique simulée de la capacité CGS en fonction de la tension de grille pour une polarisation VDS=3 V.

Figure II-18: Caractéristique simulée de CGS(VGS) du transistor TA33210.

Les autres éléments du schéma équivalent du transistor TA33210 sont considérés constants, leurs valeurs sont regroupées dans le tableau Ta.II-6.

| RG (Ω) | RD (Ω) | RS (Ω) | Ri (Ω) | CGD (fF) | CDS (fF) |

|--------|--------|--------|--------|----------|----------|

| 3,66   | 4,2    | 3,8    | 2,5    | 22       | 25       |

Tableau Ta.II-6: Valeurs des éléments constants du transistor TA33210

# II-A-2-c Modélisation des transistors CHS450, FHX04, TOUTATIS TA33420 et GRINGO

#### Le transistor CHS450

Ce transistor est modélisé en utilisant le même type d'équations que pour le CHS 453. Les variations de sa transconductance et de sa capacité CGS sont représentées figure II-19 et II-20 pour une tension VDS de 2 Volts; le tableau Ta.II-7 regroupe les valeurs des éléments constants.

| RG (Ω) | RD (Ω) | RS (Ω) | Ri (Ω) | CGD (fF) | CDS (fF) |

|--------|--------|--------|--------|----------|----------|

| 2,5    | 3,4    | 2,6    | 1,7    | 60       | 150      |

Tableau Ta.II-7: Valeurs des éléments constants du transistor CHS450

Figure II-19: Transconductance du transistor CHS450 en fonction de la tension de grille.

Figure II-20 : Capacité Grille-Source du transistor CHS450 en fonction de la tension de grille.

# Le transistor FHX04

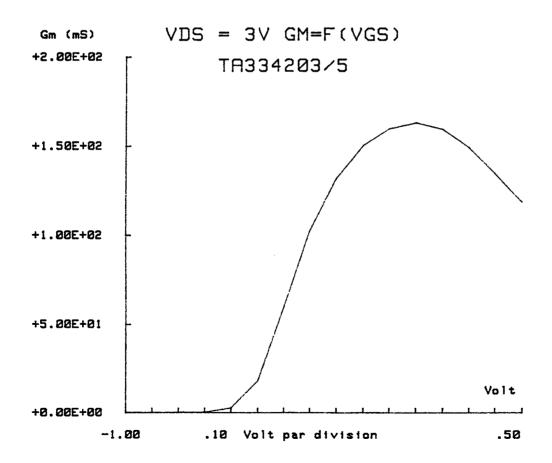

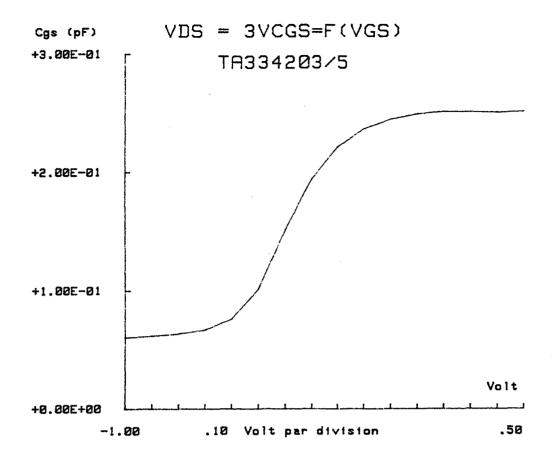

Ce composant a été caractérisé à une tension VDS de 3 Volts. Comme dans le cas du CHS453, des équations polynomiales ont été utilisées pour modéliser la transconductance (figure II-21) et la capacité CGS (figure II-22). Les valeurs des éléments constants sont regroupées dans le tableau Ta.II-8.

| RG (Ω) | RD (Ω) | RS (Ω) | Ri (Ω) | CGD (fF) | CDS (fF) |

|--------|--------|--------|--------|----------|----------|

| 2,0    | 2,8    | 3,0    | 4      | 20       | 100      |

Tableau Ta.II-8: Valeurs des éléments constants du transistor FHX04

Figure II-21: Transconductance du transistor FHX04 en fonction de la tension de grille.

Figure II-22 : Capacité Grille-Source du transistor FHX04 en fonction de la tension de grille.

#### Le transistor TOUTATIS TA33420

La différence entre le TOUTATIS TA33420 et le TOUTATIS TA33210 se limite au nombre de doigts de grille : quatre au lieu de deux. La modélisation du TA33420 est donc calquée sur celle du TA33210.

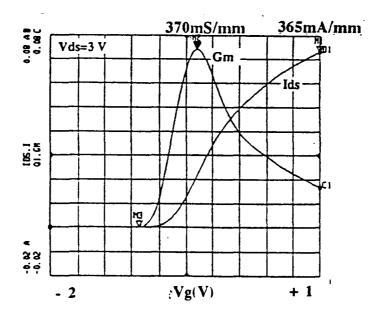

Ce composant a été caractérisé à une tension VDS de 3 Volts. Comme dans le cas du CHS453, des équations polynomiales ont été utilisées pour modéliser les deux non linéarités du transistor

La transconductance (figure II-23), la capacité CGS (figure II-24). et les valeurs des éléments constants (tableau Ta.II-9) sont données à une tension VDS de 3 Volts.

| RG (Ω) | RD (Ω) | RS (Ω) | Ri (Ω) | CGD (fF) | CDS (fF) |

|--------|--------|--------|--------|----------|----------|

| 1,65   | 2,1    | 1,9    | 3      | 40       | 30       |

Tableau Ta.II-8: Valeurs des éléments constants du transistor TA33420

Figure II-23: Transconductance mesurée du transistor TA33420 en fonction de la tension de grille.

Figure II-24 : Capacité Grille-Source mesurée du transistor TA33420 en fonction de la tension de grille.

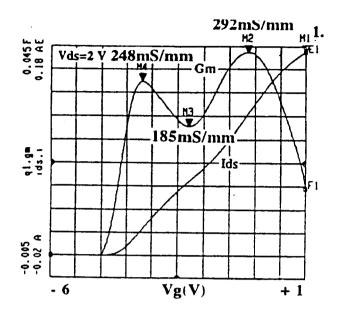

#### Le transistor GRINGO

Ce transistor est celui qui, des six transistors modélisés, a la plus petite longueur de grille (0,15µm).

La forme de l'évolution de sa capacité CGS (figure II-25) permet d'utiliser une modélisation identique à celle développée pour le TOUTATIS TA33210.

L'évolution de sa transconductance et les valeurs de ses éléments constants sont présentées figure II-26 et tableau Ta.II-9.

| RG (Ω) | RD (Ω) | RS (Ω) | Ri (Ω) | CGD (fF) | CDS (fF) |

|--------|--------|--------|--------|----------|----------|

| 5      | 4,9    | 3,4    | 5      | 15       | 20       |

Tableau Ta.II-9: Valeurs des éléments constants du transistor GRINGO

Figure II-25: Transconductance du transistor GRINGO en fonction de la tension de grille.

Figure II-26: Capacité Grille-Source du transistor GRINGO en fonction de la tension de grille.

Les caractéristiques et les modèles des six transistors utilisés étant décrits, nous pouvons maintenant passer aux simulations de multiplication de fréquence.

# II-B choix de la technologie

# **II-B-1 Introduction**

Dans cette partie, nous comparons les potentialités en tripleurs de fréquences de deux types différents de transistors :

- le CHS 450, transistor simple puits, ayant une caractéristique gm(VGS) "classique". Ce type de composant présente une réponse en courant (figure III-27) entre Vp et VB typique de beaucoup de HEMTs simple puits. A cette réponse en courant correspond une courbe en cloche, à sommet unique, pour la transconductance gm.

- le CHS453, un transistor double puits. Sa réponse en courant (figure II-28) est notablement différente de celle du CHS450 car elle présente trois points d'inflexion en fonction de VGS. A ces trois points d'inflexion correspondent trois extremums (deux maxima et un minimum) de la transconductance.

Figure II-27: Transconductance et courant du transistor CHS450 en fonction de la tension VGS

Figure II-28: Transconductance et courant du transistor CHS453 en fonction de la tension VGS

Les modèles de ces deux transistors sont utilisés dans un circuit électrique permettant de simuler le triplement de fréquence de 12 vers 36 GHz.

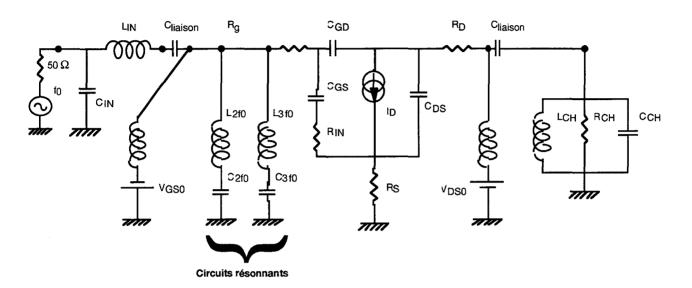

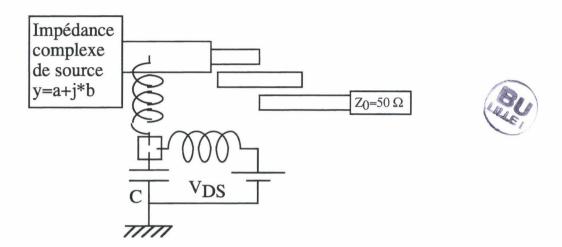

#### II-B-2 Description du circuit de simulation

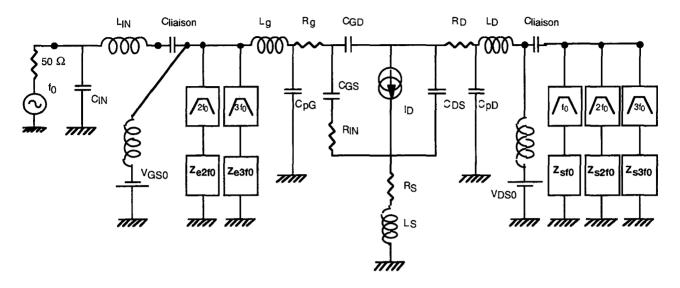

Figure II-29 : Schéma du circuit électrique de multiplication de fréquence introduit dans le simulateur MDS

Le circuit utilisé est décrit figure II-29, il est composé des éléments suivants :

- un générateur, de résistance interne  $50\Omega$ , délivrant une puissance variable utile PIN à une fréquence f0 de 12 GHz.

- Un circuit d'accord, constitué d'une capacité et d'une self, qui assure l'adaptation à  $50\Omega$  de l'entrée du transistor.

- Une capacité d'isolation, interdisant le retour de tension continue sur le générateur.

- Un circuit de polarisation de la grille, comportant une self en série avec une source de tension continue. La self a pour but de laisser passer le courant continu tout en se présentant comme un circuit ouvert aux hautes fréquences.

- Le modèle du transistor utilisé.

- Un circuit de polarisation du drain suivi d'une capacité d'isolation.

- Un circuit bouchon (R-L-C parallèle), accordé à 3f0 (la fréquence triple de celle du générateur), se comportant comme une charge résistive de valeur RCH pour le troisième harmonique et comme un quasi-court-circuit pour toutes les autres fréquences. La valeur de RCH est fixée à 200Ω et celle de LCH à 12pH.

# II-B-3 Les simulations réalisées

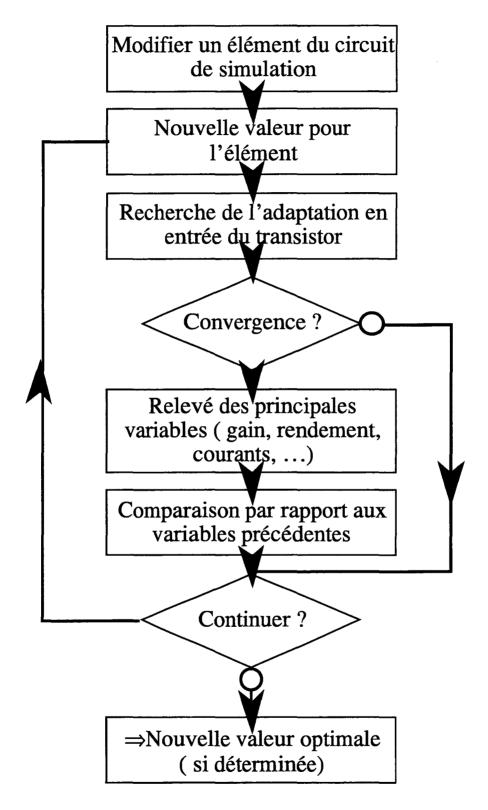

La procédure d'optimisation consiste, d'une part, à accorder le circuit d'entrée (CIN et LIN) et d'autre part, à accorder le circuit de sortie (CCH).

La valeur de la capacité CCH peut être calculée de façon approximative en considérant qu'elle se trouve en parallèle avec la capacité CDS du transistor. Les éléments LCH, CCH et CDS doivent alors répondre à l'équation suivante pour qu'il y ait accord à la fréquence 3f0:  $L_{CH}*(C_{CH}+C_{DS})*(2\pi*3f_0)^2=1$

Le gain de conversion et le rendement sont calculés de la façon suivante :

$$G[dB] = 10 * log \left( \frac{Puissance de sortie à 3f_0}{Puissance d'entrée à f_0} \right)$$

$$\eta[\%] = 100 * \left( \frac{\text{Puissance de sortie à } 3f_0}{\text{Puissance continue+ Puissance d'entrée à } f_0} \right)$$

Il faut remarquer que, dans le cas de la multiplication de fréquence, la formule du rendement en puissance ajoutée (  $PAE \left[\%\right] = 100 * \left(\frac{Puissance de sortie - Puissance d'entrée}{Puissance continue}\right)$ ) ne peut être utilisée car elle conduirait, dans certains cas, à obtenir des rendements négatifs.

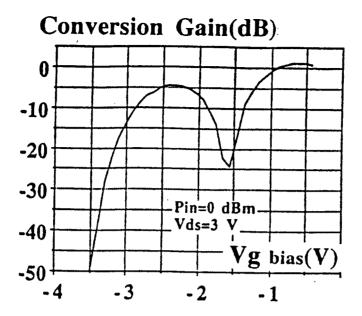

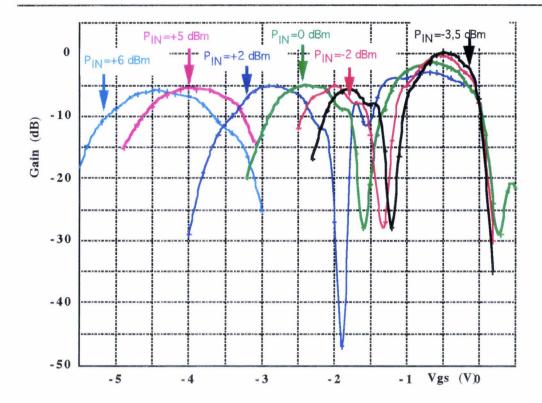

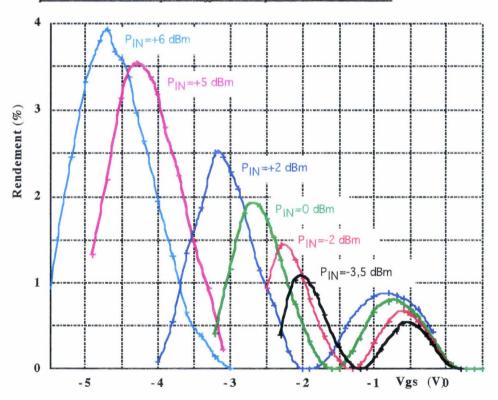

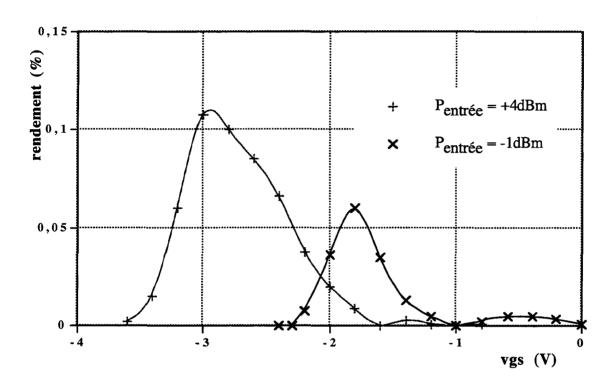

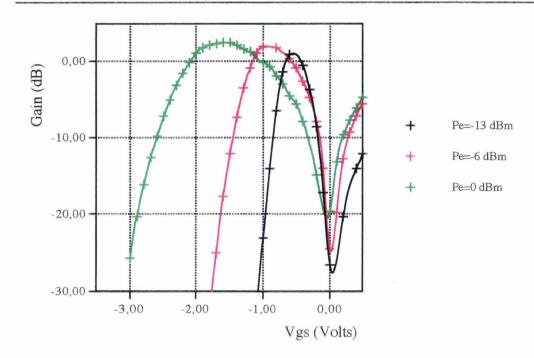

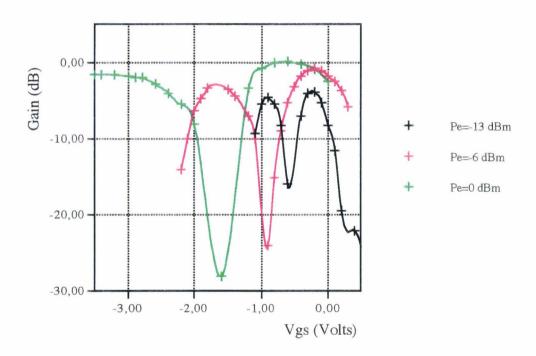

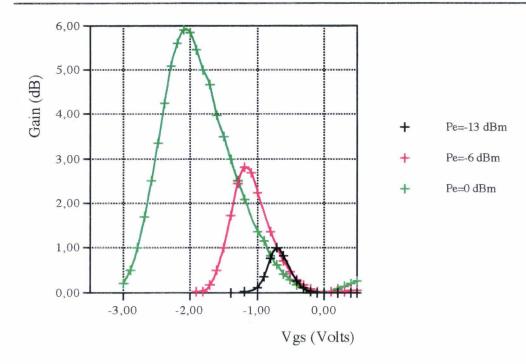

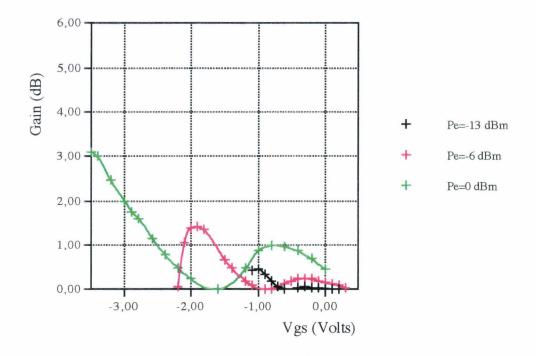

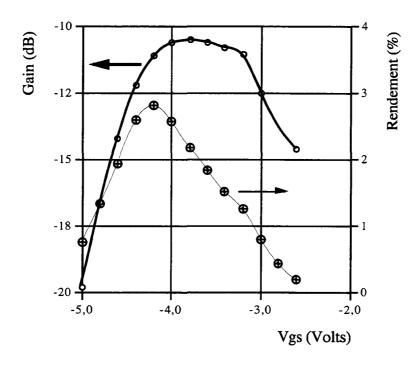

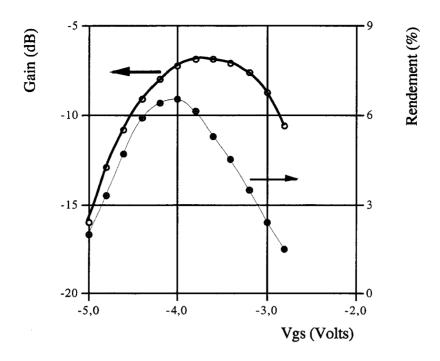

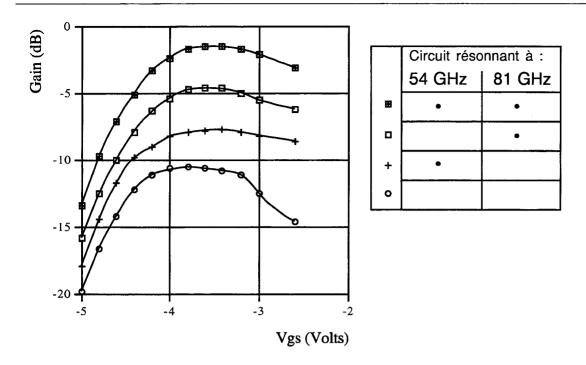

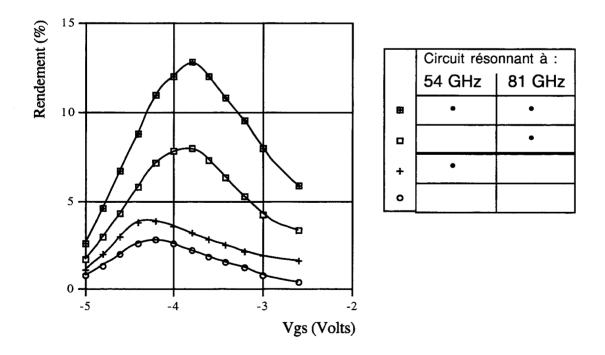

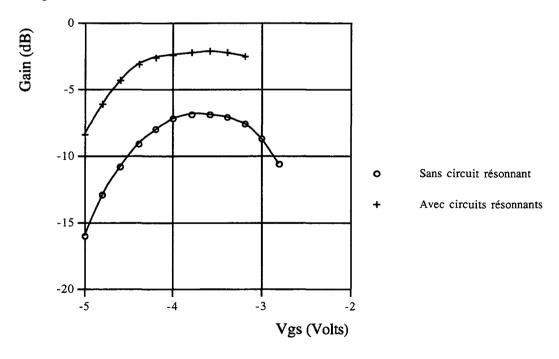

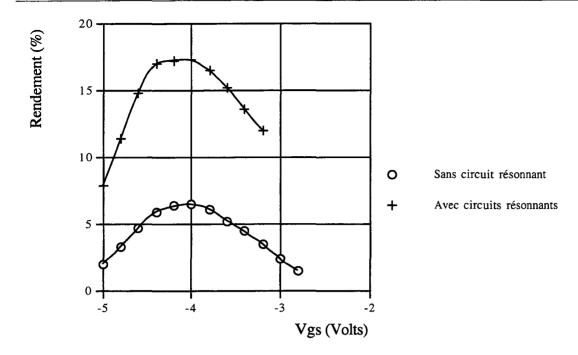

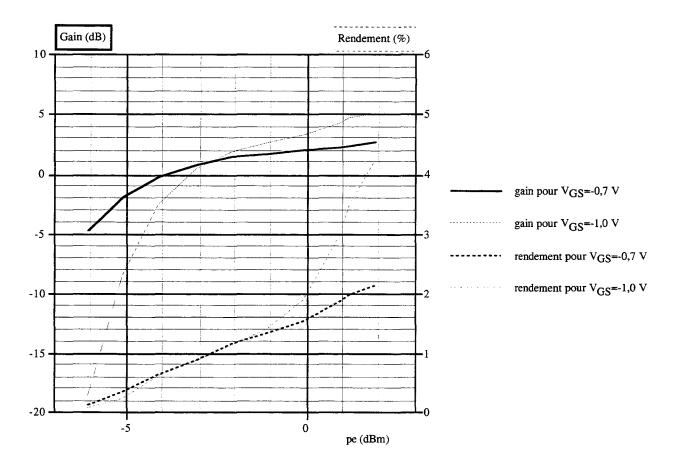

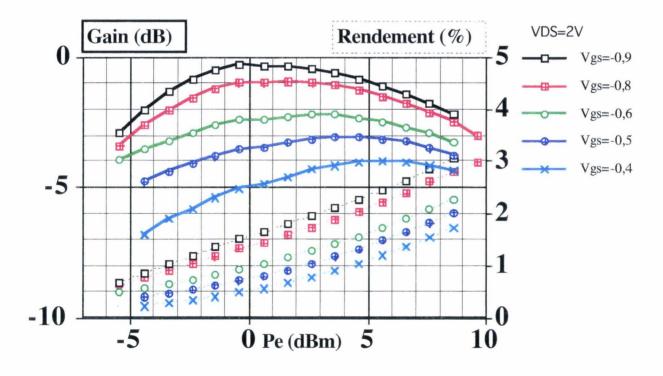

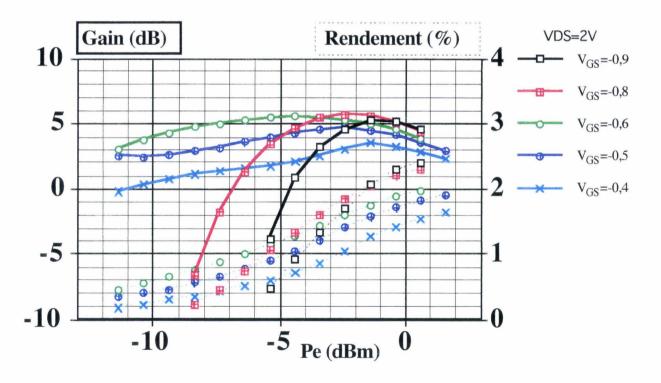

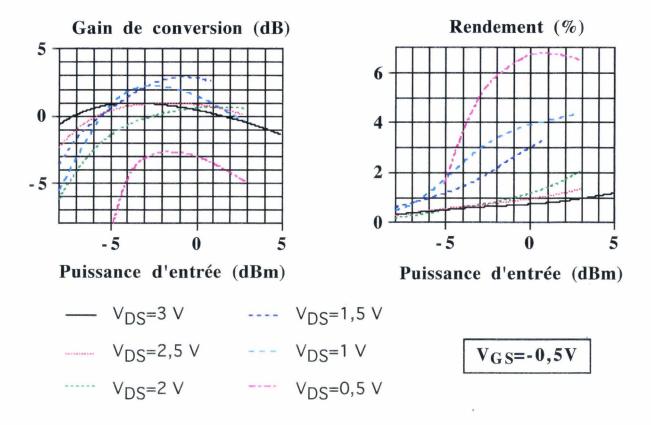

Le gain obtenu avec le transistor CHS450 est présenté figure II-30.

Les conditions de fonctionnement du transistor sont :

- VDS0=3 Volts

- PIN=0 dBm

- VGS0 variant de -3,5 à -0,4 Volts

Figure II-30 : Gain de conversion du transistor CHS450 en mode tripleur en fonction de la tension de polarisation VGS0

La courbe du gain possède deux maxima : l'un se positionne à une tension de polarisation correspondant à la tension de pincement du transistor (-0,7V) et l'autre, se trouve à une tension VGS0 de -2,4 Volts qui a pour effet de faire fonctionner le générateur de courant du transistor avec un temps d'ouverture très faible.

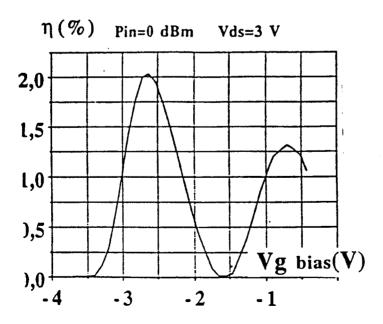

La figure II-31 représente le rendement obtenu dans les mêmes conditions de fonctionnement.

Figure II-31: Rendement du transistor CHS450 en mode tripleur en fonction de la tension de polarisation VGS0

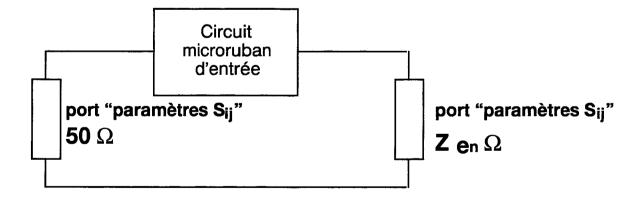

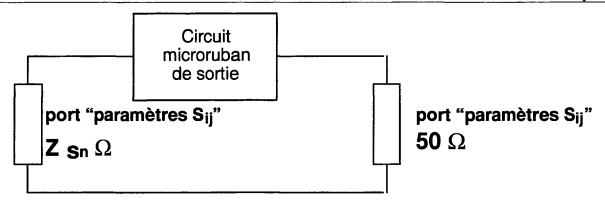

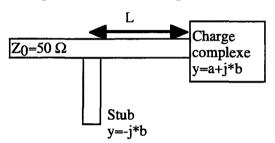

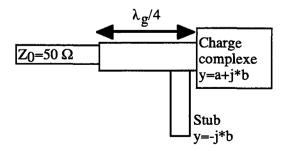

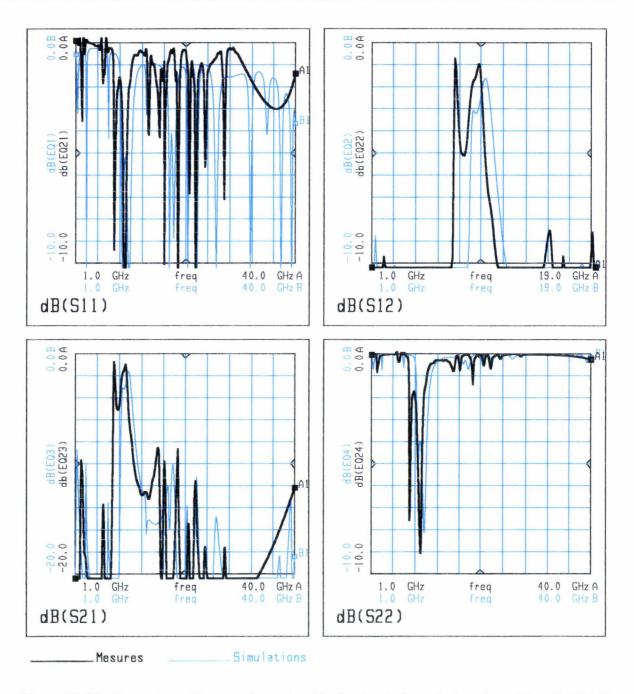

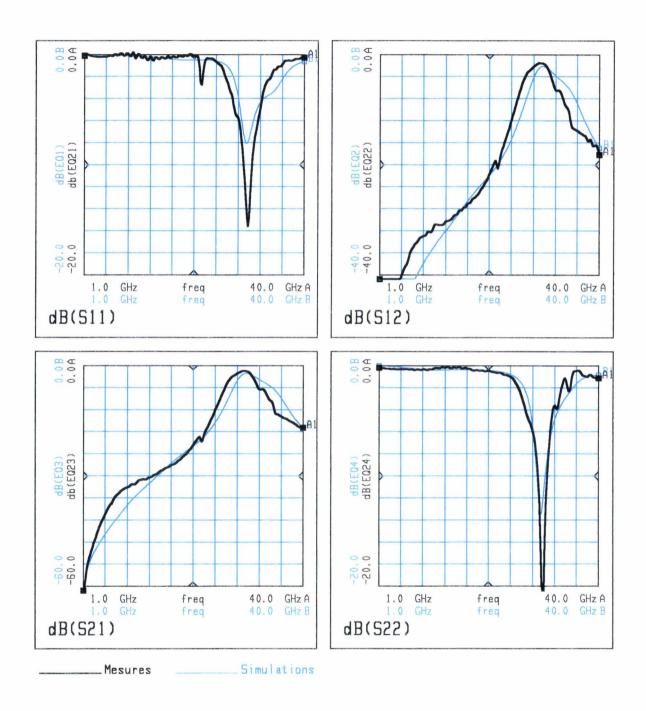

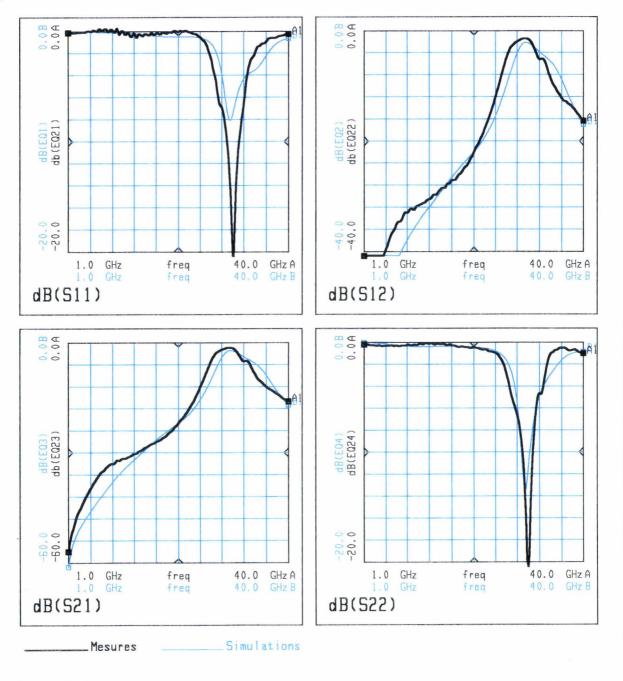

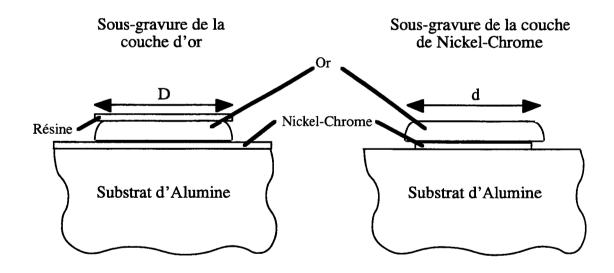

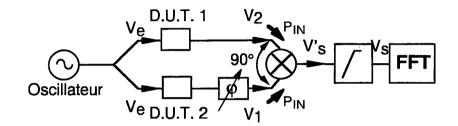

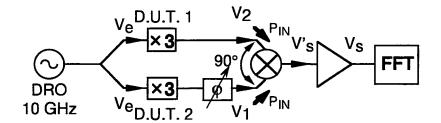

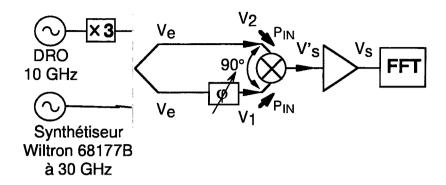

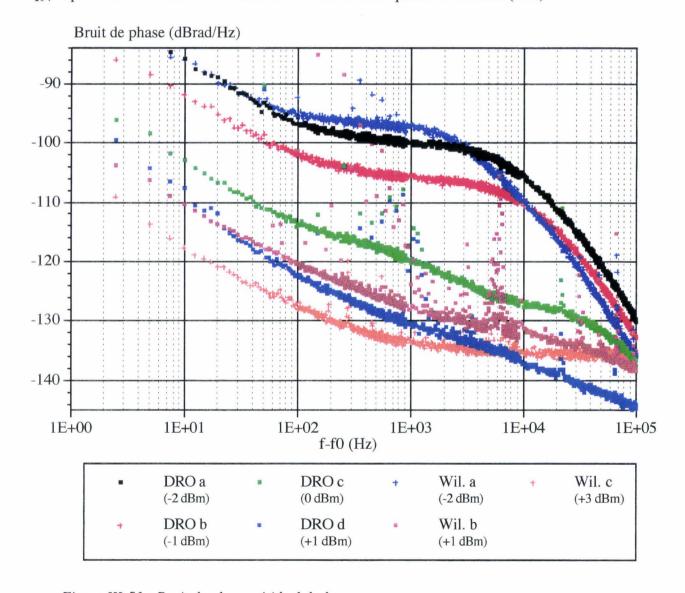

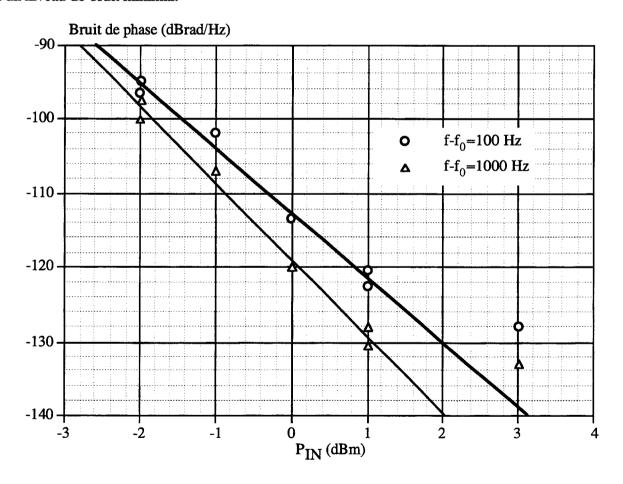

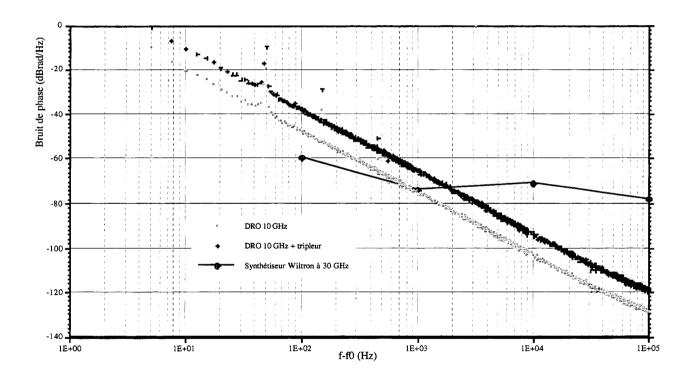

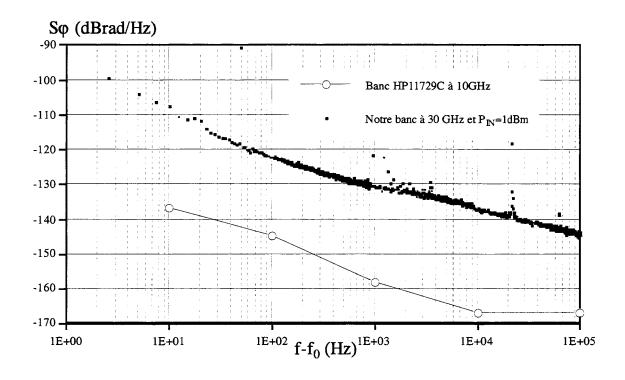

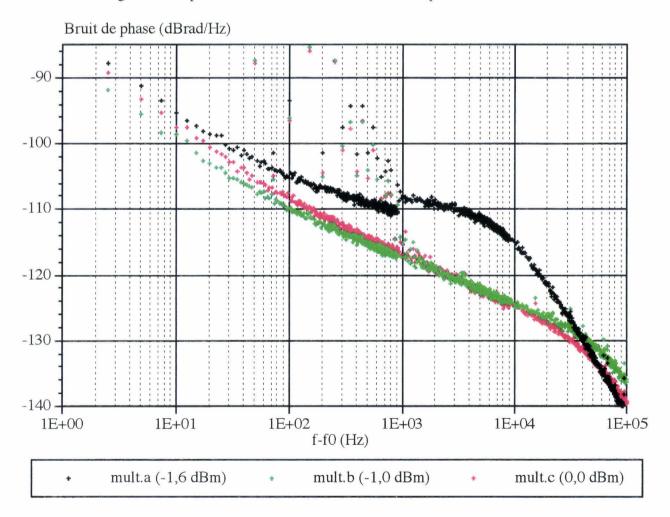

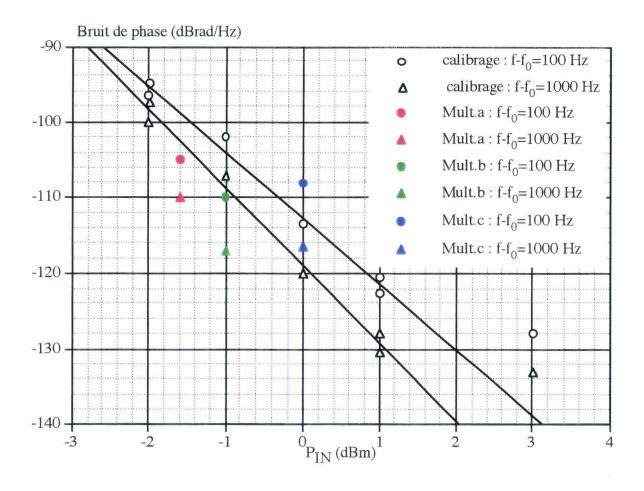

Les maxima de la courbe de rendement se trouvent pratiquement aux mêmes valeurs de VGS0 que pour la courbe de gain.