#### UNIVERSITE DES SCIENCES ET TECHNOLOGIES DE LILLE

## **THESE**

Spécialité : GENIE ELECTRIQUF

pour l'obtention du grade de

### **DOCTEUR** de l'Université des Sciences et Technologies de Lille

présentée par

#### **Alain BRIFFAUT**

## MODELISATION DES INTERRUPTEURS FORMES PAR L'ASSOCIATION TRANSISTOR-MOS+DIODE EN SERIE

Application à la cellule de commutation à interrupteurs bidirectionnels en tension et en courant

> Soutenue le 10 Décembre 1997 Devant la Commission d'Examen:

M. J.L COCQUERELLE

Président

M. C GLAIZE

Rapporteur

M. GROJAT

Rapporteur

M. R BAUSIERE

Examinateur

M. NIDIR

Examinateur

#### **AVANT-PROPOS**

Le travail présenté dans ce mémoire a été réalisé au Laboratoire d'Electrotechnique et d'Electronique de Puissance (L2EP) de l'Université des Sciences et Technologies de Lille dirigé par Monsieur le Professeur Christian ROMBAUT, au sein de l'équipe "Composants et Structures de Conversion" dirigée par Monsieur le Professeur Robert BAUSIERE.

Ce travail a été encadré par Monsieur le Professeur Robert BAUSIERE, je le prie de trouver ici l'expression de ma plus profonde reconnaissance pour l'aide fructueuse qu'il m'a apportée. Je tiens aussi à transmettre mes plus sincères remerciements à Monsieur Nadir IDIR, Maître de Conférences à l'IUT-A de Lille pour avoir accepté de co-encadrer ce travail; son aide et ses encouragements ont témoigné de son intérêt pour ces travaux.

Je remercie vivement Monsieur le Professeur Jean-Louis COCQUERELLE de l'IRESTE de Nantes, pour l'honneur qu'il m'a fait en acceptant de présider le jury de thèse.

Je suis très reconnaissant à Monsieur le Professeur Christian GLAIZE de l'Université de Montpellier II et à Monsieur Gérard ROJAT, Maître de Conférences HDR de l'Ecole Centrale de Lyon d'avoir accepté de juger ce mémoire.

Je tiens à remercier également les thésards et les étudiants de DEA du L2EP et particulièrement O. Barre, B. Boualem, S. Brulé, C. Cot, L. Deprez, C. Desombre, J-P. Dhaine, D. Dujardin, P. Dzwiniel, F. Hembert, I. Haouara, Y. Le Ménach, F. Marmin, C. Nen, J-L. Ranson, H. Roisse et O. Walti pour la bonne ambiance qu'ils ont su créer au sein du laboratoire, ainsi que tous les membres du laboratoire et plus particulièrement Madame Del Vitto, Monsieur Franchaud et Monsieur Ferla.

Enfin, j'exprime tout particulièrement ma plus grande reconnaissance aux membres de ma famille, pour leur soutien permanent et leur volonté de suivre le déroulement de mon travail.

**SOMMAIRE**

|  |  | 1 |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

#### **SOMMAIRE**

| INTRODUCTION                                                                   | 1  |

|--------------------------------------------------------------------------------|----|

| CHAPITRE I : Les cellules de commutation                                       |    |

| I.1) Introduction                                                              | 5  |

| I.2) Les interrupteurs                                                         | 5  |

| I.2.1) Interrupteur parfait                                                    | 5  |

| I.2.2) Interrupteur à semi-conducteur                                          | 6  |

| I.3) Les fonctions « interrupteur »                                            | 8  |

| I.4) Cellule élémentaire de commutation                                        | 9  |

| I.5) Cellules élémentaires à interrupteurs unidirectionnels en tension         | 11 |

| I.5.1) Interrupteurs unidirectionnels en courant (deux segments)               | 11 |

| I.5.2) Interrupteurs bidirectionnels en courant (trois segments)               | 12 |

| I.6) Cellules à interrupteurs bidirectionnels en tension                       | 14 |

| I.6.1) Interrupteurs unidirectionnels en courant (trois segments)              | 14 |

| I.6.2) Interrupteurs bidirectionnels en courant                                | 15 |

| I.7) Techniques de commande des cellules à IBTC                                | 16 |

| CHAPITRE II : Méthodes de modélisation des interrupteurs                       |    |

| II 1) Différentes méthodes de modélisation des composants de puissance         | 20 |

| II.2) Modélisation binaire                                                     | 21 |

| II.3) Modélisation de type comportemental                                      | 22 |

| II.3.1) Modèles comportementaux d'interrupteurs statiques à topologie variable | 23 |

| II.3.2). Modèles comportementaux d'interrupteurs statiques à topologie fixe    | 26 |

| II.3.3) Modèle de MOSFET                                                       | 26 |

| II.4) Méthode de résolution des équations de la physique des semi-conducteurs  | 27 |

| II.5) Identification des paramètres                                            | 28 |

| II.6) Conclusion                                                               | 28 |

| CHAPITRE III : Modélisation de la diode                                        |    |

| III.1) Principe de fonctionnement de la jonction PN                            | 30 |

| III.1.1) Les mouvements de charge dans un semi-conducteur                      | 31 |

| III.1.2) La jonction PN à l'équilibre                                          | 32 |

| III.1.3) La jonction PN en polarisation inverse                                | 34 |

| III.1.4) La jonction PN en polarisation directe                                | 36 |

| III.2) La diode de puissance                                                   | 37 |

| III.3) Modèle comportemental de la diode                                      | 40  |

|-------------------------------------------------------------------------------|-----|

| III.3.1) Capacités de jonction                                                | 40  |

| III.3.2) Modèle de la diode au blocage                                        | 41  |

| III.3.3) Modélisation de la diode à la fermeture                              | 47  |

| CITA DITTOE IN . M. 141 1 A MOCERT                                            |     |

| CHAPITRE IV : Modélisation du transistor MOSFET                               |     |

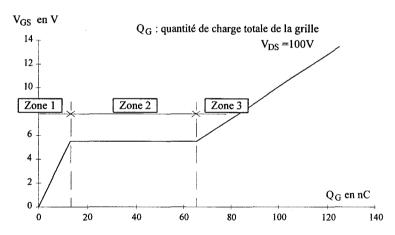

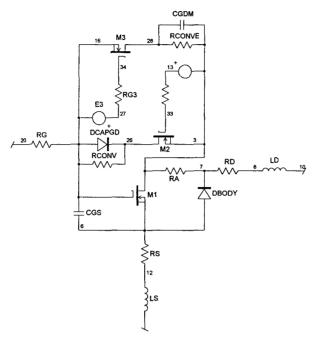

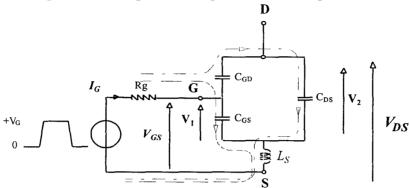

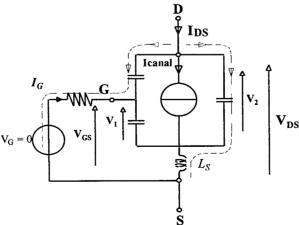

| IV.1) Etude d'un modèle comportemental de transistor MOS                      | 52  |

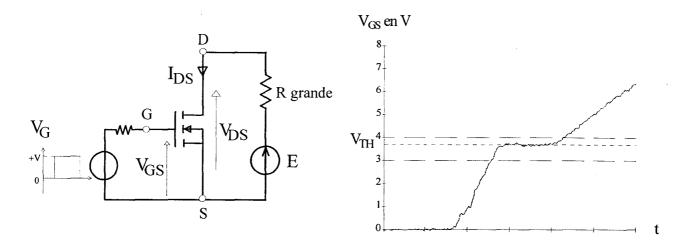

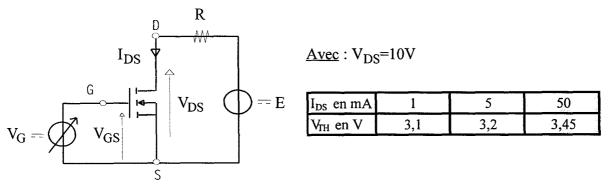

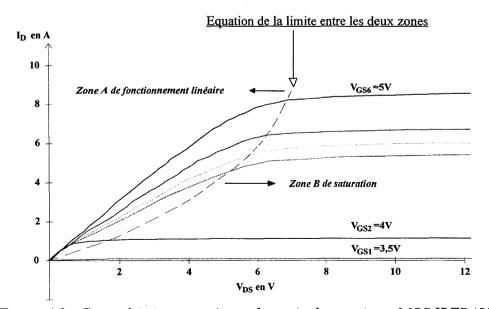

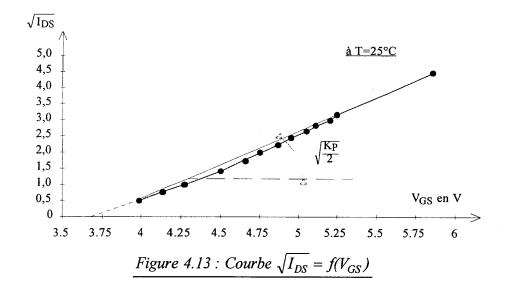

| IV.1.1) Détermination des paramètres du générateur de courant                 | 53  |

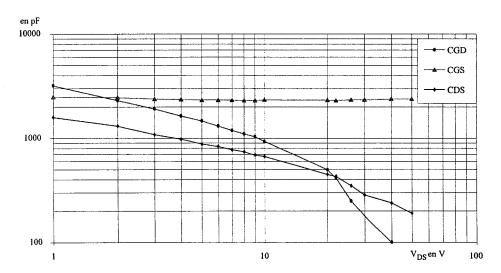

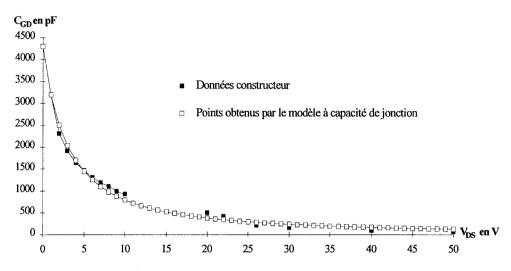

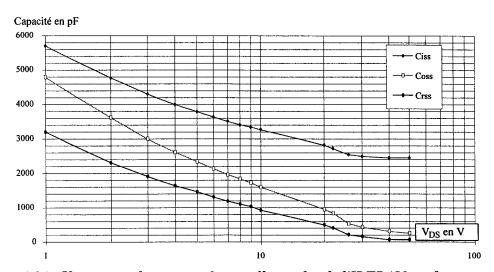

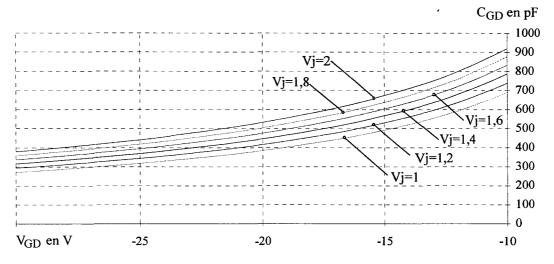

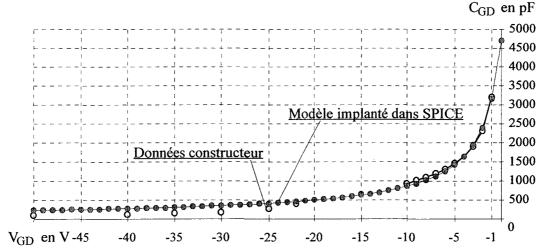

| IV.1.2) Détermination des capacités interélectrodes.                          | 57  |

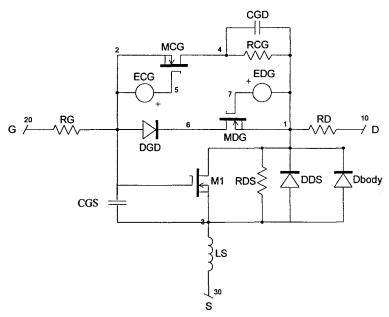

| IV.2) Modèles SPICE                                                           | 60  |

| IV.2.1) Les différents modèles MOS du logiciel SPICE                          | 61  |

| IV.2.2) Description du transistor IRFP450 de la bibliothèque SPICE            | 65  |

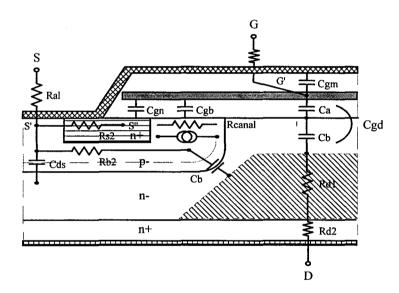

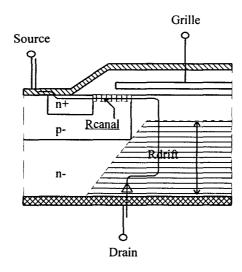

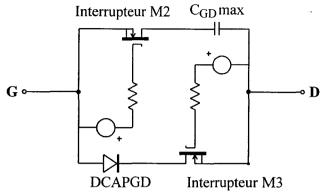

| IV.3) Modèle SPICE modifié                                                    | 67  |

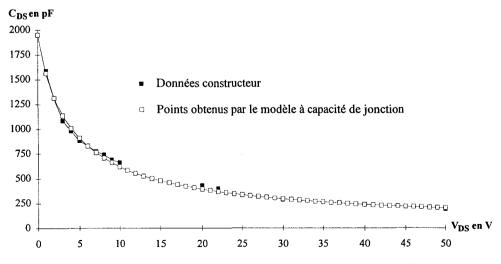

| IV.3.1) Modélisation de la résistance R <sub>DS</sub>                         | 68  |

| IV.3.2) Modélisation du canal                                                 | 69  |

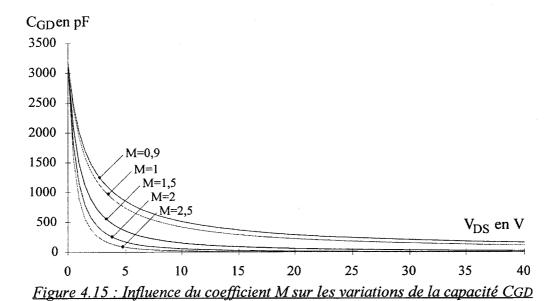

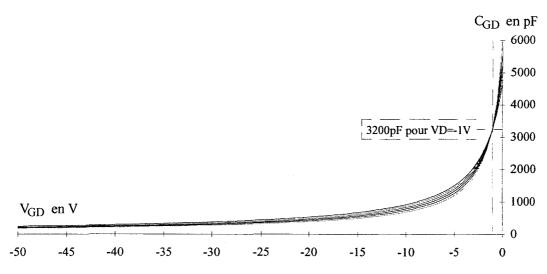

| IV.3.3) Modélisation des capacités interélectrodes du MOS IRFP450             | 71  |

| IV.3.4) Description du modèle modifié final de l'IRFP450                      | 78  |

| CHAPITRE V : Modélisation d'une cellule à interrupteurs deux segments         |     |

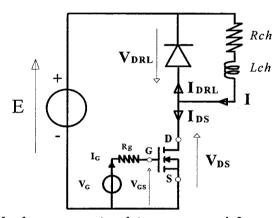

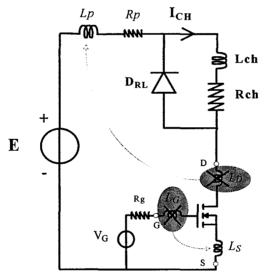

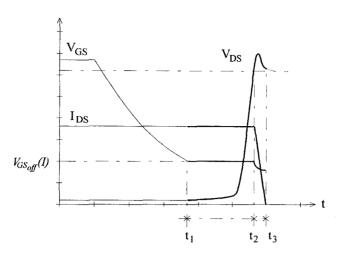

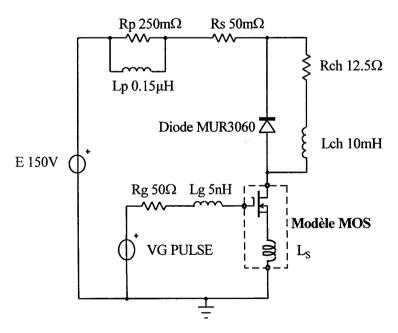

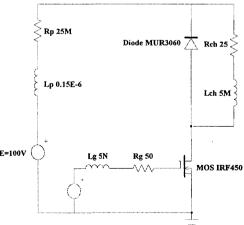

| V.1) Description de la commutation MOS-diode                                  | 81  |

| V.1.1) Introduction                                                           | 81  |

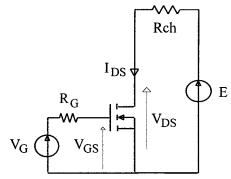

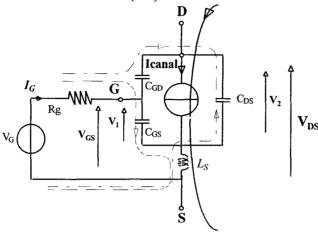

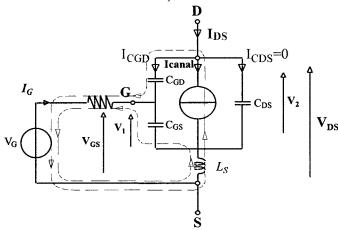

| V.1.2) Modélisation de la cellule et de son circuit de commande               | 82  |

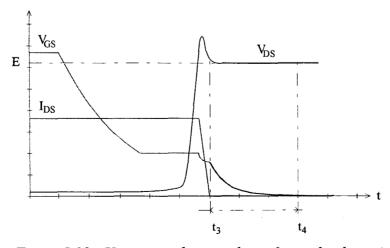

| V.2) Modèle comportemental                                                    | 84  |

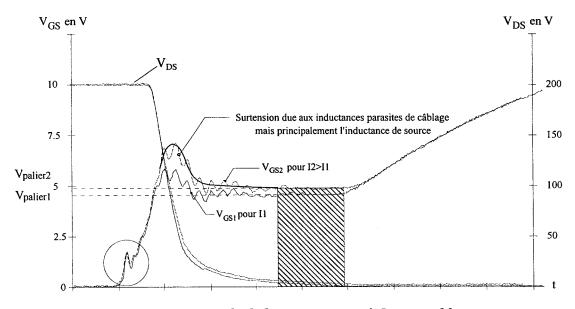

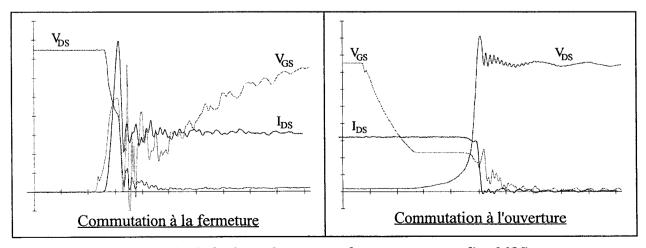

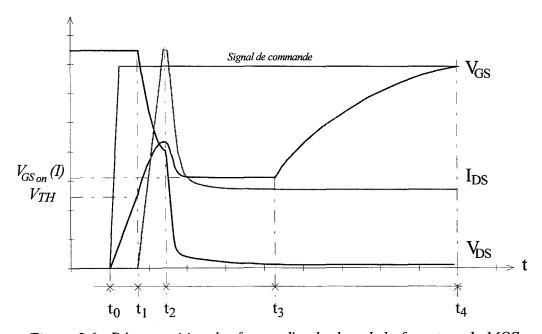

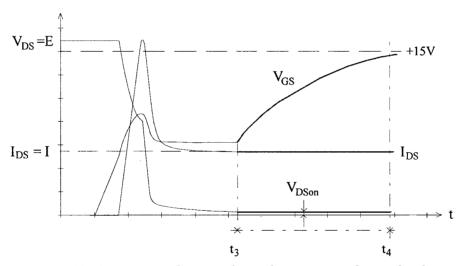

| V.2 .1) Etude de la commutation à la fermeture du transistor MOS              | 84  |

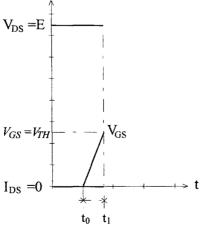

| V.2.1.1) Première phase: (t <sub>0</sub> -t <sub>1</sub> )                    | 84  |

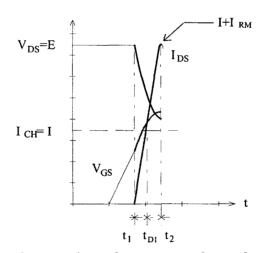

| $V.2.1.2$ ) Deuxième phase: $(t_1-t_2)$                                       | 87  |

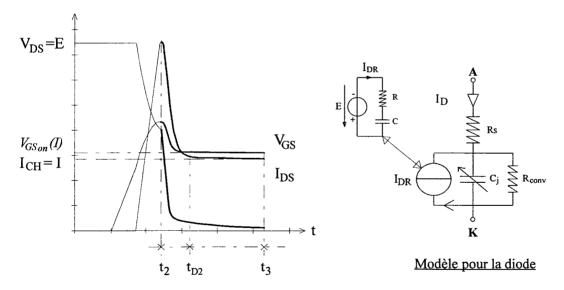

| V.2.1.3) Troisième phase: (t <sub>2</sub> -t <sub>3</sub> )                   | 88  |

| V.2.1.4) Quatrième phase: (t <sub>3</sub> -t <sub>4</sub> )                   | 89  |

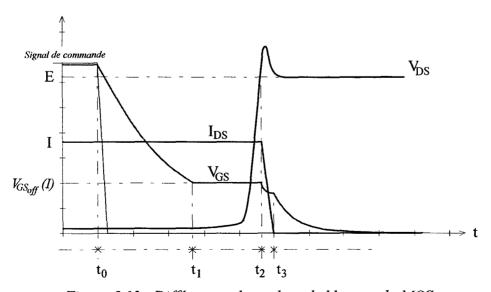

| V.2.2) Etude de la commutation à l'ouverture du transistor MOS                | 90  |

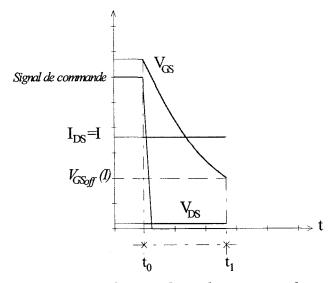

| V.2.2.1) Première phase: (t <sub>0</sub> -t <sub>1</sub> )                    | 91  |

| V.2.2.2) Deuxième phase: (t <sub>1</sub> -t <sub>2</sub> )                    | 92  |

| V.2.2.3) Troisième phase: (t <sub>2</sub> -t <sub>3</sub> )                   | 93  |

| V.2.2.4) Quatrième phase: (t <sub>3</sub> -t <sub>4</sub> )                   | 93  |

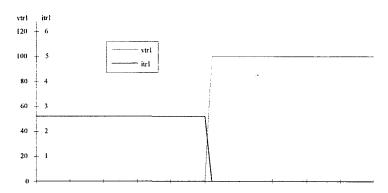

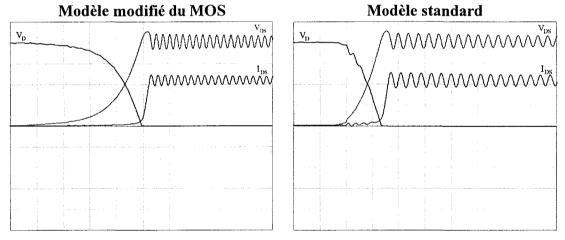

| V.3) Modèles SPICE standard et modifié                                        | 94  |

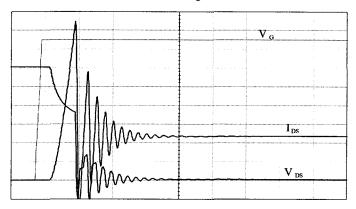

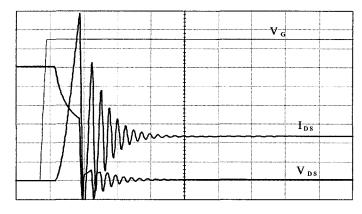

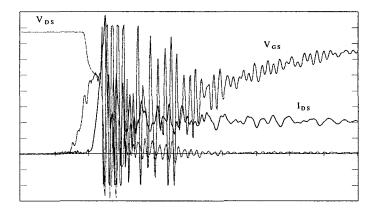

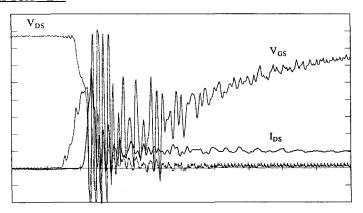

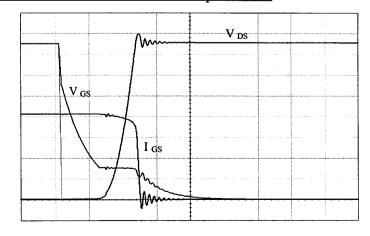

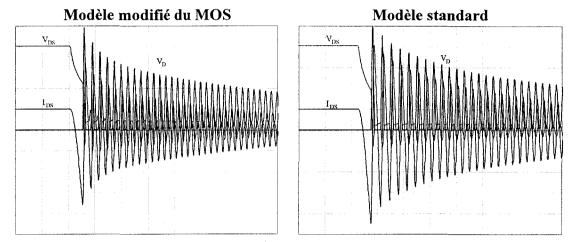

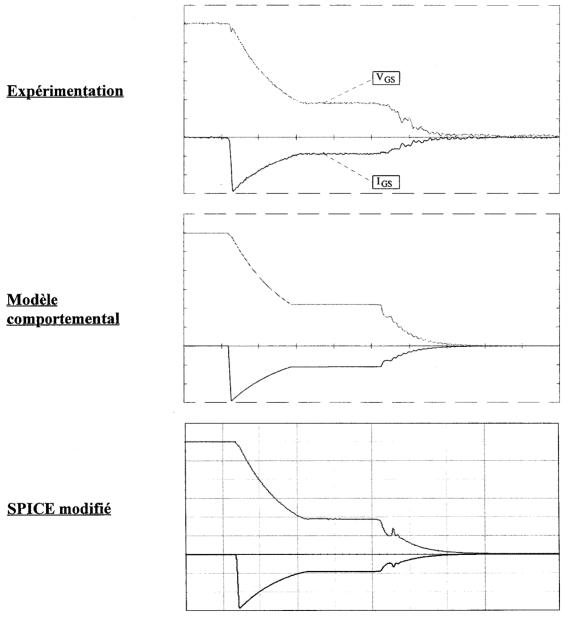

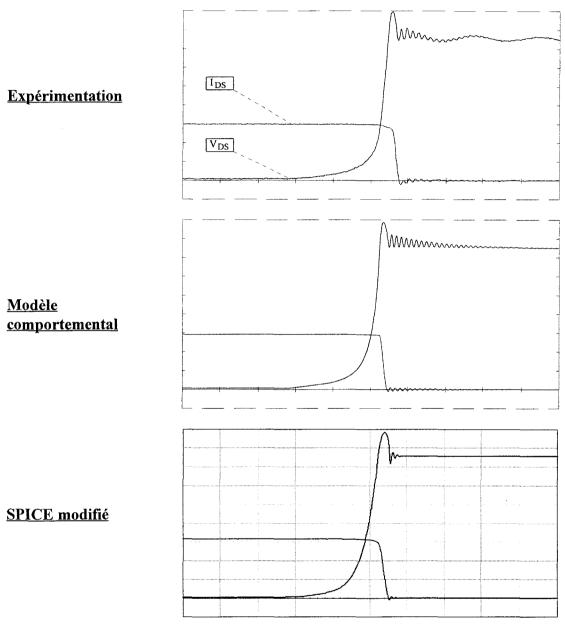

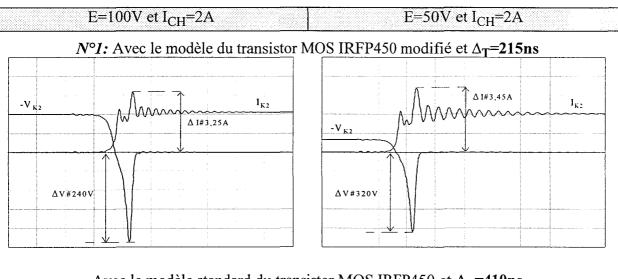

| V.3.1) Comparaison des deux modèles à la mise en conduction du transistor MOS | 95  |

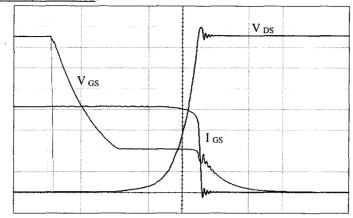

| V.3.2) Comparaison des deux modèles au blocage du transistor                  | 97  |

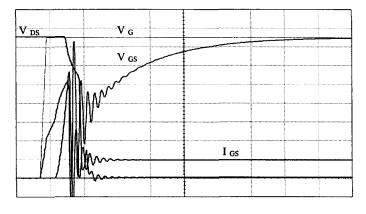

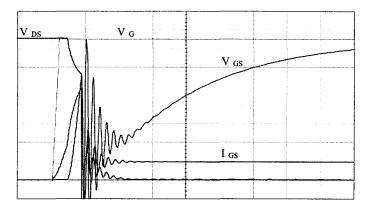

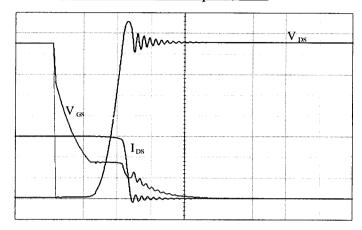

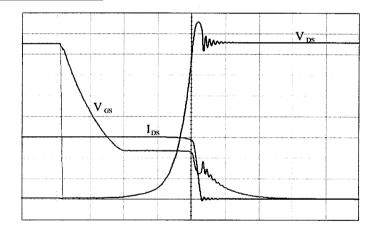

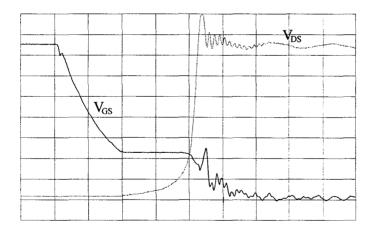

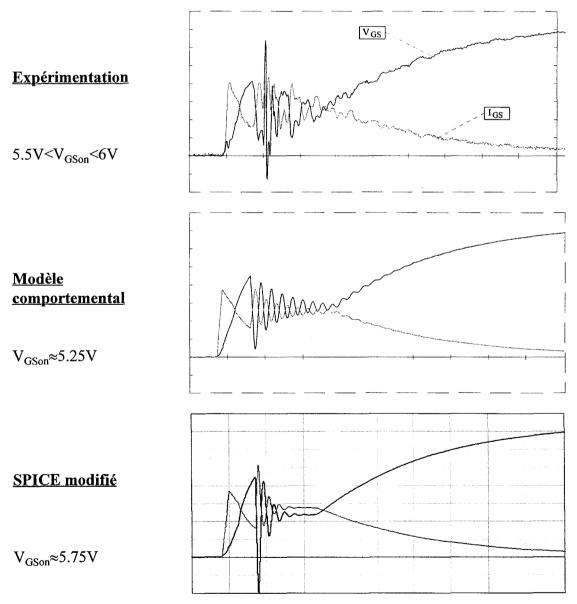

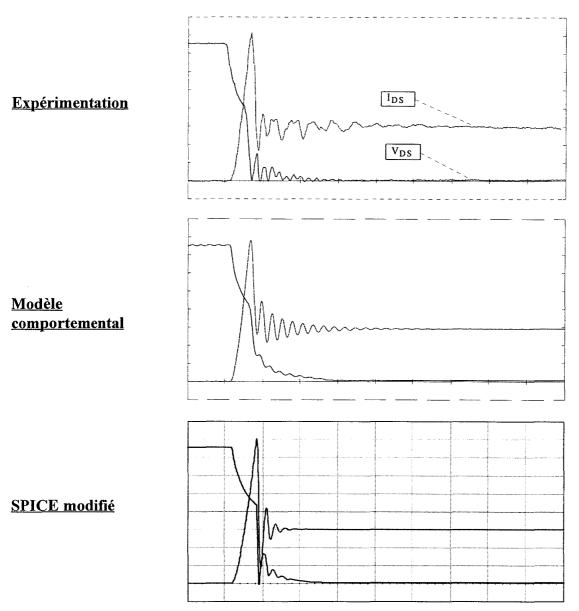

| V.4) Comparaison des modèles avec les résultats expérimentaux                 | 102 |

| CHAPITRE VI : Modélisation de la cellule à interrupteurs trois segments   |     |

|---------------------------------------------------------------------------|-----|

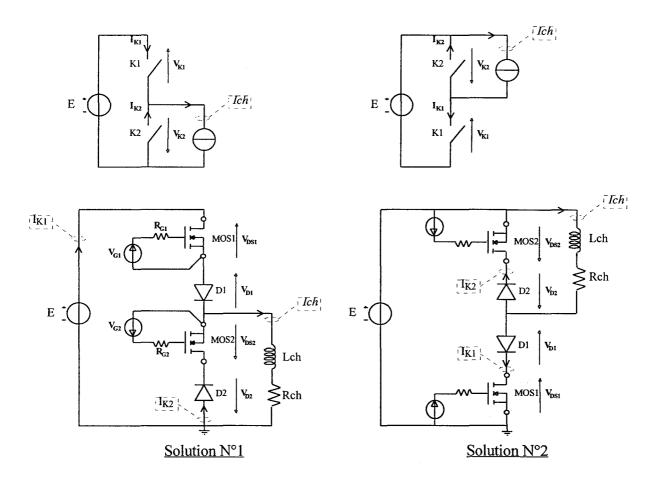

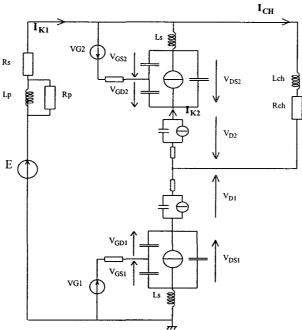

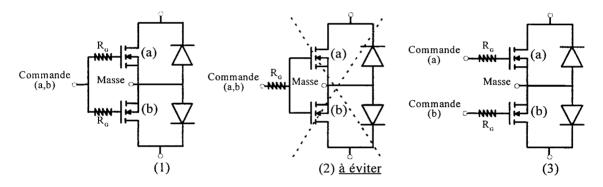

| VI.1) Présentation générale                                               | 108 |

| VI.1.1) Choix de la disposition des interrupteurs                         | 108 |

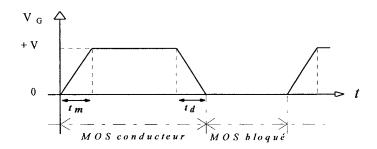

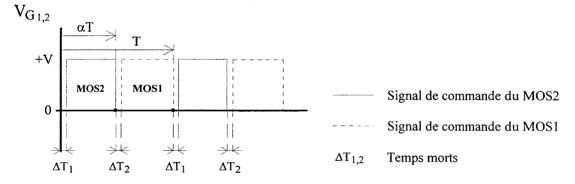

| VI.1.2) Elaboration des signaux de commande des MOS                       | 109 |

| VI.1.3) Conditions imposées lors de la manipulation                       | 110 |

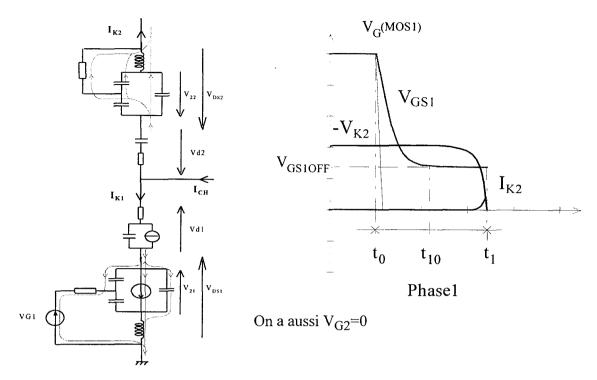

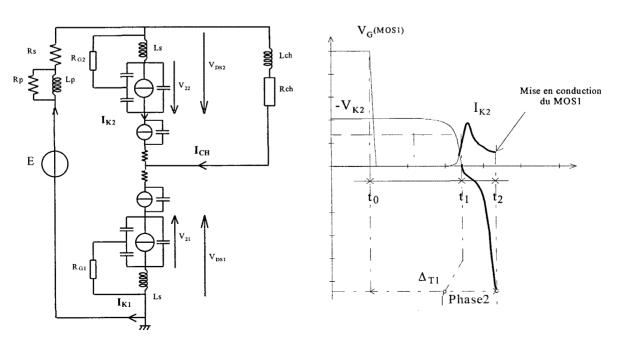

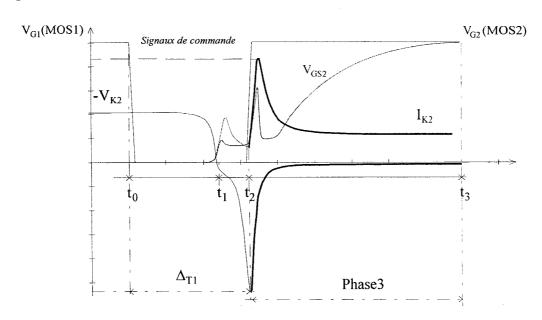

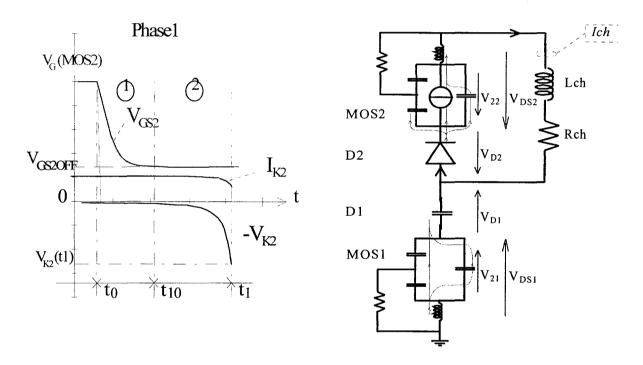

| VI.2) Etude de la commutation de l'interrupteur K1 vers K2                | 110 |

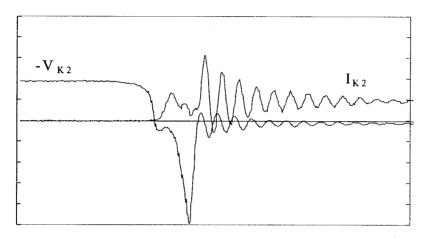

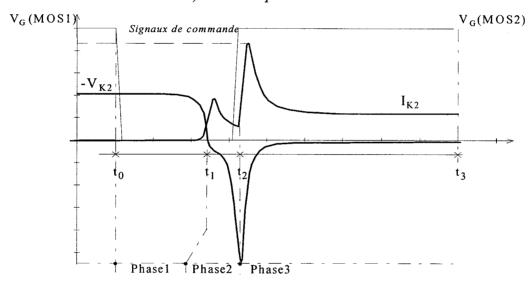

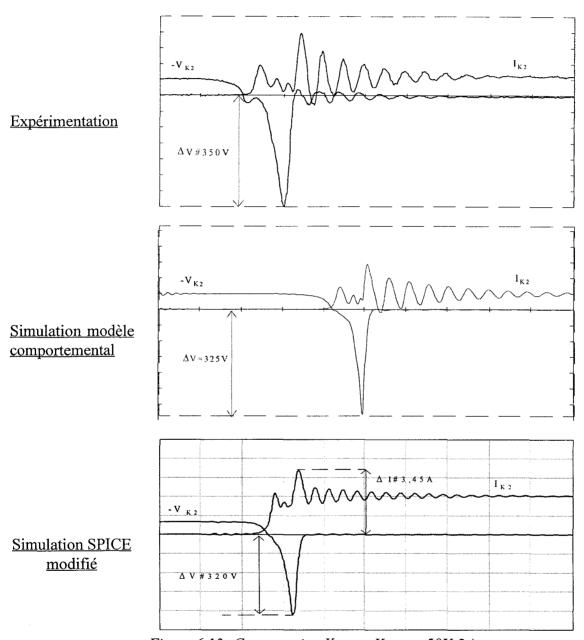

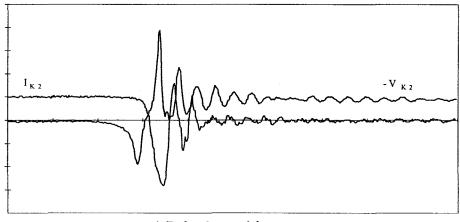

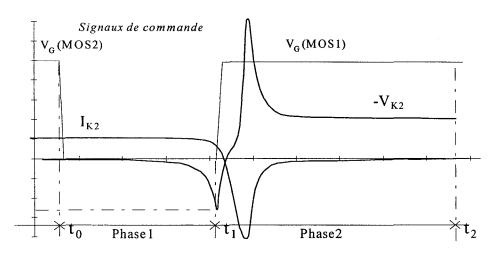

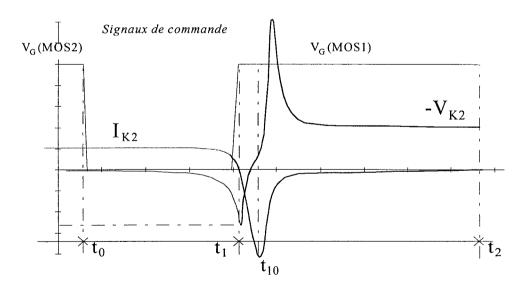

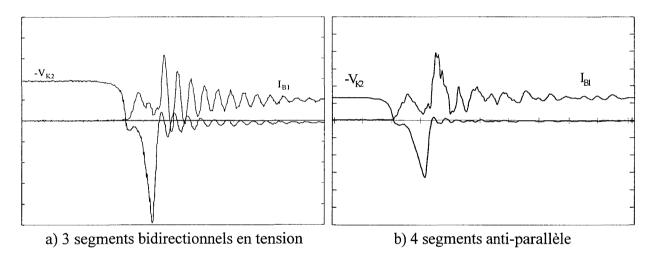

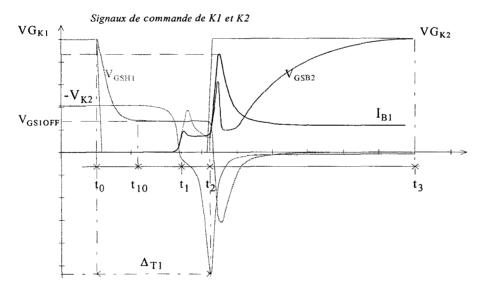

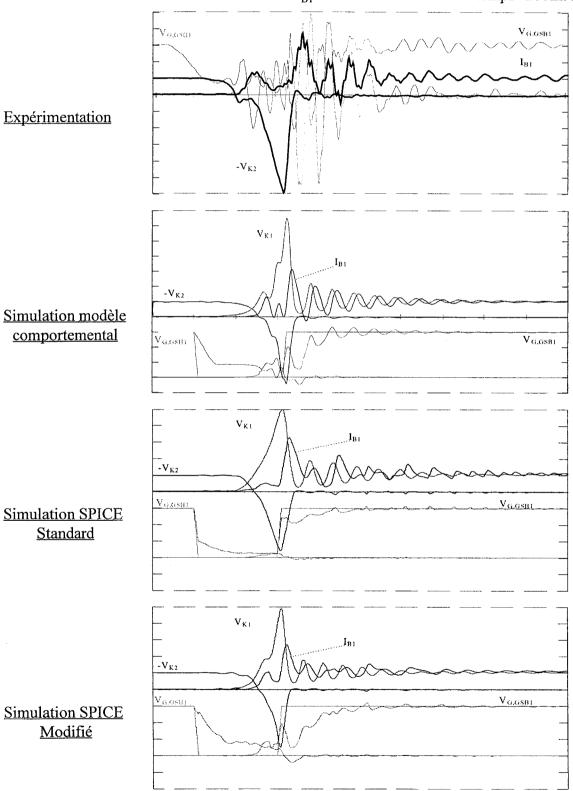

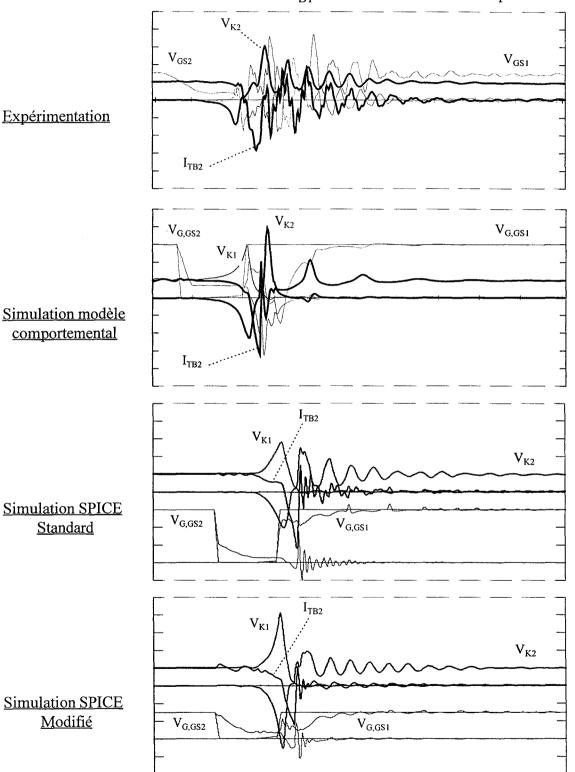

| VI.2.1) Formes d'ondes                                                    | 110 |

| VI.2.2) Modèle comportemental                                             | 111 |

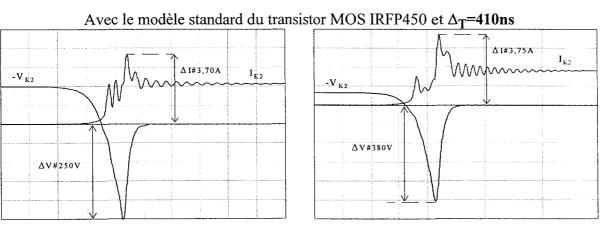

| VI.2.3) Modèles SPICE standard et modifié                                 | 117 |

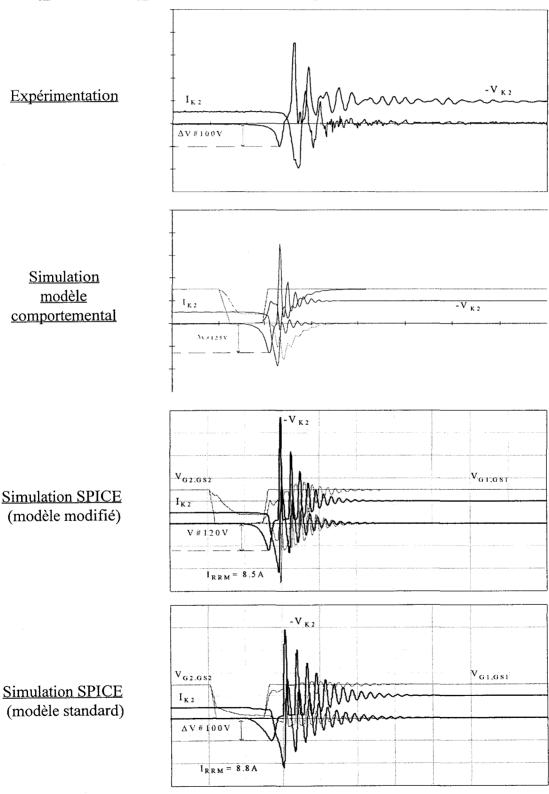

| VI.2.4) Comparaison des modèles avec les résultats expérimentaux          | 119 |

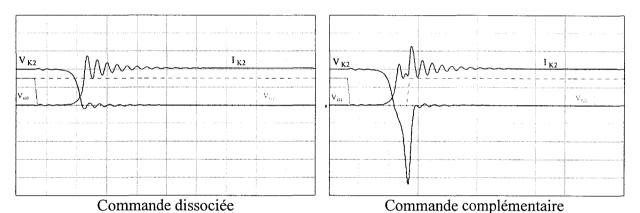

| VI.2.5 Commande dissociée                                                 | 122 |

| VI.3) Etude de la commutation de K <sub>2</sub> vers K <sub>1</sub>       | 124 |

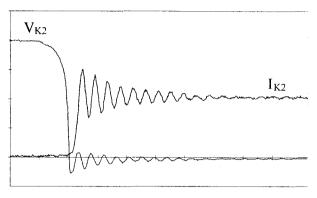

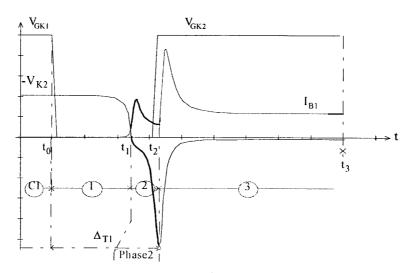

| VI.3.1) Formes d'ondes                                                    | 124 |

| VI 3.2) Modèle comportemental                                             | 125 |

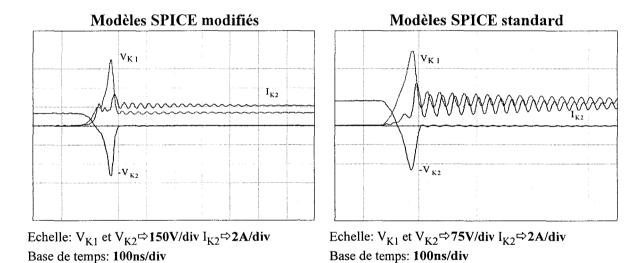

| VI.3.3) Comparaisons entre les résultats expérimentaux et les simulations | 128 |

| CHAPITRE VII : Modélisation de la cellule de commutation à IBTC           |     |

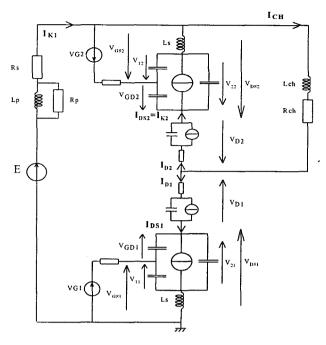

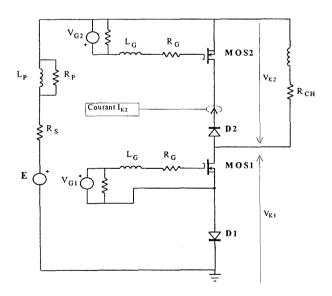

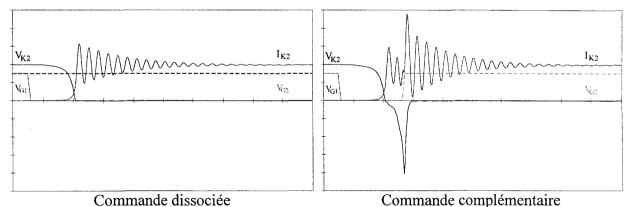

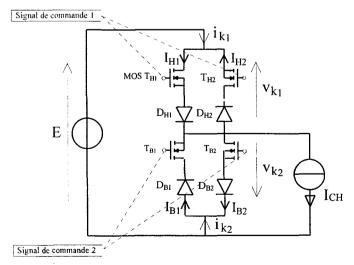

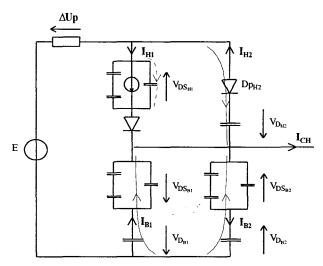

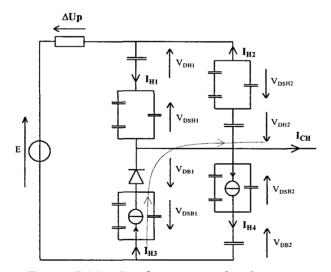

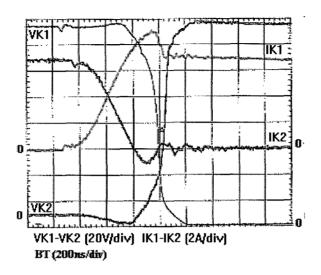

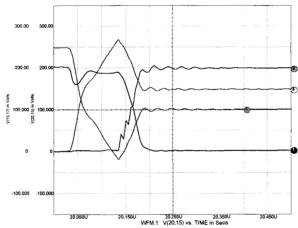

| VII.1) Etude de la commutation de K1 vers K2                              | 134 |

| VII.1.1) Formes d'ondes                                                   | 135 |

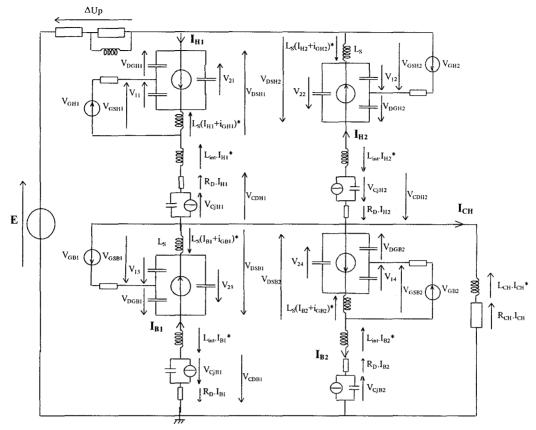

| VII.1.2) Modèle comportemental                                            | 135 |

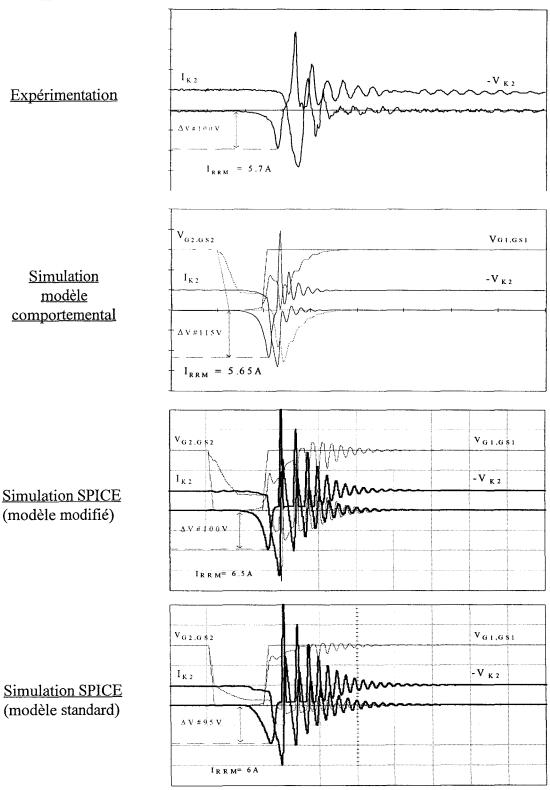

| VII.1.3) Relevés expérimentaux et résultats de simulation                 | 142 |

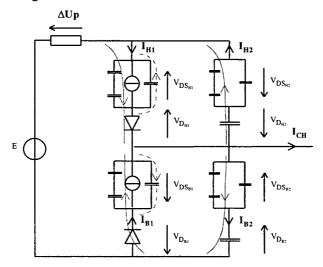

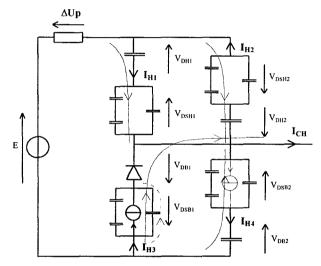

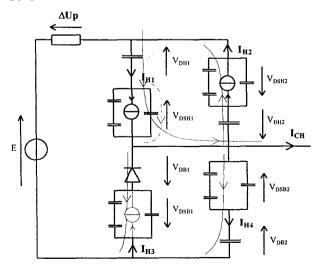

| VII.2) Etude de la commutation de K2 vers K1                              | 145 |

| VII.2.1) Modèle comportemental                                            | 146 |

| VII.2.2) Relevés expérimentaux et résultats de simulation                 | 148 |

| VII.3) Analyse générale des résultats de simulation                       | 151 |

| CONCLUSION                                                                | 155 |

| BIBLIOGRAPHIE                                                             | 158 |

| GLOSSAIRE                                                                 | 163 |

INTRODUCTION

La plupart des systèmes de l'Electronique de Puissance utilisent une cascade de convertisseurs dont les fonctionnements sont découplés grâce à l'utilisation d'éléments intermédiaires de stockage d'énergie, condensateurs ou inductances mais la puissance moyenne qui sort d'un convertisseur est égale à celle qui rentre dans un autre.

Dans certains cas, il est possible de remplacer ces convertisseurs successifs et leurs éléments intermédiaires par un étage de conversion unique appelé convertisseur matriciel ou direct. Dans ce type de convertisseur, chacune des bornes d'entrée est reliée à chacune des bornes de sortie par un interrupteur, l'ensemble formant une matrice d'interrupteurs. Avec cette structure, le transfert de puissance peut s'effectuer dans les deux sens entre les sources connectées. L'absence de tout élément intermédiaire de stockage permet d'avoir à tout instant l'égalité entre les puissances instantanées à l'entrée et à la sortie du convertisseur, dans l'hypothèse où les pertes dans les interrupteurs sont négligées, alors que les puissances réactives à l'entrée et à la sortie peuvent être différentes. La nature de l'énergie électrique (continue ou alternative) et la fréquence des tensions et des courants de chaque côté du convertisseur sont indépendantes.

Cependant, les interrupteurs doivent satisfaire à certaines conditions, et les sources reliées doivent être de natures différentes (de courant ou de tension). La commande des interrupteurs doit empêcher la mise en court-circuit d'une (ou des) source(s) de tension, et l'ouverture du circuit d'une (ou des) source(s) de courant.

Les interrupteurs d'un convertisseur matriciel doivent être capables de supporter une tension positive ou négative à l'état ouvert, et de laisser passer un courant positif ou négatif à l'état fermé. On les appelle IBTC (Interrupteurs Bidirectionnels Totalement Commandables) ou Bi-bi (Bidirectionnels bicommandables). De tels interrupteurs ne sont pas actuellement disponibles à l'état de composants discrets. Ils doivent être synthétisés par l'association de transistors et de diodes.

Les convertisseurs matriciels n'existent encore qu'à l'état de prototypes de laboratoire. Malgré les nombreuses publications sur le sujet, ils n'ont pas encore pu démontrer d'avantages significatifs sur les convertisseurs classiques et n'ont donc pas trouvé de créneau d'application.

L'objectif initial de notre travail était de proposer un modèle d'IBTC réalisé par association de transistors IGBT et de diodes, à la fois simple et fidèle pour pouvoir étudier les contraintes subies par ses éléments constitutifs dans le cadre d'une cellule élémentaire de commutation, et développer des dispositifs de commande capables de minimiser ces contraintes.

L'IGBT et la diode étant tous deux des composants bipolaires, pour lesquels il est difficile d'obtenir un compromis entre la simplicité et la précision du modèle, nous avons dû nous limiter à l'utilisation de transistors MOS, composants unipolaires plus faciles à modéliser, pour la construction des IBTC.

Dans le premier chapitre, nous présentons les différentes cellules de commutation, de la cellule élémentaire à la cellule à quatre quadrants, en prenant la bidirectionnalité en tension comme critère principal.

Le chapitre II passe en revue les différentes méthodes utilisées pour modéliser les interrupteurs de puissance à semi-conducteur.

Les chapitres III et IV sont consacrés à l'élaboration des modèles comportementaux et à la modification des modèles SPICE de diode et de transistor MOS destinés à être associés dans les cellules de commutation.

Ces différents modèles sont assemblés morceau par morceau pour être validés en comparant les relevés expérimentaux et les résultats de simulation obtenus successivement:

- dans la cellule élémentaire de commutation au chapitre V

- dans la cellule à interrupteurs 3 segments bidirectionnels en tension au chapitre VI

- dans la cellule à IBTC au chapitre VII.

## Chapitre I:

LES CELLULES DE COMMUTATION

#### I.1) Introduction

Dans ce chapitre, nous rappelons quelques notions sur la cellule de commutation élémentaire que l'on retrouvera tout au long de ce mémoire. Nous expliquons les mécanismes qui permettent d'aboutir à cette cellule élémentaire, et pourquoi son étude conditionne la totalité des commutations dans les convertisseurs directs. Notre objectif consiste à étudier le fonctionnement de cette cellule lorsque les interrupteurs qui la composent sont bidirectionnels en courant et en tension. L'élaboration et la mise en oeuvre d'un modèle numérique de ce type de composant nécessitent une progression logique dans notre travail. Nous aboutirons à ce résultat en augmentant successivement le nombre de segments des interrupteurs de la cellule de commutation.

Un convertisseur statique d'énergie électrique a pour rôle de permettre le réglage du transit d'énergie entre un générateur et un récepteur, et/ou de modifier la présentation de cette énergie qui peut être continue ou alternative. Les générateurs et les récepteurs peuvent être classés en deux catégories : « sources » de tension ou de courant, suivant que leur nature empêche les discontinuités de la tension à leurs bornes ou du courant qui les traverse.

Le convertisseur qui assure la liaison entre le générateur et le récepteur est qualifié de direct s'il est formé uniquement d'interrupteurs. Il est indirect s'il comporte en plus de ces indispensables interrupteurs des éléments de stockage momentané de l'énergie.

#### I.2) Les interrupteurs

Nous allons d'abord présenter les caractéristiques d'un interrupteur parfait, puis celles d'un interrupteur à semi-conducteur en faisant apparaître les contraintes imposées par ce type de composant, qui reste actuellement celui qui permet de s'approcher le plus d'un interrupteur idéal.

#### I.2.1) Interrupteur parfait

Un interrupteur possède 2 états : ouvert ou fermé.

A l'état ouvert, un interrupteur parfait impose une valeur nulle au courant i qui le traverse, alors que la tension v à ses bornes est imposée par le circuit extérieur et peut être positive ou négative.

A l'état fermé, un interrupteur parfait impose une valeur nulle à la tension v entre ses bornes, alors que le courant i qui le traverse est imposé par le circuit extérieur et peut être positif ou négatif.

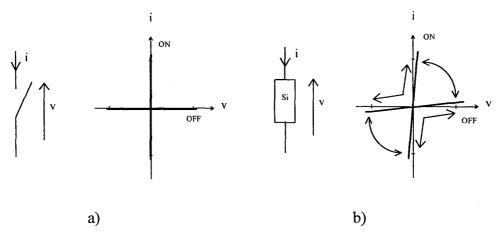

Les caractéristiques statiques d'un interrupteur parfait sont donc formées de 4 segments confondus avec les axes v et i (figure I.1.a)

Les commutations ou changements d'état d'un interrupteur parfait sont immédiates, et le point de fonctionnement passe instantanément d'un segment à un autre dans le sens voulu par l'opérateur.

Figure I.1 : Caractéristiques des interrupteurs

#### I.2.2) Interrupteur à semi-conducteur

Le comportement d'un interrupteur à semi-conducteur s'écarte de celui d'un interrupteur parfait à la fois par ses caractéristiques statiques et dynamiques.

Un interrupteur à semi-conducteur est constitué d'un morceau de Silicium dont la résistance peut varier entre une valeur très élevée correspondant à l'état ouvert de l'interrupteur, et une valeur très faible correspondant à l'état passant. La première imperfection de ce type d'interrupteur apparait donc sur les caractéristiques statiques sous la forme d'une tension v faible mais non nulle à l'état fermé, et d'un courant i faible mais non nul à l'état ouvert. En première approximation on peut admettre que les résistances  $r_{ON}$  à l'état fermé et  $r_{OFF}$  à l'état ouvert sont constantes, et donc que les caractéristiques statiques d'un interrupteur à semi-conducteur qui serait bidirectionnel en courant et en tension ont l'allure indiquée sur la figure I.1.b.

Les caractéristiques dynamiques correspondent au passage d'un état à l'autre de l'interrupteur, qui se fait par modulation de la conductivité du Silicium. Cette modulation peut être obtenue de 2 façons :

1°) par modulation externe, quand le changement d'état est dû au circuit extérieur: la modulation est alors provoquée par le changement de polarité de la tension qui apparaît aux bornes de l'interrupteur ou du courant qui le traverse, ce changement de polarité étant consécutif aux variations imposées par le circuit extérieur. C'est ce type de modulation qui provoque par exemple le changement d'état d'une diode.

2°) par modulation interne quand le changement d'état est dû à un signal de commande: la modulation est ici consécutive à l'application d'un courant ou d'une tension sur une électrode de commande de l'interrupteur. La résistance apparente de l'interrupteur passe

d'une valeur faible à une valeur élevée ou inversement mais en restant toujours positive, ce qui impose au point de fonctionnement de se déplacer dans un des 2 quadrants pour lesquels le produit v x i est positif.

En fonction du type de modulation, le point de fonctionnement ne peut donc se déplacer :

- 1°) que sur les segments de la caractéristique statique lors d'une commutation où i et v changent de signe: la commutation est dite douce car elle se produit théoriquement sans pertes.

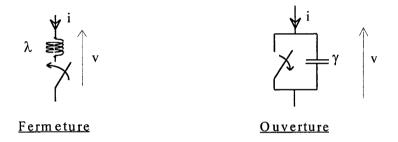

- $2^{\circ}$ ) que dans un des 2 quadrants pour lesquels le produit v x i est positif lors d'une commutation où i et v gardent le même signe: la commutation est dite dure car elle est accompagnée de pertes dans l'interrupteur. En première approximation, pour tenir compte des temps de commutation, on peut modéliser un interrupteur commandé à la fermeture par un interrupteur idéal en série avec une inductance  $\lambda$ , et un interrupteur commandé à l'ouverture par un interrupteur idéal en parallèle avec une capacité  $\gamma$ .

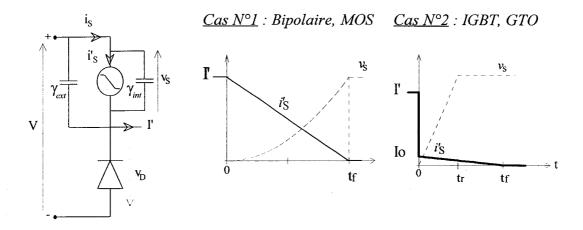

Figure 1.2 : Modèles rudimentaires d'interrupteurs à semi-conducteur

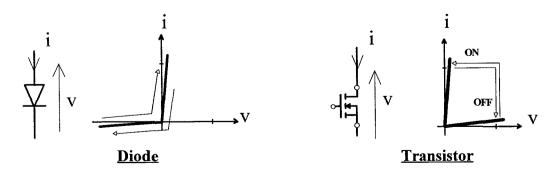

Parmi les composants électroniques de base utilisés pour réaliser les interrupteurs des convertisseurs statiques, nous ne considèrerons que la diode et le transistor, qui sont tout deux unidirectionnels en courant et en tension et dont les caractéristiques statiques se réduisent donc à deux segments. Pour le transistor, on s'intéressera exclusivement au MOSFET, mais les considérations développées dans ce chapitre s'appliquent également au bipolaire, à l'IGBT et au thyristor GTO asymétrique.

Figure 1.3 : Caractéristiques simplifiées de la diode et du transistor

Les commutations de la diode correspondent au passage d'un courant i positif à l'état passant vers une tension v négative à l'état bloqué, ou au passage inverse, et ne peuvent être que douces.

Les commutations du transistor font passer le point de fonctionnement d'un courant i positif quand l'interrupteur est fermé vers une tension v positive quand il est ouvert, et réciproquement, et doivent donc être commandées à partir de créneaux de tension appliqués entre la grille et la source dans le cas d'un MOSFET.

#### I.3) Les fonctions « interrupteur »

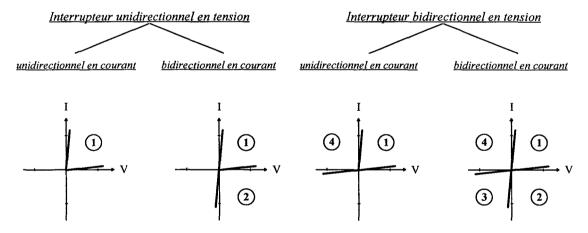

Suivant le type d'application envisagé, les caractéristiques statiques des interrupteurs à utiliser dans un convertisseur peuvent être :

à 2 segments : unidirectionnel en courant et en tension

à 3 segments : unidirectionnel en courant et bidirectionnel en tension ou unidirectionnel

en tension et bidirectionnel en courant

à 4 segments : bidirectionnel en courant et en tension.

Figure 1.4: les quatre fonctions « interrupteur » commandables

La fonction « interrupteur à 2 segments » a obligatoirement une caractéristique du type diode ou transistor, et peut donc être réalisée avec un seul composant.

La fonction « interrupteur à 3 segments bidirectionnel en courant » ne peut être réalisée que par association complémentaire d'interrupteurs à 2 segments en mettant en commun leurs segments de tension : une diode est branchée en parallèle inverse sur un transistor. Un tel interrupteur ne peut être commandé que dans le quadrant correspondant aux segments du transistor.

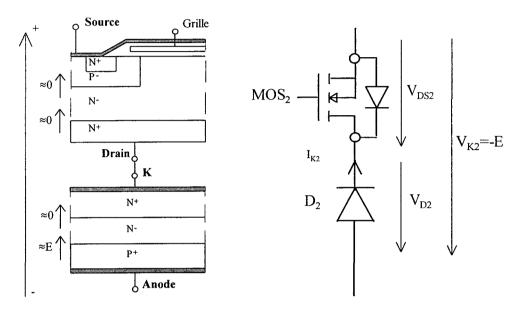

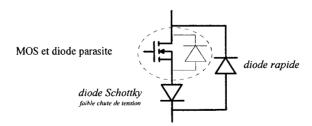

La fonction « interrupteur à 3 segments bidirectionnel en tension » peut être réalisée encore par association complémentaire d'interrupteurs à 2 segments, mais en mettant en commun leurs segments de courant : une diode est branchée en série avec un transistor. Comme le précédent, cet interrupteur ne peut être commandé que dans le quadrant correspondant aux segments du transistor.

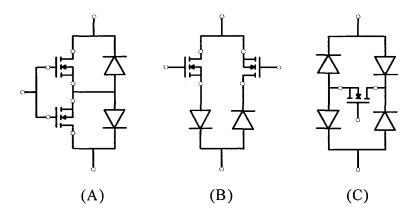

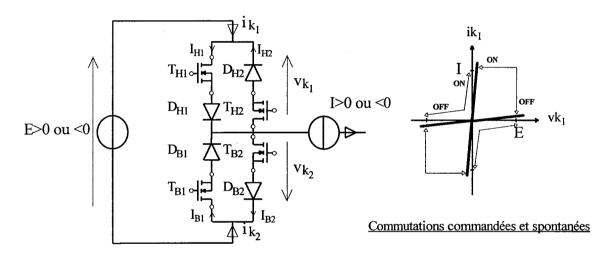

La fonction « interrupteur à 4 segments » peut être synthétisée par le branchement en antiparallèle de deux interrupteurs 3 segments bidirectionnels en tension (B), ou le branchement en anti-série de deux interrupteurs 3 segments bidirectionnels en courant (A). Une troisième solution consiste à insérer un transistor unique dans un pont à 4 diodes. Dans la suite du mémoire, on désignera la fonction interrupteur bidirectionnel en courant et en tension totalement commandable par le terme IBTC.

Figure 1.5: Réalisation d'un IBTC

#### I.4) Cellule élémentaire de commutation

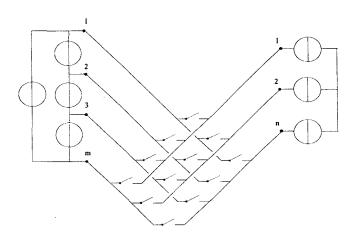

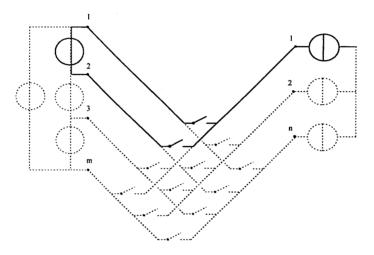

La structure des convertisseurs directs généralisés est présentée sur la figure 1.6. Elle est basée sur la théorie des structures matricielles développée par VENTURINI en 1980. Dans l'exemple présenté, les sources de tension  $V_m$  sont interconnectées avec les sources de courant  $I_n$  grâce à une matrice d'interrupteurs  $K_{mn}$ . Dans les applications usuelles, on travaille avec des rangs de matrice ramenés à  $(3\times2)$ ,  $(2\times2)$  et  $(2\times1)$ . Les stratégies de commande appliquées sur les interrupteurs de la matrice permettent de réaliser toutes les fonctions de conversion possibles s'ils sont bidirectionnels en courant et en tension.

Figure 1.6 : Le convertisseur direct généralisé

En appliquant les règles élémentaires qui découlent de la nature des sources :

**Règle n°1)** Il ne faut jamais court-circuiter une source de tension sinon il apparait une surintensité dans le circuit

**Règle n°2)** Il ne faut jamais ouvrir le circuit d'une source de courant sinon il apparait une surtension dans le circuit

on déduit qu'il ne peut et qu'il ne doit y avoir dans chaque configuration qu'un et un seul interrupteur passant par série d'interrupteurs reliés à une même source de courant. Pour respecter cette condition lors d'une commutation, il faut obligatoirement que les interrupteurs d'une même série changent d'état deux à deux. Ceux-ci forment une cellule de commutation élémentaire semblable à celle présentée sur la figure 1.7.

Figure 1.7: Isolation d'une cellule de commutation élémentaire

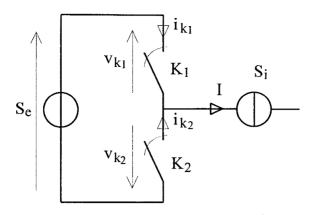

Nous allons effectuer une présentation condensée des cellules élémentaires de commutation obtenues à partir des différentes fonctions « interrupteur » en nous appuyant sur la méthode de synthèse développée par l'équipe de H.FOCH [17,18]. Nous avons choisi de classer ces cellules en deux familles en fonction de leur architecture de réalisation. Une cellule élémentaire de commutation est constituée de deux interrupteurs  $K_1$  et  $K_2$  (figure 1.8). L'identification des fonctions « interrupteur » dépend de la nature et de la réversibilité des sources  $S_e$  et  $S_i$  à interconnecter. De plus, ces deux interrupteurs doivent posséder des caractéristiques statiques similaires, c'est à dire travailler dans le même nombre de quadrants, pour avoir un fonctionnement optimal de la cellule.

Figure 1.8: Cellule de commutation élémentaire.

On peut dénombrer toutes les combinaisons réalisables en fonction des caractéristiques de chacune des sources (Tab 1.1).

| ·                                | $S_i \Rightarrow Unidirectionnel$ | $S_i \Rightarrow Bidirectionnel$ |

|----------------------------------|-----------------------------------|----------------------------------|

| S <sub>e</sub> ⇒ Unidirectionnel | 2 segments                        | 3 segments                       |

| S <sub>e</sub> ⇒ Bidirectionnel  | 3 segments                        | 4 segments                       |

Tableau 1.1 : Synthèse des interrupteurs en fonction des caractéristiques des sources.

Il y a quatre solutions distinctes : elles nécessitent l'utilisation d'autant de fonctions « interrupteur » différentes. Les informations indiquées dans les cases ombrées du tableau ne correspondent pas à la seule solution envisageable. Elles définissent une limite minimale du nombre de quadrants de travail nécessaires à chaque cellule. Nous avons choisi de réaliser l'étude des différentes cellules de commutation en fonction de la symétrie en tension des interrupteurs, en présentant les quatre configurations possibles d'interrupteurs qui suffisent à résoudre l'ensemble des solutions réalisables.

#### I.5) Cellules élémentaires à interrupteurs unidirectionnels en tension

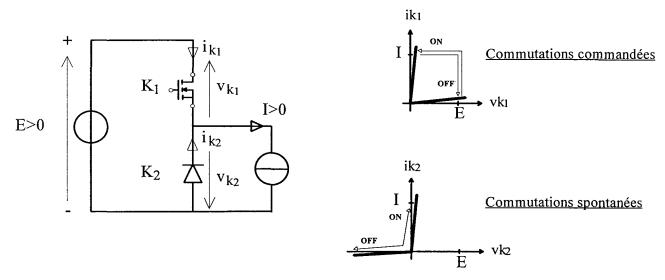

#### I.5.1) Interrupteurs unidirectionnels en courant (deux segments)

La cellule élémentaire présentée sur la figure 1.9. permet de relier deux sources non réversibles en courant et en tension. Ce résultat est obtenu par l'utilisation de deux interrupteurs, chacun d'eux étant unidirectionnel en tension et en courant. Il existe cependant une différence dans le fonctionnement de ces deux interrupteurs. Pour l'interrupteur  $K_2$  les commutations sont spontanées ou douces (diode); par contre pour l'autre interrupteur  $K_1$ , elles sont commandées ou dures (transistor).

Figure 1.9: Cellule de commutation unidirectionnelle en tension et en courant

Cette cellule de commutation est constituée de deux interrupteurs à deux segments. Les deux sources sont non réversibles, définies positives; l'étude dynamique de cette structure se limite aux *deux* commutations possibles: du transistor  $K_1$  vers la diode  $K_2$  et vice-versa. Si on adopte les modèles rudimentaires présentés plus haut pour modéliser le transistor pendant les phases de commutation, on obtient les formes d'ondes simplifiées ci-dessous :

Figure 1.10: Formes d'ondes simplifiées

A la fermeture, la montée du courant  $i_{K1}$  se fait sous la pleine tension E; à l'ouverture, la remontée de la tension  $v_{K1}$  se fait alors que la totalité du courant I traverse encore le transistor. Les variations de  $i_{K2}$  et  $v_{K2}$  sont imposées par celles de  $i_{K1}$  et  $v_{K1}$ .

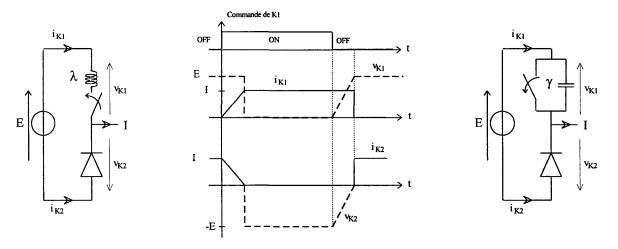

#### I.5.2) Interrupteurs bidirectionnels en courant (trois segments)

Cette cellule correspond à une source de courant réversible en courant. Le schéma de la figure 1.11 indique les modifications apportées à la configuration de la cellule de commutation.

Figure 1.11 : Cellule de commutation réversible en courant

Les indices B et H permettent de dissocier respectivement les éléments de la partie Basse de ceux du Haut. La cellule comprend quatre éléments, deux diodes et deux transistors. Chacun des deux interrupteurs synthétiques peut travailler dans les trois quadrants et voir son point de fonctionnement suivre les évolutions décrites sur la caractéristique de la figure 1.11.

Cette structure d'interrupteur est classée dans la même famille que la cellule précédente pour une raison simple : quelle que soit la commutation, on peut toujours se ramener à une commutation diode-transistor comme cela est présenté dans le tableau 1.2. Toutes les commutations propres à cette cellule font intervenir des combinaisons entre une des diodes (D<sub>H</sub> ou D<sub>B</sub>) et le transistor situé dans la partie opposée (T<sub>B</sub> ou T<sub>H</sub>). La logique de commande doit être appropriée et ne permettre ni court-circuit de la source E, ni ouverture du circuit de la source I.

| I>0 | Etude des commutations $T_H \Leftrightarrow D_B$ |

|-----|--------------------------------------------------|

| I<0 | Etude des commutations $T_B \Leftrightarrow D_H$ |

Tableau 1.2 : Définition du type de commutation en fonction du signe de I

Les formes d'ondes du paragraphe précédent (I.5.1) peuvent s'appliquer aux situations rencontrées dans cette cellule de commutation. Lorsque le courant I est positif, le comportement de la cellule peut être réduit à une cellule constituée de  $T_H$  et  $D_B$ . L'action occupée par chacun des composants associés:  $T_B$  pour  $D_B$ , et de façon symétrique  $T_H$  et  $D_H$  ne modifie pas le principe de fonctionnement. On retrouve de la même façon une cellule imbriquée  $T_B + D_H$  quand le courant est négatif.

En pratique, l'association des composants formant K<sub>1</sub> et K<sub>2</sub> fait intervenir des effets de couplage de type inductif et surtout capacitif. Si on désire un résultat plus précis, il sera nécessaire de tenir compte de ces phénomènes.

#### I.6) Cellules à interrupteurs bidirectionnels en tension

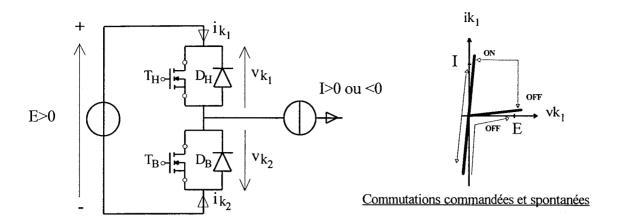

#### I.6.1) Interrupteurs unidirectionnels en courant (trois segments)

Cette cellule de commutation (figure 1.12) est réalisée au moyen de quatre composants, le même nombre d'éléments que dans celle présentée ci-dessus. La différence intervient dans leur arrangement puisque la diode et le transistor se trouvent maintenant placés en série. Cette fois, on se retrouve avec une cellule de commutation réversible uniquement en tension.

Figure 1.12 : Cellule de commutation réversible en tension

Les commutations existant entre les deux interrupteurs  $K_1$  et  $K_2$  font maintenant intervenir tous les éléments. On ne peut plus se rapporter à une simple commutation de type diodetransistor ou inversement comme on pouvait le faire avec les interrupteurs unidirectionnels en tension.

Lorsque l'un des deux interrupteurs est fermé, la tension aux bornes de la diode conductrice est nulle et la tension aux bornes de l'interrupteur est imposée par le transistor.

#### Quand un interrupteur est ouvert :

- si la tension à ses bornes est positive, elle est supportée entièrement par le transistor puisque la tension aux bornes de la diode ne peut pas être supérieure à zéro

- si la tension à ses bornes est négative, elle est supportée entièrement par la diode puisque la tension aux bornes du transistor ne peut pas être inférieure à zéro.

Pour étudier le fonctionnement de cette cellule, il suffit de connaître *deux* commutations sur les quatre possibilités envisageables que l'on détaille dans le tableau 1.3.

| E>0 | Commutation $T_H$ - $D_H$ $\Leftrightarrow$ $T_B$ - $D_B$ | Commutation $T_B$ - $D_B$ $⇔$ $T_H$ - $D_H$ |

|-----|-----------------------------------------------------------|---------------------------------------------|

| E<0 | Commutation $T_B$ - $D_B \Rightarrow T_H$ - $D_H$         | Commutation $T_H$ - $D_H$ $⇒$ $T_B$ - $D_B$ |

Tableau 1.3 : Définition du type de commutation en fonction du signe de E

Il n'y aura jamais de court-circuit de la source d'entrée E dans cette cellule de commutation. Pour les deux configurations de tension envisageables, on trouve des situations similaires aux précédentes en adaptant le rôle joué par chaque interrupteur. L'étude de cette structure se ramène à celle des commutations à la fermeture et à l'ouverture de  $K_1$  (combinaison de  $T_H+D_H$ ) et  $K_2$  (combinaison de  $T_B+D_B$ ). Les solutions correspondant à une tension E négative sont symétriques : il faut modifier les signes en fonction de la convention utilisée.

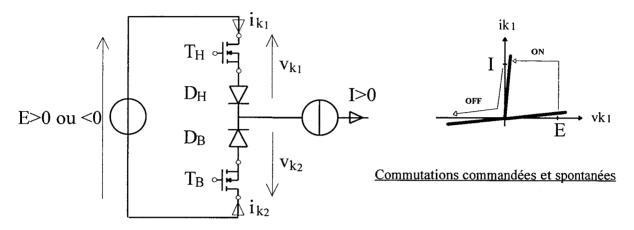

#### I.6.2) Interrupteurs bidirectionnels en courant

En ajoutant la bidirectionnalité en courant, on obtient un interrupteur à quatre segments. Ces interrupteurs sont nécessaires dans les cellules de commutation reliant deux sources réversibles en courant et en tension. Les deux fonctions interrupteur peuvent être réalisées ici par association anti-parallèle d'interrupteurs 3 segments bidirectionnels en tension comme ceux utilisés dans la cellule précédente.

Figure 1.13 : Cellule de commutation réversible en tension et en courant

Le nombre de commutations possibles sur cette structure s'élève à huit en fonction des différentes combinaisons de polarité des sources de tension E et de courant I. Cette cellule est classée dans la même famille que la cellule étudiée au paragraphe I.6.1 car les changements d'état des interrupteurs peuvent être ramenés en partie à ceux entre deux interrupteurs bidirectionnels en tension et unidirectionnels en courant.

Une seule différence apparaît, ce sont les commutations entre  $T_{H1}$ - $D_{H1}$  et  $T_{B2}$ - $D_{B2}$  ou entre  $T_{B1}$ - $D_{B1}$  et  $T_{H2}$ - $D_{H2}$  qui sont des commutations douces et s'effectuent à courant I nul. Ces configurations posent uniquement des problèmes de commande car on se retrouve avec un court-circuit de la source d'entrée si les commandes de  $T_{H1}$  et  $T_{B2}$  se chevauchent (même chose pour le couple  $T_{H2}$  et  $T_{B1}$ ) et un circuit ouvert pour  $S_i$  si les commandes sont décalées. Les autres commutations peuvent être ramenées à des commutations de type diode-transistor.

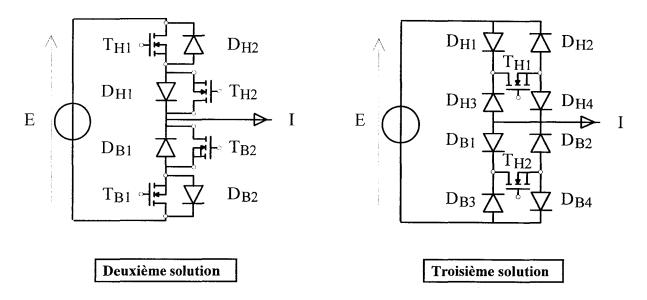

Figure 1.14: Autres réalisations de la cellule de commutation à interrupteurs 4 segments

La deuxième solution présentée sur la figure 1.14 est souvent utilisée. Son étude nécessite des hypothèses supplémentaires de travail : soit on utilise la diode interne des transistors MOS pour concevoir l'interrupteur, soit on inhibe son action en utilisant des diodes rapides externes. Il faut dans cette dernière éventualité utiliser huit composants pour réaliser l'interrupteur synthétique  $K_1$  ou  $K_2$ .

La troisième solution est moins intéressante car elle nécessite cinq composants pour obtenir les interrupteurs synthétiques  $K_1$  et  $K_2$ . En outre, elle implique la commutation de trois éléments à chaque changement d'état pour un interrupteur qui ne possède de surcroît qu'un degré de liberté de commande, et présente plus de contraintes.

Nous nous limiterons donc à la première solution car elle s'adapte facilement à notre démarche de travail en utilisant directement les résultats de la cellule à interrupteurs 3 segments bidirectionnels en tension.

#### I.7) Techniques de commande des cellules à IBTC

La cellule de commutation à IBTC représente une solution idéale pour recréer toutes les possibilités de connexion directe entre deux sources. La difficulté d'emploi de ces IBTC est essentiellement située dans la logique de commande à appliquer sur ces interrupteurs, elle devient rapidement très complexe [19,20,21,22]. Le choix entre les trois structures proposées pour réaliser un IBTC se fait essentiellement sur deux critères: celui de la puissance dissipée pendant la conduction et les commutations, et celui du nombre de commandes nécessaires. Une étude basée sur le critère de puissance a été développée par CITTADINI [10].

Un bilan énergétique a été réalisé sur la cellule élémentaire en utilisant les trois possibilités de réalisation de l'IBTC pour établir un premier critère de sélection. La solution à un seul transistor par interrupteur est la plus désavantageuse car la puissance dissipée par cette

structure est nettement supérieure aux deux autres. De plus on ne dispose que d'un seul degré de liberté pour commander cet interrupteur synthétique. Si on compare les solutions anti-série et anti-parallèle, on note une augmentation des pertes si on utilise les diodes internes des MOS classiques dans la configuration anti-série : il faut donc l'éviter dans la mesure du possible.

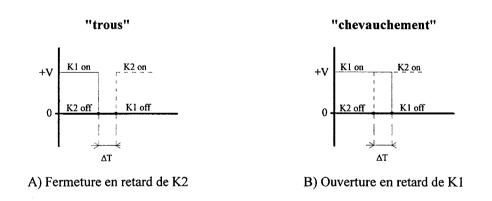

Les règles à respecter vis-à-vis des sources de tension et de courant imposent aux deux interrupteurs  $K_1$  et  $K_2$  qui constituent la cellule de se trouver dans des états complémentaires. Lors des changements d'état des interrupteurs on assiste à des commutations qui ne seront jamais parfaites et à l'origine de problèmes à résoudre.

#### L'obtention de commandes synchrones est irréaliste.

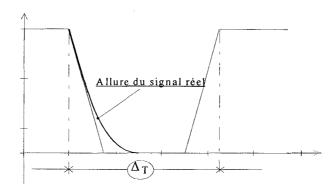

Il faut établir des lois de commande appropriées pour limiter les contraintes imposées aux composants, plusieurs méthodes de commande ont été développées dans ce but. Pour minimiser les pertes de commutation il faut ramener toutes les commutations dans la cellule à des commutations Diode⇔Transistor. Il existera toujours un décalage temporel (il peut être positif ou négatif) entre les deux signaux de commande (figure 1.15).

Figure 1.15 : Décalage des commandes appliquées sur les interrupteurs K1 et K2

Deux problèmes peuvent survenir lors d'un changement d'état dans la cellule : soit les instants de commande se chevauchent soit on voit apparaître un trou entre les deux commandes. Ces deux configurations donnent naissance respectivement à une surtension ou à une surintensité selon le signe de  $\Delta T$ .

Pour réaliser une commutation  $T_H$ - $D_H \Rightarrow T_B$ - $D_B$ :

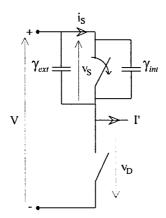

Solution anti-série (figure 1.14): si on commande la fermeture de  $T_{H1}$  avant l'ouverture de  $T_{B1}$ , comme le montre le schéma équivalent obtenu à partir des modèles rudimentaires d'interrupteurs commandés, le courant qui s'installe dans  $T_{H1}$  doit charger la capacité parasite de  $T_{B1}$  au moment de son ouverture et présente une surintensité. Il faut limiter  $\Delta T$  ou placer une inductance dans la maille.

Solution anti-parallèle (figure 1.13): si on commande l'ouverture de  $T_{\rm HI}$  avant la fermeture de  $T_{\rm BI}$ , la tension aux bornes de  $T_{\rm HI}$  subit une surtension pendant la croissance du courant

dans  $T_{B1}$ . Il faut limiter  $\Delta T$  ou ajouter des capacités en parallèle sur les interrupteurs pour diminuer les gradients de tension.

CITTADINI [10] a recensé et groupé en trois catégories les commandes d'IBTC en boucle ouverte ou fermée qui permettent d'optimiser la commande des interrupteurs  $K_1$  et  $K_2$ :

#### a) les commandes dissociées

Comme leur nom l'indique, les commandes des deux interrupteurs sont adaptées en fonction du signe des grandeurs E et I. C'est un fonctionnement avec séparation des commandes où est reproduit le fonctionnement d'un hacheur dans les quatre quadrants. On dispose de quatre commandes séparées sur  $K_1$  et  $K_2$ .

#### b) les commandes complémentaires

Cette technique de commande est la plus simple car on applique des signaux complémentaires sur  $K_1$  et  $K_2$ . Les contraintes sont minimales lorsque l'interrupteur "diode" est commandé très rapidement par rapport à l'interrupteur "transistor". Il faut prédéterminer le fonctionnement de chacun des deux interrupteurs en fonction du signe de E et I. Pour chaque commutation il existe un réglage optimum de  $\Delta T$  pour obtenir le meilleur compromis sur les pertes (surtension et surintensité). Il est nécessaire de réaliser un asservissement pour s'adapter aux variations qui apparaissent lors des différentes commutations.

#### c) les commandes de synthèse

Cette solution consiste à mélanger les deux types de commande précédents. Si les grandeurs E et I sont importantes, la méthode de commande a) est appliquée. Par contre, lorsque les deux grandeurs deviennent inférieures à un certain seuil à fixer, on bascule à la méthode de commande b). Même si on ne se situe pas dans un état de commutation optimale, les valeurs de E et I sont suffisamment faibles pour générer peu de pertes.

En ce qui concerne les catégories b) et c) les travaux de recherche ne sont pas assez développés pour envisager une réalisation à court terme. La meilleure solution semble être la catégorie a) mais la recherche sur le sujet reste d'actualité car différents travaux ont montré les difficultés à réaliser des commutations fines sans créer des contraintes supplémentaires sur les interrupteurs. JAUNAY [24] a montré que pour étudier correctement les phénomènes de commutation dans ce genre de structure, il faut choisir un modèle d'IBTC assez précis pour obtenir une image correcte des phénomènes engendrés.

Notre objectif est donc d'établir un modèle d'IBTC alliant simplicité et performance pour pouvoir être utilisé comme outil de développement de stratégies de commande d'IBTC n'ayant pas recours aux circuits d'aide à la commutation.

# Chapitre II : METHODES DE MODELISATION DES INTERRUPTEURS

La modélisation dans le domaine du génie électrique permet de décrire le comportement d'un composant, d'un circuit ou d'un système d'une manière plus ou moins fidèle à la réalité. C'est un outil de calcul et son expansion a apporté une révolution dans la méthode de travail employée par les concepteurs de circuits de puissance. Elle est devenue une étape essentielle dans l'étude et le développement de nouvelles structures. La révolution informatique de ces dernières années a permis grâce à l'augmentation de sa puissance de calcul de banaliser la modélisation par l'emploi des logiciels de simulation. En effet, il est plus facile d'évaluer par le biais d'un logiciel l'influence de la modification de n'importe quel élément d'un circuit ou de sa valeur, plutôt que d'intervenir sur la maquette ou recommencer les calculs analytiques et perdre par conséquent un temps excessif... Cependant comme dans toute chose l'utilisateur doit savoir fixer des limites dans les moyens qu'il utilise en fonction de ses besoins.

Avec un modèle, on essaye de reproduire le comportement d'un système. Quand le modèle est choisi, il faut identifier ses paramètres pour pouvoir procéder aux simulations et aux comparaisons avec les résultats expérimentaux qui permettront de juger de la validité du modèle. Ces modèles validés peuvent être utilisés dans le cadre de la CAO pour optimiser les stratégies de commande et le dimensionnement des CALC, évaluer les pertes dans les composants et étudier les caractéristiques de dispositifs obtenus par association de ces composants.

#### II 1) Différentes méthodes de modélisation des composants de puissance

La première étape de la modélisation consiste à poser les hypothèses simplificatrices qui permettent de faire des approximations sur le comportement réel. Pour élaborer un modèle, il faut définir de façon implicite les limites de son domaine de validité.

Dans le domaine de l'électronique de puissance, il est nécessaire avant tout de définir les besoins réels et de recentrer chaque étude dans son contexte. Les objectifs de chaque utilisateur permettent de choisir le type de modélisation le mieux adapté à ses besoins. Il existe plusieurs niveaux de modélisation pour les interrupteurs de puissance :

- les modèles binaires : 0/1 ou Ron/Roff

- les modèles de représentation, construits à partir des phénomènes observés et ne permettant pas la prévision

- les modèles de connaissance (à constantes localisées ou purement numériques) construits à partir des phénomènes physiques et permettant la prévision.

L'utilisateur peut ensuite choisir un des nombreux logiciels disponibles sur le marché sachant que dans cette gamme de produits, les modèles utilisés vont de la représentation la plus simple à la plus complexe. Les nouvelles stratégies de commande appliquées dans les

convertisseurs modernes nécessitent une maîtrise et une analyse parfaites des nombreuses phases de commutation. Il faut de ce fait un outil performant pour modéliser ce genre de convertisseur et ainsi aboutir à une représentation satisfaisante des phénomènes. Quel type de modélisation faut-il adopter pour cette configuration de travail?

La meilleure solution consiste à utiliser des modèles physiques extrêmement précis, mais doit-on forcément avoir recours à ceux-ci? Deux aspects peuvent infléchir cette première tendance qui consiste à toujours appuyer ses recherches avec les outils les plus performants. L'implantation des composants et de leur environnement joue un rôle prépondérant dans le fonctionnement d'un convertisseur. De plus, les problèmes de compatibilité électromagnétique (CEM) ne peuvent plus être ignorés car l'évolution technologique des composants permet de travailler à des fréquences de commutations très élevées. Les perturbations, qu'elles soient conduites ou rayonnées, génèrent des contre réactions sur le circuit de commande et provoquent des écarts entre les phénomènes observés expérimentalement et le comportement des modèles. Il apparaît de façon évidente que le modèle même le plus complexe ne prend pas en compte actuellement tous ces problèmes. On peut alors utiliser un modèle de base assez simple sur lequel on ajoute des modifications susceptibles de représenter ces effets et d'améliorer les résultats de simulation. Ce modèle personnalisé permet de se rapprocher des évolutions réelles.

<u>Remarque</u>: Il existe un facteur important dans la phase de validation par comparaison entre les résultats de simulation et les relevés pratiques. Ces derniers peuvent être soumis à discussion car il est quelquefois difficile de se prononcer sur la nature exacte des relevés obtenus (à cause des perturbations engendrées par les appareils de mesure).

Avant de passer à la mise en équations et la résolution numérique, il est nécessaire de trouver une représentation équivalente et convenable du système. Ce dernier point est sûrement l'un des plus délicats.

#### II.2) Modélisation binaire

C'est l'outil le plus simple pour simuler le fonctionnement des interrupteurs dans les convertisseurs statiques. On rencontre cette méthode dans les logiciels du type SIMUL, SCRIPT et SUCCESS (version N°1). La représentation est très simple car on affecte une valeur logique ou une valeur de résistance pour les deux états stables (passant et bloqué) des interrupteurs. Cette méthode est suffisante pour caractériser le fonctionnement global d'un système pendant les états stables. Elle ne permet en aucun cas de donner une image des évolutions des différents paramètres durant les commutations. Les surtensions et surintensités apparaissant lors de ces phases ne peuvent être reproduites par la simple utilisation d'une résistance.

Figure 2.1 : Résultat de simulation par résistance binaire sur un hacheur série (le temps de commutation est dû au pas de calcul)

Il existe deux variantes possibles pour ce type de simulateur, en fonction de la méthode d'analyse employée:

- 1) La simulation à topologie fixe est la plus simple à mettre en oeuvre puisqu'elle utilise une représentation constante du circuit durant toute la durée d'une simulation. La totalité du circuit est mise en équation une seule fois. Le plus souvent, on caractérise l'état ON d'un composant par une résistance de faible valeur R<sub>ON</sub> (quelques mΩ). De la même façon, lors de l'état OFF du composant, on associe une valeur élevée de résistance R<sub>OFF</sub> (quelques kΩ). Cette technique de modélisation oblige à effectuer un compromis dans le choix du rapport R<sub>ON</sub>/R<sub>OFF</sub>. Sa valeur doit être inférieure à 10<sup>6</sup> pour conserver une bonne stabilité des méthodes numériques employées alors qu'une représentation correcte nécessiterait un rapport d'environ 10<sup>10</sup> à 10<sup>12</sup>.

- 2) La simulation à topologie variable [33] permet d'éliminer la mise en équations des branches inutiles (technique des arbres) pendant une phase de fonctionnement donnée du convertisseur. L'étude préalable du circuit est beaucoup plus fastidieuse par rapport à la première méthode mais on gagne au niveau de la précision et des temps de calcul. Les semiconducteurs sont considérés comme parfaits et on les remplace soit par un circuit ouvert ou par un circuit fermé.

L'inconvénient majeur de cette méthode est qu'elle ne permet pas de visualiser finement le comportement d'un interrupteur lors des commutations. Elle donne uniquement la possibilité d'observer l'évolution des grandeurs à l'échelle des temps du convertisseur qui utilise ces interrupteurs. Il faut donc utiliser une autre technique pour améliorer les performances de ce modèle.

#### II.3) Modélisation de type comportemental

La première méthode de modélisation (comportement tout ou rien) ne convient plus pour faire une analyse des mécanismes de commutation. Il est donc nécessaire de se rapprocher du

comportement réel du composant à étudier [1-8-31]. On part d'une constatation simple : durant les commutations, les évolutions des différentes grandeurs d'un composant sont simultanées et elles génèrent des pertes. Cette puissance est dissipée sous forme thermique lors de l'ouverture et de la fermeture d'un interrupteur statique.

Il faut élaborer un circuit électrique qui s'identifie au comportement du composant durant les états stables (ON et OFF) et surtout pendant les phases de commutation. Pour obtenir un tel modèle, on peut utiliser des éléments passifs (inductances et capacités) et/ou des sources quelconques (tension ou courant) pour représenter les transferts d'énergie. Certains éléments peuvent être considérés comme faisant partie intégrante du composant ou assimilés à des éléments extérieurs comme les liaisons de câblage du convertisseur. Pour les modèles plus développés, on emploie des sources liées afin de retranscrire une formule empirique ou une approximation des lois issues de la physique du semi-conducteur.

Bien souvent, on ne retrouve pas de relation physique entre le schéma équivalent et le principe de fonctionnement du dispositif étudié. Les modèles mis au point n'ont souvent aucun lien direct avec les semi-conducteurs étudiés. L'identification des paramètres du schéma équivalent se fait par comparaison avec des résultats de manipulation ou sont issus directement de données techniques du fabricant. L'intérêt de cette méthode réside dans la grande liberté de manoeuvre laissée au concepteur pour aboutir à un modèle. Cette méthode est bien sûr plus précise que la précédente dans la mesure où elle prend en compte le comportement du composant et de son environnement.

#### II.3.1) Modèles comportementaux d'interrupteurs statiques à topologie variable

Le but de cette méthode consiste à trouver un modèle de représentation du composant lors des phases de commutation. On commence par insérer l'interrupteur dans une structure simple, généralement la cellule élémentaire de commutation.

Figure 2.2 : Influence des éléments parasites sur les commutations

Une fois que les modèles des deux interrupteurs de la cellule sont définis (l'un à commutation spontanée et l'autre commandée), il est possible de simuler le comportement de l'ensemble du convertisseur et d'apporter des modifications aux modèles si cela semble nécessaire. Avant de proposer un modèle pour chacun des deux interrupteurs, il est intéressant d'examiner le comportement de l'interrupteur dans son environnement et surtout l'influence des éléments parasites du circuit de puissance ( $\ell_{\rm ext}$  et  $\gamma_{\rm ext}$ ).

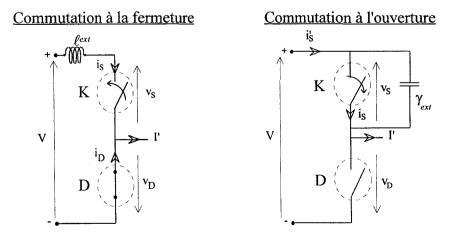

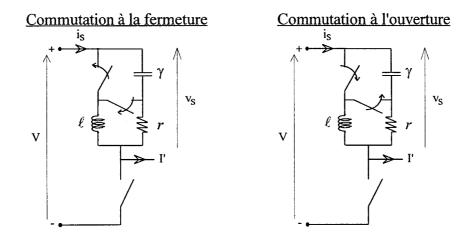

La figure 2.2 représente les deux topologies de la cellule élémentaire durant la commutation à la fermeture et à l'ouverture en tenant compte des éléments parasites du circuit:  $\ell_{\rm ext}$  intervient uniquement au moment de la fermeture de K, et  $\gamma_{\rm ext}$  pour l'ouverture. Il est aussi possible de développer des modèles moins rudimentaires d'interrupteur différents entre l'ouverture et la fermeture en essayant de se rapprocher au maximum des variations réelles en tension et en courant du composant.

#### a) Mise en conduction

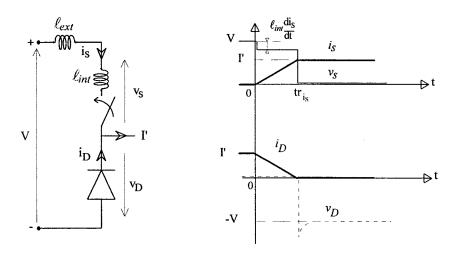

La solution la plus simple consiste à utiliser une inductance  $\ell$  pour limiter la croissance  $di_S/dt$  du courant dans l'interrupteur lors de la mise en conduction. La montée du courant dans l'interrupteur est représentée en utilisant les inductances parasites externe  $\ell_{ext}$  et interne au composant  $\ell_{int}$  (figure 2.3)

Figure 2.3 : Modélisation de la montée du courant is

L'inductance interne est directement liée à  $W_{SON} = \int_{0}^{t_{ris}} v_{S}.i_{S}.dt = \frac{1}{2} \ell_{int} (I')^{2}$ .

Le modèle présenté peut être amélioré en remplaçant l'interrupteur par une source de tension placée en série avec l'inductance externe  $\ell_{ext}$ . Le profil de tension  $v_S$  est choisi afin qu'il s'adapte au mieux pour le composant étudié (figure 2.4). En particulier,  $v_S$  doit être ramené à zéro dès que  $i_S$  atteint sa valeur finale I'.

Figure 2.4 : Modélisation de la descente de la tension vs

#### b) Blocage

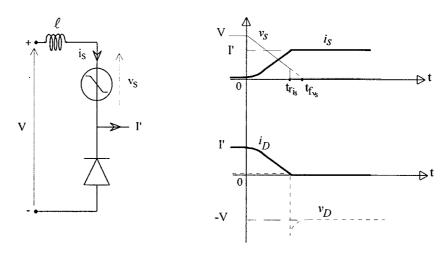

On obtient par dualité avec les schémas de la commutation à la fermeture ceux de la commutation au blocage.

Durant le processus du blocage, ce sont les capacités parasites qui interviennent. On peut les considérer externes ou internes au composant de la même façon que pour les inductances. Avec ce modèle on a une bonne approximation de la montée de la tension aux bornes de l'interrupteur mais pour faire apparaître la variation du courant i<sub>S</sub> il faut ajouter un autre élément.

Figure 2.5: Modélisation de la montée de la tension vs

La solution consiste à placer une source de courant à la place de l'interrupteur commandé. Elle va permettre (figure 2.6) d'imposer la forme d'onde du courant i's dans une branche pendant l'ouverture. On peut donner à i's l'allure d'une décroissance linéaire, comme cela se produit dans le cas du transistor MOS, ou créer un courant de queue, phénomène que l'on rencontre dans certains composants de puissance (IGBT, GTO).

Figure 2.6 : Modèle à capacités et gradient de courant

#### II.3.2) Modèles comportementaux d'interrupteur statique à topologie fixe

Un modèle unique valable pour les deux commutations associe les deux effets précédents. (figure 2.7). Ce modèle comprend un circuit r $\ell\gamma$  et deux interrupteurs parfaits. Il est intéressant de travailler avec ce type de modèle car la simulation du circuit s'effectue sans changement de configuration. Il faut noter que les modèles décrits jusqu'à présent peuvent être simulés et testés avec des logiciels existant dans le commerce. La mise en équation reste assez simple dans ce cas de figure contrairement à tous les modèles qui vont suivre.

Figure 2.7: Modèle à topologie fixe

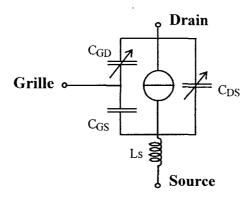

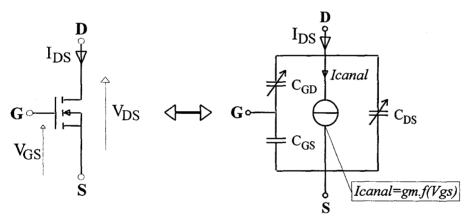

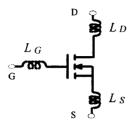

#### II.3.3) Modèle de MOSFET

La particularité de ce composant unipolaire permet de prendre en compte la technologie du composant dans une modélisation de type comportemental. La reproduction des phénomènes réels provoqués par le composant lui-même permet d'obtenir un modèle de connaissance simple. De nombreux travaux de recherche ont développé plusieurs modèles de composant. Les résultats sont suffisamment précis pour faire de cet outil une référence. Cette

représentation est à la base du modèle de MOS dans les logiciels du type SUCCESS (version2) et SPICE.

Figure 2.8: Modèle comportemental du MOS

Parmi les avantages de cette méthode, il y a tout d'abord le temps de calcul qui est assez faible et la possibilité de simuler le comportement du convertisseur et de celui des composants. Il est intéressant de disposer d'un pas de calcul auto adaptatif entre les phases de conduction et de commutation. Le modèle du composant est alors moins complexe durant les phases de conduction où il ne requiert pas une précision très importante.

L'inconvénient majeur de ces modèles comportementaux est la limite de leurs domaines de validité. Ils permettent de prévoir les variations du composant uniquement dans les conditions de fonctionnement d'où sont extraits les paramètres du modèle.

#### II.4) Méthode de résolution des équations de la physique des semi-conducteurs

Cette méthode est la plus précise car elle utilise les équations de transport et de continuité [réf 2-3] qui régissent le comportement des porteurs de charge dans le semi-conducteur. Le mouvement de transit et la répartition des différentes charges sont connus à chaque instant. Les modèles obtenus sont très précis et donnent les évolutions quasi réelles de toutes les grandeurs du composant. Le traitement des équations locales traduit de manière fidèle tous les phénomènes liés à un changement d'état du composant modélisé.

Pour calculer les répartitions de charges, il faut résoudre des systèmes d'équations très complexes qui impliquent la présence d'un outil informatique très performant. La résolution de ce genre de système passe par des approximations ou l'utilisation d'artifices mathématiques. Bien souvent, il est difficile de mettre en équation les relations exactes et de pouvoir les exploiter directement. Ce sont généralement des équations non linéaires à coefficients non constants. La plupart des logiciels traitent des problèmes de répartition de surface ou 2D (deux dimensions) mais il existe aussi des logiciels 3D (trois dimensions).

L'épaisseur des couches de blocage et la durée de vie moyenne relativement élevée des porteurs de charge, qui caractérisent les interrupteurs de puissance à semi-conducteur, sont à l'origine, dans les composants bipolaires, de phénomènes répartis dont ne peuvent pas rendre compte les modèles à constantes localisées. Il est cependant possible, en réduisant les structures à des associations de zones étroites et faiblement dopées avec des zones plus épaisses et faiblement dopées, de diminuer le nombre de paramètres nécessaires pour tenir compte des relations entre les diverses grandeurs caractéristiques d'un composant, et de simplifier ainsi les équations de transport des charges.

L'inconvénient majeur de cette technique reste le temps de calcul nécessaire pour effectuer une simulation correcte. Il paraît difficile d'insérer un tel modèle de composant dans un convertisseur et d'espérer obtenir dans des délais rapides, ne serait-ce qu'une période de fonctionnement. Actuellement, cette méthode s'applique dans des domaines bien spécifiques comme le développement de nouveaux composants mis au point par les grandes firmes de fabrication.

#### II.5) Identification des paramètres

L'acquisition des paramètres nécessaires au modèle se fait à partir de relevés expérimentaux ou des informations fournies par le fabricant. Il est souvent difficile d'obtenir de la part du fabricant les valeurs des paramètres de structure d'un composant, mais le nombre de paramètres à introduire dans le modèle reste relativement faible et ne nécessite pas toujours une analyse technologique inverse du composant.

Par exemple, il est possible d'obtenir un modèle très satisfaisant de diode de puissance à partir de la surface de la pastille de silicium, de l'épaisseur et du dopage de la zone N-, de la durée de vie moyenne des porteurs de charge dans cette région, et des gradients de concentration d'impuretés dans les zones P<sup>+</sup> et N<sup>+</sup> de chaque côté.

#### II.6) Conclusion

L'utilisation des modèles physiques numériques restera sans doute limitée si le temps de calcul demeure un frein. Ce problème ne semble pas près d'être résolu. Il semble inconcevable de vouloir créer un modèle pour tous les composants. Non seulement, leurs calibres en tension et en courant diffèrent mais ce sont surtout les paramètres intrinsèques de chacun d'eux qui changent.

Pour obtenir un modèle de connaissance suffisamment simple, il faut partir d'un modèle de base et lui associer quelques coefficients qui peuvent être identifiés à partir des caractéristiques du fabricant ou de tests ne demandant pas de matériel lourd. C'est la solution que nous avons choisie pour modéliser les interrupteurs obtenus par association de transistors MOS et de diodes.

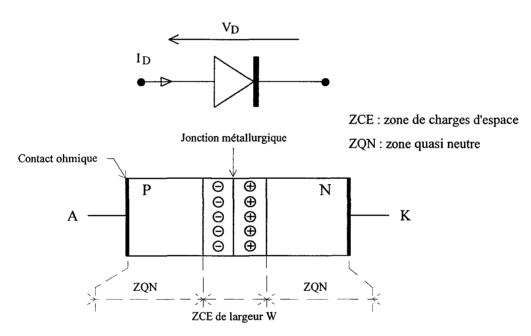

## Chapitre III : MODELISATION DE LA DIODE

Ce chapitre est consacré à l'élaboration d'un modèle de diode destiné à être introduit dans les interrupteurs qui seront utilisés pour la modélisation des différentes cellules de commutation. Après avoir mis l'accent sur les principaux phénomènes devant être restitués, nous proposons d'une part un modèle comportemental, et d'autre part nous indiquons comment acquérir les paramètres permettant d'obtenir des modèles satisfaisants.

# III.1) Principe de fonctionnement de la jonction PN

Dans ce paragraphe, avant de faire une présentation du fonctionnement de la diode de puissance, nous allons détailler les principaux phénomènes physiques intrinsèques de ce type de composant et nous essayerons de mettre en évidence les aspects importants à retenir pour pouvoir les retranscrire par un modèle simple [24]. Notre but n'est pas de traiter de la physique des semi-conducteurs ni de la technologie de fabrication des diodes, mais de fournir le minimum d'explications nécessaires pour comprendre leurs caractéristiques.

Les différents phénomènes dont nous allons donner une description succincte et qualitative vont permettre d'expliquer l'allure des caractéristiques, tant statiques que dynamiques, des interrupteurs à semi-conducteurs.

Tous ces dispositifs ont en commun une zone N faiblement dopée dont l'épaisseur est proportionnelle à la tension maximale que peut supporter l'interrupteur à l'état bloqué.

Au repos, cette zone N est électriquement neutre, les charges positives fixes équilibrant les charges négatives mobiles.

L'état bloqué de l'interrupteur s'obtient par extraction des charges mobiles ce qui fait apparaître une zone de déplétion plus ou moins étendue dans N.

Le passage de l'état bloqué à l'état passant nécessite au minimum la réinjection de charges négatives dans N pour retrouver l'état de repos, qui correspond à l'état passant pour les composants unipolaires.

Pour les composants bipolaires, les plus nombreux, l'état de repos n'est qu'une transition entre les états passant et bloqué. L'état passant est obtenu par forte injection de charges positives et négatives, en nombre égal pour maintenir la neutralité électrique de la zone N dont la résistivité devient très faible.

Ce sont les différentes méthodes utilisées pour injecter ou extraire les charges mobiles dans la zone N qui différencient les interrupteurs de puissance à semi-conducteur.

## III.1.1) Les mouvements de charge dans un semi-conducteur

Dans un métal, les charges négatives que constituent les électrons de la bande de conduction sont libres de se déplacer au sein du matériau. Les charges positives que constituent les atomes ionisés par le passage de leurs électrons périphériques dans la bande de conduction sont fixes. Toute variation spatiale de la concentration en électrons au sein du matériau entraînerait un déséquilibre de concentration entre les charges positives et négatives, et donc l'apparition d'un champ électrique s'opposant à ce déséquilibre.

Dans un semi-conducteur, on dispose de deux types de charges mobiles: les électrons et les trous. On peut donc avoir une variation spatiale de la concentration en porteurs sans qu'il y ait apparition d'un champ électrique: il suffit que les variations de concentration des électrons et des trous soient égales.

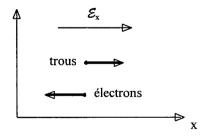

Par conséquent, dans un semi-conducteur, deux mécanismes peuvent contribuer à produire des mouvements de charges et donc à faire circuler un courant au sein du matériau :

- <u>Effet des gradients de potentiel</u>: l'existence d'un champ électrique  $E_x$  dirigé suivant l'axe x exerce une force sur les charges mobiles et provoque donc un mouvement global de ces charges dans le sens de  $E_x$  pour les trous et dans le sens opposé pour les électrons. Il en résulte un courant de conduction dans le sens de  $E_x$  et dont la densité est donnée par :

$$J_{cond,x} = q(n.\mu_n + p.\mu_p)E_x$$

où n et p représentent les concentrations en électrons et en trous par cm $^3$   $\mu_n$  et  $\mu_p$  les mobilités des électrons et des trous et q la charge de l'électron

Figure 3.1: Courants de conduction

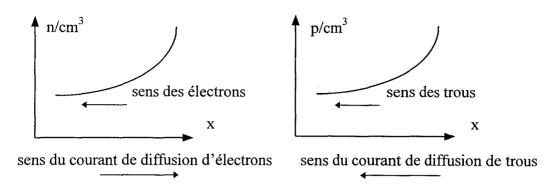

- Effet des gradients de concentration : une variation de la concentration en électrons suivant la direction x entraine un gradient de concentration dn/dx et un mouvement des électrons dans le sens qui contribue à rétablir l'équilibre. Il en va de même d'une variation de la concentration de trous.

Figure 3.2: Courants de diffusion

Il en résulte un courant de diffusion dont la densité est donnée par :

$$J_{diff,x} = q. \left( D_n \frac{\delta n}{\delta x} - D_p \frac{\delta p}{\delta x} \right)$$

Dn et Dp sont les constantes de diffusion des électrons et des trous, qui sont liées aux mobilités  $\mu_n$  et  $\mu_p$  par la relation d'Einstein :

$$\frac{D_n}{\mu_n} = \frac{D_p}{\mu_p} = \frac{kT}{q} = U_T$$

= potential thermodynamique

où T est la température en degrés Kelvin, et k la constante de Boltzmann ( $U_T = 26 \text{mV}$  à  $25^{\circ}\text{C}$ ).

C'est l'existence de ces deux types de courant qui est à la base des propriétés particulières des dispositifs à semi-conducteur.

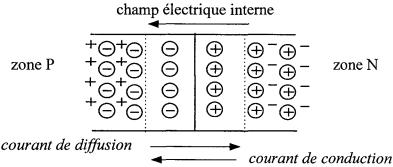

## III.1.2) La jonction PN à l'équilibre

Pratiquement tous les dispositifs à semi-conducteur et en particulier les interrupteurs de puissance sont obtenus en réalisant des structures dans lesquelles certaines régions sont de type P et d'autres de type N. La jonction PN désigne la zone de faible épaisseur (quelques microns) où la conductivité passe du type P au type N. L'étude des phénomènes qui se produisent au niveau de la jonction joue donc un rôle essentiel dans le fonctionnement de la plupart des interrupteurs de puissance à semi-conducteur.

Les gradients de concentration donnent naissance à un courant de diffusion dû aux porteurs majoritaires. Les recombinaisons entre charges mobiles de signes opposés sont très nombreuses à proximité immédiate de la jonction, et il ne reste dans ces régions que les charges fixes: ions négatifs du côté P, positifs du côté N, qui font disparaitre localement la neutralité électrique. Dans cette zone dite de déplétion ou de charge d'espace apparaît un champ électrique dirigé de la zone N vers la zone P qui est à l'origine d'un courant de

conduction dû aux porteurs minoritaires. A l'équilibre, aucun courant ne pouvant traverser la jonction isolée, ce courant de conduction compense le courant de diffusion dirigé en sens inverse.

Figure 3.3 : Jonction PN à l'équilibre

Puisque les charges mobiles disparaissent deux par deux lors des recombinaisons, la charge positive localisée du côté N de la jonction est égale à la charge négative localisée du côté P. En dehors de la zone de déplétion, le champ électrique est nul, comme le sont les gradients de concentration en porteurs. Si on fait l'hypothèse que les limites de la zone de déplétion sont abruptes, par centimètre carré de surface de jonction, on a :

- du côté P, une charge égale à - $qN_Al_{P0}$ , en désignant par  $N_A$  le nombre d'atomes accepteurs par cm<sup>3</sup> et par  $l_{P0}$  la largeur en cm de la zone de déplétion dans la zone P

- du côté N, une charge égale à  $+qN_Dl_{N0}$ , en désignant par  $N_D$  le nombre d'atomes donneurs par cm<sup>3</sup> et par  $l_{N0}$  la largeur en cm de la zone de déplétion dans la zone N

L'égalité des charges de part et d'autre implique donc que l'on ait :

$$N_A l_{P0} = N_D l_{N0}$$

Si les concentrations en impuretés N<sub>A</sub> et N<sub>D</sub> sont nettement différentes, cette relation montre que c'est dans la zone la plus faiblement dopée que la largeur de la zone de déplétion est la plus importante.

L'hypothèse de frontières abruptes de la zone de déplétion revient à admettre que le champ électrique évolue dans cette zone de manière linéaire :

$$\frac{dE}{dx} = \frac{qN_A}{\epsilon} \qquad \text{dans la zone P} \qquad \qquad \frac{dE}{dx} = \frac{qN_D}{\epsilon} \qquad \text{dans la zone N}$$

où ε est la constante diélectrique du silicium =  $10^{-12}$  F/cm

On en déduit la valeur maximale  $E_{max}$  du champ électrique dans la zone de déplétion, et celle de la barrière de potentiel  $\Delta V_0$  qui s'installe entre la zone P et la zone N :

$$E_{\text{max}} = \frac{q N_{\text{D}}}{\varepsilon} l_{\text{N0}} = \frac{q N_{\text{A}}}{\varepsilon} l_{\text{P0}}$$

et

$$\Delta V_0 = E_{\text{max}} \frac{l_{P0} + l_{N0}}{2}$$

La zone de charge d'espace étant dépourvue de charges libres, la densité de courant y est nulle. Si on prend la composante due aux électrons, on obtient :

$$J_n = J_{cond,n} + J_{diff,n} = q.n.E.\mu_n + q.D_n.\frac{dn}{dx} = 0$$

dont on tire:

$$E(x) = -\frac{D_n}{n \cdot \mu_n} \cdot \frac{dn}{dx} = -\frac{dV}{dx}$$

$$dV = \frac{D_n}{\mu_n} \cdot \frac{dn}{n} = U_T \cdot \frac{dn}{n}$$

$$\Delta V_0 = \int_{I_{P0}}^{I_{N0}} dV = U_T Log_e \frac{n_N}{n_P} = U_T Log_e \frac{N_D N_A}{n_I^2}$$

(3.1)

On obtient bien sûr le même résultat en prenant la composante due aux trous. La valeur obtenue pour  $\Delta V_0$  est de l'ordre du volt.

## III.1.3) La jonction PN en polarisation inverse

Si on polarise négativement la zone P par rapport à la zone N à l'aide d'une source extérieure négative  $V_R$  (reverse), la zone de déplétion s'élargit à mesure que  $V_R$  augmente et renforce la barrière de potentiel.

## • Tenue en tension inverse

La tension inverse maximale que peut supporter une jonction est limitée par deux phénomènes :

- Le perçage de la jonction intervient lorsque la largeur de la zone de déplétion tend à devenir supérieure à celle de la zone, P ou N, la plus faiblement dopée. Ainsi, si la zone N est faiblement dopée par rapport à la zone P, la tension de perçage est la valeur de V<sub>R</sub> pour laquelle l<sub>N</sub> devient égale à la largeur W<sub>N</sub> de la zone N.

- Le claquage de la jonction intervient lorsque la valeur E<sub>max</sub> du champ électrique au droit de la jonction atteint le seuil d'avalanche E<sub>BR</sub> à partir duquel l'énergie cinétique transmise aux électrons mobiles devient suffisante pour arracher lors des collisions les électrons captifs du réseau cristallin, multipliant ainsi les paires électron-trou.

Par conséquent, pour qu'une jonction puisse supporter une tension inverse élevée, il faut qu'une des deux zones soit épaisse et peu dopée.

On peut limiter la largeur de la zone faiblement dopée en lui accollant une zone de même type, mais fortement dopée. Par exemple, on fait suivre une zone N faiblement dopée notée N d'une zone N fortement dopée notée N<sup>+</sup>. Comme la pente du champ électrique dans la zone de déplétion est proportionnelle à la densité d'ions présents, cette pente augmente brutalement

quand x passe de la zone  $N^-$  à la zone  $N^+$ , ce qui permet de supprimer la limite correspondant à la tension de perçage de la jonction  $PN^-$ . Il ne reste que la tension de claquage pour laquelle  $E_{max} = E_{BR}$ .

Pour que cette valeur soit inférieure à la tension de perçage de la jonction PN, il suffit que le produit (E<sub>BR</sub>.W<sub>N</sub>) soit supérieur à cette tension de perçage.

## • Remarque sur le courant inverse

Lorsqu'une diode est polarisée en inverse, elle est traversée par un faible courant négatif (courant de fuite), qui correspond à l'augmentation du courant de conduction due à l'action du champ électrique sur les porteurs minoritaires des zones P et N (les trous de la zone N, les électrons de la zone P) dont les concentrations sont peu élevées. Toutefois, lors de variations brusques de la tension V<sub>R</sub>, ce courant peut atteindre transitoirement des valeurs élevées pour enlever ou apporter les charges nécessaires à assurer les variations de largeur de la zone de déplétion.

# • Capacité parasite d'une jonction PN<sup>-</sup> polarisée en inverse

Lorsqu'une zone de déplétion de largeur  $l_N$  apparaît dans une couche  $N^-$  de section A (area) et possédant  $N_D$  ions positifs par cm<sup>3</sup>, la charge contenue dans cette zone est égale à :

$$Q = q.N_D.A.l_N$$

La largeur  $l_N$  est donnée par la relation :

$$l_{N} = \sqrt{\frac{2\epsilon \left(\Delta V_{0} + V_{R}\right)}{qN_{D}\left(1 + \frac{N_{D}}{N_{A}}\right)}} \cong \sqrt{\frac{2\epsilon \Delta V_{0}}{qN_{D}}\left(1 + \frac{V_{R}}{\Delta V_{0}}\right)}$$

En reportant cette expression dans celle de Q, on obtient :

$$Q \cong A \sqrt{2qN_D \epsilon \Delta V_0 \left(1 + \frac{V_R}{\Delta V_0}\right)}$$

La capacité parasite de la jonction PN polarisée en inverse s'obtient à partir de :

$$C_{J} = \frac{dQ}{dV_{R}} = A\sqrt{2qN_{D}\epsilon\Delta V_{0}} \frac{1}{2} \left(1 + \frac{V_{R}}{\Delta V_{0}}\right)^{-\frac{1}{2}} \cdot \frac{1}{\Delta V_{0}} = A\sqrt{\frac{qN_{D}\epsilon}{2\Delta V_{0}}} \frac{1}{1 + \frac{V_{R}}{\Delta V_{0}}}$$

qui peut s'écrire:

$$C_{J} = \frac{C_{J0}}{\sqrt{1 + \frac{V_{R}}{\Delta V_{0}}}} \quad \text{en posant} \quad C_{J0} = C_{J} (V_{R} = 0) = A \sqrt{\frac{q N_{D} \varepsilon}{2 \Delta V_{0}}}$$

C'est cette capacité qu'il faut charger ou décharger chaque fois qu'on veut atteindre ou quitter l'état bloqué de la jonction.

## III.1.4) La jonction PN en polarisation directe

Lorsqu'on applique aux bornes de la jonction PN une tension directe  $V_F$  qui polarise positivement la zone P par rapport à la zone N, la barrière de potentiel est réduite ainsi que la largeur de la zone de déplétion. Le courant de conduction diminue tandis que le courant de diffusion augmente: la jonction PN devient passante dans le sens direct. A mesure que  $V_R$  tend vers  $\Delta V_0$ , un courant de diffusion de plus en plus important traverse la jonction. Ce courant peut atteindre des valeurs élevées car les gradients de concentration sont importants au niveau de la jonction.

La diffusion des trous de la zone P vers la zone N entraı̂ne une forte augmentation de la concentration en trous dans la zone N au droit de la jonction.

Si la concentration en trous reste inférieure à la concentration en atomes donneurs du côté N, on dit qu'il y a faible injection, et la relation (3.1) reste applicable.

Si la zone N comporte une partie N faiblement dopée pour assurer une bonne tenue en tension inverse, l'injection de trous peut rendre la concentration en trous supérieure à la concentration en électrons qui proviennent des atomes donneurs situés dans cette zone. Il y a alors forte injection. Pour rétablir la neutralité électrique, il faut que la zone N située de l'autre côté de la zone N injecte des électrons dans la zone N.

Le double phénomène d'injection dans la zone N :

- de trous par la zone P

- d'électrons par la zone N<sup>+</sup>

a comme avantage de fortement augmenter la concentration en porteurs dans cette zone par rapport à la situation d'équilibre, et donc de fortement réduire la résistance de cette zone ainsi que la chute de tension qui y apparaît lors du passage du courant direct.

On peut montrer que, en régime établi, la concentration n = p en paires électron-trou dans la zone  $N^-$  est proportionnelle à la densité de courant J à travers la jonction et à la durée de vie  $\tau_a$  (a pour ambipolaire) des paires électron-trou dans la zone  $N^-$ . La charge  $Q_S$  correspondant au nombre total d'électrons dans la zone  $N^-$  en forte injection est égale à :

$$Q_{S} = I.\tau_{a} \tag{3.2}$$

où I est le courant qui traverse la jonction.

Par contre, lors du retour à une polarisation inverse de la jonction, il faut évacuer les porteurs excédentaires amenés par injection dans la zone N<sup>-</sup>. La quantité de charges à extraire pour élargir la zone de déplétion se trouve augmentée, et donc la pointe de courant négative nécessaire pour assurer cette évacuation.

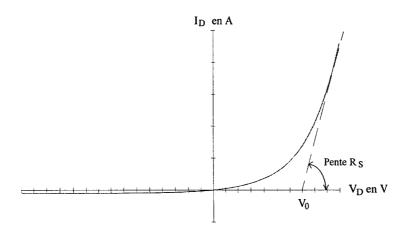

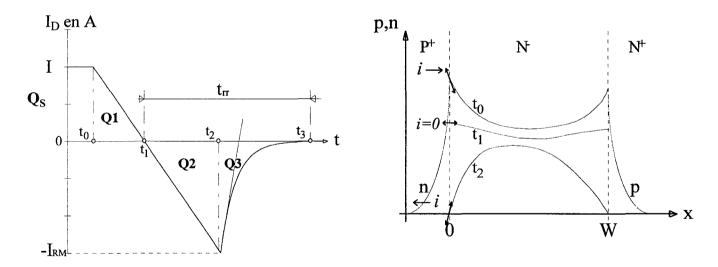

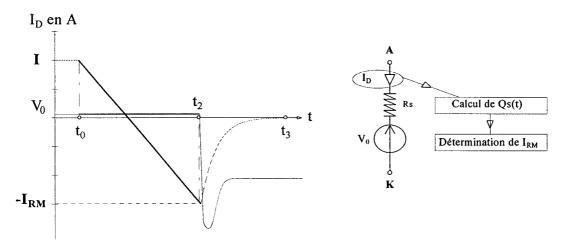

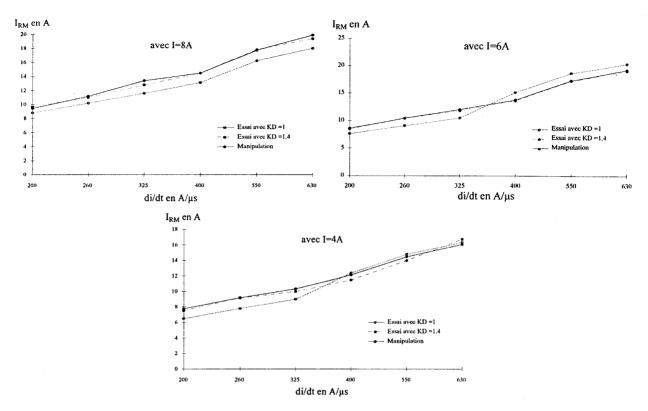

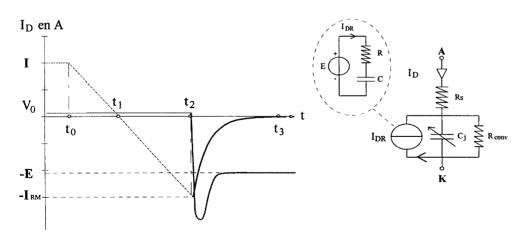

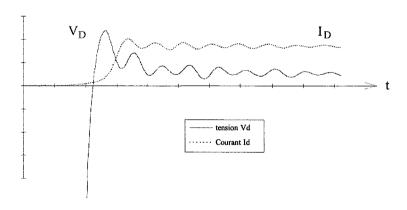

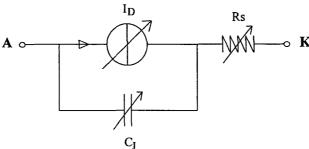

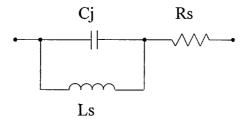

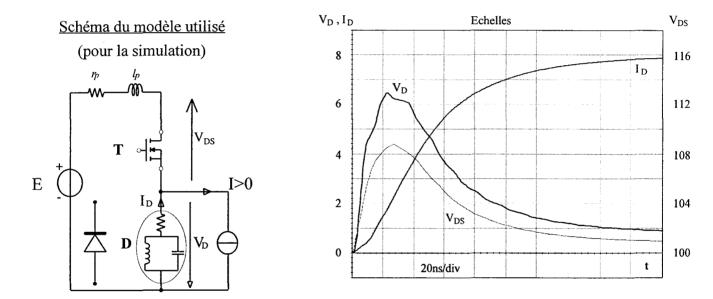

## III.2) La diode de puissance