Nº d'ordre :

the Your MIL

## **THESE**

#### Présentée à

L'Université des Sciences et Technologies de Lille

pour obtenir le titre de

#### DOCTEUR DE L'UNIVERSITE

Spécialité: ELECTRONIQUE

par

#### Frédéric DIETTE

Etude des transistors à effet de champ de type HEMT sur substrat GaAs et InP pour l'amplification de puissance en gamme millimétrique.

Soutenue le 5 janvier 1998 devant la commission d'examen

Membres de jury : MM. E. CONSTANT Président

Y. CROSNIER Directeur de thèse D. THERON Co-directeur de thèse

M. ILEGEMS Rapporteur

A. SCAVENNEC Rapporteur

P. VIKTOROVITCH Rapporteur

L. MALIER Examinateur

X. WALLART Examinateur

A tous ceux qui me sont chers.

Ce travail a été effectué à l'Institut d'Electronique et de Microélectronique du Nord (IEMN) dirigé par Monsieur le Professeur E. CONSTANT, au Département Hyperfréquences et Semi-conducteurs, dirigé par Monsieur le Professeur G. SALMER. Je les remercie de m'avoir accueilli dans leur laboratoire.

Je remercie vivement Monsieur le Professeur E. CONSTANT, Professeur à l'Université de Lille I, qui me fait l'honneur de présider la commission d'examen.

Je tiens à exprimer ma plus vive reconnaissance envers Monsieur D. THERON, chargé de recherche au CNRS et Monsieur le Professeur Y. CROSNIER qui ont assuré la direction de ce travail. Leurs compétences scientifiques et pédagogiques ainsi que leur disponibilité m'ont permis de mener ce travail à bien dans de très bonnes conditions.

Je remercie sincèrement Monsieur le Professeur M. ILEGEMS, directeur de l'institut de micro et optoélectronique de l'Ecole Fédérale Polytechnique de Lausanne, Monsieur le Professeur P. VIKTOROVITCH de l'Ecole Centrale de Lyon et Monsieur A. SCAVENNEC, responsable du groupement C.C.O. au CNET de Bagneux pour l'honneur qu'ils m'ont fait de juger ce travail et d'en être les rapporteurs.

Je tiens également à remercier Monsieur L .MALIER, Ingénieur au département Composants DSP/STTC à la DGA et Monsieur X. WALLART, chargé de recherche au CNRS qui me font l'honneur d'évaluer ce travail en participant à ce jury d'examen.

Un grand merci aux personnes avec qui j'ai eu le plaisir de travailler à l'IEMN et qui m'ont aidé dans mes différentes réalisations ainsi que les caractérisations de celles-ci. Leurs compétences en MBE, en technologie front-end, en caractérisation ou en technologie back-end, et leurs gentillesses ont facilité mes travaux.

Je ne saurais oublier mes camarades de laboratoire pour toutes ces discussions enrichissantes au long de ces années.

Enfin, je remercie Monsieur J.P. DEHORTER pour la reproduction de ce mémoire.

## Introduction générale

## Chapitre 1

## Généralités

| INTRODUCTION                                                                    | 3  |

|---------------------------------------------------------------------------------|----|

| 1. LES FILIÈRES CONVENTIONNELLES DE TEC                                         | 4  |

| 1.1 Origines                                                                    |    |

| 1.2 Le MESFET GAAS                                                              |    |

| 1.3 LES TECS À HÉTÉROJONCTIONS (HEMTS)                                          |    |

| ,                                                                               |    |

| 1.3.1 Le HEMT GaAlAs/GaAs                                                       |    |

| 1.3.2 Le HEMT pseudomorphique GaAlAs/GaInAs/GaAs (PM-HEMT) et ses améliorations |    |

| 1.3.3 Le HEMT adapté en maille AlInAs/GaInAs/InP (LM-HEMT)                      |    |

| 1.3.4 Le HEMT Métamorphique sur GaAs (MM-HEMT)                                  |    |

| 2. LES AUTRES FILIÈRES                                                          | 13 |

| 2.1 LE MISFET                                                                   | 13 |

| 2.1.1 Le MISFET InP                                                             | 13 |

| 2.1.2 Le DMT GaAs et InP                                                        |    |

| 2.2 LE TRANSISTOR BIPOLAIRE À HÉTÉROJONCTIONS (TBH)                             | 15 |

| 2.3 LES NOUVEAUX MATÉRIAUX                                                      | 17 |

| 2.3.1 Le MISFET GaAs Basse Température (BT)                                     | 17 |

| 2.3.2 Le Carbure de Silicium (SiC)                                              | 18 |

| 2.3.3 Le Nitrure de Gallium (GaN) et les alliages AlGaN et InGaN                |    |

| 3. LA CARACTÉRISATION DES COMPOSANTS                                            | 19 |

| 3.1 La caractérisation statique ou quasi-statique                               | 19 |

| 3.1.1 Présentation du matériel à disposition                                    |    |

| 3.1.1.1 ICCAP                                                                   |    |

| 3.1.1.2 La mesure en impulsion                                                  |    |

| 3.1.2 La mesure des caractéristiques I-V                                        |    |

| 3.1.3 Le courant de grille en configuration diode                               |    |

| 3.1.3.1 La mesure de la diode Schottky en direct                                |    |

| 3.1.3.2 La mesure de la diode Schottky en inverse                               |    |

| 3.1.4 La caractéristique Rds(Vgs)                                               | 25 |

| 3.1.5 La mesure du courant de grille en fonctionnement transistor               | 26 |

| 3.2 CARACTÉRISATION BASSE FRÉQUENCE                                             |    |

| 3.2.1 La mesure de mobilité par magnéto-résistance                              |    |

| 3.2.2 La mesure C(V)                                                            |    |

| 3.3 LA CARACTÉRISATION HYPERFRÉQUENCE PETIT SIGNAL                              |    |

| 3.3.1 Les performances hyperfréquence                                           |    |

| 3.3.1.1 Le gain maximum disponible MAG (Maximum Available Gain)                 |    |

| 3.3.1.2 Le gain stable maximum MSG (Maximum Stable Gain)                        |    |

| 3,3,1,3 Le gain unilatéral U : le gain de MASON                                 | 29 |

| 3.3.1.4 Le gain en courant de court-circuit : H <sub>21</sub> <sup>2</sup>      |    |

| 3.3.2 Le schéma équivalent petit signal                                         |    |

| 3.3.2.1 Détermination des éléments extrinsèques                                 |    |

| 3.3.2.2 Détermination des éléments intrinsèques                                 |    |

| 3.3.3 Performances des transistors a partir du schéma équivalent                |    |

| 3.4 LA CARACTÉRISATION DE PUISSANCE OU GRAND SIGNAL                             |    |

| 3.4.1 Description du banc de mesure                                             |    |

| 3.4.2 Définition des gains                                                      |    |

| 3.4.2.1 Le gain en puissance G <sub>P</sub>                                     |    |

| 3.4.2.2 Le gain transducteur G <sub>T</sub>                                     |    |

| 3.4.3 Définitions des rendements                                                |    |

| 3.4.3.1 Le rendement drain $\eta_D$                                             | 40 |

| 5.4.5.2 Le l'endement en puissance ajoutee (pae                | *************************************** |

|----------------------------------------------------------------|-----------------------------------------|

| 4. ETAT DE L'ART DES TECS POUR LA PUISSANCE                    | 41                                      |

| 4.1 DENSITÉ DE PUISSANCE DE SORTIE DES TECS DISCRETS           | 41                                      |

| 4.2 RENDEMENT EN PUISSANCE AJOUTÉE DES TECS DISCRETS           |                                         |

| CONCLUSION                                                     | 45                                      |

|                                                                |                                         |

| Chapitre 2                                                     |                                         |

| Technologie des TECs appliquée aux filières GaAs pseudon       | norphique et                            |

| métamorphique et à la filière InP                              |                                         |

| INTRODUCTION                                                   | 49                                      |

| 1. LES ÉTAPES GÉNÉRALES                                        | 51                                      |

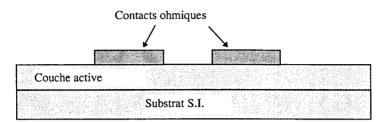

| 1.1 LES CONTACTS OHMIQUES                                      | 51                                      |

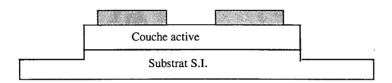

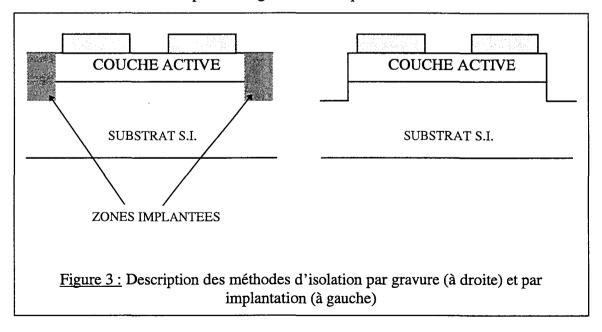

| 1.2 L'ISOLATION                                                | 52                                      |

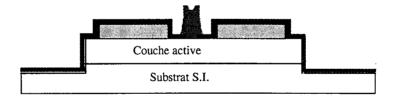

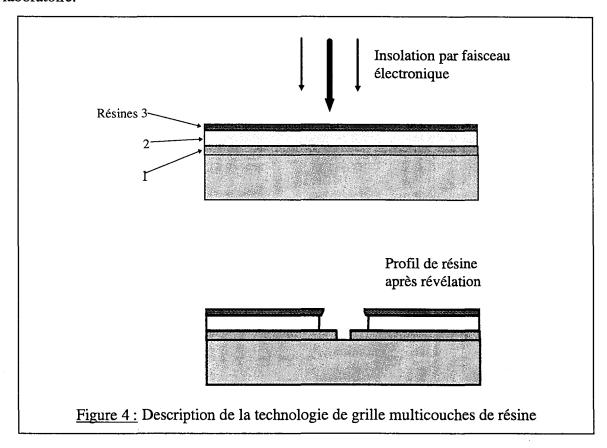

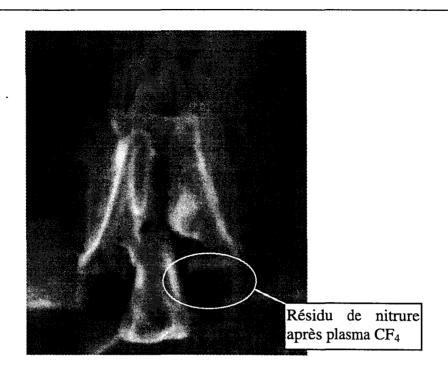

| 1.3 LE FOSSÉ DE GRILLE                                         |                                         |

| 1.4 LE DÉPÔT DE GRILLE                                         |                                         |

| 1.5 LES PLOTS D'ÉPAISSISSEMENT                                 |                                         |

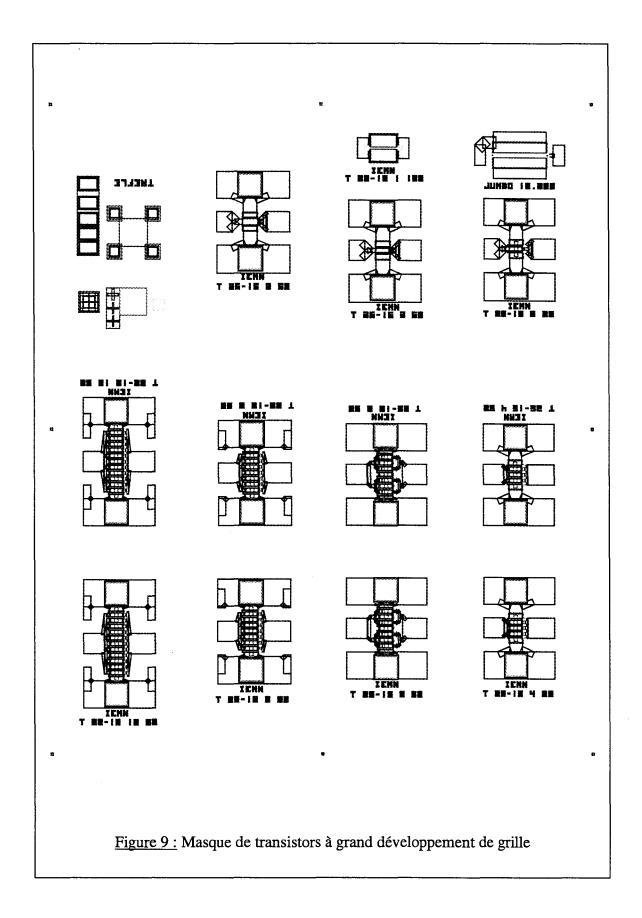

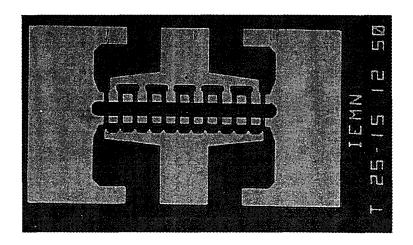

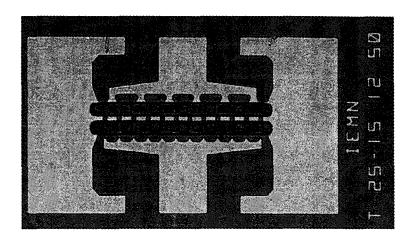

| 2. LES ÉTAPES SPÉCIFIQUES AUX GRANDS DÉVELOPPEMENTS            | 50                                      |

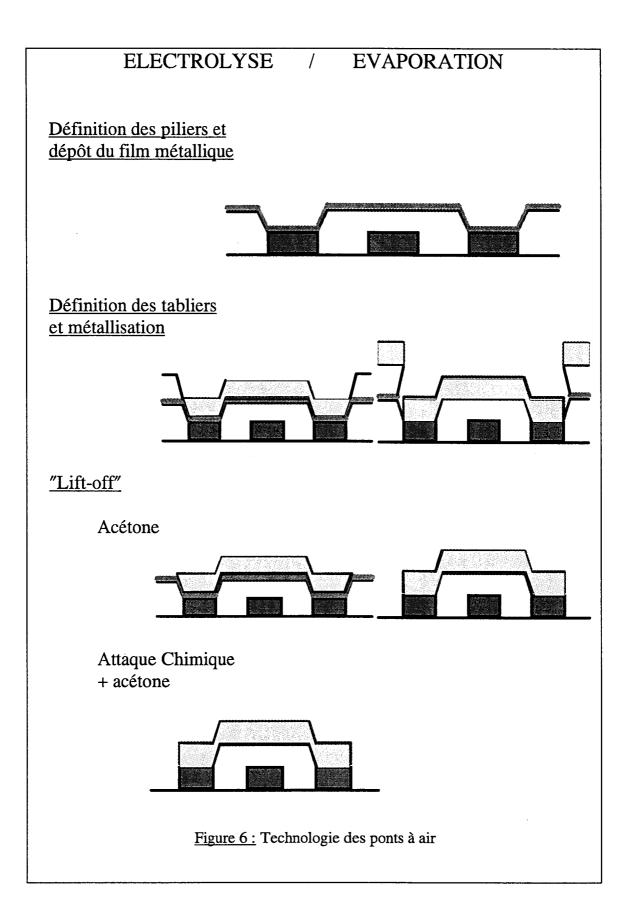

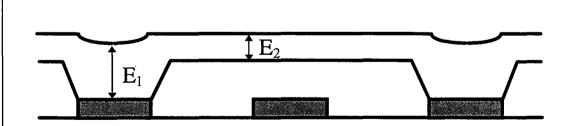

| 2.1 LES PONTS À AIR                                            | 5                                       |

| 2.1.1 La technologie                                           |                                         |

| 2.1.2 Etude électrique du pont                                 |                                         |

| 2.2 LES TROUS MÉTALLISÉS                                       | 66                                      |

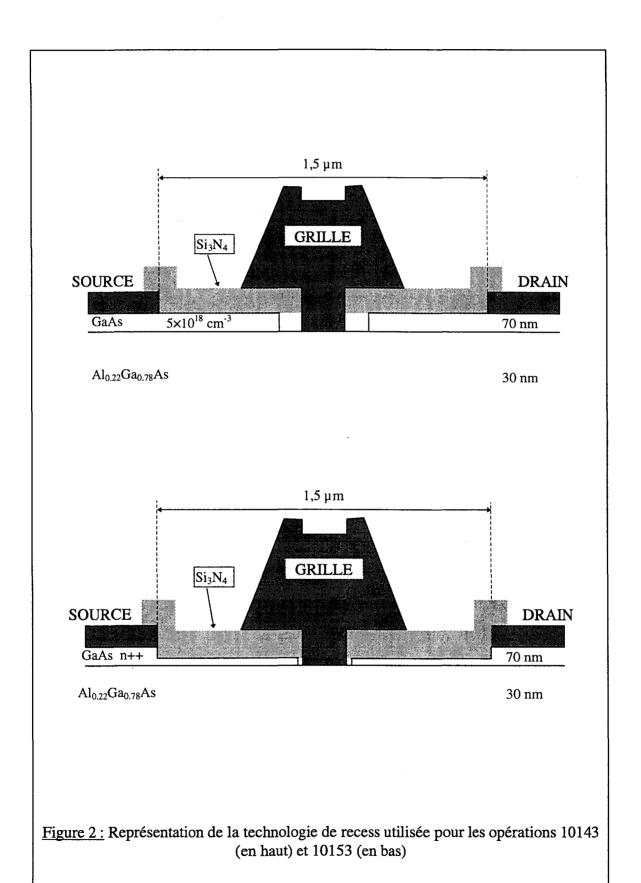

| 3. LA TECHNOLOGIE DE LA FILIÈRE GaAs PSEUDOMORPHIQUE ET SES AM | TÉLIORATIONS69                          |

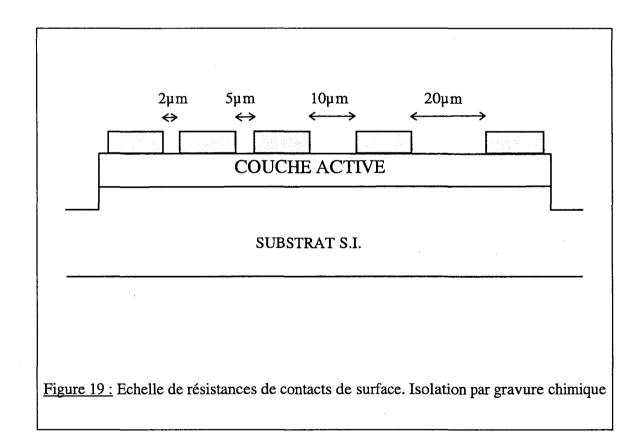

| 3.1 LES CONTACTS OHMIQUES                                      |                                         |

| 3.2 LE MESA                                                    |                                         |

| 3.3 LA GRILLE                                                  |                                         |

| 3.4 LA GRAVURE DU FOSSÉ DE GRILLE                              |                                         |

|                                                                |                                         |

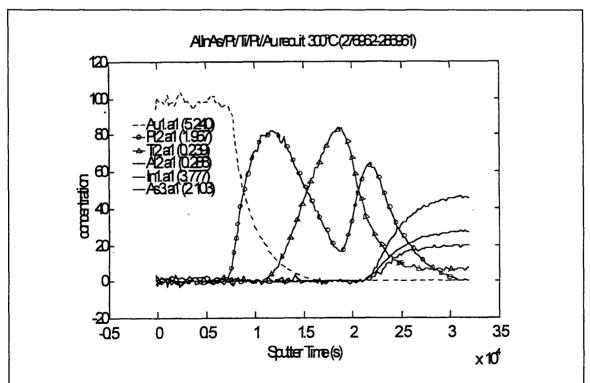

| 4. LA TECHNOLOGIE DES FILIÈRES InP ET GaAs MÉTAMORPHIQUE       | 70                                      |

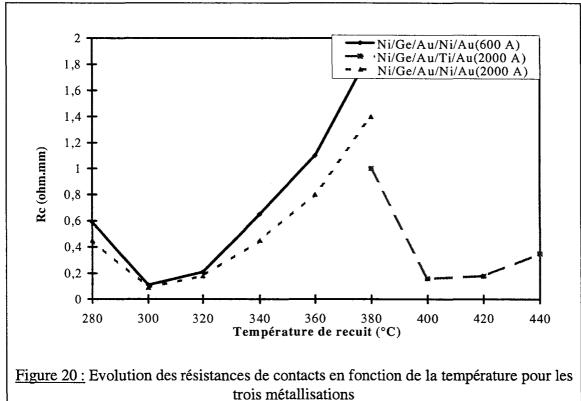

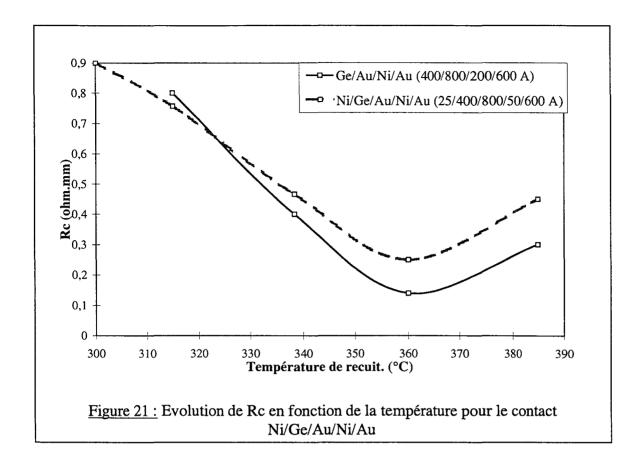

| 4.1 LES CONTACTS OHMIQUES                                      |                                         |

| 4.1.1 La filière InP                                           |                                         |

| 4.1.2 La filière GaAs Métamorphique                            |                                         |

| 4.2 L'ISOLATION ET LA GRAVURE DU FOSSÉ DE GRILLE               |                                         |

| 4.2.1 L'isolation4.2.2 La gravure du fossé de grille           |                                         |

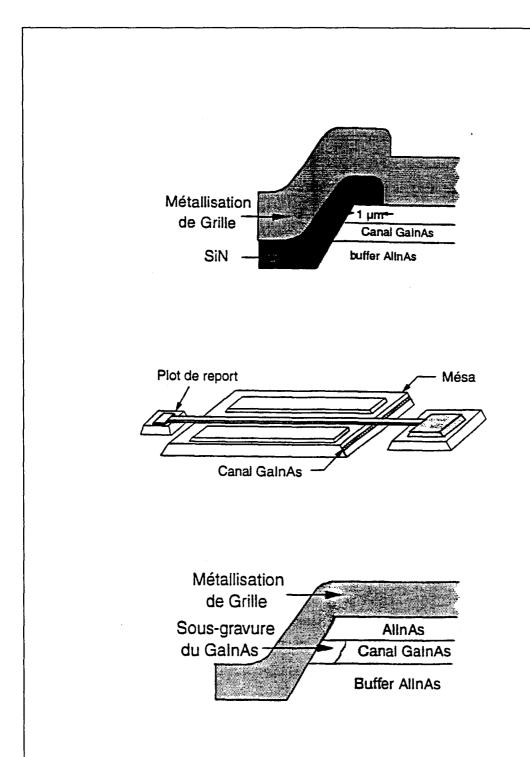

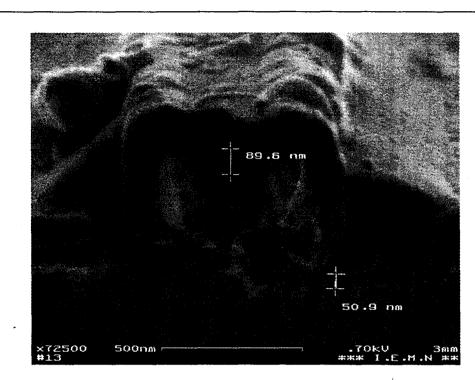

| 4.3 LA MÉTALLISATION ET LA TECHNOLOGIE DE GRILLE               |                                         |

| 4.3.1 La métallisation de grille                               |                                         |

| 4.3.2 La technologie de grille                                 |                                         |

| 4 4 I A PASSIVATION DES TRANSISTORS                            | 100                                     |

## Chapitre 3

# Etude des potentialités de la filière InP. Optimisation de la technologie et de la structure des transistors

| INTRODUCTION                                                                     | 117 |

|----------------------------------------------------------------------------------|-----|

| 1. LES PROBLÈMES RENCONTRÉS DANS LES HEMTS DE PUISSANCE ET LES SOLU<br>POSSIBLES |     |

| 1.1 Le claquage à canal fermé                                                    | 119 |

| 1.2 LE CLAQUAGE À CANAL OUVERT.                                                  |     |

| 1.3 LES SOLUTIONS TECHNOLOGIQUES                                                 |     |

| 1.3.1 Les solutions pour réduire l'ionisation par impact                         |     |

| 1.3.2 Les solutions pour réduire la remontée des trous                           |     |

| 1.3.3 Les solutions pour réduire l'injection dans le buffer                      |     |

| 1.4 RÉSUMÉ. CHOIX DES SOLUTIONS À ÉTUDIER                                        |     |

| 2. MISE AU POINT DE LA COUCHE ET DE LA TECHNOLOGIE DE RÉFÉRENCE                  | 127 |

| 2.1 MISE AU POINT DE LA COUCHE PAR SIMULATION UNIDIMENSIONNELLE                  | 127 |

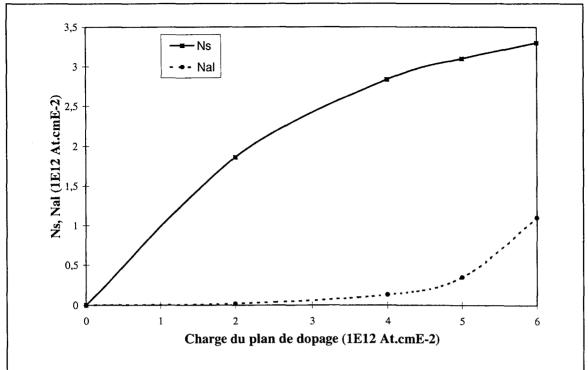

| 2.1.1 Détermination du plan de dopage optimal                                    |     |

| 2.1.2 Mise au point des épaisseurs des couches canal et barrière                 |     |

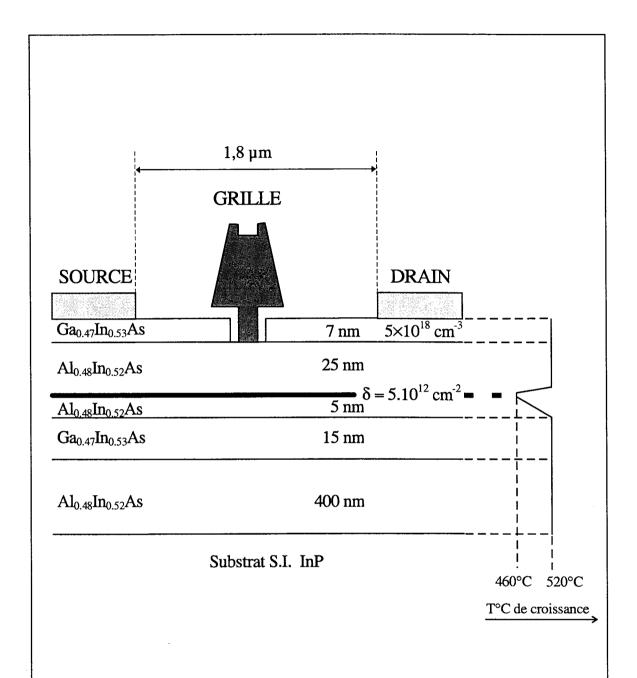

| 2.2 RÉALISATION ET CARACTÉRISATION DE L'OPÉRATION 10237                          |     |

| 2.2.1 Epitaxie et technologie                                                    | 130 |

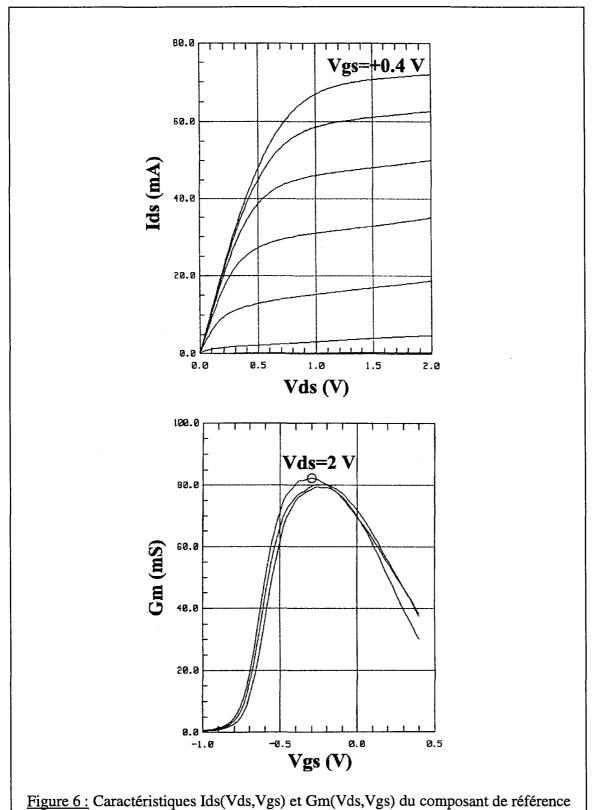

| 2.2.2 La caractérisation statique                                                |     |

| 2.2.3 La caractérisation hyperfréquence                                          | 137 |

| 2.3 CONCLUSION                                                                   |     |

| 3. ETUDE DE LA COUCHE TAMPON                                                     | 139 |

| 3.1 LA COUCHE TAMPON À BARRIÈRE DE COMPENSATION                                  |     |

| 3.2 LA COUCHE TAMPON BASSE TEMPÉRATURE (BT)                                      | 140 |

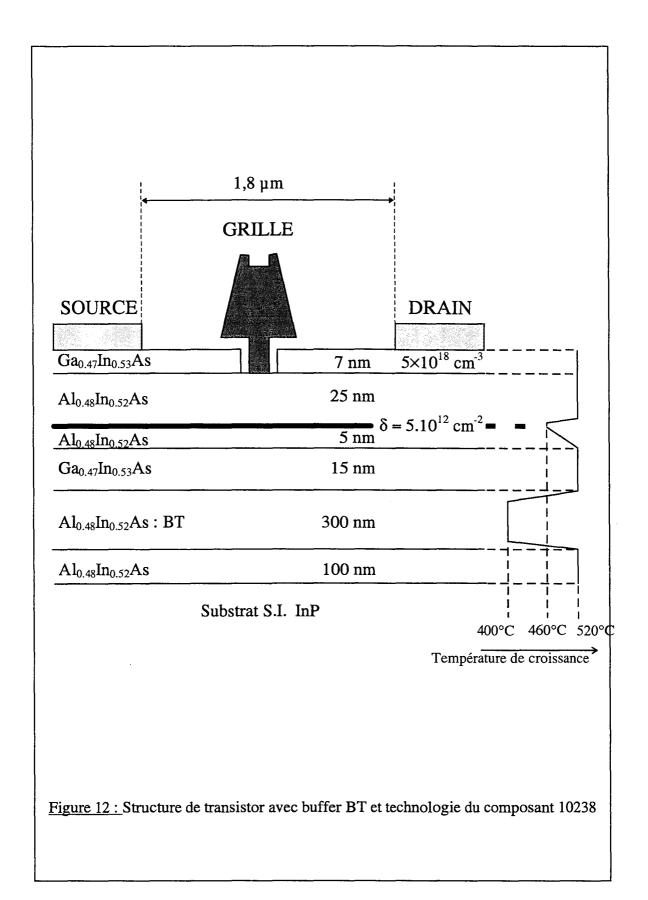

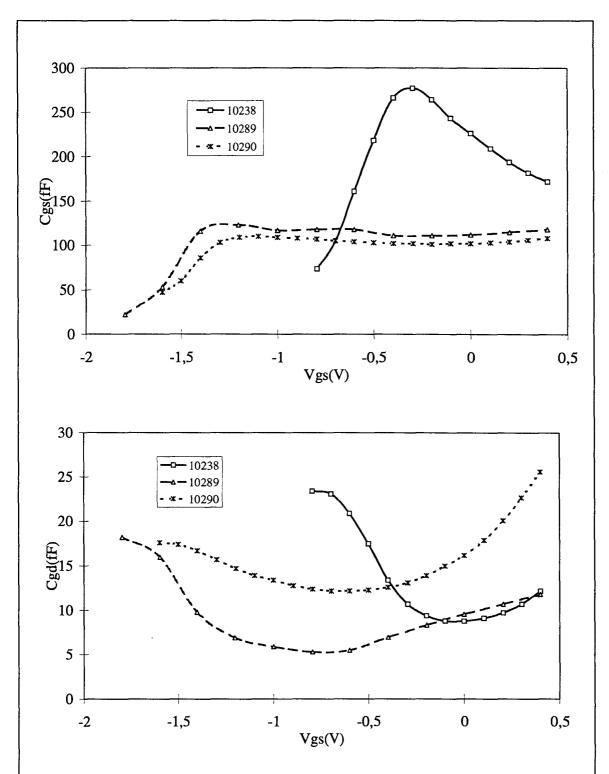

| 3.3 RÉALISATION ET CARACTÉRISATION DE L'OPÉRATION 10238                          | 140 |

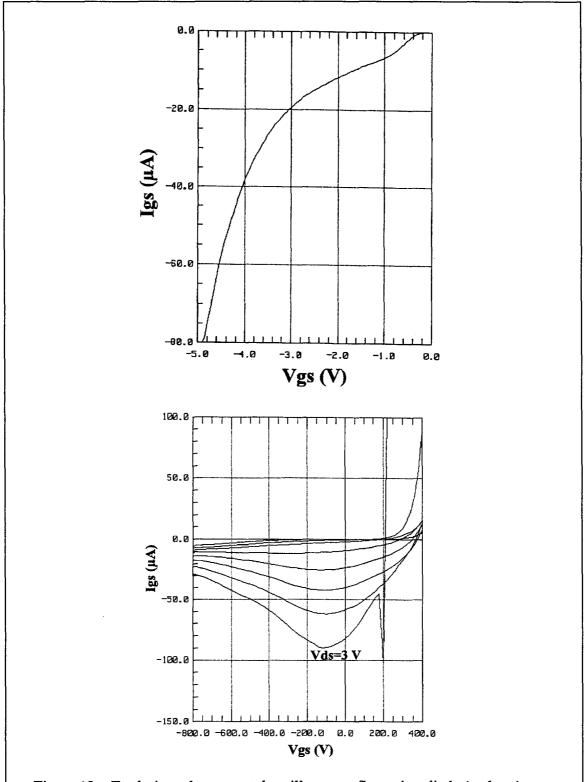

| 3.3.1 La caractérisation statique                                                | 142 |

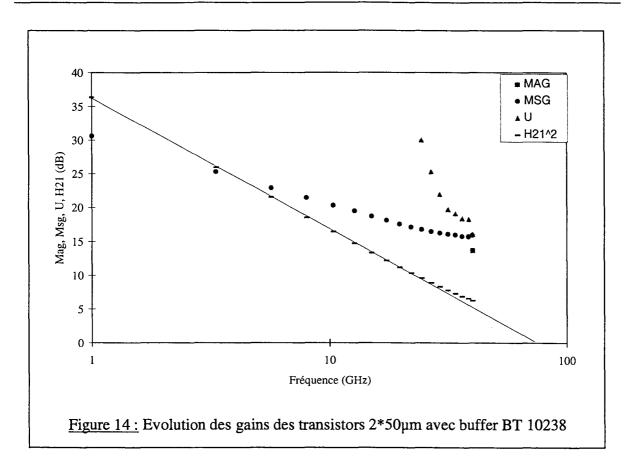

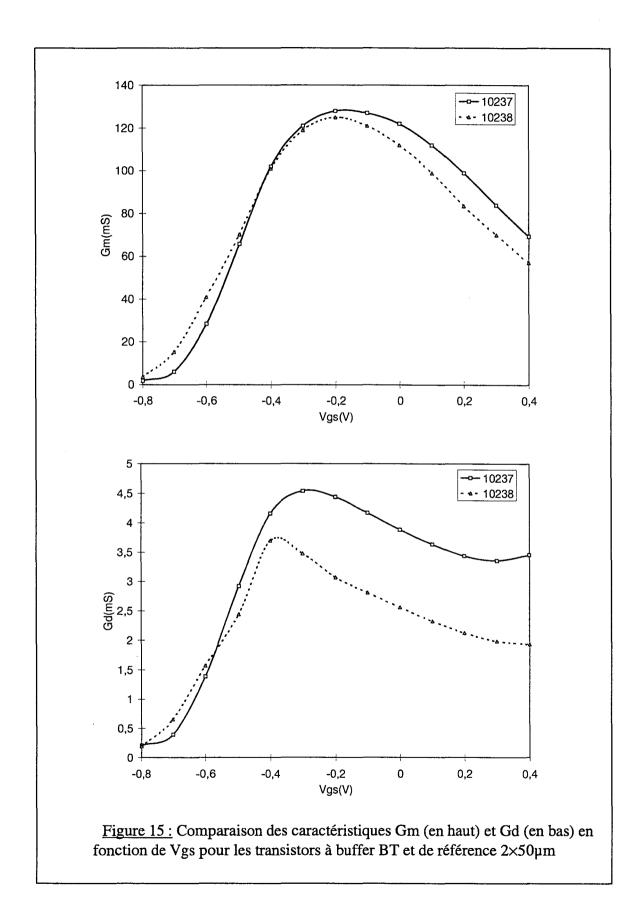

| 3.3.2 La caractérisation hyperfréquence                                          | 144 |

| 3.4 CONCLUSION                                                                   | 148 |

| 4. ETUDE DE LA CONFIGURATION DU FOSSÉ DE GRILLE                                  | 148 |

| 4.1 RÉALISATION TECHNOLOGIQUE                                                    |     |

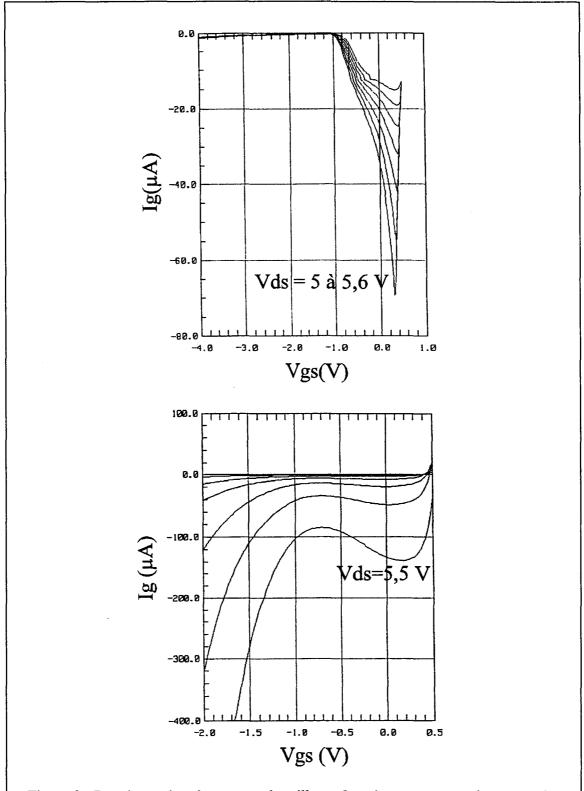

| 4.2 LA CARACTÉRISATION STATIQUE                                                  |     |

| 4.3 LES PERFORMANCES HYPERFRÉQUENCES                                             |     |

| 4.4 Le schéma équivalent                                                         |     |

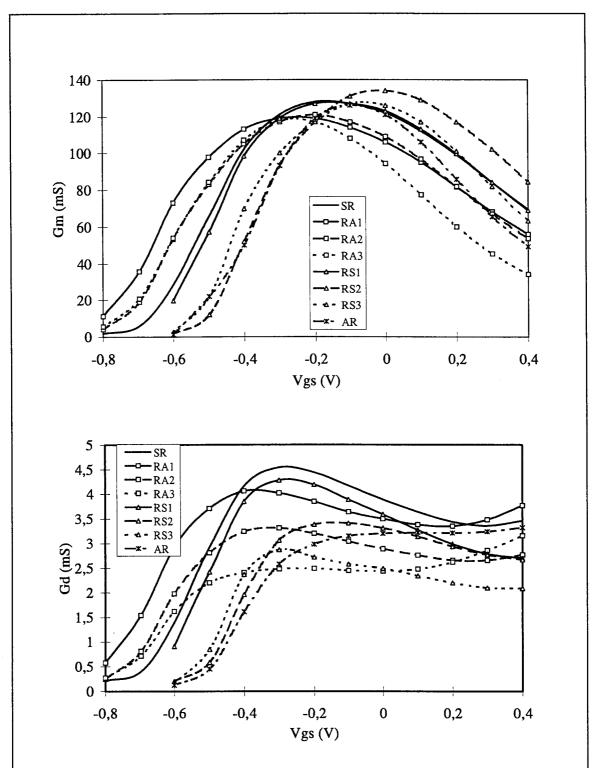

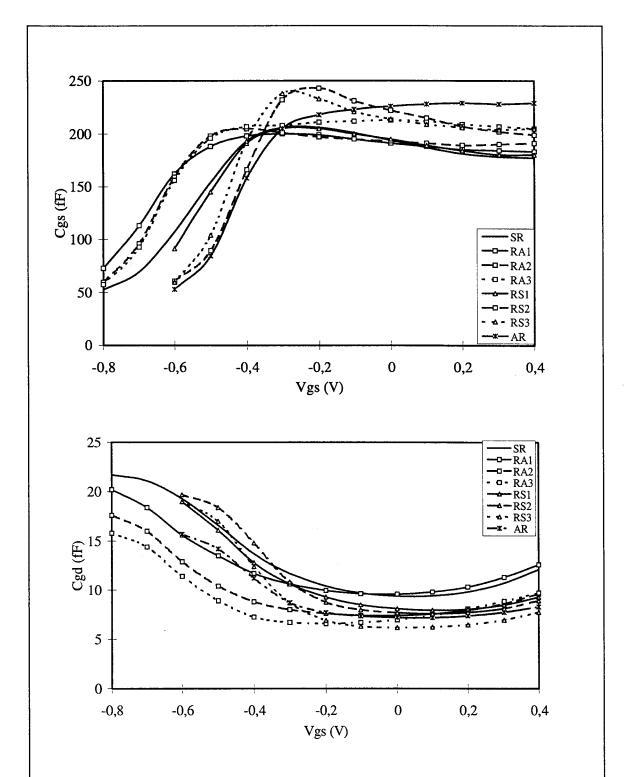

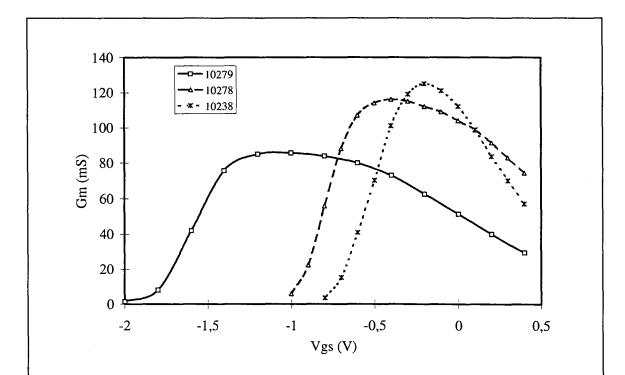

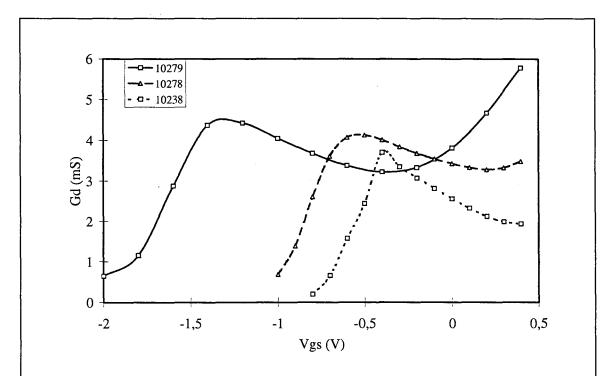

| 4.4.1 La transconductance et la conductance de sortie                            |     |

| 4.4.2 La capacité grille-source et la capacité grille-drain                      |     |

| 4.4.3 Relation entre les performances et le schéma équivalent                    |     |

| 4.4.4 Limitations de la longueur du fossé de grille                              |     |

| 4.5 CONCLUSION                                                                   | 163 |

| 5. ETUDE DES BARRIÈRES DE TROUS EN AlinAs À FORT TAUX D'ALUMINIUM                |     |

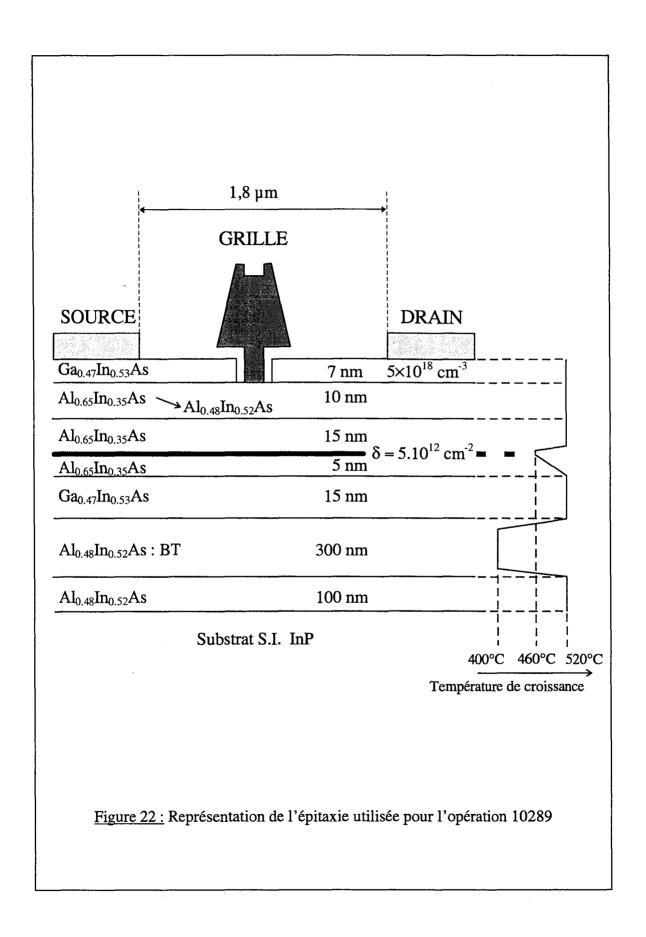

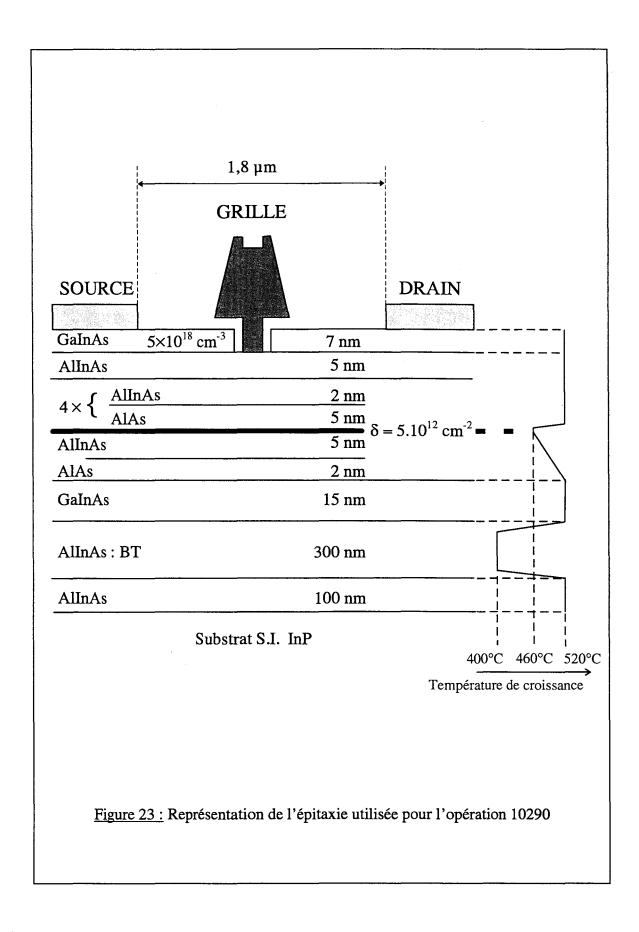

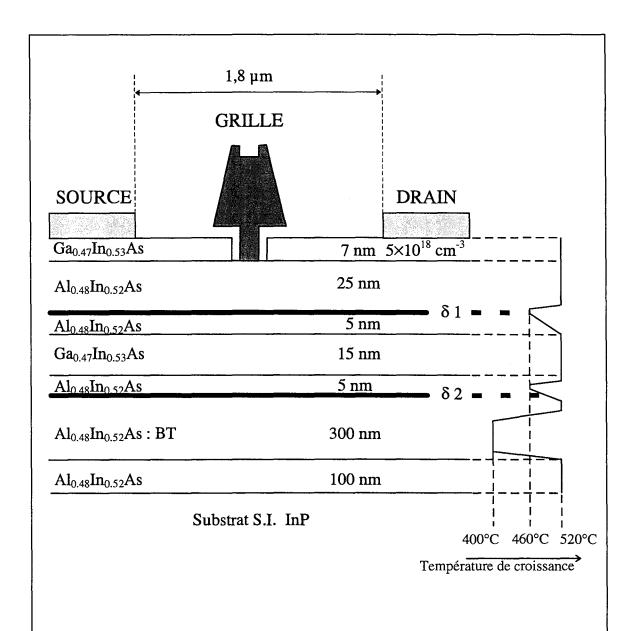

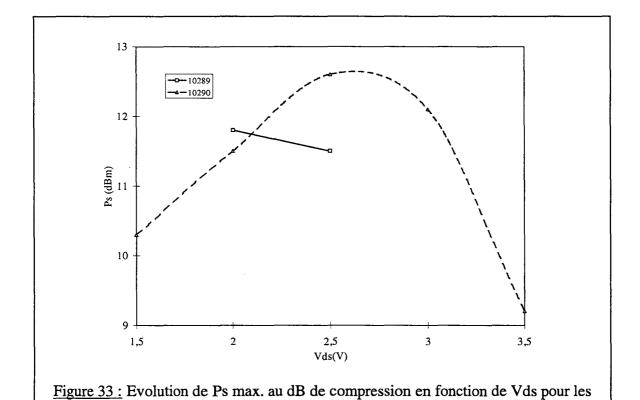

| 5.1 Réalisation des opérations 10289 - 10290                                     |     |

| 5.2 LA CARACTÉRISATION STATIQUE ET HYPERFRÉQUENCE                                |     |

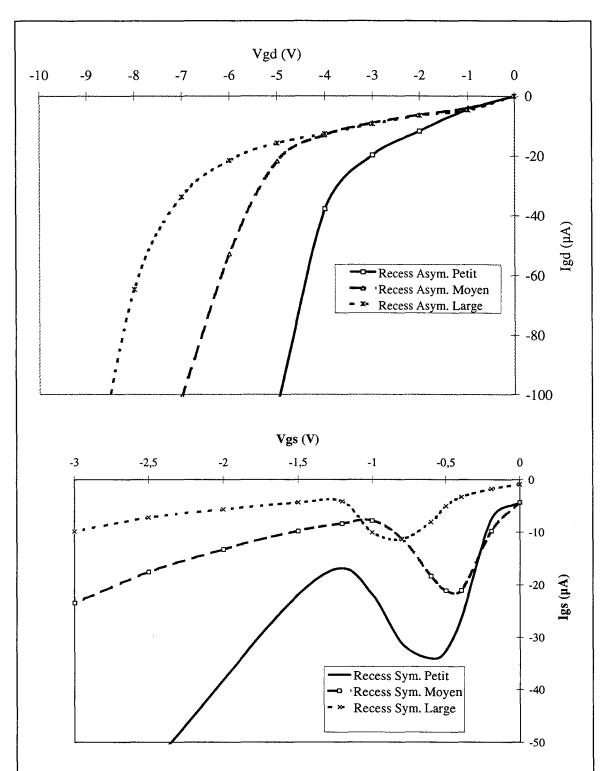

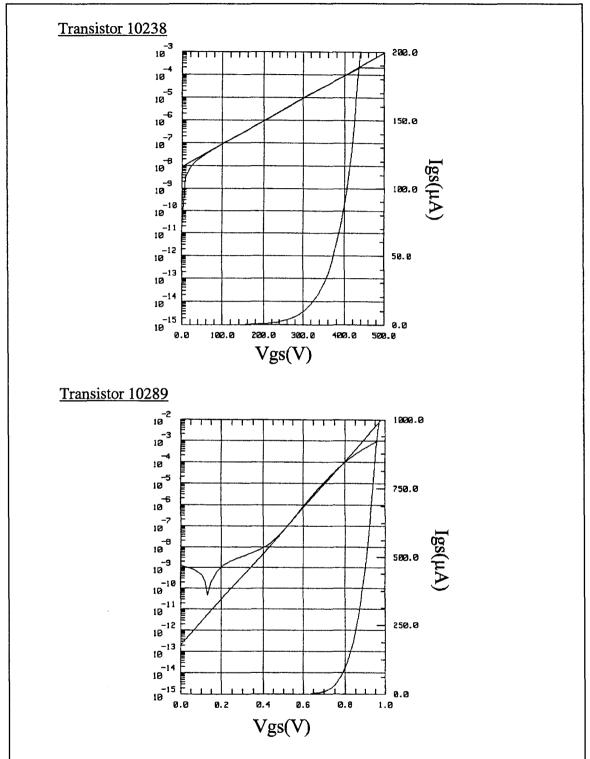

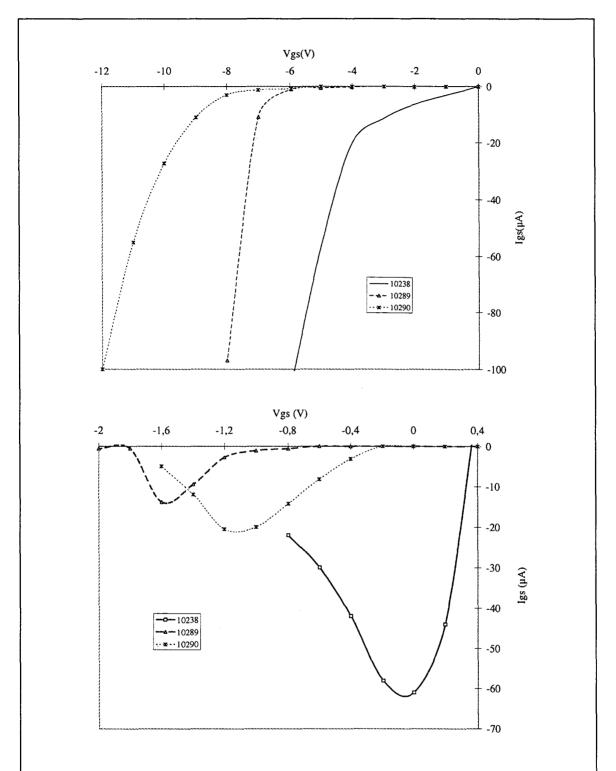

| 5.2.1 Le claquage en diode                                                       |     |

| 5.2.2 Le claquage à canal ouvert                                                 |     |

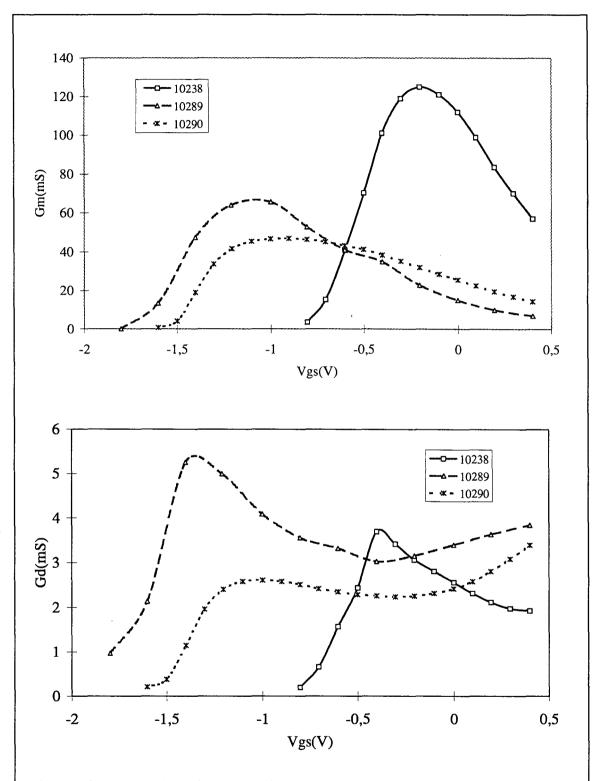

| 5.2.3 Les performances en fréquence et en gain                                   |     |

| 5.2.4 Le schéma équivalent                                                       |     |

| 5.3 CONCLUSION                                                                   |     |

| 6. ETUDE DES STRUCTURES À DEUX PLANS DE DOPAGE                                   | 178 |

| 6.1 MISE AU POINT THÉORIQUE DES ÉPITAXIES                                        | 170                         |

|----------------------------------------------------------------------------------|-----------------------------|

| 0.2 KEALISATION DES OPERATIONS 102// * 102/9 * 102/9                             |                             |

| 6.3 LA CARACTÉRISATION STATIQUE ET HYPERFRÉQUENCE                                |                             |

| 6.3.1 La caractérisation statique                                                |                             |

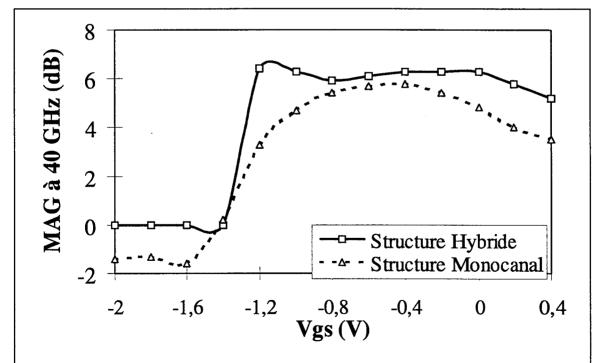

| 6.3.2 Les performances en fréquence et en gain                                   |                             |

| 6.3.3 Le schéma équivalent                                                       |                             |

| 6.4 Conclusion.                                                                  | 188                         |

| 7. RÉSULTATS DE PUISSANCE DES TRANSISTORS RÉALISÉS                               | 189                         |

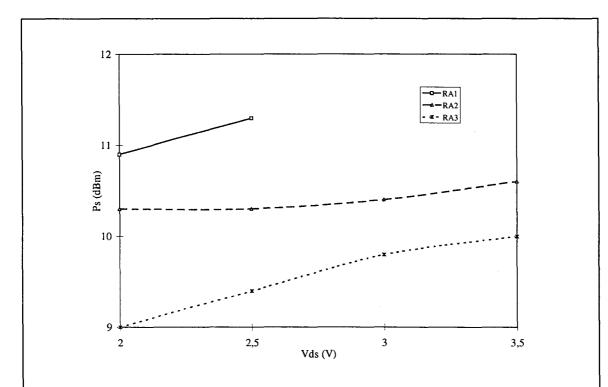

| 7.1 POTENTIALITÉS DES TRANSISTORS EN RÉGIME STATIQUE                             | 189                         |

| 7.2 POTENTIALITÉS DES TRANSISTORS EN RÉGIME GRAND SIGNAL                         |                             |

| 7.3 CONCLUSION                                                                   |                             |

| 8. PROPOSITION DE LA STRUCTURE FINALE - RÉSULTATS                                | 195                         |

| 8.1 RÉSULTATS DE CARACTÉRISATION STATIQUE ET HYPERFRÉQUENCE PETIT SIGNAL         | 107                         |

| 8.1.1 Caractérisation statique                                                   |                             |

| 8.1.2 Caractérisation de claquage                                                |                             |

| 8.1.3 Caractérisation hyperfréquence petit signal                                |                             |

| 8.2 PERFORMANCES EN PUISSANCE                                                    |                             |

| 8.3 CONCLUSION                                                                   |                             |

| CONCLUSION                                                                       | 205                         |

| Chapitre 4                                                                       |                             |

| Comparaison des filières GaAs Pseudomorphique, GaAs Métamo                       | rphique et                  |

| Comparaison des filières GaAs Pseudomorphique, GaAs Métamo                       | •                           |

| Comparaison des filières GaAs Pseudomorphique, GaAs Métamo<br>InP                | •                           |

| Comparaison des filières GaAs Pseudomorphique, GaAs Métamo.  InP  Introduction   | 209                         |

| Comparaison des filières GaAs Pseudomorphique, GaAs Métamol InP  INTRODUCTION    | 209                         |

| Comparaison des filières GaAs Pseudomorphique, GaAs Métamol InP  INTRODUCTION    | 209<br>210                  |

| Comparaison des filières GaAs Pseudomorphique, GaAs MétamolInP  INTRODUCTION     | 209210211                   |

| Comparaison des filières GaAs Pseudomorphique, GaAs Métamol InP  INTRODUCTION    | 209210211217                |

| Comparaison des filières GaAs Pseudomorphique, GaAs Métamo InP  INTRODUCTION     | 209210211217220             |

| Comparaison des filières GaAs Pseudomorphique, GaAs Métamo InP  INTRODUCTION     | 209210211220220226          |

| Comparaison des filières GaAs Pseudomorphique, GaAs MétamolinP  INTRODUCTION     | 209210210217226228          |

| Comparaison des filières GaAs Pseudomorphique, GaAs MétamolinP  INTRODUCTION     | 209210210211220220226228    |

| Comparaison des filières GaAs Pseudomorphique, GaAs Métamoline InP  INTRODUCTION | 209210210217226226228229232 |

| Comparaison des filières GaAs Pseudomorphique, GaAs MétamolinP  INTRODUCTION     |                             |

| Comparaison des filières GaAs Pseudomorphique, GaAs Métamoline InP  INTRODUCTION |                             |

Conclusion générale

Le monde que nous connaissons bénéficie d'un confort grandissant jour après jour. L'unanimité est faite pour associer directement ou indirectement ces améliorations au progrès de l'électronique.

Ce progrès s'est concrétisé, depuis l'invention du transistor en 1952, par une réduction des dimensions afin d'intégrer à très haute densité le nombre grandissant de transistors formant une puce, dans le but d'accroître les performances des systèmes. Aujourd'hui, la naissance d'applications à très haute fréquence (supérieures à quelques GHz) nécessitent l'exploitation de voies autres que celle du traditionnel silicium.

Il en est une, explorée depuis quelques années, qui nécessite encore l'attention de la communauté scientifique pour atteindre la maturité d'une technologie industrielle. Celle-ci consiste en une association de matériaux de type III et de matériaux de type V tel que le GaAs ou l'InP.

Parmi les différentes fonctions assurées par les systèmes électroniques, nous nous proposons dans ce travail d'étudier l'amplification de puissance et plus particulièrement les potentialités des transistors à effet de champ dans les filières GaAs et InP pour cette application. Ce travail s'intègre dans le cadre de deux contrats DRET portant sur la réalisation dans la filière GaAs d'un amplificateur de puissance en classe B à 26 GHz et sur la réalisation dans la filière InP d'un amplificateur de puissance à 60 GHz.

Dans le premier chapitre, les différentes filières de transistors à effet de champ sont présentées dans leur ordre d'apparition. Ensuite, les matériaux et familles de transistors concurrents aux TECs sont présentés. Puis, un inventaire des différentes méthodes de caractérisation des composants est effectué. Celles-ci sont utilisées dans la suite de notre travail. Enfin, un état de l'art des performances des transistors discrets dédiés à l'amplification de puissance est présenté.

Dans le deuxième chapitre, nous présentons de manière générale, les différentes étapes technologiques possibles pour la réalisation de transistors, ainsi que les étapes spécifiques à la réalisation de transistors à grand développement de grille. Enfin, sont présentées les technologies de la filière GaAs (AlGaAs/InGaAs), de la filière InP et la filière métamorphique sur GaAs (AlInAs/InGaAs).

Le troisième chapitre est consacré à l'étude de la filière InP. Après avoir dressé une liste des mécanismes physiques et des effets limitatifs sur l'utilisation de cette filière pour l'amplification grand signal, nous abordons les études pratiques. Celles-ci sont divisées en deux grandes catégories portant sur l'étude de la zone active (épitaxie) ou l'étude des paramètres technologiques. Dans les deux cas, l'objectif est de permettre un accroissement de la densité de courant et/ou de la tenue en tension des transistors. Les différentes réalisations sont caractérisées en puissance afin de valider ou d'invalider les paramètres étudiés. Enfin, la réalisation et les résultats de caractérisation de deux structures englobant les éléments bénéfiques sont présentés. L'une d'elle a permis d'atteindre l'état de l'art mondial.

Le quatrième chapitre, traite des filières pseudomorphique et métamorphique sur substrat GaAs. La filière pseudomorphique est étudiée par le biais d'études technologiques

visant à améliorer les performances des transistors. De plus, deux structures à deux canaux sont étudiées afin de valider la possible utilisation pour l'amplification de puissance. Enfin, l'étude de la filière métamorphique se concrétise par la réalisation et la caractérisation d'un transistor. Le but étant de donner un aperçu des potentialités de cette filière face aux deux autres.

Chapitre 1

#### **Introduction**

Avant d'entrer dans le sujet que nous avons traité, il nous a semblé utile de commencer par un chapitre permettant à la fois de situer nos travaux dans le vaste domaine que couvrent les transistors à effet de champ (TEC) pour amplification de puissance en hyperfréquence et de définir les différentes notions qui seront utilisées dans les chapitres suivant.

Pour commencer, un inventaire des différentes filières de transistor à effet de champ sera effectué. La présentation suivant l'ordre chronologique de l'apparition de ces différentes filières permettra de présenter les améliorations apportées au fil des années et donnera une idée claire et précise sur les filières actuellement en phase d'étude.

Ensuite, toujours pour situer nos travaux, nous présenterons les diverses structures des transistors à effet de champ ainsi que les nouveaux matériaux dont pourraient émerger les filières futures.

Puis, une présentation complète des différentes méthodes de caractérisation appliquées aux transistors sera effectuée, celles-ci permettant de valider les réalisations technologiques pour la caractérisation statique. La caractérisation dynamique (hyperfréquence) permet quant à elle de réaliser des comparaisons entre les différents composants grâce à la détermination des performances en fréquence de ceux-ci ou encore, des paramètres physiques constituant les transistors. Nous présenterons également la caractérisation grand signal spécifique au transistors de puissance, ainsi que les différentes grandeurs utilisées pour définir les potentialités des transistors à travailler dans ce domaine.

Enfin, nous ferons un bilan des meilleures performances mondiales obtenues pour les transistors à effet de champ de puissance.

#### 1. Les filières conventionnelles de TEC

#### 1.1 Origines

Le TEC est né en 1952 d'après une idée de W.Shockley [1]. Il proposa de déposer aux extrémités d'un barreau de semi-conducteur, deux électrodes appelées source et drain. Entre ces deux électrodes, il y déposa une troisième, la grille afin de pouvoir moduler le courant traversant le barreau de semi-conducteur.

#### 1.2 Le MESFET GaAs

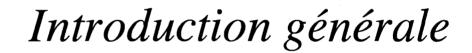

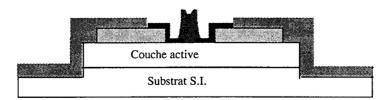

Longtemps considéré comme le composant de référence pour l'amplification de puissance en hyperfréquence, le MESFET GaAs est constitué (fig.1) d'une couche de GaAs dopée (n) épitaxiée sur substrat GaAs Semi-Isolant ou directement par implantation de donneurs.

Pour améliorer la montée en fréquence du composant, il est nécessaire de diminuer la longueur de grille Lg. Il faut alors, pour conserver une efficacité de commande de grille efficace, diminuer l'épaisseur de la couche dopée pour garder un rapport d'aspect Lg/a au moins égal à 5. Si l'application envisagée pour le composant est l'amplification de puissance microonde, il faut que le composant délivre un courant le plus élevé possible. Par conséquent, il faut augmenter le dopage de la couche active. Cette modification de la couche active entraîne une augmentation du champ électrique dans la structure et par conséquent une

diminution de la tenue en tension du transistor (tension de claquage). Cela constitue la limitation principale de ce type de transistor.

Néanmoins, il faut préciser que les nombreux travaux réalisés ont permis d'obtenir des densités de puissance d'environ 700mW/mm à 35 GHz [2].

Enfin, si le MESFET devient de plus en plus important dans le domaine de la production, il est quelque peu tombé en désuétude dans le domaine de la recherche. En effet, il a été supplanté par la solution apportée pour remédier aux limitations du composant : les hétérojonctions.

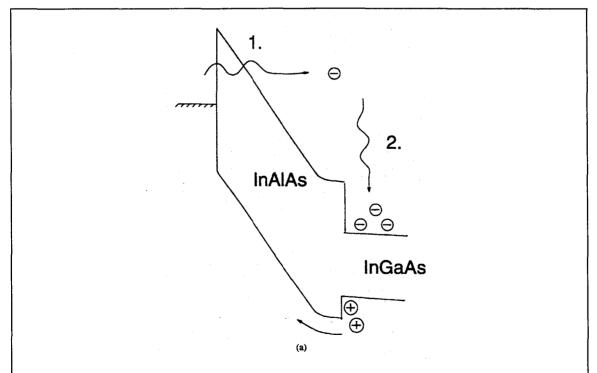

#### 1.3 Les TECs à hétérojonctions (HEMTs)

Les développements des techniques des méthodes de croissances de semi-conducteurs telles que l'épitaxie par jet moléculaire (EJM ou MBE pour Mollecular Beam Epitaxy) ou le dépôt en phase vapeur d'organo-métallique (MOCVD en anglais) ont permis d'améliorer considérablement la qualité des interfaces entre matériaux semi-conducteurs.

Grâce à ces progrès, une nouvelle structure de transistors a vu le jour au début des années 80 : le HEMT (High Electron Mobility Transistor). Ce composant utilise les propriétés électriques des jonctions entre deux semi-conducteurs différents. Dans ce cas, les porteurs libres se trouvent séparés des dopants de la couche de donneurs [3], ce qui a pour conséquence l'obtention d'une importante quantité de charge (appelée gaz d'électrons) localisée dans le puits de potentiel de GaAs près de l'interface des deux matériaux. Ce résultat obtenu grâce à la déformation des bandes de conduction et de valence des matériaux à l'interface est dû à la différence de bande interdite des deux matériaux et au dopage sélectif de la barrière.

Notons que la séparation spatiale entre les donneurs ionisés et porteurs libres diminue les effets d'interactions. La globalité de ces effets contribue à accroître les propriétés de transport par rapport au MESFET.

Outre les performances en bruit améliorées grâce à la diminution des interactions entre porteurs, ce sont des courants et des transconductances plus élevées qui peuvent être obtenus.

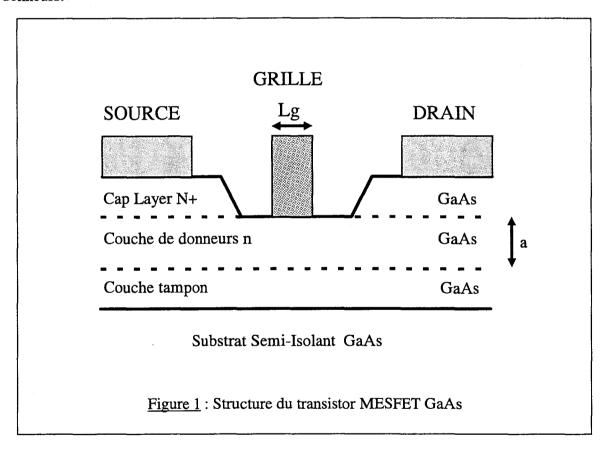

#### 1.3.1 Le HEMT GaAlAs/GaAs

Le HEMT GaAlAs est le premier des transistors à hétérojonctions. Il consiste à associer (fig.2) un matériau fortement dopé à large bande interdite à un matériau intrinsèque de bande interdite plus faible.

Ainsi, cette structure peut être optimisée en choisissant le pourcentage d'aluminium de la couche de GaAlAs suffisant pour obtenir une discontinuité de bande de conduction GaAlAs/GaAs (valeur maximale de l'ordre de 0,2 eV) sans introduire de centres DX [4], qui auraient pour conséquence de piéger les électrons sur les donneurs, et en dopant au maximum la couche de donneurs. De cette façon, des densités de charge de l'ordre de 0,8.10<sup>12</sup> cm<sup>-2</sup> peuvent être obtenues et ont permis de réaliser des transistors délivrant 400mW/mm à 60 GHz ou 560 mW/mm à 40 GHz [5].

Cependant, il faut remarquer que la grille est comme dans le cas du MESFET, déposée sur une couche de matériau dopée, ce qui par conséquent limite la tension de claquage du composant.

De plus, notons que l'avènement des plans de dopage a permis de déposer la grille sur un matériau nid (non intentionnellement dopé). Enfin, l'obtention de barrières plus élevées avec d'autres matériaux a rendu le HEMT conventionnel moins attractif.

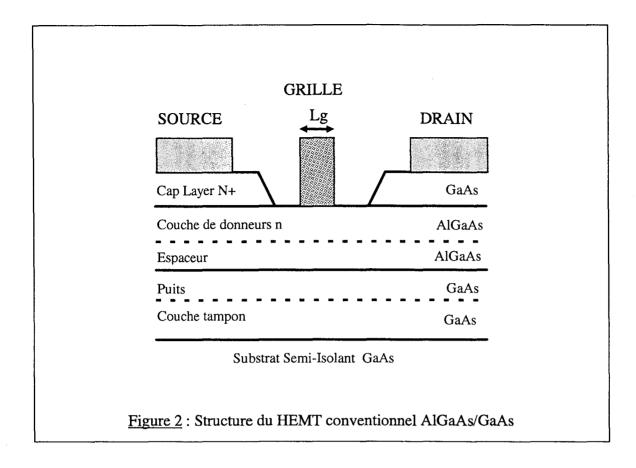

## 1.3.2 Le HEMT pseudomorphique GaAlAs/GaInAs/GaAs (PM-HEMT) et ses améliorations

Une augmentation du taux d'aluminium dans la couche de donneurs doit permettre d'accroître la densité de charge transférée dans le puits du HEMT conventionnel grâce à une discontinuité de bande de conduction plus importante entre les deux matériaux en jeu. Néanmoins, cette augmentation a pour effet d'introduire des centres DX. Le blocage des donneurs empêche alors le transfert de charge et par conséquent, l'augmentation du courant.

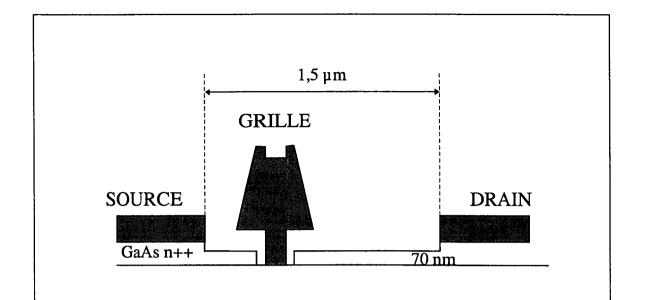

Par conséquent, pour augmenter la discontinuité de bande de conduction, il est nécessaire de changer de matériau. Il s'avère qu'il est préférable de changer le matériau constituant le puits pour le remplacer par un matériau possédant une mobilité électronique plus élevée afin d'accroître les potentialités pour la montée en fréquence. C'est ainsi qu'est apparu le HEMT GaAlAs/GaInAs/GaAs (fig.3).

Le composant consiste en une croissance de GaInAs sur substrat GaAs. Le matériau GaInAs possédant un paramètre de maille différent de celui du GaAs, doit se déformer afin de s'adapter au GaAs. L'épaisseur de GaInAs restant faible (de l'ordre de 100 Å), le matériau ne se relaxe pas. Pour cette raison, la structure formée par ces matériaux est appelée pseudomorphique. Ensuite, est épitaxiée la couche de donneurs GaAlAs.

L'hétérojonction formée par le couple GaAlAs/GaInAs présente une plus importante discontinuité de bande de conduction (0,3 eV) comparée à celle du couple GaAlAs/GaAs (0,2 eV). Il en découle une densité de charge Ns dans le puits plus élevée, ce qui par conséquent, dispense de l'utilisation de fort taux d'aluminium pour la couche de GaAlAs, évitant ainsi les effets néfastes des centres DX.

L'autre avantage de l'utilisation du GaInAs est l'obtention d'une deuxième hétérojonction à l'arrière du puits permettant une nette diminution de l'injection des porteurs vers le substrat GaAs et par conséquent, un meilleur contrôle (modulation) des charges.

Cette structure s'avère donc être un excellent candidat pour la réalisation de transistor de puissance fonctionnant en gamme de fréquence millimétrique [6].

Les travaux menés ces dernières années sur ce composant ont consisté à améliorer la montée en fréquence et la puissance de sortie délivrable par le composant.

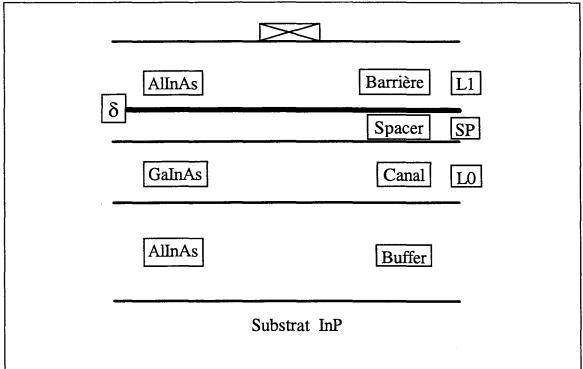

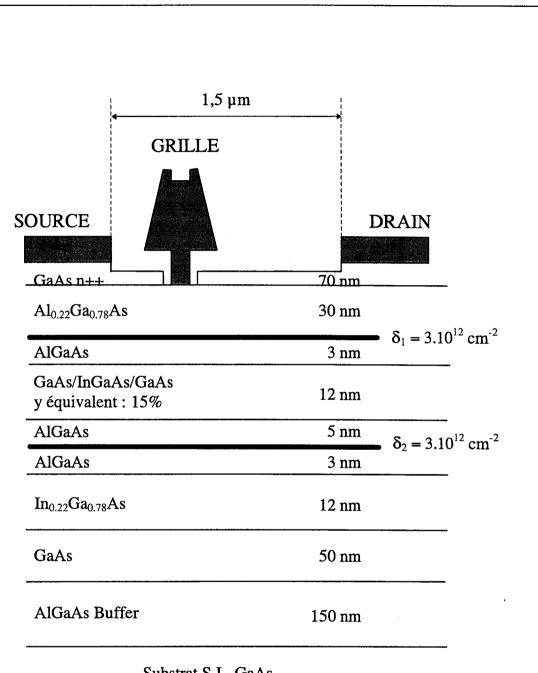

Pour le premier point, la solution immédiate a consisté à diminuer la longueur de grille, mais comme dans le cas du MESFET, cette réduction s'accompagne d'une diminution de l'épaisseur de la couche active. Nous retrouvons alors les problèmes liés aux faibles épaisseurs fortement dopées. Est apparue alors, grâce aux progrès apportés par les techniques d'épitaxie, la solution du plan de dopage. Celle-ci consiste à introduire les donneurs (Si) en très forte concentration sur une épaisseur très faible (de 20 à 30 Å). Ainsi, des densités de dopage de 5.10<sup>12</sup> cm<sup>-2</sup> peuvent être facilement obtenus pour un plan et permettent la croissance du matériau GaAlAs non dopé pour former l'hétérojonction (espaceur) et une séparation entre la couche donneurs et la grille (la couche barrière). Cette dernière couche étant non dopée, elle permet d'obtenir des tensions de claquage plus élevées.

En conséquence, la diminution de la longueur de grille n'entraîne que la diminution de la couche barrière nid.

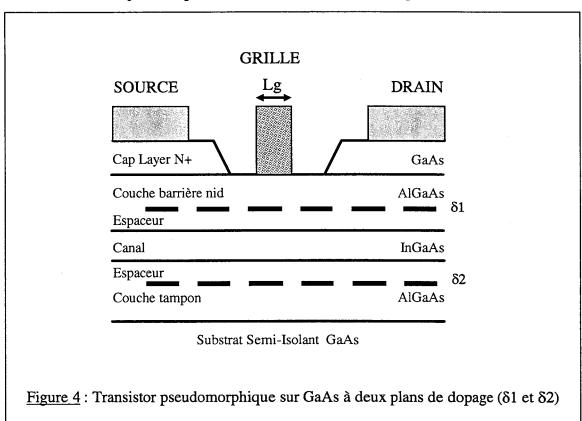

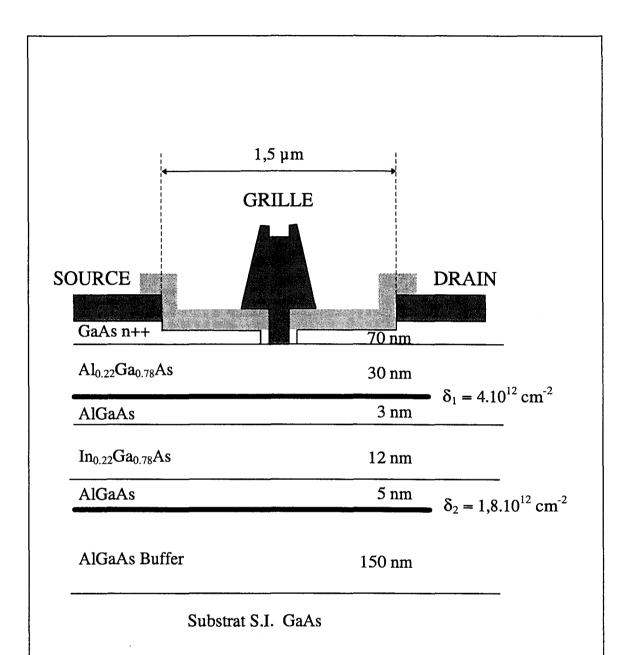

En ce qui concerne l'augmentation de la puissance de sortie, celle-ci passe par l'augmentation du courant délivré par le composant. Si au delà d'une certaine valeur, l'augmentation du nombre de donneur ne suffit plus à accroître la densité de charge dans le puits, l'adjonction d'un deuxième plan sous le canal le permet facilement. Si de plus, le deuxième plan est inséré dans une couche de GaAlAs, la différence de bande de conduction de cette deuxième hétérojonction permettra un excellent transfert (fig.4).

Ce type de structure représente alors le composant privilégié dans la filière GaAs pour les applications de puissance puisqu'il permet d'obtenir des densités de charge transférées pouvant atteindre 4.10<sup>12</sup> cm<sup>-2</sup> et un courant de 1 A par millimètre de développement de grille.

Il est d'ailleurs à noter que ce type de composant a déjà permis d'obtenir une puissance de sortie de 960 mW/mm à 60 GHz avec une longueur de grille de 0,15µm [7].

Enfin, une structure utilisant les mêmes critères, mais un peu plus complexe est la structure à plusieurs canaux. Ceux-ci possédant chacun leur propre plan de dopage [8]. Ces structures envisagées au départ pour la réalisation de multiplieur de fréquences ou de mélangeur [9] en utilisant les propriétés de non linéarité [10] se sont montrées très intéressantes pour les applications de puissance aux fréquences de 30 GHz. En effet, compte tenu de l'épaisseur de la couche active (incluant 2 ou plusieurs canaux) la longueur de grille raisonnable est de 0,25µm.

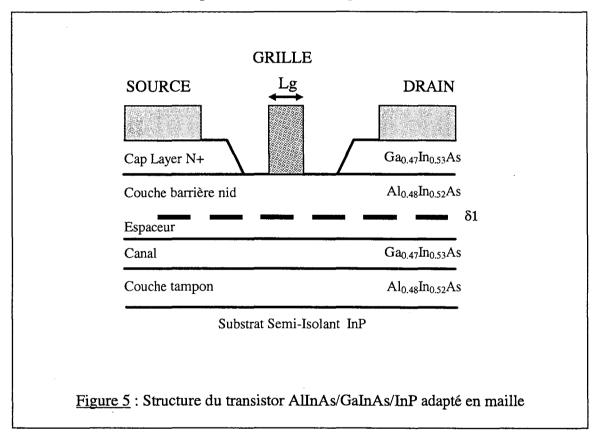

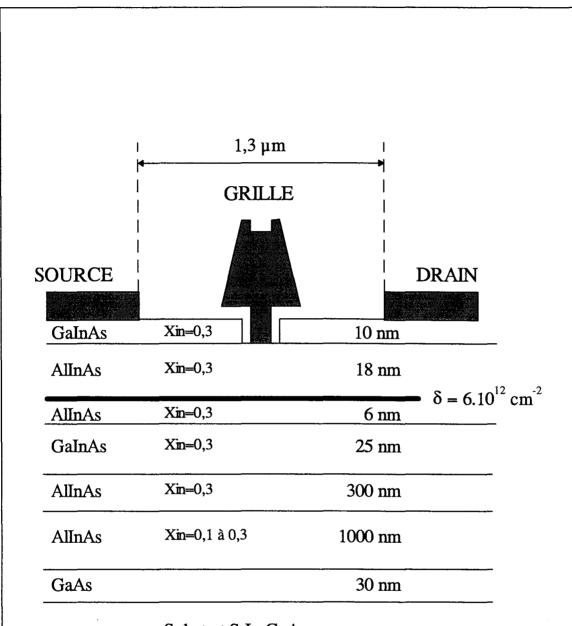

#### 1.3.3 Le HEMT adapté en maille AlInAs/GaInAs/InP (LM-HEMT)

Une filière autre que celle du GaAs est apparue ces dernières années. Celle-ci avait pour objectif de tirer profit des caractéristiques du matériau pour former une différence de bande de conduction et une mobilité dans le puits plus élevées que sur GaAs. Ainsi, avec les progrès des techniques d'épitaxie, la croissance de matériau sur Phosphure d'Indium (InP) a donné naissance à cette nouvelle filière.

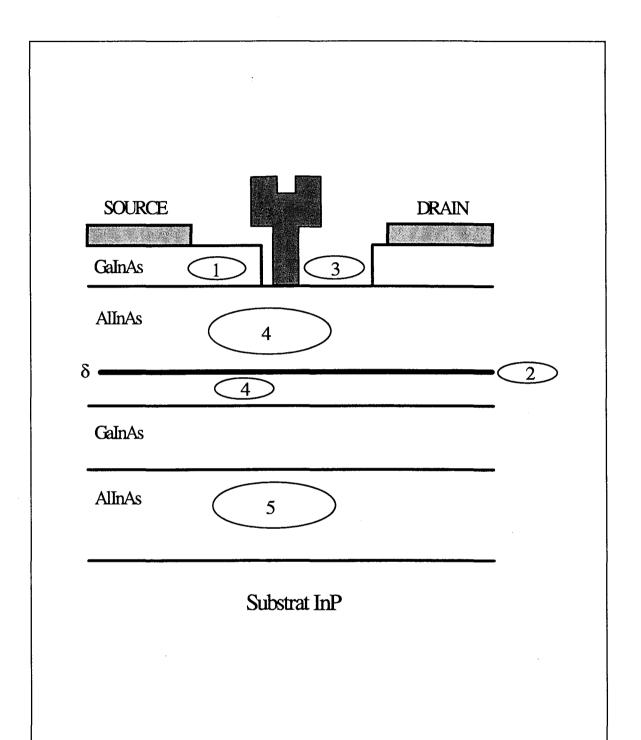

La structure du transistor LM-HEMT sur InP (Lattice Matched -HEMT) représentée sur la figure 5 est analogue à celle du transistor pseudomorphique sur GaAs. Le canal restant en GaInAs, celui-ci doit avoir un taux d'indium égal à 53 % afin de respecter l'accord de maille avec l'InP. Aussi, pour assurer une discontinuité de bande de conduction la plus élevée possible, il faut utiliser le matériau AlInAs pour réaliser les hétérojonctions. Le matériau doit alors avoir, si l'on veut comme précédemment être adapté sur l'InP, un taux d'indium de 52%.

L'avantage de cette structure est d'avoir une différence de bande de conduction égale à 0,5 eV pour l'hétérojonction AlInAs/GaInAs. Elle permet également d'obtenir des mobilités électroniques de l'ordre de 10000 cm²/V.s à température ambiante. La combinaison de ces deux améliorations conduit directement à une augmentation de la densité de courant (comparée au structures sur GaAs).

Si à cela, nous ajoutons une conductivité thermique supérieure à celle du GaAs (0,68 Wcm<sup>-1</sup>K<sup>-1</sup> contre 0,44 Wcm<sup>-1</sup>K<sup>-1</sup> à 300 K), il est aisé de comprendre l'intérêt porté par ce type de structures pour les applications à des fréquences supérieures à 60 GHz.

Il faut toutefois garder à l'esprit que le matériau GaInAs possède une bande interdite faible, ce qui a pour conséquence de laisser apparaître les phénomènes de claquage dès les faibles tensions de drain.

Néanmoins, des études ont été récemment entreprises et nous nous proposons dans la suite de ce travail de décrire plus précisément nos travaux à ce sujet.

A ce jour, une densité de puissance de 340 mW/mm au dB de compression et 400 mW/mm à la saturation a été obtenu à 60 GHz [11].

De la même façon que sur GaAs, il est possible d'imaginer une filière pseudomorphique sur InP, donc à canal contraint.

L'intérêt réside dans le fait d'accroître encore la mobilité électronique dans le puits en augmentant le pourcentage d'Indium du GaInAs du canal. Le contre effet de cette modification est la diminution de la bande interdite du GaInAs et par conséquent, une apparition des phénomènes de claquage plus précoce que dans le cas du LM-HEMT InP.

Il semble donc que ce type de composant ne réponde pas aux exigences demandées par les applications de puissance. Néanmoins, il semble être un composant de choix pour les applications faible bruit puisqu'en effet, le record de bruit à 94 GHz a été obtenu avec ce type de transistor à 80% d'indium [12].

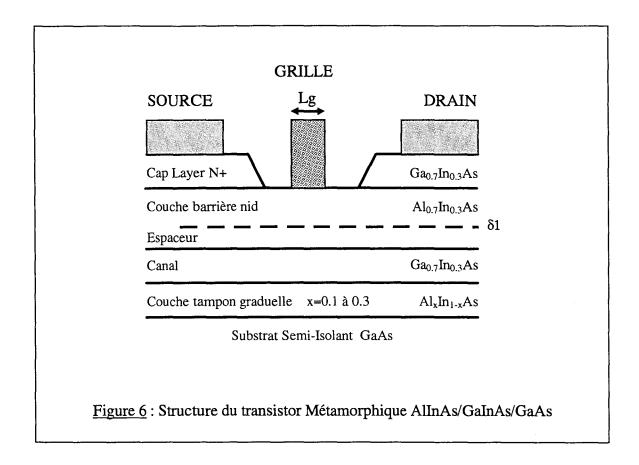

#### 1.3.4 Le HEMT Métamorphique sur GaAs (MM-HEMT)

Issu de la filière InP, la volonté d'accroître au maximum la différence de bande de conduction a conduit à l'hétérojonction Al<sub>0.7</sub>In<sub>0.3</sub>As/Ga<sub>0.7</sub>In<sub>0.3</sub>As.

Ces matériaux, si ils sont adaptés en maille entre eux, présentent un très grand désaccord de maille par rapport au matériau GaAs du substrat. Il est alors nécessaire d'utiliser un buffer d'adaptation afin de confiner les dislocations dans celui-ci pour croître les matériaux de la couche active sans contrainte. En effet, les défauts de matériau ont pour conséquence de dégrader les propriétés électriques des semi-conducteurs.

Pour ce faire, il faut sur le substrat, croître une couche tampon graduelle, c'est à dire en faisant varier la composition du matériau en débutant de façon a être adapté en maille avec le substrat, puis continuer en modifiant progressivement les taux de composition jusqu'à l'obtention de l'adaptation avec les matériaux de la couche active (fig. 6).

On obtient alors pour ce composant (fig.6) une différence de bande de conduction de 0,7 eV avec des densités de charge dans le puits de  $4.10^{12}$  cm<sup>-2</sup>, permettant une amélioration de 30% par rapport aux résultats de la filière InP.

Le matériau GaInAs du canal possède alors une bande interdite de 1 eV et par conséquent laisse présager une très bonne tenue en tension des composants.

Les récents travaux sur ces composants ont permis d'obtenir de très bons résultats : 750 mA/mm, 160 GHz de Ft pour une longueur de grille de 0,15µm [13] qui, il faut le penser, seront améliorés à l'avenir tant ce composant semble être un bon candidat pour les applications de puissance dans les gammes millimétriques. Actuellement, les travaux réalisés dans cette filière consistent essentiellement en des études matériaux afin de résoudre les problèmes de croissance concernant les couches tampon et le choix des compositions des alliages des matériaux de la couche active.

#### 2. Les autres filières

#### 2.1 Le MISFET

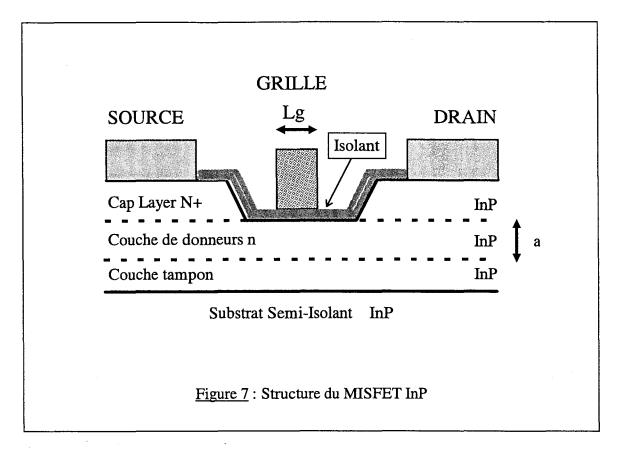

Dans le but de réduire de façon drastique l'effet néfaste du claquage, il a semblé intéressant d'utiliser le principe de la grille isolée des MOSFET.

#### 2.1.1 Le MISFET InP

Le MISFET InP (fig.7) a été le premier transistor étudié dans la famille MISFET. La réalisation de contacts Métal-Isolant-Semi-conducteur (MIS) sur InP est très rapidement apparu comme une solution prometteuse.

Cependant, si le contact MIS est très facile à réaliser, il n'en reste pas moins le problème de l'instabilité de l'isolant, conduisant rapidement aux dégradations des performances des transistors en fonctionnement. De plus, la présence d'isolant a pour effet de diminuer l'efficacité de la commande de grille sur le semi-conducteur et par conséquent, rend très difficile l'obtention de transconductances élevées.

Malgré ces problèmes, des résultats intéressants ont été obtenus. Le plus marquant est l'obtention d' une puissance de sortie de 1,8 W/mm à 30 GHz [14].

#### 2.1.2 Le DMT GaAs et InP

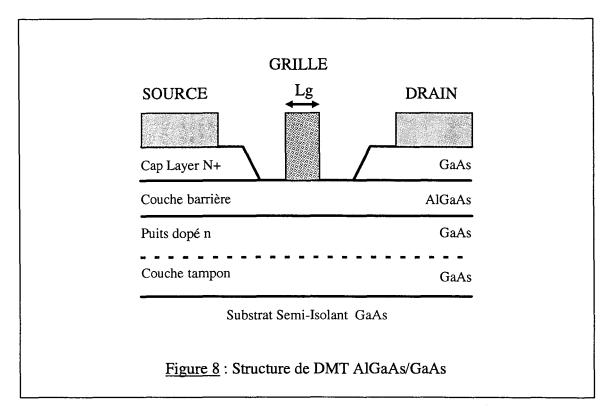

Outre les problèmes posés par la dégradation rapide de la couche isolant, le MISFET souffre d'une montée en fréquence insuffisante. Pour remédier aux deux problèmes, est né le DMT (Doped Channel MIS-Like Field Effect Transistor). Celui-ci consiste en une couche très dopée constituée par le canal et une couche isolante semi-conductrice nid (fig.8). Ces deux critères permettent d'obtenir des courants élevés et de supporter des tensions relativement importantes. Notons que pour la montée en fréquence, le progrès le plus remarquable a été effectué en croissance, car c'est avec des structures de faibles épaisseurs et à très forts dopages que les meilleurs résultats de puissance ont été obtenus.

Parmi la multitude de variantes de ce type de structure, nous ne présenterons que les plus classiques. Le DMT AlGaAs/GaAs a permis d'obtenir une puissance de sortie de 840 mW/mm et 7 dB de gain à 10 GHz [15] avec une technologie de grille de 0,6µm, la tension de claquage étant de 20 Volts.

Comme dans le cas du HEMT, le remplacement du GaAs du canal par de l'InGaAs a permis d'améliorer les performances du composant. Outre la montée en fréquence, c'est également une augmentation spectaculaire du courant de drain qui a été observée. Il en a résulté les meilleurs performances obtenues pour toute la famille des DMT, à savoir une puissance de sortie de 760 mW/mm à 60 GHz avec un gain de 3,6 dB [16].

Enfin, la dernière variante du transistor DMT qui nous paraît la plus intéressante, est celle issue de la filière InP. Afin de bénéficier des propriétés de transport dans le canal, celuici est remplacé par de l'InP et la couche semi-isolante est remplacée par de l'AlInAs en accord de maille sur l'InP. Ce type de structure a permis d'obtenir un gain petit signal de 11,5 dB à 10 GHz pour une technologie de grille de 1,25µm [17].

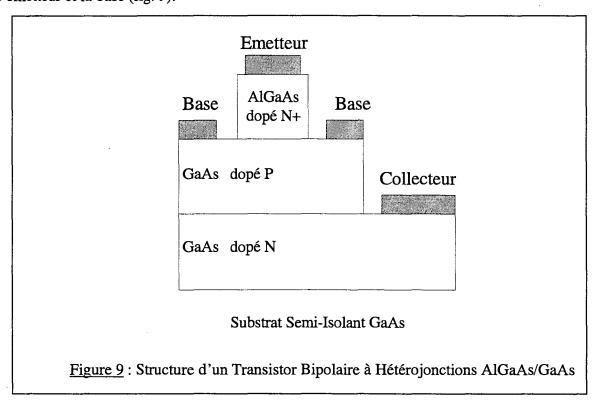

#### 2.2 Le Transistor Bipolaire à Hétérojonctions (TBH)

Jusqu'ici, nous n'avons présenté que le TEC et ses variantes. Aussi, il semble intéressant de se pencher sur son concurrent direct : le Transistor Bipolaire à Hétérojonctions (TBH). Issu de la technologie bipolaire utilisée très couramment sur silicium, le TBH se différencie par l'utilisation de différents matériaux afin de réaliser l'hétérojonction entre l'émetteur et la base (fig. 9).

Bénéficiant d'une vitesse plus élevée, les électrons injectés dans la base voient leurs temps de transit dans cette région considérablement réduits. Ceci permet alors une montée en fréquence du composant face au transistor bipolaire à homojonctions.

Avec ce type de transistors, une densité de puissance de 3,1 W/mm a été obtenu à 10 GHz [18] associée à un gain en puissance de 5,8 dB et un rendement en puissance ajoutée de 30 %. Des travaux ont montré des niveaux de puissance supérieurs à ceux du MESFET GaAs [19].

Bien que ce composant semble être un concurrent sérieux du HEMT, il faut se rendre à l'évidence des problèmes posés par la difficulté à travailler au delà de 10 GHz. De plus, sa faible impédance d'entrée le rend difficile à adapter. Enfin, la valeur très élevée de sa résistance thermique empêche la dissipation de chaleur de façon optimale et gène son aptitude à fonctionner à fort courant, puisqu'apparaît rapidement un phénomène de second claquage (l'effet 'crunch').

#### 2.3 Les nouveaux matériaux

Enfin, si dans les paragraphes relatifs aux HEMTs nous avons détaillé les principaux matériaux utilisés, il n'en reste pas moins deux nouveaux sur lesquels un bon nombre de travaux semble se porter actuellement et laisse présager des résultats intéressants compte tenu de leur caractéristiques intrinsèques.

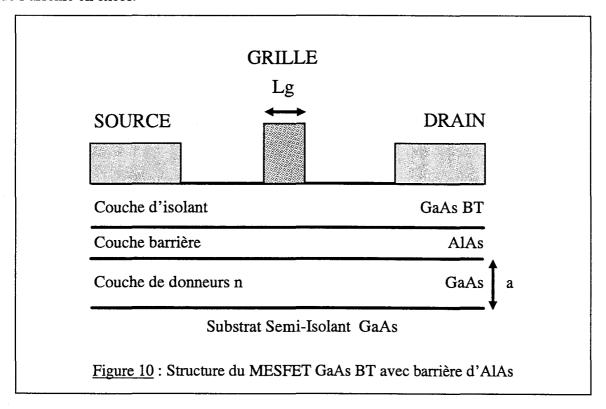

#### 2.3.1 Le MISFET GaAs Basse Température (BT)

Afin de s'affranchir des problèmes d'instabilité, le GaAs Basse Température (BT) a été récemment utilisé comme isolant et passivant. Alors que le GaAs semi-conducteur usuel est épitaxié au environ de 600°C, la GaAs BT est épitaxié à 200°C permettant l'incorporation de l'arsenic en excès.

Lorsqu'il est recuit, le matériau possède alors toutes les qualités d'un isolant, à savoir une résistance proche de  $10^6 \Omega$ .mm et une densité de piège de l'ordre de  $10^{19}$  cm<sup>-3</sup>.

La structure du transistor (fig. 10) consiste alors en une zone active de GaAs et une couche de GaAs BT servant d'isolant pour la grille. Notons qu'une fine couche (barrière) d'AlAs est déposée entre les deux matériaux afin d'empêcher la diffusion de l'arsenic en excès du matériau BT vers la couche active lors d'un éventuel recuit.

Ce composant a permis d'atteindre un produit courant-tension de sortie de 3,5 W/mm en continu [20] ou encore 820 mW/mm à 4 GHz [21] pour des tensions de claquage supérieures à 40 Volts [22].

Si cette filière ne laisse espérer pour l'instant aucun résultat satisfaisant en gamme millimétrique, l'idée de réaliser des structures HEMTs BT alliant la montée en fréquence du HEMT et tenue en tension du BT pourra sans doute le permettre.

#### 2.3.2 Le Carbure de Silicium (SiC)

En réalité, il ne faudrait pas parler du SiC, mais des SiC. Selon l'arrangement des liaisons atomiques, le SiC peut adopter différentes structures cristallines. Ces dernières peuvent être de type cubique (pour le 3C-SiC) ou hexagonal (pour les 2H-SiC, 4H-SiC, 6H-SiC). Malgré ces différences, certaines propriétés intéressantes pour les applications de puissance hyperfréquence leurs sont communes. En effet, ces matériaux possèdent une large bande interdite d'environ 3 eV. Ils possèdent également une excellente conductivité thermique (environ 4,5 W.cm<sup>-1</sup>.K<sup>-1</sup>), une très bonne tenue en tension et une vitesse de saturation élevée (environ 2.10<sup>7</sup> cm.s<sup>-1</sup>). Tous ces paramètres font des SiC un candidat potentiel pour fonctionner à hautes températures [23].

Bien que des performances intéressantes aient été obtenues pour des MESFET [24], le manque de maturité de leurs technologies pénalise pour l'instant leurs potentialités [25].

#### 2.3.3 Le Nitrure de Gallium (GaN) et les alliages AlGaN et InGaN

Possédant des propriétés similaires à celle des SiC, le nitrure de Gallium se présente comme son concurrent direct.

Il est à noter que des transistors utilisant l'hétérojonction Al<sub>0.15</sub>Ga<sub>0.85</sub>N/GaN de 0,12μm de longueur de grille ont déjà été réalisés et ont permis d'obtenir une fréquence de coupure de gain en courant de 47 GHz et un courant de drain de 500 mA/mm [26]. Aussi, tout comme les SiC, lorsque la croissance du InGaN sera viable et lorsque la technologie GaN sera un peu plus avancée, il est à penser que cette filière donnera entière satisfaction.

## 3. La caractérisation des composants

#### 3.1 La caractérisation statique ou quasi-statique

La caractérisation statique ou quasi-statique constitue une première approche du composant. En effet, celle-ci se faisant à l'aide de signaux continus, aucune information sur

les potentialités en hyperfréquence du composant ne peuvent être tirées de ces caractérisations.

Cependant, une énorme quantité d'informations sera disponible sur les qualités du composant face au courant qu'il pourra délivrer et ses limites en tension.

#### 3.1.1 Présentation du matériel à disposition

#### 3.1.1.1 ICCAP

Pour réaliser les mesures statiques, notre laboratoire est équipé d'un système de mesures automatiques (ICCAP) composé de trois alimentations programmables et d'un logiciel de contrôle installé sur station. Un banc de tests sous pointes étant associé à ce système, nous effectuons les mesures directement sur wafer.

Aussi, grâce à son automatisation, le banc permet des mesures rapides et précises sans dégradation pour le composant sous test puisqu'il est possible de limiter les grandeurs mesurées. Par exemple, la mesure du courant de grille effectuée pour déterminer les tensions de claquage doit être limitée à 1 mA/mm de développement de grille. Cette mesure sur un composant de faible développement s'avérerait très délicate sans système automatisé.

#### 3.1.1.2 La mesure en impulsion

Nous disposons également dans notre laboratoire, d'un banc de mesures en impulsion [27]. Celui-ci effectue le même type de mesure que le système précèdent. Aussi, dans le cas des mesures statiques, les mesures se font par enchaînement et la mesure est relativement longue. Dans le cas des mesures pulsées, les mesures sont effectuées durant des temps très court (jusqu'à quelques dizaines de nanosecondes) et l'état de repos est observé entre deux mesures. Cette méthodologie permet de s'affranchir des effets thermiques que l'on rencontre souvent dans les transistors de puissance fonctionnant en continu. Notons que les impulsions délivrées aux bornes de la grille ou du drain ont une durée modulable. Ceci permet alors de s'adapter au transistor à étudier et d'observer les phénomènes transitoires ou de piégeage.

Si cet outil permet d'effectuer un très grand nombre de mesures (il est possible, comme dans le cas du système ICCAP de relever les tensions et les courants à chaque borne du transistor), il n'est pas équipé pour l'instant d'un système de pointes. Nous préférons donc utiliser le système statique pour notre étude.

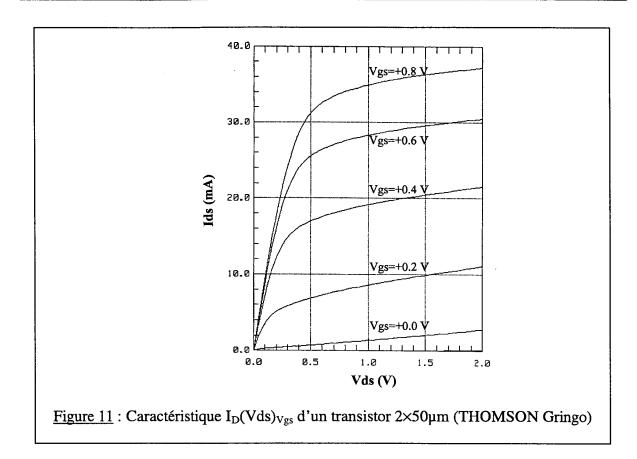

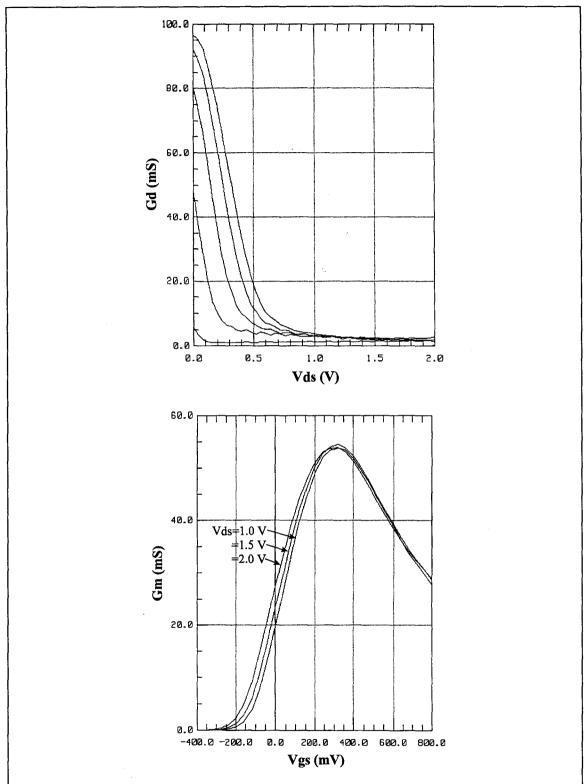

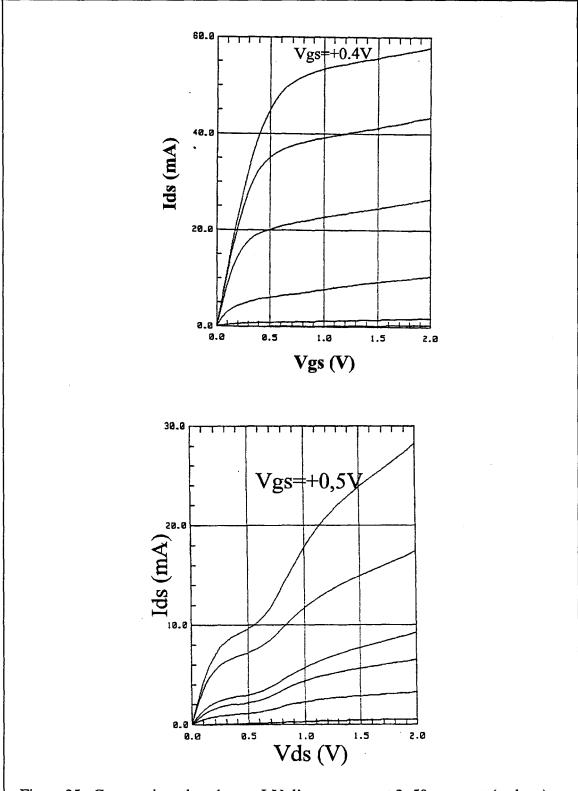

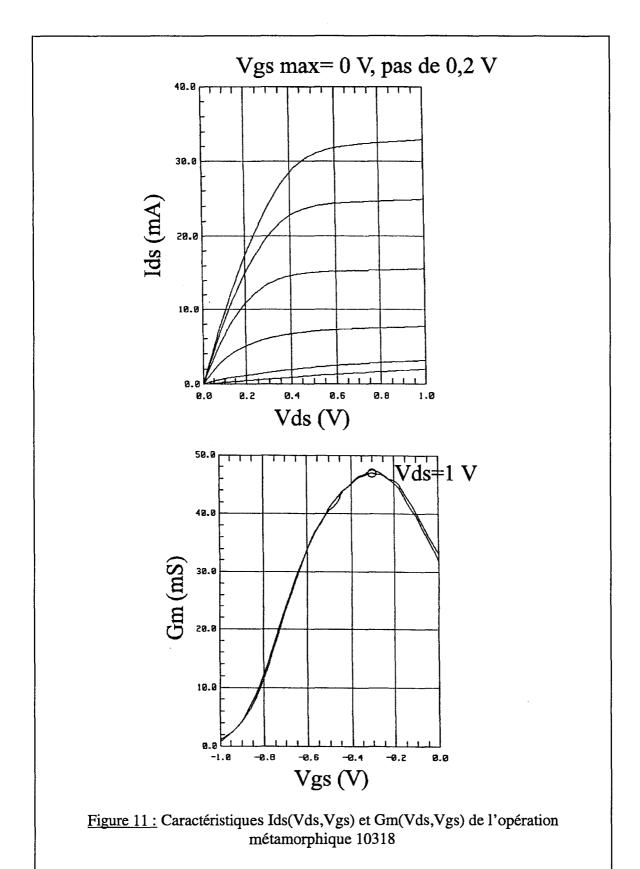

#### 3.1.2 La mesure des caractéristiques I-V

Il existe deux réseaux de caractéristiques. La première,  $I_D(Vds)_{Vgs}$  (fig. 11) consiste à relever le courant de drain ( $I_D$ ) en fonction de la tension Vds pour une ou plusieurs tensions Vgs. La seconde,  $I_D(Vgs)_{Vds}$  consiste à relever le courant en fonction de la tension Vgs pour une ou plusieurs tensions Vds.

La mesure de  $I_D(Vds)_{Vgs}$  est généralement la première effectuée sur le composant car elle permet de déterminer deux caractéristiques essentielles du composant; à savoir : le courant drain maximum et la tension de pincement.

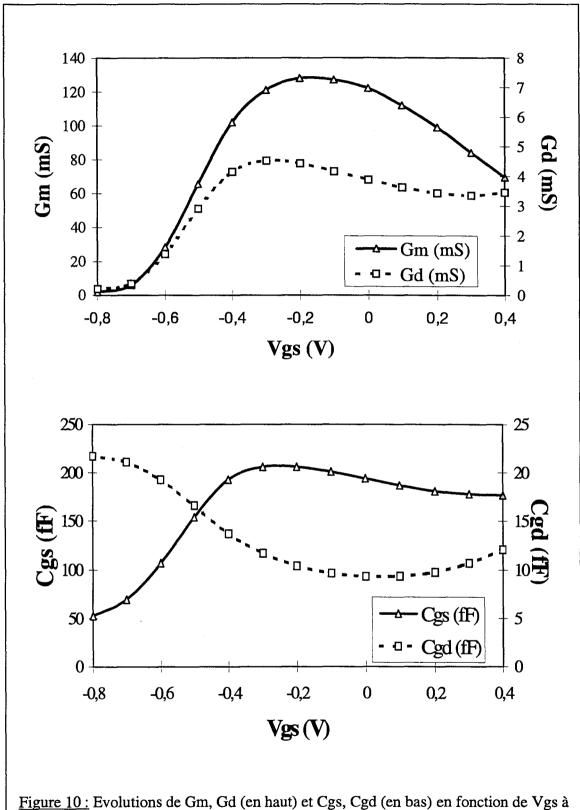

Du réseau de caractéristique Ids(Vds), il est possible d'extraire la conductance statique gd (fig. 12) défini par :

$$Gd = \left(\frac{\partial \quad ID}{\partial \quad Vds}\right)_{Vgs = cte}$$

Du réseau de caractéristique Ids(Vgs), la transconductance extrinsèque Gm (fig. 12) peut être extraite selon la formulation :

$$Gm = \begin{pmatrix} \frac{\partial & ID}{\partial & Vgs} \end{pmatrix}_{Vds = cte}$$

#### 3.1.3 Le courant de grille en configuration diode

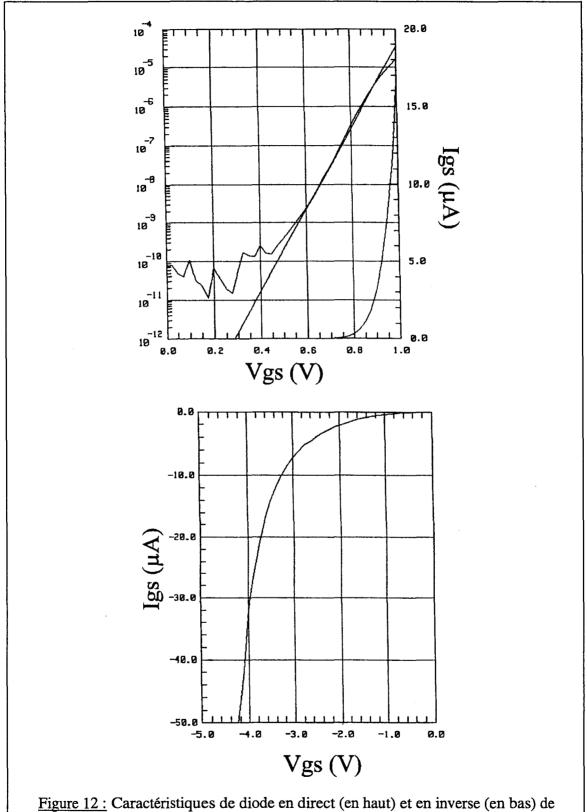

La mesure du courant de grille en configuration de diode permet de valider la qualité du contact Schottky.

Cette validation aussi bien technologique, qu'électrique doit se faire en direct (pour les courants >0) et en inverse (pour les courants <0). Notons que celle-ci se fait indépendamment pour le dipôle Grille-Source et pour le dipôle Grille-Drain.

Figure 12: Evolution de la conductance (en haut) et de la transconductance (en bas) en fonction de Vgs pour un composant 2×50μm (THOMSON Gringo)

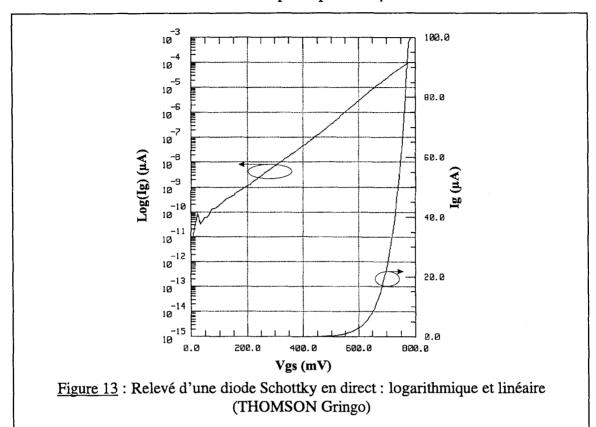

#### 3.1.3.1 La mesure de la diode Schottky en direct

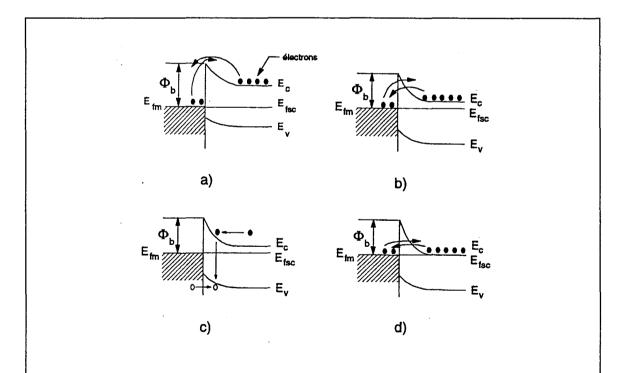

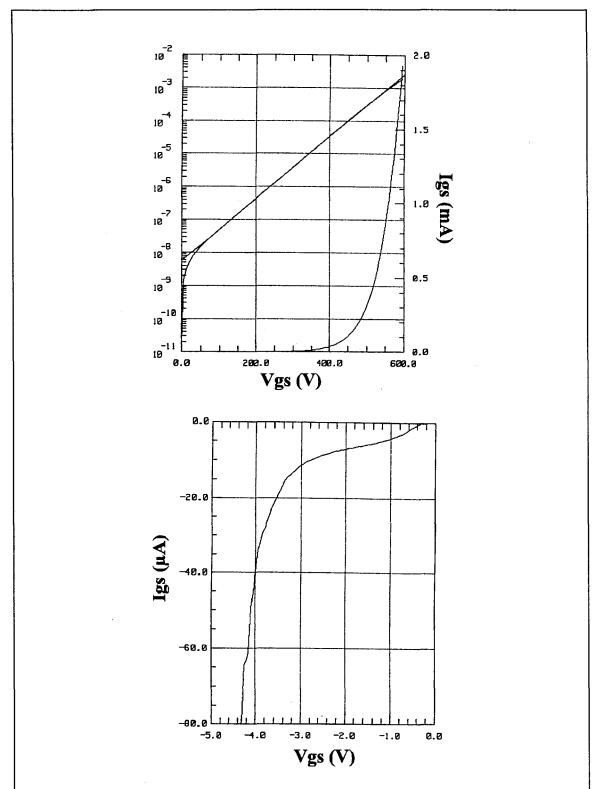

La caractéristique Igs(Vgs) (par exemple), lorsqu'elle est tracée sur échelle semi-log (fig. 13) permet de déterminer aisément le coefficient d'idéalité ' $\eta$ ' et la tension de built-in 'Vb'. La hauteur de barrière ' $\Phi$ b' est défini par le produit ' $\eta \times V$ b'.

Lorsque la diode est polarisée en direct, le courant Igs suit la loi :

$$Igs = A^* T^2 S \exp \left( \frac{-q \phi b}{\eta kT} \right) \left( \exp \left( \frac{qVgs}{\eta kT} \right) - 1 \right)$$

avec: A\*: constante de Richardson; A\*=8,4.10<sup>4</sup> A.m<sup>-2</sup>.K<sup>-1</sup>;

S: surface de la jonction de grille (Lg x développement total);

$\eta$ : coefficient d'idéalité (diode idéale :  $\eta = 1$ );

$\Phi_b$ : hauteur de barrière.

Ainsi, à partir de la pente de la caractéristique ln(Igs)=f(Vgs), le facteur d'idéalité se détermine d'après la relation :

$$\eta = \frac{q}{kT} \quad \frac{\Delta \quad Vgs}{\Delta \quad \ln(Igs)}$$

La hauteur de barrière de built-in se déduit alors de la relation :

$$\phi b = \frac{\eta \quad kT}{q} \quad \ln \left( \frac{AT^2S}{I_{SO}} \right)$$

(Iso étant déduit de la valeur de l'ordonnée à l'origine de la pente linéaire de ln(Igs)).

La valeur de  $\eta$  caractérise l'interface Metal-Semi-conducteurs. Plus cette valeur sera proche de 1, meilleur sera le contact, la valeur de 1 signifiant la diode idéale.

La valeur de la tension de built-in (Vb) correspond à la tension maximale (positive) que l'on pourra appliquer sur la grille sans créer de dégradations.

Aussi, pour les applications de puissance, plus cette tension sera élevée, plus le sera l'excursion du signal appliqué sur la grille.

Des travaux ont montré que le métal utilisé pour le contact Schottky n'a que peu d'influence sur la valeur de  $\phi$ b [28] pour les matériaux GaAs et GaAlAs. Cependant, pour une métallisation donnée, les diodes réalisées sur le matériau  $Al_xGa_{1-x}As$  montrent une forte dépendance de leurs caractéristiques en fonction du taux d'Aluminium du matériau semiconducteur [29].

Enfin, remarquons que le courant de grille ( $I_G$ ) développe une tension aux bornes de la résistance d'accès de source Rs en série avec la résistance  $\frac{Rc}{2}$  d'environ la moitié du canal ouvert.

En relevant la tension drain (laissé en l'air), nous déterminons la somme des résistances  $Rs + \frac{Rc}{2}$ .

De la même façon, en affectant le rôle de la source au drain, il est possible en relevant la tension sur la source (laissé en l'air) de déterminer la somme des résistances  $Rd + \frac{Rc}{2}$ .

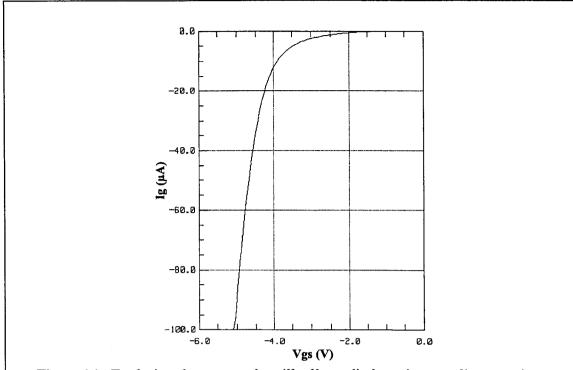

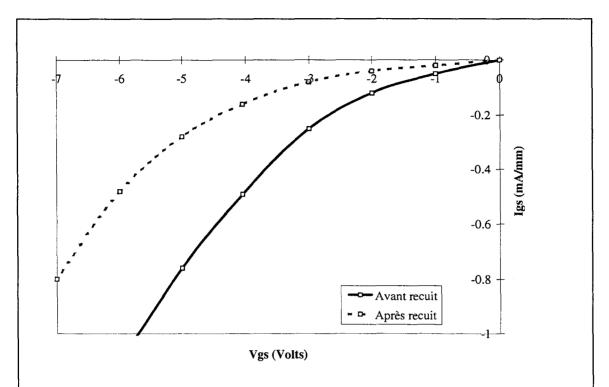

#### 3.1.3.2 La mesure de la diode Schottky en inverse

Cette mesure permet de déterminer la tension de claquage de la diode et en première approximation, celle du transistor. En effet, la tension de claquage se déduit de la caractéristique Igs(Vgs) en inverse (fig. 14) lorsque le courant atteint la valeur limite. Cette valeur limite a été choisie à 1 mA/mm de développement de grille, car elle correspond au courant admissible par la grille sans que n'apparaissent d'éventuelles dégradations des transistors.

L'origine de ce courant de grille dans les filières GaAs et InP est maintenant bien connue et reconnue comme résultant d'un effet tunnel pur ou tunnel assisté thermoioniquement à travers l'épaisseur de la couche barrière.

Figure 14: Evolution du courant de grille d'une diode en inverse d'un transistor 2×50μm (THOMSON Gringo)

#### 3.1.4 La caractéristique Rds(Vgs)

composant.

La résistance drain-source Rds en fonction de Vgs est donnée, dans le cas du MESFET, par l'expression :

$$Rds = Rs + Rd + Rc\frac{1}{1 - \sqrt{n}}$$

avec :

$$Rc = \frac{Lg}{q.\mu.Nd.a.Z}$$

= résistance du canal et  $n = \frac{-Vgs + Vb}{|Vt| + Vb}$

En pratique, le relevé de Rds en fonction de  $\frac{1}{1-\sqrt{n}}$  permet de déterminer Rc et Rs+Rd. Si à ces deux grandeurs, nous associons les valeurs précédemment obtenues lors de la mesure des diodes en direct, nous pouvons déterminer les résistances d'accès statique du

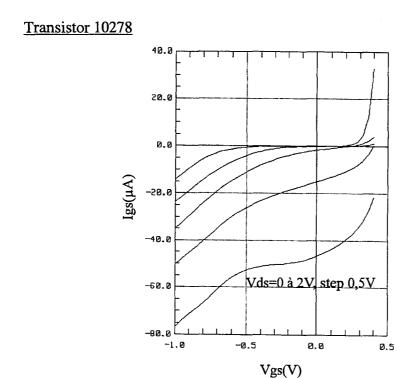

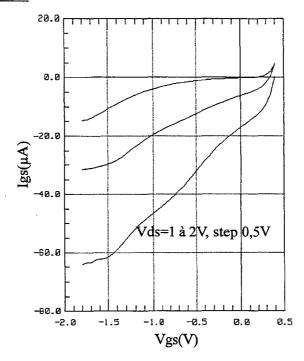

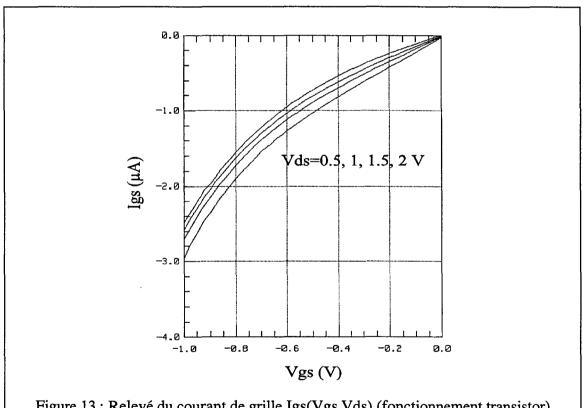

#### 3.1.5 La mesure du courant de grille en fonctionnement transistor

Si la mesure de la tension de claquage en configuration de diode permet de valider la technologie et de donner une première idée quand à la tenue en tension du composant, il est nécessaire d'aller plus loin si l'on désire approfondir l'étude du composant. Aussi, l'étude du courant de grille en mode de fonctionnement transistor permet cet approfondissement puisqu'elle indique les limites en tension dans les conditions d'utilisation du transistor.

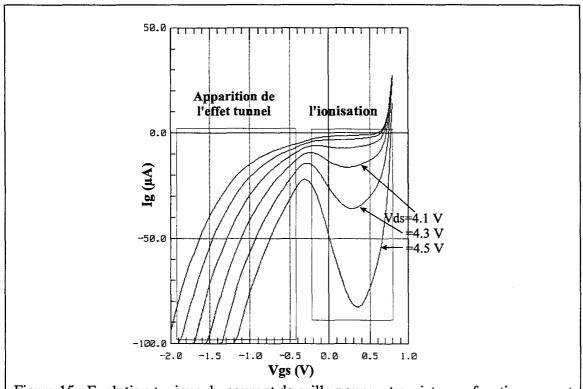

Cette mesure permettra alors la détermination des limites en tension du composant et d'analyser les phénomènes physiques en jeu dans le composant. De plus, elle permettra de déterminer le point de polarisation optimum pour la caractérisation de puissance, donc la classe de fonctionnement appropriée pour le transistor.

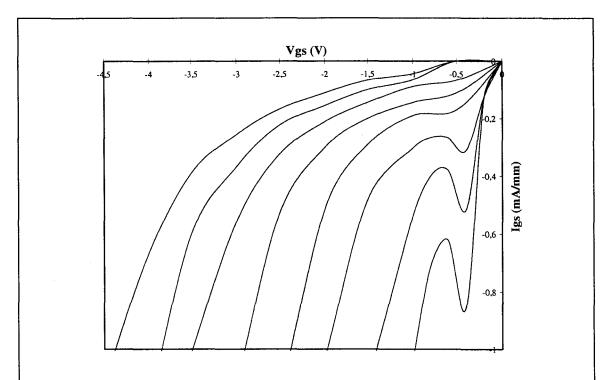

La mesure du courant de grille est réalisée lors du fonctionnement du transistor. Ainsi, le balayage en tension sur Vgs se fait de la tension de claquage en configuration diode jusqu'à l'ouverture complète du canal, et le balayage en Vds se fait de 0 Volt jusqu'à apparition de la limitation du courant de grille (1mA/mm de développement de grille). La figure 15 représente une évolution typique du courant de grille en fonctionnement transistor.

<u>Figure 15</u>: Evolution typique du courant de grille pour un transistor en fonctionnement (THOMSON Gringo)

Sur ce relevé, apparaissent deux zones. La première zone définit le canal ouvert ou apparaît le courant dû à l'ionisation dans le canal. La seconde zone définit la fermeture du canal ou apparaît alors l'effet tunnel [30].

#### 3.2 Caractérisation Basse Fréquence

Moins connue que la caractérisation statique, la caractérisation basse fréquence permet de valider la qualité de l'épitaxie sur laquelle sont réalisés les transistors. De cette façon, cette caractérisation permet d'aider à la mise au point des épitaxies et d'aider à la compréhension des éventuels problèmes rencontrés en caractérisation.

Ce type de caractérisation peut se faire par magnéto-résistance ou par mesure capacitive C(V).

#### 3.2.1 La mesure de mobilité par magnéto-résistance

La mesure au pont d'impédance de la résistance drain-source Rds (à 100 MHz) en fonction de Vgs sans et avec l'application d'un champ magnétique B, permet de déduire la mobilité moyenne des porteurs selon la formule :

$$\mu moy(Vgs) = \frac{1}{B} \sqrt{\frac{Rds(B)}{Rds(0)} - 1}$$

La mobilité moyenne caractérisant l'ensemble des électrons dans le canal.

Connaissant deux valeurs de Rds pour des tensions Vgs proches, il est alors possible de déterminer la mobilité différentielle µdiff(Vgs). Celle-ci caractérise la mobilité des porteurs sous la grille [31].

#### 3.2.2 La mesure C(V)

La quantité de charge libre Q(Vgs) sous la grille obéit (dans le cas du MESFET) à la loi de Shockley [32]:

$$Q(Vgs) = Q_0 \left(1 - \sqrt{\frac{-Vgs + Vb}{W_{00}}}\right)$$

avec:

$$Q_0 = q.Z.Lg.a.Nd$$

et  $W_{00} = Vp = \frac{q N_D a^2}{2\varepsilon}$

En pratique, la caractéristique de la capacité Cg en fonction de Vgs est mesurée à l'aide d'un pont de mesure d'impédance.

Par intégration, nous déterminons la quantité de charge sous la grille Q. L'évolution de Q en fonction de  $\sqrt{-Vgs+Vb}$  permet de déduire  $Q_0$  et  $W_{00}$ .

L'exploitation de la valeur de  $W_{00}$  dans la caractéristique Rds(Vgs) permet de déterminer correctement la valeur de (Rs+Rd).

#### 3.3 La Caractérisation hyperfréquence petit signal

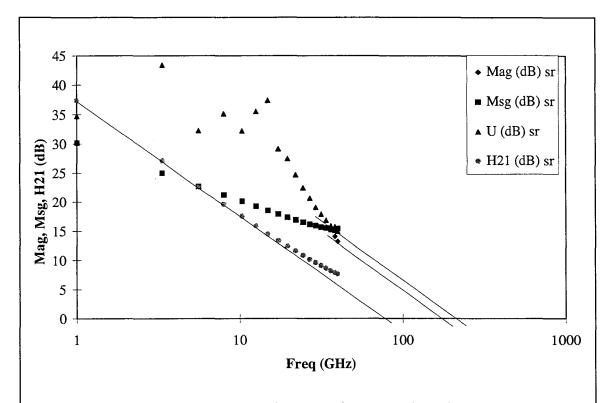

La mesure des paramètres Sij en régime petit signal permet de déterminer les performances fréquentielles du transistor. Il est également possible, à partir des paramètres Sij, de déterminer le schéma électrique équivalent du transistor. Notons cependant que si le matériel dont dispose le laboratoire permet des mesures jusqu'à 110 GHz, les analyseurs de réseau avec lesquels le schéma équivalent est déterminé sont limités à 40 ou 50 GHz. Par conséquent, la plage de fréquence à utiliser pour la détermination du schéma équivalent ne dépasse pas 40 ou 50 GHz.

#### 3.3.1 Les performances hyperfréquence

Les potentialités du composant se résument aux différents gains et à leurs fréquences de coupure respective.

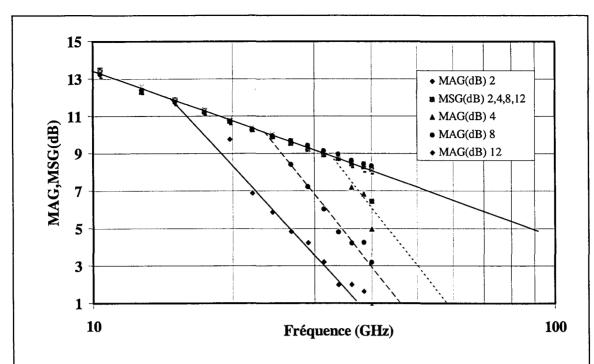

#### 3.3.1.1 Le gain maximum disponible MAG (Maximum Available Gain)

Le MAG correspond au maximum de transfert de puissance entre l'entrée et la sortie dans les conditions optimales d'adaptation en entrée et en sortie. Cette adaptation n'est réalisée simultanément que si le transistor est inconditionnellement stable.

Le MAG est défini par :

$$MAG = \frac{\left|S_{21}\right|}{\left|S_{12}\right|} \quad \left(k \pm \sqrt{k^2 - 1}\right)$$

avec k>1, k étant le coefficient de stabilité.

La fréquence de coupure du MAG: Fmag, est déterminée à partir de l'extrapolation de son évolution en fonction de la fréquence. Nous obtenons alors la fréquence maximale pour laquelle le transistor possède du gain en puissance.

#### 3.3.1.2 Le gain stable maximum MSG (Maximum Stable Gain)

Le MSG correspond au gain maximum du transistor lorsqu'il est conditionnellement stable. Il est utilisé (lorsque le MAG n'est pas défini) comme critère d'évaluation des possibilités d'amplification du transistor.

Il est défini par :

$$MSG = \frac{\left|S_{21}\right|}{\left|S_{12}\right|}$$

#### 3.3.1.3 Le gain unilatéral U : le gain de MASON

Le gain unilatéral est le gain à l'adaptation du transistor neutrodyné. Le paramètre S12 est dans ce cas, compensé par des circuits passifs sans pertes.

Le gain unilatéral est défini par :

$$U = \frac{1}{2} \frac{\left| S_{21} - S_{12} \right|^2}{k \left| S_{12} S_{21} \right| - \text{Re} \left| S_{12}^* S_{21} \right|}$$

Bien que ce gain ne présente aucun intérêt en caractérisation hyperfréquence, puisqu'il est purement hypothétique, il est utilisé pour déterminer par extrapolation de son évolution lorsqu'elle atteint -6 dB/octave, la fréquence Fmax : la fréquence maximale d'oscillation du transistor.

### 3.3.1.4 Le gain en courant de court-circuit : H<sub>21</sub><sup>2</sup>

Le gain en courant de court circuit extrinsèque est obtenu d'après la conversion des paramètres Sij en paramètres Hij selon la formulation :

$$\left|H_{21}\right|^{2} = \left|\frac{-2S_{21}}{(1-S_{11})(1+S_{22})+S_{12}S_{21}}\right|^{2}$$

L'extrapolation de ce gain avec une pente de -6 dB/octave lorsque celui-ci varie en fonction de la fréquence, permet de déterminer la fréquence de coupure du gain en courant de court-circuit : Ft.

Remarque: Ces gains et leurs fréquences de coupure respectives peuvent être également déterminés d'après les éléments du schéma équivalent petit signal. Ces formulations seront définies dans la partie traitant du schéma équivalent, mais leurs valeur est moins précise en raison des approximations nécessaires.

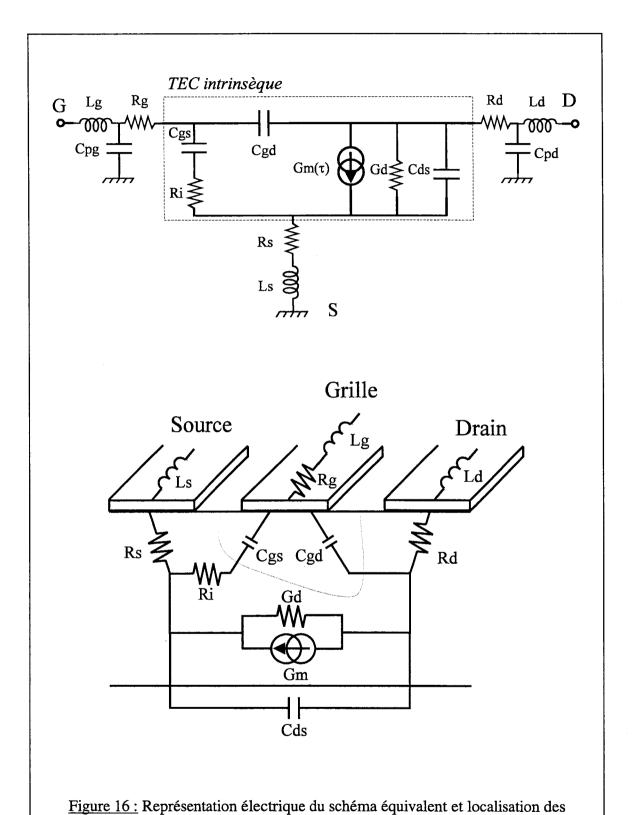

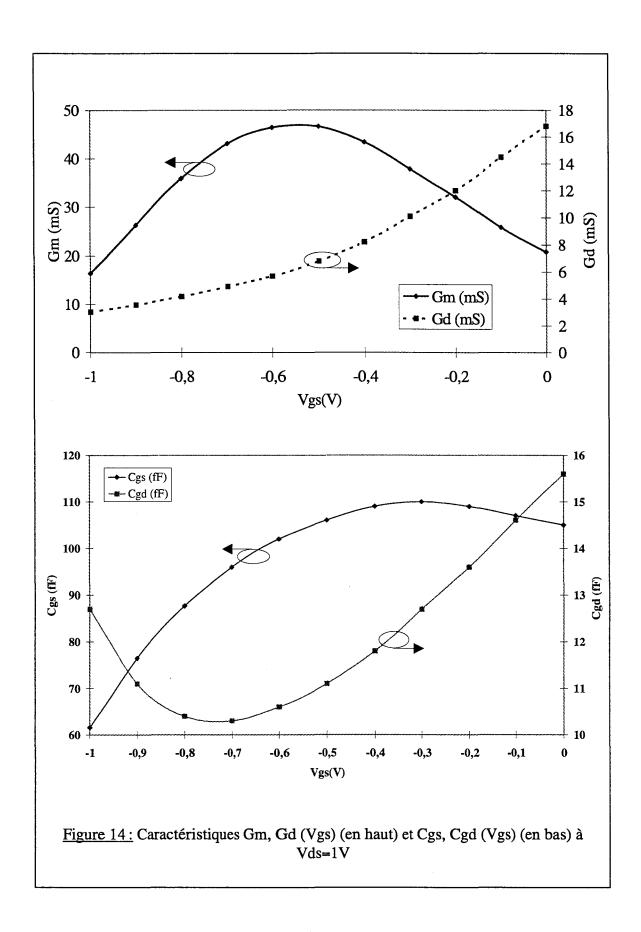

#### 3.3.2 Le schéma équivalent petit signal

La méthode utilisée au laboratoire que nous présentons dans cet ouvrage a été mise au point par G.DAMBRINE [33]. Pour déterminer le schéma équivalent du transistor (fig. 16), la méthode consiste, dans un premier temps à déterminer les éléments extrinsèques du composants et dans un deuxième temps, à déterminer les éléments intrinsèques. Enfin, à partir du schéma équivalent, il est possible de déterminer les performances du transistor.

#### 3.3.2.1 Détermination des éléments extrinsèques

#### 3.3.2.1.1 Détermination des éléments séries (R et L)

Pour déterminer les éléments d'accès série, il est nécessaire de court-circuiter en hyperfréquence, les accès du schéma intrinsèque. Pour cela, la réactance intrinsèque du transistor est court-circuitée par la mise en directe de la diode Schottky (résistance dynamique). Dans ce cas, Ig >0 et Vds=0V.

Cette configuration laisse apparaître les effets selfiques, et il est possible à partir des paramètres Sij de déterminer les inductances Ls, Lg et Ld et les résistances Rs, Rg et Rd.

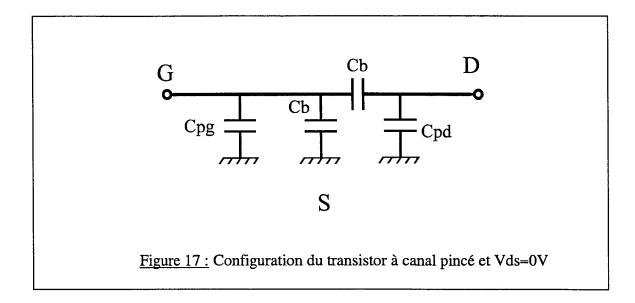

#### 3.3.2.1.2 Détermination des éléments parallèles (Capacité de plot)

Dans ce cas, il est nécessaire d'isoler les accès du schéma intrinsèque. Cette isolation se fait par désertion totale du canal en appliquant une tension sur la grille au delà du pincement (Vgs < Vt) et Vds=0V.

Le transistor se réduit alors à une association de capacités (fig. 17), la capacité Cb étant due à l'extension de la zone désertée dans le canal.

A l'aide des paramètres Yij, il est possible de déduire les capacités de plots de grille et de drain Cpg et Cpd.

principaux éléments dans la structure du FET

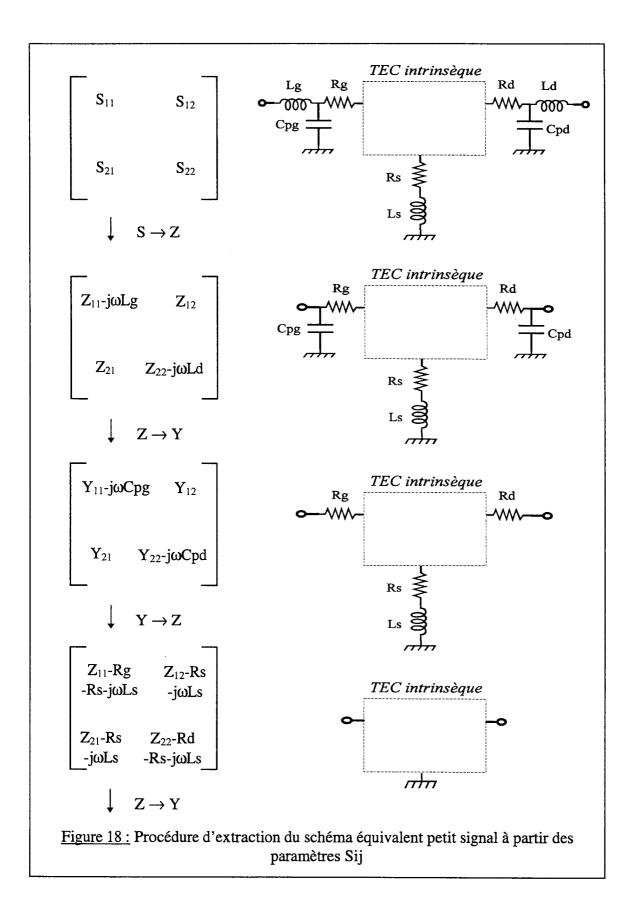

#### 3.3.2.2 Détermination des éléments intrinsèques

La détermination des éléments d'accès est la première étape de détermination du schéma équivalent. Ensuite, les éléments intrinsèques sont déterminés à partir de la matrice admittance Yij intrinsèque extraite de la matrice de répartition Sij selon la méthode décrite par la figure 18.

On calcule alors les valeurs des éléments en effectuant des moyennes sur la fréquence :

$$Gm = \sqrt{\left[1 + \left(\frac{\text{Re}(Y11) + \text{Re}(Y12)}{\text{Im}(Y11) + \text{Im}(Y12)}\right)^{2}\right] \left[\left(\text{Re}(Y21) - \text{Re}(Y12)\right)^{2} + \left(\text{Im}(Y21) - \text{Im}(Y12)\right)^{2}\right]}$$

$$Gd = \text{Re}(Y22) + \text{Re}(Y12)$$

$$Cgs = \frac{\left[\text{Im}(Y11) + \text{Im}(Y12)\right] \left[1 + \left(\frac{\text{Re}(Y11) + \text{Re}(Y12)}{\text{Im}(Y11) + \text{Im}(Y12)}\right)^{2}\right]}{\omega}$$

$$Cgd = \frac{-\text{Im}(Y12)\left[1 + \left(\frac{\text{Re}(Y12)}{\text{Im}(Y12)}\right)^{2}\right]}{\omega}$$

$$Cds = \frac{\text{Im}(Y22) + \text{Im}(Y12)}{\omega}$$

$$Rgd = \frac{\text{Re}(Y12)}{\text{Im}(Y12) \cdot Ced \cdot \omega}$$

$$Ri = \frac{\text{Re}(Y11) + \text{Re}(Y12)}{\left[\text{Im}(Y11) + \text{Im}(Y12)\right] \quad Cgs \cdot \omega}$$

$$\tau = Arc \tan \left[\frac{\Delta - Ri \cdot Cgs \cdot \omega}{1 + \Delta \cdot Ri \cdot Cgs \cdot \omega}\right] \cdot \frac{1}{\omega} \quad \text{avec} \quad \Delta = \text{Im}(Y21) \text{Im}(Y12) \left[1 + \left(RiCgs\omega\right)^{2}\right]$$

#### 3.3.3 Performances des transistors a partir du schéma équivalent

L'obtention du schéma équivalent permet de déduire les critères de qualité des composants. Ces critères sont liés aux fréquences maximales d'utilisation et sont définis comme suit :

La fréquence de coupure intrinsèque du gain en courant : Fc

$$Fc = \frac{Gm}{2\pi \cdot Cgs}$$

La fréquence de coupure du gain en puissance disponible : Fmag

$$Fmag = \frac{Fc}{\left[4Gd(Rd + \frac{\omega_c Ls}{2}) + 2\omega_c Cgd(Rs + Rg + \omega_c Ls)\right]^{1/2}}$$

La fréquence maximale d'oscillation: Fmax

$$F \max = \frac{Fc}{2[RoGd + \omega_c RgCgd]^{1/2}}$$

avec Ro=Rs+Rg+Ri

Notons que d'autres critères de performances peuvent être directement obtenus à partir de la valeurs des éléments du schéma équivalent :

Le gain en courant de court-circuit  $H_{21}^2$  intrinsèque [34] dont l'expression simplifiée s'écrit :

$$\left|H_{21}\right|_{\text{int rin}}^{2} = \frac{Gm^{2}}{\left(Cgs + Cgd\right)^{2} \quad \omega^{2}}$$

Le gain maximum disponible MAG

L'expression complète du MAG en fonction des éléments du schéma équivalent du transistor [35] est complexe. Cependant, il est possible de la simplifier lorsque le coefficient de stabilité k dépasse 2. Nous obtenons alors l'expression :

$$MAGapproch\acute{e} = \left(\frac{Ft}{F}\right) \quad \frac{1}{4 \cdot gd \cdot (Rs + Rg + \pi \cdot Ft \cdot Ls) + 4 \cdot \pi \cdot Ft \cdot Cgd(Rs + 2Rg + 2 \cdot \pi \cdot Ft \cdot Ls)}$$

avec

$$Ft = \frac{Gm}{2 \cdot \pi \cdot (Cgs + Cgd)}$$

#### 3.4 La caractérisation de puissance ou grand signal

Le fonctionnement des transistors en régime d'amplification de puissance est très différent du fonctionnement en régime petit signal. En effet, si en régime petit signal, le transistor peut être considéré comme un circuit linéaire, en régime grand signal (ou d'amplification de puissance), cette considération est exclue.

Aussi, après avoir été caractérisé en régime statique et en régime hyperfréquence petit signal, le maître mot, quant aux potentialités du transistor à fournir de la puissance, sera donné par la caractérisation grand signal.

Pour ce faire, un banc de mesure spécifique est nécessaire, et permet de déterminer trois grandeurs caractéristiques principales pour les transistors de puissance, à savoir : la puissance de sortie Ps, le gain en puissance Gp et le rendement en puissance ajoutée efficace  $\eta_{PAE}$ .

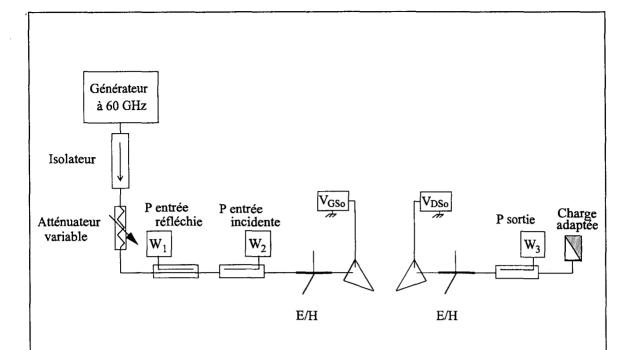

#### 3.4.1 Description du banc de mesure

Notre laboratoire est pourvu d'un banc de mesure Load-Pull très performant [36][37], permettant la caractérisation en puissance dans la bande de fréquence de 26 à 40 GHz. Aussi, pour les applications visant un fonctionnement à 60 GHz, il nous a semblé utile de réaliser (en doublon avec les mesures 26-40 GHz) la caractérisation des transistors à la fréquence de fonctionnement souhaitée. Les mesures sur banc Load-Pull destinées à des caractérisations spécifiques seront utilisées afin d'analyser plus finement le comportement des transistors en fonctionnement grand signal [38].

Le banc de mesure à 60 GHz utilisé pour nos mesures est représenté à la figure 19. Il est constitué des éléments suivants :

- une source microonde à 60 GHz (constitué par un oscillateur Gunn) qui fournit le signal RF d'entrée au composant.

- un isolateur protégeant la source des ondes réfléchies par le transistor.

- un atténuateur permettant le réglage du niveau de signal RF incident.

- des appareils de mesure de puissance connectés au banc par coupleur permettant la mesure des puissances incidentes, réfléchies et transmises au composant.

- deux adaptateurs de type plan E/H permettant la correction des coefficients de réflexion des impédances présentées en entrée et en sortie afin d'assurer les adaptations.

- un système de pointes cascade permettant l'accès direct au transistor.

La caractérisation directe sous pointes donne alors l'avantage de rester en guide d'onde rectangulaire sur l'intégralité du banc, évitant ainsi les transitions guide/coaxial gênantes. De plus elle écarte les problèmes liés aux boîtiers puisqu'une étape d'étalonnage complexe est alors nécessaire afin de déterminer les pertes du boîtier et les pertes apportées par les bondings. En effet, cette étape d'étalonnage est nécessaire pour la mesure de chaque transistor

en boîtier, alors que la mesure sous pointes ne nécessite que d'une procédure d'étalonnage pour toute la campagne de mesure.

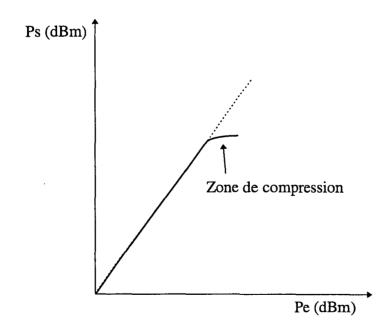

La méthode consiste alors à ajuster les adaptateurs plan E/H d'entrée et de sortie pour obtenir le minimum de puissance réfléchie et le maximum de puissance à la sortie du composant pour une puissance d'entrée donnée. Connaissant les pertes causées par les différents éléments du banc, il est possible de corriger partiellement les valeurs obtenues pour les puissance d'entrée Pe et de sortie Ps aux bornes du transistor. En appliquant cette méthode pour différents niveaux de signal en entrée, nous en déduisons la réponse du transistor en puissance Ps(Pe) dont un exemple est donné figure 20. Nous pouvons alors déduire de cette caractéristique, la puissance de sortie maximale délivrable par le transistor.

## 3.4.2 Définition des gains

Dans une chaîne d'amplification (comme celle du banc de caractérisation de puissance), différentes puissances peuvent être définies aussi bien en entrée qu'en sortie. En entrée par exemple, nous pouvons considérer la puissance disponible à la source (Pavs) ou la puissance absorbée par le transistor en entrée (Pe). Il en résulte plusieurs définitions de gains. Dans ce travail, nous nous limiterons à ceux qui nous ont paru être les plus essentiels pour définir les potentialités des transistors en puissance.

# 3.4.2.1 Le gain en puissance GP

Ce premier concept consiste à comparer la puissance absorbée Ps dans la charge vue par la sortie du transistor à la puissance absorbée par l'entrée Pe du transistor. Le gain en puissance est alors définit par le rapport entre Ps et Pe :

$$Gp = \frac{Ps}{Pe}$$

#### 3.4.2.2 Le gain en transducteur G<sub>T</sub>

Le gain en transducteur fait intervenir par définition, le rapport de la puissance absorbée Ps dans la charge vue par le transistor sur la puissance disponible de la source Pavs. Ce gain est définit par :

$$Gt = \frac{Ps}{Pavs}$$

La puissance disponible de source est la puissance maximale que celle-ci peut délivrer. Pour avoir le maximum de gain en transducteur, il faut assurer de manière optimale le transfert de puissance de la source à l'entrée du transistor et de la sortie du transistor à la charge.

Notons que l'adaptation simultanée entrée-sortie nécessite la stabilité inconditionnelle du transistor (k>1). Nous obtenons dans ce cas le gain en transducteur maximum  $G_{Tmax}$ . Celuici correspondant alors au gain maximum disponible, le MAG.

Figure 19 : Synoptique du banc de mesure de puissance à 60 GHz

<u>Figure 20</u>: Représentation schématique de la caractéristique Ps(Pe) montrant le phénomène de compression

Notons également, que ces définitions sont basées sur l'hypothèse d'un fonctionnement en petit signal, et par conséquent ces gains caractérisent le fonctionnement linéaire du transistor. Ces gains restent constants tant que le niveau de puissance reste suffisamment faible. Au delà d'un certain niveau, les mécanismes de non linéarité se mettent à intervenir progressivement et entraînent l'apparition du phénomène de compression du gain (fig. 20).

Dans ces conditions de non linéarité, les paramètres Sij petit signal ne correspondent pas à la réalité car la génération de composantes aux fréquences harmoniques fait tomber l'hypothèse de base du formalisme des paramètres Sij, à savoir le fonctionnement à la fréquence fondamentale.

#### 3.4.3 Définitions des rendements

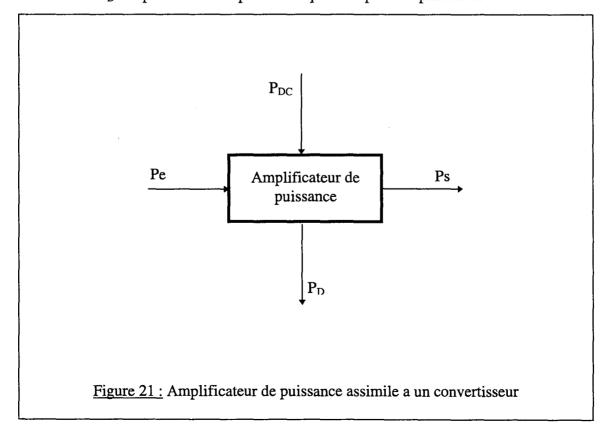

Comme dans le cas des définitions de gains, la multitude des puissances intervenant dans la chaîne d'amplification donne naissance à de multiples définitions de gains. Aussi, avant de procéder à l'inventaire de ces définitions, il apparaît judicieux de définir les puissances intervenant directement sur le transistor. L'amplificateur de puissance peut être considéré comme un convertisseur de puissance [39] (fig. 21).

Ce convertisseur fait alors intervenir quatre puissance :

- P<sub>E</sub>: la puissance hyperfréquence absorbée par l'entrée

- P<sub>DC</sub>: la puissance continue d'alimentation de l'amplificateur

- P<sub>S</sub>: la puissance hyperfréquence absorbée par la charge

- P<sub>D</sub>: la puissance dissipée thermiquement par l'amplificateur

Ce système étant à équilibré énergétiquement, le bilan de puissance s'écrit :

$$P_E + P_{DC} = P_S + P_D$$

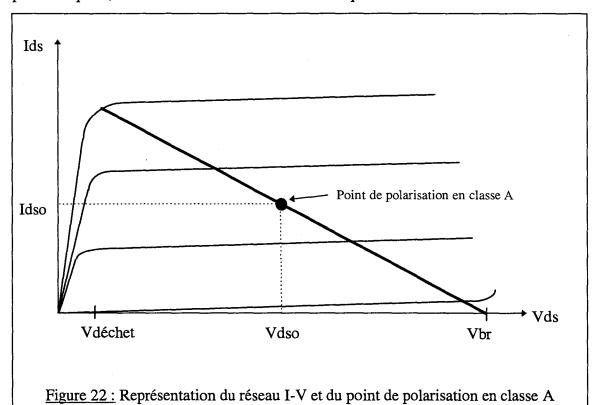

Notons que les puissances  $P_E$  et  $P_S$  sont déterminées à l'aide d'appareils de mesure et que la puissance fournie par la source d'alimentation continue est définie (fig. 22) par :

$$P_{DC} = I_{DO} \cdot V_{DSO}$$

où  $I_{D0}$  et  $V_{DS0}$  sont les courants et tensions continues de celle-ci.

A l'aide du bilan de puissance, la détermination de la puissance dissipée thermiquement P<sub>D</sub> devient implicite.

## 3.4.3.1 Le rendement drain $\eta_D$

Ce rendement est défini comme étant le rapport entre la puissance  $P_S$  fournie à la charge vue par le transistor et la puissance continue d'alimentation  $P_{DC}$ :

$$\eta_D = \frac{P_S}{P_{DC}}$$

Dans le cas de l'amplification en classe A, le point de polarisation est placé au milieu de la droite de charge (fig. 22). La puissance de sortie maximale du transistor  $P_{smax}$  est alors :

$$P_{S \max} = \frac{1}{2} I_{DSO} \cdot (V_{DSO} - V_{d\acute{e}chet})$$

et par conséquent, le rendement drain maximum théorique est de 50%.

#### 3.4.3.2 Le rendement en puissance ajoutée η<sub>PAE</sub>

Le rendement en puissance ajoutée est défini par :

$$\eta_{PAE} = \frac{P_S - P_E}{P_{DC}} = 1 - \frac{P_D}{P_{DC}}$$

Avec la définition du gain  $G_p = \frac{P_s}{P_E}$ , nous obtenons :

$$\eta_{PAE} = \eta_D \left( 1 - \frac{1}{G_P} \right)$$

Cette équation met en évidence la nécessité de l'utilisation optimale du réseau  $I_D(Vds)$  afin d'obtenir les performances maximales en rendement. Elle montre également l'influence de la puissance dissipée sur ce même rendement.

# 4. Etat de l'art des TECs pour la puissance

Les progrès technologiques réalisés au cours des années 85 à 95 ont permis d'obtenir les meilleurs résultats mondiaux que nous connaissons actuellement. Aujourd'hui, ces résultats semblent figés étant donné les difficultés rencontrées pour repousser encore plus loin les limitations des composants. Mais, il est fort à parier que le développement des nouvelles filières donnera naissance à de nouveaux records.

#### 4.1 Densité de puissance de sortie des TECs discrets

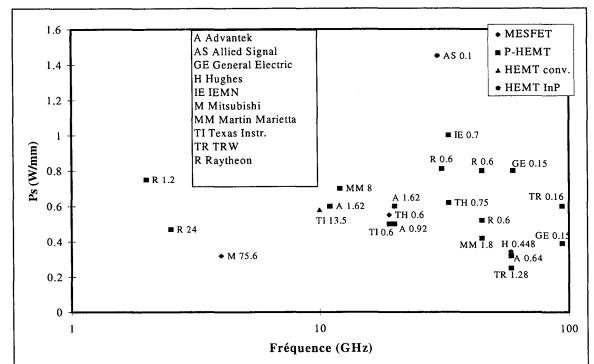

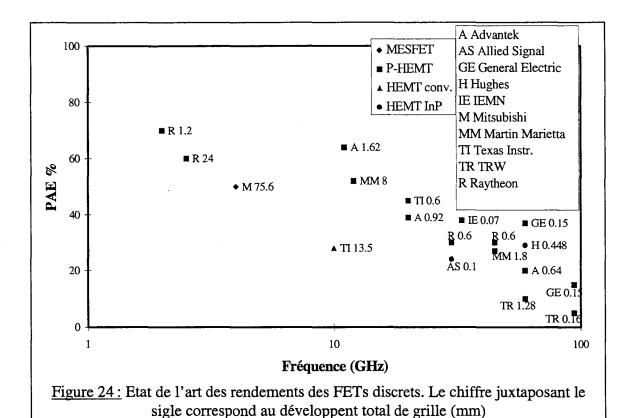

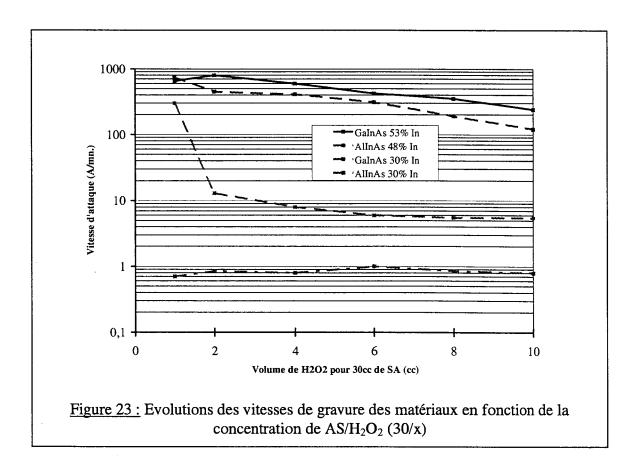

L'état de l'art des densités de puissance des FETs discrets en fonction de la fréquence est représentée figure 23.

De ce tableau, peuvent être tirés trois enseignements. Le premier est que la puissance de sortie des transistors semble être limitée à 1 W/mm de développement de grille (si l'on excepte le résultat de 1,45 W/mm obtenu par Allied Signal [40] qui n'a jamais été reproduit). Le deuxième enseignement tiré est qu'à partir de 40 GHz, la puissance de sortie (jusque là égale à 1 W/mm) diminue progressivement pour atteindre 0,5 W/mm à 100 GHz.

Enfin, le tableau confirme ce qui avait été énoncé dans la première partie de ce chapitre, à savoir que le MESFET a été relégué au second plan (même si pour des considérations économiques, il reste le favori des industriels) compte tenu des résultats obtenus par les PM-HEMT. Comme le montre l'état de l'art, ceux-ci supplantent toutes les autres structures de TEC et ceci quelle que soit la fréquence.

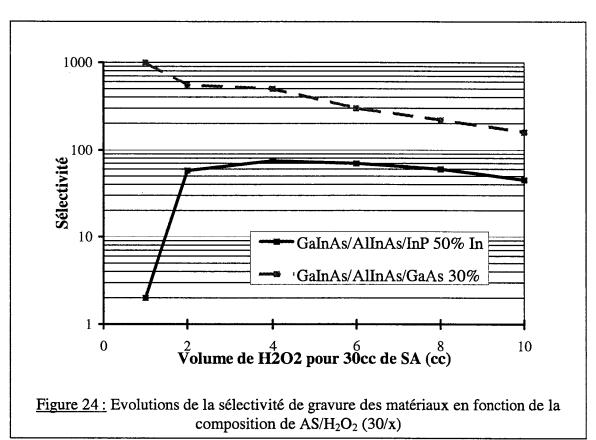

#### 4.2 Rendement en puissance ajoutée des TECs discrets

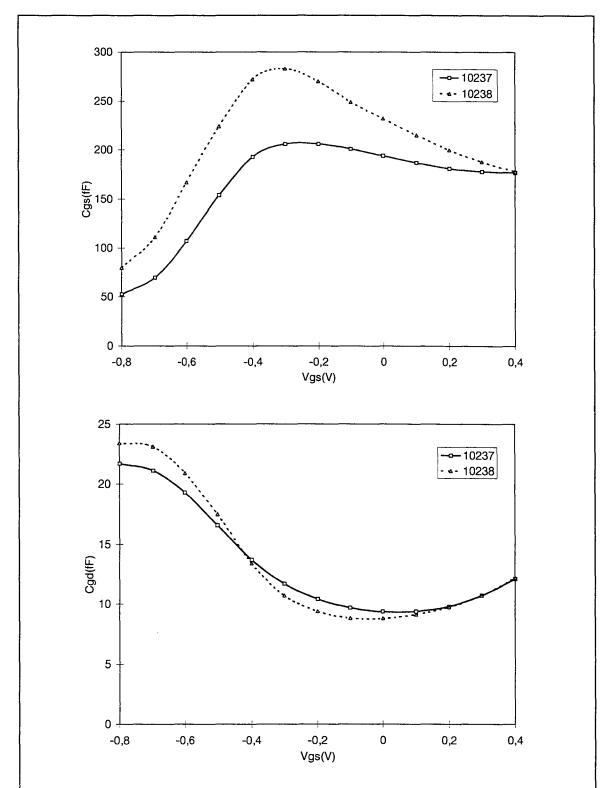

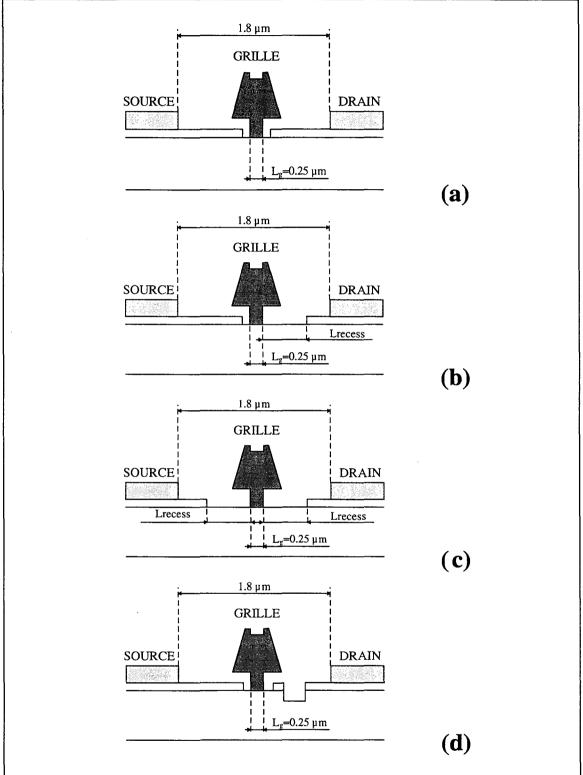

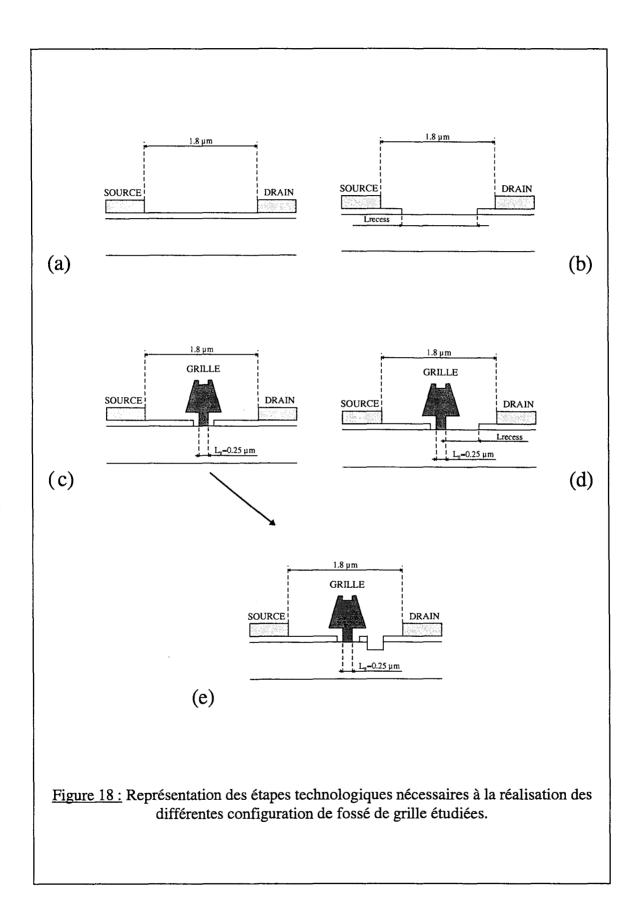

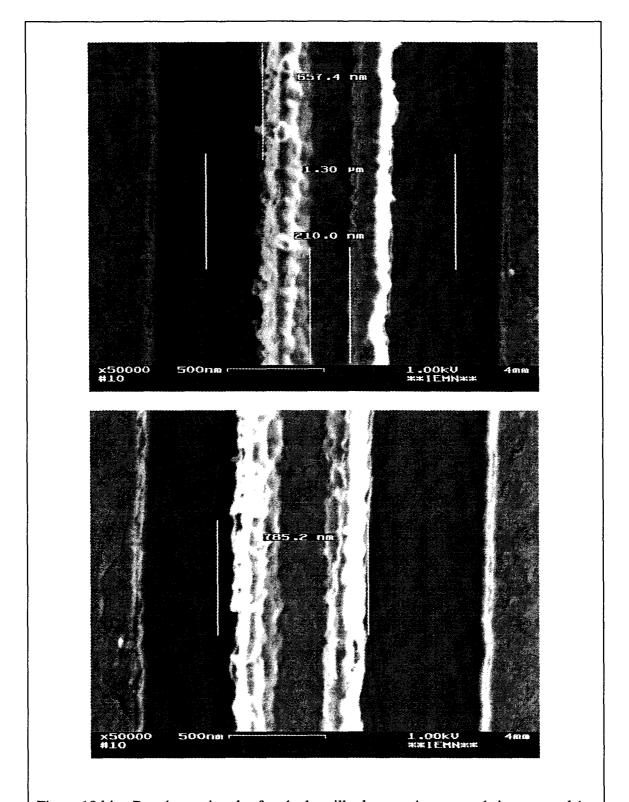

En ce qui concerne l'état de l'art du rendement en puissance ajoutée (représenté fig. 24), nous pouvons observer qu'il est possible d'obtenir des valeurs supérieures à 50% jusqu'à 20 GHz. Le rendement diminue alors en fonction de la fréquence pour obtenir difficilement 15% à 94 GHz.