( he lo 000 635

N° d'ordre: 2506

50376 1999 253

## **THESE**

#### Présentée à

# L'UNIVERSITE DES SCIENCES ET TECHNOLOGIQUES DE LILLE

#### Pour obtenir le titre de

#### **DOCTEUR DE L'UNIVERSITE**

**Discipline: ELECTRONIQUE**

#### Par

# Stéphane PIOTROWICZ

Intégration monolithique de HEMT's sur substrat InP en vue de l'amplification de puissance en bande V

### Soutenue le 26 Mars 1999 devant la commission d'examen

### Membres du jury:

MM

G. SALMER

Président

Y. CROSNIER

Directeur de thèse

B. BONTE

Co-directeur de thèse

J.M. DUMAS

Rapporteur

J.L. GAUTIER

Rapporteur

R. FAUQUEMBERGUE

Examinateur

R. LEVEVRE

Examinateur

M.SOULARD

Examinateur

A Rachel et Clémentine,

9 mes Parents.

## Remerciements

Ce travail a été réalisé à l'Université des Sciences et Technologies de Lille au sein de l'Institut d'Electronique et de Micro-électronique du Nord (I.E.M.N.) dirigé Monsieur par Professeur G.Salmer et dans le département Hyperfréquences et Semi-conducteurs (D.H.S.) dirigé par Monsieur le Professeur P.A.Rolland.

Je remercie Monsieur le Professeur P.A.Rolland, de me faire l'honneur de présider la commission d'examen.

La direction de ce travail a été assurée par Monsieur le Professeur Y.Crosnier, Messieurs B.Bonte et C.Gaquière à qui j'exprime ma plus vive reconnaissance. Leurs compétences scientifique et pédagogique ainsi que leur disponibilité m'ont permis de mener à bien ce travail.

Monsieur J.M.Dumas, Professeur à l'E.N.S.I.L. de Limoges et Monsieur J.L.Gautier Professeur à l'E.N.S.E.A. de Cergy Pontoise, me font l'honneur de juger ce travail et d'en être les rapporteurs. Je leur exprime toute ma reconnaissance.

Mes remerciements vont également à Messieurs :

R.Fauquembergue, Professeur à l'Université de Lille;

R.Lefevre, Ingénieur au CNET Bagneux;

M.Soulard, Docteur, responsable du Laboratoire d'Étude des M.M.I.C. à Alcatel Space Industries; représenté par le Docteur D.Langrez.

qui me font l'honneur de participer à la commission d'examen.

La partie expérimentale de cette étude a fait appel aux compétences de l'ensemble du personnel du D.H.S. Je tiens ici à leur exprimer toute ma gratitude et en particulier à :

Sylvie et Babette de la centrale de caractérisation,

Pascal Tilmant, Michel Muller et Marc François de la lithographie

Pierre,

V.D. et Christophe de la Micro-électronique,

Monsieur J.P.Dehorter du service de reprographie.

A Bertrand et Christophe, pris sur le fait lors d'une discussion sur le nombre de doigts de transistors ...

A Bertrand, plongé dans des lectures bibliographiques ...

A Didier, prenant son souffle avant de rédiger un rapport de contrat ...

A Momo, qui a toujours répondu présent alors que je n'étais plus à Lille ...

ps: tu peux t'installer sur mon ancien bureau ... si tu as besoin de place ...

A Stef, que j'écrase au bad ... quand il veut ...

A Eric, dont j'ai toujours plaisir à écouter les idéologies ...

Sans oublier Xavier, qui n'est malheureusement pas pris sur le fait ... en grande réflexion ...

# 7able des Matières

| INTRODUCTION GENERALE                                                                          | 5         |

|------------------------------------------------------------------------------------------------|-----------|

| CHAPITRE I :Caractéristiques des amplificateurs de puissance et état de l'art à 60 GHz         | 9         |

| I. Introduction                                                                                | 9         |

| II. LES PRINCIPALES GRANDEURS CARACTÉRISANT UN TRANSISTOR DE PUISSANCE MICROONDE               | 9         |

| II.1. Le concept des paramètres de répartition                                                 | 9         |

| II.2. Les concepts de gain                                                                     | 11        |

| II.2.1. Gain de transducteur                                                                   | 12        |

| II.2.2. Gain en puissance                                                                      | 14        |

| II.2.3. Gain en puissance disponible                                                           | 15        |

| II.3. Les critères d'évaluations des performances des transistors à effet de champ             | 15        |

| II.3.1. Critères d'évaluations en fonctionnement linéaire                                      | 16        |

| II.3.2. Les critères d'évaluations en fonctionnement non linéaire                              | 19        |

| III. STABILITÉ DES TRANSISTORS                                                                 | 24        |

| III.1. Les critères de stabilité                                                               | 24        |

| III.1.1. Le coefficient de stabilité K                                                         | 24        |

| III.1.2. Les cercles de stabilité                                                              | 26        |

| II.1.3. Validité d'utilisation du coefficient de stabilité                                     | 28        |

| III.2. Les méthodes de stabilisation                                                           | 29        |

| III.2.1. Stabilisation à la fréquence de travail                                               | 29        |

| III.2.2. Stabilisation hors de la bande de travail                                             | 30        |

| IV. MÉTHODES D'ADAPTATION DES TRANSISTORS                                                      | 31        |

| IV.1. Transformateur à ligne de compensation                                                   | 31        |

| IV.2. Adaptation par transformateur à tronçon de ligne                                         | 32        |

| V. ETAT DE L'ART DES TRANSISTORS ET AMPLIFICATEURS DE PUISSANCE À 60 GHZ ET 94 GHZ             | 33        |

| V.1. Les familles de transistors à effet de champ dédiées à l'amplification de puissance en go | ımmes     |

| de fréquences millimétriques                                                                   | 33        |

| V.1.1. Le HEMT conventionnel sur substrat GaAs                                                 | 34        |

| V.1.2. le HEMT pseudomorphique sur substrat GaAs                                               | 34        |

| V.1.3. Le HFET sur GaAs à canal dopé                                                           | 34        |

| V.1.3. Le HEMT conventionnel sur InP                                                           | 35        |

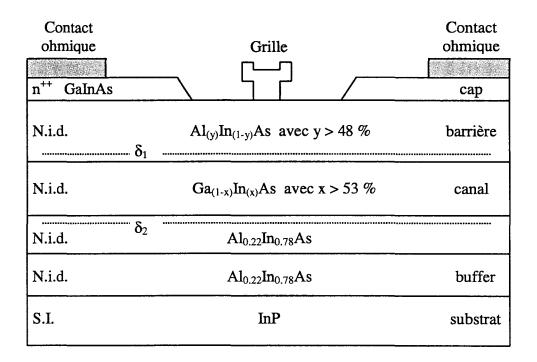

| V.1.4. Le HEMT pseudomorphique sur InP                                                         | 35        |

| V.1.5. Le HEMT métamorphique sur GaAs                                                          | 36        |

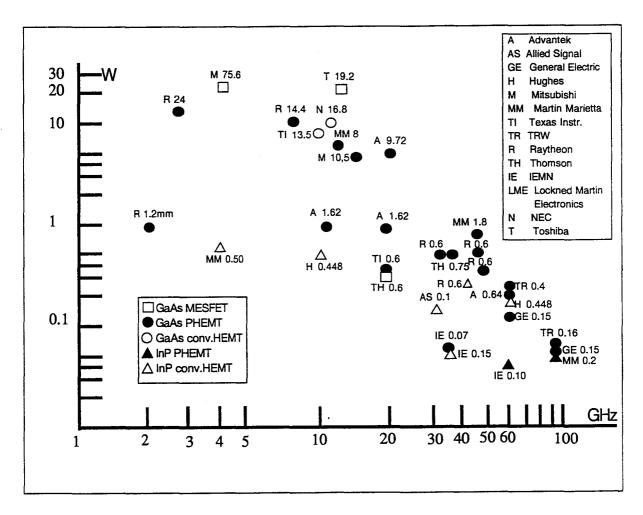

| V.2. Puissance absolue des FET discrets de 1 GHz à 94 GHz                                      | 37        |

| V.3. Puissance absolue des FET discrets                                                        | <i>38</i> |

| V.4. Rendement en puissance ajoutée des FET discrets                                       | <i>38</i> |

|--------------------------------------------------------------------------------------------|-----------|

| V.5. Densité de puissance des FET discrets                                                 | 39        |

| V.6. Puissance absolue des amplificateurs MMIC                                             | 40        |

| V.7. Conclusion et perspectives sur les filières de composants destinées à la puissance et | n bande   |

| millimétrique                                                                              | 41        |

| VI. CONCLUSION                                                                             | 43        |

| Bibliographie                                                                              | 44        |

| CHAPITRE II : Réalisation, mesures et définition des modèles d'éléments passifs            | £1        |

|                                                                                            |           |

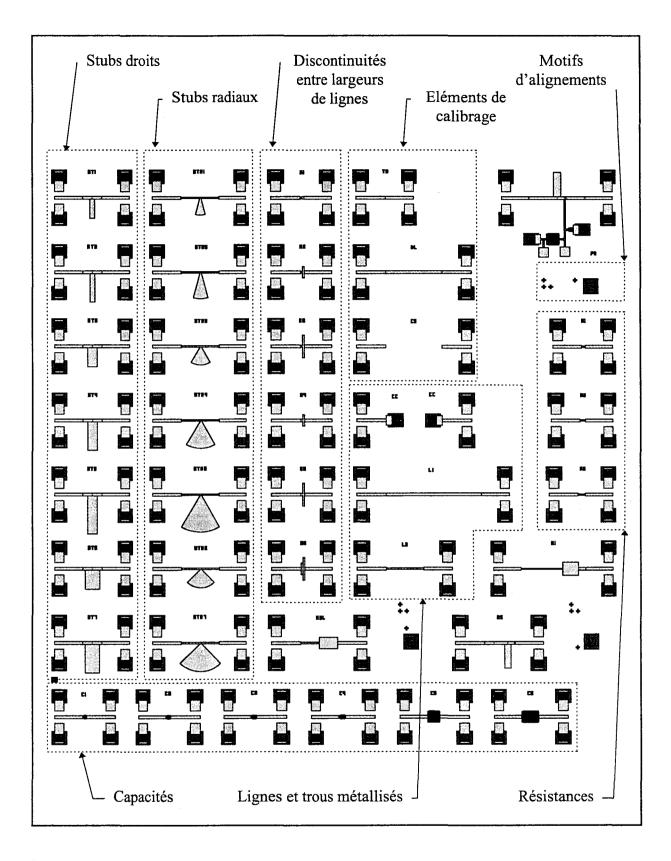

| I. Introduction                                                                            |           |

| II. CONCEPTION DES NIVEAUX DE MASQUES                                                      |           |

| II.1. Les motifs à réaliser                                                                |           |

| II.2. Règles de dessin                                                                     |           |

| II.2.1. Présentation des logiciels utilisés                                                |           |

| II.2.2. Modifications à apporter sous le logiciel MASTEK                                   |           |

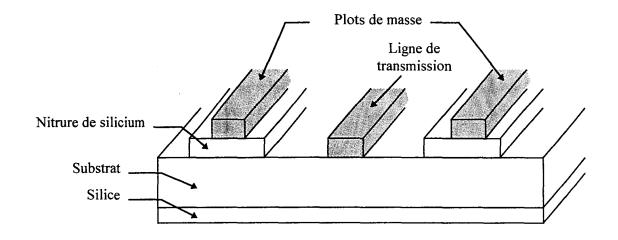

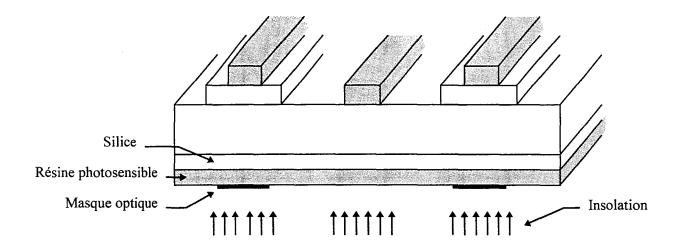

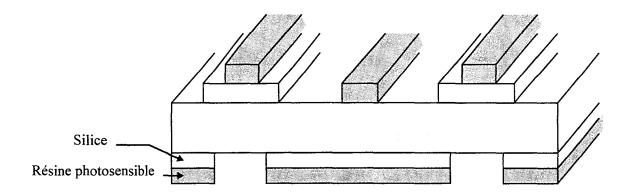

| III. DESCRIPTION DE LA RÉALISATION DES ÉLÉMENTS PASSIFS                                    | 55        |

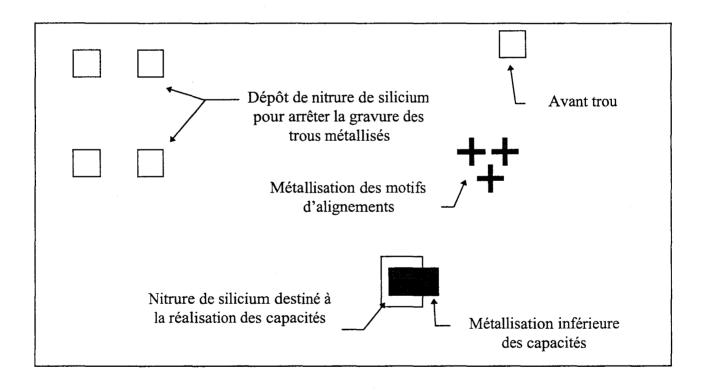

| III.1. Métallisation inférieure des capacités et motifs d'alignements                      |           |

| III.2. Réalisation de l'avant trou                                                         | 55        |

| III.3. Dépôt du diélectrique pour la réalisation des capacités                             | 56        |

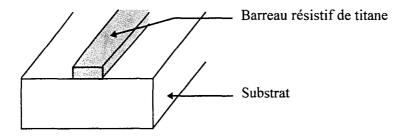

| III.4. Réalisation des résistances                                                         | 56        |

| III.5. Dépôt de la métallisation supérieure                                                | 57        |

| III.6. L'amincissement                                                                     | 57        |

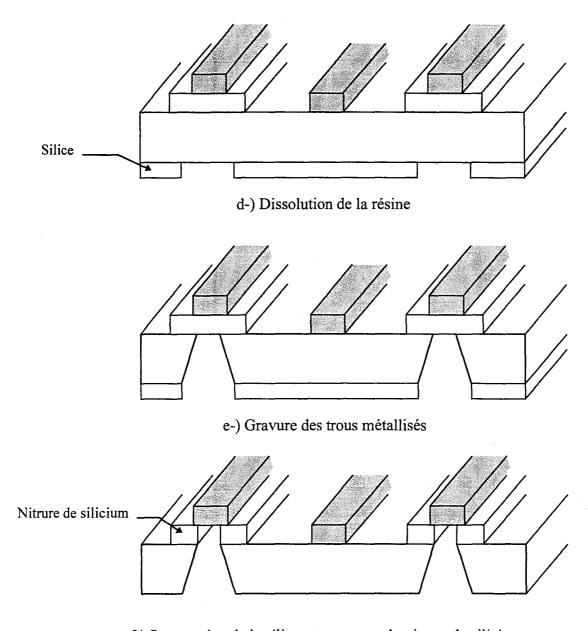

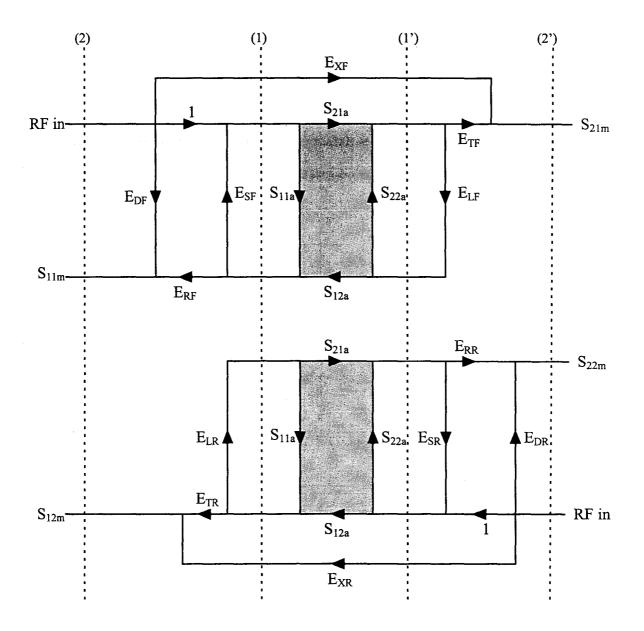

| III.7. La gravure des trous métallisés                                                     | 58        |

| III.8. Relaxation des contraintes                                                          | 59        |

| IV. MESURES DES ÉLÉMENTS PASSIFS                                                           | 59        |

| IV.1. Les méthodes de calibrage utilisées                                                  | 60        |

| IV.1.1. Le calibrage LRM (Line Reflect Match)                                              |           |

| IV.1.2. Le calibrage LRL (Line Reflect Line)                                               |           |

| IV.2. Difficultés rencontrées lors des premières réalisations                              | 62        |

| IV.2.1. Planéité du substrat                                                               | 63        |

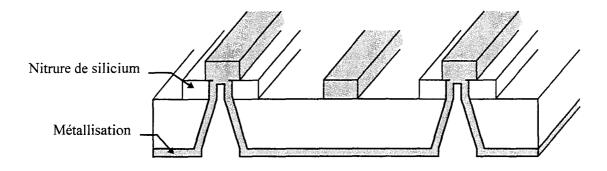

| IV.2.2. Non uniformité des trous métallisés                                                | 63        |

| IV.2.3. Impédance caractéristique différente de 50 Ω                                       | 64        |

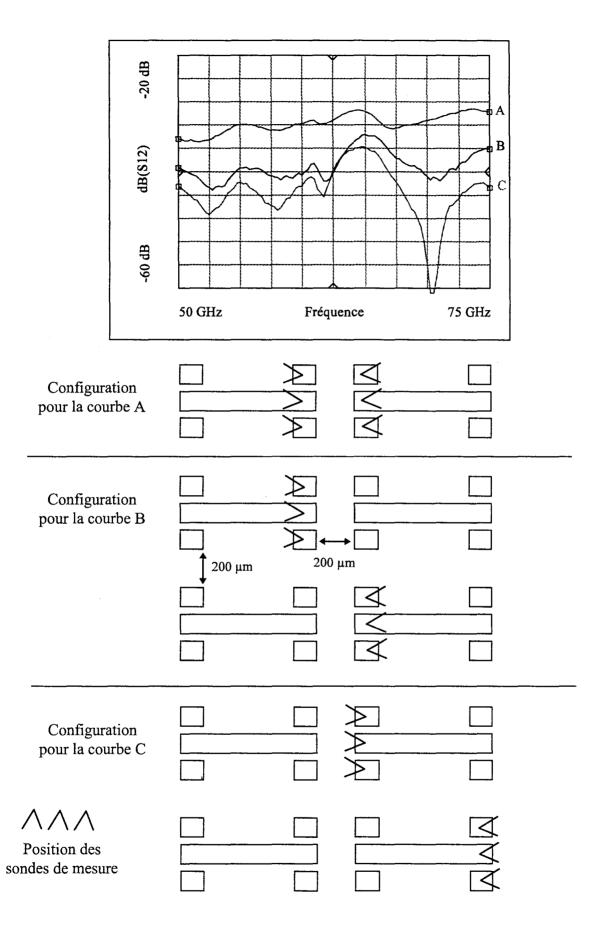

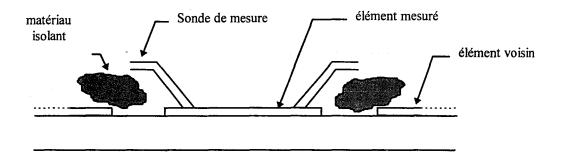

| IV.2.4. Etude du couplage existant entre deux structures voisines                          | 65        |

| IV.3. Résultats obtenus lors des réalisations suivantes                                    | 66        |

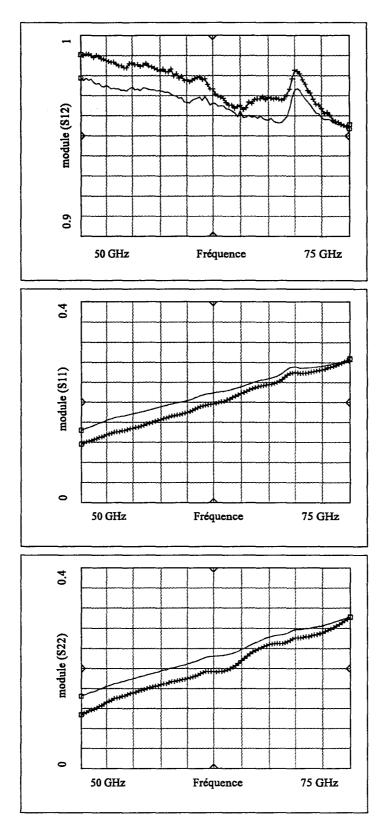

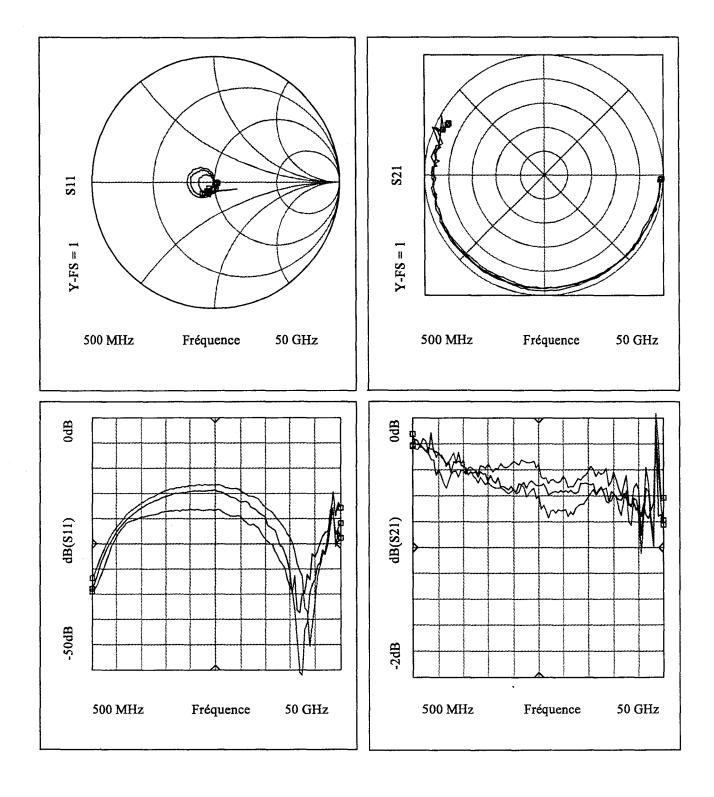

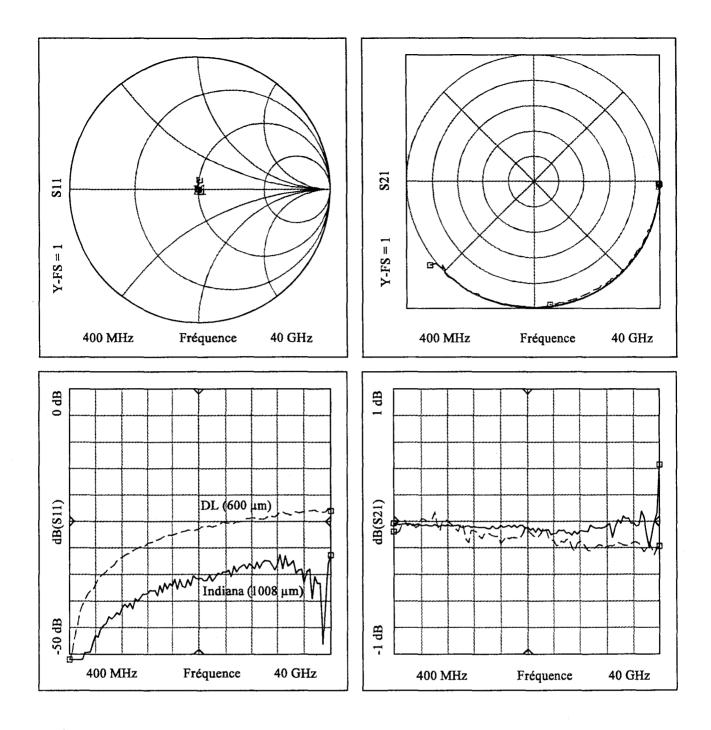

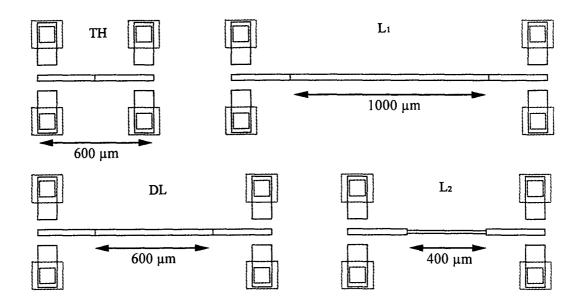

| IV.3.1. Mesures des éléments de calibrage                                                  | 66        |

| IV.3.2. Comparaison de nos lignes avec celles d'un fondeur                                 | 68        |

| V. COMPARAISON MESURES - SIMULATIONS : VALIDITÉ DES MODÈLES                                | 70        |

| V.1. Les lignes de transmission                                                            | 70        |

| V.1.1. Les différents types de lignes présentes                                            | 70        |

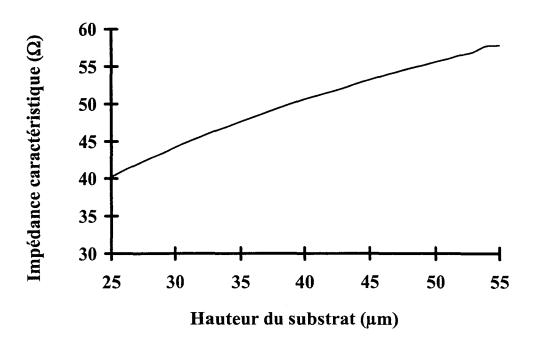

| V.1.2. Influence de l'épaisseur du substrat sur l'impédance caractéristique des lignes       | 71  |

|----------------------------------------------------------------------------------------------|-----|

| V.1.3. Valeurs nécessaires au simulateur                                                     | 72  |

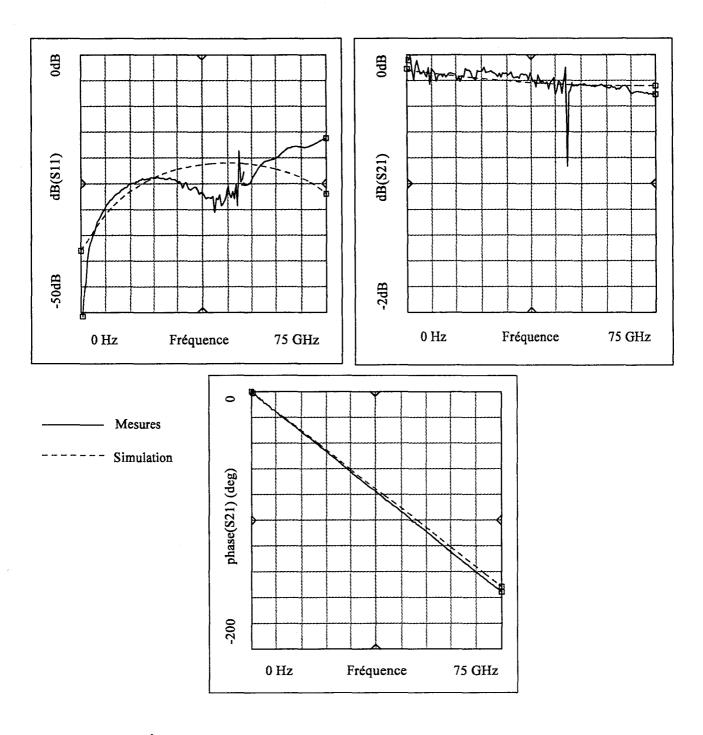

| V.1.4. Mesure des lignes et validation du modèle                                             | 73  |

| V.1.5. Conclusion sur ces modèles de lignes                                                  | 76  |

| V.2. Les résistances                                                                         | 76  |

| V.2.1.Les différentes résistances présentes                                                  | 76  |

| V.2.2.Mesures en courant continu                                                             | 77  |

| V.2.3.Mesures hyperfréquences et validation du modèle                                        | 79  |

| V.2. Les capacités MIM                                                                       | 79  |

| V.3.1. Les différentes capacités réalisées                                                   | 80  |

| V.3.2. Détermination de la valeur de la permittivité relative                                | 81  |

| V.3.3. Comparaison entre les mesures hyperfréquences et les simulations                      | 83  |

| V.4. Les lignes de compensation droites                                                      | 84  |

| V.4.1. Les différentes configurations réalisées                                              | 84  |

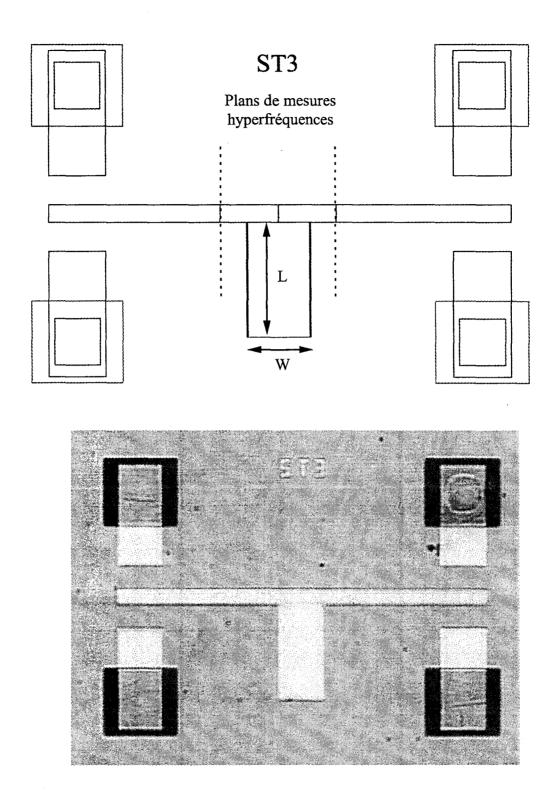

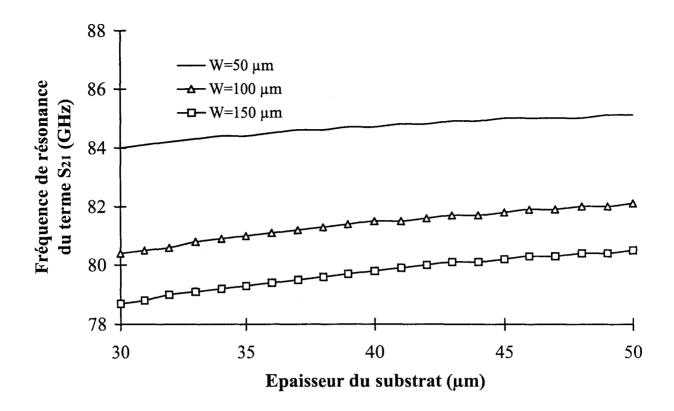

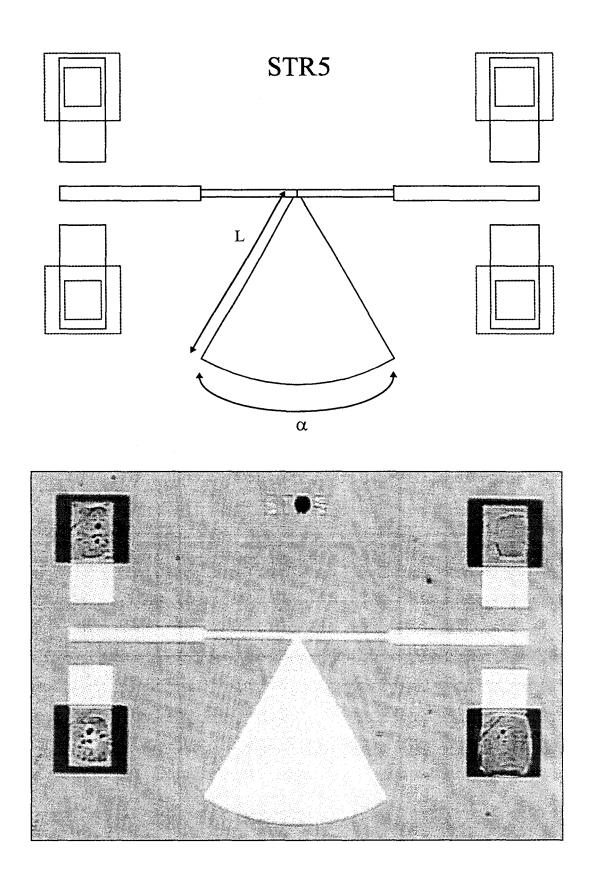

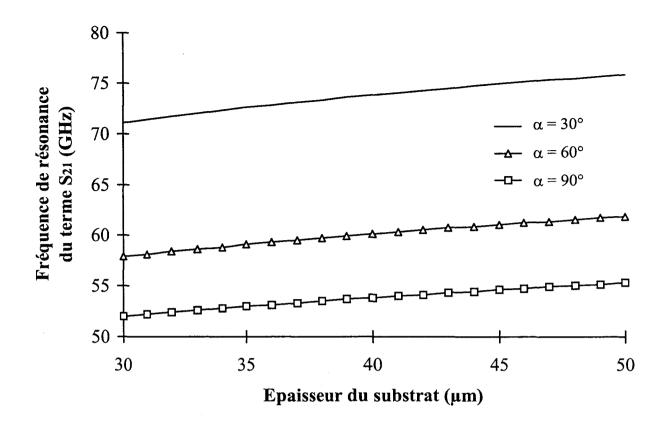

| V.4.2. Fréquence de résonance du terme S <sub>21</sub>                                       | 85  |

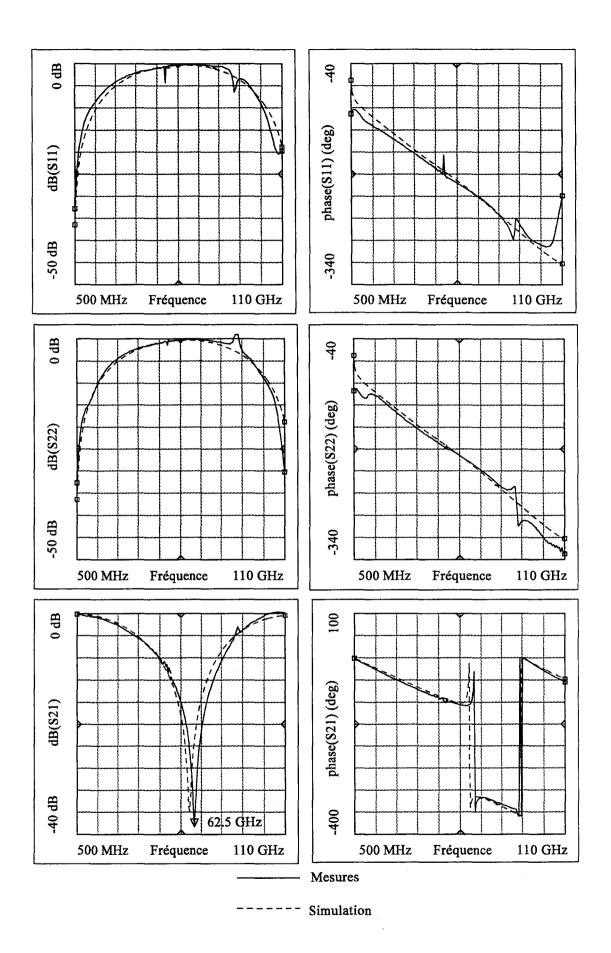

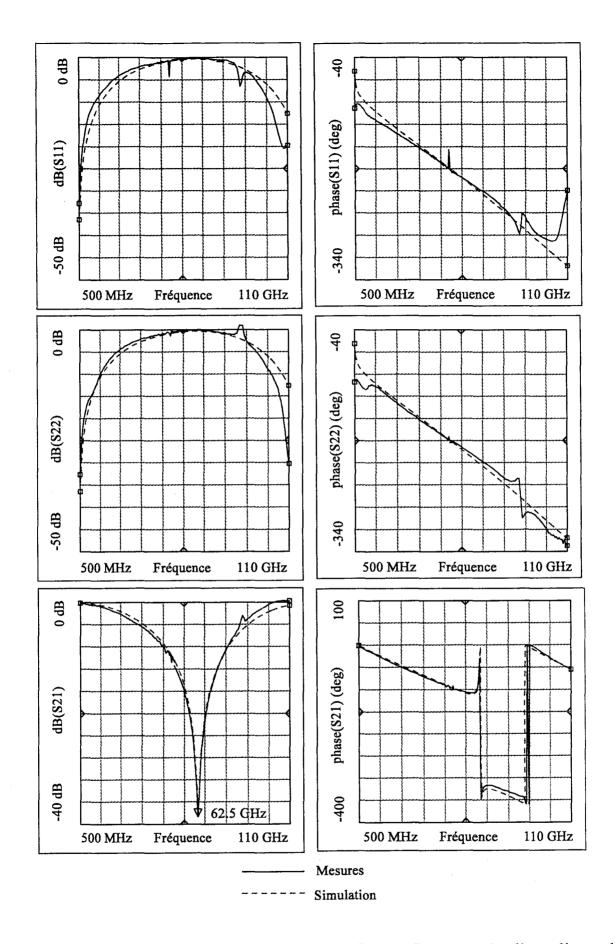

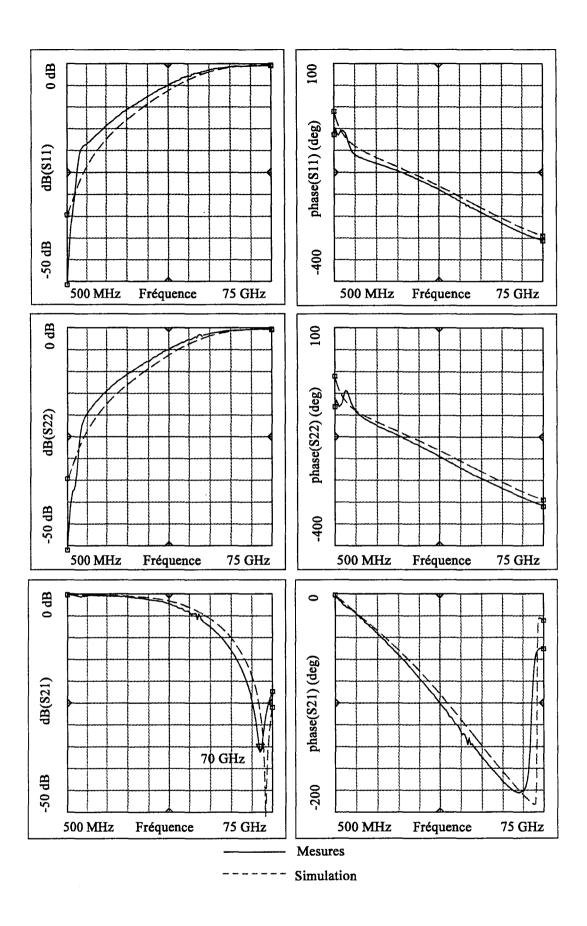

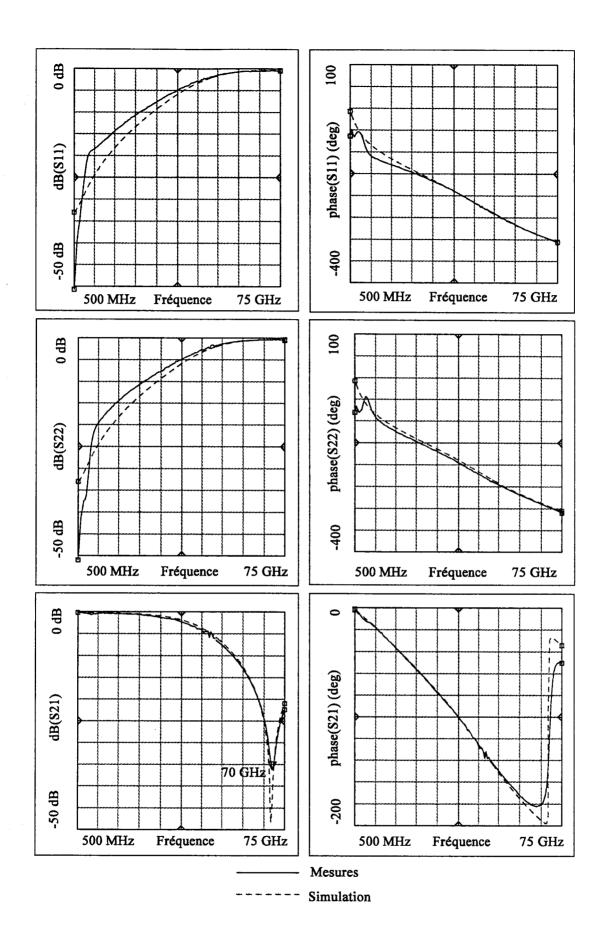

| V.4.3. Validation des compensations                                                          | 89  |

| V.5. Les lignes de compensation radiales                                                     | 90  |

| V.5.1. Les différentes configurations réalisées                                              | 90  |

| V.5.2. Mise en évidence des problèmes et compensation des modèles                            | 91  |

| V.5.3. Validation de la méthode de compensation                                              | 94  |

| V.6. Les trous métallisés                                                                    | 95  |

| V.7. Les discontinuités de largeur de ligne                                                  | 96  |

| V.8. Validation sur une structure complète                                                   | 97  |

| VI. CONCLUSION                                                                               | 98  |

| BIBLIOGRAPHIE                                                                                | 100 |

| CHAPITRE III : Réalisation, mesures et modélisation des éléments actifs                      | 101 |

| I. Introduction                                                                              | 102 |

| II. CARACTÉRISATION DES COMPOSANTS                                                           | 102 |

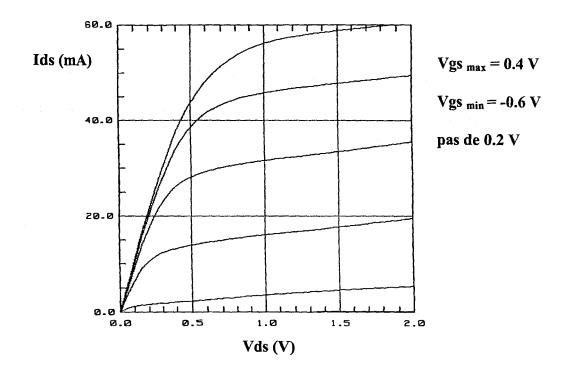

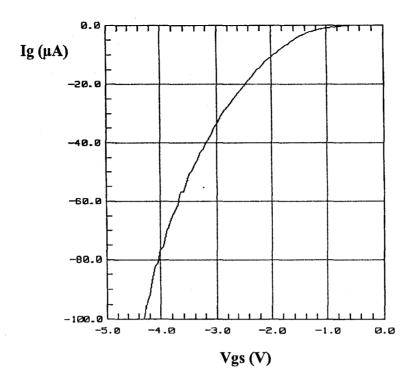

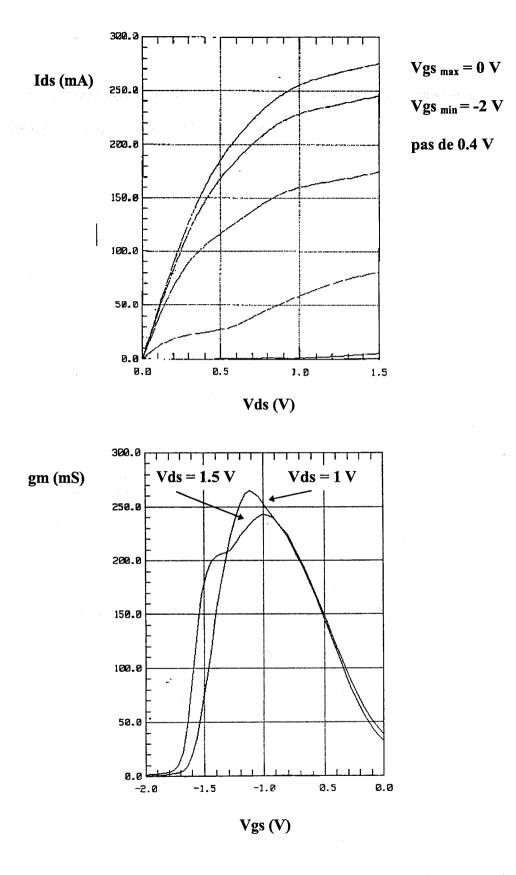

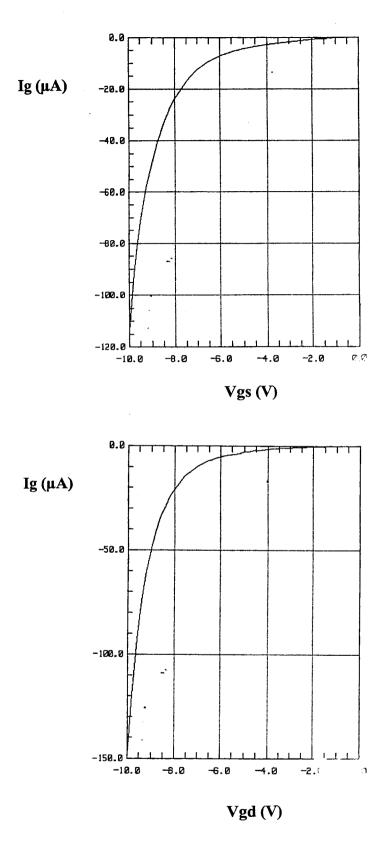

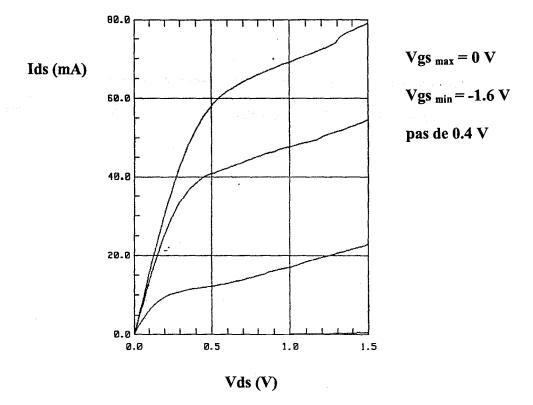

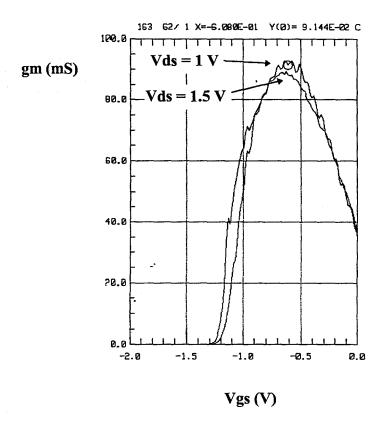

| II.1. Caractérisation en régime statique et présentation des épitaxies étudiées              | 103 |

| II.1.1 Présentation d'ICCAP                                                                  | 103 |

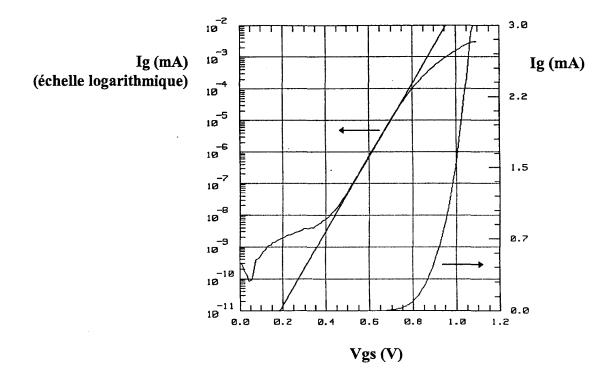

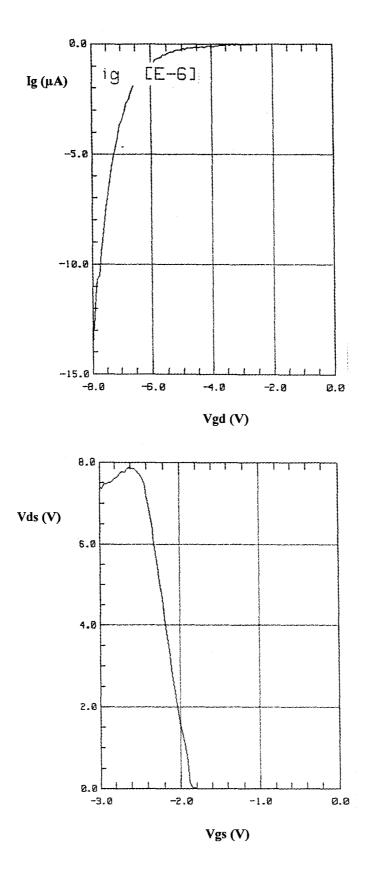

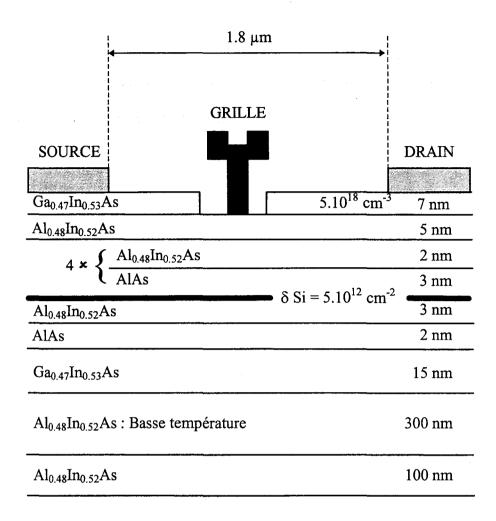

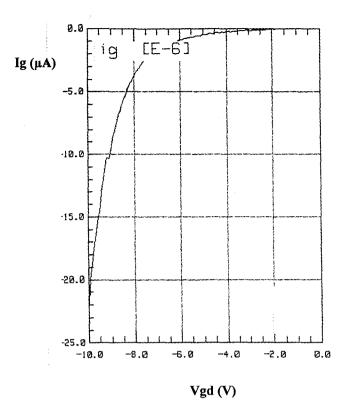

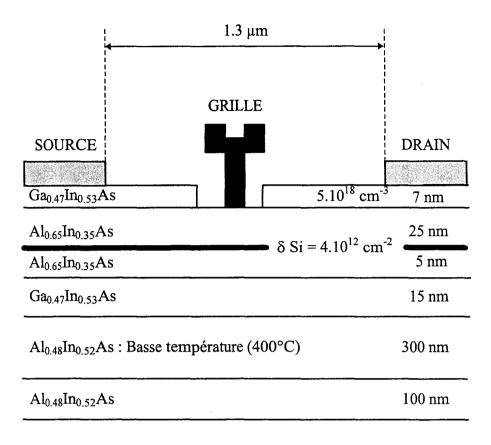

| II.1.2. L'opération 10174B                                                                   | 104 |

| II.1.3. L'épitaxie 10289                                                                     | 107 |

| II.1.4. L'opération 10290                                                                    | 109 |

| II.1.5. L'opération 10347                                                                    | 110 |

| II.1.6. L'opération 10315                                                                    | 112 |

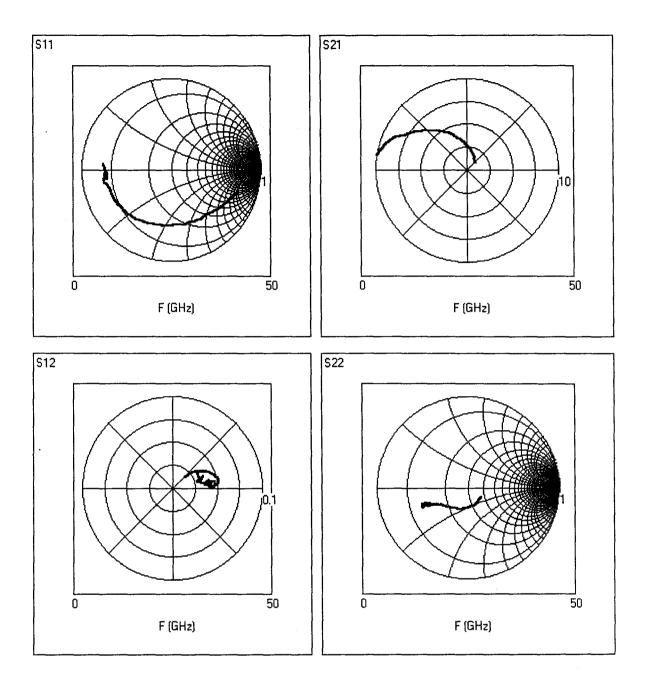

| II.2. Caractérisation hyperfréquence petit signal                                            | 113 |

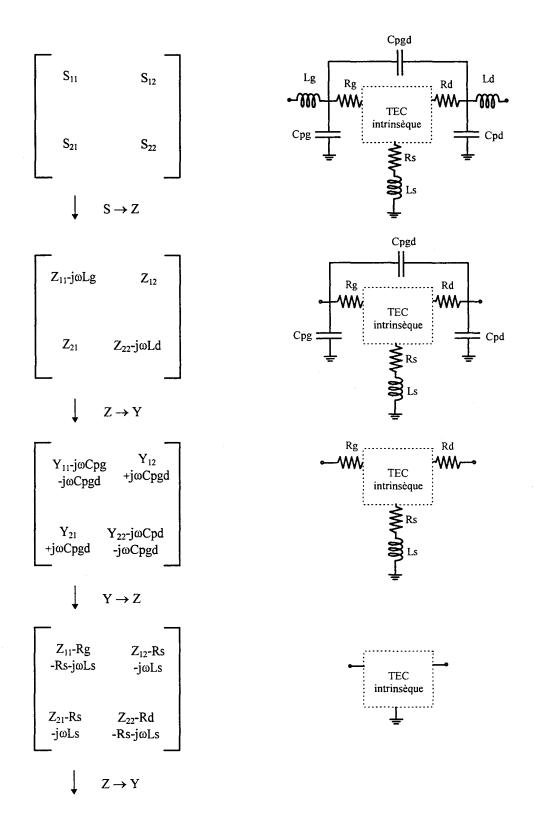

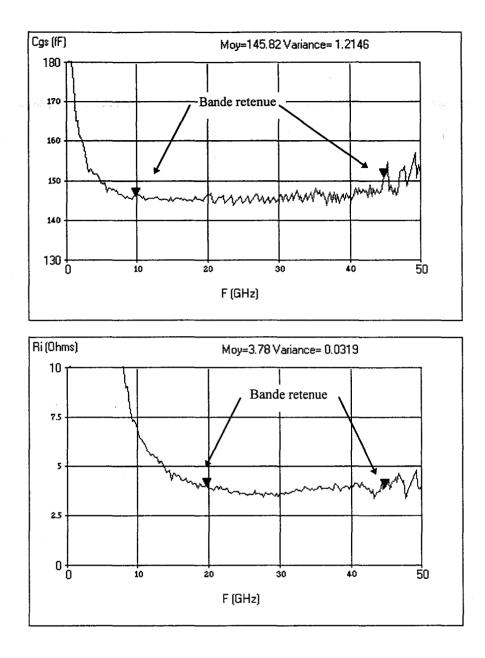

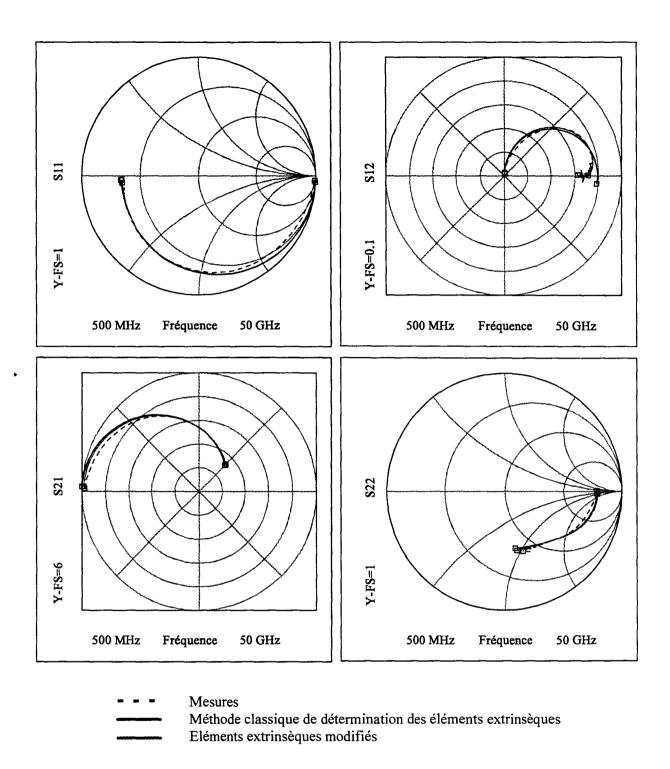

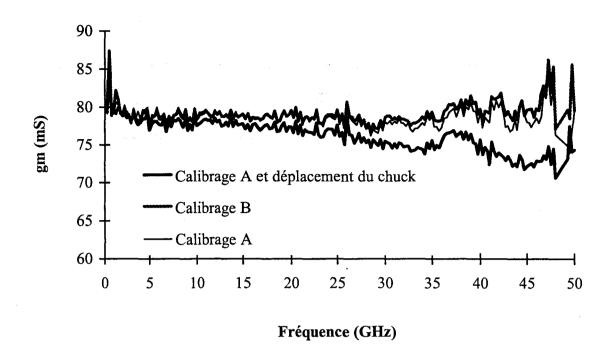

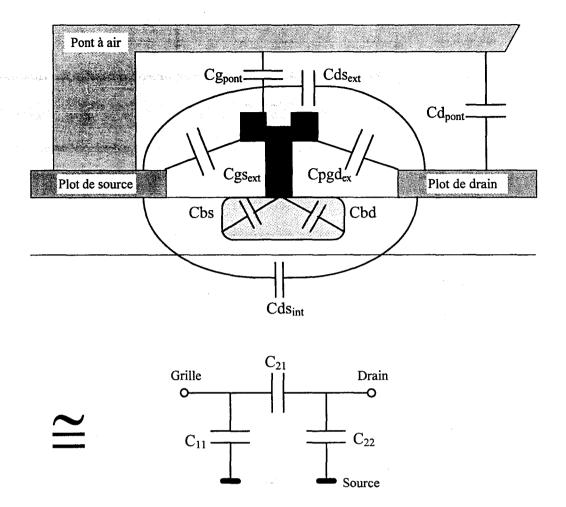

| II.2.1. Schéma équivalent petit signal des transistors                                       | 114 |

| II.2.2. Résultats hyperfréquences petit signal obtenu sur les différentes épitaxies étudiées | 133 |

| II.3. Caractérisation hyperfréquence grand signal en bande V                                 | 136 |

|                                                                                              |     |

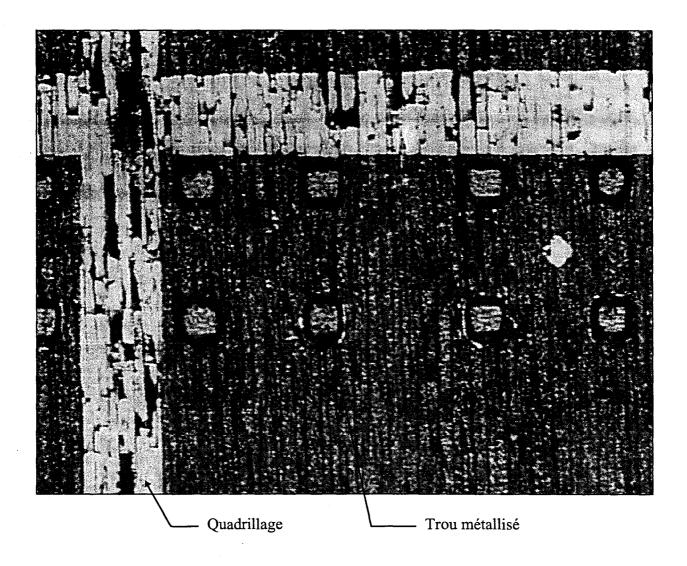

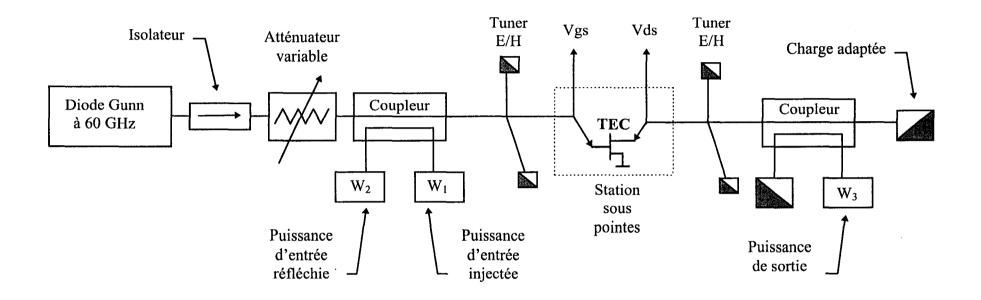

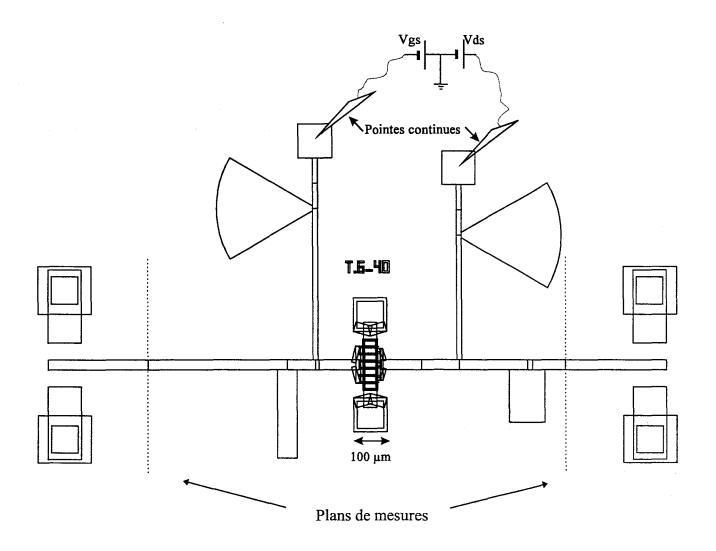

| II.3.1. Présentation du banc de mesure                                                   | 136 |

|------------------------------------------------------------------------------------------|-----|

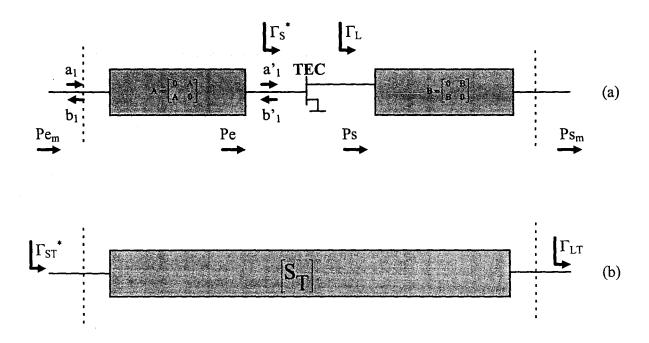

| II.3.2. Méthode de correction des mesures                                                | 137 |

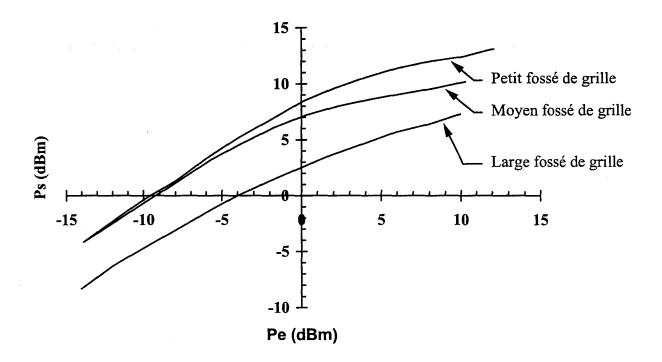

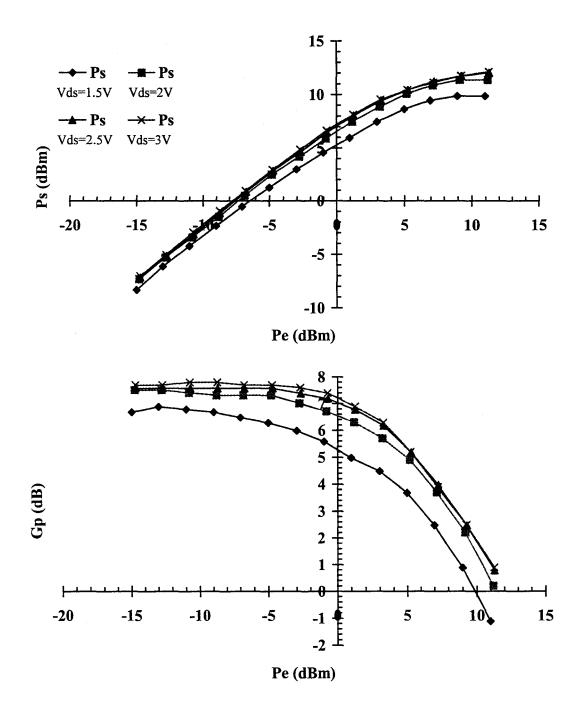

| II.3.3. Résultats des mesures de puissances                                              | 140 |

| II.4. Conclusion : choix de l'épitaxie                                                   | 142 |

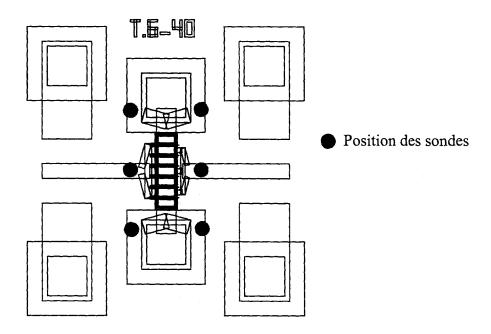

| III. DESCRIPTION DES ÉLÉMENTS PRÉSENTS SUR LE NOUVEAU MASQUE DE TRANSISTOR MAGIC         | 143 |

| III.1. Les éléments de calibrage                                                         | 143 |

| III.2. Les structures supplémentaires permettant de déterminer les éléments extrinsèques | 144 |

| III.2.1. Structures sans doigts de drain ni de grille                                    | 145 |

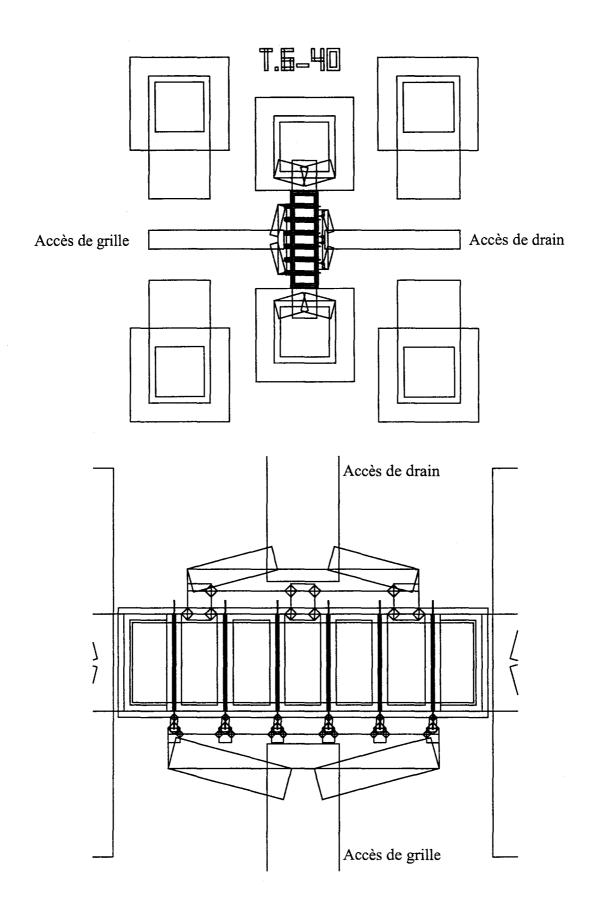

| III.2.2. Structures sans zone active                                                     | 146 |

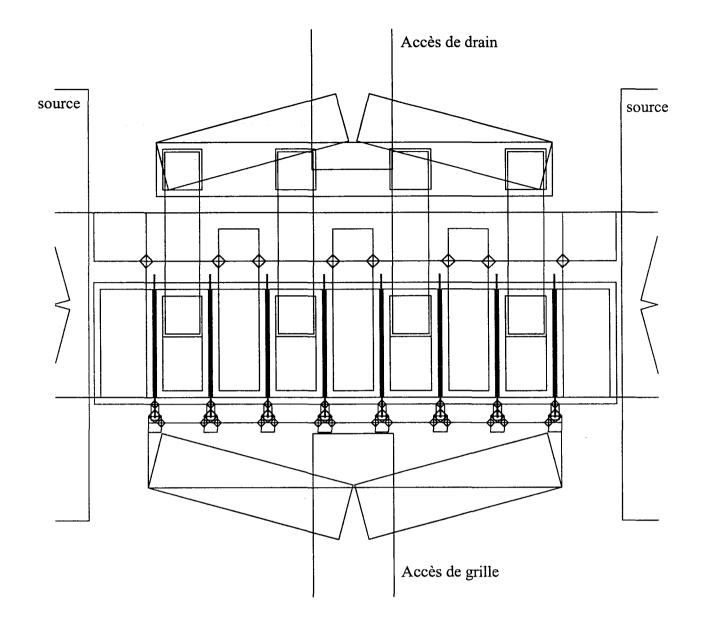

| III.3. Les différents développements de transistors                                      | 147 |

| III.4. Les autres topologies de transistors                                              | 147 |

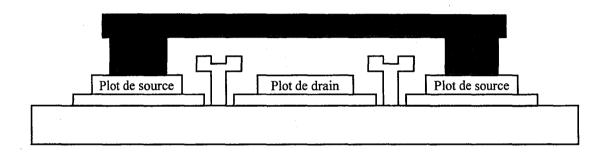

| III.4.1. Transistor avec pont sur le drain                                               | 148 |

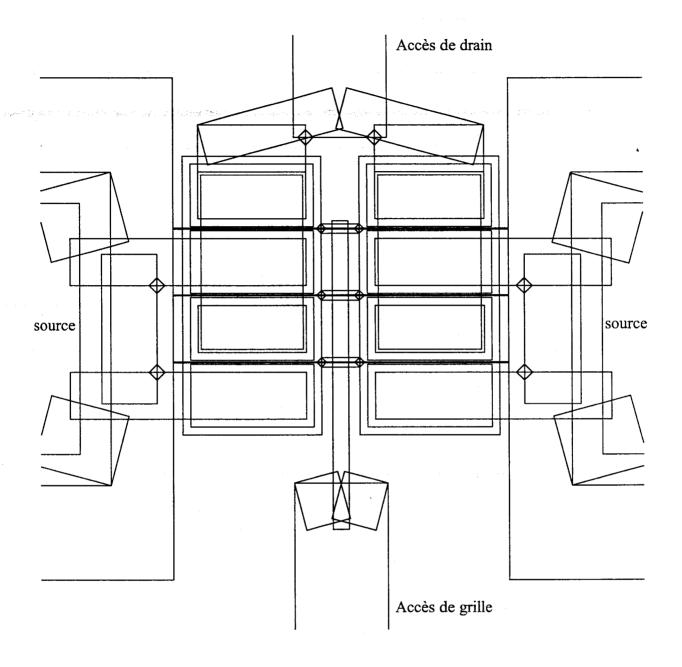

| III.4.2. Transistor en T dit en "arête de poisson"                                       |     |

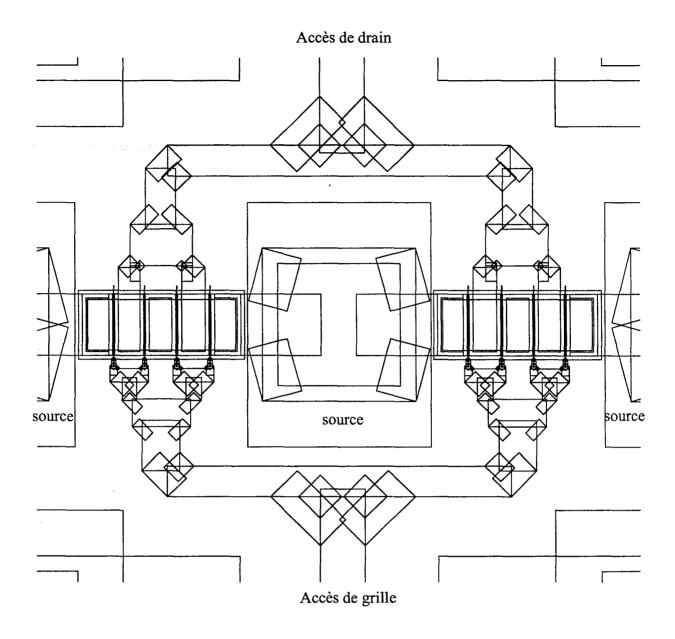

| III.4.3. Composant à trois trous métallisés de source                                    |     |

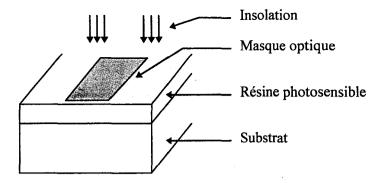

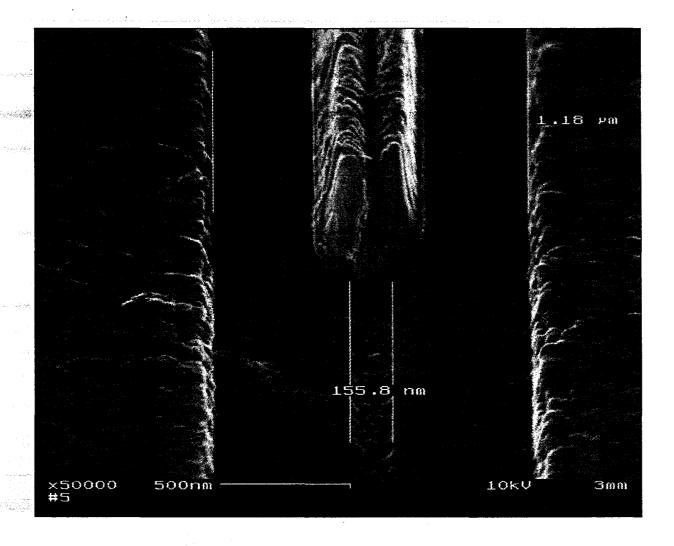

| IV. DESCRIPTION DU PROCÉDÉ DE RÉALISATION DES COMPOSANTS                                 |     |

| IV.1. Marques et motifs d'alignements                                                    | 149 |

| IV.2. Réalisation de l'avant trou                                                        |     |

| IV.3. Les contacts ohmiques                                                              | 150 |

| IV.4. Isolation des transistors                                                          | 150 |

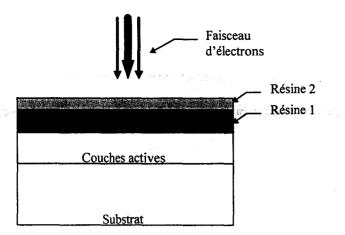

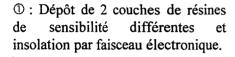

| IV.5. Le fossé de grille                                                                 | 151 |

| IV.6. L'épaississement                                                                   | 151 |

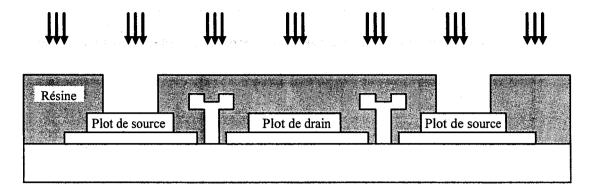

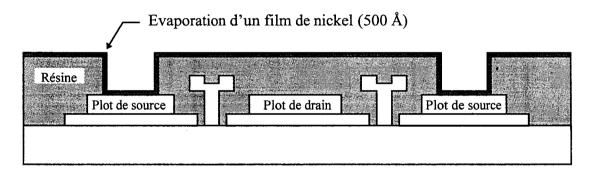

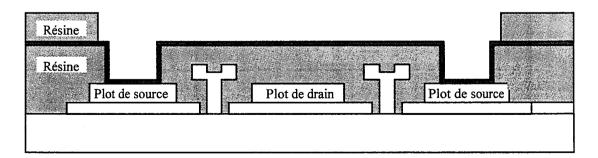

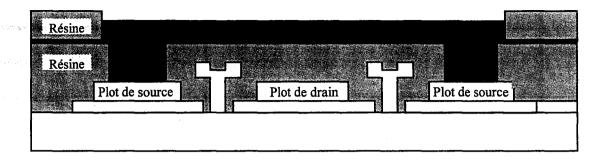

| IV.7. Réalisation des ponts à air                                                        | 152 |

| IV.8. Traitement de la face arrière                                                      | 152 |

| V. CARACTÉRISATION DES COMPOSANTS RÉALISÉS AVEC LE MASQUE MAGIC                          | 152 |

| V.1. Caractérisation statique                                                            | 153 |

| V.1.1. Avant l'étape d'amincissement du substrat                                         | 153 |

| V.1.2. Caractérisation des composants terminés                                           | 155 |

| V.2. Caractérisation hyperfréquence petit signal                                         | 156 |

| V.2.1. Avant l'étape d'amincissement du substrat                                         |     |

| V.2.2. Caractérisation des composants terminés                                           |     |

| V.3. Conclusion                                                                          |     |

| VI. LA FILIÈRE MÉTAMORPHIQUE ALINAS/GAINAS SUR GAAS                                      | 158 |

| VII. CONCLUSION                                                                          | 159 |

| BIBLIOGRAPHIE                                                                            | 161 |

| CHAPITRE IV :Conception d'un amplificateur de puissance en technologie MMIC à 60 GHz     | 165 |

| I. Introduction                                                                          | 166 |

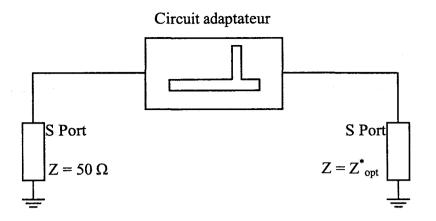

| II. ETUDE DE L'ADAPTATION DES TRANSISTORS                                                | 167 |

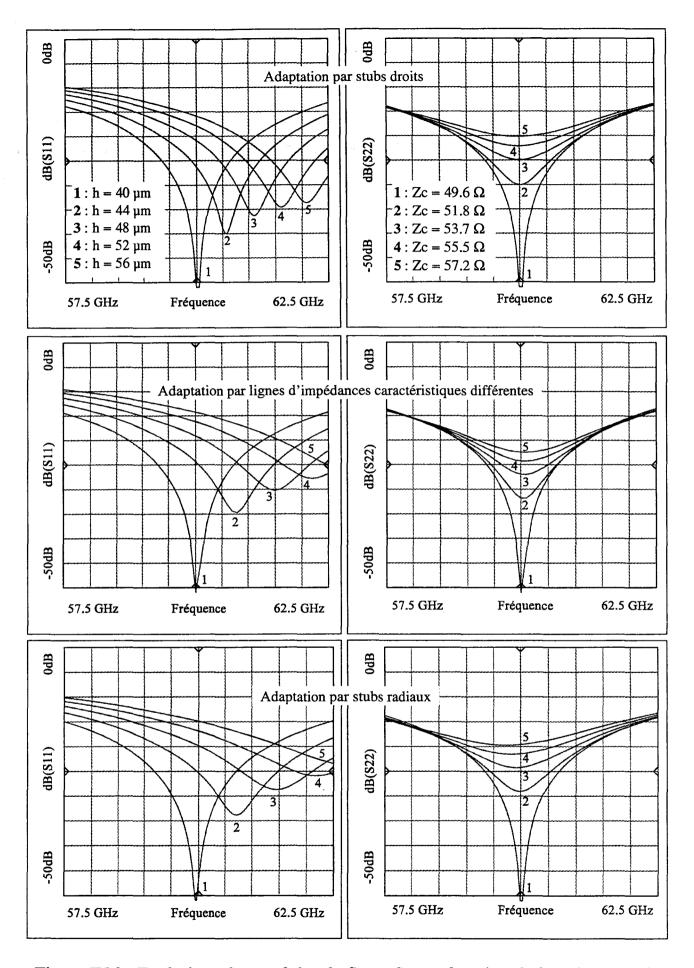

| II.1. Optimisation linéaire des circuits adaptateurs                                     | 167 |

| II.2. Comparaison des trois méthodes d'adaptation                                      | 168 |

|----------------------------------------------------------------------------------------|-----|

| II.2.1. Epaisseur de substrat de 40 µm                                                 | 168 |

| II.2.2. Sensibilité des circuits adaptateurs aux variations de l'épaisseur du substrat | 169 |

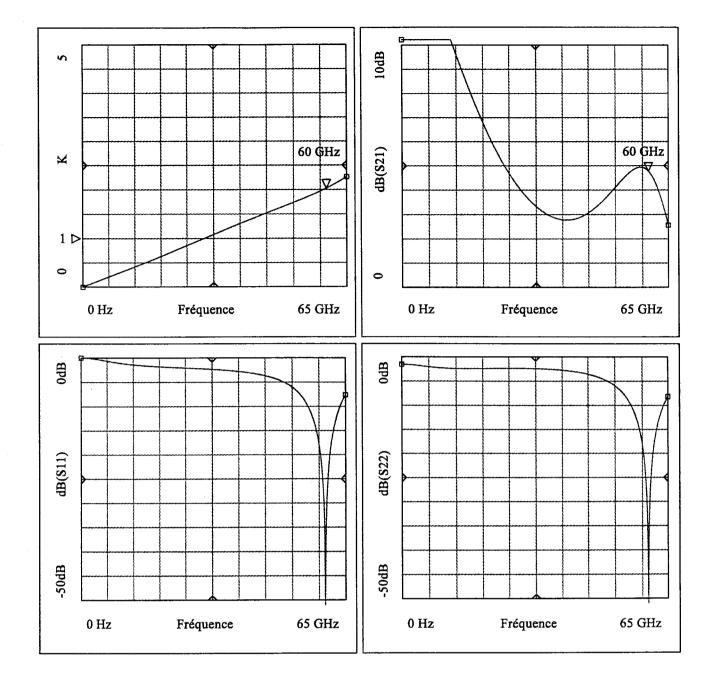

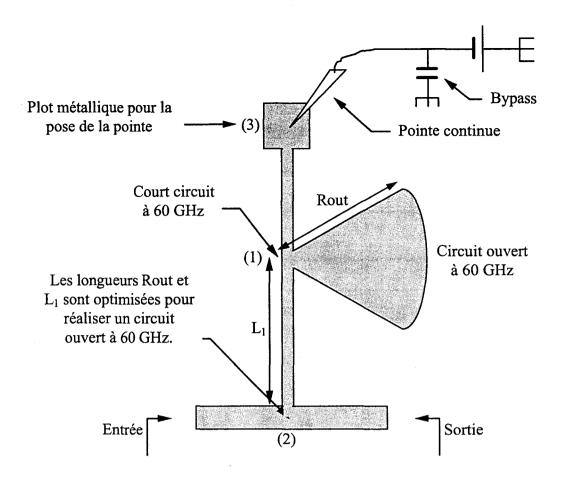

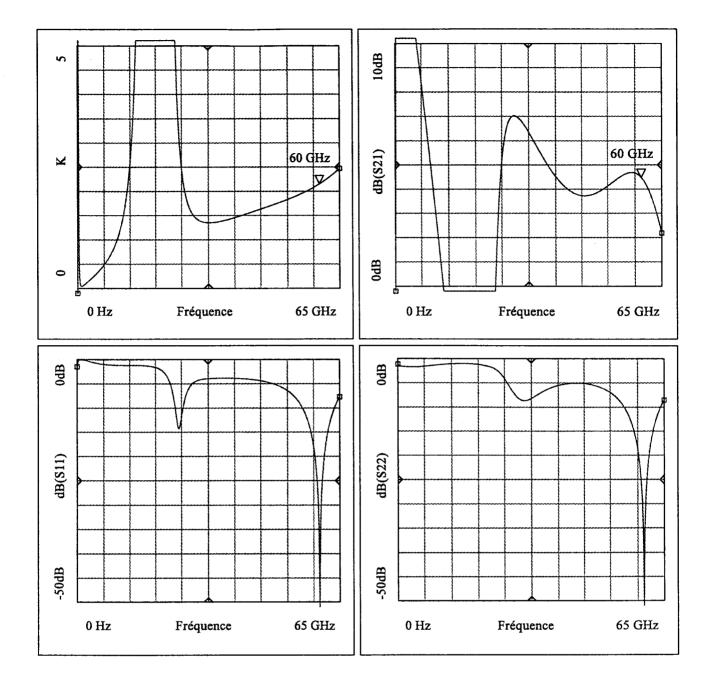

| III. ETUDE DES CIRCUITS DE POLARISATION ET DE STABILISATION                            | 170 |

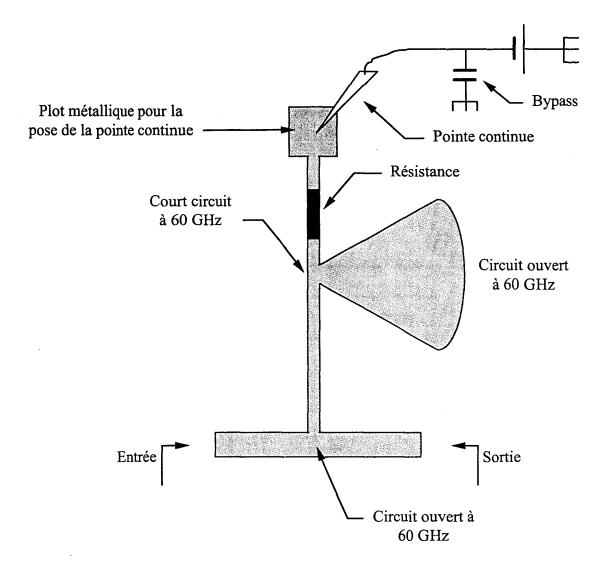

| III.1. Circuits de polarisation                                                        | 171 |

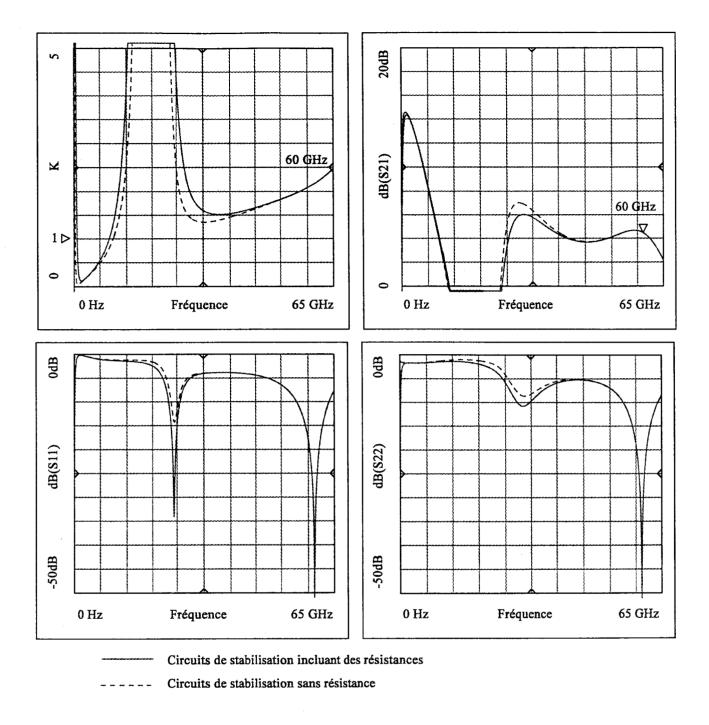

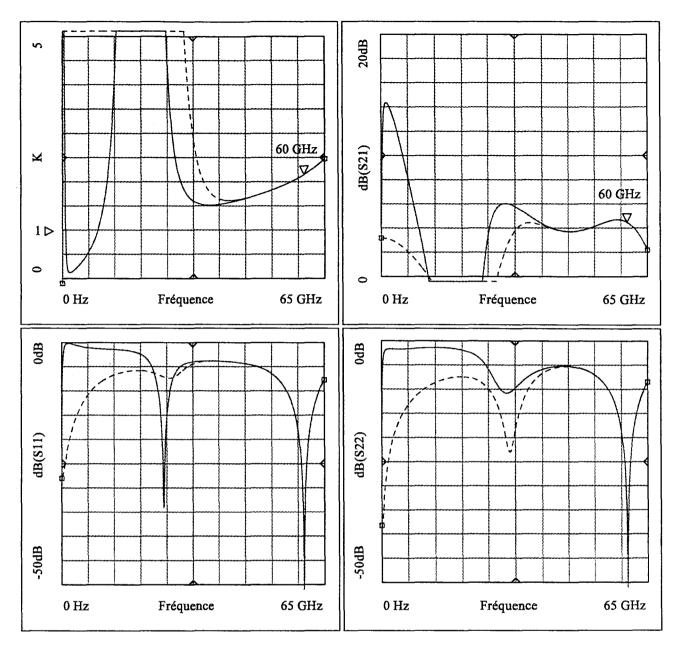

| III.2. Etude des circuits de stabilisation                                             | 172 |

| III.2.1. En fonction des éléments résistifs                                            | 172 |

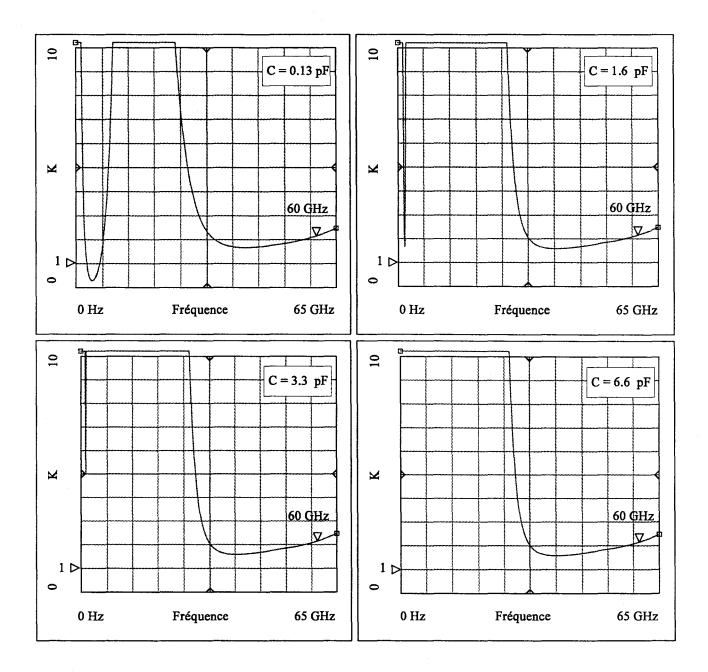

| III.2.2. En fonction des éléments capacitifs                                           | 172 |

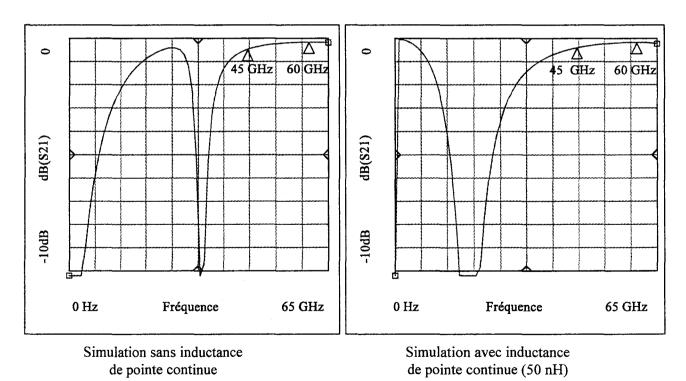

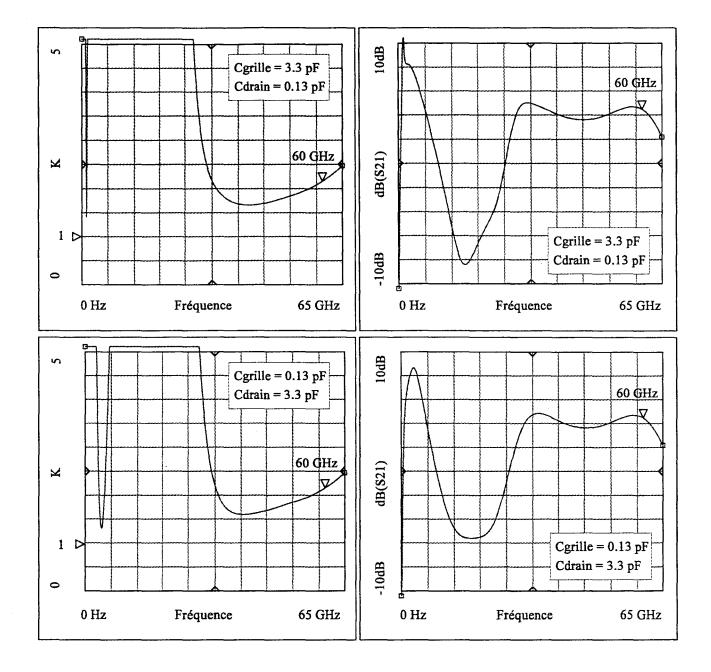

| III.3. Influence des éléments du Té sur le comportement du circuit                     | 174 |

| III.3.1. Partie du circuit ramenant un circuit ouvert à 60 GHz                         | 174 |

| III.3.2. Valeurs et positions des résistances de stabilisation                         | 175 |

| III.3.3. Valeurs des capacités de découplage                                           | 176 |

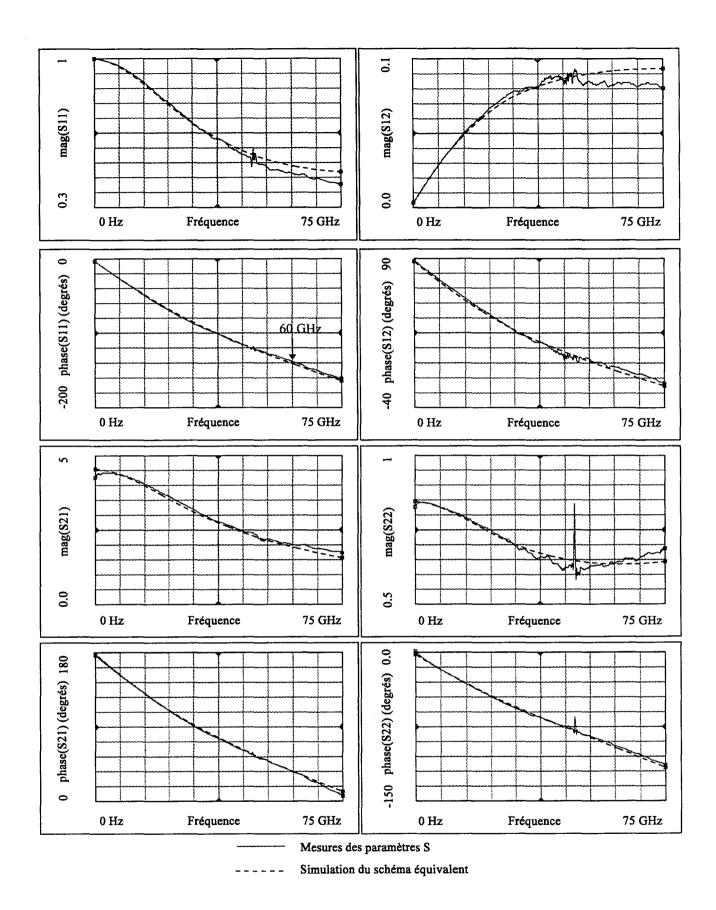

| IV . MODÉLISATION DU COMPOSANT ACTIF POUR LA CONCEPTION DU CIRCUIT                     | 177 |

| V. CONCEPTION DU DÉMONSTRATEUR.                                                        | 179 |

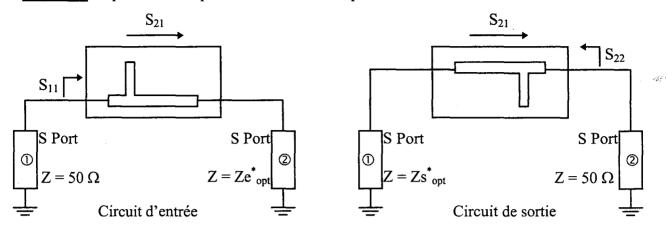

| V.1. Méthodologie de conception                                                        | 179 |

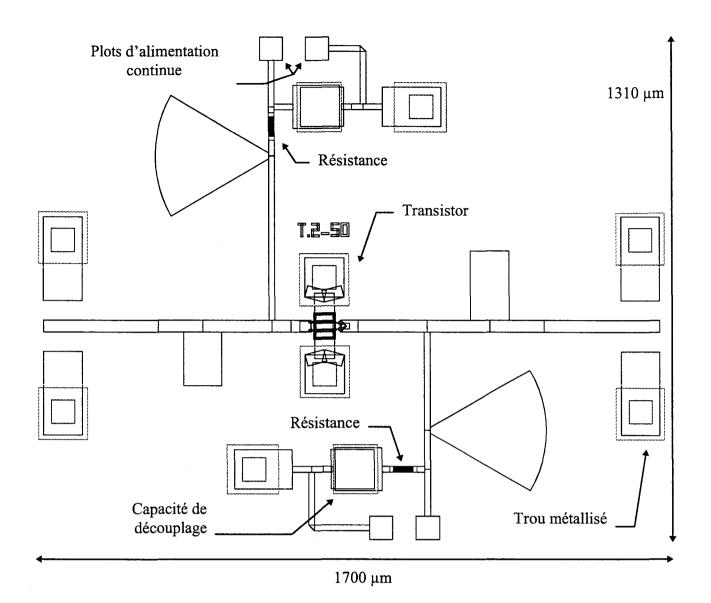

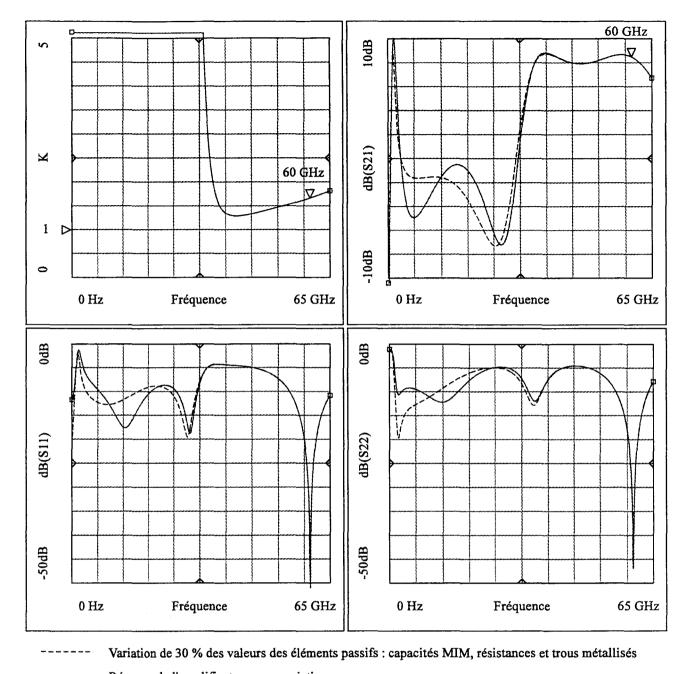

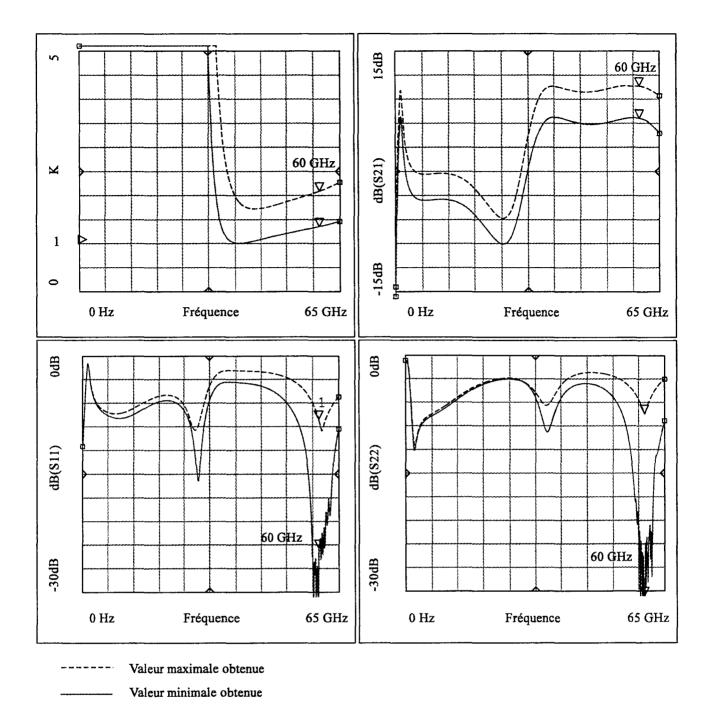

| V.2. Analyse de tolérance du circuit en fonction des éléments passifs                  | 182 |

| V.2.1. Sensibilité à la variation des éléments passifs localisés du circuit            | 182 |

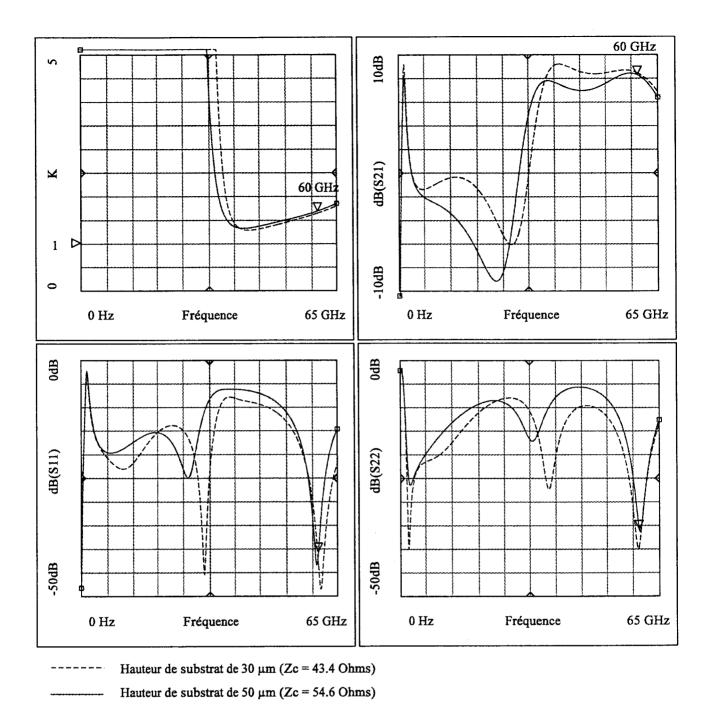

| V.2.2. Sensibilité à la variation de l'épaisseur du substrat                           | 182 |

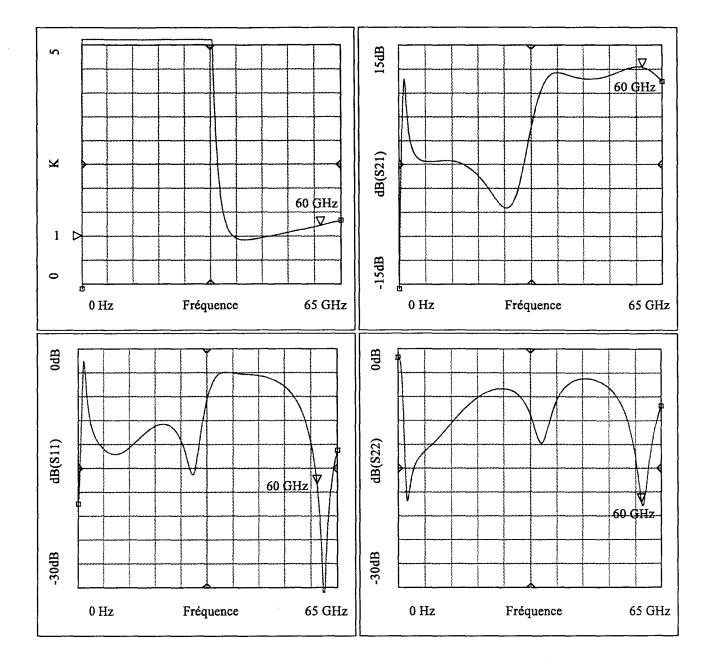

| V.3. Analyse de tolérance du circuit en fonction de l'élément actif                    | 183 |

| V.4. Analyse de sensibilité à la dispersion technologique                              | 184 |

| VI. CONCLUSION                                                                         | 185 |

| BIBLIOGRAPHIE                                                                          | 187 |

| CONCLUSION GENERALE                                                                    | 100 |

| CONCLUSION GENERALE                                                                    | 100 |

# **INTRODUCTION**

Les applications microondes sont en pleine expansion et la saturation progressive des bandes de fréquences allouées pour celles-ci conduisent à développer des applications vers de plus hautes fréquences. Citons par exemple les réseaux locaux multicanaux de distribution de service (LMDS) qui visent la bande des 40 GHz, les communications entre satellites à 60 GHz, les radars anti collision à bord des véhicules opérant autour de 77 GHz, sans oublier les applications militaires à 94 GHz.

A ces fréquences, la maîtrise des interconnexions dans les circuits constitue un point important pour la fiabilité de ces ensembles. C'est pourquoi la technologie MMIC (Monolithic Microwave Integrated Circuit) a supplanté la technologie hybride qui a montré ses limites pour la réalisation des fonctions de ces systèmes au delà de 40 GHz. Parmi ces fonctions, l'amplificateur de puissance tient un rôle primordial dans les chaînes d'émission où il constitue bien souvent l'un des derniers maillons.

Ce travail a pour objectif la conception et la réalisation, pour la première fois au laboratoire et en Europe, d'un amplificateur de puissance en technologie intégrée sur substrat de phosphure d'indium. Une structure en guide de propagation microruban a été préférée à une structure coplanaire car la compacité et la dissipation thermique s'y avèrent meilleures. Cette étude s'insère dans un vaste projet supporté par la DGA (convention DRET 94-160) destiné à l'étude des "potentialités des transistors de la filière GaInAs pour applications microondes faible bruit, de puissance et la conversion optoélectronique."

Le premier chapitre de ce manuscrit est consacré aux caractéristiques des amplificateurs de puissance. Il aborde le rappel des principales grandeurs qui les caractérisent, l'analyse de leur stabilité ainsi que les méthodes habituellement utilisées pour adapter ces composants. Enfin, un état de l'art des transistors à effet de champ et des amplificateurs de puissance aux fréquences de 60 GHz et 94 GHz termine ce chapitre.

Le deuxième chapitre porte sur la réalisation, les mesures et la modélisation d'éléments passifs afin de créer une bibliothèque d'éléments fiables pour la conception du démonstrateur. La réalisation de lignes de transmission, de résistances, de capacités, de trous métallisés et de divers éléments d'adaptation et de calibrage a été mise au point au sein de l'équipe Dispositifs Microondes de Puissance du Professeur Crosnier. Les mesures de ces éléments dans la centrale de caractérisation du laboratoire jusque 110 GHz ont permis leur comparaison aux modèles disponibles sur le simulateur commercial MDS (Microwave Design System). Cette étude a conduit à la nécessité d'élaborer une bibliothèque d'éléments passifs fiables jusque 60 GHz propre à la technologie développée à l'IEMN.

Le troisième chapitre est consacré à la réalisation, aux mesures et à la modélisation des transistors à effet de champ. Des réalisations préliminaires de composants couplées à des caractérisations en régime statique, petit signal et grand signal à 60 GHz permettront la mise au point d'une épitaxie mieux adaptée au fonctionnement en régime d'amplification de puissance. Afin de réaliser des composants multi doigts de grille, un nouveau jeu de masques de transistors sera conçu en attachant une importance particulière à l'amélioration de la détermination des éléments extrinsèques gage d'une meilleure validité en fréquence du schéma équivalent des transistors.

Dans le dernier chapitre nous effectuerons la conception du démonstrateur. Les différentes étapes de la conception seront abordées en tenant compte des contraintes imposées sur les modèles des éléments passifs décrits au deuxième chapitre. Nous adopterons alors une méthodologie de conception progressive afin de s'attacher à distinguer le rôle tenu par chaque élément de ces circuits.

# CHAPITRE I

# CARACTERISTIQUES DES AMPLIFICATEURS DE PUISSANCE ET ETAT DE L'ART A 60 GHZ

## I. Introduction

Nous avons souhaité dans ce premier chapitre rappeler les principales notions relatives à l'amplification de puissance microonde. Ce sont tout d'abord les différents gains que nous définirons ainsi que les critères permettant d'évaluer les performances des transistors en régime de fonctionnement linéaire et non linéaire. Nous aborderons ensuite un des points clé de toute conception d'amplificateurs qui est l'étude de la stabilité des transistors. Puis, nous nous intéresserons aux méthodes permettant de présenter en entrée et en sortie des transistors les impédances optimales souhaitées afin de les adapter. Enfin, afin de situer ce travail, il nous est apparu important d'effectuer un état de l'art des transistors et des amplificateurs de puissance en portant une attention plus particulière sur ceux fonctionnant à 60 GHz et au delà.

# II. Les principales grandeurs caractérisant un transistor de puissance microonde.

# II.1. Le concept des paramètres de répartition

Le court circuit et le circuit ouvert sont les éléments les plus utilisés pour déterminer les coefficients des matrices impédance et admittance des quadripôles. Toutefois, pour des applications à plus hautes fréquences, il devient difficile de réaliser un circuit ouvert ou un court circuit du fait des éventuels couplages et effets parasites qui peuvent apparaître. Ces effets qui affectent la précision de la mesure se révèlent être plus présents lorsque la fréquence augmente. De plus, les éléments actifs étant très

sensibles à ces terminaisons, ils réagissent le plus souvent en oscillant; des mesures dans cet état n'ayant alors que peu d'intérêt pour les concepteurs de circuits.

C'est pourquoi, une représentation pratique des quadripôles basée sur le concept d'onde a été développée pour caractériser les circuits microondes : les paramètres S ou paramètres de répartition (Scattering parameters) dont le nom vient de la similitude de comportement entre la lumière et l'énergie microonde. Les plus importantes caractéristiques de ces paramètres sont la relative facilité et la précision avec laquelle ils peuvent être mesurés à très hautes fréquences ainsi que leur interprétation physique vis à vis des autres matrices.

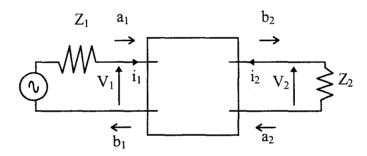

Nous présentons figure I.1 un quadripôle fermé par une impédance  $Z_1$  en entrée et  $Z_2$  en sortie.  $Z_1$  et  $Z_2$  sont les impédances de référence et peuvent prendre n'importe quelle valeur ; toutefois 50  $\Omega$  est la valeur la plus utilisée.

Figure I.1: Représentation générale d'un quadripôle

Les relations reliant les ondes incidentes  $a_1$ ,  $a_2$  et réfléchies  $b_1$ ,  $b_2$  aux courants et tensions fermés sur l'impédance de référence  $Z_0$  sont les suivantes :

$$a_i = \frac{1}{2} \left( \frac{V_i}{Z_0} + \sqrt{Z_0} . I_i \right)$$

$b_i = \frac{1}{2} \left( \frac{V_i}{Z_0} - \sqrt{Z_0} . I_i \right)$   $(i = 1, 2)$

La matrice de répartition est définie par :

$$\begin{cases} b_1 = S_{11}a_1 + S_{12}a_2 \\ b_2 = S_{21}a_1 + S_{22}a_2 \end{cases}$$

Il peut parfois être utile de les convertir en d'autres paramètres : impédance, admittance, hybride ou chaîne, ce qui peut être réalisé aisément à partir de simples conversions de matrice [1].

# II.2. Les concepts de gain

En régime d'amplification de puissance, le composant actif est rapidement appelé à fonctionner en régime non linéaire, à cause des importantes excursions de tension et de courant qui lui sont appliquées. La prise en compte de ces phénomènes dans une conception d'amplificateur nécessite l'utilisation de simulateurs performants car l'estimation analytique des performances du transistor dans ce mode de fonctionnement reste difficile. Toutefois, une approche analytique en régime de fonctionnement linéaire, que nous allons décrire dans la partie suivante, est possible [2].

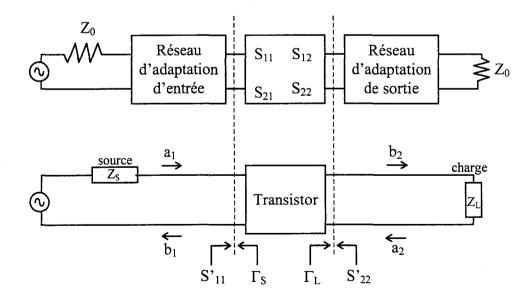

Dans la pratique, le transistor est généralement inséré entre deux réseaux d'adaptations afin de présenter à ses bornes, à partir de l'impédance de référence  $Z_0 = 50 \Omega$ , les impédances de source  $Z_S$  et de charge  $Z_L$  souhaitées (figure I.2).

Figure I.2 : Schéma équivalent d'un étage amplificateur à transistor.

Partant de cette configuration, trois concepts de gain sont utilisés en puissance, un paragraphe est consacré à chacun d'eux dans ce qui suit.

#### II.2.1. Gain de transducteur

Le gain de transducteur est défini comme étant le rapport entre la puissance absorbée par la charge en sortie du transistor et la puissance disponible de la source située à l'entrée du transistor.

$$G_T = \frac{P_S}{P_{AVS}}$$

Son expression dans le formalisme des paramètres [S] est la suivante :

$$G_{T} = \frac{\left|S_{21}\right|^{2} (1 - \left|\Gamma_{S}\right|^{2}) (1 - \left|\Gamma_{L}\right|^{2})}{\left|1 - S'_{11} \Gamma_{S}\right|^{2} \left|1 - S_{22} \Gamma_{L}\right|^{2}} = \frac{\left|S_{21}\right|^{2} (1 - \left|\Gamma_{S}\right|^{2}) (1 - \left|\Gamma_{L}\right|^{2})}{\left|1 - S_{11} \Gamma_{S}\right|^{2} \left|1 - S'_{22} \Gamma_{L}\right|^{2}}$$

où:

$\Gamma_S$  est le coefficient de réflexion de l'impédance de source  $Z_S$  vue par l'entrée du transistor et  $\Gamma_L$  est le coefficient de réflexion de l'impédance de charge  $Z_L$  vue par la sortie du transistor.

$S'_{11}$  est le coefficient de réflexion présenté par l'entrée du transistor lorsqu'il est chargé en sortie par l'impédance  $Z_L$ :

$$S'_{11} = S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L}$$

et  $S'_{22}$  le coefficient de réflexion présenté par la sortie du transistor lorsque celui-ci est fermé en entrée par l'impédance  $Z_S$ :

$$S'_{22} = S_{22} + \frac{S_{12}S_{21}\Gamma_S}{1 - S_{11}\Gamma_S}$$

Ce gain est fonction simultanément des coefficients de réflexion de source  $\Gamma_S$  et de charge  $\Gamma_L$  vus par le transistor. Il est possible d'obtenir un gain de transducteur

maximum lorsque l'on adapte de manière optimale le transistor à la fois en entrée et en sortie. Cela nécessite de satisfaire simultanément aux deux conditions suivantes :

$$S'_{11} = \Gamma_S^*$$

et  $S'_{22} = \Gamma_L^*$

Par la résolution de ce système d'équations, et si la valeur du coefficient K est supérieure à l'unité, il est possible d'obtenir les valeurs des coefficients de réflexion optimum  $\Gamma_{\text{Sopt}}$  et  $\Gamma_{\text{Lopt}}$  à présenter au transistor en entrée et en sortie. Leurs expressions sont les suivantes :

$$\Gamma_{\text{Sopt}} = \frac{1}{2C_1} (B_1 \pm 2 | S_{12} S_{21} | \sqrt{K^2 - 1})$$

+ si  $B_1 < 0$  - si  $B_1 > 0$

$$\Gamma_{\text{Lopi}} = \frac{1}{2C_2} (B_2 \pm 2 | S_{12} S_{21} | \sqrt{K^2 - 1}) + \text{si } B_2 < 0$$

$$- \text{si } B_2 > 0$$

avec

$$B_{1} = 1 + |S_{11}|^{2} - |S_{22}|^{2} - |\Delta|^{2}$$

$$B_{2} = 1 - |S_{11}|^{2} + |S_{22}|^{2} - |\Delta|^{2}$$

$$C_{1} = S_{11} - \Delta S_{22}^{*}$$

$$C_{2} = S_{22} - \Delta S_{11}^{*}$$

$$\Delta = S_{11}S_{22} - S_{12}S_{21}$$

$$K = \frac{1 - |S_{11}|^{2} - |S_{22}|^{2} + |\Delta|^{2}}{2|S_{12}S_{21}|}$$

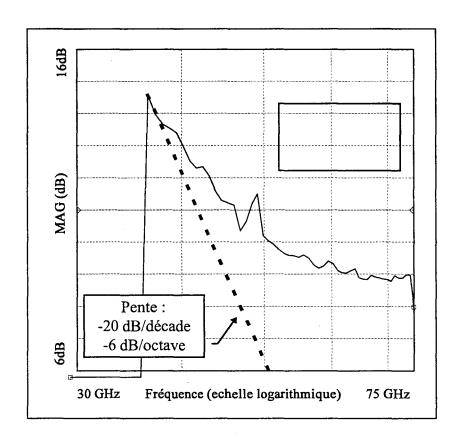

Nous pouvons constater que, suivant les valeurs prises par le coefficient K, il sera ou non possible de réaliser ces conditions optimales. Ce coefficient, appelé plus communément coefficient de stabilité du transistor (ou facteur de Rollet), sera détaillé plus spécifiquement au paragraphe III.1. de ce chapitre. Lorsque ce coefficient est supérieur à l'unité, il est possible d'adapter le transistor par ses impédances optimales à la fois en entrée et en sortie. Dans ces conditions, le gain de transducteur est maximum et est aussi appelé MAG (Maximum Available Gain). Son expression est alors :

MAG =

$$\frac{|S_{21}|}{|S_{12}|} (K \pm \sqrt{K^2 - 1})$$

avec le signe :  $+ \text{ si } B_1 < 0$

- si  $B_1 > 0$

Ce gain, qui représente le gain en puissance maximal que va pouvoir fournir le transistor, est un des critères important d'évaluation des performances des transistors en régime de fonctionnement linéaire.

#### II.2.2. Gain en puissance

Le gain en puissance est défini comme étant le rapport entre la puissance absorbée par la charge présentée en sortie du transistor et la puissance absorbée en entrée par le transistor. Son expression est :

$$G_P = \frac{P_S}{P_E} = \frac{|S_{21}|^2 (1 - |\Gamma_L|^2)}{|1 - S_{22}\Gamma_L|^2 (1 - |S'_{11}|^2)}$$

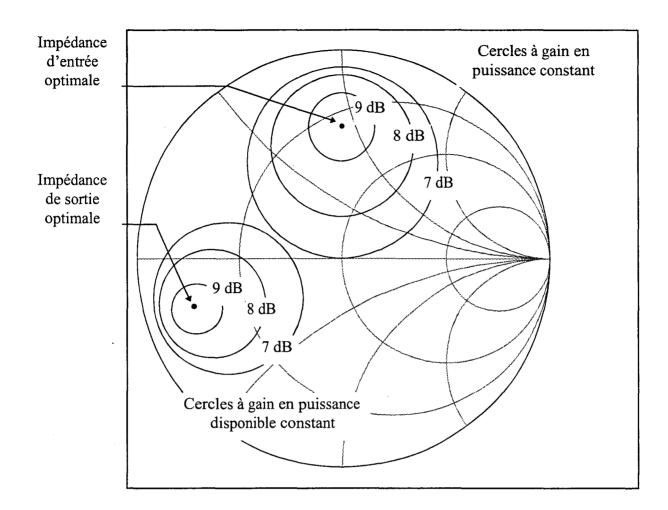

Nous pouvons constater que ce gain est uniquement fonction des conditions d'adaptation en sortie du transistor. Sa valeur sera donc inchangée que l'on présente en entrée du composant,  $50~\Omega$ , ou toute autre impédance. On peut également montrer que les lieux des coefficients de réflexion  $\Gamma_L$  permettant d'obtenir un gain en puissance constant sont des cercles de centre C et de rayon R ayant pour expressions :

$$C = \frac{g_p(S_{22}^* - S_{11}\Delta^*)}{1 + g_p(|S_{22}|^2 - |\Delta|^2)} \qquad R = \frac{\sqrt{1 - 2.K.g_p.|S_{12}S_{21}| + g_p^2|S_{12}S_{21}|^2}}{1 + g_p(|S_{22}|^2 - |\Delta|^2)}$$

$$avec \qquad g_p = \frac{G_P}{|S_{21}|^2}$$

L'adaptation optimale en sortie est obtenue lorsque le rayon du cercle devient nul. Dans ce cas, il est également possible de montrer que le gain en puissance optimum est égal au gain maximum disponible et que l'impédance de charge optimale obtenue pour le gain en puissance est la même que celle obtenue pour le gain maximum disponible.

#### II.2.3. Gain en puissance disponible

Le gain en puissance disponible est défini comme étant le rapport entre la puissance disponible en sortie du transistor et la puissance disponible en entrée du transistor. Son expression s'écrit :

$$G_{av} = \frac{|S_{21}|^2 (1 - |\Gamma_S|^2)}{|1 - S_{11}\Gamma_S|^2 (1 - |S'_{22}|^2)}$$

Cette quantité n'est cette fois uniquement fonction que des conditions d'adaptation en entrée du transistor. Elle est essentiellement utilisée lors de mesures de facteurs de bruit. Comme pour le gain en puissance, il est possible de montrer que les lieux des coefficients de réflexion  $\Gamma_S$  permettant d'obtenir un gain en puissance disponible constant sont des cercles de centre C et de rayon R définis comme suit :

$$C = \frac{g_{av}(S_{11}^* - S_{22}\Delta^*)}{1 + g_{av}(|S_{11}|^2 - |\Delta|^2)} \qquad R = \frac{\sqrt{1 - 2.K.g_{av} \cdot |S_{12}S_{21}| + g_{av}^2 |S_{12}S_{21}|^2}}{1 + g_{av}(|S_{11}|^2 - |\Delta|^2)}$$

$$avec \qquad g_{av} = \frac{G_{av}}{|S_{21}|^2}$$

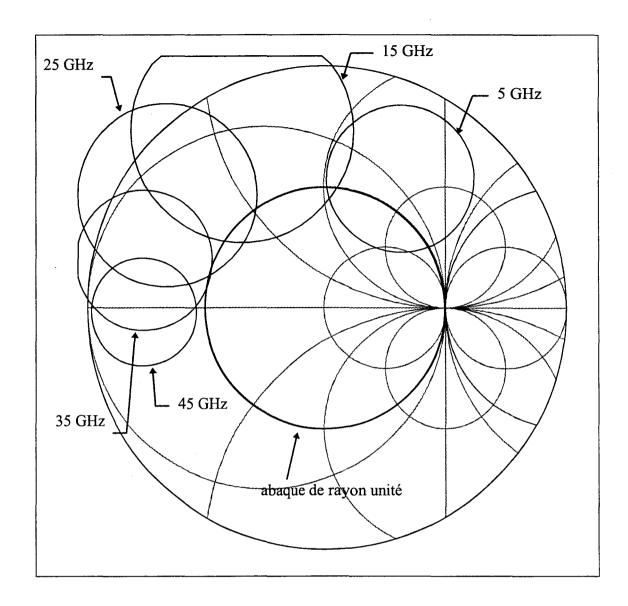

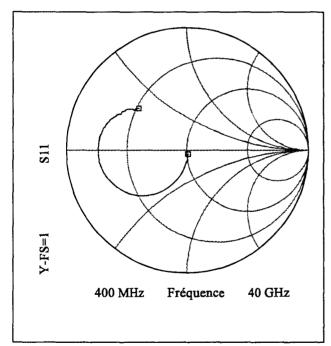

L'adaptation optimale pour le gain en puissance disponible est également réalisée lorsque le rayon du cercle devient nul. Dans ce cas, le gain en puissance disponible est égal au gain maximum disponible (MAG) et l'impédance d'entrée optimale obtenue pour le gain en puissance disponible est la même que celle obtenue pour le gain maximum disponible. Un exemple des lieux des impédances en entrée et en sortie permettant d'obtenir un gain en puissance constant ainsi qu'un gain en puissance disponible constant est donné figure I.3.

# II.3. Les critères d'évaluations des performances des transistors à effet de champ

Figure I.3: Cercles donnant les lieux des impédances permettant d'obtenir un gain en puissance constant et un gain en puissance disponible constant à 60 GHz.

(InP HEMT  $2 \times 50 \mu m$ , réalisé au laboratoire Vds = 2 V; Vgs = 0 V)

La différentiation de composants repose souvent sur l'estimation de leurs performances, ce qui nécessite la définition de critères d'évaluations. Ces critères vont nous permettre à partir des performances des transistors d'estimer par exemple les performances que pourrait développer un circuit MMIC (Microwave Monolithic Integrated Circuit) réalisé à partir de ces composants. Nous avons classé ces critères suivant qu'ils se manifestent soit lors d'un fonctionnement linéaire, ou non linéaire du transistor.

#### II.3.1. Critères d'évaluations en fonctionnement linéaire

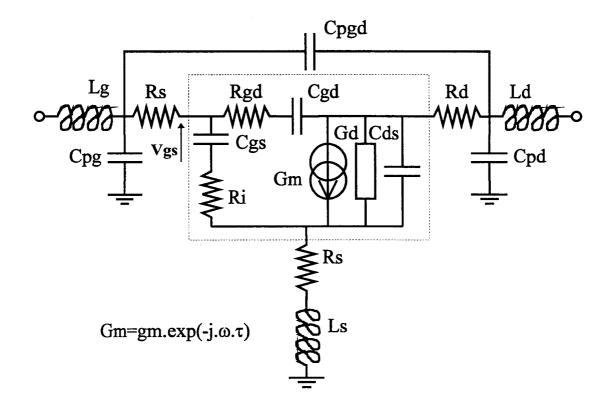

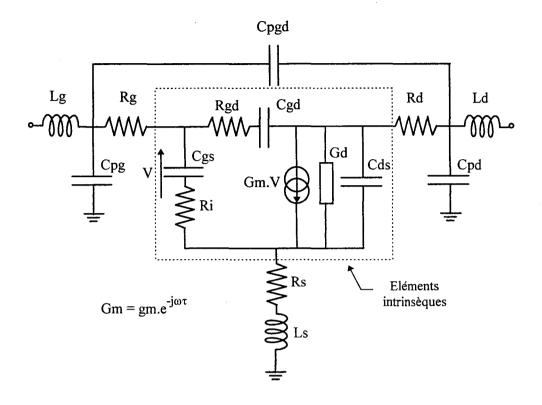

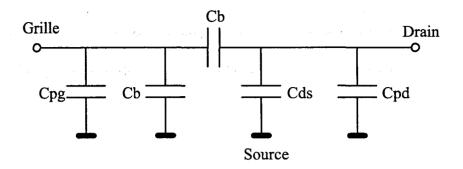

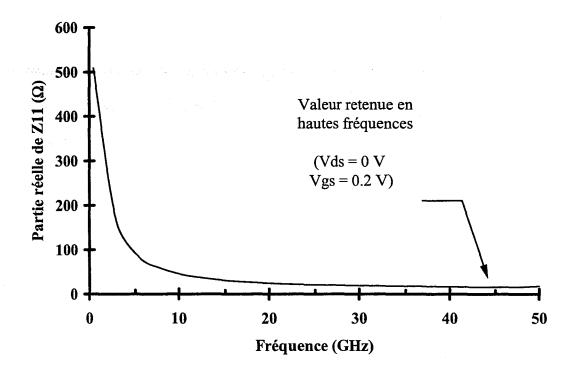

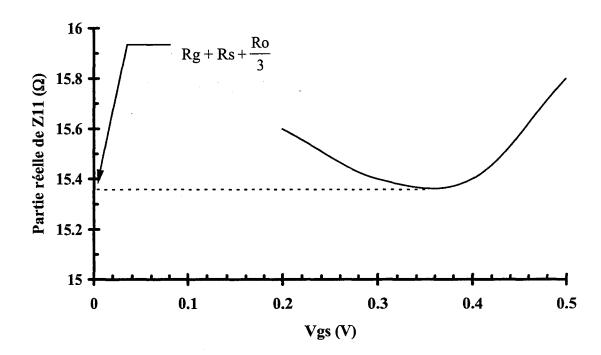

Les critères d'évaluations en fonctionnement linéaire du transistor peuvent être soit directement obtenus de la mesure de paramètres [S] à l'analyseur de réseau vectoriel, soit déduits du schéma équivalent électrique localisé du transistor à effet de champ présenté figure I.4. Ce schéma permet de décrire le fonctionnement du transistor à effet de champ en fonction de la fréquence en régime de fonctionnement petit signal. Il est composé d'une partie extrinsèque et d'une partie intrinsèque. La partie extrinsèque représente les éléments d'accès ou parasites du transistor. Ces éléments sont considérés indépendants du point de polarisation appliqué au transistor. La partie intrinsèque représente la partie active du composant dont les éléments varient en fonction de la polarisation appliquée au transistor.

Il est important d'essayer de conserver une bonne correspondance entre la signification des éléments de ce schéma et les grandeurs physiques du transistor afin de pouvoir l'utiliser non seulement pour évaluer les performances globales des transistors, mais aussi pour pouvoir évaluer les performances de la partie intrinsèque uniquement.

#### II.3.1.1. Le gain maximum disponible et sa fréquence de coupure

Comme nous l'avons vu dans le paragraphe II.2.1., ce gain est obtenu dans les conditions d'adaptation optimales à la fois en entrée et en sortie du transistor. On a alors le maximum de transfert de puissance entre l'entrée et la sortie du composant. Toutefois, ces conditions ne peuvent être réalisées que si le transistor est stable, ce qui correspond à un coefficient de stabilité K>1. Rappelons l'expression de ce gain en fonction des paramètres [S], expression déjà définie au paragraphe II.2.1. :

Figure I.4 : Schéma équivalent localisé du transistor à effet de champ

MAG =

$$\frac{|S_{21}|}{|S_{12}|} (K \pm \sqrt{K^2 - 1})$$

+ si B<sub>1</sub> < 0

- si B<sub>1</sub> > 0

Ce gain est une des caractéristiques essentielles pour la conception de circuits MMIC ou hybrides car, aux pertes près localisées dans les circuits d'adaptation en entrée et en sortie du composant, il représente le gain en puissance réellement disponible en fonctionnement petit signal de l'étage amplificateur.

Lorsque le coefficient de stabilité K est inférieur à l'unité, on utilise alors le gain maximum stable (MSG) comme critère d'évaluation des performances amplificatrices du transistor.

$$MSG = \left| \frac{S_{21}}{S_{12}} \right|$$

Toutefois, ce gain, supérieur au MAG quand le transistor est stable surestime les performances amplificatrices réelles du composant. L'évolution du MAG en fonction de la fréquence permet de définir sa fréquence de coupure  $F_{MAG}$  comme étant la valeur de la fréquence pour laquelle le MAG vaut 0 dB.

Le MAG ainsi que sa fréquence de coupure peuvent également être exprimés en fonction des éléments du schéma équivalent électrique localisé [3] selon la relation :

$$\begin{split} MAG \ = \ & \left(\frac{F_T}{f}\right)^2 \frac{1}{4Gd(Rg + Rs + Ri + \pi F_T Ls) + 4\pi F_T Cgd(2Rg + Ri + Rs + 2\pi F_T Ls)} \\ et \\ F_{mag} \ = \ & \frac{F_T}{2\sqrt{Gd}} \frac{1}{\sqrt{(Rs + Ri + Rg) + \pi F_T Ls + \pi F_T \frac{Cgd}{Gd}(Rs + 2Rg + Ri + 2\pi F_T Ls)}} \end{split}$$

....

$F_T = \frac{gm}{2\pi(Cgs + Cgd)}$ ; fréquence de coupure intrinsèque du gain en courant.

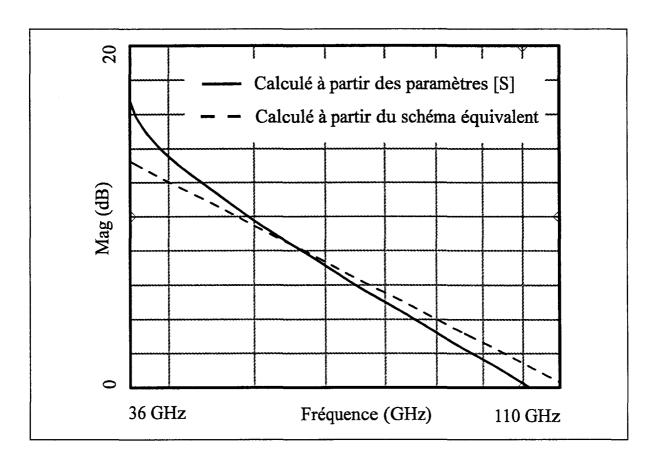

Figure I.5: Comparaison entre le MAG calculé à partir de la formule faisant intervenir les différents éléments du schéma équivalent et le MAG calculé à partir de la formule déduite des paramètres [S] (K > 1 pour f > 36 GHz).

(Composant InP HEMT  $2 \times 50 \times 0.25 \text{ } \mu\text{m}^2$  réalisé au laboratoire : Vds = 2 V ; Vgs = 0V)

Ces expressions simplifiées comportent des approximations habituellement utilisées pour des transistors de longueurs de grille importante (>1 µm) [4]. Afin de vérifier la validité de ces approximations pour des composants de plus faible longueur de grille (0.2 µm) nous présentons figure I.5 une comparaison entre le MAG calculé à partir des paramètres [S] déduits du schéma équivalent et du MAG calculé à partir de la formule faisant intervenir les éléments les plus influents. On constate que lorsque l'on s'éloigne de la fréquence pour laquelle le transistor atteint la stabilité inconditionnelle (K = 1), ces formulations permettent une estimation du MAG à mieux que 1 dB et de sa fréquence de coupure à mieux que 10 %; ce qui permet l'utilisation de ces formules pour des composants de faible longueur de grille. L'intérêt de ces expressions réside dans l'étude des performances du composant en fonction des éléments du schéma équivalent afin de guider les évolutions technologiques des transistors.

#### II.3.1.2. Gain en courant de court circuit et fréquences de coupures

Le gain en courant à sortie court-circuitée  $|H_{21}|^2$  est obtenu par conversion des paramètres [S] en paramètres hybrides [H]. Son expression est donnée par la relation suivante :

$$|H_{21}|_{\text{ext}}^2 = \frac{-2S_{21}}{(1-S_{11})(1-S_{22})+S_{12}S_{21}}|_{\text{ext}}^2$$

On définit également la fréquence de coupure du gain en courant de court circuit comme étant la fréquence pour laquelle  $|H_{21}|^2 = 0$  dB. Elle s'obtient en traçant l'évolution de  $|H_{21}|^2$  en décibels en fonction de la fréquence en coordonnées logarithmiques. Ce gain, ainsi que sa fréquence de coupure, sont déterminés à partir des paramètres [S] mesurés et représentent des quantités extrinsèques. On peut cependant être amené à vouloir comparer des quantités intrinsèques et s'affranchir des éléments d'accès et se rapprocher ainsi plus près de la partie active du transistor [5]. On exprime alors le gain en courant de court circuit intrinsèque à partir des éléments du schéma équivalent électrique par la relation :

$$|H21|_{int}^2 = \frac{gm^2}{\omega^2(Cgs + Cgd)^2}$$

Toutefois, il est nécessaire de remarquer que le schéma équivalent localisé du transistor à effet de champ utilisé pour établir cette expression néglige l'effet de la résistance de contre réaction Rgd située entre les électrodes de grille et de drain [6]. Cette approximation, valable pour des composants fonctionnant à des fréquences allant jusque quelques dizaines de gigahertz, l'est beaucoup moins aux fréquences millimétriques où l'on ne peut plus négliger l'influence de cette résistance. Rappelons l'expression de la fréquence de coupure intrinsèque du gain en courant de court circuit :

$$F_T = \frac{gm}{2\pi(Cgs + Cgd)}$$

#### II.3.1.3. Gain unilatéral

Le gain unilatéral U est obtenu lorsque le transistor est neutrodyné. Le neutrodynage consiste à compenser l'effet du paramètre S<sub>12</sub> par des circuits passifs et sans perte. Il est alors possible d'obtenir un gain en puissance supérieur au MAG. Cependant, le neutrodynage est de plus en plus difficile à réaliser aux fréquences élevées avec des transistors à effet de champ car il est quasiment impossible de compenser les éléments Rgd et Cgd avec des circuits passifs et sans perte. Ce gain reste cependant utilisé comme critère d'évaluation des performances des transistors. Son expression en fonction des paramètres [S] est la suivante :

$$U = \frac{1}{2} \frac{\left| \frac{S_{21}}{S_{12}} - 1 \right|^2}{K \left| \frac{S_{21}}{S_{12}} \right| - Re \left( \frac{S_{21}}{S_{12}} \right)}$$

#### II.3.2. Les critères d'évaluations en fonctionnement non linéaire

Tant que la puissance de sortie du transistor évolue linéairement avec le niveau de puissance à son entrée, le fonctionnement du composant est dit linéaire. C'est le cas de l'amplification faible bruit où les niveaux de puissance à l'entrée des composants

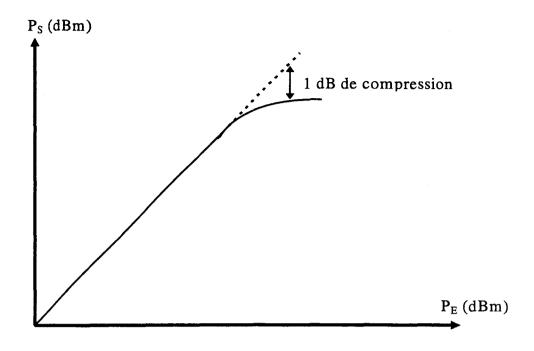

Figure I.6 : Evolution typique de la puissance de sortie en fonction de la puissance d'entrée d'un amplificateur.

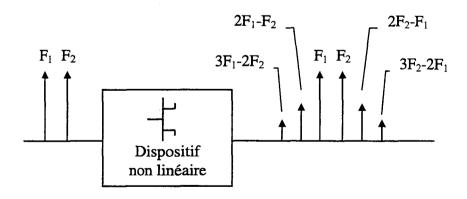

Figure I.7: Schématisation de l'effet d'intermodulation entre deux signaux

sont faibles. Par contre, lorsque les puissances appliquées à l'entrée du composant deviennent trop importantes, les mécanismes de non linéarités se mettent à intervenir et entraînent progressivement une réponse en puissance hors de la linéarité. Dans ces conditions, les paramètres [S] petit signal n'ont plus qu'une correspondance lointaine avec la réalité. Ceci résulte de la génération de composantes aux fréquences harmoniques qui ôtent sa validité au formalisme des paramètres [S], formalisme qui repose sur un fonctionnement uniquement à la fréquence fondamentale. On définit alors d'autres critères que nous allons décrire dans les parties qui suivent.

#### II.3.2.1. Point à 1 dB de compression

La puissance de sortie d'un transistor est classiquement mentionnée à deux valeurs particulières de celle-ci :

la première est la puissance de sortie obtenue pour la valeur de 1 dB de compression du gain en puissance. Cette valeur s'obtient à partir du tracé de la caractéristique représentant l'évolution de la puissance de sortie du transistor en fonction de la puissance d'entrée qui lui est appliquée. On obtient alors la puissance de sortie à 1 dB de compression du gain en puissance lorsque le gain a diminué de 1 dB par rapport au gain de la zone linéaire (figure I.6).

La seconde puissance usuellement mentionnée est la puissance maximale obtenue en sortie du transistor qui peut être obtenue pour plusieurs décibels de compression du gain. Elle se nomme également puissance de saturation.

#### II.3.2.2. Intermodulation d'ordre 3

L'intermodulation résulte de l'interférence de deux signaux de fréquences voisines injectées à l'entrée d'un dispositif non linéaire. Le transistor, par l'intermédiaire de ses non linéarités, va générer en sortie des signaux aux fréquences fondamentales  $F_1$  et  $F_2$  mais également à d'autres fréquences (figure I.7). Ces fréquences résultent du développement polynomial des non linéarités du transistor et en particulier du générateur de courant. Les composantes au premier ordre seront les fréquences fondamentales  $F_1$  et  $F_2$ , au second ordre, les termes en  $2F_1$ ,  $2F_2$ ,  $F_1+F_2$ , et  $F_2-F_1$ , et au troisième ordre les termes en  $3F_1$ ,  $3F_2$ ,  $2F_1+F_2$ ,  $2F_1-F_2$ ,  $2F_2+F_1$ ,  $2F_2-F_1$ .

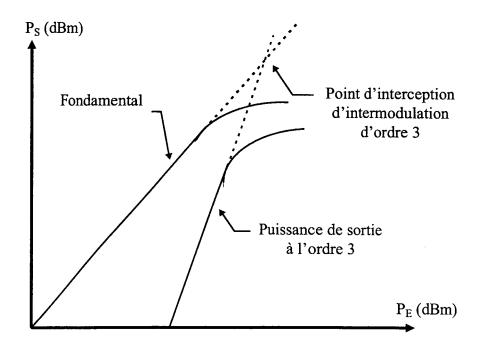

Figure I.8 : Détermination du point d'interception d'intermodulation d'ordre 3

Les termes du second ordre peuvent être aisément supprimés par filtrage dans la plupart des systèmes, et les termes supérieurs à l'ordre 3 sont en général de très faible amplitude. Par contre, les termes du  $3^e$  ordre en  $2F_1$ - $F_2$  et  $2F_2$ - $F_1$  risquent de se trouver contenus dans la bande passante du dispositif et ne pourront pas être supprimés par filtrage. Pour quantifier la linéarité du dispositif, on utilise alors le rapport d'intermodulation  $\frac{C}{I}$  (pour  $\frac{\text{carrier}}{\text{intermodulation}}$ ) qui traduit l'écart de puissance contenue entre les raies d'ordre 3 et les raies à la fréquence fondamentale, pour un point de fonctionnement donné :

$$\left(\frac{C}{I}\right)_{dB_c} = 10 \log \left(\frac{P_{S1}}{P_{S3}}\right)$$

pour une puissance injectée identique pour les 2 raies fondamentales.  $P_{S1}$  est la puissance de sortie mesurée à l'une des fréquences fondamentales et  $P_{S3}$  la puissance de sortie mesurée sur l'une des raies d'ordre 3.

On peut également caractériser l'intermodulation par son point d'interception d'ordre 3 appelé IP<sub>3</sub>. Il s'obtient en traçant les caractéristiques linéaires extrapolées des évolutions des puissances de sortie du dispositif en fonction de la puissance d'entrée, à la fréquence fondamentale ainsi qu'à l'ordre 3. Le point fictif d'intersection, où le prolongement des réponses linéaires du fondamental et du 3<sup>e</sup> ordre se croisent, caractérise l'IP<sub>3</sub> [7] (figure I.8). Ce point, indépendant de la puissance d'entrée, constitue un critère de qualité pratique pour caractériser le degré de linéarité d'un amplificateur.

#### II.3.2.3. Rendement en puissance ajoutée et classes de fonctionnement

Le concept de rendement traduit l'aptitude du transistor à transformer l'énergie continue apportée par les alimentations en énergie hyperfréquence. Le bilan des puissances entrantes et sortantes de l'amplificateur peut s'écrire :

$$P_E + P_{DC} = P_S + P_{dis}$$

où:

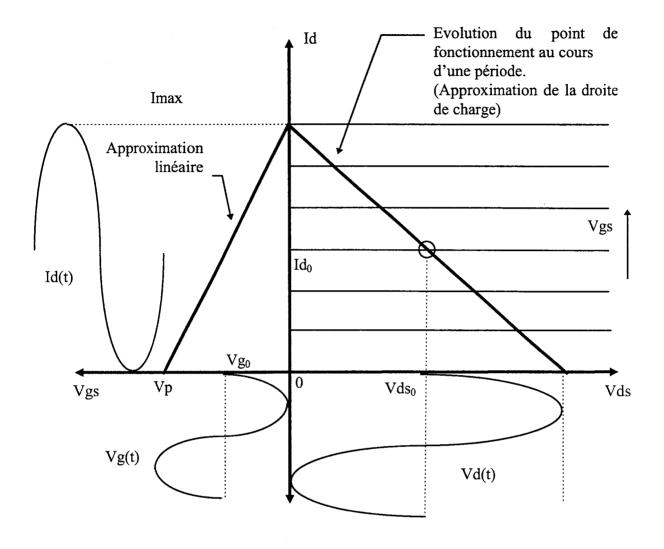

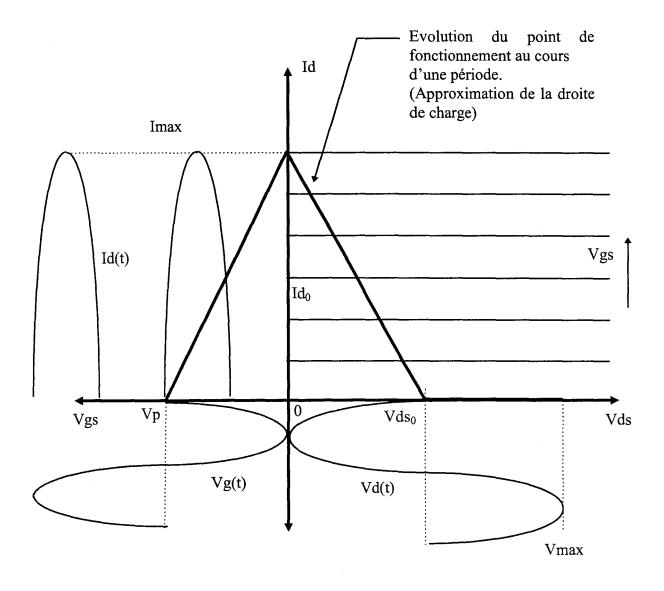

Figure I.9: Représentation des signaux disponibles en classe A

$P_E$  est la puissance hyperfréquence absorbée en entrée de l'amplificateur,  $P_S$  la puissance hyperfréquence absorbée par la charge,  $P_{DC}$  la puissance continue fournie par l'alimentation et  $P_{dis}$  la puissance dissipée par l'amplificateur.

Le rendement le plus couramment utilisé est le rendement en puissance ajoutée qui prend en considération le bilan des puissances appliquées à l'amplificateur. On le définit par les relations suivantes :

$$\eta_{PAE} = \frac{Ps - PE}{PDC} = \frac{Ps}{PDC} \left( 1 - \frac{1}{GP} \right) = 1 - \left( \frac{Pdis}{PDC} \right)$$

où G<sub>P</sub> est le gain en puissance de l'amplificateur.

Le terme

$$\frac{P_S}{P_{DC}}$$

est aussi appelé rendement drain de l'amplificateur.

Le rendement en puissance ajoutée dépend de la puissance continue fournie par l'alimentation, donc du point de polarisation du transistor. Ce point, appelé aussi point de repos, est également utilisé pour définir les classes de fonctionnement du transistor :

- ✓ En classe A, le transistor est polarisé à la moitié de son courant maximum, les signaux de commande et de sortie sont sinusoïdaux. Le rendement drain maximum est de 50 % pour une approximation linéaire du courant. Cette classe de fonctionnement est particulièrement bien adaptée aux applications nécessitant une puissance de sortie ainsi qu'un gain important. Une représentation des signaux disponibles sur le transistor pour cette classe de fonctionnement est donné figure I.9.

- ✓ En classe B, le point de repos se situe au pincement du transistor. Le composant ne conduit que durant une demi alternance ce qui permet un rendement drain maximum théorique de 78.5 %. Cette classe de fonctionnement permet d'obtenir un rendement supérieur mais pour une puissance d'entrée injectée au composant identique à celle du fonctionnement en classe A, la puissance de sortie sera deux fois plus faible. Le point de polarisation choisi dépendra du type d'application envisagée. L'amplification de puissance en classe B conviendra aux applications demandant une faible

Figure I.10: Représentation des signaux disponibles en classe B

consommation ainsi qu'un rendement élevé. Une représentation des signaux disponibles sur le transistor pour cette classe de fonctionnement est donnée figure I.10.

✓ La classe AB correspond à un état intermédiaire entre les deux classes précédemment citées. Elle permet d'obtenir un compromis entre la puissance de sortie, le gain et le rendement.

Ces classes de fonctionnement sont actuellement les seules à être utilisées aux fréquences millimétriques. Les autres classes de fonctionnement, comme la classe C ou F ne sont utilisées jusqu'à aujourd'hui que pour des applications autour de la bande X, c'est pourquoi nous n'en parlerons pas ici.

#### II.3.2.4. Conversion AM-AM et AM-PM

Lorsque le gain d'un quadripôle est dépendant de l'amplitude de la puissance injectée à l'entrée de celui-ci, le phénomène de conversion AM-AM (AM pour modulation d'amplitude) peut apparaître. De même, si l'écart de phase produit à travers un quadripôle est dépendant de la puissance injectée à l'entrée du quadripôle, le phénomène de conversion AM-PM (PM pour modulation de phase) peut également apparaître [8]. La distorsion AM-AM en hyperfréquence se caractérise par la déviation du gain du quadripôle par rapport à sa valeur mesurée en petit signal. On définit alors un coefficient de conversion AM-AM par la relation :

$$k_{AM-AM} = \frac{dGP}{dPE}$$

avec

$$\begin{cases} G_P: \text{ gain en puissance} \\ P_E: \text{ puissance d'entrée aborbée} \end{cases}$$

La distorsion en phase est caractérisée par un décalage de la phase entre l'entrée et la sortie du quadripôle par rapport à un décalage de phase de référence déterminé pour un fonctionnement en petit signal et une impédance de charge donnée. Ce coefficient de distorsion AM-PM s'exprime par le rapport entre la dérivée de cet écart de phase  $\Phi$  et la dérivée de la puissance d'entrée [9].

$$k_{AM-PM} = \frac{d\Phi}{dP_E}$$

Pour réduire la consommation des téléphones portables, les amplificateurs de puissance opèrent parfois près de la zone de saturation afin d'obtenir un rendement important. Dans ces conditions de fonctionnement, les distorsions en amplitude et en phase augmentent de façon significative, accentuant les interférences entre les canaux adjacents. On utilise alors pour atténuer ces distorsions des compensateurs de linéarisation [10].

#### III. Stabilité des transistors

L'étude de la stabilité est un point important dans la phase de conception de tout amplificateur. Le concepteur aura en charge durant cette phase de stabiliser l'amplificateur dans une gamme de fréquences allant du continu à la fréquence de travail, voire jusqu'aux harmoniques 2, 3... afin d'éviter que les impédances présentées au transistor n'entraînent son entrée en oscillation et ne le détruisent. Nous étudierons dans la première partie la stabilité des transistors, puis dans la seconde, nous verrons différentes techniques utilisées pour les stabiliser.

# III.1. Les critères de stabilité

#### III.1.1. Le coefficient de stabilité K

Le coefficient de stabilité K, encore appelé coefficient de Rollet [11], est le critère le plus utilisé par les concepteurs de circuits pour étudier la stabilité des quadripôles linéaires. Son expression, déjà définie dans la partie II.2.1. de ce chapitre, s'exprime en fonction des paramètres [S] de la façon suivante :

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{12}S_{21}|} \quad \text{avec} \quad \Delta = S_{11}S_{22} - S_{12}S_{21}$$

Le quadripôle sera dit inconditionnellement stable si et seulement si les deux conditions suivantes sont remplies :

$$\begin{cases} K > 1 \\ |\Delta| < 1 \end{cases} \quad \text{pour toutes les fréquences}$$

Notons que la condition  $|\Delta| < 1$  peut être exprimée sous des formes équivalentes soit :

$$B_1 > 0$$

avec  $B_1 = 1 + |S_{11}|^2 - |S_{22}|^2 - |\Delta|^2$

ou encore

1 -

$$|S_{ii}|^2 > |S_{ij}S_{ji}|$$

avec  $i = 1, 2$  et  $i \neq j$ .

Le coefficient de stabilité peut également être exprimé dans le formalisme des paramètres Z, Y ou H, où il prend une forme identique :

$$K = \frac{2Re(\gamma_{11})Re(\gamma_{22}) - Re(\gamma_{12}\gamma_{21})}{|\gamma_{12}\gamma_{21}|} \quad \text{avec} \quad \gamma = z, y \text{ ou } h$$

La stabilité est alors inconditionnelle si et seulement si :

$$\begin{cases} K > 1 \\ Re(\gamma_{11}) > 0 \\ Re(\gamma_{22}) > 0 \end{cases}$$

Lorsque le quadripôle est inconditionnellement stable, il ne pourra pas osciller, quelles que soient les impédances passives qui pourraient lui être présentées en entrée ou en sortie. On peut également calculer les impédances optimales  $\Gamma_{\text{Lopt}}$  et  $\Gamma_{\text{Sopt}}$  à présenter au composant de manière à réaliser le MAG à la fréquence de travail. Durant la phase de conception d'un amplificateur, on s'efforcera de réaliser les conditions K > 1 et  $|\Delta| < 1$  dans la gamme de fréquence allant du continu à la fréquence de travail, et de manière plus générale jusqu'à ce que l'amplificateur n'ait plus de gain.

Lorsque le coefficient de stabilité est inférieur à l'unité, la stabilité du quadripôle est dite conditionnelle et l'étude de sa stabilité nécessite celle des cercles de stabilité.

#### III.1.2. Les cercles de stabilité

Lorsque le coefficient de stabilité K est inférieur à l'unité, l'étude de la stabilité du transistor est conditionnelle. Il est alors nécessaire de vérifier pour chaque fréquence où K < 1 si les impédances présentées en entrée et en sortie du transistor ne vont pas entraîner son instabilité. Ceci s'effectue à partir de l'étude des cercles de stabilité.

Dans le formalisme des paramètres [S], un système devient instable lorsque  $|S'_{11}| > 1$  ou  $|S'_{22}| > 1$ . La limite de la stabilité est alors obtenue pour des valeurs de  $|S'_{11}|$  ou  $|S'_{22}|$  égales à l'unité.

Nous avons vu dans la partie II.2.1. de ce chapitre que le coefficient de réflexion présenté par l'entrée du transistor lorsqu'il est chargé en sortie par une impédance  $Z_L$  peut s'exprimer par :

$$S'_{11} = S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1-S_{22}\Gamma_L}$$

A la limite de stabilité, nous avons donc  $|S'_{11}| = 1$  soit :

$$|S'_{11}| = |S_{11}| + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L}| = 1$$

Cette expression représente dans l'abaque de Smith un cercle de rayon  $|R_L|$  et de centre  $C_L$  tel que :

$$|R_L| = \frac{|S_{12}S_{21}|}{|S_{22}|^2 - |\Delta|^2}$$

$C_L = \frac{S_{22}^* - \Delta^*S_{11}}{|S_{22}|^2 - |\Delta|^2}$

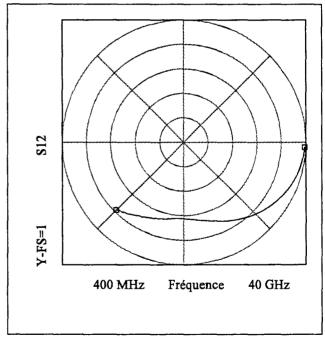

Il est ensuite nécessaire de déterminer si la zone de stabilité se trouve à l'intérieur ou à l'extérieur de ce cercle. Une méthode simple et rapide consiste à

Figure I.11: Lieu des impédances de source pour les fréquences de 5 GHz, 15 GHz, 25 GHz, 35 GHz, et 45 GHz entraînant une instabilité en sortie du transistor. La zone d'instabilité est à l'intérieur des cercles.

(InP HEMT  $2 \times 50$  µm, réalisé au laboratoire : Vds = 2 V ; Vgs = 0V)

considérer le cas particulier où  $\Gamma_L = 0$ , point représentant le centre de l'abaque de Smith. Ce point sera situé dans la zone de stabilité si  $|S'_{11}| = |S_{11}| < 1$ .

Un raisonnement analogue peut être appliqué pour la sortie. Le coefficient de réflexion présenté par la sortie du transistor lorsqu'il est chargé en entrée par une impédance  $Z_S$ , de coefficient de réflexion  $\Gamma_S$ , s'exprime par :

$$S'_{22} = S_{22} + \frac{S_{12}S_{21}\Gamma_S}{1 - S_{11}\Gamma_S}$$

A la limite de stabilité, l'étude du cas  $|S'_{22}| = 1$  permet d'établir l'équation d'un cercle de centre  $C_S$  et de rayon  $|R_S|$  définie par :

$$|R_S| = \frac{|S_{12}S_{21}|}{|S_{11}|^2 - |\Delta|^2}$$

$C_S = \frac{S_{11}^* - \Delta^*S_{22}}{|S_{11}|^2 - |\Delta|^2}$

Afin de déterminer si la zone de stabilité se trouve à l'intérieur ou à l'extérieur du cercle, on étudiera alors le cas particulier où  $\Gamma_S = 0$ .

Nous pouvons remarquer que la stabilité en entrée du transistor va dépendre uniquement de la charge qui lui sera présentée en sortie. De même, la stabilité en sortie du transistor va dépendre uniquement de valeur de la charge qui lui sera présentée en entrée. A titre d'exemple, nous présentons sur la figure I.11, le lieu des impédances d'entrée qui vont entraîner une instabilité en sortie d'un composant de développement 2×50 µm réalisé sur substrat InP pour les fréquences particulières de 5 GHz, 15 GHz, 25 GHz, 35 GHz et 45 GHz. Nous constatons que le transistor est inconditionnellement stable pour la fréquence de 45 GHz car le cercle d'instabilité est situé à l'extérieur de l'abaque de Smith de rayon unité.

Malheureusement, toutes ces considérations ne sont valables que dans le formalisme des paramètres [S], c'est à dire lorsque l'on ne considère qu'un seul mode de propagation ainsi qu'un niveau de puissance suffisamment faible pour demeurer en régime de fonctionnement linéaire. C'est pourquoi, nous allons nous intéresser dans la partie suivante aux limitations du coefficient de stabilité K.

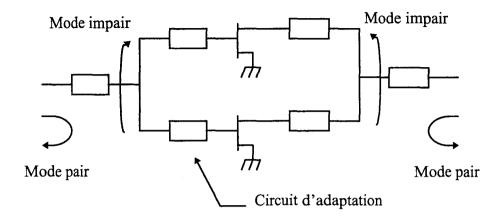

Figure I.12 : Schématisation de la localisation de l'apparition du mode impair dans un circuit à deux transistors.

#### II.1.3. Validité d'utilisation du coefficient de stabilité

L'analyse de la stabilité des amplificateurs de puissance ou d'oscillateur est une préoccupation importante pour tout concepteur. Plusieurs auteurs, à travers leurs publications, font remarquer que le coefficient de stabilité K, classiquement utilisé, n'est pas suffisant pour prédire la stabilité des quadripôles linéaires [12], [13], [14]. La stabilité d'un quadripôle linéaire est déterminée par les coefficients vus à l'entrée ainsi qu'à la sortie de celui-ci. Il sera inconditionnellement stable si les conditions K > 1 et la condition auxiliaire  $|\Delta| < 1$  sont vérifiées. Toutefois, ces auteurs ajoutent que ces conditions ne sont valables que si elles sont accompagnées d'une condition supplémentaire. Cette condition stipule que le quadripôle non chargé ne doit pas posséder de pôles à partie réelle positive, c'est à dire de pôles situés dans le demi plan droit du plan complexe. Platzker [12] propose une définition plus complète du critère de stabilité d'un quadripôle linéaire : "un quadripôle non chargé qui ne possède aucun pôle dans le demi plan complexe droit sera rendu stable lorsqu'il sera chargé de manière externe à son entrée et à sa sortie si et seulement si les deux conditions K > 1 et  $|\Delta| < 1$  sont vérifiées pour toutes les fréquences."

L'étude de la stabilité reposant uniquement sur les deux conditions K > 1 et  $|\Delta| < 1$  a été mise en défaut pour les amplificateurs de puissance composés de plusieurs transistors placés en parallèle. Pour de telles configurations, plusieurs auteurs montrent que pour des circuits MMIC de puissance comportant deux ou quatre transistors en parallèle, les deux conditions classiquement utilisées lorsqu'elles sont vérifiées ne sont plus suffisantes puisqu'il y a apparition d'oscillations dans leurs circuits [15], [16]. Ces oscillations sont engendrées par l'apparition de mode de propagation impair appelé également push-pull mode entre les transistors (figure I.12).

De manière générale, n modes peuvent exister quand n transistors sont associés : un mode pair et n-1 modes impairs.

Freitag [13] propose une méthode pour tester la stabilité des circuits basée sur l'étude des paramètres Z lorsque l'on va scinder le circuit. Toutefois, cette méthode n'est applicable qu'à une configuration de circuit symétrique (2, 4, 8 transistors ...) [17].

Platzker [12], quant à lui, propose une méthode basée sur la généralisation du critère de Bode et de la définition du "Return Ratio". Des études menées à l'université de Limoges tentent d'étendre cette définition à l'étude de la stabilité en régime de fonctionnement non linéaire [14].

L'étude de la stabilité des amplificateurs de puissance multi-étages suscite beaucoup d'intérêts car le simple critère K > 1 a montré ses limites. Il est cependant nécessaire d'ajouter que les méthodes citées deviennent vite très lourdes lorsque beaucoup d'étages sont associés et ne sont actuellement pas introduites dans les simulateurs commerciaux.

# III.2. Les méthodes de stabilisation

Lors de toute conception d'amplificateur, le concepteur cherchera à rendre inconditionnellement stable son circuit. Dans ce paragraphe, nous allons décrire brièvement les méthodes habituellement utilisées pour stabiliser un transistor. Comme nous l'avons vu dans la partie précédente, l'étude de la stabilité des amplificateurs multi-étages nécessitera une fois ces conditions remplies une étude supplémentaire globale du circuit. Ce paragraphe se décompose en deux parties : dans la première, nous étudierons le cas où le transistor est instable à la fréquence de travail, et dans la seconde, les techniques utilisées pour le stabiliser à toutes les autres fréquences.

# III.2.1. Stabilisation à la fréquence de travail

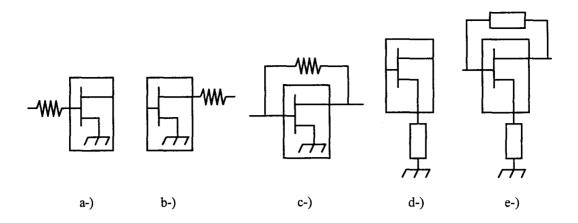

Lors de la phase de stabilisation d'un transistor, la première démarche est de vérifier s'il est ou non inconditionnellement stable à la fréquence de travail. S'il est instable, il faudra dans un premier temps le stabiliser autour de cette fréquence. Pour cela, il va falloir "brider" le composant en ajoutant des éléments passifs au transistor afin d'augmenter son coefficient de stabilité jusqu'à ce qu'il atteigne l'unité à la fréquence de travail. Dans la pratique, on se fixera plutôt un coefficient K # 2 afin de s'octroyer une marge liée à la dispersion technologique lors de la réalisation. Bien entendu, la principale conséquence de l'augmentation du coefficient de stabilité va être

Figure I.13 : Schématisation de diverses possibilités pour stabiliser un transistor en diminuant son gain

Figure I.14 : Circuits RLC utilisés pour polariser et stabiliser les montages amplificateurs en technologie MMIC aux fréquences millimétriques.

une diminution du gain du transistor. Des exemples typiques de stabilisation par adjonction d'éléments passifs sont donnés en figure I.13. Les cas a, b, et c, font intervenir un élément résistif pour stabiliser le transistor. Le principal inconvénient de ces méthodes réside dans une puissance dissipée importante dans les résistances ce qui se traduit par une baisse du rendement des circuits. Les cas e et d, font intervenir des éléments réactifs. Ils ne consommeront donc pas de puissance active et n'influenceront pas le rendement de l'amplificateur. A notre connaissance, le cas d qui consiste à placer une longueur de ligne dans la source du transistor est la plus utilisée pour stabiliser les amplificateurs en technologie MMIC en gamme millimétrique. L'ajout de cette longueur de ligne dans la source du transistor va se traduire par une augmentation de la quantité Ls du schéma équivalent localisé du transistor, terme fortement lié à la valeur du gain du transistor [18]. Un autre avantage de cette technique est un contrôle très précis de la valeur du coefficient de stabilité et du gain en fonction de la longueur de la ligne.

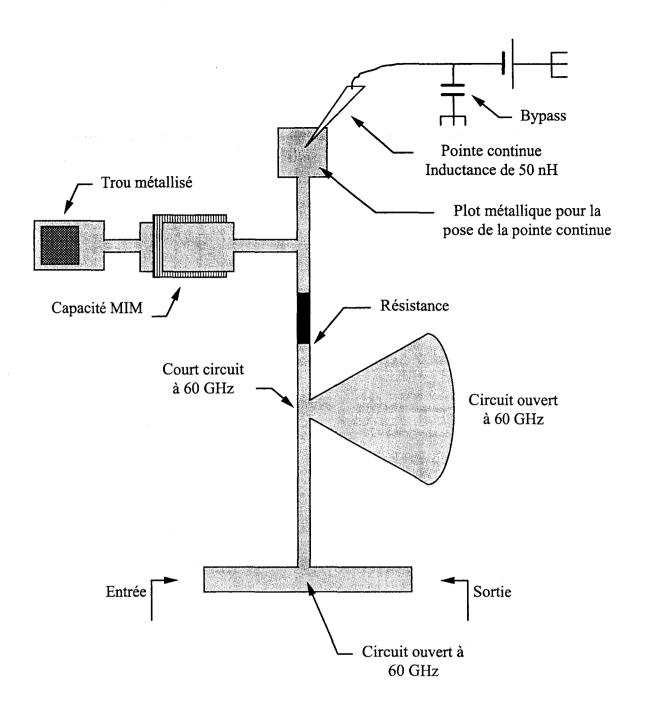

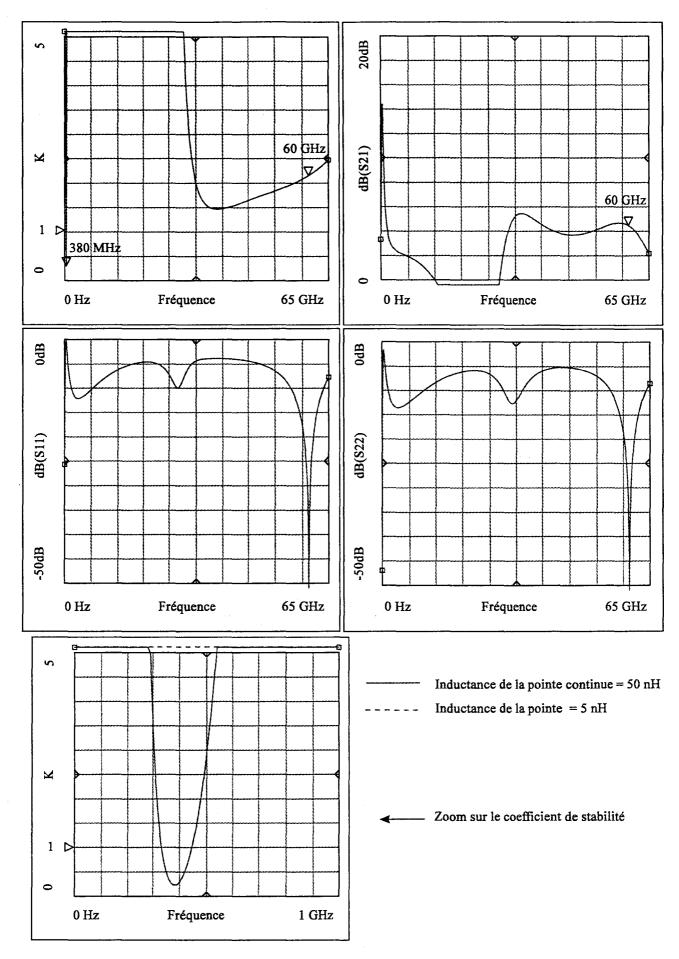

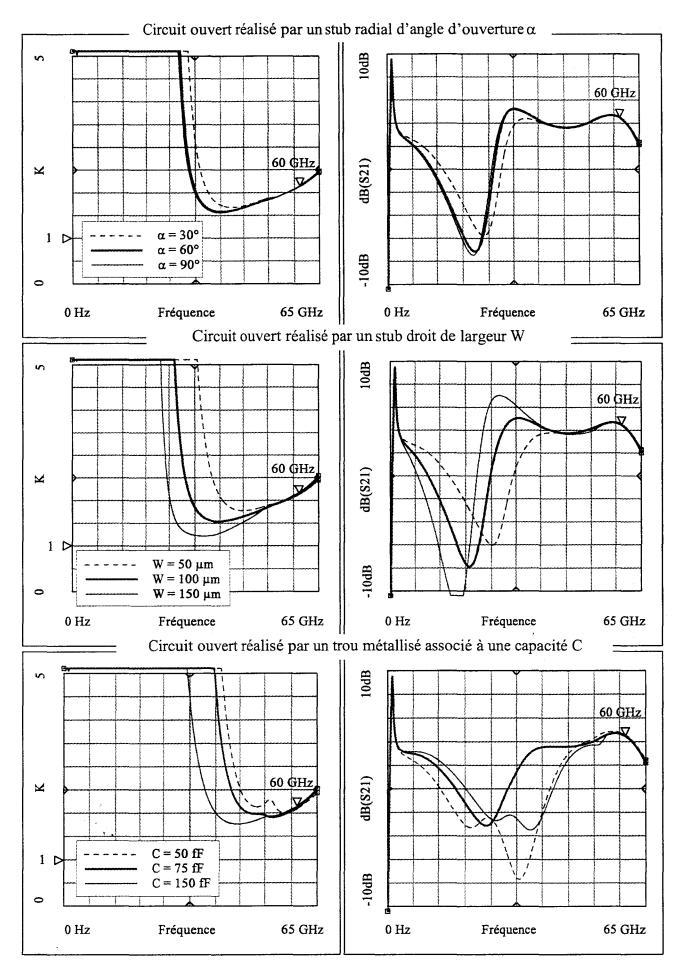

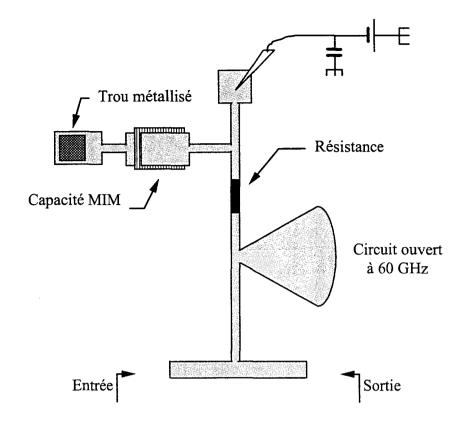

# III.2.2. Stabilisation hors de la bande de travail

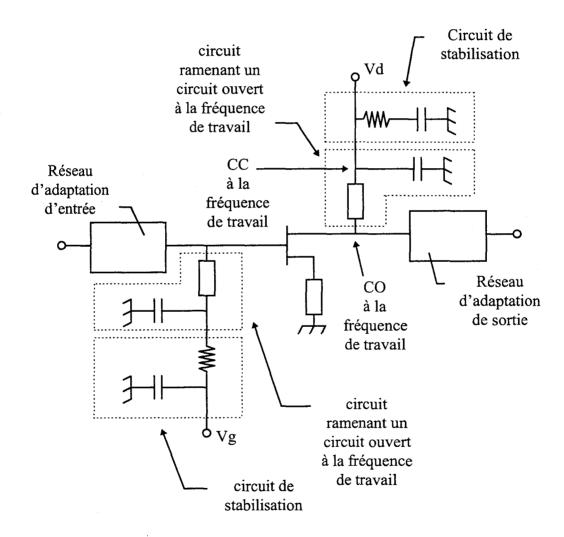

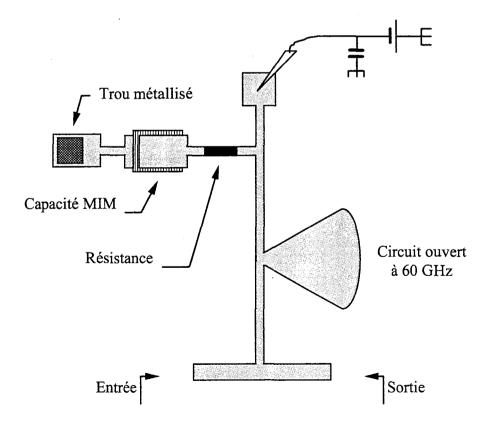

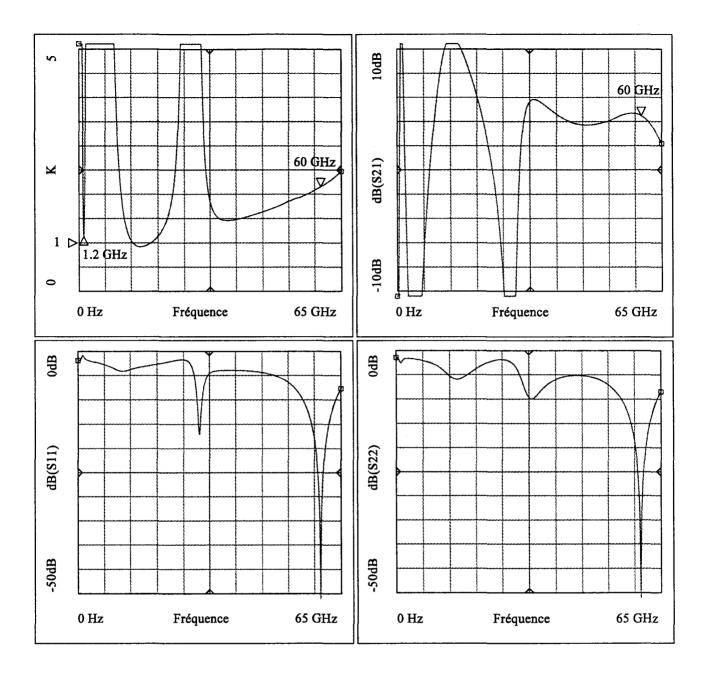

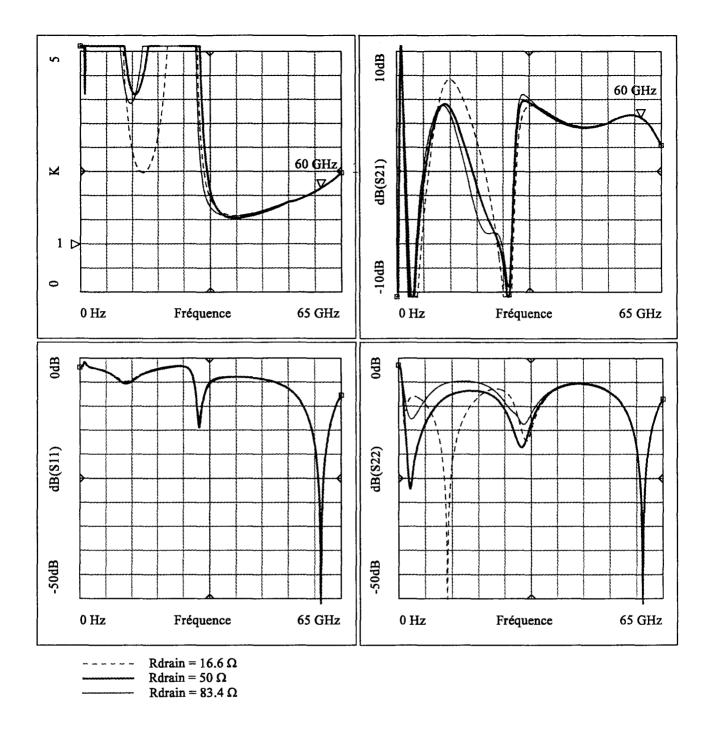

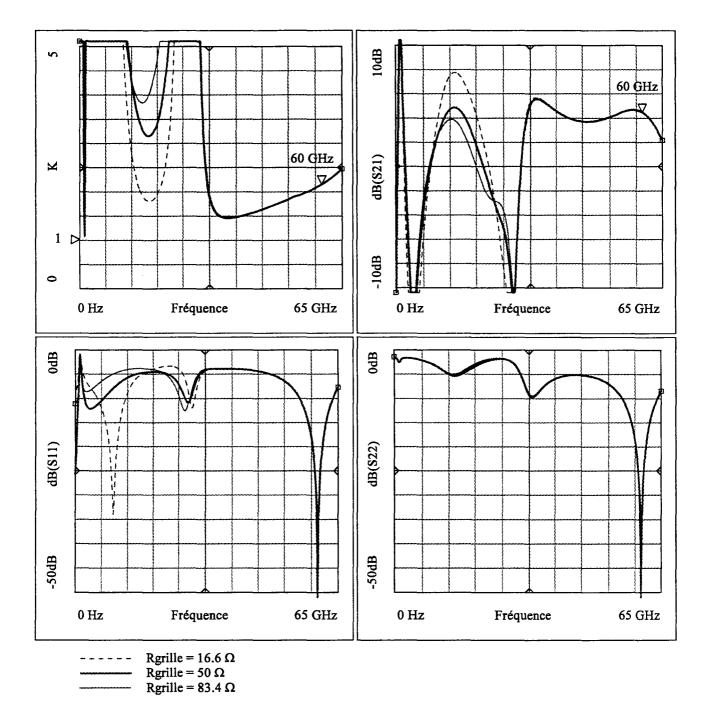

Une fois le transistor rendu stable à sa fréquence de travail, l'étape suivante de la conception de l'amplificateur va consister à rendre l'amplificateur inconditionnellement stable à toutes les fréquences. Le gain du transistor et l'étude de sa stabilité étant étroitement liés, rendre stable l'amplificateur va se résumer à diminuer le plus possible le gain du transistor afin de se prémunir de toute amplification d'éventuels parasites qui pourraient naître dans le circuit et engendrer l'apparition d'oscillations. Pour les circuits en technologie intégrée au delà de la bande X, la solution la plus répandue pour remplir cette fonction est l'utilisation de circuit RLC. Ces circuits permettent à la fois d'amener les tensions de polarisation aux transistors mais aussi de les rendre stables dans une large bande de fréquence. Ils permettent également d'obtenir des dimensions de circuit en accord avec la technologie MMIC où le coût est fortement lié à la surface du circuit. Un schéma typique de circuits RLC utilisé pour polariser un transistor est représenté figure I.14.

Il peut être décomposé en deux circuits distincts. Le premier aura en charge de ramener au niveau de l'entrée et de la sortie du transistor un circuit ouvert pour la fréquence de travail afin de rendre transparent le second circuit placé derrière. Ce second circuit, composé d'éléments capacitifs et résistifs, fera chuter le gain du montage hors de la bande de travail. Remarquons que la résistance est placée en série dans la grille puisqu'il n'y a pas de courant dans celle-ci alors qu'elle est placée en parallèle dans le drain, afin d'éviter une chute de tension à ses bornes et donc une modification du point de polarisation du transistor. La complémentarité des divers éléments constituant ce type de circuit en font un circuit performant pour polariser et stabiliser les amplificateurs en technologie MMIC et hybride en onde millimétrique. Dans le chapitre IV une description plus détaillée de la simulation et l'incorporation de ce type de circuit dans notre amplificateur sera effectuée.

# IV. Méthodes d'adaptation des transistors

Maintenant que nous avons évoqué les principales techniques utilisées pour stabiliser les transistors, nous allons nous intéresser à la partie suivante de la conception qui est leur adaptation. Cette étape va consister à concevoir le circuit passif permettant de présenter en entrée et en sortie du transistor les impédances optimales souhaitées. Nous verrons dans la première partie comment réaliser cette adaptation à partir de ligne de compensation ou "stub". Dans la seconde, nous utiliserons des lignes d'impédance caractéristiques différentes.

# IV.1. Transformateur à ligne de compensation

Les lignes de compensation ou "stub" en anglais sont des lignes terminées par un circuit ouvert ou un court circuit placées en parallèle sur la ligne principale. Elles permettent de réaliser une transformation d'impédance afin de procéder à l'adaptation du transistor. La transformation d'impédance, réalisée par des circuits passifs, permettra

Figure I.15 : Schématisation de la transformation d'impédance par lignes de compensation fermées.

Figure I.16: Schématisation du transformateur d'impédance à tronçon de ligne.

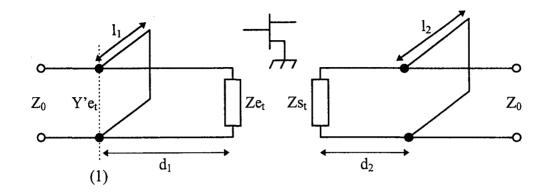

de transformer les impédances d'entrée  $Ze_t$  et de sortie  $Zs_t$  du transistor en l'impédance de référence  $Z_0$ , valant classiquement 50  $\Omega$  (figure I.15).

L'adaptation en entrée du transistor dépendra des longueurs de ligne d<sub>1</sub> et l<sub>1</sub> et en sortie des longueurs de ligne d2 et l2. Prenons l'exemple de l'entrée où l'admittance complexe du transistor peut s'écrire  $Ye_t = a_{et} + jb_{et}$ . La longueur de ligne  $l_1$  doit permettre d'obtenir dans le plan (1) l'admittance  $Y'e_t = 1 + jb_{et}$ . Ceci s'obtient en plaçant l'admittance Yet du transistor sur l'abaque de Smith et en se déplaçant à taux d'ondes stationnaires constant vers le générateur jusqu'à couper le cercle des parties réelles égales à l'unité. Deux solutions sont possibles permettant un choix parmi deux longueurs de lignes, l'une d'elle étant égale à la valeur de la ligne d<sub>1</sub>. Puis, partant du court circuit (cas de la figure I.15) ou du circuit ouvert sur l'abaque de Smith, on détermine la longueur de ligne l<sub>1</sub> qui compensera le terme +jbet de l'admittance Y'et. Cette admittance est égale à l'admittance conjuguée -jbet. On obtient ainsi une admittance ou une impédance résultante normalisée égale à l'unité soit 50  $\Omega$  dans notre système de référence. Cette technique très utilisée pour la conception de circuit en technologie MMIC permet de rapidement estimer de manière analytique ces longueurs, ceci afin de mieux les contrôler lors de l'optimisation du circuit sur le simulateur utilisé pour la conception.

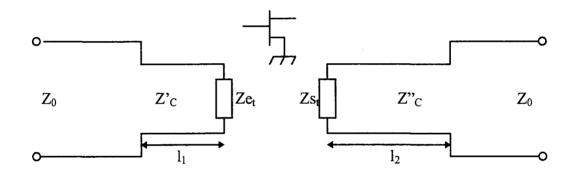

# IV.2. Adaptation par transformateur à tronçon de ligne

La transformation d'impédances est ici réalisée par juxtaposition de lignes d'impédances caractéristiques différentes (figure I.16). Comme pour la méthode précédente, il est possible de calculer analytiquement la valeur de l'impédance caractéristique  $Z'_C$  ainsi que la longueur de la ligne  $l_1$  nécessaire à la transformation de l'impédance d'entrée du transistor  $Ze_t$  en l'impédance de référence  $Z_0$ . Ces deux grandeurs s'obtiennent à partir des formulations suivantes :

$$tg(\beta l_1) = \frac{Z_C(Z_0 - Re_t)}{Z_0 X e_t} \qquad Z_C = \sqrt{Z_0 Re_t - \frac{X e_t^2 Z_0}{Z_0 - Re_t}}$$

avec

$$Ze_t = Re_t + jXe_t$$

et  $\beta = \frac{2\pi}{\lambda}$

# λ : longueur d'onde guidée

En guide de propagation microruban, l'impédance caractéristique de la ligne est fixée principalement par sa largeur pour une épaisseur de substrat donnée. Afin de diminuer le critère sélectif de l'adaptation et d'éviter les discontinuités trop importantes dues à des largeurs de ligne trop différentes, on peut faire appel à des sections quart d'onde d'impédance caractéristique progressive. Par contre, cela augmentera les dimensions du circuit donc également son coût. Cette technique d'adaptation est toutefois très utilisée par les concepteurs de circuits. Nous effectuerons dans le chapitre IV de ce manuscrit une comparaison de ces deux méthodes.

# V. Etat de l'art des transistors et amplificateurs de puissance à 60 GHz et 94 GHz

Avant de présenter les différents résultats de puissance relevés dans la littérature avec des transistors à effet de champ, nous allons tout d'abord décrire les différentes familles de composants utilisés pour l'amplification de puissance en gamme d'onde millimétrique.

# V.1. Les familles de transistors à effet de champ dédiées à l'amplification de puissance en gammes de fréquences millimétriques

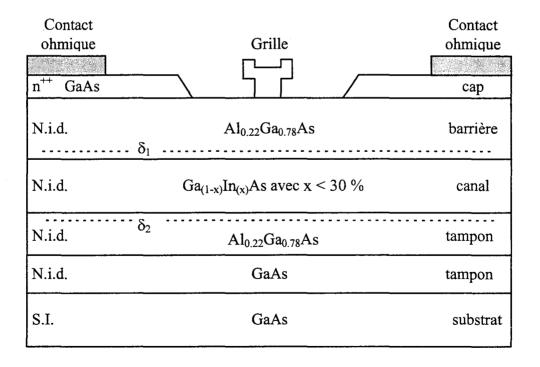

Figure I.17: Structure type du HEMT conventionnel sur substrat GaAs à 1 plan de dopage.

Figure I.18: Structure type du HEMT pseudomorphique sur substrat GaAs à 2 plans de dopages.

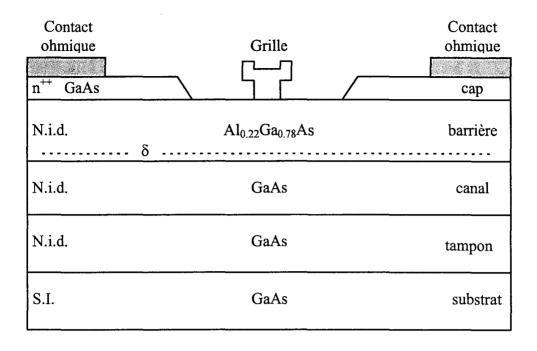

#### V.1.1. Le HEMT conventionnel sur substrat GaAs

Le HEMT conventionnel est réalisé à partir de l'hétérojonction AlGaAs/GaAs, les deux matériaux possédant les mêmes paramètres de maille. La barrière d'AlGaAs n'est pas dopée ce qui permet d'obtenir une bonne tenue en tension. Un ou deux plans de dopages sont classiquement introduits de par et d'autre du canal GaAs non dopé procurant une densité de courant importante. Sa structure est représentée figure I.17.

Ce type de composant n'est pas utilisé pour l'amplification de puissance en bande V parce que dépassé par les performances du HEMT pseudomorphique sur substrat GaAs, mais nous l'avons tout de même présenté afin qu'il lui serve d'introduction.

# V.1.2. le HEMT pseudomorphique sur substrat GaAs

Dans ce type de structure, le canal GaAs est ici remplacé par un canal  $In_xGa_{(1-x)}As$ . Ce matériau offre à la fois de meilleures propriétés de transport ainsi qu'une hauteur de barrière supérieure permettant un meilleur confinement des porteurs dans le puits. Mais, la taille de la maille cristalline de la couche d'InGaAs étant différente de celle du GaAs, la couche d'InGaAs sera contrainte ce qui limitera son épaisseur. Celle ci sera d'autant plus faible que le taux d'indium sera élevé. Une valeur typiquement rencontrée est une épaisseur de 150 Å pour 22 % d'indium dans la couche InGaAs. La structure d'un transistor PHEMT sur substrat GaAs avec deux plans de dopage est présentée figure I.18.

Le PHEMT sur substrat GaAs est un composant qui a démontré d'excellentes performances pour les applications de puissance en bande V. Ce type de structure a permis à la société TRW d'obtenir l'état de l'art en terme de puissance de sortie en 1993 avec 225 mW sur un transistor de développement total de grille de 450 µm à la fréquence de 60 GHz [19].

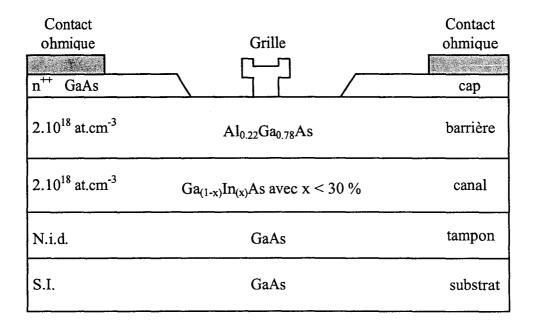

#### V.1.3. Le HFET sur GaAs à canal dopé

La principale différence entre le PHEMT sur substrat GaAs et le HFET sur substrat GaAs concerne le canal. Pour le PHEMT, comme nous l'avons vu, la réserve

Figure I.19: Structure type d'un HFET mono-canal sur substrat GaAs.

Figure I.20: Structure type d'un HEMT conventionnel sur substrat InP à un plan de dopage.

d'électrons constituée par les plans de dopages est séparée du canal InGaAs non dopé. Pour le HFET le dopage est volumique et est situé dans le canal comme dans la barrière. Historiquement, cette structure est plus ancienne que le PHEMT sur substrat GaAs mais des densités de puissance très importantes ont été obtenues avec ce type de structure. La barrière de 1 W/mm de développement de grille a été obtenue avec une structure à deux canaux par la société Texas Instrument en 1989 à 60 GHz [20]. La structure typique d'un transistor HFET composé d'un seul canal est présenté figure I.19.

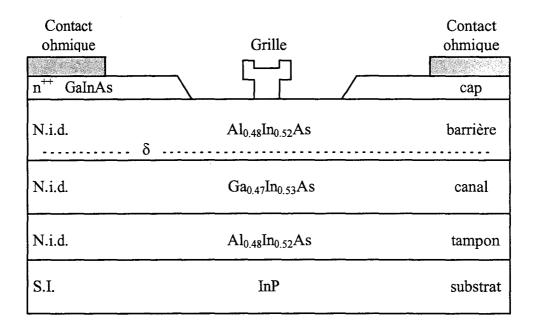

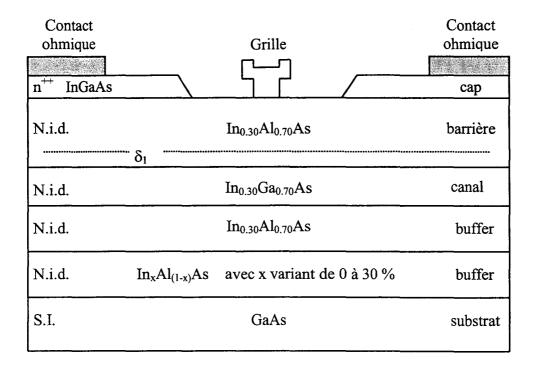

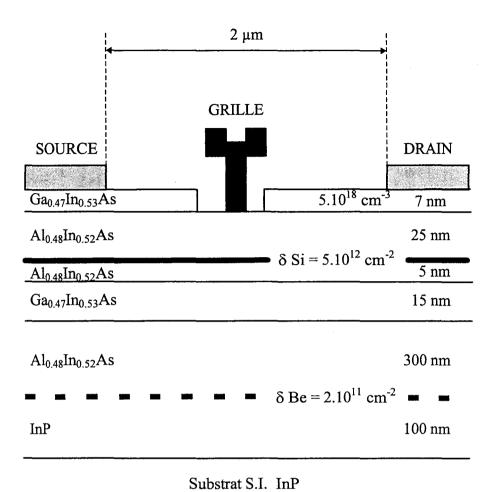

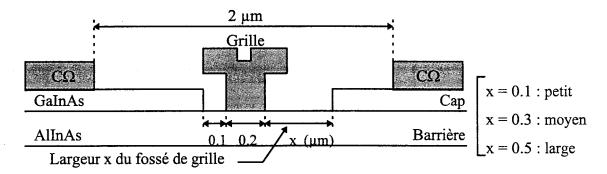

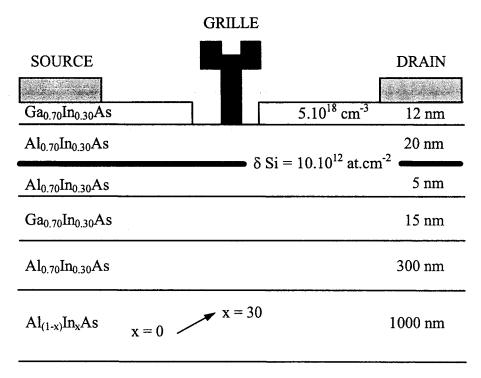

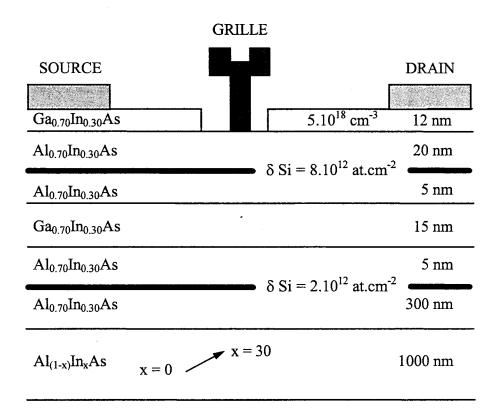

#### V.1.3. Le HEMT conventionnel sur InP

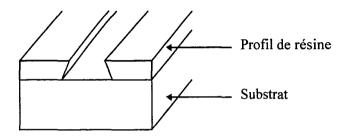

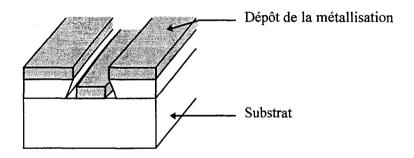

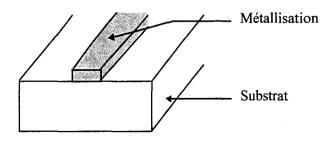

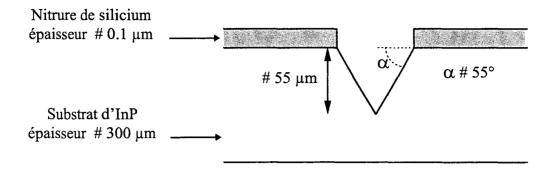

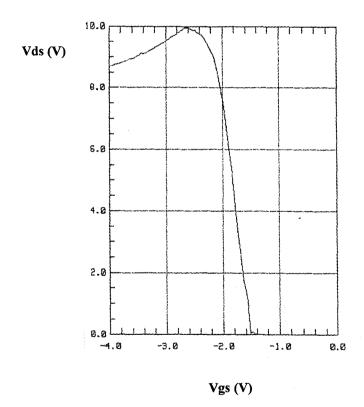

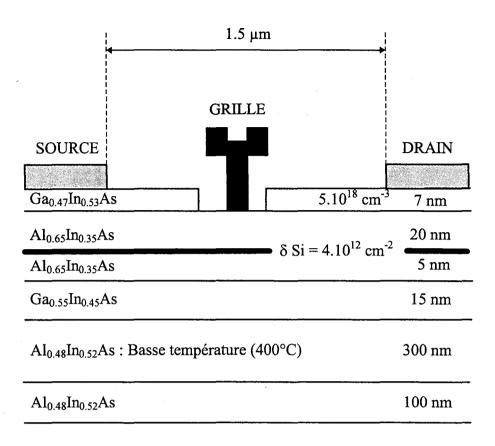

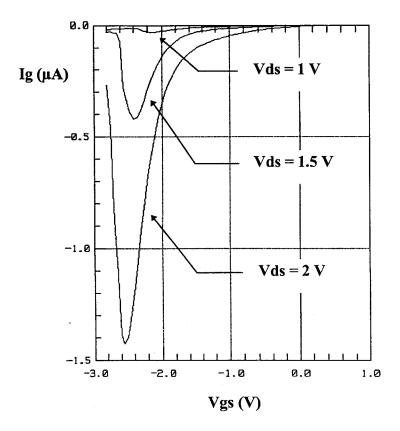

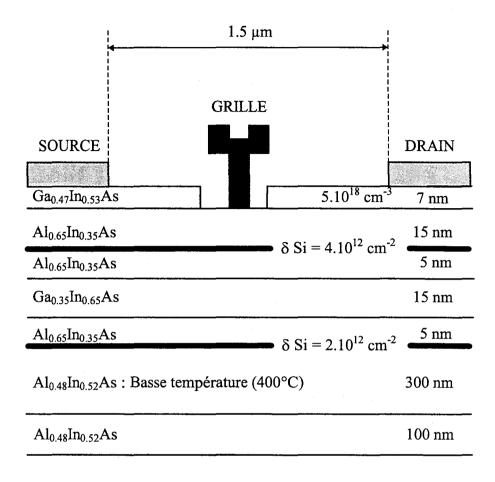

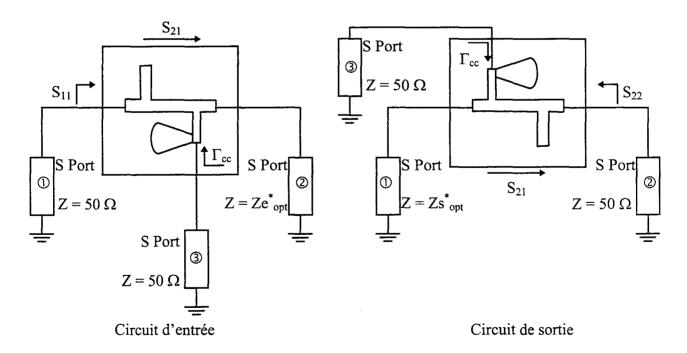

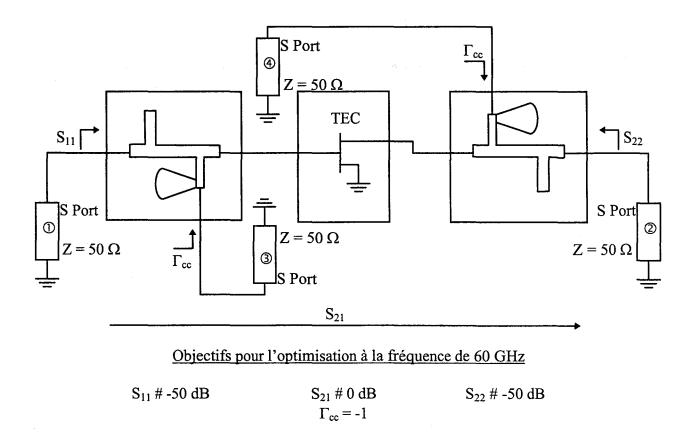

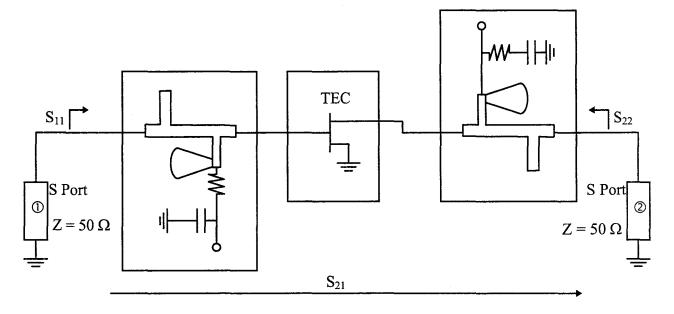

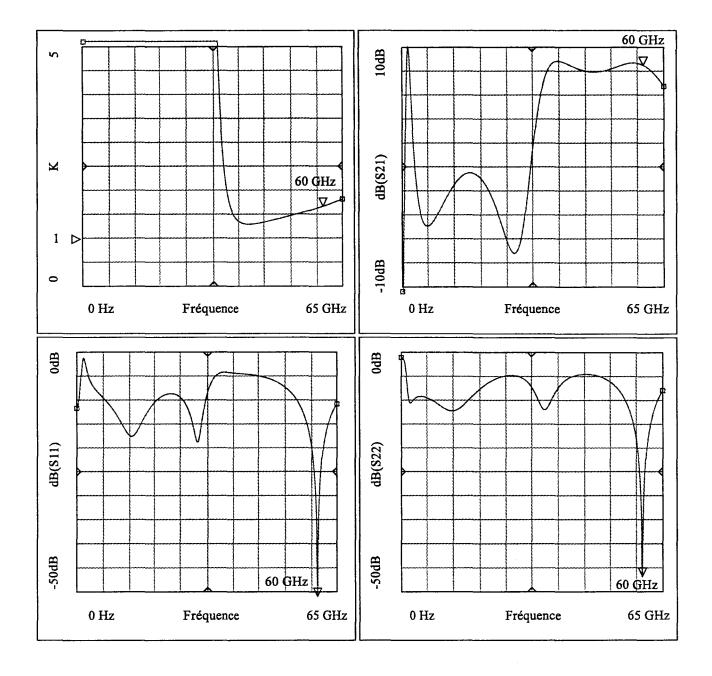

La dimension de la maille cristalline plus importante du substrat InP par rapport au substrat GaAs permet la croissance de l'hétérojonction AlInAs/GaInAs sans contrainte avec un taux important d'indium de 53 % dans le canal GaInAs et de 52 % dans la barrière d'AlInAs (figure I.20). Cet important taux d'indium dans le canal permet de bénéficier d'une mobilité supérieure à celle obtenue pour le PHEMT sur GaAs où le taux d'indium est moins élevé (< 30 %). Cette hétérostructure permet également une hauteur de barrière plus élevée ( $\Delta E_C = 500$  meV) permettant un meilleur confinement des porteurs dans le canal. Le phosphure d'indium possède de plus une meilleure conductivité thermique (0.68 Wcm<sup>-1</sup>K<sup>-1</sup> à 300 K) que l'arséniure de gallium (0.44 Wcm<sup>-1</sup>K<sup>-1</sup> à 300 K). Tous ces avantages en font une filière très avantageuse.