## Université des Sciences et Technologies de Lille École Doctorale Sciences Pour l'Ingénieur de Lille

#### **THÈSE**

#### pour obtenir le titre de

### DOCTEUR EN INFORMATIQUE

par

#### Arnaud BAILLY

## TEST & VALIDATION DE COMPOSANTS LOGICIELS

Soutenue publiquement le 15 décembre 2005 devant la commission d'examen :

Président : Pr. Laurence DUCHIEN LIFL, Université de Lille I

Rapporteurs : Pr. Ana CAVALLI INT, Évry

: M. Jean-Louis LANET, HDR GEMPLUS LABS, La Ciotat

Examinateurs: Pascal FLAMENT NORSYS, Ennevelin

Directrice : Pr. Mireille CLERBOUT LIFL, Université de Lille I Co-encadrante : Dr. Isabelle SIMPLOT-RYL LIFL, Université de Lille I

# Remerciements

Merci tout d'abord à Marie-Aimée de m'avoir soutenu et supporté tout au long de ces sept années. C'est promis, je ne le ferai plus, ou alors j'attendrai la retraite.

Merci à Isabelle Ryl devenue Simplot-Ryl d'être venue me chercher en licence, de m'avoir gardé en DEA et de m'avoir proposé ce sujet de thèse. Merci à Mireille Clerbout d'avoir accepté de diriger et coencadrer ce travail.

Merci à Pascal Flament, Sylvain Breuzard et au Conseil Régional Nord-Pas-de-Calais de m'avoir permis de manger et faire manger ma famille pendant ces trois ans et demi. Merci aussi aux ASSEDIC qui m'ont rémunéré pendant les trois années ayant précédé la thèse.

Merci à Ana Rosa Cavalli et à Jean-Louis Lanet d'une part, à Laurence Duchien d'autre part, d'avoir accepté respectivement de rapporter ce travail un peu particulier et de présider le jury de soutenance, malgré leur emploi du temps surchargé.

Merci à Yves Roos, Michel Latteux, Isabelle et Mireille encore, Jean-Marc Talbot, Sophie Tison, Jean Berstel, Jacques Sakarovitch et plein d'autres de m'avoir fait découvrir le monde merveilleux des automates et plus généralement de l'informatique théorique. Je ne manquerais pas de propager la bonne parole dans la mesure de mes moyens même si hélas, les temps sont durs pour la théorie.

Merci à Raphaël Marvie, Emmanuel Renaux, Philippe Merle, Olivier Barais, Lionel Seinturier, Dolorès Diaz, Jérémie Hattat, Renaud Pawlak pour les discussions souvent éclairantes sur la vraie nature des composants et l'existence d'un génie du logiciel.

Merci à Mirabelle Nebut, Yann Hodique, Iovka Boneva, Denis Debarbieux, encore Yves Roos et de manière générale toute l'équipe STC et une grande partie du LIFL pour leur agréable compagnonnage de bureau et leur indulgence envers mes sautes d'humeur.

Pour les mêmes raisons, merci à tous les collègues de Norsys avec lesquels j'ai eu l'occasion de discuter, travailler et même rigoler ces dernières années : Pascal bien sûr, Thomas Recloux, Christophe Cordennier, Xavier Farine, Éric Sillègue, Edwige Renaux et tous les autres.

Merci à Florence Mignard de m'avoir accompagné durant le *Nouveau Chapitre de Thèse* et à l'*Association Bernard Grégory* d'avoir permis que cela se fasse.

Merci à Douglas Hofstadter d'avoir écrit « *Gödel Escher Bach* ». C'est après la lecture de son livre que je me suis décidé à reprendre des études d'informatique. Merci donc aux enseignants et non-enseignants du FIL qui ont rendu ces années d'études souvent passionnantes, Patricia Caron, Bruno Bogaert, le SUDES, Jean-Paul Delahaye, Michel Petitot, Sophie Tison, Jean-Marc Geib, Philippe Mathieu, François Denis, David Simplot-Ryl et tous les autres.

Merci à Arnaud Fontaine, Damien Devigne et Lætitia Bonte d'avoir souffert en silence sur mon logiciel boursouflé durant leurs stages respectifs.

Merci enfin<sup>1</sup> à Isabelle Simplot-Ryl, Mireille Clerbout, Annie Audoux, Marie-Aimée Bailly et Jean-Louis Lanet pour leur vigilance dans la traque des fautes d'orthographe et de syntaxe innombrables de ce manuscrit.

<sup>&</sup>lt;sup>1</sup>Si vous lisez ces lignes et que vous estimez mériter des remerciements que je ne vous ai pas accordé, envoyer moi un mail à abailly@achilleus.net

# Table des matières

| 1                 | Pro  | rocessus de développement 1                                |  |  |  |  |  |  |  |  |  |

|-------------------|------|------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|                   | 1.1  | État de la pratique                                        |  |  |  |  |  |  |  |  |  |

|                   |      | 1.1.1 Infrastructure technique                             |  |  |  |  |  |  |  |  |  |

|                   |      | 1.1.2 Architecture logicielle                              |  |  |  |  |  |  |  |  |  |

|                   |      | 1.1.3 Processus de développement                           |  |  |  |  |  |  |  |  |  |

|                   |      | 1.1.4 Méthodologie d'analyse & conception                  |  |  |  |  |  |  |  |  |  |

|                   |      | 1.1.5 Infrastructure de développement                      |  |  |  |  |  |  |  |  |  |

|                   | 1.2  | Analyse critique                                           |  |  |  |  |  |  |  |  |  |

|                   |      | 1.2.1 Complexité                                           |  |  |  |  |  |  |  |  |  |

|                   |      | 1.2.2 Cohérence des éléments du développement              |  |  |  |  |  |  |  |  |  |

|                   |      | 1.2.3 Interpénétration des domaines                        |  |  |  |  |  |  |  |  |  |

|                   |      | 1.2.4 Formalisation                                        |  |  |  |  |  |  |  |  |  |

|                   |      | 1.2.5 Architecture                                         |  |  |  |  |  |  |  |  |  |

|                   | 1.3  | Préconisation                                              |  |  |  |  |  |  |  |  |  |

|                   | 1.0  | 1.3.1 Pour une architecture des logiciels                  |  |  |  |  |  |  |  |  |  |

|                   |      | 1.3.2 Test & fiabilité                                     |  |  |  |  |  |  |  |  |  |

|                   |      | 1.5.2 Test & habine                                        |  |  |  |  |  |  |  |  |  |

| 2                 | Arc  | hitecture & composants 27                                  |  |  |  |  |  |  |  |  |  |

|                   | 2.1  | Plate-formes de composants                                 |  |  |  |  |  |  |  |  |  |

|                   |      | 2.1.1 Intergiciels à composants                            |  |  |  |  |  |  |  |  |  |

|                   |      | 2.1.2 Containers de composants                             |  |  |  |  |  |  |  |  |  |

|                   | 2.2  | ADL                                                        |  |  |  |  |  |  |  |  |  |

|                   |      | 2.2.1 UML                                                  |  |  |  |  |  |  |  |  |  |

|                   |      | 2.2.2 Les ADL                                              |  |  |  |  |  |  |  |  |  |

| 2.3 Formalisation |      |                                                            |  |  |  |  |  |  |  |  |  |

|                   |      | Formalisation                                              |  |  |  |  |  |  |  |  |  |

|                   |      | 2.3.2 Composants & coalgèbres                              |  |  |  |  |  |  |  |  |  |

|                   | 2.4  | Conclusion                                                 |  |  |  |  |  |  |  |  |  |

|                   | 2. 1 | Conclusion                                                 |  |  |  |  |  |  |  |  |  |

| 3                 | Test | de conformité 41                                           |  |  |  |  |  |  |  |  |  |

|                   | 3.1  | Généralités                                                |  |  |  |  |  |  |  |  |  |

|                   |      | 3.1.1 Typologie                                            |  |  |  |  |  |  |  |  |  |

|                   |      | 3.1.2 Exécution du test                                    |  |  |  |  |  |  |  |  |  |

|                   |      | 3.1.3 Synthèse                                             |  |  |  |  |  |  |  |  |  |

|                   | 3.2  | Test de conformité                                         |  |  |  |  |  |  |  |  |  |

|                   |      | 3.2.1 Test algébrique                                      |  |  |  |  |  |  |  |  |  |

|                   |      | 3.2.2 Test d'automates d'états fini (FSM)                  |  |  |  |  |  |  |  |  |  |

|                   |      | 3.2.3 Sélection des cas de test dans les FSM déterministes |  |  |  |  |  |  |  |  |  |

|                   |      | 3.2.4 Sélection de cas de test généralisée                 |  |  |  |  |  |  |  |  |  |

|                   |      | 3.2.5 Test de LTS                                          |  |  |  |  |  |  |  |  |  |

|                   |      | 3.2.6 Algorithmes de tests dans les IOLTS                  |  |  |  |  |  |  |  |  |  |

|                   |      | 3.2.7 Sélection de cas de tests pour les IOLTS             |  |  |  |  |  |  |  |  |  |

|                   |      | Fam. 1                                                     |  |  |  |  |  |  |  |  |  |

|   |             | 3.2.8 Le tes                                 | t réparti                |        |  |  |  |  |  |  |  |  |       | <br>  |   | . 56  |

|---|-------------|----------------------------------------------|--------------------------|--------|--|--|--|--|--|--|--|--|-------|-------|---|-------|

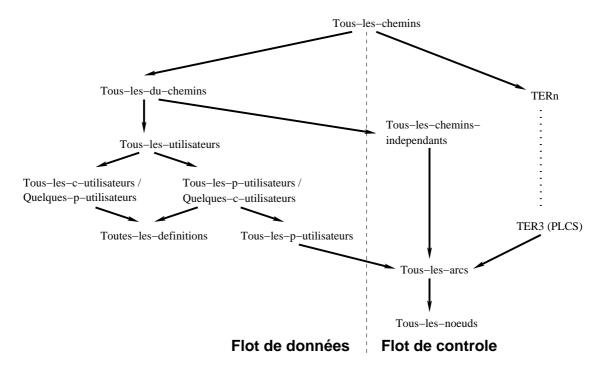

|   | 3.3         | Test structurel                              |                          |        |  |  |  |  |  |  |  |  |       | <br>  |   | . 58  |

|   |             | 3.3.1 Sélect                                 | ion statistique & aléato | oire . |  |  |  |  |  |  |  |  |       |       |   | . 61  |

|   |             | 3.3.2 Test n                                 | nutationnel              |        |  |  |  |  |  |  |  |  |       |       |   | . 62  |

|   | 3.4         | Discussion                                   |                          |        |  |  |  |  |  |  |  |  |       | <br>  |   | . 63  |

|   |             | 3.4.1 Test b                                 | asé sur les modèles      |        |  |  |  |  |  |  |  |  |       | <br>  |   | . 63  |

|   |             | 3.4.2 Analy                                  | se                       |        |  |  |  |  |  |  |  |  |       | <br>  |   | . 63  |

| 4 | N.T         | (S1. a                                       | 4 FIDI                   |        |  |  |  |  |  |  |  |  |       |       |   |       |

| 4 | <b>M100</b> | Modèle de composants FIDL<br>1.1 Généralités |                          |        |  |  |  |  |  |  |  |  | . 65  |       |   |       |

|   | 4.1         |                                              |                          |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             | ,                                            | aces & ports synchrone   |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | ments & ports asynchi    |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | exion & composition .    |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   | 4.0         |                                              | tion & Communication     |        |  |  |  |  |  |  |  |  |       |       |   |       |

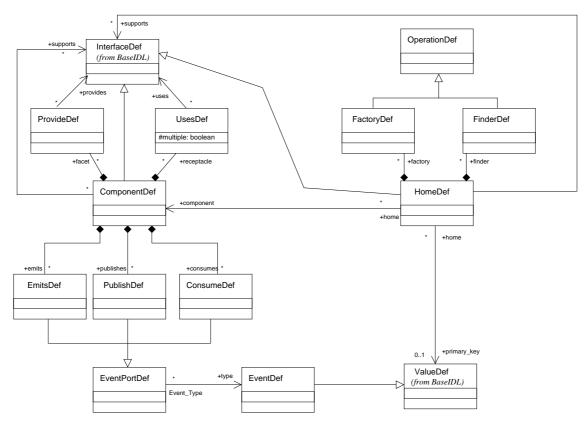

|   | 4.2         | 0 0                                          | DL                       |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             | 4.2.1 IDL3                                   |                          |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             | -                                            | ication                  |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | ices                     |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | osants                   |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | maire                    |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   | 4.3         | •                                            |                          |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             | _                                            | ichet automatique de b   | -      |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             | 4.3.2 Un sy                                  | stème de vote électron   | ique . |  |  |  |  |  |  |  |  |       | <br>  |   | . 74  |

| 5 | Anta        | mates FIDL                                   |                          |        |  |  |  |  |  |  |  |  |       |       |   | 79    |

| J | 5.1         |                                              | FIDL                     |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   | 5.1         |                                              | ninaires                 |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | nates                    |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | bet                      |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             | 1                                            | oles & Contraintes       |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              |                          |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             | $\mathcal{C}$                                | ge reconnu par un auto   |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | naissance par synchro    |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | nate bien-formé          |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   | <i>-</i> 2  |                                              | éterminisme              |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   | 5.2         | -                                            | IDL                      |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             | •                                            | ssions                   |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   | <b>~</b> 0  |                                              | ruction                  |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   | 5.3         |                                              | Validations              |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | ines finis               |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | ines reconnaissables .   |        |  |  |  |  |  |  |  |  | <br>• | <br>  |   |       |

|   | 5.4         | Conclusion .                                 |                          |        |  |  |  |  |  |  |  |  | <br>• | <br>• | • | . 95  |

| 6 | Sém         | antique                                      |                          |        |  |  |  |  |  |  |  |  |       |       |   | 97    |

| Ū | 6.1         |                                              | niques                   |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   | 0.1         |                                              | ments                    |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | de ports                 |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             | 7 1                                          | osants                   |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | ssions FIDL              |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | ible de traces d'une int |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             |                                              | ible de traces d'un con  |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   | 6.2         |                                              |                          |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   | 0.2         | -                                            |                          |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             | •                                            | ne                       |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             | 1                                            | ct des contrats          |        |  |  |  |  |  |  |  |  |       |       |   |       |

|   |             | 6.2.3 Indépe                                 | endance des facettes .   |        |  |  |  |  |  |  |  |  |       |       |   | . 105 |

TABLE DES MATIÈRES 7

| В                | Glos        | ssaire    |                                  | 161 |  |  |  |

|------------------|-------------|-----------|----------------------------------|-----|--|--|--|

| A Grammaire FIDL |             |           |                                  |     |  |  |  |

|                  |             | 8.3.4     | Production                       | 142 |  |  |  |

|                  |             | 8.3.3     | Intégration                      |     |  |  |  |

|                  |             | 8.3.2     | Développement                    | 142 |  |  |  |

|                  |             | 8.3.1     | Conception                       |     |  |  |  |

|                  | 8.3         | Modèle    | es et processus de développement |     |  |  |  |

|                  |             | 8.2.5     | Contrôleur                       |     |  |  |  |

|                  |             | 8.2.4     | Exécuteur                        |     |  |  |  |

|                  |             | 8.2.3     | Déployeur                        |     |  |  |  |

|                  |             | 8.2.2     | Plate-forme de test              |     |  |  |  |

|                  |             | 8.2.1     | Analyse syntaxique & compilation |     |  |  |  |

|                  | 8.2         | Outillag  |                                  |     |  |  |  |

|                  | 0.5         | 8.1.3     | Validation dynamique             |     |  |  |  |

|                  |             | 8.1.2     | Validation statique              |     |  |  |  |

|                  |             | 8.1.1     | Vérification de l'architecture   |     |  |  |  |

|                  | 8.1         |           | ations & Validations             |     |  |  |  |

| ō                |             | e en œuv  |                                  |     |  |  |  |

| 8                | Mice        | o on or   | 770                              | 133 |  |  |  |

|                  | 7.4         | Conclu    | sion                             | 132 |  |  |  |

|                  |             | 7.3.2     | Algorithme général               |     |  |  |  |

|                  |             | 7.3.1     | Scénarios de test                |     |  |  |  |

|                  | 7.3         |           | composants FIDL                  |     |  |  |  |

|                  | 7.2         | 7.2.3     | Conformité                       |     |  |  |  |

|                  |             | 7.2.2     | Test d'IOLTS                     |     |  |  |  |

|                  |             | 7.2.1     | Rappels                          |     |  |  |  |

|                  | 7.2         | _         | hme de test                      |     |  |  |  |

|                  | 7.2         | 7.1.2     | Respect des ports                |     |  |  |  |

|                  |             | 7.1.1     | Indépendance des facettes        |     |  |  |  |

|                  | 7.1         |           | Ation                            |     |  |  |  |

| 7                |             | ification |                                  | 119 |  |  |  |

| 7                | <b>1</b> 74 | Goot! ar- | Pr tout                          | 110 |  |  |  |

|                  | 6.5         | Conclu    | sion                             | 118 |  |  |  |

|                  |             | 6.4.3     | Substitution de composants       |     |  |  |  |

|                  |             | 6.4.2     | Sous-typage & Connexions         |     |  |  |  |

|                  |             | 6.4.1     | Relation de sous-typage          |     |  |  |  |

|                  | 6.4         | _         | e                                |     |  |  |  |

|                  |             | 6.3.4     | Composition & Modèles            |     |  |  |  |

|                  |             | 6.3.3     | Propriétés d'un assemblage       |     |  |  |  |

|                  |             | 6.3.2     | Assemblages                      |     |  |  |  |

|                  |             | 6.3.1     | Connexions                       |     |  |  |  |

|                  | 6.3         | -         | sitionnalité                     |     |  |  |  |

|                  |             | 6.2.4     | Fiabilité d'un système           |     |  |  |  |

|                  |             |           |                                  | 40. |  |  |  |

## Introduction

#### **Contexte**

Ce travail de thèse s'est déroulée dans le cadre d'une collaboration entre la société NORSYS et le *Laboratoire d'Informatique Fondamental de Lille*, cofinancée par la Région Nord-Pas-de-Calais. NORSYS est une société de services informatiques créée en 1990 et spécialisée dans la réalisation de logiciels à façon pour des clients de taille et d'activité diverses : banque, assurance, secteur social, grande distribution. Les logiciels réalisés ont tous pour caractéristiques communes d'être des outils de gestion participant d'un système d'information d'entreprise, évoluant dans un environnement techniquement hétérogène, pour des utilisateurs de qualifications diverses. Il s'agit donc pour l'essentiel de traitement de l'information, autrement dit de l'informatique de gestion.

Le démarrage de cette thèse s'est fait à peu près conjointement avec l'apparition au sein de la société de ce qu'il était convenu d'appeler les *Nouvelles Technologies de l'Information et de la Communication*. Ce terme désigne l'ensemble des techniques — langages, environnements, réseaux, Internet, systèmes — qui ont transformé l'informatique à la fin du XX<sup>e</sup> siècle. Les applications ont évolué depuis des systèmes centralisés — client lourd-site central — vers des technologies décentralisées dites *réparties* accessibles depuis des *clients légers*. Les systèmes sont devenus ouverts et communiquants. Ce changement technologique ne s'est pas fait et ne se fait pas sans heurts et il a nécessité la mise en œuvre de méthodes d'analyse, de conception et de développement différentes. Une partie non négligeable de mon travail au sein de l'entreprise a donc consisté à accompagner ce changement par la réalisation de prototypes, le conseil dans la conception d'architectures logicielles, la mise en œuvre de techniques de développement inspirées des pratiques de l'*open-source* et la formation des personnels.

Une autre « révolution », dont le terme n'a pas encore été atteint, est la généralisation du phénomène d'externalisation des développements ou développement off-shore. L'arrivée sur le marché des services informatiques de concurrents issus de pays émergents — Inde, Chine, ex-Pays de l'Est, Maghreb et Moyen-Orient — et proposant les services d'une main d'œuvre qualifiée à des salaires nettement inférieurs à ceux pratiqués dans les pays développés entraîne une baisse des prix généralisée dans les métiers du développement à façon de logiciels. La question se pose donc pour les sociétés de services et de manière plus générale les « professionnels de la profession » des pays développés de la stratégie à adopter face à cette évolution.

Parmi les solutions possibles, il en est une qui concerne directement mon activité au sein de l'entreprise, c'est la mise en place d'un processus de développement « industriel ». L'intensité capitalistique est l'une des barrières d'entrée à la concurrence les plus efficaces sur un marché : plus les investissements seront lourds pour espérer obtenir des parts de marché, moins les concurrents seront tentés de s'y intéresser. Le concept, initialement forgé pour l'industrie classique, peut parfaitement s'appliquer au secteur des services avec une modification de taille : ici le capital est essentiellement humain. Industrialiser les développements consistera donc à créer des procédures, des normes, des contrôles, bref une chaîne de production, qui permette simultanément de réduire le temps de développement et d'accroître la qualité de la production.

### **Problèmes**

Cet objectif se traduit sur le plan scientifique en termes de problèmes de *génie logiciel*. Les grandes questions qui se posent sont donc : comment automatiser le processus de développement? Comment

10 INTRODUCTION

améliorer le contrôle de la qualité de ce processus ? Comment accroître la fiabilité — mesurée en taux de défauts résiduels — des applications produites ?

Cette thèse cherche à contribuer à la résolution de ces problèmes, à partir des trois hypothèses suivantes :

- 1. les *composants logiciels* sont la bonne réponse à la complexité croissante des applications, si on ne se limite pas à leur utilisation dans le cadre de plate-formes technologiques *ad hoc* mais si on s'en sert aussi comme un outil pour concevoir les applications et leur architecture;

- 2. la vérification et la validation automatisées des composants produits doivent être au cœur du processus de développement pour assurer un niveau de qualité élevé et constant;

- 3. des contrats comportementaux formalisés supportant de multiples niveaux d'abstraction sont le carburant dont peut se nourrir un tel processus.

Il est bien connu que le test représente une part très importante du coût d'un projet de développement, les évaluations se trouvant généralement dans une fourchette de 30 à 50% du coût total. Ce que l'on entend par test dans ces évaluations est le test système ou dans notre contexte le test de recette — ou plus communément la recette — c'est-à-dire la phase succédant au développement et durant laquelle le logiciel produit est testé par des utilisateurs. Ce coût comprend non seulement le temps nécessaire pour exécuter les plans de test en fonction des exigences initiales de l'application, mais aussi le temps nécessaire à l'analyse des résultats de ces tests, le temps pris à corriger les erreurs détectées et bien entendu le temps nécessaire à la correction des erreurs introduites par les corrections. Dans le meilleur des cas, ce processus converge jusqu'à ce que plus aucune erreur ne soit signalée ou jusqu'à ce qu'un certain seuil — de temps ou de niveau d'exigences — soit franchi.

Le coût de cette phase de recette est non seulement corrélé à la qualité des développements proprement dits mais aussi à la qualité du processus d'analyse et de modélisation des exigences, donc à l'ensemble des activités du processus de construction du logiciel. Il est évident que si les spécifications sont incomplètes, ambiguës, changeantes, si elles sont mal comprises par les concepteurs et développeurs, la phase de recette verra son coût augmenter considérablement. L'importance de disposer de spécifications précises est donc une fois encore à souligner.

A contrario, le coût des tests réalisés en cours de développement, ce que l'on appelle communément les tests unitaires est relativement faible : ces tests sont écrits au fil de l'eau par les équipes de développement et s'intègrent naturellement dans la réalisation de l'application proprement dite. Il est par conséquent évident que la meilleure manière de réduire le coût parfois prohibitif de la recette est de maximiser le nombre d'erreurs détectées le plus tôt possible, et donc d'introduire le plus tôt possible les tests fonctionnels complets de l'application de sorte que le passage en recette se fasse sur un logiciel déjà en grande partie testé, unitairement et globalement.

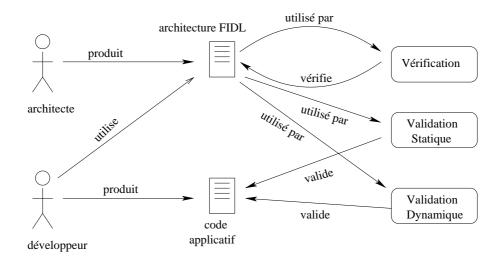

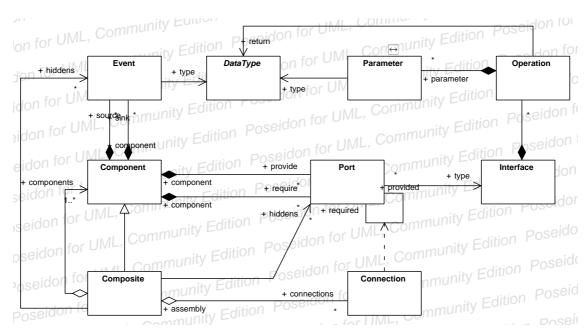

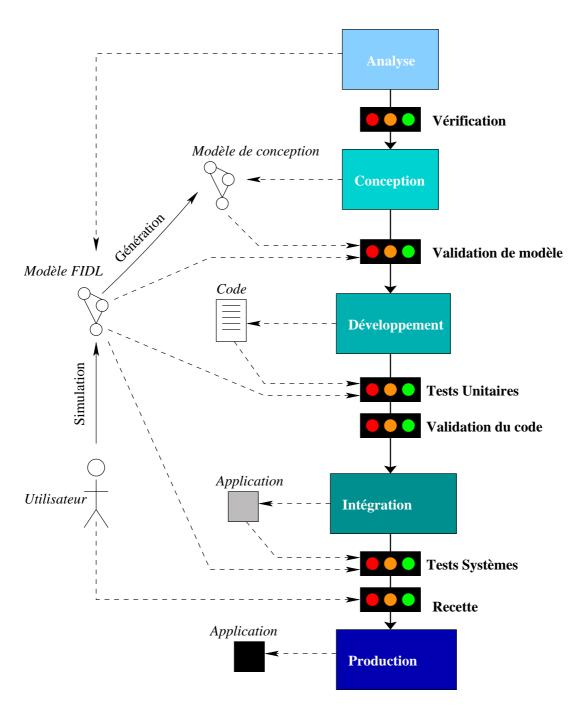

Ces hypothèses et constats nous ont conduits à formuler la proposition qui est défendue dans cette thèse et qui se compose : d'un modèle abstrait de composants permettant l'expression de contrats comportementaux à partir des interfaces et dépendances de composants ; d'une sémantique formelle de la statique et de la dynamique de ce modèle sous la forme de langages et d'opérations simples ; d'outils théoriques pour la validation et la vérification de composants concrets, et plus particulièrement par des méthodes de test de conformité ; d'une intégration de cette démarche dans le cycle de production du logiciel ; enfin d'un prototype d'outil démontrant les capacités d'automatisation des tests fonctionnels à partir d'un modèle de composants abstrait et selon différentes implantations cibles.

En résumé, je défends l'idée que des composants formalisés dans un langage idoine peuvent être testés automatiquement et utilisés à différents degrés d'abstraction de manière à obtenir et maintenir un niveau de qualité mesuré.

#### Résumé

Le premier chapitre est une analyse de l'existant : comment sont actuellement produites les applications, dans quels langages, avec quelles méthodes ; et quels sont les problèmes que posent ces techniques. Le chapitre 2 est une synthèse des travaux et systèmes existants que l'on peut rapprocher de près ou de loin de la notion d'architecture de composants. Nous étudierons des plate-formes dites « à composants », des langages de modélisation, des langages de description d'architectures, des modèles et systèmes formels

INTRODUCTION 11

permettant de construire de telles architectures et de raisonner dessus. Le chapitre 3 se veut un panorama du test de logiciel, de son vocabulaire, de ses problèmes, plus particulièrement focalisé sur le *test fonctionnel* ou test *boîte noire*, et encore plus précisément sur le test de conformité à partir de modèles à systèmes de transitions.

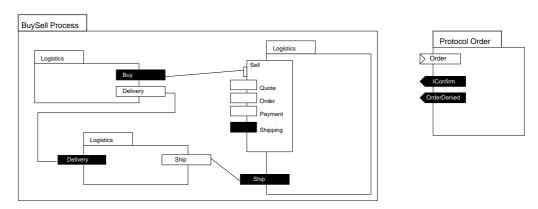

Après cet état de l'art et de la pratique, le chapitre 4 décrit de manière informelle les différents éléments que nous avons choisi de prendre en compte et qui collectivement définissent le modèle FIDL d'architecture à composants. Ce chapitre contient une section introductive présentant les grandes caractéristiques du modèle, une description de la syntaxe du langage et deux exemples de modélisation. Le chapitre 5 est une définition formelle des automates FIDL, une variété d'automates qui décrivent la sémantique des composants et systèmes de composants. Sont aussi définis précisément les expressions qui servent à dénoter ces automates et le processus de transformation de l'un en l'autre. Enfin le chapitre 6 relie les deux chapitres précédents en décrivant comment sont construits les langages associés à chacun des éléments d'un modèle FIDL, depuis les données primitives jusqu'aux assemblages de composants. Nous montrons en particulier que la composition de composants préserve certaines propriétés « naturelles » des systèmes ouverts de composants. La question de l'héritage comportemental est aussi abordée succinctement.

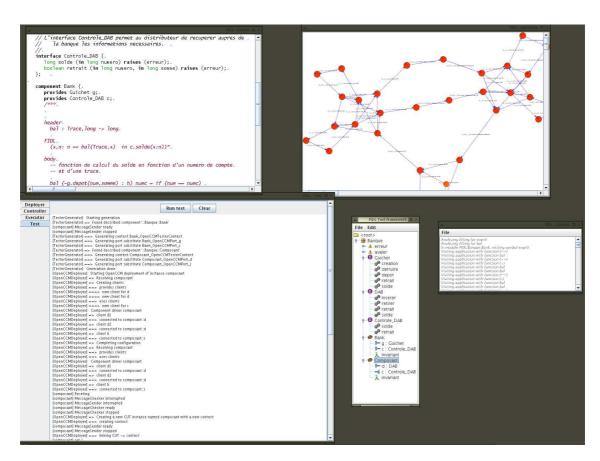

Le chapitre 7 est consacré aux problèmes de vérifications des propriétés de composition des modèles FIDL et surtout du test de conformité de composants concrets par rapport à des spécifications. Nous montrons que ce problème peut être traité de manière *décompositionnelle* en s'intéressant à certaines parties significatives du comportement spécifié des composants. Le chapitre 8, enfin, introduit brièvement la question de la mise en œuvre concrète de l'ensemble de cette démarche basée sur des architectures de composants. La structure et les possibilités d'un prototype sont décrites, ainsi que les interactions des activités de V&V basées sur des modèles FIDL dans le processus de développement.

Je concluerai enfin par un résumé des contributions que j'estime être les plus importantes de ce travail et par une revue des perspectives ouvertes et qu'il serait souhaitable d'approfondir. Le lecteur pointilleux pourra se reporter aux annexes pour y découvrir le détail de la grammaire du langage FIDL ainsi qu'un glossaire des nombreux termes techniques et acronymes qui parsèment ce document.

12 INTRODUCTION

## Chapitre 1

# Processus de développement

Les « nouvelles technologies » avaient pour ambition de pallier les insuffisances des modes traditionnels de production de logiciel — systèmes centralisés, client-serveurs — en particulier pour ce qui concernait la maintenance et l'évolutivité. Ces technologies — langages orienté-objets, clients légers universels, intergiciels, réseaux ouverts ... — ont induit une modification du processus de développement logiciel qui s'est faite progressivement au fil des nouveaux projets, avec l'intégration de nouvelles méthodes de conception dirigées par les modèles UML et de nouvelles pratiques inspirées des techniques des logiciels libres et de l'eXtreme Programming. Le constat que l'on peut faire aujourd'hui et qui sera développé dans ce chapitre est que, si la phase de développement et dans l'ensemble les aspects technologiques sont bien maîtrisés, la conception des systèmes, leur articulation avec l'analyse des besoins du client et surtout la qualité et la fiabilité du produit fini posent encore de nombreux problèmes. Ces problèmes nous semblent provenir d'un manque de maturité du processus, de compréhension globale de l'architecture des systèmes et de formalisation du processus de validation et de vérification des développements.

Nous commencerons ce chapitre par une présentation du processus de développement qui nous permettra d'exposer les pratiques actuelles, les outils et les méthodes. Cette présentation nous permettra par ailleurs de présenter nos contributions pratiques dans l'amélioration du suivi et de la qualité du processus de développement de ce type d'application. Cette première section sera suivie d'une analyse critique de ce processus et d'une première exposition des solutions envisageables qui nous permettra de mettre l'accent sur les besoins de formalisation et de vérification d'architectures.

## 1.1 État de la pratique

Norsys est une société de services et comme telle est amenée à réaliser des logiciels à façon pour un grand nombre de clients possédant chacun des métiers différents. Toutefois, tous les développements réalisés depuis quelques années dans le domaine des « nouvelles technologies » possèdent nombres de caractéristiques communes :

- le langage support est Java;

- l'infrastructure technique est basée sur J2EE[149], la spécification orientée « composants » de Sun pour les systèmes d'information d'entreprises;

- les phases de recueil des exigences, d'analyse et de conception utilisent une modélisation à base de diagrammes UML complétée de nombreux documents textuels;

- le processus de développement est proche d'un processus de type RUP Rational Unified Process

avec des adaptations spécifiques et des allégements par rapport aux préconisations du modèle;

- l'architecture logicielle est structurée en couches, depuis la présentation jusqu'à la persistance des données. Les services transversaux authentification, habilitation, contexte transactionnel, répartition de charges ... sont assurés par l'infrastructure J2EE ou développés de manière ad hoc;

- les systèmes développés ont généralement à s'intégrer dans un existant complexe, mélange d'applications client-serveurs, de bases de données, de moniteurs transactionnels et de systèmes centralisés

en COBOL.

La complexité des développements provient de la nécessité de fonctionner dans un environnement hétérogène avec des contraintes techniques et organisationnelles fortes. Il est rare de rencontrer dans ce type de logiciel de la complexité dans les fonctionnalités ou les algorithmes.

#### 1.1.1 Infrastructure technique

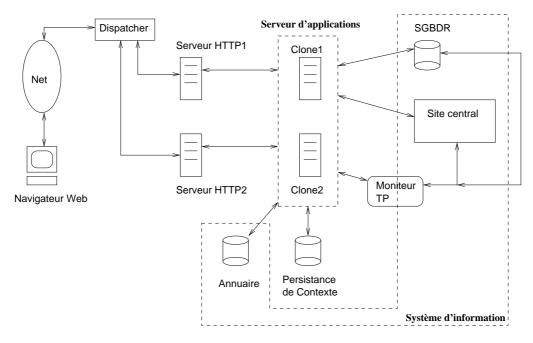

La cible technique est constituée de systèmes répartis généralement redondants hébergés sur des fermes de serveurs. La figure 1.1 représente une architecture technique type sur laquelle sont déployées les applications produites. Il s'agit là bien évidemment d'une configuration idéale qui peut être adaptée en fonction des contraintes de coûts, de performances ou de sécurité du projet.

FIG. 1.1 – Architecture technique.

La communication avec le client est gérée par un ou plusieurs serveurs HTTP avec un répartiteur de charge permettant de minimiser temps de réponse et trafic réseau. Le serveur HTTP communique avec le serveur d'applications généralement au travers d'un protocole ad hoc, serveur qui peut être cloné de sorte que là aussi, la charge soit répartie sur plusieurs machines et la tolérance aux pannes soit améliorée. Le contexte, c'est-à-dire l'ensemble des informations relatives à une session, est persistant selon un mécanisme propre au serveur d'applications choisi : en cas de transfert de traitement d'un serveur à un autre ou de reprise sur erreur, le contexte peut être restauré assurant de manière transparente un service continu du point de vue du client. Les besoins d'authentification des clients, qu'ils soient réalisés par mots de passe ou par une infrastructure à clés publiques (PKI), sont le plus souvent gérés par un annuaire d'entreprise de type LDAP. Il en va de même pour l'habilitation des utilisateurs, c'est-à-dire pour la définition de leurs droits d'accès sur les fonctions du système. Notons que l'authentification se fait généralement au niveau des serveurs HTTP tandis que l'habilitation se fait dans le serveur d'applications.

Le serveur d'applications contient l'ensemble de la logique applicative (voir ci-dessous) et a la charge de communiquer au travers de connecteurs idoines avec le reste du système d'information : bases de données relationnelles, sites centraux, moniteurs transactionnels. L'architecture J2EE prévoit, au travers des connecteurs JCA, la possibilité de relier un tel système à n'importe quel autre en maintenant des propriétés transactionnelles. Pour une présentation générale de l'architecture de la plate-forme J2EE, voir la section 2.1.1 du chapitre 2.

#### 1.1.2 Architecture logicielle

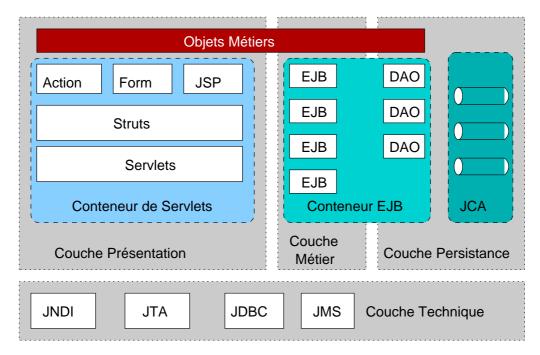

L'architecture logicielle utilisée est une architecture en couches qui reprend un certain nombre de « bonnes pratiques » désormais courantes dans le domaine. Elle s'inspire de *patrons de conceptions*[11, 62] usuels, tels que le patron *Modèle-Vue-Contrôleur* popularisé par le framework Struts pour la gestion des interactions avec le client, ou le patron *Recherche de Services* — *Service Locator* — pour la localisation d'interfaces métiers offertes par les EJB. La figure 1.2 reprend les différents éléments de manière synthétique.

FIG. 1.2 – Architecture logicielle.

La couche présentation s'appuie sur des servlets encapsulées dans un conteneur, qui permettent de développer des contenus dynamiques en Java en s'abstrayant d'un certain nombre de détails techniques tels que la gestion de la transformation des paramètres — marshalling — depuis ou vers le protocole HTTP, la gestion du contexte de session et du contexte applicatif et surtout la communication par appels de méthodes distants avec la couche métier, c'est-à-dire les EJB. Struts fournit un canevas pour gérer les interactions avec le client et sur cette base sont développés des actions, des formulaires — forms — et des JSP — Java Server Pages — représentant respectivement la partie contrôle, modèle et vue du patron MVC.

La couche métier contient les Enterprise Java Beans, un ensemble de services métiers utilisés par la couche présentation en fonction des besoins de l'application. Ces EJB sont le plus souvent de type Session sans état et le traitement de l'accès aux données est délégué à des objets spécialisés appelés Data Access Objects ou DAO, plutôt que laissé à la discrétion du conteneur et d'EJB Entités.

La couche persistance est souvent la plus technique et la plus délicate. Dans l'idéal, elle réalise une simple projection du modèle de classes des objets métiers depuis ou vers un système de base de données quelconque, ce qui peut être fait de manière automatisée en s'appuyant sur un framework tel que les EJB Entités ou Hibernate. Dans la pratique, compte tenu du fait que les schémas de table sont généralement préexistants aux applications développées, que les canevas de projection objet-relationnel automatisés ne parviennent pas à optimiser correctement les transactions et les requêtes et que l'on n'a pas uniquement affaire à des systèmes relationnels mais aussi à des applications légataires, à des transactions stockées CO-BOL ou encore à des couches de moniteurs transactionnels propriétaires, cette gestion est le plus souvent développée de manière ad hoc.

La couche transversale objets métiers contient l'ensemble des objets du domaine applicatif, autrement

dit l'instantiation du diagramme de classes des données manipulées par l'application. Ces objets sont utilisés par toutes les couches car l'utilisation d'objets de granularité importante, voire de grappes d'objets, dans les interactions entre couches permet de réduire le nombre d'appels de méthodes réalisés et donc d'accroître les performances du système.

La *couche technique*, enfin, comprend un certain nombre de services sur lesquels s'appuient les différents composants du système :

- service de nommage Java Naming and Directory Interface;

- service de transaction Java Transaction API;

- service d'accès aux données Java DataBase Connectivity;

- service de messagerie asynchrone Java Message Service.

### 1.1.3 Processus de développement

Le processus de développement utilisé est largement inspiré du RUP, mâtiné d'une bonne dose de pragmatisme et d'un zeste d'*eXtreme Programming*. Nous renvoyons aux travaux réalisés au sein de l'entreprise par E.Renaux[136] pour une analyse plus poussée de ce processus et de ses défauts.

Il s'agit là d'un principe théorique qui dans la pratique recouvre un découpage plus « traditionnel » en activités et en lots :

- les phases d'expression des besoins et d'analyse se confondent. Elles produisent un cahier des charges, des diagrammes de cas d'utilisation, des scénarios et des règles métiers;

- la conception produit les diagrammes de classes et éventuellement d'états-transitions associés, ainsi que les schémas de données;

- le développement réalise effectivement l'application à partir des documents de conception ;

- la phase de test ou phase de recette valide l'application produite par rapport aux besoins initiaux.

Les itérations et incréments ont une granularité beaucoup plus grande que dans les préconisations des méthodes citées, problème important dont on verra par la suite qu'il découle de carences dans la modélisation de l'architecture globale de l'application.

Le processus de développement s'appuie par ailleurs sur une analyse d'*urbanisation* du système d'informations qui permet de découper globalement les processus métiers en différents *quartiers* et *blocs* reproduisant au niveau informatique l'organisation du client. Le processus tel que nous le présentons ici doit être compris comme une synthèse d'un ensemble de pratiques sur différents projets.

#### 1.1.4 Méthodologie d'analyse & conception

La méthodologie articule la conception en *couches* et le résultat du processus d'analyse en *vues*. Les différentes couches recensées sont :

- la couche *Présentation* qui contient essentiellement les éléments régissant les interactions avec l'utilisateur : description de l'interface graphique, règles de navigation entre écrans ;

- la couche *Dynamique applicative* qui contient les processus de l'application proprement dite, c'està-dire essentiellement les actions Struts;

- la couche Métier qui définit et contient les services métiers et les objets associés ;

- la couche *Persistance* qui décrit les règles d'interaction entre objets-métiers et système de stockage.

Le processus d'analyse et de conception produit un ensemble de *vues* qui sont chacune représentées par différents modèles et documents. Ces différentes vues sont :

- la **vue utilisateur** qui décrit les besoins de l'utilisateur en termes généraux ;

- la **vue processus** qui modélise chaque processus d'interaction entre un utilisateur et le système ;

- la vue composant qui identifie les composants du système, leur fonctionnement et leur interaction avec d'autres composants;

- la vue persistance qui décrit les règles de projection entre objets-métiers et système de stockage persistant.

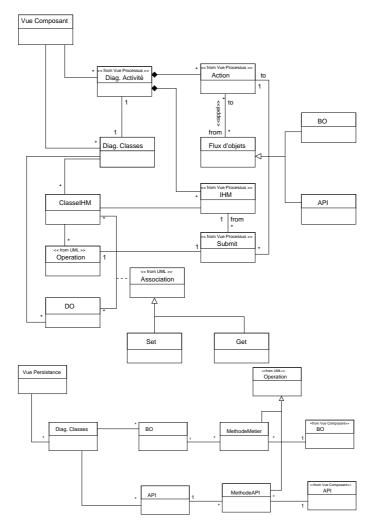

Nous décrivons succinctement chacune des vues dans les sections ci-dessous en proposant systématiquement une synthèse sous la forme d'un *méta-modèle* UML de chaque vue.

#### Vue utilisateur

Les besoins utilisateurs sont décrits sous la forme de diagrammes de cas d'utilisation et de diagrammes de classes. Un méta-modèle de cette vue utilisateur est donné ci-dessous (partie supérieure de la figure 1.3).

FIG. 1.3 – Vues utilisateurs & métiers.

Dans cette vue, on exprime les besoins de l'utilisateur, on définit le périmètre du système et les interactions avec les différents rôles de l'utilisateur. Cette vue permet de dégager des **entités fonctionnelles** (domaines) représentées dans le méta-modèle par une classe dont les attributs et les opérations sont définis par les différents cas d'utilisation.

#### **Vue Processus**

Cette vue, à partir des besoins utilisateurs exprimés précédemment, va définir précisément les interactions existant entre les différents rôles (acteurs) intervenant dans l'application et le système : c'est un *scénario*. Ces interactions sont représentées dans un diagramme de cas d'utilisation, chaque cas d'utilisation se trouvant par la suite associé à un ou plusieurs diagrammes d'activité. Les regroupements de cas

d'utilisation représentent en fait des menus/actions accessibles par différents rôles du système. Les interactions ou activités sont réalisées par des échanges entre des *éléments d'IHM* et des *actions* : une IHM permet d'invoquer une ou plusieurs actions qui en retour produit une nouvelle IHM.

Cette vue permet en particulier d'identifier et de caractériser les objets IHM utilisés (types d'éléments d'interfaces, ordres de navigation, accessibilité) et de définir les processus métiers, c'est-à-dire de documenter les algorithmes relatifs à chaque Action : quelles sont les éléments de données de l'IHM qui sont transmis et quels en sont les résultats ?

#### **Vue Composants**

La vue « composants » détaille :

- les éléments d'IHM, plus particulièrement du point de vue de la couche dynamique applicative, c'està-dire du serveur d'application dans l'architecture choisie;

- les services métiers, c'est-à-dire les objets et leurs interfaces permettant de réaliser les fonctions demandées par l'utilisateur.

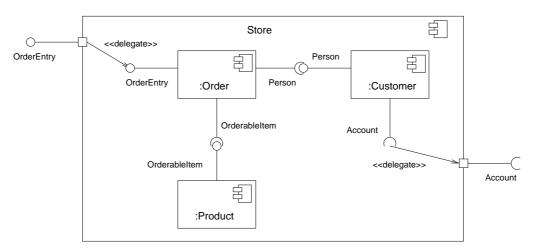

FIG. 1.4 – Vue composants métiers & persistance.

Le diagramme d'activité issu de la phase précédente est enrichi par des informations supplémentaires sur les éléments concrets de réalisation des classes IHM (maquette HTML, page JSP, attributs) et des éléments Flux d'objet. Ces flux d'objets correspondent à des invocations de services métiers (BO) ou d'éléments de l'infrastructure logicielle sous-jacente (API). À chaque transition déclenchée par une activité

d'IHM correspond une méthode dans la classe d'IHM correspondante, méthode qui sera documentée en décrivant les contrôles effectués sur les attributs de l'objet.

#### Vue métier/persistance

Cette dernière vue définit comment les objets métiers communiquent avec des données présentes dans des applications patrimoniales (sites centraux), des SGBD ou toute autre forme de stockage de longue durée. Comme indiqué dans le paragraphe précédent, les objets BO et API ont pour fonction de faire le lien entre les services du point de vue de l'application et les données et couches techniques. Des règles d'accès aux données persistantes sont par ailleurs définies à ce stade qui ne sont pas traitées dans le cadre de cette étude.

#### 1.1.5 Infrastructure de développement

Les développements s'appuient sur un certain nombre d'outils et de pratiques ayant pour objectif d'accroître la qualité et la fiabilité du résultat final. D'une part est mise en œuvre une démarche globale d'ingénierie dirigée par les modèles permettant de tirer partie de l'existence de modèles de conception et de libérer le développeur des contraintes techniques induites par la plate-forme. Concrètement, cela signifie qu'à partir des diagrammes de classes des objets métiers, on utilise des outils de génération de code pour produire automatiquement les éléments nécessaires à l'infrastructure technique : interfaces distantes et fabriques dans le cas des EJB, fichiers de configurations XML pour la persistance des données et la couche présentation, formulaires Struts.

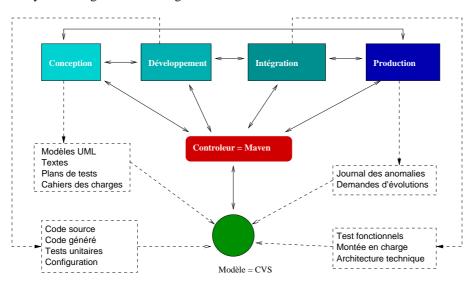

D'autre part, un processus d'intégration continue piloté par Maven et basé sur un système de gestion de versions permet d'automatiser la construction des livrables de l'application — paquetages, archives, descripteurs de déploiement — et surtout de produire à intervalles réguliers une photographie de l'ensemble de l'application, sa documentation et une batterie de vérifications statiques et dynamiques. Ce principe est résumé dans la figure 1.5 et reprend la forme d'un patron MVC dans lequel les vues sont les différentes phases ou acteurs du processus de développement, le contrôleur est le moteur d'intégration continue et le modèle est le système de gestion de configurations.

FIG. 1.5 – Modèle de processus de développement.

Les vérifications réalisées par le contrôleur à partir du code source sont les suivantes :

- vérifications des règles syntaxiques de codage : nommage des entités dans le code, indentation et formatage ...;

- vérifications de règles simples de sémantique : code mort, variables inutilisées et déclarations incorrectes ...;

- calculs de métriques par paquetage telles que le degré d'abstraction/concrétion, le taux de couplage, le degré de complexité ...;

- vérification des règles d'accès architecturales entre classes et paquetages permettant de vérifier le respect par les développeurs de l'architecture globale du système;

- exécution des tests unitaires et calcul de la couverture de code instructions et branchements réalisée.

Le développement et la mise en œuvre de ces outils a constitué une part importante de notre contribution au sein de l'entreprise et s'est étalée sur différents projets. En l'état actuel des choses, seule la vue *Développement* est réellement opérationnelle. Une partie de l'objectif de cette thèse est de faire en sorte que les autres vues, et plus particulièrement les vues *Conception* et *Intégration* soient mises en place par la gestion automatisée des tests fonctionnels à différents niveaux de l'architecture et la validation croisée entre modèles et sources.

## 1.2 Analyse critique

Après un rapide tour d'horizon du processus type de développement d'applications réparties sur architecture J2EE, cette section est consacrée à une analyse critique dudit processus en partant des problèmes constatés concrètement lors de la vie des projets et des éléments méthodologiques présentés.

Un des problèmes essentiels auquel nous sommes confrontés est le passage de l'analyse à la conception, c'est-à-dire la transformation d'un schéma de compréhension général du processus métier de l'application en un modèle de conception à base de composants. La proposition Component Unified Process[136, 137] a pour objectif de résoudre ce problème en introduisant au plus tôt une structuration en composants des différentes fonctionnalités de l'application. Notons que c'est partiellement ce qui est préconisé dans le processus de modélisation que nous avons détaillé ci-dessus. Nous nous intéressons toutefois à un problème différent : il s'agit, rappelons-le, de vérifier que ce qui est développé correspond bien à ce qui est attendu, pas plus, pas moins.

#### 1.2.1 Complexité

Les systèmes d'information en particulier, et les gros systèmes informatiques en général, ont toujours été complexes mais cette complexité conceptuelle se trouve aujourd'hui démultipliée par la complexité des architectures techniques et applicatives mises en place. L'hétérogénéité des systèmes, la répartition des processus, l'omniprésence des réseaux, rendent la tâche du concepteur et du développeur encore plus difficile. Le « paradigme » de programmation orientée-objet n'a rien résolu puisqu'il exige de distribuer non seulement les processus de traitements informatiques mais aussi les processus métiers : le résultat d'une invocation d'une méthode d'un objet métier peut dépendre de l'invocation d'une dizaine, centaine ou millier d'objets éventuellement répartis sur un réseau.

Les plate-formes de composants n'ont pas mieux réussi à simplifier le problème et ont même plutôt accru la fragilité des applications en les rendant dépendantes de services techniques. Ces derniers sont parfois difficiles à appréhender et toujours délicats à intégrer dans une conception de par la multiplication des fichiers de configurations divers et des contraintes de programmation et de conception. Par exemple, la réalisation d'une application web classique sur plate-forme J2EE suppose non seulement d'être capable de programmer en Java mais en plus de maîtriser la syntaxe des fichiers de configuration de Struts, de l'application Web, du serveur d'application, des fichiers de description de propriétés, des descripteurs de déploiement ... Les ateliers de développement, s'ils permettent d'alléger certaines tâches, ne résolvent pas tout.

#### 1.2.2 Cohérence des éléments du développement

Le processus de développement, considéré à partir de l'expression des besoins, n'est absolument pas incrémental ni itératif mais est bien plus proche d'un modèle en cascade traditionnel : les phases d'analyse, de conception et de développement s'enchaînent dans un ordre descendant mais sans que l'information ne

puisse « remonter la cascade ». Au final, il est fréquent que les documents d'analyse et de conception soient obsolètes lors de la livraison. Au mieux, ils sont écrits *a posteriori* en fonction du code effectivement livré.

Ce problème provient de l'absence de lien direct et surtout automatisé avec la réalisation concrète du logiciel, autrement dit du découplage entre les modèles et le code. Même dans les domaines où le code est généré à partir de modèles, l'information est à sens unique et il est difficile d'intégrer à la fois les développements manuels et la production automatisée d'une partie du code.

Enfin, nombre de développements sont des *redéveloppements*. On suppose donc que le travail d'analyse a déjà été fait et on en fait l'économie. Malheureusement, les processus évoluent aussi et sont rarement indépendants des technologies qui permettent de les mettre en œuvre. Les documents sur lesquels sont basés des redéveloppements sont donc souvent obsolètes, incomplets voire faux, d'où l'impossibilité de valider les logiciels produits *a priori* et de manière mécanique.

#### 1.2.3 Interpénétration des domaines

Les fonctionnalités de l'application se trouvent souvent mélangées à des éléments réglant la navigation et l'accès de l'utilisateur à ces différentes fonctions. C'est particulièrement le cas dans les éléments d'IHM, qui mélangent niveaux de validation et règles de navigation. Il nous semble qu'il s'agit de problèmes strictement orthogonaux :

- l'application offre la possibilité à l'utilisateur de réaliser certaines opérations, ce sont les services offerts. Leur enchaînement, leur structure, leurs besoins, l'algorithmique sont détaillés par les différents documents décrivant les processus et le métier. En particulier, les enchaînements de processus nécessaires ou possibles sont modélisés sous la forme de diagrammes d'activités ou automates d'états finis :

- l'IHM est une traduction à l'usage des opérateurs humains interagissant avec le système du comportement attendu du système. En particulier, les enchaînements imposés et les actions activées et inactivées du système en fonction de l'état de l'activité se trouvent réalisés graphiquement par des modifications d'écran et d'attributs des éléments composant l'IHM.

On retrouve le même problème dans la couche composants/persistance. Le problème de la persistance des objets métiers se trouve traité au même niveau que celui de leur définition et de leur manipulation. Des objets purement mécaniques tels que les *objets données* se trouvent présents dans la modélisation alors même qu'ils sont automatiquement générés par des règles de projection. Enfin, la structure des tables relationnelles se trouve reproduite dans le modèle qui *de facto* perd ainsi sa structure objet.

#### 1.2.4 Formalisation

Au sein des phases d'analyse et de conception elles-mêmes, la cohérence entre les modèles et le respect d'un certain nombre de règles générales ne sont pas systématiquement vérifiés. Si les normes de conception et de modélisation (UML, OCL, RUP ...) prévoient effectivement des règles de validation croisées et de respect de cohérences, les outils disponibles ne sont pas toujours capables de vérifier le respect de ces règles. Par ailleurs, l'écriture de règles nécessite une expertise spécifique qui est rarement présente.

Les modèles d'analyse et de conception ne sont donc pas tels quels vérifiables automatiquement. Leur cohérence est assurée par des règles de nommage qui ne sont pas toujours respectées à la lettre, la dynamique et les algorithmes sont documentés en commentaires sous la forme de pseudo-code non formalisé et donc non interprétable, les modèles d'analyse (diagrammes d'activités) ne sont pas suffisamment précis pour permettre de dériver automatiquement des scénarios de tests (quand bien même ceci est prévu dans le processus, voir ci-dessus).

La structure des modèles n'est pas suffisamment congruente avec l'architecture finale, ni liée au code développé, pour permettre de faire des liens et déductions automatiques et générer éventuellement des squelettes de tests unitaires. Ces modèles ne sont pas maintenus d'une étape à une autre, ce qui produit donc des dérives entre phases qui rendent rapidement la tâche de génération automatique impossible. Ce problème est crucial lors de la *réutilisation* de modèles et d'applications existants : si modèles et codes ne sont pas congruents, la conception de la nouvelle application ne peut réutiliser tels quels les anciens modèles. La production de tests unitaires pour les différents composants du système devient plus difficile

car elle nécessite de la part des équipes de développement de se plonger dans les détails de la documentation d'analyse et de conception pour évaluer les fonctionnalités attendues de tel ou tel objet.

Cette absence de formalisation est aussi un problème aux extrémités de la chaîne puisque les imprécisions dans l'expression des besoins et l'analyse des fonctionnalités de l'application rendent très difficile la mise en œuvre de stratégies de tests système et de tests d'intégration efficaces pour améliorer la qualité de l'application avant le passage en recette. Un grand nombre d'erreurs triviales sont ainsi repérées, parfois avec difficulté, lors de cette phase de recette alors qu'elles auraient pu être détectées plus tôt.

#### 1.2.5 Architecture

Le gros point noir du processus de développement, duquel découle une grande partie des autres problèmes, est l'absence d'un modèle global d'architecture de l'application et d'un découpage clair de celle-ci à différents niveaux de détails. Bien sûr, cette architecture existe et le découpage réalisé lors de la réalisation du cahier des charges et/ou de l'urbanisation du système d'information est repris lors des phases du développement.

Mais aucun modèle n'offre une vue d'ensemble synthétique du système, ni la possibilité de visiter les éléments du système de manière hiérarchique ou thématique : par couche ou par domaine fonctionnel. Les différents modèles sont découpés en fonction des phases du processus, et nous l'avons vu, il n'est pas prévu la possibilité de revenir sur des diagrammes plus abstraits en fonction de choix et de découvertes faits à des niveaux plus concrets.

Le résultat net est une extraordinaire complexité des modèles dans les détails desquels l'utilisateur se trouve très rapidement noyé. Cette complexité est mieux maîtrisée dans le code écrit qui se trouve structuré de manière plus évidente et pour lequel les outils de construction offrent une vue synthétique rapide.

Alors même que l'on parle beaucoup de composants, tant pour ce qui concerne les plate-formes que pour la structuration des applications et du processus de développement, on se rend compte que ces composants ne sont pas des concepts utilisés lors de l'analyse et de la conception. Dans les développements, seuls les composants imposés par l'infrastructure technique apparaissent : EJB, Servlets, éventuellement connecteurs JCA pour la couche persistance. Rien dans les modèles d'analyse ou de conception ne permet de déduire une structure compositionnelle de l'application : il n'y a pas de définition explicite de composants et pas de schéma d'architecture représentant les différents composants et leurs interactions.

#### 1.3 Préconisation

Il n'y a bien sûr pas de solution unique pour résoudre cet ensemble de problèmes, et il est même certain qu'il est impossible de les résoudre complètement, mais l'expérience même de Norsys sur d'autres technologies a montré qu'il était possible d'*industrialiser* les développements pour accroître leur qualité et leur productivité. Nous avons déjà signalé les travaux d'E.RENAUX sur le *Processus Unifié de Composants* — CUP — [137] réalisés dans le cadre d'une collaboration avec Norsys.

Le point clé de cette démarche consiste à identifier les composants le plus tôt possible, dès la modélisation des exigences de l'utilisateur au travers des *cas d'utilisations*. Cette identification précoce permet d'assurer lors des phases ultérieures de conception et de développement un suivi continu. Cette approche est articulée autour de la notion de composant logique correspondant à un méta-modèle et concrétisée en quatre vues complémentaires basées sur ce méta-modèle :

- 1. la vue des cas d'utilisation;

- 2. la vue d'interactions;

- 3. la vue de conception;

- 4. et la vue d'assemblage.

D'autre travaux de recherche sont en cours dans l'entreprise sur les problèmes de la réingénierie d'applications patrimoniales — J.HATTAT — et de la séparation des préoccupations par des *aspects* de conception — D.DIAZ.

De notre côté, nous avons focalisé notre travail sur les deux points suivants :

1.3. PRÉCONISATION 23

la mise en place d'une architecture à base de composants contractualisés depuis l'analyse jusqu'à la réalisation;

- l'amélioration de la qualité des dits composants par la génération automatisée de tests fonctionnels.

### 1.3.1 Pour une architecture des logiciels

Le meilleur processus de fabrication non informatique auquel on peut comparer la conception et la réalisation d'un système d'information est celui de la conception et de la réalisation d'un bâtiment ou d'un ouvrage d'art. Dans chacun des cas :

- le produit final est unique;

- il fait appel à la compétence d'une multitude de métiers ;

- il nécessite une vision à la fois générale et détaillée;

- il est soumis aux mêmes contraintes dans ses rapports avec l'utilisateur, contraintes exprimées au travers d'un cahier des charges;

- son résultat ne peut-être évalué in fine que par l'usage qui en est fait ;

- il peut s'inscrire dans un ensemble pré-existant ou être conçu ex nihilo;

- il peut produire un résultat dont la qualité va de désastreuse le terminal T3 de l'aéroport Roissy-Charles-de-Gaulle ou la première version d'Amadeus, le système de réservation de la SNCF à admirable Taliesin par Frank Lloyd Wright ou le système d'exploitation Unix;

- il peut être prévu pour durer la cathédrale de Chartres ou Internet ou être jetable ;

- les deux marchés représentent à l'échelle mondiale des tailles comparables et considérables \$3500 milliards pour le génie civil, \$1322 milliards pour les services des technologies de l'information;

- enfin, il rentre dans le jugement que l'on peut en faire une part essentielle de critères esthétiques.

De cette analogie, on peut inférer que le concept central au cœur de l'activité de conception et de réalisation de logiciels est celui d'*architecture*. L'architecture est ici comprise non pas uniquement dans sa dimension purement conceptuelle de production de formes, d'agencements de structures et de réalisation de plans, mais aussi dans sa dynamique concrète en tant que point d'articulation entre les différents acteurs d'un processus et leurs contraintes.

Un composant est donc dans cette vision architecturale la matérialisation dans un plan plus large d'un concept et d'un ensemble de contraintes, une partie d'un tout. Il est nécessairement défini par les relations qu'il entretient avec les autres composants du plan. De plus, un composant peut être lui même composé de parties concourant à la réalisation de ses fonctions. Une architecture est donc de manière duale définie comme un agencement de composants dans l'objectif de fournir un ensemble de fonctionnalités. Sans composants, pas d'architecture; sans architecture, pas de composants.

Nous n'avons pas la prétention de penser que ce point de vue soit original mais il nous paraît essentiel, et c'est tout l'enjeu de ce travail, de réaffirmer son importance et surtout de se donner les moyens de le rendre opérationnel.

#### Compositionnalité

De toute évidence, les composants doivent pouvoir être composés pour former à leur tour de nouveaux composants, plus gros ou plus généraux. Inversement, un composant doit pouvoir être arbitrairement décomposé en divers constituants détaillant ses fonctionnalités.

Toutes les exigences qu'un composant impose à son environnement doivent être explicitement spécifiées. Les fonctionnalités ainsi que les dépendances d'un composant doivent être exprimées *contractuellement*, en termes des relations qu'il entretient avec son environnement et non pas en termes de la structure interne du composant.

Les relations que les composants entretiennent entre eux sont ainsi toujours exprimées par des *contrats bilatéraux* : un composant ne peut subordonner l'exécution d'un service à la réalisation par un tiers d'un autre service ou d'une obligation d'un autre contrat. De la sorte, tout composant devient substituable à un autre pour autant qu'il remplisse chaque obligation contractuelle déléguée par la substitution.

Ces relations peuvent être décrites soit comme des *connecteurs*, auquel cas la sémantique des relations entre composants est exogène, soit comme un ensemble de propriétés générales du système dans lequel sont plongés les composants.

#### **Formalisation**

Le comportement d'un composant et la structure d'une architecture doivent pouvoir être définis formellement, c'est-à-dire associés à une sémantique non ambiguë et susceptible d'être vérifiable, même partiellement, par des moyens mécaniques. De même, une architecture donnée — un agencement de composants — doit pouvoir être validée mécaniquement en fonction de règles de cohérence générales.

Il doit donc être possible d'exprimer des propriétés et de vérifier que ces propriétés sont bien présentes dans l'architecture. Les propriétés exprimables doivent au minimum être les propriétés de *sûreté*, c'est-àdire une propriété exprimant l'impossibilité de survenue d'un événement.

Enfin, une architecture doit se prêter à toute opération de *raffinement* consistant à appliquer une transformation produisant une nouvelle architecture correcte à un niveau d'abstraction différent de l'architecture de départ.

#### **Abstraction & concrétion**

Un composant doit être une *abstraction* indépendante de toute implantation mais susceptible de s'incarner dans la plus grande palette possible de plate-formes techniques. Autrement dit, un composant est un *modèle*. De plus, si un composant est formellement spécifié et indépendant de toute plate-forme, il doit pouvoir être *concrétisé* mécaniquement de sorte que le résultat soit par construction une implantation conforme et exécutable.

De manière symétrique, étant donnés un composant et une réalisation concrète de ce composant, il doit être possible de vérifier mécaniquement que la réalisation concrète est conforme aux propriétés attendues du composant.

Les données, leur structure, leurs propriétés et leurs transformations constituant la majeure partie des fonctionnalités d'un système d'information, leur définition et leur manipulation doivent être prises en compte dans la description des propriétés des composants, ce à un niveau d'abstraction adéquat avec la représentation du *métier* que ces éléments modélisent.

#### Synthèse

En résumé, nous attendons d'un modèle d'architecture de composants qu'il soit :

- simple à manipuler avec un nombre de concepts restreints ;

- formel:

- exécutable;

- testable :

- compositionnel et hiérarchique.

#### 1.3.2 Test & fiabilité

Pour s'assurer de la validité d'un logiciel par rapport au cahier des charges, on peut appliquer le principe des *méthodes formelles*: partir d'une expression abstraite et non ambiguë des exigences, et réaliser, par des étapes de raffinement et de preuve du maintien des propriétés du niveau précédent, différents modèles de plus en plus détaillés, jusqu'à obtenir un modèle suffisamment précis pour qu'il soit possible de le traduire directement dans un langage d'implantation concret. C'est la stratégie des méthodes telles que B, Z ou VDM, illustrée dans la figure 1.6.

FIG. 1.6 – Développement formel par raffinement.

1.3. PRÉCONISATION 25

Cette méthode présente l'avantage évident de produire une application dont la validité eu égard aux spécifications est *prouvée*, sous réserve de la preuve de correction de la projection terminale d'un modèle en code.

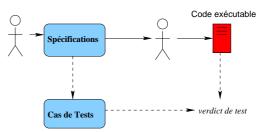

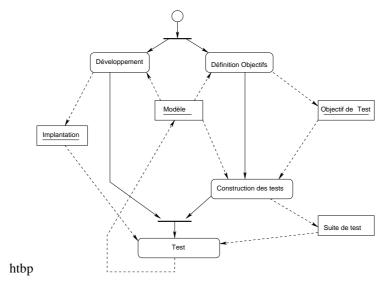

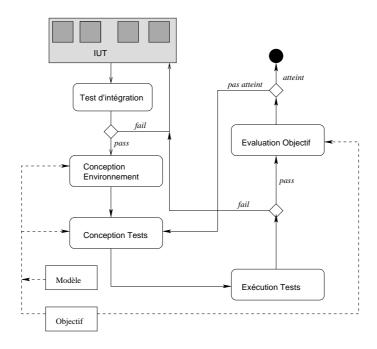

Une autre solution est, toujours à partir d'une expression formelle des exigences, de produire automatiquement des *cas de test* qui permettront à l'issue du processus de développement de valider le logiciel produit : c'est ce qu'illustre la figure 1.7.

La première solution est aujourd'hui inaccessible dans le contexte qui est le nôtre, pour un certain nombre de raisons : le niveau de fiabilité exigé dans les applications de systèmes d'informations est nettement moins élevé que dans des systèmes critiques temps réels ; le coût de la mise en œuvre de méthodes formelles est très élevé, surtout compte tenu du fait que la phase de preuve ne peut être totalement automatisée ; l'intérêt de mettre en place un tel processus dans des systèmes hétérogènes en constante évolution paraît limité.

FIG. 1.7 – Développement formel par test.

La seconde solution est plus aisée à mettre en place. Elle exige toutefois un certain nombre de prérequis : l'existence d'une spécification suffisamment formalisée pour permettre la dérivation automatique de cas de tests pertinents; le maintien d'une cohérence dans le processus de développement permettant de faire en sorte que les cas de tests produits initialement restent applicables à l'autre bout de la chaîne, c'est-à-dire lors de la construction du logiciel fini; l'existence de procédures automatiques fiables et de mesures de la fiabilité atteinte par l'exécution d'un ensemble donné de tests.

Nous partons donc de l'hypothèse que le processus de développement par raffinement formalisé restera encore longtemps impraticable pour la majeure partie des développements. Il y aura donc encore longtemps production de deux artefacts disjoints : un *modèle* ou spécification des fonctionnalités attendues de l'application, et l'*application* elle-même. Par conséquent, il restera nécessaire de disposer des processus permettant de valider et vérifier avec le maximum de précision possible la conformité entre les spécifications et le résultat final. De la même manière que pour un bâtiment, tant que l'on ne saura pas produire automatiquement un bâtiment à partir des plans de l'architecte, il sera indispensable de disposer d'outils permettant le contrôle du processus de construction : suivi de chantier, bureau de vérification, certificat de conformité, normes, qualifications ...

## Chapitre 2

# **Architecture & composants**

Nous avons, dans le chapitre 1, insisté sur le besoin d'une conception formalisée de l'architecture des logiciels. Nous avons aussi conclu que la notion d'architecture était liée à la notion de composants. Ce chapitre sera donc consacré à ce qu'il est convenu d'appeler l'état de l'art dans le domaine de la modélisation, de la spécification et de la réalisation d'architecture de systèmes à base de composants.

Nous partirons des outils et plate-formes orientées-composant concrètes, dans lesquelles un composant est une entité logicielle bien définie, s'insérant dans un modèle d'exécution et de communication lui aussi précis. Le développement sur ces plate-formes — J2EE, Corba, .Net — constituent aujourd'hui une part importante de l'activité des sociétés de services. Nous essaierons de comprendre pourquoi ces plate-formes ont échoué à améliorer la qualité des logiciels.

Ceci nous mènera naturellement à l'étude d'un certain nombre de propositions pour la conception d'architectures. À partir des outils de modélisation proposés autour du langage UML, nous nous intéresserons plus particulièrement aux nombreux travaux autour des *Langages de Description d'Architecture* — ADL en anglais. Sachant qu'il existe déjà des excellentes synthèses sur les ADL les plus anciens, nous nous concentrerons sur quelques propositions plus récentes du domaine.

Enfin, nous aborderons certains modèles plus théoriques qui s'intéressent à la composition de composants possédant une description comportementale formalisée.

## 2.1 Plate-formes de composants

Une définition très fréquemment reprise du terme de composant est celle proposée dans Szyperski [150] (p.36, traduction par nos soins) :

« Un composant logiciel est une unité de composition avec des interfaces contractuellement spécifiées et des dépendances uniquement contextuelles. Un composant logiciel peut être déployé de manière indépendante et composé par des éléments tiers. »

Cette définition est axée comme l'ensemble de l'ouvrage cité sur une vision essentiellement *technologique* et économique de la notion de composants : le problème considéré est celui de la construction de logiciels à partir de composants réutilisables et du développement subséquent d'un *marché* de composants.

Cette première partie présente les outils répondant à cette définition : les *plate-formes à composants* ou *intergiciels à composants*. Trois acteurs de taille inégale se partagent aujourd'hui ce marché : Java et J2EE qui en possèdent la plus grand part, .Net qui est la réponse de MICROSOFT et qui prend de l'ampleur, et Corba et le *Corba Component Model* — ou CCM — qui est conceptuellement la meilleure proposition des trois mais qui reste marginale. Nous inclurons dans cette catégorie Fractal qui se présente comme une plate-forme de composants, bien qu'elle ne soit pas encore présente dans le domaine des services logiciels.

La seconde partie de cette section s'intéressera à des technologies plus récentes et moins ambitieuses qui visent à pallier à la grande complexité de mise en œuvre des intergiciels. Ces technologies sont généralement inspirées des *langages de configuration* et offrent essentiellement un *cadre méthodologique* basé sur la notion de composants.

#### 2.1.1 Intergiciels à composants

Les intergiciels sont nés de la volonté de résoudre le problème de la *distribution* des applications sur un ensemble de systèmes inter connectés par un réseau. L'objectif initial et à ce jour non atteint était de rendre *transparente* pour le développeur et l'utilisateur la structure répartie des applications. Pour le développeur, il s'agissait par ailleurs de faciliter le développement, le déploiement et la maintenance de telles applications. Les intergiciels que nous étudions ici ne constituent qu'une réponse parmi d'autres possibles à ce problème et l'on trouvera dans Tannenbaum et van Steen [151] une introduction complète et accessible sur les autres solutions techniques.

Tous les intergiciels à composants s'appuient sur un certain nombre de concepts communs :

- la notion de *conteneur* qui assure la séparation des préoccupations entre les aspects techniques des logiciels répartis et les aspects fonctionnels;

- l'adressage symbolique médiatisé par un système d'annuaire dynamique ou serveur de nommage qui minimise le couplage entre les entités d'un système;

- le serveur d'application qui orchestre l'exécution effective des applications.

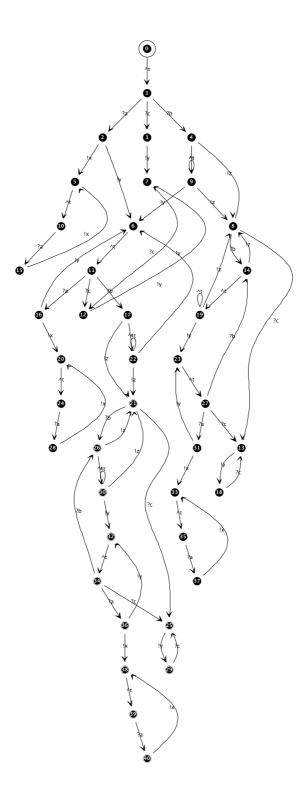

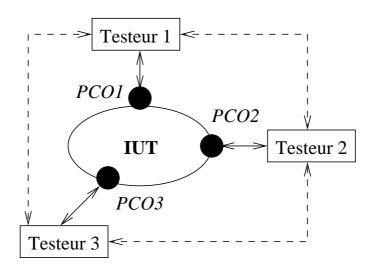

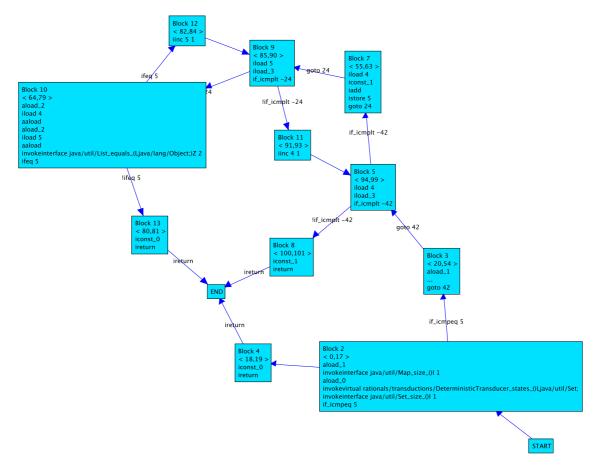

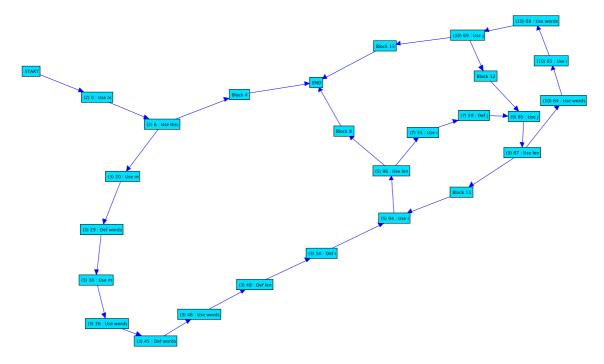

#### J2EE